RISC vs CISC: Which Offers Better Energy Optimization?

MAR 26, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

RISC vs CISC Energy Optimization Background and Goals

The fundamental architectural divide between Reduced Instruction Set Computing (RISC) and Complex Instruction Set Computing (CISC) has shaped processor design philosophy for decades. RISC architectures emerged in the 1980s as a response to the growing complexity of CISC designs, advocating for simplified instruction sets that could execute more efficiently. CISC processors, exemplified by x86 architectures, feature rich instruction sets capable of performing complex operations in single instructions, while RISC processors like ARM and RISC-V emphasize simple, uniform instructions that execute in fewer clock cycles.

The evolution of both architectures has been driven by the relentless pursuit of computational efficiency, but energy optimization has become increasingly critical in recent years. The proliferation of mobile devices, IoT systems, and battery-powered computing platforms has elevated energy efficiency from a secondary consideration to a primary design constraint. This shift has fundamentally altered the competitive landscape between RISC and CISC architectures.

Modern computing demands span from ultra-low-power embedded systems requiring months of battery life to high-performance data centers where energy costs represent significant operational expenses. The challenge lies in determining which architectural approach provides superior energy optimization across these diverse application domains. Traditional performance metrics focused primarily on computational throughput and clock speeds, but contemporary evaluation frameworks must incorporate power consumption, thermal management, and energy-per-operation metrics.

The primary objective of this technical investigation is to establish a comprehensive framework for evaluating energy optimization capabilities of RISC versus CISC architectures. This analysis aims to identify the fundamental architectural characteristics that influence energy efficiency, examine real-world performance data across various application scenarios, and determine optimal use cases for each approach.

Furthermore, this research seeks to understand how emerging technologies such as advanced manufacturing processes, dynamic voltage scaling, and specialized execution units impact the energy efficiency equation. The goal extends beyond simple architectural comparison to provide actionable insights for system designers, enabling informed decisions based on specific application requirements, performance targets, and energy constraints.

The evolution of both architectures has been driven by the relentless pursuit of computational efficiency, but energy optimization has become increasingly critical in recent years. The proliferation of mobile devices, IoT systems, and battery-powered computing platforms has elevated energy efficiency from a secondary consideration to a primary design constraint. This shift has fundamentally altered the competitive landscape between RISC and CISC architectures.

Modern computing demands span from ultra-low-power embedded systems requiring months of battery life to high-performance data centers where energy costs represent significant operational expenses. The challenge lies in determining which architectural approach provides superior energy optimization across these diverse application domains. Traditional performance metrics focused primarily on computational throughput and clock speeds, but contemporary evaluation frameworks must incorporate power consumption, thermal management, and energy-per-operation metrics.

The primary objective of this technical investigation is to establish a comprehensive framework for evaluating energy optimization capabilities of RISC versus CISC architectures. This analysis aims to identify the fundamental architectural characteristics that influence energy efficiency, examine real-world performance data across various application scenarios, and determine optimal use cases for each approach.

Furthermore, this research seeks to understand how emerging technologies such as advanced manufacturing processes, dynamic voltage scaling, and specialized execution units impact the energy efficiency equation. The goal extends beyond simple architectural comparison to provide actionable insights for system designers, enabling informed decisions based on specific application requirements, performance targets, and energy constraints.

Market Demand for Energy-Efficient Processor Architectures

The global semiconductor market is experiencing unprecedented demand for energy-efficient processor architectures, driven by the convergence of multiple technological and environmental factors. Mobile computing devices, including smartphones, tablets, and wearables, represent the largest segment demanding low-power processors. These devices require extended battery life while maintaining high performance, creating a critical need for architectures that can optimize energy consumption without compromising computational capabilities.

Data centers and cloud computing infrastructure constitute another major demand driver for energy-efficient processors. As digital transformation accelerates across industries, the power consumption of server farms has become a significant operational cost and environmental concern. Organizations are actively seeking processor architectures that can deliver superior performance-per-watt ratios to reduce electricity costs and meet sustainability targets.

The Internet of Things ecosystem is generating substantial demand for ultra-low-power processor architectures. Edge computing devices, sensors, and embedded systems require processors that can operate for extended periods on battery power or energy harvesting systems. This market segment particularly values architectures that can maintain functionality while consuming minimal energy during idle states.

Automotive electronics represent an emerging high-growth segment for energy-efficient processors. Electric vehicles require sophisticated computing capabilities for autonomous driving features, infotainment systems, and battery management, while maintaining optimal energy efficiency to preserve driving range. The automotive industry's transition toward electrification is creating new requirements for processor architectures that can balance computational performance with energy conservation.

Enterprise computing environments are increasingly prioritizing energy efficiency due to rising electricity costs and corporate sustainability initiatives. Organizations are evaluating processor architectures based on total cost of ownership, which includes both initial hardware costs and long-term energy consumption. This trend is particularly pronounced in high-performance computing applications where energy costs can exceed hardware acquisition costs over the system lifecycle.

The regulatory landscape is also shaping market demand, with governments implementing energy efficiency standards and carbon reduction mandates. These policies are compelling manufacturers to prioritize energy-optimized processor architectures in their product development strategies, creating sustained market pressure for more efficient computing solutions across all application domains.

Data centers and cloud computing infrastructure constitute another major demand driver for energy-efficient processors. As digital transformation accelerates across industries, the power consumption of server farms has become a significant operational cost and environmental concern. Organizations are actively seeking processor architectures that can deliver superior performance-per-watt ratios to reduce electricity costs and meet sustainability targets.

The Internet of Things ecosystem is generating substantial demand for ultra-low-power processor architectures. Edge computing devices, sensors, and embedded systems require processors that can operate for extended periods on battery power or energy harvesting systems. This market segment particularly values architectures that can maintain functionality while consuming minimal energy during idle states.

Automotive electronics represent an emerging high-growth segment for energy-efficient processors. Electric vehicles require sophisticated computing capabilities for autonomous driving features, infotainment systems, and battery management, while maintaining optimal energy efficiency to preserve driving range. The automotive industry's transition toward electrification is creating new requirements for processor architectures that can balance computational performance with energy conservation.

Enterprise computing environments are increasingly prioritizing energy efficiency due to rising electricity costs and corporate sustainability initiatives. Organizations are evaluating processor architectures based on total cost of ownership, which includes both initial hardware costs and long-term energy consumption. This trend is particularly pronounced in high-performance computing applications where energy costs can exceed hardware acquisition costs over the system lifecycle.

The regulatory landscape is also shaping market demand, with governments implementing energy efficiency standards and carbon reduction mandates. These policies are compelling manufacturers to prioritize energy-optimized processor architectures in their product development strategies, creating sustained market pressure for more efficient computing solutions across all application domains.

Current Energy Consumption Challenges in RISC and CISC

RISC and CISC architectures face distinct energy consumption challenges that stem from their fundamental design philosophies and implementation approaches. These challenges have become increasingly critical as mobile computing, IoT devices, and data centers demand higher energy efficiency while maintaining performance standards.

RISC processors encounter energy consumption challenges primarily related to instruction fetch overhead and memory access patterns. The simplified instruction set requires more instructions to complete complex operations, leading to increased instruction cache misses and higher memory bandwidth requirements. This results in elevated dynamic power consumption during instruction fetching and decoding phases. Additionally, RISC architectures often require larger code sizes to accomplish equivalent tasks, creating pressure on memory subsystems and contributing to leakage power in expanded cache hierarchies.

CISC architectures face energy challenges centered around complex instruction decoding and execution unit utilization. The variable-length instruction format and sophisticated addressing modes demand substantial decoding logic, consuming significant static power even during idle periods. Complex instructions often require multiple microoperations, leading to inefficient pipeline utilization and increased switching activity in execution units. The extensive instruction set also necessitates larger decode logic and control units, contributing to higher leakage currents in advanced process nodes.

Both architectures struggle with power management granularity issues. RISC processors often lack fine-grained power control mechanisms due to their streamlined design, making it difficult to selectively disable unused functional units. CISC processors, while offering more sophisticated power management features, face challenges in accurately predicting instruction complexity for dynamic voltage and frequency scaling decisions.

Thermal management presents another shared challenge, particularly in high-performance implementations. RISC processors may experience thermal hotspots due to concentrated activity in specific pipeline stages, while CISC processors face thermal challenges from complex decode units and large cache structures. Both architectures must balance performance optimization with thermal design power constraints.

Modern implementations of both architectures also confront challenges related to manufacturing process variations and aging effects, which can significantly impact energy efficiency over the processor's operational lifetime. These factors require sophisticated compensation mechanisms that add complexity and potential energy overhead to both RISC and CISC designs.

RISC processors encounter energy consumption challenges primarily related to instruction fetch overhead and memory access patterns. The simplified instruction set requires more instructions to complete complex operations, leading to increased instruction cache misses and higher memory bandwidth requirements. This results in elevated dynamic power consumption during instruction fetching and decoding phases. Additionally, RISC architectures often require larger code sizes to accomplish equivalent tasks, creating pressure on memory subsystems and contributing to leakage power in expanded cache hierarchies.

CISC architectures face energy challenges centered around complex instruction decoding and execution unit utilization. The variable-length instruction format and sophisticated addressing modes demand substantial decoding logic, consuming significant static power even during idle periods. Complex instructions often require multiple microoperations, leading to inefficient pipeline utilization and increased switching activity in execution units. The extensive instruction set also necessitates larger decode logic and control units, contributing to higher leakage currents in advanced process nodes.

Both architectures struggle with power management granularity issues. RISC processors often lack fine-grained power control mechanisms due to their streamlined design, making it difficult to selectively disable unused functional units. CISC processors, while offering more sophisticated power management features, face challenges in accurately predicting instruction complexity for dynamic voltage and frequency scaling decisions.

Thermal management presents another shared challenge, particularly in high-performance implementations. RISC processors may experience thermal hotspots due to concentrated activity in specific pipeline stages, while CISC processors face thermal challenges from complex decode units and large cache structures. Both architectures must balance performance optimization with thermal design power constraints.

Modern implementations of both architectures also confront challenges related to manufacturing process variations and aging effects, which can significantly impact energy efficiency over the processor's operational lifetime. These factors require sophisticated compensation mechanisms that add complexity and potential energy overhead to both RISC and CISC designs.

Existing Energy Optimization Solutions in Both Architectures

01 Power management through instruction set optimization

Energy optimization can be achieved by optimizing the instruction set architecture to reduce power consumption during instruction execution. This involves designing instruction formats and execution mechanisms that minimize switching activity and reduce the number of clock cycles required for common operations. Techniques include instruction compression, efficient encoding schemes, and selective execution of instructions based on power states.- Power management through instruction set optimization: Energy optimization can be achieved by optimizing the instruction set architecture to reduce power consumption during instruction execution. This involves designing instruction formats and execution mechanisms that minimize switching activity and reduce the number of clock cycles required for common operations. The approach focuses on balancing performance with energy efficiency through careful instruction set design that considers both RISC and CISC architectural principles.

- Dynamic voltage and frequency scaling techniques: Energy optimization is accomplished through dynamic adjustment of operating voltage and clock frequency based on workload requirements. The processor can scale its performance and power consumption by detecting instruction complexity and computational demands, then adjusting voltage and frequency accordingly. This technique is particularly effective for both architecture types as it adapts to varying processing needs in real-time.

- Instruction pipeline and execution unit power gating: Power consumption is reduced by selectively disabling unused pipeline stages and execution units during operation. This approach involves monitoring instruction flow and identifying opportunities to gate power to inactive functional units. The technique applies to both architectural styles by recognizing when certain processing resources are idle and temporarily shutting them down to conserve energy while maintaining system responsiveness.

- Instruction cache and memory hierarchy optimization: Energy efficiency is improved through optimized cache design and memory access patterns that reduce the frequency and energy cost of memory operations. This includes implementing intelligent cache management policies, prefetching strategies, and memory hierarchy organizations that minimize power-hungry memory accesses. The optimization considers the different instruction fetch patterns characteristic of each architecture type.

- Hybrid architecture and instruction translation for energy efficiency: Energy optimization is achieved by combining advantages of both architectures through hybrid designs or dynamic instruction translation mechanisms. This approach allows the system to execute instructions using the most energy-efficient method available, whether through simple RISC-style operations or complex CISC-style instructions. The system can adaptively choose execution strategies based on power and performance requirements.

02 Dynamic voltage and frequency scaling for processors

Both RISC and CISC architectures can implement dynamic voltage and frequency scaling to optimize energy consumption based on workload requirements. The processor adjusts its operating voltage and clock frequency in real-time to match the computational demands, reducing power consumption during low-intensity tasks while maintaining performance during high-demand operations. This approach is particularly effective in mobile and embedded systems.Expand Specific Solutions03 Pipeline architecture and execution unit optimization

Energy efficiency can be improved through optimized pipeline design and execution unit management in both architecture types. This includes techniques such as pipeline gating, selective activation of functional units, and efficient branch prediction to reduce unnecessary computations. The optimization focuses on minimizing idle power consumption and reducing the energy cost of instruction processing through intelligent resource allocation.Expand Specific Solutions04 Cache memory hierarchy and power optimization

Implementing efficient cache memory hierarchies with power-aware policies helps reduce energy consumption in processor architectures. This involves designing cache structures with selective activation, implementing low-power cache access modes, and optimizing data placement strategies to minimize memory access energy. The approach reduces the frequency of high-power main memory accesses while maintaining performance.Expand Specific Solutions05 Instruction scheduling and compiler optimization techniques

Energy optimization through intelligent instruction scheduling and compiler-level optimizations that consider power consumption characteristics of different instruction types. This includes reordering instructions to minimize pipeline stalls, grouping operations to enable power gating opportunities, and selecting instruction sequences that result in lower energy consumption. The techniques work at both hardware and software levels to achieve optimal energy efficiency.Expand Specific Solutions

Key Players in RISC and CISC Processor Development

The RISC vs CISC energy optimization debate reflects a mature semiconductor industry undergoing significant transformation toward power-efficient computing. The market, valued at hundreds of billions globally, is driven by mobile computing, IoT, and AI workloads demanding better performance-per-watt ratios. Technology maturity varies significantly across players: Intel and Qualcomm lead with advanced CISC and RISC implementations respectively, while Samsung and Texas Instruments excel in specialized low-power designs. Google's custom silicon initiatives and Huawei's ARM-based processors demonstrate growing in-house capabilities. Traditional players like IBM maintain relevance through specialized applications, while emerging companies like Wolfspeed focus on wide-bandgap semiconductors for next-generation efficiency. The competitive landscape shows convergence between architectures, with hybrid approaches becoming prevalent as companies prioritize energy optimization over pure architectural philosophy.

Intel Corp.

Technical Solution: Intel has developed hybrid architectures combining CISC x86 cores with energy-efficient designs, implementing advanced power management techniques including dynamic voltage and frequency scaling (DVFS), turbo boost technology, and fine-grained clock gating. Their latest processors feature multiple power states and can dynamically adjust performance per core based on workload demands. Intel's approach focuses on maintaining CISC compatibility while optimizing energy consumption through architectural enhancements like out-of-order execution improvements and cache hierarchy optimizations that reduce memory access power consumption.

Strengths: Mature CISC optimization techniques, extensive software ecosystem compatibility, advanced manufacturing processes. Weaknesses: Higher baseline power consumption compared to RISC alternatives, complex instruction decoding overhead.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung develops both RISC-based Exynos processors and memory solutions optimized for energy efficiency. Their approach includes implementation of advanced FinFET manufacturing processes that reduce leakage current and overall power consumption. Samsung's energy optimization strategy incorporates intelligent frequency scaling, thermal management systems, and specialized low-power memory architectures. Their processors feature multiple voltage domains and can selectively power down unused functional units, achieving significant energy savings in mobile and IoT applications through careful balance of performance and power consumption.

Strengths: Advanced semiconductor manufacturing capabilities, integrated memory and processor optimization, strong mobile market presence. Weaknesses: Limited market penetration in high-performance computing, dependency on ARM licensing for RISC designs.

Core Patents in RISC and CISC Power Management

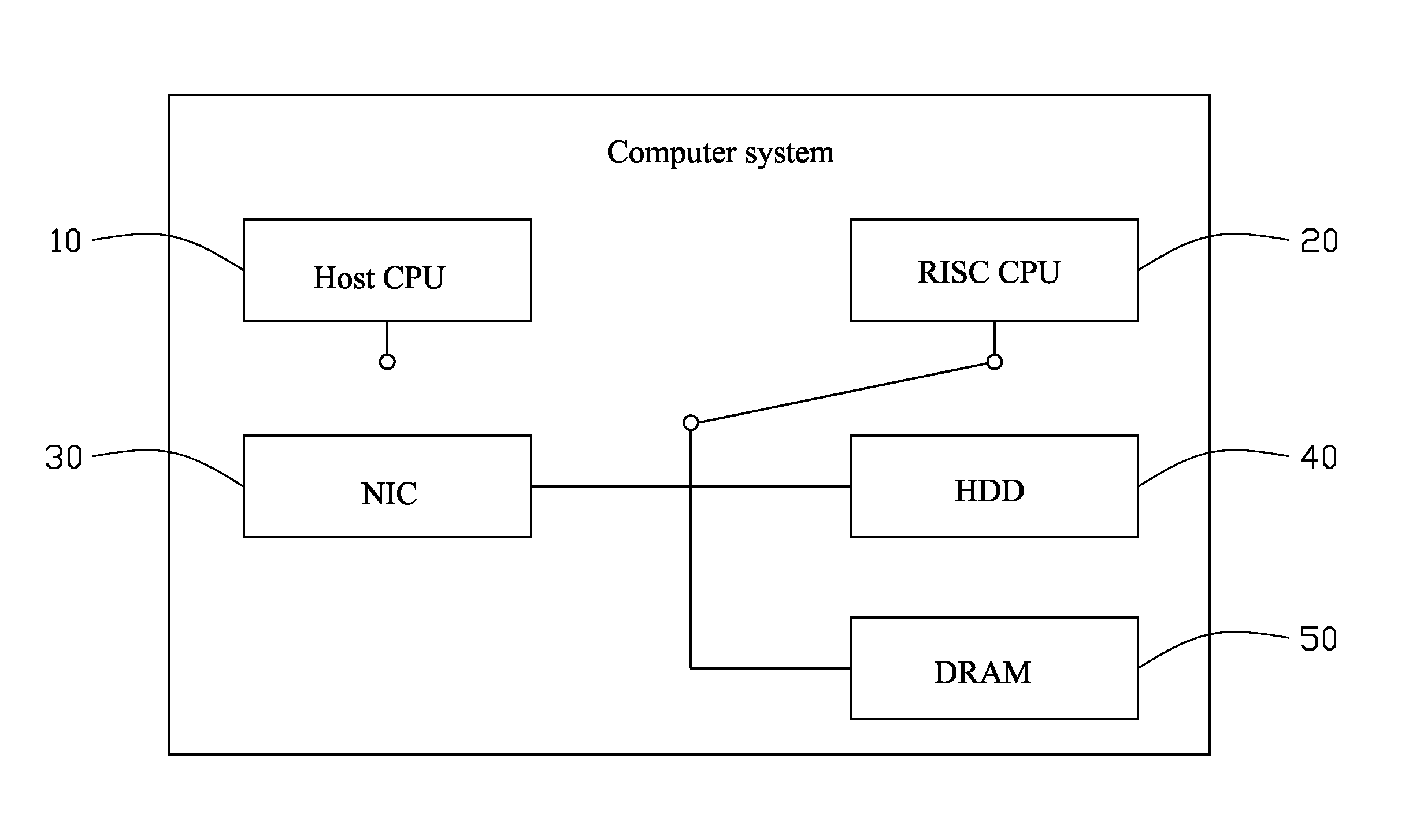

Computer system

PatentInactiveUS20100005235A1

Innovation

- A computer system utilizing a reduced instruction set computing (RISC) CPU, which takes over specific tasks from a host CPU during shutdown, minimizing resource usage and power consumption by only powering necessary components, such as a network interface card and keyboard, with the OS loaded from the HDD to DRAM, allowing designated tasks to be completed efficiently and securely.

Pipeline controller for context-based operation reconfigurable instruction set processor

PatentInactiveUS7669042B2

Innovation

- A context-based operation reconfigurable instruction set processor (CRISP) with an optimized instruction execution pipeline that includes an instruction fetch, decode, execution, and write-back stage, where repetitive instructions are fetched and decoded only once and stored for subsequent iterations, reducing pipeline stage activity and power consumption.

Industry Standards for Processor Energy Efficiency

The semiconductor industry has established comprehensive standards and benchmarks to evaluate processor energy efficiency, providing crucial frameworks for comparing RISC and CISC architectures. These standards serve as essential tools for manufacturers, system designers, and researchers to assess and optimize energy consumption across different processor implementations.

The most widely adopted standard is the Standard Performance Evaluation Corporation (SPEC) benchmark suite, particularly SPECpower_ssj2008 and its successor SPECpower_ssj2016. These benchmarks measure server-side Java operations per joule, providing normalized metrics that enable direct comparison between different processor architectures regardless of their underlying instruction set complexity. The benchmarks evaluate performance across various workload levels, from idle states to maximum utilization, offering comprehensive energy efficiency profiles.

IEEE 1621 standard defines the methodology for measuring and reporting energy efficiency in computing systems. This standard establishes protocols for power measurement accuracy, environmental conditions, and reporting formats that ensure consistency across different testing scenarios. The standard specifically addresses the challenges of comparing processors with different architectural approaches by focusing on workload-based energy consumption rather than theoretical power ratings.

The Energy Star program, administered by the EPA, has extended its certification criteria to include server processors and embedded systems. These criteria establish minimum energy efficiency thresholds and provide tiered ratings that help organizations select processors based on their energy performance characteristics. The program's metrics consider both active and idle power consumption, which is particularly relevant when comparing RISC and CISC processors that may exhibit different power scaling behaviors.

Industry consortiums such as the Green Grid have developed additional metrics like Power Usage Effectiveness (PUE) and Data Center Infrastructure Efficiency (DCiE) that, while focused on data center operations, influence processor selection criteria. These standards emphasize the importance of processor energy efficiency in overall system-level power optimization strategies.

Emerging standards from organizations like JEDEC are addressing energy efficiency in mobile and embedded applications, where the distinction between RISC and CISC architectures becomes particularly significant due to battery life constraints and thermal management requirements.

The most widely adopted standard is the Standard Performance Evaluation Corporation (SPEC) benchmark suite, particularly SPECpower_ssj2008 and its successor SPECpower_ssj2016. These benchmarks measure server-side Java operations per joule, providing normalized metrics that enable direct comparison between different processor architectures regardless of their underlying instruction set complexity. The benchmarks evaluate performance across various workload levels, from idle states to maximum utilization, offering comprehensive energy efficiency profiles.

IEEE 1621 standard defines the methodology for measuring and reporting energy efficiency in computing systems. This standard establishes protocols for power measurement accuracy, environmental conditions, and reporting formats that ensure consistency across different testing scenarios. The standard specifically addresses the challenges of comparing processors with different architectural approaches by focusing on workload-based energy consumption rather than theoretical power ratings.

The Energy Star program, administered by the EPA, has extended its certification criteria to include server processors and embedded systems. These criteria establish minimum energy efficiency thresholds and provide tiered ratings that help organizations select processors based on their energy performance characteristics. The program's metrics consider both active and idle power consumption, which is particularly relevant when comparing RISC and CISC processors that may exhibit different power scaling behaviors.

Industry consortiums such as the Green Grid have developed additional metrics like Power Usage Effectiveness (PUE) and Data Center Infrastructure Efficiency (DCiE) that, while focused on data center operations, influence processor selection criteria. These standards emphasize the importance of processor energy efficiency in overall system-level power optimization strategies.

Emerging standards from organizations like JEDEC are addressing energy efficiency in mobile and embedded applications, where the distinction between RISC and CISC architectures becomes particularly significant due to battery life constraints and thermal management requirements.

Sustainability Impact of Processor Architecture Choices

The choice between RISC and CISC processor architectures carries profound implications for environmental sustainability, extending far beyond immediate performance considerations. As global computing infrastructure continues to expand exponentially, the cumulative environmental impact of architectural decisions becomes increasingly significant for planetary resource management and climate change mitigation.

Energy consumption patterns differ substantially between RISC and CISC implementations, directly affecting carbon footprint calculations. RISC processors typically demonstrate superior energy efficiency per instruction due to their simplified instruction sets and streamlined execution pipelines. This efficiency translates to reduced electricity consumption across data centers, mobile devices, and embedded systems, potentially decreasing greenhouse gas emissions from power generation. Conversely, CISC architectures may require more complex circuitry and higher power consumption for equivalent computational tasks, though modern implementations have significantly narrowed this gap through advanced manufacturing processes and architectural optimizations.

Manufacturing sustainability represents another critical dimension of architectural choice impact. RISC processors often require fewer transistors and simpler fabrication processes, potentially reducing semiconductor manufacturing energy consumption and material waste. The simplified design philosophy can lead to higher manufacturing yields and reduced defect rates, minimizing resource wastage during production cycles. However, CISC processors may achieve better computational density, potentially reducing the total number of chips required for specific applications.

Lifecycle considerations reveal complex sustainability trade-offs between architectures. RISC-based systems may offer longer operational lifespans due to lower thermal stress and reduced component degradation from heat generation. This extended lifespan reduces electronic waste generation and decreases the frequency of hardware replacement cycles. Additionally, the modular nature of RISC designs often facilitates easier recycling and component recovery at end-of-life stages.

The proliferation of mobile and IoT devices amplifies these sustainability impacts across billions of deployed units. Even marginal improvements in per-device energy efficiency can yield substantial aggregate environmental benefits when multiplied across global device populations, making architectural choices increasingly consequential for sustainable technology development.

Energy consumption patterns differ substantially between RISC and CISC implementations, directly affecting carbon footprint calculations. RISC processors typically demonstrate superior energy efficiency per instruction due to their simplified instruction sets and streamlined execution pipelines. This efficiency translates to reduced electricity consumption across data centers, mobile devices, and embedded systems, potentially decreasing greenhouse gas emissions from power generation. Conversely, CISC architectures may require more complex circuitry and higher power consumption for equivalent computational tasks, though modern implementations have significantly narrowed this gap through advanced manufacturing processes and architectural optimizations.

Manufacturing sustainability represents another critical dimension of architectural choice impact. RISC processors often require fewer transistors and simpler fabrication processes, potentially reducing semiconductor manufacturing energy consumption and material waste. The simplified design philosophy can lead to higher manufacturing yields and reduced defect rates, minimizing resource wastage during production cycles. However, CISC processors may achieve better computational density, potentially reducing the total number of chips required for specific applications.

Lifecycle considerations reveal complex sustainability trade-offs between architectures. RISC-based systems may offer longer operational lifespans due to lower thermal stress and reduced component degradation from heat generation. This extended lifespan reduces electronic waste generation and decreases the frequency of hardware replacement cycles. Additionally, the modular nature of RISC designs often facilitates easier recycling and component recovery at end-of-life stages.

The proliferation of mobile and IoT devices amplifies these sustainability impacts across billions of deployed units. Even marginal improvements in per-device energy efficiency can yield substantial aggregate environmental benefits when multiplied across global device populations, making architectural choices increasingly consequential for sustainable technology development.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!