Wafer Thinning Process: Handling Delicate Thin-Film Elements

APR 7, 20268 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Wafer Thinning Technology Background and Objectives

Wafer thinning technology has emerged as a critical enablement process in the semiconductor industry, driven by the relentless pursuit of miniaturization and enhanced device performance. The evolution from thick silicon substrates to ultra-thin wafers represents a fundamental shift in semiconductor manufacturing paradigms, enabling the development of advanced packaging solutions, three-dimensional integrated circuits, and flexible electronic devices.

The historical development of wafer thinning can be traced back to the early 1990s when the semiconductor industry first recognized the need for thinner substrates to improve electrical performance and reduce form factors. Initial approaches relied primarily on mechanical grinding and chemical-mechanical polishing techniques, which were adequate for achieving wafer thicknesses in the 100-200 micrometer range. However, as device requirements evolved toward sub-50 micrometer thicknesses, traditional methods revealed significant limitations in handling delicate thin-film elements.

The technological evolution has been marked by several key milestones, including the introduction of temporary bonding and debonding processes, advanced plasma etching techniques, and precision stress management systems. These innovations have collectively enabled the industry to achieve wafer thicknesses below 25 micrometers while maintaining structural integrity and preserving the functionality of sensitive thin-film components such as metal interconnects, dielectric layers, and active device regions.

Current technological objectives center on achieving ultra-thin wafer processing capabilities with thicknesses approaching 10-15 micrometers while ensuring zero defectivity in thin-film elements. The primary technical goals include developing non-contact handling methodologies, implementing real-time stress monitoring systems, and establishing predictive process control algorithms that can anticipate and prevent thin-film delamination or cracking during the thinning process.

The strategic importance of mastering delicate thin-film element handling extends beyond traditional semiconductor applications into emerging fields such as flexible electronics, biomedical implants, and advanced sensor technologies. These applications demand unprecedented levels of precision in maintaining the electrical, mechanical, and optical properties of thin-film structures throughout the thinning process, necessitating breakthrough innovations in process control and material science understanding.

The historical development of wafer thinning can be traced back to the early 1990s when the semiconductor industry first recognized the need for thinner substrates to improve electrical performance and reduce form factors. Initial approaches relied primarily on mechanical grinding and chemical-mechanical polishing techniques, which were adequate for achieving wafer thicknesses in the 100-200 micrometer range. However, as device requirements evolved toward sub-50 micrometer thicknesses, traditional methods revealed significant limitations in handling delicate thin-film elements.

The technological evolution has been marked by several key milestones, including the introduction of temporary bonding and debonding processes, advanced plasma etching techniques, and precision stress management systems. These innovations have collectively enabled the industry to achieve wafer thicknesses below 25 micrometers while maintaining structural integrity and preserving the functionality of sensitive thin-film components such as metal interconnects, dielectric layers, and active device regions.

Current technological objectives center on achieving ultra-thin wafer processing capabilities with thicknesses approaching 10-15 micrometers while ensuring zero defectivity in thin-film elements. The primary technical goals include developing non-contact handling methodologies, implementing real-time stress monitoring systems, and establishing predictive process control algorithms that can anticipate and prevent thin-film delamination or cracking during the thinning process.

The strategic importance of mastering delicate thin-film element handling extends beyond traditional semiconductor applications into emerging fields such as flexible electronics, biomedical implants, and advanced sensor technologies. These applications demand unprecedented levels of precision in maintaining the electrical, mechanical, and optical properties of thin-film structures throughout the thinning process, necessitating breakthrough innovations in process control and material science understanding.

Market Demand for Ultra-Thin Semiconductor Devices

The semiconductor industry is experiencing unprecedented demand for ultra-thin devices driven by the relentless pursuit of miniaturization across multiple technology sectors. Consumer electronics manufacturers are pushing for thinner smartphones, tablets, and wearable devices, creating substantial pressure on semiconductor suppliers to deliver wafers with reduced thickness while maintaining electrical performance and mechanical integrity.

The automotive sector represents a rapidly expanding market segment for ultra-thin semiconductors, particularly in electric vehicles and advanced driver assistance systems. These applications require compact, lightweight components that can withstand harsh operating conditions while delivering high performance. The integration of multiple sensors, processors, and power management units in limited space necessitates wafers with thickness reductions of up to fifty percent compared to traditional specifications.

Internet of Things applications are driving demand for ultra-thin semiconductor solutions that enable seamless integration into everyday objects and environments. Smart home devices, industrial sensors, and medical implants require components with minimal form factors that do not compromise functionality. This market segment particularly values wafers processed through advanced thinning techniques that preserve delicate thin-film elements essential for sensor functionality and wireless communication capabilities.

The telecommunications infrastructure supporting fifth-generation networks requires high-frequency components manufactured on ultra-thin substrates to achieve optimal signal propagation characteristics. Base station equipment, mobile devices, and network infrastructure components increasingly rely on wafers processed to precise thickness specifications that enhance electromagnetic performance while reducing overall system weight and power consumption.

Medical device manufacturers are increasingly adopting ultra-thin semiconductor solutions for implantable devices, diagnostic equipment, and portable monitoring systems. These applications demand exceptional reliability and biocompatibility, placing stringent requirements on wafer thinning processes that must preserve the integrity of specialized thin-film coatings and surface treatments critical for medical applications.

The aerospace and defense sectors continue to drive demand for ultra-thin semiconductors capable of operating in extreme environments while meeting strict weight and space constraints. Satellite systems, avionics, and military electronics require components manufactured through precision thinning processes that maintain performance under temperature cycling, radiation exposure, and mechanical stress conditions.

The automotive sector represents a rapidly expanding market segment for ultra-thin semiconductors, particularly in electric vehicles and advanced driver assistance systems. These applications require compact, lightweight components that can withstand harsh operating conditions while delivering high performance. The integration of multiple sensors, processors, and power management units in limited space necessitates wafers with thickness reductions of up to fifty percent compared to traditional specifications.

Internet of Things applications are driving demand for ultra-thin semiconductor solutions that enable seamless integration into everyday objects and environments. Smart home devices, industrial sensors, and medical implants require components with minimal form factors that do not compromise functionality. This market segment particularly values wafers processed through advanced thinning techniques that preserve delicate thin-film elements essential for sensor functionality and wireless communication capabilities.

The telecommunications infrastructure supporting fifth-generation networks requires high-frequency components manufactured on ultra-thin substrates to achieve optimal signal propagation characteristics. Base station equipment, mobile devices, and network infrastructure components increasingly rely on wafers processed to precise thickness specifications that enhance electromagnetic performance while reducing overall system weight and power consumption.

Medical device manufacturers are increasingly adopting ultra-thin semiconductor solutions for implantable devices, diagnostic equipment, and portable monitoring systems. These applications demand exceptional reliability and biocompatibility, placing stringent requirements on wafer thinning processes that must preserve the integrity of specialized thin-film coatings and surface treatments critical for medical applications.

The aerospace and defense sectors continue to drive demand for ultra-thin semiconductors capable of operating in extreme environments while meeting strict weight and space constraints. Satellite systems, avionics, and military electronics require components manufactured through precision thinning processes that maintain performance under temperature cycling, radiation exposure, and mechanical stress conditions.

Current Challenges in Thin-Film Wafer Processing

The wafer thinning process faces unprecedented challenges as semiconductor devices continue to shrink and thin-film elements become increasingly delicate. Modern wafers, particularly those processed to thicknesses below 50 micrometers, exhibit extreme fragility that makes traditional handling and processing methods inadequate. The mechanical stress induced during conventional grinding and polishing operations can cause micro-cracks, warpage, and catastrophic failure of the thin-film structures.

Temperature management represents a critical challenge throughout the thinning process. The heat generated during mechanical grinding can cause thermal expansion mismatches between different material layers, leading to delamination and stress-induced defects. Advanced cooling systems and temperature monitoring are essential but add complexity to the process control requirements.

Contamination control becomes exponentially more difficult as wafer thickness decreases. Ultra-thin wafers are highly susceptible to particle contamination, which can penetrate through the entire wafer thickness and compromise device functionality. Traditional cleaning methods may be too aggressive for delicate thin-film structures, requiring development of gentler yet effective contamination removal techniques.

Chemical mechanical planarization processes face significant challenges when dealing with thin-film elements. The pressure distribution across ultra-thin wafers becomes non-uniform, resulting in thickness variations and surface roughness issues. The chemical selectivity between different thin-film materials becomes critical to prevent over-etching or under-polishing of specific layers.

Wafer handling and transportation present substantial risks due to the increased flexibility and fragility of thinned substrates. Conventional vacuum chucks and mechanical grippers can induce stress concentrations that lead to wafer breakage. The development of specialized handling equipment with distributed support systems and reduced contact pressure is essential for maintaining process yield.

Edge quality control emerges as a paramount concern since thin wafers are prone to edge chipping and micro-crack propagation. Traditional dicing and edge trimming techniques often generate excessive mechanical stress, requiring innovative approaches such as laser processing or plasma etching to achieve clean, damage-free edges while preserving the integrity of delicate thin-film structures.

Temperature management represents a critical challenge throughout the thinning process. The heat generated during mechanical grinding can cause thermal expansion mismatches between different material layers, leading to delamination and stress-induced defects. Advanced cooling systems and temperature monitoring are essential but add complexity to the process control requirements.

Contamination control becomes exponentially more difficult as wafer thickness decreases. Ultra-thin wafers are highly susceptible to particle contamination, which can penetrate through the entire wafer thickness and compromise device functionality. Traditional cleaning methods may be too aggressive for delicate thin-film structures, requiring development of gentler yet effective contamination removal techniques.

Chemical mechanical planarization processes face significant challenges when dealing with thin-film elements. The pressure distribution across ultra-thin wafers becomes non-uniform, resulting in thickness variations and surface roughness issues. The chemical selectivity between different thin-film materials becomes critical to prevent over-etching or under-polishing of specific layers.

Wafer handling and transportation present substantial risks due to the increased flexibility and fragility of thinned substrates. Conventional vacuum chucks and mechanical grippers can induce stress concentrations that lead to wafer breakage. The development of specialized handling equipment with distributed support systems and reduced contact pressure is essential for maintaining process yield.

Edge quality control emerges as a paramount concern since thin wafers are prone to edge chipping and micro-crack propagation. Traditional dicing and edge trimming techniques often generate excessive mechanical stress, requiring innovative approaches such as laser processing or plasma etching to achieve clean, damage-free edges while preserving the integrity of delicate thin-film structures.

Current Solutions for Delicate Thin-Film Handling

01 Mechanical grinding and polishing methods for wafer thinning

Wafer thinning can be achieved through mechanical grinding and polishing processes that remove material from the backside of the wafer. These methods typically involve multiple stages of grinding with progressively finer abrasives, followed by polishing steps to achieve the desired thickness and surface quality. The process parameters such as grinding pressure, rotation speed, and abrasive particle size are carefully controlled to minimize subsurface damage and achieve uniform thickness across the wafer.- Mechanical grinding and polishing methods for wafer thinning: Wafer thinning can be achieved through mechanical grinding and polishing processes that remove material from the backside of the wafer. These methods typically involve using abrasive wheels or pads with progressively finer grits to reduce wafer thickness while maintaining surface quality. The process may include multiple grinding stages followed by polishing steps to achieve the desired thickness and surface finish. This approach is widely used for achieving uniform thickness reduction across the wafer surface.

- Chemical mechanical polishing (CMP) techniques: Chemical mechanical polishing combines chemical etching with mechanical abrasion to thin wafers with high precision and minimal surface damage. This technique uses a slurry containing chemical agents and abrasive particles that react with and remove wafer material simultaneously. The method provides excellent surface planarity and reduces subsurface damage compared to purely mechanical approaches. It is particularly effective for achieving ultra-thin wafers with superior surface quality.

- Plasma etching and dry etching processes: Plasma-based and dry etching methods utilize reactive gases and plasma to remove material from wafer surfaces without physical contact. These processes offer precise control over material removal rates and can achieve highly uniform thinning across the wafer. The technique minimizes mechanical stress and damage to the wafer structure while enabling selective etching of specific materials. This approach is particularly suitable for advanced semiconductor devices requiring minimal subsurface damage.

- Wet chemical etching methods: Wet chemical etching employs liquid chemical solutions to dissolve and remove wafer material in a controlled manner. This method can achieve high throughput and uniform thinning by immersing wafers in etchant baths or applying chemical solutions through spray systems. The process parameters such as temperature, concentration, and etching time can be adjusted to control the thinning rate and final thickness. This technique is cost-effective and suitable for batch processing of multiple wafers.

- Laser-assisted wafer thinning and dicing: Laser-based techniques use focused laser beams to ablate or modify wafer material for thinning purposes. This method offers high precision and flexibility in material removal with minimal mechanical stress on the wafer. Laser processing can be combined with other thinning methods to enhance efficiency and achieve specific thickness profiles. The technique is particularly advantageous for processing brittle materials and creating ultra-thin wafers with reduced risk of breakage.

02 Chemical mechanical polishing (CMP) for wafer thinning

Chemical mechanical polishing combines chemical etching with mechanical abrasion to thin wafers while maintaining excellent surface planarity and minimal defects. This technique uses a slurry containing abrasive particles and chemical agents that react with the wafer surface. The process provides better control over material removal rates and surface finish compared to purely mechanical methods, making it suitable for achieving ultra-thin wafers with high-quality surfaces.Expand Specific Solutions03 Plasma etching and dry etching techniques for wafer thinning

Plasma-based and dry etching methods utilize reactive gases and plasma to remove material from the wafer backside through chemical reactions. These non-contact methods can achieve precise thickness control and minimize mechanical stress on the wafer. The process is particularly advantageous for thinning fragile wafers or those with sensitive device structures on the front side, as it reduces the risk of physical damage during thinning.Expand Specific Solutions04 Wafer support and handling systems during thinning process

Specialized support systems and handling mechanisms are employed to secure and protect wafers during the thinning process. These systems include temporary bonding techniques, carrier wafers, protective tapes, and vacuum chucks that hold the wafer firmly while allowing access to the backside for thinning operations. Proper support prevents wafer breakage, warping, and contamination, which are critical concerns when processing ultra-thin wafers.Expand Specific Solutions05 Stress relief and damage layer removal after wafer thinning

Post-thinning treatments are necessary to remove subsurface damage layers and relieve residual stress introduced during the thinning process. These treatments may include wet chemical etching, thermal annealing, or additional polishing steps to restore the crystalline quality of the wafer surface. Removing the damaged layer is essential for maintaining the electrical properties and mechanical strength of the thinned wafer, particularly for applications requiring high device performance.Expand Specific Solutions

Major Players in Wafer Thinning Equipment Industry

The wafer thinning process for handling delicate thin-film elements represents a mature yet rapidly evolving semiconductor manufacturing segment, driven by increasing demand for miniaturized electronics and advanced packaging technologies. The market demonstrates significant growth potential, particularly in automotive, mobile, and IoT applications. Technology maturity varies considerably across the competitive landscape. Established equipment manufacturers like DISCO Corp. and precision machinery specialists lead in grinding and polishing technologies, while foundry giants such as Taiwan Semiconductor Manufacturing Co. and Semiconductor Manufacturing International Corp. drive process innovation through advanced fabrication capabilities. Chemical solution providers including Shin-Etsu Chemical, JSR Corp., and Tokyo Ohka Kogyo contribute specialized materials for thinning processes. The ecosystem spans from equipment suppliers to foundries and materials companies, with Asian players particularly prominent. Emerging companies like Hwatsing Technology and established semiconductor manufacturers such as Infineon Technologies continue advancing process capabilities, indicating a competitive market with ongoing technological advancement and consolidation trends.

DISCO Corp.

Technical Solution: DISCO Corporation specializes in precision cutting, grinding, and polishing equipment for semiconductor wafer processing. Their wafer thinning solutions include advanced back-grinding systems that can achieve ultra-thin wafer thicknesses down to 25 micrometers while maintaining excellent thickness uniformity across the entire wafer surface. The company's DGP (Dicing before Grinding Process) technology enables handling of delicate thin-film elements by providing better support during the thinning process. Their equipment features advanced chuck systems with optimized vacuum distribution and temperature control to minimize wafer warpage and stress during processing. DISCO's solutions also incorporate real-time monitoring systems that track grinding parameters and automatically adjust processing conditions to maintain consistent results across different wafer types and thin-film configurations.

Strengths: Industry-leading precision grinding technology with excellent thickness uniformity control and specialized equipment for ultra-thin wafer processing. Weaknesses: High equipment costs and complex setup requirements for optimal performance.

Infineon Technologies AG

Technical Solution: Infineon has developed specialized wafer thinning processes for power semiconductor devices and automotive applications where thin-film handling is critical. Their approach focuses on maintaining the electrical properties of sensitive layers during mechanical processing. The company utilizes a multi-step thinning process that combines coarse grinding, fine grinding, and stress relief etching to achieve target thicknesses while minimizing subsurface damage. Infineon's process includes specialized handling techniques for compound semiconductor materials and wide-bandgap devices that require careful temperature and stress management. They have implemented advanced process monitoring systems that track key parameters such as grinding force, spindle vibration, and wafer temperature to ensure consistent quality. The company's wafer thinning capabilities support their power management ICs, automotive semiconductors, and RF devices where precise thickness control is essential for optimal electrical performance and thermal management.

Strengths: Strong expertise in power semiconductor processing with excellent understanding of material properties and thermal management requirements. Weaknesses: Process optimization primarily focused on specific device types, limiting flexibility for diverse applications.

Core Patents in Advanced Wafer Thinning Processes

Method for thinning a semiconductor wafer

PatentInactiveUS5476566A

Innovation

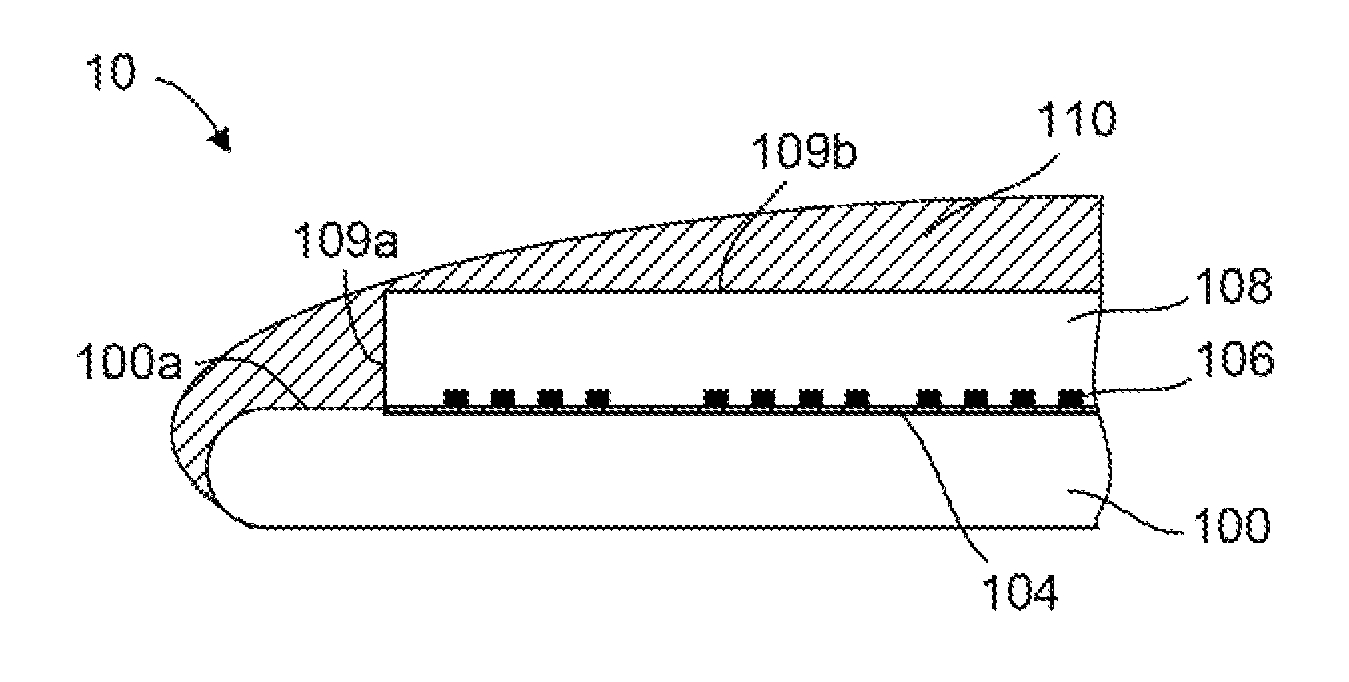

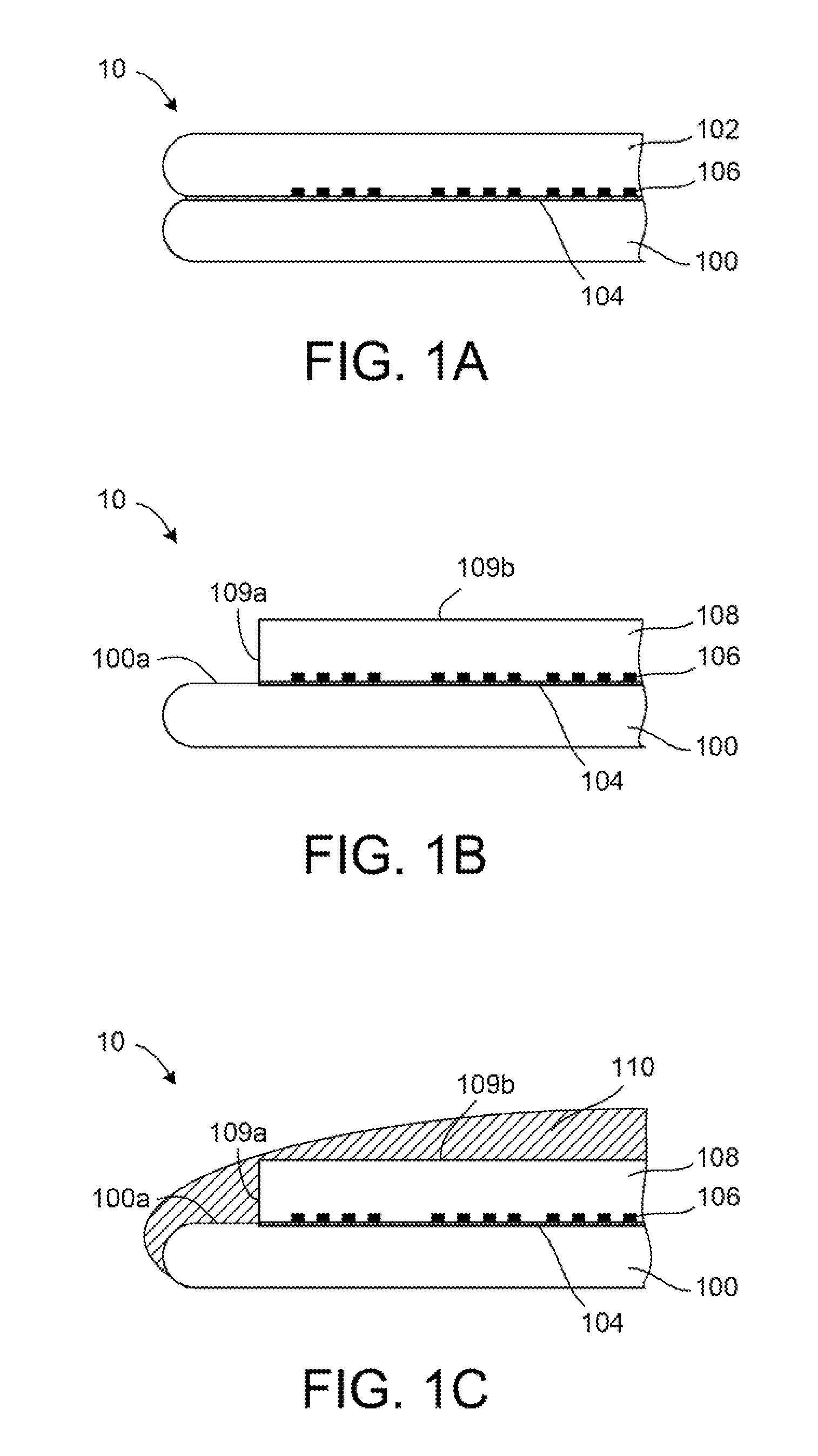

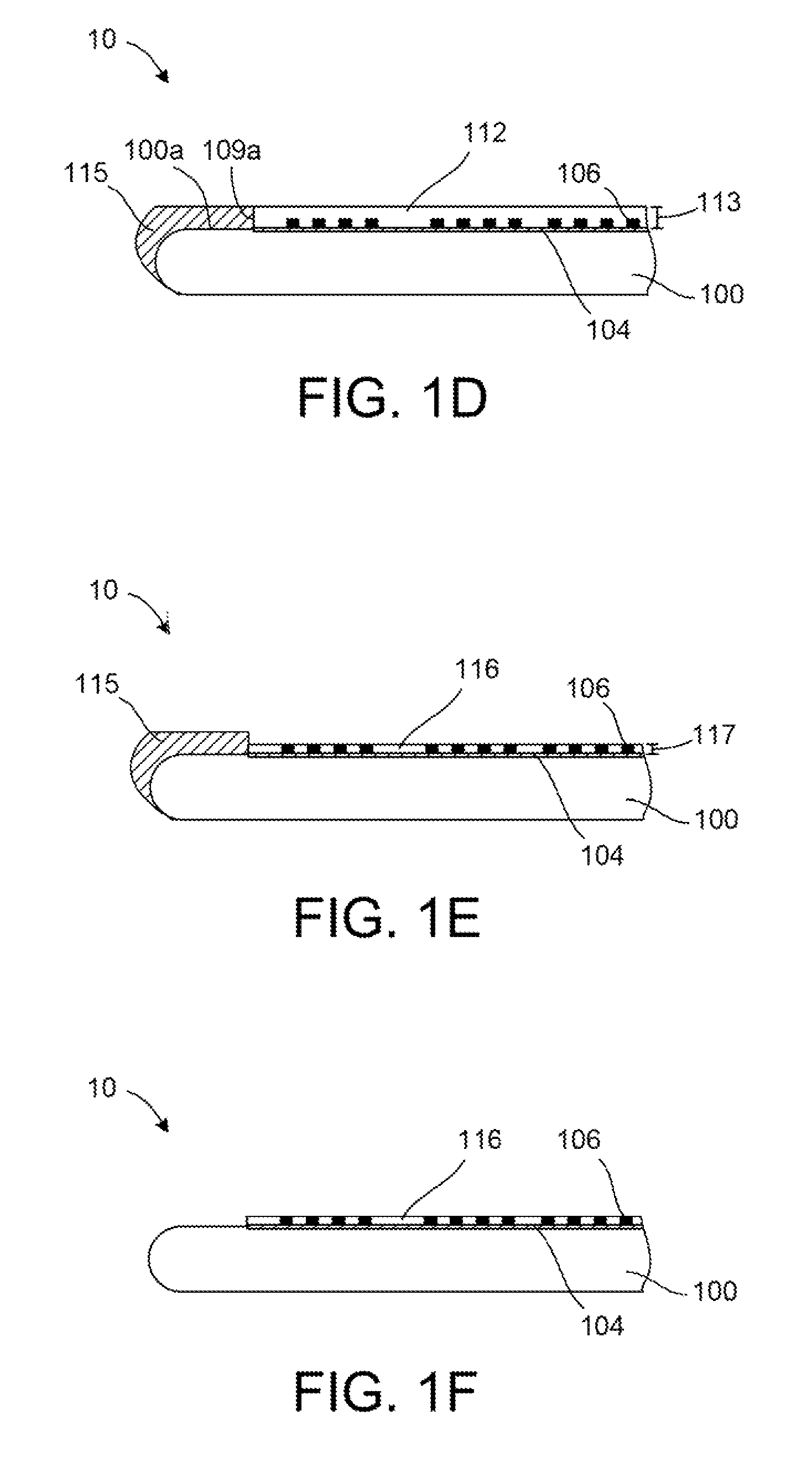

- A laminated semiconductor wafer structure is created by affixing the wafer to a UV transparent support substrate with a double-sided adhesive tape having dissimilar adhesives, providing mechanical support during backgrinding and subsequent handling, and allowing UV curable adhesive to be released without bending stress.

Method for thinning a bonding wafer

PatentActiveUS8476165B2

Innovation

- A method involving wafer edge trimming followed by the formation of a protective mask, which is then planarized and selectively etched to thin the wafer while preventing damage, using a combination of mechanical and chemical processes to remove the mask and bonding layer without compromising the structural integrity.

Quality Control Standards for Thinned Wafer Products

Quality control standards for thinned wafer products represent a critical framework ensuring the reliability and performance of semiconductor devices manufactured through wafer thinning processes. These standards encompass comprehensive measurement protocols, defect classification systems, and acceptance criteria specifically tailored to address the unique challenges posed by ultra-thin substrates and delicate thin-film elements.

Dimensional accuracy standards constitute the foundation of quality control, requiring precise thickness uniformity measurements across the entire wafer surface. Industry specifications typically demand thickness variations within ±2-5 micrometers for production-grade wafers, with advanced applications requiring even tighter tolerances. Total thickness variation (TTV) and local thickness variation (LTV) measurements utilize high-resolution capacitive or optical interferometry systems to ensure compliance with these stringent requirements.

Surface integrity assessment protocols focus on detecting and quantifying mechanical damage introduced during the thinning process. These standards define acceptable limits for surface roughness, typically requiring Ra values below 10 nanometers for critical applications. Microscopic crack detection, edge chipping evaluation, and subsurface damage assessment form integral components of surface quality verification procedures.

Thin-film element preservation standards address the specific challenges of maintaining delicate surface structures during wafer thinning operations. These criteria establish maximum allowable stress levels, temperature exposure limits, and contamination thresholds to prevent degradation of sensitive components such as MEMS structures, optical coatings, or electronic circuits deposited on wafer surfaces.

Statistical process control methodologies integrate real-time monitoring systems with automated feedback mechanisms to maintain consistent quality levels throughout production runs. Control charts, capability indices, and trend analysis tools enable proactive identification of process deviations before they impact product quality, ensuring sustained compliance with established quality benchmarks.

Traceability requirements mandate comprehensive documentation of all quality control measurements, linking individual wafer performance data to specific process parameters and equipment conditions. This systematic approach facilitates rapid root cause analysis and enables continuous improvement initiatives targeting enhanced yield and reliability outcomes.

Dimensional accuracy standards constitute the foundation of quality control, requiring precise thickness uniformity measurements across the entire wafer surface. Industry specifications typically demand thickness variations within ±2-5 micrometers for production-grade wafers, with advanced applications requiring even tighter tolerances. Total thickness variation (TTV) and local thickness variation (LTV) measurements utilize high-resolution capacitive or optical interferometry systems to ensure compliance with these stringent requirements.

Surface integrity assessment protocols focus on detecting and quantifying mechanical damage introduced during the thinning process. These standards define acceptable limits for surface roughness, typically requiring Ra values below 10 nanometers for critical applications. Microscopic crack detection, edge chipping evaluation, and subsurface damage assessment form integral components of surface quality verification procedures.

Thin-film element preservation standards address the specific challenges of maintaining delicate surface structures during wafer thinning operations. These criteria establish maximum allowable stress levels, temperature exposure limits, and contamination thresholds to prevent degradation of sensitive components such as MEMS structures, optical coatings, or electronic circuits deposited on wafer surfaces.

Statistical process control methodologies integrate real-time monitoring systems with automated feedback mechanisms to maintain consistent quality levels throughout production runs. Control charts, capability indices, and trend analysis tools enable proactive identification of process deviations before they impact product quality, ensuring sustained compliance with established quality benchmarks.

Traceability requirements mandate comprehensive documentation of all quality control measurements, linking individual wafer performance data to specific process parameters and equipment conditions. This systematic approach facilitates rapid root cause analysis and enables continuous improvement initiatives targeting enhanced yield and reliability outcomes.

Environmental Impact of Wafer Thinning Processes

The wafer thinning process generates significant environmental concerns that require comprehensive assessment and mitigation strategies. Chemical mechanical planarization (CMP) and wet etching procedures consume substantial quantities of hazardous chemicals including hydrofluoric acid, sulfuric acid, and various organic solvents. These chemicals pose risks to both human health and environmental systems when not properly managed throughout the manufacturing lifecycle.

Water consumption represents another critical environmental factor, with wafer thinning operations requiring extensive rinsing cycles to remove chemical residues and particulate contamination. A typical 300mm wafer fabrication facility can consume millions of gallons of ultrapure water daily, placing considerable strain on local water resources. The subsequent wastewater treatment processes must address complex chemical mixtures while meeting stringent discharge standards.

Air quality impacts emerge from volatile organic compound emissions during solvent-based cleaning operations and plasma etching processes. These emissions contribute to atmospheric pollution and require sophisticated abatement systems including scrubbers and thermal oxidizers. The energy-intensive nature of these control systems further amplifies the overall environmental footprint of wafer thinning operations.

Solid waste generation presents additional challenges, particularly regarding the disposal of spent grinding wheels, polishing pads, and chemical filters contaminated with semiconductor materials. Many of these waste streams contain heavy metals and toxic compounds that necessitate specialized hazardous waste treatment protocols.

Energy consumption throughout wafer thinning processes contributes substantially to carbon emissions, especially considering the precision temperature control requirements and cleanroom environmental maintenance. Advanced facilities are increasingly adopting renewable energy sources and implementing energy recovery systems to reduce their carbon footprint while maintaining the stringent process control necessary for handling delicate thin-film elements.

Regulatory compliance frameworks continue evolving to address these environmental impacts, with semiconductor manufacturers facing increasingly strict requirements for emissions monitoring, waste minimization, and resource conservation across global manufacturing locations.

Water consumption represents another critical environmental factor, with wafer thinning operations requiring extensive rinsing cycles to remove chemical residues and particulate contamination. A typical 300mm wafer fabrication facility can consume millions of gallons of ultrapure water daily, placing considerable strain on local water resources. The subsequent wastewater treatment processes must address complex chemical mixtures while meeting stringent discharge standards.

Air quality impacts emerge from volatile organic compound emissions during solvent-based cleaning operations and plasma etching processes. These emissions contribute to atmospheric pollution and require sophisticated abatement systems including scrubbers and thermal oxidizers. The energy-intensive nature of these control systems further amplifies the overall environmental footprint of wafer thinning operations.

Solid waste generation presents additional challenges, particularly regarding the disposal of spent grinding wheels, polishing pads, and chemical filters contaminated with semiconductor materials. Many of these waste streams contain heavy metals and toxic compounds that necessitate specialized hazardous waste treatment protocols.

Energy consumption throughout wafer thinning processes contributes substantially to carbon emissions, especially considering the precision temperature control requirements and cleanroom environmental maintenance. Advanced facilities are increasingly adopting renewable energy sources and implementing energy recovery systems to reduce their carbon footprint while maintaining the stringent process control necessary for handling delicate thin-film elements.

Regulatory compliance frameworks continue evolving to address these environmental impacts, with semiconductor manufacturers facing increasingly strict requirements for emissions monitoring, waste minimization, and resource conservation across global manufacturing locations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!