Electrical Property Improvements through Optimized Computational Lithography

APR 24, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Computational Lithography Background and Electrical Goals

Computational lithography has emerged as a critical technology in semiconductor manufacturing, representing the convergence of advanced mathematical algorithms, optical physics, and high-performance computing to address the fundamental challenges of pattern transfer in integrated circuit fabrication. This field encompasses sophisticated computational techniques including optical proximity correction (OPC), inverse lithography technology (ILT), and source mask optimization (SMO) that collectively enable the precise control of light manipulation through photomasks to achieve desired pattern fidelity on silicon wafers.

The evolution of computational lithography stems from the industry's relentless pursuit of Moore's Law scaling, where traditional optical lithography approaches have reached physical limitations imposed by diffraction effects and wavelength constraints. As feature sizes have shrunk below the wavelength of exposure light, computational methods have become indispensable for predicting and correcting optical proximity effects, managing process variations, and optimizing mask designs to maintain pattern integrity across diverse process conditions.

The primary electrical performance goals driving computational lithography optimization center on achieving superior device characteristics through enhanced pattern control and reduced variability. Critical dimension uniformity represents a fundamental objective, as variations in gate lengths, contact sizes, and interconnect dimensions directly impact transistor threshold voltages, drive currents, and overall circuit performance. Minimizing line edge roughness and line width roughness through optimized computational algorithms significantly reduces device-to-device variations that can degrade analog circuit precision and digital timing margins.

Advanced computational lithography techniques specifically target electrical parameter improvements including reduced parasitic capacitances through precise spacer control, optimized contact resistance via improved via formation, and enhanced electromigration reliability through better interconnect geometry control. The integration of electrical simulation feedback into lithographic optimization workflows enables direct correlation between mask design parameters and final device electrical characteristics.

Contemporary research focuses on machine learning-enhanced computational lithography approaches that can simultaneously optimize multiple electrical metrics while maintaining manufacturing feasibility. These methodologies incorporate electrical design rule checking, timing analysis, and power consumption optimization directly into the lithographic solution space, enabling holistic optimization strategies that transcend traditional geometric-only approaches and deliver measurable improvements in circuit performance, yield, and reliability across advanced technology nodes.

The evolution of computational lithography stems from the industry's relentless pursuit of Moore's Law scaling, where traditional optical lithography approaches have reached physical limitations imposed by diffraction effects and wavelength constraints. As feature sizes have shrunk below the wavelength of exposure light, computational methods have become indispensable for predicting and correcting optical proximity effects, managing process variations, and optimizing mask designs to maintain pattern integrity across diverse process conditions.

The primary electrical performance goals driving computational lithography optimization center on achieving superior device characteristics through enhanced pattern control and reduced variability. Critical dimension uniformity represents a fundamental objective, as variations in gate lengths, contact sizes, and interconnect dimensions directly impact transistor threshold voltages, drive currents, and overall circuit performance. Minimizing line edge roughness and line width roughness through optimized computational algorithms significantly reduces device-to-device variations that can degrade analog circuit precision and digital timing margins.

Advanced computational lithography techniques specifically target electrical parameter improvements including reduced parasitic capacitances through precise spacer control, optimized contact resistance via improved via formation, and enhanced electromigration reliability through better interconnect geometry control. The integration of electrical simulation feedback into lithographic optimization workflows enables direct correlation between mask design parameters and final device electrical characteristics.

Contemporary research focuses on machine learning-enhanced computational lithography approaches that can simultaneously optimize multiple electrical metrics while maintaining manufacturing feasibility. These methodologies incorporate electrical design rule checking, timing analysis, and power consumption optimization directly into the lithographic solution space, enabling holistic optimization strategies that transcend traditional geometric-only approaches and deliver measurable improvements in circuit performance, yield, and reliability across advanced technology nodes.

Market Demand for Advanced Lithography Solutions

The semiconductor industry faces unprecedented demand for advanced lithography solutions as device scaling approaches fundamental physical limits. Traditional optical lithography techniques struggle to meet the stringent requirements for next-generation semiconductor nodes, particularly in achieving the precise electrical properties necessary for high-performance integrated circuits. This challenge has created substantial market opportunities for computational lithography solutions that can optimize electrical characteristics through advanced modeling and correction algorithms.

Market demand is primarily driven by the transition to extreme ultraviolet lithography and the need for enhanced process control in manufacturing nodes below 7nm. Leading semiconductor manufacturers require lithography solutions that not only achieve geometric accuracy but also optimize electrical parameters such as resistance, capacitance, and leakage current. The growing complexity of three-dimensional device structures, including FinFETs and gate-all-around transistors, further amplifies the need for sophisticated computational approaches that can predict and optimize electrical behavior during the lithography process.

The artificial intelligence and machine learning sectors represent significant growth drivers for advanced lithography demand. High-performance computing applications, including AI accelerators and graphics processing units, require transistors with precisely controlled electrical characteristics to achieve optimal power efficiency and performance. These applications demand lithography solutions capable of minimizing process variations that directly impact electrical properties, creating substantial market opportunities for computational optimization technologies.

Memory manufacturers constitute another major market segment driving demand for electrical property-focused lithography solutions. Advanced memory technologies such as 3D NAND and emerging non-volatile memory devices require extremely tight control over electrical parameters to ensure reliable data storage and retrieval. The increasing density requirements and shrinking feature sizes in memory applications necessitate computational lithography approaches that can simultaneously optimize geometric and electrical characteristics.

The automotive and industrial electronics sectors are emerging as significant demand drivers due to the proliferation of electric vehicles and Industry 4.0 applications. These markets require semiconductor devices with enhanced reliability and specific electrical performance characteristics, creating opportunities for lithography solutions that can optimize electrical properties for harsh operating environments and extended operational lifetimes.

Regional market dynamics show particularly strong demand in Asia-Pacific regions, where major semiconductor foundries are investing heavily in advanced manufacturing capabilities. The concentration of leading semiconductor manufacturers in this region creates substantial market potential for computational lithography solutions that can deliver superior electrical property optimization compared to conventional approaches.

Market demand is primarily driven by the transition to extreme ultraviolet lithography and the need for enhanced process control in manufacturing nodes below 7nm. Leading semiconductor manufacturers require lithography solutions that not only achieve geometric accuracy but also optimize electrical parameters such as resistance, capacitance, and leakage current. The growing complexity of three-dimensional device structures, including FinFETs and gate-all-around transistors, further amplifies the need for sophisticated computational approaches that can predict and optimize electrical behavior during the lithography process.

The artificial intelligence and machine learning sectors represent significant growth drivers for advanced lithography demand. High-performance computing applications, including AI accelerators and graphics processing units, require transistors with precisely controlled electrical characteristics to achieve optimal power efficiency and performance. These applications demand lithography solutions capable of minimizing process variations that directly impact electrical properties, creating substantial market opportunities for computational optimization technologies.

Memory manufacturers constitute another major market segment driving demand for electrical property-focused lithography solutions. Advanced memory technologies such as 3D NAND and emerging non-volatile memory devices require extremely tight control over electrical parameters to ensure reliable data storage and retrieval. The increasing density requirements and shrinking feature sizes in memory applications necessitate computational lithography approaches that can simultaneously optimize geometric and electrical characteristics.

The automotive and industrial electronics sectors are emerging as significant demand drivers due to the proliferation of electric vehicles and Industry 4.0 applications. These markets require semiconductor devices with enhanced reliability and specific electrical performance characteristics, creating opportunities for lithography solutions that can optimize electrical properties for harsh operating environments and extended operational lifetimes.

Regional market dynamics show particularly strong demand in Asia-Pacific regions, where major semiconductor foundries are investing heavily in advanced manufacturing capabilities. The concentration of leading semiconductor manufacturers in this region creates substantial market potential for computational lithography solutions that can deliver superior electrical property optimization compared to conventional approaches.

Current State and Challenges in Computational Lithography

Computational lithography has emerged as a critical technology in semiconductor manufacturing, enabling the production of increasingly smaller feature sizes that approach and exceed the physical limits of traditional optical lithography. Current state-of-the-art systems utilize advanced algorithms including optical proximity correction (OPC), inverse lithography technology (ILT), and source mask optimization (SMO) to achieve sub-wavelength patterning capabilities. These techniques have successfully enabled the continuation of Moore's Law scaling down to 3nm and 2nm process nodes.

The technology landscape is dominated by sophisticated computational models that simulate the complex interactions between light, photoresist, and mask patterns. Leading-edge foundries currently employ resolution enhancement techniques such as multiple patterning, extreme ultraviolet (EUV) lithography integration, and machine learning-enhanced process optimization. These approaches have demonstrated significant improvements in critical dimension uniformity, pattern fidelity, and defect reduction across various device structures.

However, several fundamental challenges continue to constrain the advancement of computational lithography for electrical property optimization. The primary technical bottleneck lies in the computational complexity required for full-chip optimization, where current algorithms struggle to balance processing time with solution accuracy. Edge placement error (EPE) control remains problematic, particularly for complex two-dimensional patterns and through-process variations that directly impact device electrical performance.

Stochastic effects present another significant challenge, especially in EUV lithography where photon shot noise and resist molecular discreteness create unpredictable pattern variations. These stochastic variations translate directly into electrical parameter fluctuations, affecting device matching and circuit reliability. Current computational models inadequately capture these quantum-level phenomena, limiting their predictive accuracy for electrical property optimization.

The integration of electrical performance metrics into lithographic optimization workflows represents a major technical gap. Traditional computational lithography focuses primarily on geometric pattern fidelity rather than the resulting electrical characteristics such as parasitic capacitance, resistance variations, and leakage currents. This disconnect between lithographic optimization objectives and electrical performance requirements creates suboptimal solutions for advanced technology nodes.

Manufacturing constraints further complicate the implementation of computationally optimized solutions. Mask complexity limitations, exposure tool capabilities, and process window requirements often conflict with theoretically optimal computational solutions. The industry faces increasing challenges in translating sophisticated computational optimizations into manufacturable processes while maintaining acceptable throughput and cost structures.

Geographically, computational lithography development is concentrated in regions with advanced semiconductor manufacturing capabilities, including Taiwan, South Korea, and select locations in the United States and Europe. This concentration reflects the substantial infrastructure and expertise requirements for developing and implementing these complex technologies at production scale.

The technology landscape is dominated by sophisticated computational models that simulate the complex interactions between light, photoresist, and mask patterns. Leading-edge foundries currently employ resolution enhancement techniques such as multiple patterning, extreme ultraviolet (EUV) lithography integration, and machine learning-enhanced process optimization. These approaches have demonstrated significant improvements in critical dimension uniformity, pattern fidelity, and defect reduction across various device structures.

However, several fundamental challenges continue to constrain the advancement of computational lithography for electrical property optimization. The primary technical bottleneck lies in the computational complexity required for full-chip optimization, where current algorithms struggle to balance processing time with solution accuracy. Edge placement error (EPE) control remains problematic, particularly for complex two-dimensional patterns and through-process variations that directly impact device electrical performance.

Stochastic effects present another significant challenge, especially in EUV lithography where photon shot noise and resist molecular discreteness create unpredictable pattern variations. These stochastic variations translate directly into electrical parameter fluctuations, affecting device matching and circuit reliability. Current computational models inadequately capture these quantum-level phenomena, limiting their predictive accuracy for electrical property optimization.

The integration of electrical performance metrics into lithographic optimization workflows represents a major technical gap. Traditional computational lithography focuses primarily on geometric pattern fidelity rather than the resulting electrical characteristics such as parasitic capacitance, resistance variations, and leakage currents. This disconnect between lithographic optimization objectives and electrical performance requirements creates suboptimal solutions for advanced technology nodes.

Manufacturing constraints further complicate the implementation of computationally optimized solutions. Mask complexity limitations, exposure tool capabilities, and process window requirements often conflict with theoretically optimal computational solutions. The industry faces increasing challenges in translating sophisticated computational optimizations into manufacturable processes while maintaining acceptable throughput and cost structures.

Geographically, computational lithography development is concentrated in regions with advanced semiconductor manufacturing capabilities, including Taiwan, South Korea, and select locations in the United States and Europe. This concentration reflects the substantial infrastructure and expertise requirements for developing and implementing these complex technologies at production scale.

Current Computational Lithography Optimization Methods

01 Computational lithography modeling and simulation techniques

Advanced computational methods are employed to model and simulate lithography processes, enabling accurate prediction of pattern transfer and optimization of exposure parameters. These techniques utilize mathematical algorithms and numerical methods to simulate light diffraction, photoresist behavior, and pattern formation on semiconductor wafers. The computational models help in predicting the final printed patterns and identifying potential defects before actual manufacturing.- Computational lithography modeling and simulation methods: Advanced computational techniques are employed to model and simulate lithography processes, enabling accurate prediction of pattern transfer and optimization of exposure parameters. These methods utilize mathematical algorithms and numerical simulations to account for optical effects, resist behavior, and process variations. Machine learning and artificial intelligence approaches are increasingly integrated to enhance prediction accuracy and reduce computational time.

- Optical proximity correction and resolution enhancement techniques: Computational methods are used to correct optical proximity effects and enhance resolution in lithography systems. These techniques modify mask patterns to compensate for diffraction and interference effects that occur during exposure. Advanced algorithms calculate optimal corrections based on desired circuit patterns and lithography system characteristics, improving pattern fidelity and enabling smaller feature sizes.

- Electrical property prediction and verification in lithography: Computational tools are developed to predict and verify electrical properties of patterns created through lithography processes. These methods analyze the relationship between lithographic pattern variations and resulting electrical characteristics such as resistance, capacitance, and timing. Simulation frameworks integrate lithography models with electrical circuit analysis to ensure manufactured devices meet performance specifications.

- Source mask optimization for lithography systems: Computational optimization techniques are applied to jointly optimize illumination source patterns and mask designs in lithography systems. These methods use iterative algorithms to determine optimal source and mask configurations that maximize pattern fidelity and process window. The optimization considers various constraints including manufacturing feasibility and electrical performance requirements.

- Process variation analysis and compensation in computational lithography: Computational approaches are utilized to analyze and compensate for process variations in lithography manufacturing. These techniques model the impact of variations in exposure dose, focus, resist properties, and other process parameters on final pattern geometry and electrical properties. Statistical methods and sensitivity analysis are employed to identify critical parameters and develop robust compensation strategies that ensure consistent device performance across process variations.

02 Optical proximity correction and resolution enhancement

Computational techniques are applied to correct optical proximity effects and enhance resolution in lithography processes. These methods involve modifying mask patterns to compensate for diffraction and interference effects that occur during exposure. The corrections are calculated using sophisticated algorithms that account for the interaction between adjacent features and the optical characteristics of the lithography system. This approach enables the production of smaller and more precise patterns on semiconductor devices.Expand Specific Solutions03 Machine learning and artificial intelligence in lithography optimization

Machine learning algorithms and artificial intelligence techniques are integrated into computational lithography systems to optimize process parameters and improve pattern fidelity. These methods can learn from historical data and automatically adjust lithography settings to achieve desired outcomes. The AI-based approaches enable faster optimization cycles and can handle complex multi-variable optimization problems that are difficult to solve using traditional methods.Expand Specific Solutions04 Electrical property characterization and verification in lithography

Methods for characterizing and verifying electrical properties of patterns created through computational lithography processes are developed. These techniques involve measuring and analyzing electrical parameters such as resistance, capacitance, and conductivity of the fabricated structures. The verification processes ensure that the lithographically defined patterns meet electrical specifications and performance requirements for semiconductor devices.Expand Specific Solutions05 Multi-patterning and advanced node lithography computation

Computational methods are developed specifically for multi-patterning techniques and advanced technology nodes where traditional single-exposure lithography is insufficient. These approaches involve decomposing complex patterns into multiple simpler patterns that can be printed separately and combined. The computational algorithms optimize the pattern decomposition, overlay alignment, and stitching to minimize defects and ensure pattern integrity across multiple exposure steps.Expand Specific Solutions

Key Players in Computational Lithography Industry

The computational lithography sector for electrical property improvements represents a mature yet rapidly evolving market driven by semiconductor industry demands for advanced node manufacturing. The industry has reached a critical growth phase, with market expansion fueled by AI, 5G, and automotive electronics requiring enhanced chip performance. Technology maturity varies significantly across players, with ASML Netherlands BV and Carl Zeiss SMT GmbH leading in advanced EUV lithography systems, while Taiwan Semiconductor Manufacturing Co. and GlobalFoundries excel in production implementation. Software specialists like D2S Inc., Cadence Design Systems, and Siemens Industry Software provide essential computational solutions for mask optimization and process control. Chinese players including Shanghai Microelectronics Equipment, SMIC, and research institutions are rapidly advancing but remain behind leading-edge capabilities, creating a competitive landscape where established Western companies maintain technological advantages while Asian manufacturers focus on cost-effective solutions and domestic market penetration.

ASML Netherlands BV

Technical Solution: ASML develops advanced computational lithography solutions integrated with their EUV and DUV lithography systems to optimize electrical properties of semiconductor devices. Their approach combines sophisticated optical proximity correction (OPC) algorithms with machine learning-enhanced source mask optimization (SMO) techniques. The company's computational lithography platform utilizes advanced modeling algorithms that predict and compensate for optical and process effects, enabling precise pattern fidelity and improved electrical characteristics. Their solutions incorporate resist modeling, etch bias correction, and advanced metrology feedback loops to achieve sub-7nm node requirements. ASML's computational lithography tools are specifically designed to minimize line edge roughness, reduce critical dimension variation, and optimize contact resistance through enhanced pattern placement accuracy.

Strengths: Market-leading EUV technology integration, comprehensive end-to-end lithography solutions, strong R&D capabilities. Weaknesses: High equipment costs, complex implementation requirements, dependency on advanced infrastructure.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC implements comprehensive computational lithography strategies across their advanced node manufacturing processes to enhance electrical properties of fabricated devices. Their approach integrates multi-patterning decomposition algorithms, advanced OPC techniques, and process-aware design optimization to minimize electrical variability. TSMC's computational lithography framework includes sophisticated resist and etch modeling, enabling precise control of critical dimensions and contact resistance optimization. The company employs machine learning algorithms for pattern recognition and correction, combined with extensive process characterization data to achieve superior electrical performance. Their solutions focus on minimizing parasitic capacitance, optimizing via resistance, and ensuring consistent electrical characteristics across wafer-scale manufacturing.

Strengths: Leading-edge manufacturing expertise, extensive process data, strong customer collaboration. Weaknesses: High development costs, complex process integration, limited technology sharing with competitors.

Core Patents in Electrical Property Enhancement

Optical Proximity Correction for Improved Electrical Characteristics

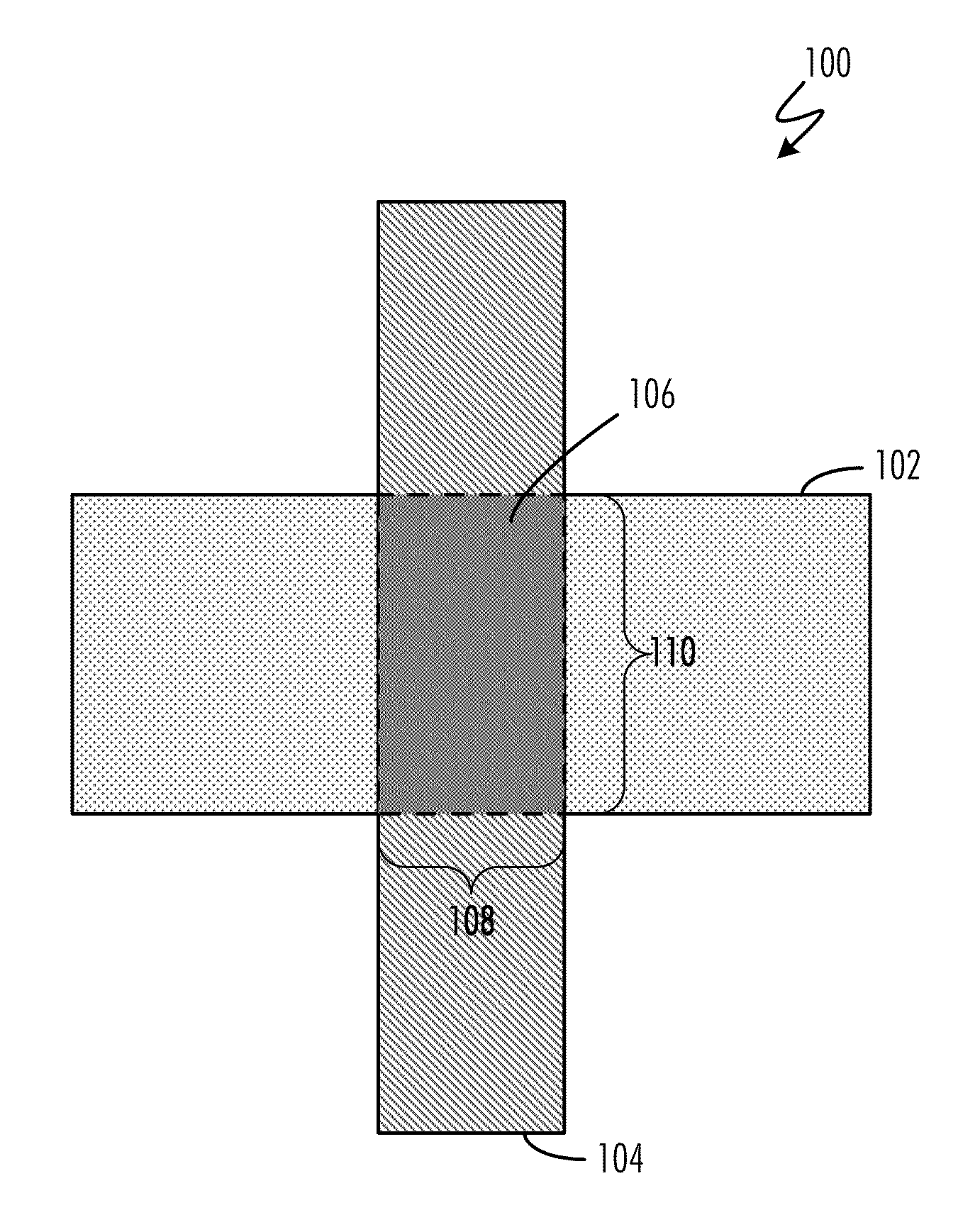

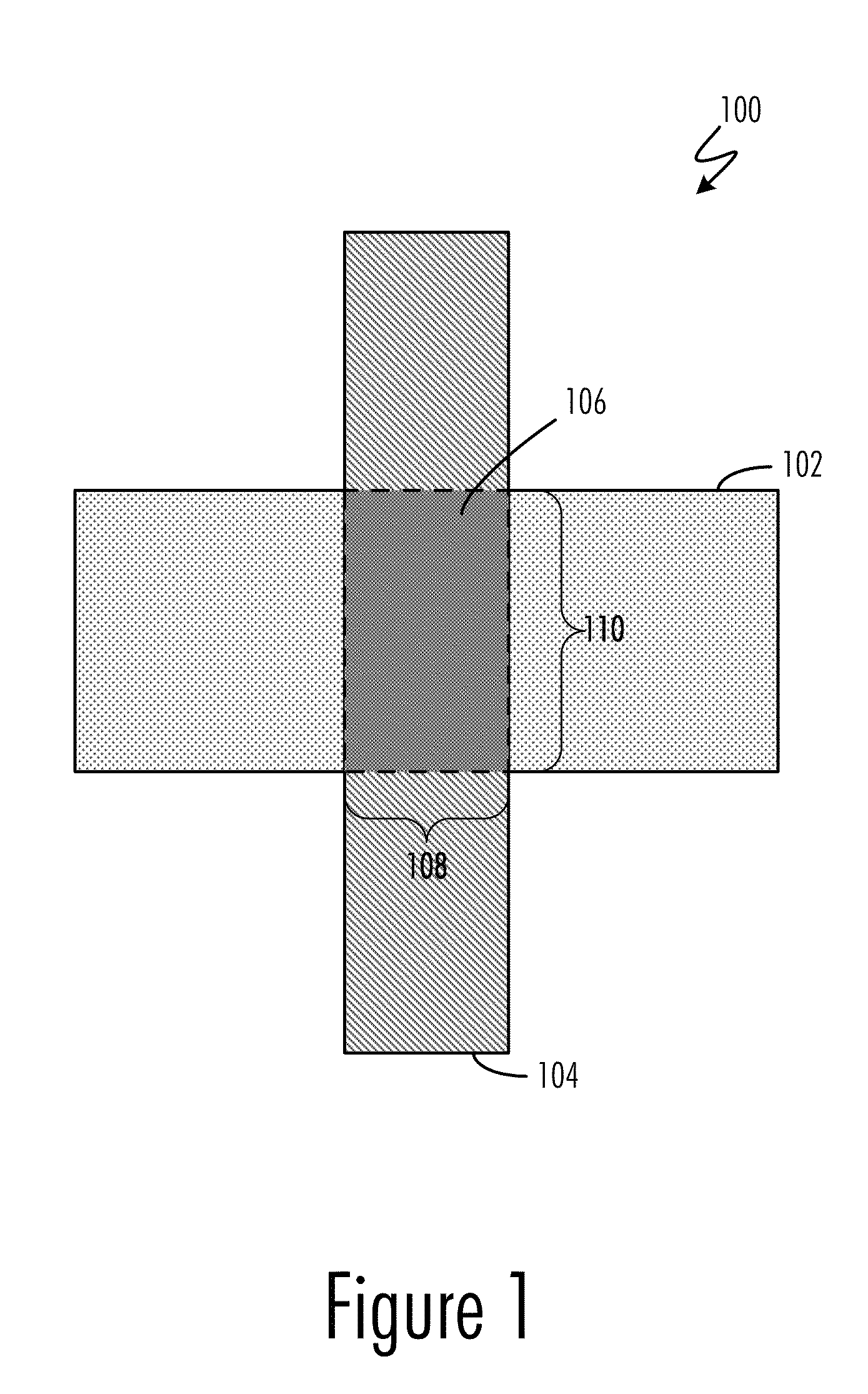

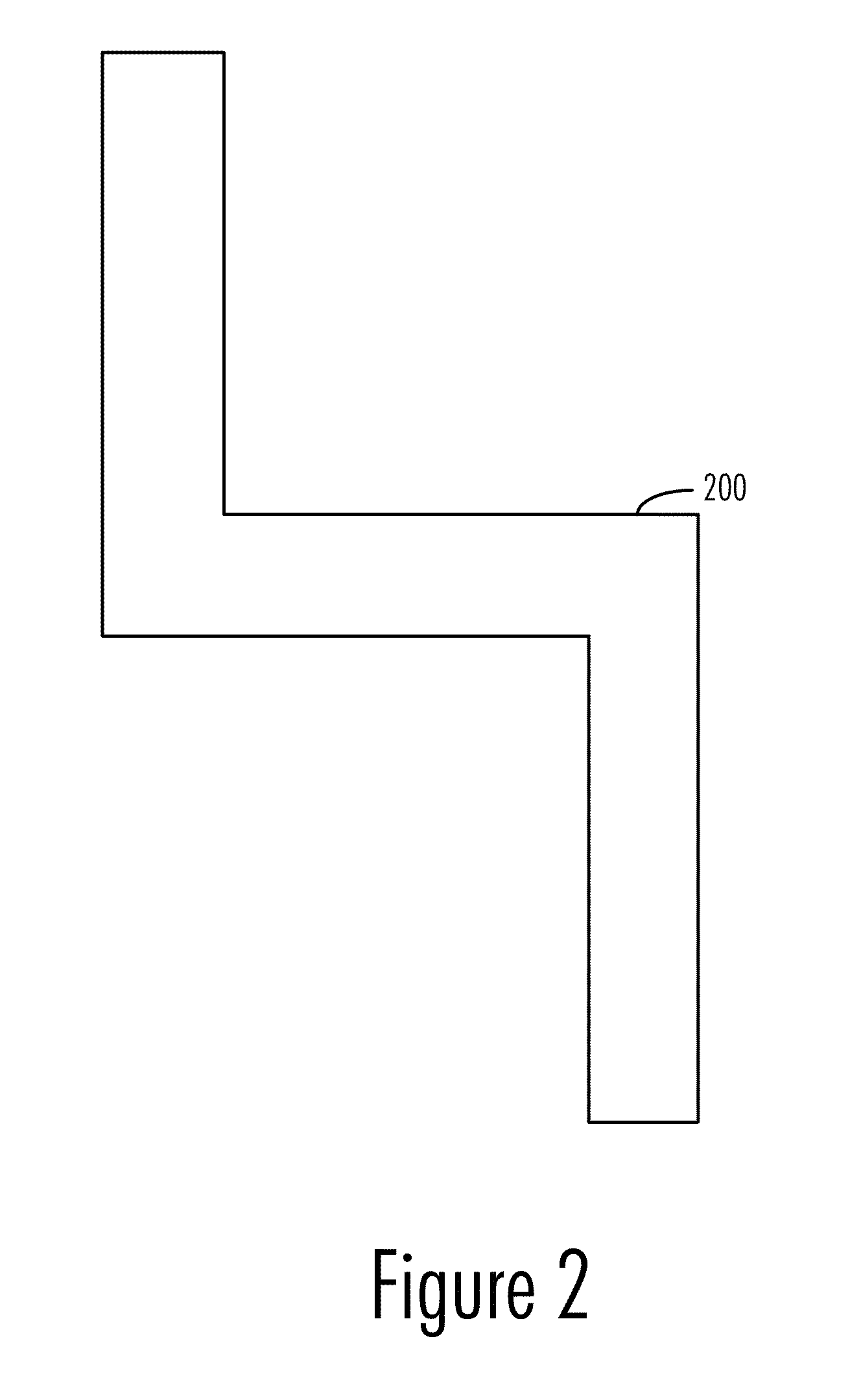

PatentInactiveUS20110154271A1

Innovation

- The method involves dividing the perimeter of a mask region into segments, grouping them for edge placement error and dimensional error correction, ensuring that adjustments respect the intended dimensions and electrical behavior of the device.

Large scale computational lithography using machine learning models

PatentActiveUS12249115B2

Innovation

- The use of machine learning models to infer aerial images and resist profiles, replacing the need for computationally expensive physical models, thereby speeding up the simulation process while maintaining accuracy.

Semiconductor Manufacturing Standards and Regulations

The semiconductor manufacturing industry operates under a comprehensive framework of standards and regulations that directly impact computational lithography optimization for electrical property improvements. International standards organizations such as SEMI, IEEE, and ISO establish critical guidelines governing lithographic processes, material specifications, and electrical performance metrics that computational lithography systems must adhere to when optimizing circuit designs.

SEMI standards particularly influence computational lithography through specifications like SEMI P37 for photomask quality and SEMI P39 for critical dimension uniformity requirements. These standards define acceptable tolerances for feature dimensions and electrical characteristics, creating constraints within which computational lithography algorithms must operate. The optimization of electrical properties through computational methods must ensure compliance with these dimensional and performance specifications while maximizing circuit efficiency.

Regional regulatory frameworks add additional complexity to computational lithography implementation. The European Union's RoHS directive restricts hazardous substances in semiconductor manufacturing, affecting material choices in lithographic processes. Similarly, REACH regulations impact chemical usage in photoresist and etching processes, requiring computational lithography systems to optimize designs within environmentally compliant manufacturing parameters.

Quality management standards such as ISO 9001 and automotive-specific ISO/TS 16949 establish rigorous process control requirements that computational lithography systems must support. These standards mandate statistical process control and traceability throughout manufacturing, necessitating that computational optimization algorithms generate reproducible results with documented process variations and electrical performance correlations.

Export control regulations, including the Wassenaar Arrangement and various national technology transfer restrictions, significantly impact the development and deployment of advanced computational lithography technologies. These regulations limit the sharing of sophisticated optimization algorithms and related intellectual property across international boundaries, affecting collaborative research and technology standardization efforts in computational lithography advancement.

Emerging standards for artificial intelligence and machine learning applications in manufacturing are beginning to influence computational lithography development. Organizations like IEEE are developing standards for AI transparency and validation in industrial applications, which will likely impact how computational lithography algorithms are validated for electrical property optimization and regulatory compliance verification.

SEMI standards particularly influence computational lithography through specifications like SEMI P37 for photomask quality and SEMI P39 for critical dimension uniformity requirements. These standards define acceptable tolerances for feature dimensions and electrical characteristics, creating constraints within which computational lithography algorithms must operate. The optimization of electrical properties through computational methods must ensure compliance with these dimensional and performance specifications while maximizing circuit efficiency.

Regional regulatory frameworks add additional complexity to computational lithography implementation. The European Union's RoHS directive restricts hazardous substances in semiconductor manufacturing, affecting material choices in lithographic processes. Similarly, REACH regulations impact chemical usage in photoresist and etching processes, requiring computational lithography systems to optimize designs within environmentally compliant manufacturing parameters.

Quality management standards such as ISO 9001 and automotive-specific ISO/TS 16949 establish rigorous process control requirements that computational lithography systems must support. These standards mandate statistical process control and traceability throughout manufacturing, necessitating that computational optimization algorithms generate reproducible results with documented process variations and electrical performance correlations.

Export control regulations, including the Wassenaar Arrangement and various national technology transfer restrictions, significantly impact the development and deployment of advanced computational lithography technologies. These regulations limit the sharing of sophisticated optimization algorithms and related intellectual property across international boundaries, affecting collaborative research and technology standardization efforts in computational lithography advancement.

Emerging standards for artificial intelligence and machine learning applications in manufacturing are beginning to influence computational lithography development. Organizations like IEEE are developing standards for AI transparency and validation in industrial applications, which will likely impact how computational lithography algorithms are validated for electrical property optimization and regulatory compliance verification.

Cost-Benefit Analysis of Advanced Lithography Systems

The economic evaluation of advanced lithography systems requires comprehensive assessment of capital expenditures, operational costs, and performance benefits. Initial capital investment for state-of-the-art computational lithography systems ranges from $150-300 million per unit, depending on the technology node and system capabilities. These systems incorporate sophisticated optical proximity correction algorithms, source mask optimization capabilities, and advanced metrology integration, which significantly impact the total cost of ownership.

Operational expenditure analysis reveals that computational lithography systems generate substantial ongoing costs through software licensing, algorithm development, and computational infrastructure. Annual software maintenance and licensing fees typically account for 15-20% of the initial system cost. Additionally, the computational requirements for advanced OPC and SMO processes demand high-performance computing clusters, contributing an estimated $5-10 million annually in computational infrastructure costs per production line.

The primary economic benefits emerge through yield improvements and defect reduction. Advanced computational lithography techniques demonstrate 15-25% improvement in critical dimension uniformity and 30-40% reduction in systematic defects compared to conventional approaches. These improvements translate to yield enhancements of 8-12% for leading-edge nodes, representing significant revenue impact for high-volume manufacturing facilities.

Process development cycle time reduction provides additional economic value. Optimized computational lithography reduces mask iterations by 40-50% and shortens time-to-market by 3-6 months for new product introductions. For semiconductor manufacturers, this acceleration can represent $50-100 million in earlier revenue recognition for major product launches.

Return on investment calculations indicate break-even periods of 18-24 months for high-volume production facilities processing advanced nodes. The economic justification becomes particularly compelling for manufacturers targeting premium market segments where yield improvements directly impact profitability margins and competitive positioning in the marketplace.

Operational expenditure analysis reveals that computational lithography systems generate substantial ongoing costs through software licensing, algorithm development, and computational infrastructure. Annual software maintenance and licensing fees typically account for 15-20% of the initial system cost. Additionally, the computational requirements for advanced OPC and SMO processes demand high-performance computing clusters, contributing an estimated $5-10 million annually in computational infrastructure costs per production line.

The primary economic benefits emerge through yield improvements and defect reduction. Advanced computational lithography techniques demonstrate 15-25% improvement in critical dimension uniformity and 30-40% reduction in systematic defects compared to conventional approaches. These improvements translate to yield enhancements of 8-12% for leading-edge nodes, representing significant revenue impact for high-volume manufacturing facilities.

Process development cycle time reduction provides additional economic value. Optimized computational lithography reduces mask iterations by 40-50% and shortens time-to-market by 3-6 months for new product introductions. For semiconductor manufacturers, this acceleration can represent $50-100 million in earlier revenue recognition for major product launches.

Return on investment calculations indicate break-even periods of 18-24 months for high-volume production facilities processing advanced nodes. The economic justification becomes particularly compelling for manufacturers targeting premium market segments where yield improvements directly impact profitability margins and competitive positioning in the marketplace.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!