Frequency-Locked Loop in Next-Generation Sensors: Reducing Error Rates

MAR 18, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

FLL Sensor Technology Background and Objectives

Frequency-Locked Loop (FLL) technology represents a critical advancement in sensor systems, emerging from the fundamental need to maintain precise frequency synchronization in increasingly complex sensing environments. Unlike traditional Phase-Locked Loops (PLLs), FLL systems demonstrate superior performance in scenarios characterized by rapid phase variations and dynamic signal conditions, making them particularly valuable for next-generation sensor applications where conventional synchronization methods fall short.

The evolution of FLL technology stems from decades of research in frequency synthesis and signal processing, initially developed for telecommunications applications in the 1970s and subsequently adapted for precision measurement systems. Early implementations focused primarily on communication systems, but the growing demand for high-precision sensors in automotive, aerospace, and industrial applications has driven significant innovations in FLL architectures specifically tailored for sensing applications.

Modern sensor systems face unprecedented challenges in maintaining measurement accuracy across diverse operating conditions. Environmental factors such as temperature fluctuations, electromagnetic interference, and mechanical vibrations can introduce frequency drift and phase noise that compromise sensor performance. Traditional error correction methods often prove inadequate when dealing with the rapid signal variations encountered in dynamic sensing scenarios, creating a compelling need for more robust synchronization solutions.

The primary objective of implementing FLL technology in next-generation sensors centers on achieving substantial error rate reduction while maintaining real-time performance capabilities. Current research targets error rate improvements of 10-100 times compared to conventional synchronization methods, with particular emphasis on applications requiring sub-microsecond response times and parts-per-billion frequency stability.

Key technical objectives include developing adaptive FLL algorithms capable of tracking frequency variations across wide bandwidth ranges, typically spanning several decades of frequency. These systems must demonstrate robust performance in high-noise environments while consuming minimal power, addressing the growing demand for battery-operated and energy-harvesting sensor networks.

Integration challenges represent another critical objective, as FLL implementations must seamlessly interface with existing sensor architectures without requiring extensive hardware modifications. This necessitates the development of software-defined FLL solutions and hybrid analog-digital implementations that can be readily incorporated into diverse sensor platforms while maintaining cost-effectiveness and manufacturing scalability.

The evolution of FLL technology stems from decades of research in frequency synthesis and signal processing, initially developed for telecommunications applications in the 1970s and subsequently adapted for precision measurement systems. Early implementations focused primarily on communication systems, but the growing demand for high-precision sensors in automotive, aerospace, and industrial applications has driven significant innovations in FLL architectures specifically tailored for sensing applications.

Modern sensor systems face unprecedented challenges in maintaining measurement accuracy across diverse operating conditions. Environmental factors such as temperature fluctuations, electromagnetic interference, and mechanical vibrations can introduce frequency drift and phase noise that compromise sensor performance. Traditional error correction methods often prove inadequate when dealing with the rapid signal variations encountered in dynamic sensing scenarios, creating a compelling need for more robust synchronization solutions.

The primary objective of implementing FLL technology in next-generation sensors centers on achieving substantial error rate reduction while maintaining real-time performance capabilities. Current research targets error rate improvements of 10-100 times compared to conventional synchronization methods, with particular emphasis on applications requiring sub-microsecond response times and parts-per-billion frequency stability.

Key technical objectives include developing adaptive FLL algorithms capable of tracking frequency variations across wide bandwidth ranges, typically spanning several decades of frequency. These systems must demonstrate robust performance in high-noise environments while consuming minimal power, addressing the growing demand for battery-operated and energy-harvesting sensor networks.

Integration challenges represent another critical objective, as FLL implementations must seamlessly interface with existing sensor architectures without requiring extensive hardware modifications. This necessitates the development of software-defined FLL solutions and hybrid analog-digital implementations that can be readily incorporated into diverse sensor platforms while maintaining cost-effectiveness and manufacturing scalability.

Market Demand for High-Precision Sensor Applications

The global sensor market is experiencing unprecedented growth driven by the proliferation of Internet of Things (IoT) devices, autonomous systems, and precision manufacturing applications. High-precision sensors have become critical components across multiple industries, with demand particularly concentrated in automotive, aerospace, industrial automation, and healthcare sectors. The automotive industry alone represents a substantial portion of this demand, as advanced driver assistance systems and autonomous vehicles require sensors with exceptional accuracy and reliability.

Industrial automation and manufacturing sectors are increasingly adopting high-precision sensors to enhance quality control, reduce waste, and improve operational efficiency. Smart factories and Industry 4.0 initiatives have created substantial demand for sensors capable of detecting minute variations in temperature, pressure, vibration, and position. These applications require error rates measured in parts per million, making frequency-locked loop technology particularly valuable for maintaining measurement consistency over extended periods.

Healthcare and medical device applications represent another significant growth area for high-precision sensors. Diagnostic equipment, patient monitoring systems, and surgical instruments demand sensors with minimal drift and exceptional stability. The aging global population and increasing focus on preventive healthcare are driving continuous expansion in this sector, with particular emphasis on wearable devices and remote monitoring systems that require long-term accuracy without frequent calibration.

Aerospace and defense applications continue to drive demand for the highest precision sensor technologies. Navigation systems, satellite communications, and guidance systems require sensors that maintain accuracy under extreme environmental conditions. These applications often justify premium pricing for advanced technologies like frequency-locked loops that can significantly reduce error rates and improve system reliability.

The telecommunications infrastructure sector is experiencing growing demand for precision sensors as 5G networks and edge computing systems require precise timing and frequency control. Base stations, network synchronization equipment, and data centers rely on sensors with exceptional stability to maintain service quality and network performance.

Emerging applications in renewable energy systems, particularly wind and solar installations, are creating new market opportunities for high-precision sensors. These systems require accurate monitoring of environmental conditions, structural health, and power generation parameters to optimize performance and ensure safety. The global transition toward sustainable energy sources is expected to sustain long-term growth in this application segment.

Industrial automation and manufacturing sectors are increasingly adopting high-precision sensors to enhance quality control, reduce waste, and improve operational efficiency. Smart factories and Industry 4.0 initiatives have created substantial demand for sensors capable of detecting minute variations in temperature, pressure, vibration, and position. These applications require error rates measured in parts per million, making frequency-locked loop technology particularly valuable for maintaining measurement consistency over extended periods.

Healthcare and medical device applications represent another significant growth area for high-precision sensors. Diagnostic equipment, patient monitoring systems, and surgical instruments demand sensors with minimal drift and exceptional stability. The aging global population and increasing focus on preventive healthcare are driving continuous expansion in this sector, with particular emphasis on wearable devices and remote monitoring systems that require long-term accuracy without frequent calibration.

Aerospace and defense applications continue to drive demand for the highest precision sensor technologies. Navigation systems, satellite communications, and guidance systems require sensors that maintain accuracy under extreme environmental conditions. These applications often justify premium pricing for advanced technologies like frequency-locked loops that can significantly reduce error rates and improve system reliability.

The telecommunications infrastructure sector is experiencing growing demand for precision sensors as 5G networks and edge computing systems require precise timing and frequency control. Base stations, network synchronization equipment, and data centers rely on sensors with exceptional stability to maintain service quality and network performance.

Emerging applications in renewable energy systems, particularly wind and solar installations, are creating new market opportunities for high-precision sensors. These systems require accurate monitoring of environmental conditions, structural health, and power generation parameters to optimize performance and ensure safety. The global transition toward sustainable energy sources is expected to sustain long-term growth in this application segment.

Current FLL Implementation Challenges in Sensors

Current frequency-locked loop implementations in sensor systems face significant technical barriers that limit their effectiveness in achieving optimal error reduction. The primary challenge stems from phase noise accumulation, which becomes particularly pronounced in high-frequency applications where sensors operate in demanding environmental conditions. Traditional FLL architectures struggle to maintain stable lock conditions when subjected to temperature variations, electromagnetic interference, and mechanical vibrations commonly encountered in industrial and aerospace applications.

Loop bandwidth optimization presents another critical implementation challenge. Narrow bandwidth configurations provide excellent noise filtering capabilities but suffer from slow acquisition times and poor tracking performance during rapid frequency changes. Conversely, wider bandwidth settings enable faster response times but compromise noise rejection, leading to increased jitter and phase instability. This fundamental trade-off forces engineers to make suboptimal compromises that directly impact sensor accuracy and reliability.

Power consumption constraints significantly complicate FLL implementation in battery-powered and portable sensor devices. High-performance voltage-controlled oscillators and phase-frequency detectors require substantial power budgets, while low-power alternatives often exhibit inferior spectral purity and temperature stability. The challenge intensifies in Internet of Things applications where sensors must operate for extended periods without maintenance while maintaining stringent accuracy requirements.

Digital implementation challenges arise from quantization noise and sampling rate limitations in software-defined FLL systems. Analog-to-digital converter resolution directly affects loop performance, while processing delays introduce additional phase errors that degrade overall system stability. Real-time processing requirements often exceed the computational capabilities of embedded processors, necessitating hardware acceleration or simplified algorithms that compromise performance.

Manufacturing variability and component tolerances create additional implementation hurdles. Process variations in integrated circuit fabrication result in parameter mismatches between nominally identical FLL circuits, requiring extensive calibration procedures and adaptive compensation mechanisms. Temperature coefficients of passive components introduce frequency drift that must be continuously corrected through complex control algorithms.

Integration complexity with existing sensor architectures poses substantial design challenges. Legacy sensor systems often lack the necessary interface circuitry and control signals required for FLL implementation, demanding significant hardware modifications. Signal routing, electromagnetic compatibility, and thermal management become increasingly difficult as FLL circuits are integrated into compact sensor packages with limited space and thermal dissipation capabilities.

Loop bandwidth optimization presents another critical implementation challenge. Narrow bandwidth configurations provide excellent noise filtering capabilities but suffer from slow acquisition times and poor tracking performance during rapid frequency changes. Conversely, wider bandwidth settings enable faster response times but compromise noise rejection, leading to increased jitter and phase instability. This fundamental trade-off forces engineers to make suboptimal compromises that directly impact sensor accuracy and reliability.

Power consumption constraints significantly complicate FLL implementation in battery-powered and portable sensor devices. High-performance voltage-controlled oscillators and phase-frequency detectors require substantial power budgets, while low-power alternatives often exhibit inferior spectral purity and temperature stability. The challenge intensifies in Internet of Things applications where sensors must operate for extended periods without maintenance while maintaining stringent accuracy requirements.

Digital implementation challenges arise from quantization noise and sampling rate limitations in software-defined FLL systems. Analog-to-digital converter resolution directly affects loop performance, while processing delays introduce additional phase errors that degrade overall system stability. Real-time processing requirements often exceed the computational capabilities of embedded processors, necessitating hardware acceleration or simplified algorithms that compromise performance.

Manufacturing variability and component tolerances create additional implementation hurdles. Process variations in integrated circuit fabrication result in parameter mismatches between nominally identical FLL circuits, requiring extensive calibration procedures and adaptive compensation mechanisms. Temperature coefficients of passive components introduce frequency drift that must be continuously corrected through complex control algorithms.

Integration complexity with existing sensor architectures poses substantial design challenges. Legacy sensor systems often lack the necessary interface circuitry and control signals required for FLL implementation, demanding significant hardware modifications. Signal routing, electromagnetic compatibility, and thermal management become increasingly difficult as FLL circuits are integrated into compact sensor packages with limited space and thermal dissipation capabilities.

Existing FLL Error Reduction Solutions

01 Phase-locked loop error detection and correction mechanisms

Frequency-locked loops incorporate error detection circuits that monitor phase differences between reference and feedback signals. These mechanisms identify deviations from the desired lock state and generate error signals proportional to the phase or frequency mismatch. Advanced error correction techniques include digital filtering, adaptive gain control, and compensation algorithms that minimize lock time and reduce steady-state errors in the loop operation.- Phase-locked loop error detection and correction mechanisms: Frequency-locked loops incorporate error detection circuits that monitor phase differences between reference and feedback signals. These mechanisms identify deviations from the desired lock state and generate error signals proportional to the phase or frequency mismatch. Advanced error correction techniques employ digital signal processing algorithms to minimize lock time and reduce steady-state errors, improving overall loop stability and performance.

- Bit error rate optimization in frequency synthesis: Techniques for reducing bit error rates in frequency-locked loop systems focus on minimizing jitter and phase noise in the synthesized output signal. Methods include adaptive bandwidth control, multi-stage filtering, and compensation circuits that dynamically adjust loop parameters based on operating conditions. These approaches ensure reliable data transmission by maintaining signal integrity across varying environmental and operational parameters.

- Clock recovery and synchronization error reduction: Clock recovery circuits utilizing frequency-locked loops implement sophisticated algorithms to extract timing information from incoming data streams while minimizing synchronization errors. These systems employ edge detection, oversampling techniques, and adaptive equalization to maintain accurate clock alignment even in the presence of noise and signal distortion. Error rate performance is enhanced through predictive filtering and decision-feedback mechanisms.

- Digital frequency-locked loop error measurement: Digital implementations of frequency-locked loops provide precise error measurement capabilities through time-to-digital converters and digital phase detectors. These architectures enable real-time monitoring of lock status and quantification of frequency deviation with high resolution. Statistical analysis of accumulated error data allows for predictive maintenance and adaptive tuning of loop parameters to maintain optimal performance across temperature and voltage variations.

- Noise immunity and error rate improvement techniques: Advanced filtering strategies and noise cancellation methods are employed to improve error rate performance in frequency-locked loop systems operating in harsh electromagnetic environments. Techniques include differential signaling, common-mode rejection, and adaptive threshold adjustment. Redundant loop architectures and voting mechanisms provide fault tolerance, while calibration routines compensate for component variations and aging effects to maintain low error rates over extended operational periods.

02 Bit error rate reduction in frequency-locked communication systems

Communication systems employing frequency-locked loops implement techniques to reduce bit error rates during signal transmission and reception. These include improved synchronization methods, enhanced carrier recovery circuits, and error correction coding schemes. The systems utilize precise frequency tracking to maintain signal integrity and minimize data corruption caused by frequency drift or phase noise in the transmission channel.Expand Specific Solutions03 Clock recovery and jitter reduction in frequency-locked systems

Clock recovery circuits in frequency-locked loops employ jitter reduction techniques to improve timing accuracy and reduce error rates. These systems utilize phase detectors with wide capture ranges, low-pass filtering to suppress high-frequency noise, and voltage-controlled oscillators with improved linearity. Advanced implementations include digital phase-locked loops with programmable bandwidth and adaptive jitter compensation to maintain stable clock signals under varying operating conditions.Expand Specific Solutions04 Frequency synthesizer error minimization techniques

Frequency synthesizers based on locked-loop architectures implement error minimization through fractional-N synthesis, delta-sigma modulation, and spurious tone suppression. These techniques reduce quantization errors, phase noise, and reference spurs that contribute to overall system error rates. The implementations include multi-modulus dividers, dithering schemes, and calibration algorithms that enhance frequency resolution while maintaining low phase error and fast settling times.Expand Specific Solutions05 Lock acquisition and tracking error management

Frequency-locked loop systems employ sophisticated acquisition and tracking algorithms to manage lock errors during initial synchronization and steady-state operation. These include sweep acquisition methods, frequency discriminators for coarse tuning, and narrow-band tracking loops for fine adjustment. Advanced systems incorporate lock detectors that monitor loop status, adaptive bandwidth control that optimizes tracking performance, and fast reacquisition mechanisms that minimize error propagation during signal interruptions or interference events.Expand Specific Solutions

Key Players in FLL Sensor Development Industry

The frequency-locked loop technology for next-generation sensors represents an emerging market segment within the broader sensor and semiconductor industry, currently in its early-to-mid development stage with significant growth potential driven by increasing demand for precision sensing applications. The market encompasses diverse applications from automotive radar systems to consumer electronics, with key players spanning established semiconductor giants and specialized technology firms. Technology maturity varies considerably across the competitive landscape, with companies like Samsung Electronics, Apple, and Analog Devices leveraging advanced manufacturing capabilities and extensive R&D resources to develop sophisticated frequency-locked loop implementations. Meanwhile, specialized firms such as Calterah Semiconductor and Cirrus Logic focus on niche applications, while research institutions like National Taiwan University and Zhejiang University contribute fundamental innovations. The competitive dynamics are intensifying as companies like Huawei, MediaTek, and SK Hynix integrate these technologies into their broader semiconductor portfolios, positioning frequency-locked loops as critical components for achieving reduced error rates in next-generation sensing applications across automotive, industrial, and consumer markets.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has implemented frequency-locked loop technology in their advanced sensor systems, particularly focusing on mobile and IoT applications. Their FLL approach utilizes a hybrid analog-digital architecture that combines the precision of analog phase detection with the flexibility of digital signal processing. The system incorporates machine learning algorithms to predict and compensate for frequency drift patterns, achieving error rate reductions of up to 40% compared to traditional PLL-based systems. Samsung's FLL technology features adaptive bandwidth control that automatically adjusts loop parameters based on operating conditions and sensor requirements. The implementation includes integrated noise filtering and jitter reduction mechanisms specifically optimized for high-density sensor arrays used in smartphones and wearable devices.

Strengths: Strong integration capabilities with existing mobile platforms and cost-effective mass production. Weaknesses: Limited customization options for specialized industrial applications and dependency on proprietary algorithms.

Siemens AG

Technical Solution: Siemens has implemented frequency-locked loop technology in their industrial automation and process control sensor systems, emphasizing precision and long-term stability. Their FLL approach focuses on high-resolution measurement applications where frequency stability directly impacts measurement accuracy. The system incorporates advanced digital signal processing algorithms that can track and compensate for slow frequency drift while rejecting high-frequency noise and interference. Siemens' FLL technology features distributed architecture that can synchronize multiple sensor nodes across industrial networks, enabling coordinated measurement campaigns and improved system-level accuracy. The implementation includes comprehensive diagnostic and monitoring capabilities that provide real-time feedback on frequency lock status and system performance. Their FLL systems are designed for continuous operation in industrial environments with minimal maintenance requirements.

Strengths: Robust industrial-grade design and excellent long-term stability performance. Weaknesses: Higher initial cost and complexity for simple applications and limited consumer market presence.

Core FLL Patents for Next-Gen Sensor Applications

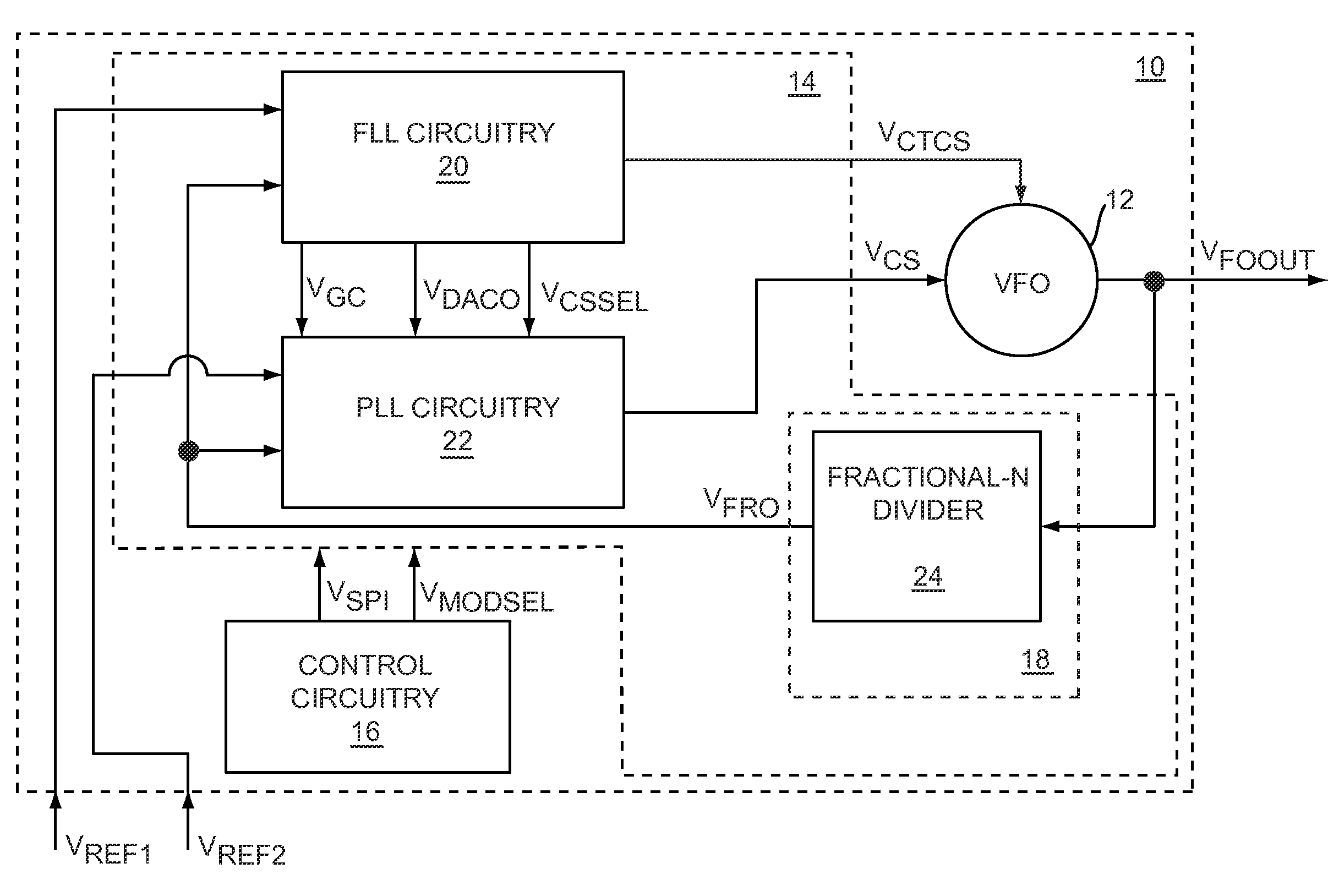

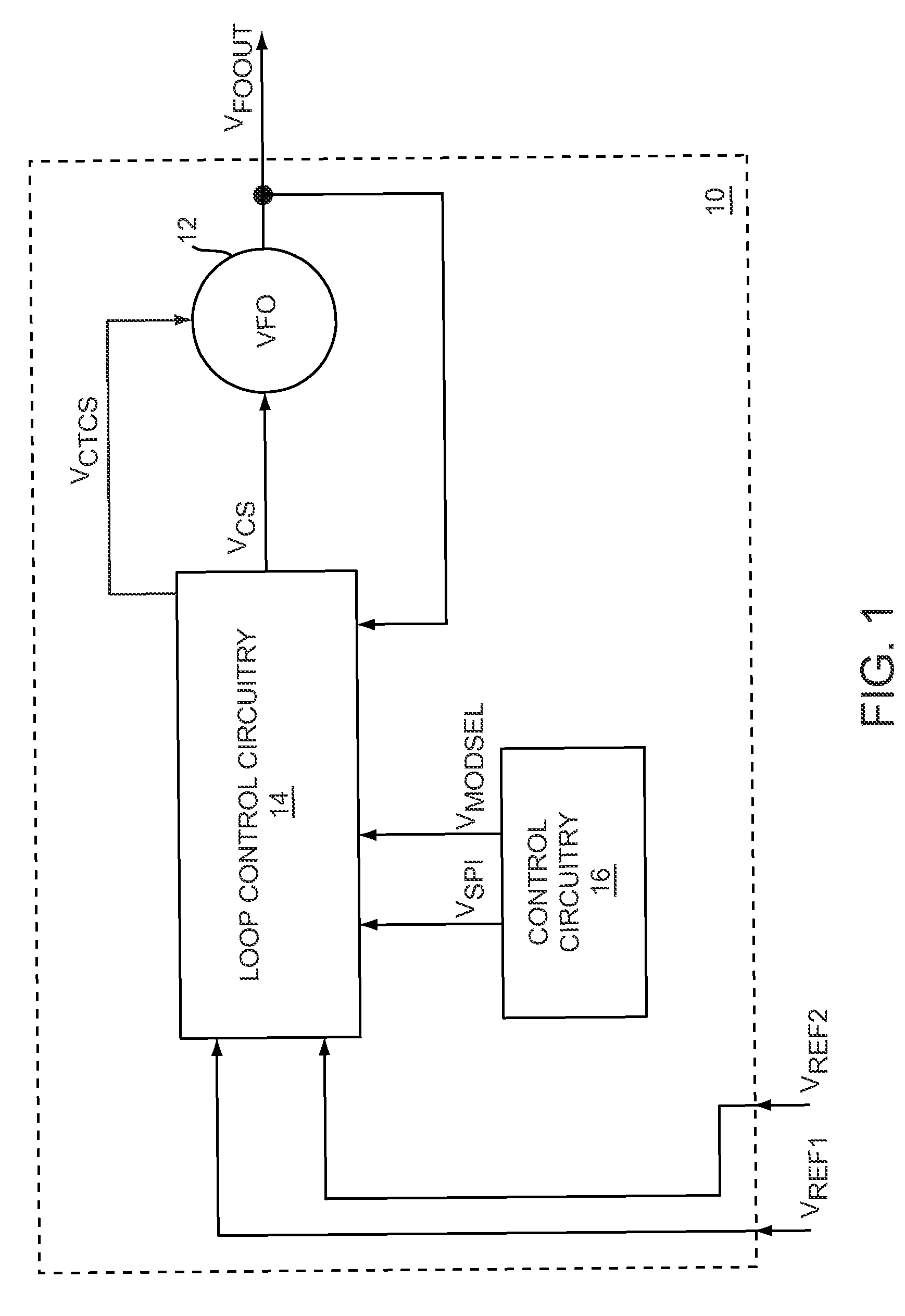

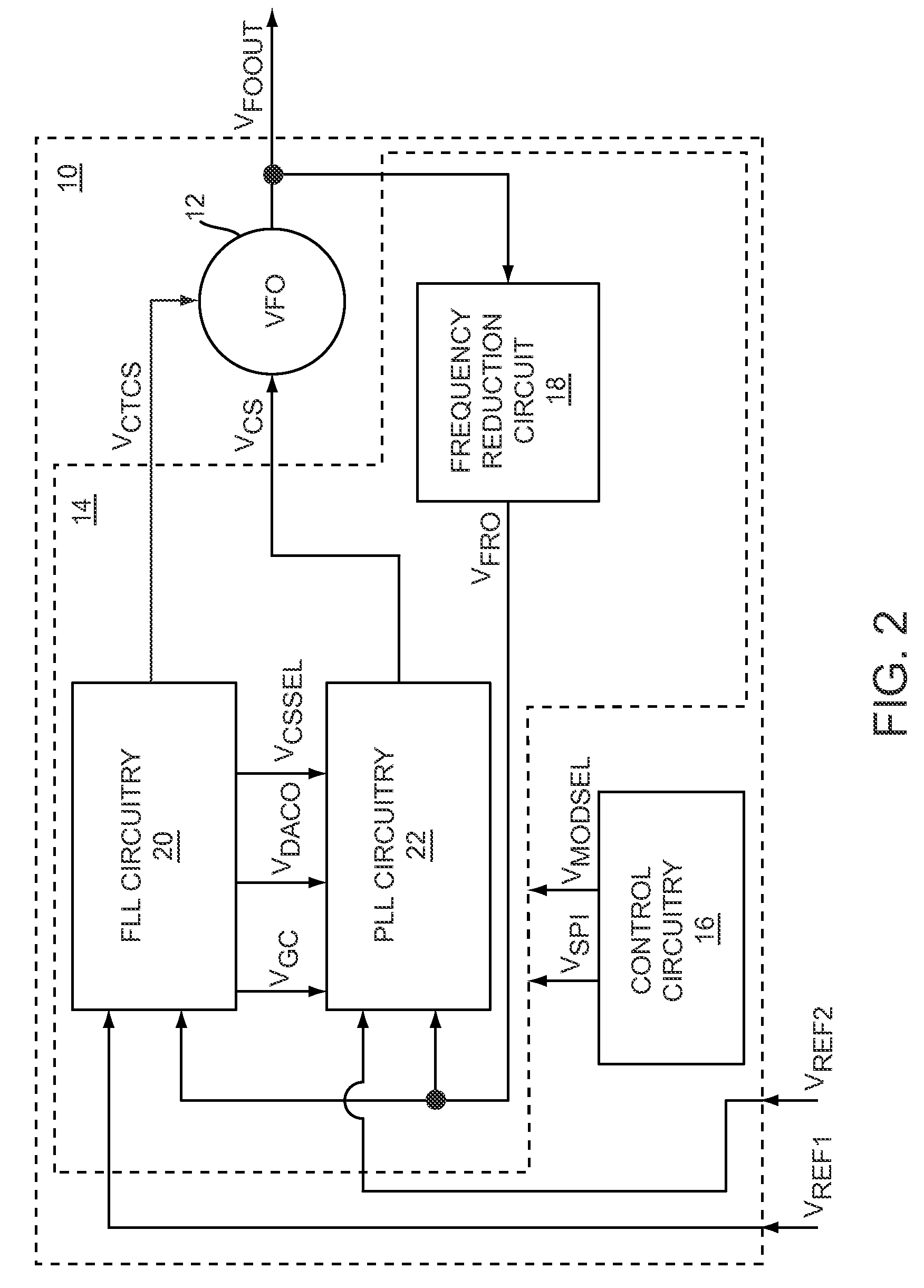

Frequency-locked loop calibration of a phase-locked loop gain

PatentInactiveUS7898343B1

Innovation

- A calibrated phase-locked loop (PLL) system with a calibration mode for measuring tuning gain and a PLL mode for normal operation, using frequency-locked loop (FLL) circuit elements for coarse tuning and PLL for high frequency accuracy, reducing phase lock times by regulating loop gain and pre-charging the PLL loop filter.

Power-supply noise suppression using a frequency-locked loop

PatentActiveUS8269544B2

Innovation

- An integrated circuit with a digitally controlled oscillator (DCO) that adjusts clock frequency based on power-supply voltage variations, using a feedback control loop and frequency-locked loop to match the manufactured delay characteristic of the critical path, thereby compensating for power-consumption-induced voltage changes and reducing power consumption.

Standards and Compliance for FLL Sensor Systems

The regulatory landscape for Frequency-Locked Loop sensor systems encompasses multiple international and regional standards that govern electromagnetic compatibility, safety, and performance requirements. IEEE 802.11 standards provide fundamental guidelines for frequency stability and spectral purity in wireless sensor applications, while IEC 61000 series addresses electromagnetic compatibility requirements crucial for FLL operation in industrial environments. These standards establish baseline performance metrics including phase noise specifications, frequency drift tolerances, and interference rejection capabilities.

Compliance with FDA regulations becomes critical when FLL sensors are deployed in medical applications, particularly for biomedical monitoring devices where frequency accuracy directly impacts patient safety. The FDA's Quality System Regulation (QSR) under 21 CFR Part 820 mandates rigorous validation protocols for sensor accuracy and reliability. Similarly, European Medical Device Regulation (MDR) 2017/745 requires comprehensive risk assessment and clinical evaluation for medical sensor systems incorporating FLL technology.

Industrial applications must adhere to IEC 61508 functional safety standards, which define Safety Integrity Levels (SIL) for sensor systems in critical applications. FLL-based sensors in automotive environments must comply with ISO 26262 standards, ensuring functional safety throughout the product lifecycle. These regulations mandate specific error detection and mitigation strategies, directly influencing FLL design parameters and redundancy requirements.

Telecommunications applications require compliance with ITU-R recommendations for frequency stability and spurious emissions. The Federal Communications Commission (FCC) Part 15 regulations in the United States and ETSI standards in Europe establish limits on electromagnetic emissions and susceptibility that directly impact FLL circuit design and shielding requirements.

Emerging standards such as IEEE 2700 for sensor performance and IEEE 1451 for smart transducer interfaces are increasingly relevant for next-generation FLL sensor systems. These standards address interoperability, calibration procedures, and data integrity requirements that influence system architecture and implementation strategies for error rate reduction.

Compliance with FDA regulations becomes critical when FLL sensors are deployed in medical applications, particularly for biomedical monitoring devices where frequency accuracy directly impacts patient safety. The FDA's Quality System Regulation (QSR) under 21 CFR Part 820 mandates rigorous validation protocols for sensor accuracy and reliability. Similarly, European Medical Device Regulation (MDR) 2017/745 requires comprehensive risk assessment and clinical evaluation for medical sensor systems incorporating FLL technology.

Industrial applications must adhere to IEC 61508 functional safety standards, which define Safety Integrity Levels (SIL) for sensor systems in critical applications. FLL-based sensors in automotive environments must comply with ISO 26262 standards, ensuring functional safety throughout the product lifecycle. These regulations mandate specific error detection and mitigation strategies, directly influencing FLL design parameters and redundancy requirements.

Telecommunications applications require compliance with ITU-R recommendations for frequency stability and spurious emissions. The Federal Communications Commission (FCC) Part 15 regulations in the United States and ETSI standards in Europe establish limits on electromagnetic emissions and susceptibility that directly impact FLL circuit design and shielding requirements.

Emerging standards such as IEEE 2700 for sensor performance and IEEE 1451 for smart transducer interfaces are increasingly relevant for next-generation FLL sensor systems. These standards address interoperability, calibration procedures, and data integrity requirements that influence system architecture and implementation strategies for error rate reduction.

Signal Integrity Considerations in FLL Design

Signal integrity represents a critical design consideration in frequency-locked loop implementations for next-generation sensors, directly impacting the system's ability to achieve reduced error rates. The electromagnetic environment within sensor systems creates numerous challenges for maintaining clean signal propagation, particularly as operating frequencies increase and component densities rise in modern sensor architectures.

Crosstalk between adjacent signal traces poses a significant threat to FLL performance, especially in multi-channel sensor configurations. High-frequency components of the reference and feedback signals can couple through parasitic capacitance and inductance, introducing unwanted noise that degrades phase detection accuracy. This interference becomes particularly problematic when multiple FLL circuits operate simultaneously within the same sensor package, requiring careful trace routing and shielding strategies.

Power supply noise represents another critical factor affecting FLL signal integrity. Voltage fluctuations on power rails can modulate the phase characteristics of oscillator circuits and introduce jitter in timing-critical components. The power distribution network must be designed with adequate decoupling capacitance and low-impedance paths to minimize supply-induced phase noise, which directly translates to sensor measurement errors.

Ground bounce and return path discontinuities significantly impact the differential signaling commonly employed in precision FLL designs. When high-speed switching occurs in digital control circuits, ground potential variations can corrupt the reference voltage levels used for phase comparison. Proper ground plane design with minimal via transitions and controlled impedance routing becomes essential for maintaining signal fidelity throughout the frequency-locked loop.

Electromagnetic interference from external sources and internal switching circuits requires comprehensive mitigation strategies. Sensitive analog components within the FLL, particularly the phase detector and voltage-controlled oscillator, must be isolated from digital switching noise through careful layout techniques, including guard rings, differential routing, and strategic component placement.

Temperature-induced signal integrity degradation affects both passive and active components within the FLL architecture. Thermal gradients can alter transmission line characteristics and component parameters, leading to phase drift and frequency instability. Design considerations must account for thermal management and temperature compensation to maintain consistent signal quality across operational temperature ranges.

Crosstalk between adjacent signal traces poses a significant threat to FLL performance, especially in multi-channel sensor configurations. High-frequency components of the reference and feedback signals can couple through parasitic capacitance and inductance, introducing unwanted noise that degrades phase detection accuracy. This interference becomes particularly problematic when multiple FLL circuits operate simultaneously within the same sensor package, requiring careful trace routing and shielding strategies.

Power supply noise represents another critical factor affecting FLL signal integrity. Voltage fluctuations on power rails can modulate the phase characteristics of oscillator circuits and introduce jitter in timing-critical components. The power distribution network must be designed with adequate decoupling capacitance and low-impedance paths to minimize supply-induced phase noise, which directly translates to sensor measurement errors.

Ground bounce and return path discontinuities significantly impact the differential signaling commonly employed in precision FLL designs. When high-speed switching occurs in digital control circuits, ground potential variations can corrupt the reference voltage levels used for phase comparison. Proper ground plane design with minimal via transitions and controlled impedance routing becomes essential for maintaining signal fidelity throughout the frequency-locked loop.

Electromagnetic interference from external sources and internal switching circuits requires comprehensive mitigation strategies. Sensitive analog components within the FLL, particularly the phase detector and voltage-controlled oscillator, must be isolated from digital switching noise through careful layout techniques, including guard rings, differential routing, and strategic component placement.

Temperature-induced signal integrity degradation affects both passive and active components within the FLL architecture. Thermal gradients can alter transmission line characteristics and component parameters, leading to phase drift and frequency instability. Design considerations must account for thermal management and temperature compensation to maintain consistent signal quality across operational temperature ranges.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!