Frequency-Locked Loop vs Direct Digital Synthesis: Harmonizing Frequencies

MAR 18, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

FLL vs DDS Technology Background and Objectives

Frequency synthesis has been a cornerstone of modern electronic systems since the mid-20th century, evolving from simple analog oscillators to sophisticated digital architectures. The development trajectory began with basic LC oscillators and progressed through phase-locked loops (PLLs) in the 1960s, eventually branching into two distinct yet complementary approaches: Frequency-Locked Loops (FLLs) and Direct Digital Synthesis (DDS). This technological evolution reflects the industry's persistent pursuit of higher precision, faster switching speeds, and improved spectral purity in frequency generation.

FLL technology emerged as a refinement of traditional PLL architectures, addressing specific limitations in frequency tracking and acquisition. Unlike PLLs that compare phase differences, FLLs directly compare frequency differences between reference and output signals, offering superior performance in environments with high phase noise or rapid frequency changes. The technology gained prominence in applications requiring robust frequency tracking, particularly in communication systems and radar applications where maintaining frequency lock under challenging conditions is paramount.

DDS technology represents a fundamentally different paradigm, leveraging digital signal processing principles to generate frequencies through mathematical computation rather than analog feedback control. Introduced in the 1970s and commercialized in the 1980s, DDS systems utilize phase accumulators and lookup tables to synthesize precise waveforms digitally. This approach enables unprecedented frequency resolution, rapid frequency switching, and excellent phase continuity, making it indispensable for modern software-defined radios and test instrumentation.

The convergence of these technologies addresses the growing demand for frequency synthesis solutions that combine the stability and tracking capabilities of FLLs with the agility and precision of DDS. Modern applications in 5G communications, aerospace systems, and high-performance computing require frequency sources that can simultaneously deliver sub-hertz resolution, microsecond switching times, and exceptional spectral purity across wide frequency ranges.

The primary objective of harmonizing FLL and DDS technologies centers on creating hybrid architectures that leverage the complementary strengths of both approaches. This integration aims to overcome individual limitations while maximizing performance benefits, ultimately delivering frequency synthesis solutions capable of meeting the stringent requirements of next-generation electronic systems where traditional single-technology approaches prove insufficient.

FLL technology emerged as a refinement of traditional PLL architectures, addressing specific limitations in frequency tracking and acquisition. Unlike PLLs that compare phase differences, FLLs directly compare frequency differences between reference and output signals, offering superior performance in environments with high phase noise or rapid frequency changes. The technology gained prominence in applications requiring robust frequency tracking, particularly in communication systems and radar applications where maintaining frequency lock under challenging conditions is paramount.

DDS technology represents a fundamentally different paradigm, leveraging digital signal processing principles to generate frequencies through mathematical computation rather than analog feedback control. Introduced in the 1970s and commercialized in the 1980s, DDS systems utilize phase accumulators and lookup tables to synthesize precise waveforms digitally. This approach enables unprecedented frequency resolution, rapid frequency switching, and excellent phase continuity, making it indispensable for modern software-defined radios and test instrumentation.

The convergence of these technologies addresses the growing demand for frequency synthesis solutions that combine the stability and tracking capabilities of FLLs with the agility and precision of DDS. Modern applications in 5G communications, aerospace systems, and high-performance computing require frequency sources that can simultaneously deliver sub-hertz resolution, microsecond switching times, and exceptional spectral purity across wide frequency ranges.

The primary objective of harmonizing FLL and DDS technologies centers on creating hybrid architectures that leverage the complementary strengths of both approaches. This integration aims to overcome individual limitations while maximizing performance benefits, ultimately delivering frequency synthesis solutions capable of meeting the stringent requirements of next-generation electronic systems where traditional single-technology approaches prove insufficient.

Market Demand for Precision Frequency Synthesis Solutions

The global precision frequency synthesis market has experienced substantial growth driven by the proliferation of wireless communication systems, aerospace applications, and high-performance instrumentation. Modern telecommunications infrastructure demands increasingly sophisticated frequency generation capabilities to support 5G networks, satellite communications, and emerging wireless standards. These applications require frequency synthesizers that can deliver exceptional phase noise performance, rapid switching speeds, and precise frequency resolution across wide bandwidth ranges.

Aerospace and defense sectors represent significant demand drivers for precision frequency synthesis solutions. Radar systems, electronic warfare equipment, and satellite payloads require frequency synthesizers capable of operating reliably in harsh environmental conditions while maintaining stringent performance specifications. The growing deployment of phased array radar systems and software-defined radio platforms has intensified requirements for agile frequency synthesis with microsecond-level switching times and sub-hertz frequency resolution.

Test and measurement instrumentation markets continue expanding as electronic systems become more complex and operate at higher frequencies. Signal generators, spectrum analyzers, and network analyzers rely heavily on precision frequency synthesis to achieve measurement accuracy and dynamic range. The emergence of millimeter-wave applications and automotive radar testing has created new market segments demanding frequency synthesis solutions operating beyond traditional microwave frequencies.

Industrial automation and scientific research applications increasingly depend on precision timing and frequency references. Atomic clocks, optical communication systems, and quantum computing platforms require ultra-stable frequency sources with exceptional long-term stability and low phase noise characteristics. These applications often demand custom frequency synthesis solutions tailored to specific performance requirements and environmental constraints.

The market exhibits distinct preferences between frequency-locked loop and direct digital synthesis approaches based on application requirements. Communications infrastructure typically favors hybrid architectures combining both technologies to optimize performance across multiple parameters. High-frequency applications often require frequency-locked loops for superior phase noise performance, while applications demanding rapid frequency agility and fine resolution increasingly adopt direct digital synthesis solutions.

Emerging markets in autonomous vehicles, Internet of Things devices, and medical instrumentation are creating new demand patterns for compact, low-power frequency synthesis solutions. These applications prioritize integration density and power efficiency while maintaining adequate performance for their specific operational requirements, driving innovation in semiconductor-based frequency synthesis architectures.

Aerospace and defense sectors represent significant demand drivers for precision frequency synthesis solutions. Radar systems, electronic warfare equipment, and satellite payloads require frequency synthesizers capable of operating reliably in harsh environmental conditions while maintaining stringent performance specifications. The growing deployment of phased array radar systems and software-defined radio platforms has intensified requirements for agile frequency synthesis with microsecond-level switching times and sub-hertz frequency resolution.

Test and measurement instrumentation markets continue expanding as electronic systems become more complex and operate at higher frequencies. Signal generators, spectrum analyzers, and network analyzers rely heavily on precision frequency synthesis to achieve measurement accuracy and dynamic range. The emergence of millimeter-wave applications and automotive radar testing has created new market segments demanding frequency synthesis solutions operating beyond traditional microwave frequencies.

Industrial automation and scientific research applications increasingly depend on precision timing and frequency references. Atomic clocks, optical communication systems, and quantum computing platforms require ultra-stable frequency sources with exceptional long-term stability and low phase noise characteristics. These applications often demand custom frequency synthesis solutions tailored to specific performance requirements and environmental constraints.

The market exhibits distinct preferences between frequency-locked loop and direct digital synthesis approaches based on application requirements. Communications infrastructure typically favors hybrid architectures combining both technologies to optimize performance across multiple parameters. High-frequency applications often require frequency-locked loops for superior phase noise performance, while applications demanding rapid frequency agility and fine resolution increasingly adopt direct digital synthesis solutions.

Emerging markets in autonomous vehicles, Internet of Things devices, and medical instrumentation are creating new demand patterns for compact, low-power frequency synthesis solutions. These applications prioritize integration density and power efficiency while maintaining adequate performance for their specific operational requirements, driving innovation in semiconductor-based frequency synthesis architectures.

Current State and Challenges in Frequency Generation

The contemporary landscape of frequency generation technology presents a complex dichotomy between traditional analog approaches and emerging digital methodologies. Frequency-Locked Loops (FLLs) and Direct Digital Synthesis (DDS) represent two fundamentally different paradigms that have evolved to address the growing demands for precise, stable, and agile frequency generation across diverse applications ranging from telecommunications to instrumentation.

Current FLL implementations demonstrate exceptional phase noise performance and frequency stability, particularly in applications requiring ultra-low jitter clock generation. These systems excel in scenarios where maintaining coherent phase relationships with reference signals is paramount. However, FLL architectures face significant limitations in frequency agility, often requiring substantial settling times when switching between frequencies, which constrains their utility in modern software-defined radio and adaptive communication systems.

DDS technology has matured considerably, offering unprecedented frequency resolution and rapid switching capabilities that enable real-time frequency hopping and complex waveform generation. Modern DDS implementations achieve frequency resolution in the micro-hertz range while maintaining switching speeds in the nanosecond domain. Nevertheless, DDS systems continue to struggle with spurious signal generation, particularly at higher output frequencies, where digital-to-analog converter limitations and quantization effects become increasingly problematic.

The integration challenges between these technologies manifest primarily in system-level implementations where both frequency stability and agility are required simultaneously. Current hybrid approaches attempt to leverage the strengths of both methodologies but often introduce additional complexity in terms of synchronization, calibration, and power consumption. Phase alignment between FLL and DDS outputs remains a critical technical hurdle, particularly in applications requiring coherent multi-channel operation.

Manufacturing variations and temperature dependencies continue to impact both technologies differently. FLL systems exhibit predictable but significant temperature coefficients that require compensation networks, while DDS implementations face challenges related to digital processing variations and reference clock stability. These factors collectively influence the overall system performance and reliability in demanding operational environments.

The bandwidth limitations inherent in both approaches present ongoing challenges for next-generation applications. FLL systems are constrained by loop dynamics and stability requirements, while DDS architectures face fundamental limitations imposed by sampling rates and reconstruction filter characteristics, creating gaps in coverage for emerging ultra-wideband applications.

Current FLL implementations demonstrate exceptional phase noise performance and frequency stability, particularly in applications requiring ultra-low jitter clock generation. These systems excel in scenarios where maintaining coherent phase relationships with reference signals is paramount. However, FLL architectures face significant limitations in frequency agility, often requiring substantial settling times when switching between frequencies, which constrains their utility in modern software-defined radio and adaptive communication systems.

DDS technology has matured considerably, offering unprecedented frequency resolution and rapid switching capabilities that enable real-time frequency hopping and complex waveform generation. Modern DDS implementations achieve frequency resolution in the micro-hertz range while maintaining switching speeds in the nanosecond domain. Nevertheless, DDS systems continue to struggle with spurious signal generation, particularly at higher output frequencies, where digital-to-analog converter limitations and quantization effects become increasingly problematic.

The integration challenges between these technologies manifest primarily in system-level implementations where both frequency stability and agility are required simultaneously. Current hybrid approaches attempt to leverage the strengths of both methodologies but often introduce additional complexity in terms of synchronization, calibration, and power consumption. Phase alignment between FLL and DDS outputs remains a critical technical hurdle, particularly in applications requiring coherent multi-channel operation.

Manufacturing variations and temperature dependencies continue to impact both technologies differently. FLL systems exhibit predictable but significant temperature coefficients that require compensation networks, while DDS implementations face challenges related to digital processing variations and reference clock stability. These factors collectively influence the overall system performance and reliability in demanding operational environments.

The bandwidth limitations inherent in both approaches present ongoing challenges for next-generation applications. FLL systems are constrained by loop dynamics and stability requirements, while DDS architectures face fundamental limitations imposed by sampling rates and reconstruction filter characteristics, creating gaps in coverage for emerging ultra-wideband applications.

Existing FLL and DDS Implementation Solutions

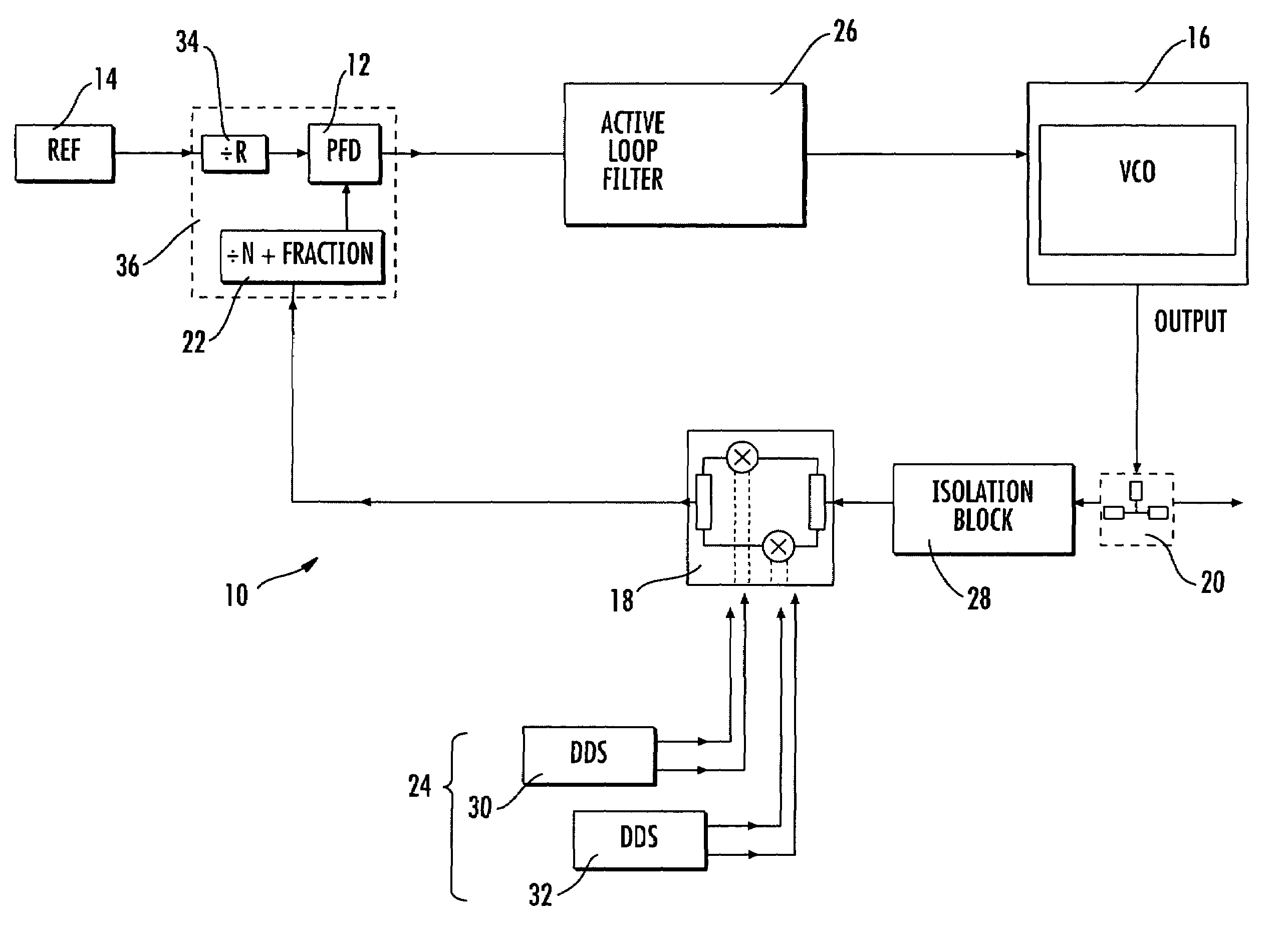

01 Frequency-locked loop with direct digital synthesis for frequency generation

Systems that combine frequency-locked loops with direct digital synthesis (DDS) technology to generate precise output frequencies. The DDS provides a digitally controlled reference signal that is locked by the frequency-locked loop, enabling accurate frequency synthesis with fine resolution and fast switching capabilities. This approach allows for programmable frequency generation with improved stability and reduced phase noise.- Frequency-locked loop using direct digital synthesis for frequency generation: Systems that employ direct digital synthesis (DDS) within a frequency-locked loop architecture to generate precise output frequencies. The DDS provides fine frequency resolution and rapid frequency switching capabilities while the frequency-locked loop maintains phase coherence and stability. This combination enables accurate frequency synthesis with low phase noise and high spectral purity.

- Phase synchronization between frequency-locked loop and DDS: Techniques for achieving phase alignment and synchronization between frequency-locked loop circuits and direct digital synthesis modules. These methods ensure that the output signals maintain consistent phase relationships, which is critical for applications requiring coherent signal generation. The synchronization mechanisms may involve phase detectors, feedback control loops, and digital phase adjustment circuits.

- Frequency tuning and calibration using combined FLL-DDS architecture: Methods for frequency tuning and calibration that leverage both frequency-locked loop and direct digital synthesis technologies. These approaches allow for wide frequency range coverage with fine resolution tuning capability. Calibration algorithms compensate for component variations and environmental factors to maintain frequency accuracy over time and operating conditions.

- Noise reduction and spurious suppression in hybrid FLL-DDS systems: Techniques for minimizing phase noise, jitter, and spurious signals in systems combining frequency-locked loops with direct digital synthesis. These methods include filtering strategies, dithering techniques, and architectural optimizations that reduce quantization noise and spurious tones inherent in digital synthesis while maintaining the stability benefits of frequency-locked operation.

- Multi-channel frequency synthesis using FLL and DDS integration: Architectures for generating multiple synchronized frequency channels by integrating frequency-locked loop and direct digital synthesis technologies. These systems enable independent control of multiple output frequencies while maintaining phase coherence across channels. Applications include multi-carrier communication systems, radar systems, and test equipment requiring multiple synchronized signal sources.

02 Phase-locked loop and DDS hybrid architecture for frequency harmonization

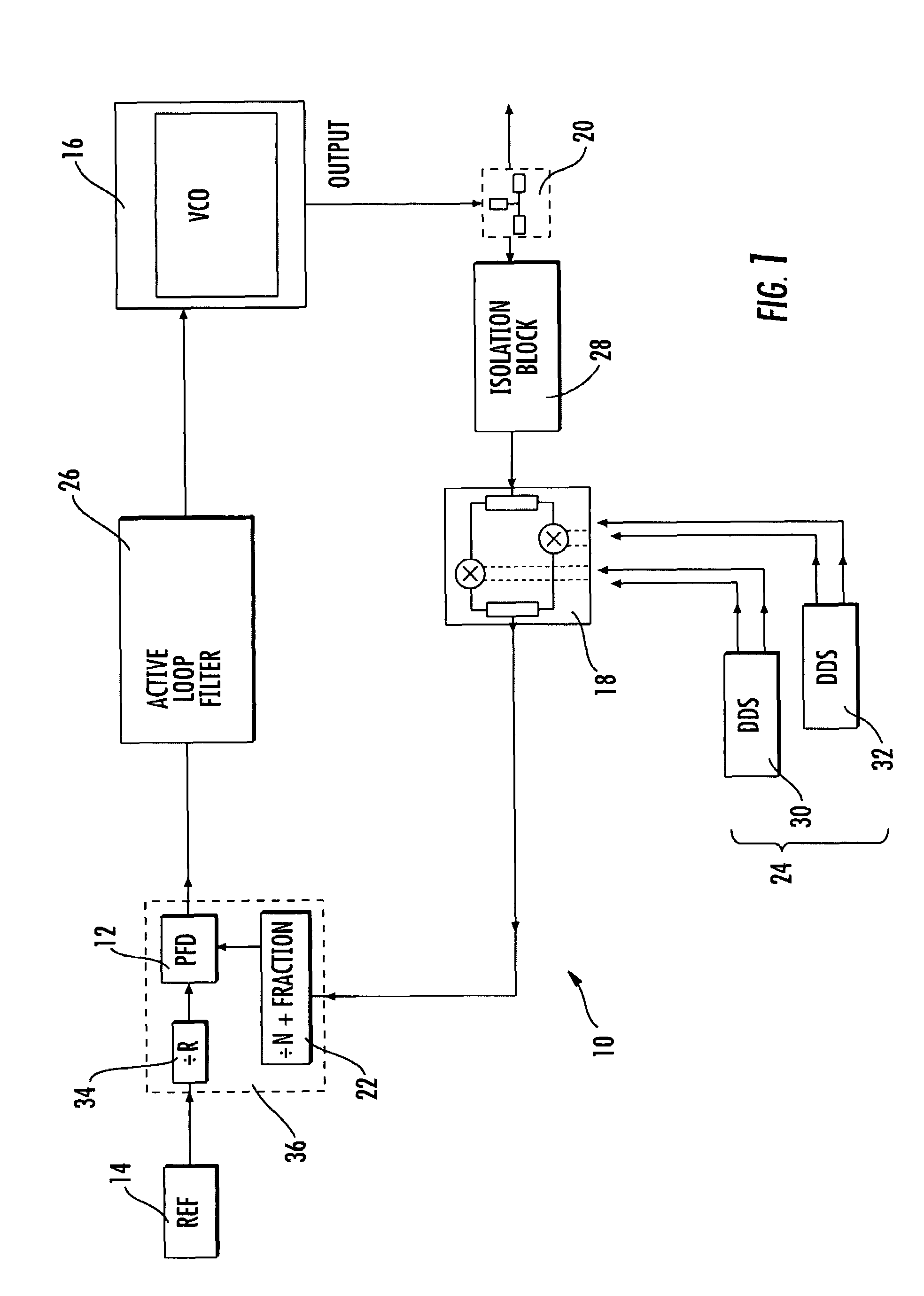

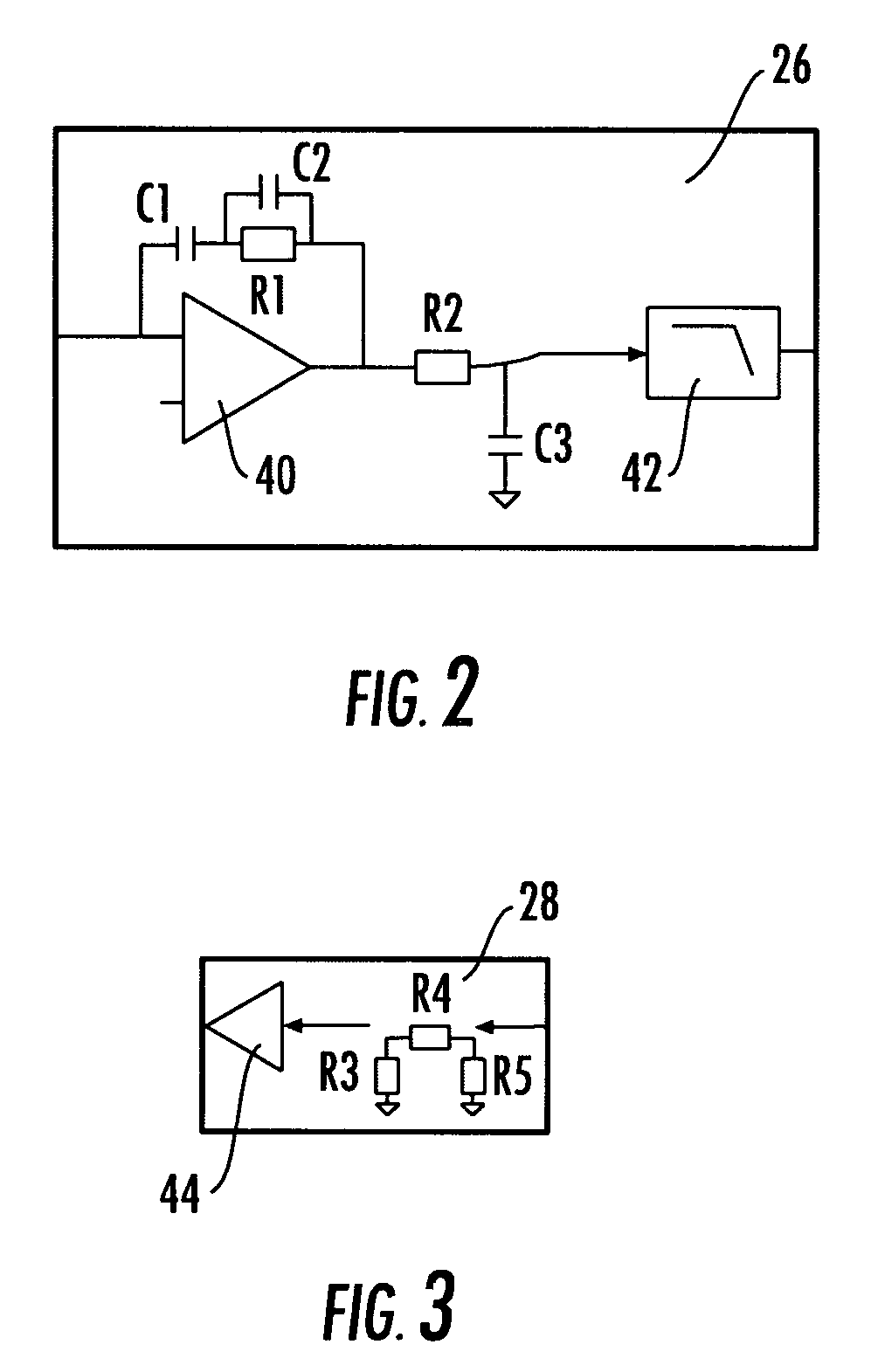

Hybrid architectures that integrate phase-locked loops with direct digital synthesis to achieve frequency harmonization and synchronization. The system uses DDS to generate a reference frequency that is phase-locked to an input signal, enabling precise frequency alignment and harmonization. This configuration provides both the frequency agility of DDS and the low phase noise characteristics of phase-locked loops.Expand Specific Solutions03 Fractional-N synthesis with DDS for fine frequency resolution

Techniques employing fractional-N frequency synthesis combined with direct digital synthesis to achieve fine frequency resolution and harmonization. The fractional-N divider works in conjunction with DDS to generate intermediate frequencies with sub-hertz resolution, enabling precise frequency tuning and harmonization across wide frequency ranges. This approach minimizes spurious signals while maintaining fast settling times.Expand Specific Solutions04 Multi-loop frequency synthesis with DDS reference

Multi-loop frequency synthesis architectures that utilize direct digital synthesis as a reference source for multiple frequency-locked loops. The DDS generates multiple reference frequencies that are independently locked by separate loops, enabling simultaneous generation of harmonized frequencies. This configuration provides flexibility in frequency planning and reduces interference between different frequency channels.Expand Specific Solutions05 Digital calibration and compensation for DDS-based frequency locking

Digital calibration and compensation techniques applied to DDS-based frequency-locked systems to improve frequency harmonization accuracy. These methods include digital pre-distortion, phase error correction, and adaptive filtering to compensate for non-linearities and spurious components in the DDS output. The calibration algorithms continuously monitor and adjust system parameters to maintain precise frequency lock and harmonization over temperature and process variations.Expand Specific Solutions

Key Players in Frequency Synthesis Industry

The frequency synthesis technology landscape, encompassing Frequency-Locked Loop (FLL) and Direct Digital Synthesis (DDS) solutions, represents a mature yet rapidly evolving market driven by 5G deployment and IoT expansion. The industry has reached technological maturity with established players like Ericsson, Nokia Technologies, and ZTE dominating telecommunications infrastructure, while semiconductor specialists including Infineon Technologies, MediaTek, Novatek Microelectronics, and Qorvo focus on component-level innovations. Defense contractors such as Lockheed Martin, Raytheon, and Northrop Grumman drive high-precision applications, alongside test equipment manufacturers like Rohde & Schwarz ensuring measurement accuracy. The competitive landscape shows clear segmentation between infrastructure providers, chip manufacturers, and specialized solution developers, with companies like Realtek and Winbond addressing consumer electronics integration, while Chinese firms including Hytera and China Electronics Technology Group strengthen domestic capabilities in this strategically important frequency harmonization technology sector.

Telefonaktiebolaget LM Ericsson

Technical Solution: Ericsson implements frequency synthesis solutions for 5G base station and network infrastructure equipment, combining DDS and PLL technologies for multi-carrier signal generation. Their approach utilizes wideband DDS engines operating at sampling rates exceeding 10 GSPS, integrated with ultra-low phase noise PLLs to support massive MIMO antenna arrays with phase coherence better than 1 degree across all elements. The company's frequency synthesis architecture supports carrier aggregation across multiple frequency bands simultaneously, with frequency switching times under 1 microsecond to enable dynamic spectrum access. Ericsson's solutions achieve spectral mask compliance for 5G NR standards while supporting bandwidth up to 400 MHz per carrier with adjacent channel leakage ratio better than -45 dBc.

Strengths: Optimized for 5G infrastructure requirements, excellent multi-carrier performance and phase coherence. Weaknesses: Highly specialized for telecom infrastructure, limited applicability outside network equipment markets.

Rohde & Schwarz GmbH & Co. KG

Technical Solution: Rohde & Schwarz develops advanced frequency synthesis solutions combining both FLL and DDS technologies for test and measurement equipment. Their approach utilizes high-resolution DDS cores with frequency accuracy better than 1 ppb, integrated with phase-locked loop architectures for enhanced spectral purity. The company's R&S FSW signal analyzers employ hybrid frequency synthesis combining DDS flexibility with PLL stability, achieving phase noise performance below -130 dBc/Hz at 10 kHz offset. Their solutions support frequency ranges from DC to 67 GHz with sub-Hz resolution, enabling precise frequency control for 5G and satellite communication testing applications.

Strengths: Industry-leading phase noise performance and frequency accuracy, comprehensive frequency range coverage. Weaknesses: High cost and complexity, primarily focused on test equipment rather than mass market applications.

Core Patents in Frequency Harmonization Technologies

Direct digital synthesis (DDS) phase locked loop (PLL) frequency synthesizer and associated methods

PatentInactiveUS7250823B2

Innovation

- A phase locked loop (PLL) frequency synthesizer with a phase detector, voltage-controlled oscillator, IQ modulator mixer, active loop filter, and isolation block, utilizing dual direct digital synthesizers to generate narrow frequency steps and reduce output spurs, allowing for fine frequency tuning with a high reference frequency.

Phase-locked loop type frequency synthesizer having improved loop response

PatentInactiveEP0444650A3

Innovation

- A frequency synthesizer using a phase-locked loop with a direct digital synthesizer and a fixed frequency divider, where the output frequency is determined by a combination of a predetermined frequency and a variable frequency multiplied by a coefficient, allowing for a quick loop response even with narrow channel spacing.

Signal Integrity Standards and Compliance Requirements

Signal integrity standards and compliance requirements play a critical role in determining the optimal frequency synthesis approach between Frequency-Locked Loops and Direct Digital Synthesis systems. These standards establish the fundamental performance benchmarks that both technologies must meet to ensure reliable operation in various applications, from telecommunications infrastructure to precision instrumentation.

The IEEE 802.3 Ethernet standards impose stringent jitter requirements, typically limiting phase noise to -120 dBc/Hz at 10 kHz offset for high-speed data transmission applications. FLL systems generally demonstrate superior performance in meeting these low-jitter specifications due to their analog phase-locked nature, which inherently filters high-frequency noise components. DDS architectures, while offering exceptional frequency agility, face challenges in achieving comparable phase noise performance, particularly at higher output frequencies where quantization noise becomes more pronounced.

Electromagnetic compatibility regulations, including FCC Part 15 and CISPR standards, establish spurious emission limits that significantly impact the choice between FLL and DDS implementations. DDS systems must carefully manage spectral purity through advanced filtering techniques and careful clock architecture design to suppress unwanted harmonics and spurious tones that arise from the digital synthesis process. The discrete nature of DDS output inherently generates quantization-related spurs that require sophisticated mitigation strategies.

Military and aerospace applications demand compliance with MIL-STD-461 for electromagnetic interference control and DO-160 for avionics equipment. These standards impose particularly stringent requirements on frequency stability, phase noise, and spurious content. FLL systems often provide inherent advantages in meeting these demanding specifications, especially for applications requiring ultra-low phase noise performance such as radar and satellite communication systems.

Telecommunications standards including ITU-T G.813 for synchronous digital hierarchy networks specify precise frequency accuracy and stability requirements. The choice between FLL and DDS must consider long-term frequency drift, temperature stability, and aging characteristics. While DDS offers superior frequency resolution and switching speed, FLL implementations typically provide better long-term stability and lower phase noise floors essential for carrier-grade applications.

Compliance verification requires comprehensive testing protocols including phase noise measurements, spurious signal analysis, and electromagnetic compatibility assessments. The testing methodologies and acceptance criteria directly influence the design trade-offs between FLL and DDS approaches, ultimately determining which technology better serves specific application requirements while maintaining regulatory compliance.

The IEEE 802.3 Ethernet standards impose stringent jitter requirements, typically limiting phase noise to -120 dBc/Hz at 10 kHz offset for high-speed data transmission applications. FLL systems generally demonstrate superior performance in meeting these low-jitter specifications due to their analog phase-locked nature, which inherently filters high-frequency noise components. DDS architectures, while offering exceptional frequency agility, face challenges in achieving comparable phase noise performance, particularly at higher output frequencies where quantization noise becomes more pronounced.

Electromagnetic compatibility regulations, including FCC Part 15 and CISPR standards, establish spurious emission limits that significantly impact the choice between FLL and DDS implementations. DDS systems must carefully manage spectral purity through advanced filtering techniques and careful clock architecture design to suppress unwanted harmonics and spurious tones that arise from the digital synthesis process. The discrete nature of DDS output inherently generates quantization-related spurs that require sophisticated mitigation strategies.

Military and aerospace applications demand compliance with MIL-STD-461 for electromagnetic interference control and DO-160 for avionics equipment. These standards impose particularly stringent requirements on frequency stability, phase noise, and spurious content. FLL systems often provide inherent advantages in meeting these demanding specifications, especially for applications requiring ultra-low phase noise performance such as radar and satellite communication systems.

Telecommunications standards including ITU-T G.813 for synchronous digital hierarchy networks specify precise frequency accuracy and stability requirements. The choice between FLL and DDS must consider long-term frequency drift, temperature stability, and aging characteristics. While DDS offers superior frequency resolution and switching speed, FLL implementations typically provide better long-term stability and lower phase noise floors essential for carrier-grade applications.

Compliance verification requires comprehensive testing protocols including phase noise measurements, spurious signal analysis, and electromagnetic compatibility assessments. The testing methodologies and acceptance criteria directly influence the design trade-offs between FLL and DDS approaches, ultimately determining which technology better serves specific application requirements while maintaining regulatory compliance.

Performance Trade-offs in FLL-DDS Integration

The integration of Frequency-Locked Loop (FLL) and Direct Digital Synthesis (DDS) technologies presents a complex landscape of performance trade-offs that must be carefully evaluated for optimal system design. The fundamental challenge lies in balancing the inherent advantages of each technology while mitigating their respective limitations when combined in a unified frequency generation architecture.

Phase noise performance represents one of the most critical trade-offs in FLL-DDS integration. While DDS systems excel in providing exceptional frequency resolution and rapid switching capabilities, they typically exhibit higher phase noise floors compared to traditional analog synthesis methods. FLL circuits, conversely, offer superior phase noise characteristics through their feedback-based frequency tracking mechanisms. The integration challenge involves leveraging FLL's noise filtering capabilities to clean up DDS-generated signals without compromising the digital synthesis advantages.

Frequency agility versus stability constitutes another significant performance dimension. DDS technology enables instantaneous frequency changes with precise digital control, supporting applications requiring rapid frequency hopping or complex modulation schemes. However, FLL systems prioritize frequency stability and lock acquisition, which can introduce settling time delays that conflict with DDS agility requirements. The integration must optimize the loop bandwidth and response characteristics to maintain acceptable switching speeds while preserving frequency accuracy.

Power consumption trade-offs become particularly pronounced in portable and battery-operated applications. DDS implementations typically require high-speed digital processing and digital-to-analog conversion, resulting in substantial power draw. FLL circuits add additional power overhead through their analog feedback components and reference oscillators. Integrated solutions must balance performance requirements against power budgets, often necessitating selective activation of subsystems or dynamic power management strategies.

Spurious signal management presents unique challenges in combined architectures. DDS systems inherently generate spurious outputs due to digital quantization effects and DAC nonlinearities, while FLL circuits can introduce their own spurious content through reference breakthrough and mixing products. The integration design must implement appropriate filtering and isolation techniques to maintain overall spectral purity without degrading the beneficial characteristics of either subsystem.

Temperature stability and environmental robustness represent additional performance considerations. FLL systems typically demonstrate superior temperature coefficient performance through their closed-loop operation, while DDS accuracy depends heavily on reference clock stability. Integrated solutions must address thermal management and compensation strategies to maintain performance across operational temperature ranges while preserving the precision advantages of digital synthesis.

Phase noise performance represents one of the most critical trade-offs in FLL-DDS integration. While DDS systems excel in providing exceptional frequency resolution and rapid switching capabilities, they typically exhibit higher phase noise floors compared to traditional analog synthesis methods. FLL circuits, conversely, offer superior phase noise characteristics through their feedback-based frequency tracking mechanisms. The integration challenge involves leveraging FLL's noise filtering capabilities to clean up DDS-generated signals without compromising the digital synthesis advantages.

Frequency agility versus stability constitutes another significant performance dimension. DDS technology enables instantaneous frequency changes with precise digital control, supporting applications requiring rapid frequency hopping or complex modulation schemes. However, FLL systems prioritize frequency stability and lock acquisition, which can introduce settling time delays that conflict with DDS agility requirements. The integration must optimize the loop bandwidth and response characteristics to maintain acceptable switching speeds while preserving frequency accuracy.

Power consumption trade-offs become particularly pronounced in portable and battery-operated applications. DDS implementations typically require high-speed digital processing and digital-to-analog conversion, resulting in substantial power draw. FLL circuits add additional power overhead through their analog feedback components and reference oscillators. Integrated solutions must balance performance requirements against power budgets, often necessitating selective activation of subsystems or dynamic power management strategies.

Spurious signal management presents unique challenges in combined architectures. DDS systems inherently generate spurious outputs due to digital quantization effects and DAC nonlinearities, while FLL circuits can introduce their own spurious content through reference breakthrough and mixing products. The integration design must implement appropriate filtering and isolation techniques to maintain overall spectral purity without degrading the beneficial characteristics of either subsystem.

Temperature stability and environmental robustness represent additional performance considerations. FLL systems typically demonstrate superior temperature coefficient performance through their closed-loop operation, while DDS accuracy depends heavily on reference clock stability. Integrated solutions must address thermal management and compensation strategies to maintain performance across operational temperature ranges while preserving the precision advantages of digital synthesis.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!