How to Configure Frequency-Locked Loop for Adaptive Signal Processing

MAR 18, 202610 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

FLL Adaptive Signal Processing Background and Objectives

Frequency-Locked Loop (FLL) technology has emerged as a critical component in modern adaptive signal processing systems, addressing the fundamental challenge of maintaining phase coherence in dynamic communication environments. The evolution of FLL systems traces back to the early developments in phase-locked loop technology during the 1960s, where researchers recognized the limitations of traditional PLL systems in handling rapid frequency variations and sought alternative approaches for frequency tracking applications.

The technological landscape has witnessed significant advancement from basic analog FLL implementations to sophisticated digital adaptive systems capable of real-time parameter adjustment. Early FLL architectures primarily focused on frequency discrimination and tracking, but contemporary systems integrate machine learning algorithms and adaptive filtering techniques to enhance performance in complex signal environments. This evolution reflects the growing demand for robust signal processing solutions in applications ranging from satellite communications to software-defined radio systems.

Current market drivers for FLL-based adaptive signal processing stem from the proliferation of wireless communication standards, increasing spectrum congestion, and the need for cognitive radio systems. The technology addresses critical challenges in 5G networks, Internet of Things deployments, and military communication systems where signal characteristics change rapidly due to environmental factors, interference, or intentional jamming. The global market for adaptive signal processing solutions incorporating FLL technology is experiencing substantial growth, driven by defense modernization programs and commercial wireless infrastructure expansion.

The primary technical objectives for FLL configuration in adaptive signal processing encompass achieving optimal frequency tracking accuracy while maintaining system stability across varying operational conditions. Key performance targets include minimizing frequency estimation error, reducing convergence time for adaptive algorithms, and ensuring robust operation in low signal-to-noise ratio environments. These objectives require careful consideration of loop bandwidth selection, discriminator design, and integration with adaptive filtering architectures.

Contemporary research focuses on developing hybrid FLL-PLL systems that combine the frequency tracking advantages of FLL with the phase coherence benefits of PLL technology. The integration of artificial intelligence techniques aims to enable autonomous parameter optimization based on real-time signal characteristics assessment. Future developments target the implementation of multi-dimensional adaptive algorithms capable of simultaneous frequency, phase, and amplitude tracking in complex modulation schemes, positioning FLL technology as a cornerstone for next-generation adaptive communication systems.

The technological landscape has witnessed significant advancement from basic analog FLL implementations to sophisticated digital adaptive systems capable of real-time parameter adjustment. Early FLL architectures primarily focused on frequency discrimination and tracking, but contemporary systems integrate machine learning algorithms and adaptive filtering techniques to enhance performance in complex signal environments. This evolution reflects the growing demand for robust signal processing solutions in applications ranging from satellite communications to software-defined radio systems.

Current market drivers for FLL-based adaptive signal processing stem from the proliferation of wireless communication standards, increasing spectrum congestion, and the need for cognitive radio systems. The technology addresses critical challenges in 5G networks, Internet of Things deployments, and military communication systems where signal characteristics change rapidly due to environmental factors, interference, or intentional jamming. The global market for adaptive signal processing solutions incorporating FLL technology is experiencing substantial growth, driven by defense modernization programs and commercial wireless infrastructure expansion.

The primary technical objectives for FLL configuration in adaptive signal processing encompass achieving optimal frequency tracking accuracy while maintaining system stability across varying operational conditions. Key performance targets include minimizing frequency estimation error, reducing convergence time for adaptive algorithms, and ensuring robust operation in low signal-to-noise ratio environments. These objectives require careful consideration of loop bandwidth selection, discriminator design, and integration with adaptive filtering architectures.

Contemporary research focuses on developing hybrid FLL-PLL systems that combine the frequency tracking advantages of FLL with the phase coherence benefits of PLL technology. The integration of artificial intelligence techniques aims to enable autonomous parameter optimization based on real-time signal characteristics assessment. Future developments target the implementation of multi-dimensional adaptive algorithms capable of simultaneous frequency, phase, and amplitude tracking in complex modulation schemes, positioning FLL technology as a cornerstone for next-generation adaptive communication systems.

Market Demand for Adaptive FLL Signal Processing Solutions

The telecommunications industry represents the largest market segment for adaptive FLL signal processing solutions, driven by the exponential growth of 5G networks and the increasing complexity of wireless communication systems. Mobile network operators require sophisticated frequency synchronization capabilities to maintain signal integrity across diverse propagation environments and dynamic channel conditions. The demand is particularly pronounced in dense urban deployments where multipath interference and frequency selective fading create challenging operating conditions that traditional fixed-parameter systems cannot adequately address.

Satellite communication systems constitute another significant market driver, especially with the rapid expansion of low Earth orbit constellation deployments. These systems face unique challenges including Doppler frequency shifts, atmospheric interference, and the need for seamless handover between satellites. Adaptive FLL solutions enable real-time frequency tracking and compensation, ensuring reliable communication links despite the dynamic nature of satellite-to-ground and inter-satellite communications.

The aerospace and defense sector demonstrates substantial demand for adaptive signal processing capabilities, particularly in radar systems, electronic warfare applications, and secure communications. Military and aerospace applications require robust frequency tracking under extreme conditions, including high-speed platform movements, intentional jamming, and harsh electromagnetic environments. The ability to adaptively configure FLL parameters based on real-time threat assessment and signal conditions has become a critical requirement for modern defense systems.

Industrial automation and Internet of Things applications are emerging as significant growth areas for adaptive FLL technologies. Manufacturing environments with high electromagnetic interference levels and varying operational conditions benefit from adaptive frequency synchronization in wireless sensor networks and industrial communication protocols. The increasing adoption of Industry 4.0 concepts drives demand for reliable, self-configuring communication systems that can maintain performance across diverse industrial environments.

The automotive sector presents growing opportunities, particularly with the advancement of vehicle-to-everything communication systems and autonomous driving technologies. These applications require precise frequency synchronization for safety-critical communications, where adaptive FLL solutions provide the necessary robustness against vehicular mobility, urban canyon effects, and interference from other electronic systems.

Research institutions and academic organizations represent a specialized but important market segment, focusing on advancing the theoretical foundations and practical implementations of adaptive signal processing algorithms. This segment drives innovation and creates demand for flexible, configurable FLL solutions that support experimental research and algorithm development activities.

Satellite communication systems constitute another significant market driver, especially with the rapid expansion of low Earth orbit constellation deployments. These systems face unique challenges including Doppler frequency shifts, atmospheric interference, and the need for seamless handover between satellites. Adaptive FLL solutions enable real-time frequency tracking and compensation, ensuring reliable communication links despite the dynamic nature of satellite-to-ground and inter-satellite communications.

The aerospace and defense sector demonstrates substantial demand for adaptive signal processing capabilities, particularly in radar systems, electronic warfare applications, and secure communications. Military and aerospace applications require robust frequency tracking under extreme conditions, including high-speed platform movements, intentional jamming, and harsh electromagnetic environments. The ability to adaptively configure FLL parameters based on real-time threat assessment and signal conditions has become a critical requirement for modern defense systems.

Industrial automation and Internet of Things applications are emerging as significant growth areas for adaptive FLL technologies. Manufacturing environments with high electromagnetic interference levels and varying operational conditions benefit from adaptive frequency synchronization in wireless sensor networks and industrial communication protocols. The increasing adoption of Industry 4.0 concepts drives demand for reliable, self-configuring communication systems that can maintain performance across diverse industrial environments.

The automotive sector presents growing opportunities, particularly with the advancement of vehicle-to-everything communication systems and autonomous driving technologies. These applications require precise frequency synchronization for safety-critical communications, where adaptive FLL solutions provide the necessary robustness against vehicular mobility, urban canyon effects, and interference from other electronic systems.

Research institutions and academic organizations represent a specialized but important market segment, focusing on advancing the theoretical foundations and practical implementations of adaptive signal processing algorithms. This segment drives innovation and creates demand for flexible, configurable FLL solutions that support experimental research and algorithm development activities.

Current FLL Configuration Challenges and Technical Barriers

Frequency-Locked Loop configuration for adaptive signal processing faces significant technical barriers that stem from the inherent complexity of maintaining phase coherence while adapting to dynamic signal environments. The primary challenge lies in achieving optimal loop bandwidth selection, where engineers must balance acquisition speed against noise rejection capabilities. Traditional fixed-bandwidth approaches prove inadequate when dealing with rapidly changing signal conditions, leading to either sluggish response times or excessive noise amplification.

Loop stability represents another critical barrier, particularly when implementing adaptive algorithms that modify loop parameters in real-time. The interaction between adaptation mechanisms and loop dynamics can introduce instabilities that manifest as phase jitter, frequency overshoot, or complete loss of lock. These stability issues become more pronounced in multi-path environments where signal reflections create additional phase distortions that challenge conventional FLL architectures.

Parameter optimization presents substantial difficulties due to the multi-dimensional nature of FLL configuration space. Engineers must simultaneously optimize loop gain, damping factor, natural frequency, and adaptation step size while considering their interdependencies. The lack of standardized optimization methodologies forces designers to rely on iterative trial-and-error approaches, resulting in suboptimal configurations and extended development cycles.

Hardware implementation constraints impose additional barriers, particularly regarding computational complexity and power consumption. Adaptive FLL algorithms require real-time processing capabilities that strain embedded system resources, especially in battery-powered applications. The trade-off between adaptation sophistication and implementation feasibility often forces compromises that limit overall system performance.

Signal acquisition challenges become amplified in adaptive scenarios where initial lock conditions may vary significantly from steady-state requirements. Cold start scenarios, where no prior signal knowledge exists, present particular difficulties for adaptive FLL systems that rely on historical data for parameter adjustment. The chicken-and-egg problem of requiring stable lock to enable adaptation while needing adaptation to achieve stable lock remains a fundamental design challenge.

Environmental robustness issues further complicate FLL configuration, as temperature variations, component aging, and electromagnetic interference can degrade loop performance over time. Adaptive mechanisms must account for these slowly varying parameters while maintaining responsiveness to legitimate signal changes, creating additional complexity in algorithm design and validation processes.

Loop stability represents another critical barrier, particularly when implementing adaptive algorithms that modify loop parameters in real-time. The interaction between adaptation mechanisms and loop dynamics can introduce instabilities that manifest as phase jitter, frequency overshoot, or complete loss of lock. These stability issues become more pronounced in multi-path environments where signal reflections create additional phase distortions that challenge conventional FLL architectures.

Parameter optimization presents substantial difficulties due to the multi-dimensional nature of FLL configuration space. Engineers must simultaneously optimize loop gain, damping factor, natural frequency, and adaptation step size while considering their interdependencies. The lack of standardized optimization methodologies forces designers to rely on iterative trial-and-error approaches, resulting in suboptimal configurations and extended development cycles.

Hardware implementation constraints impose additional barriers, particularly regarding computational complexity and power consumption. Adaptive FLL algorithms require real-time processing capabilities that strain embedded system resources, especially in battery-powered applications. The trade-off between adaptation sophistication and implementation feasibility often forces compromises that limit overall system performance.

Signal acquisition challenges become amplified in adaptive scenarios where initial lock conditions may vary significantly from steady-state requirements. Cold start scenarios, where no prior signal knowledge exists, present particular difficulties for adaptive FLL systems that rely on historical data for parameter adjustment. The chicken-and-egg problem of requiring stable lock to enable adaptation while needing adaptation to achieve stable lock remains a fundamental design challenge.

Environmental robustness issues further complicate FLL configuration, as temperature variations, component aging, and electromagnetic interference can degrade loop performance over time. Adaptive mechanisms must account for these slowly varying parameters while maintaining responsiveness to legitimate signal changes, creating additional complexity in algorithm design and validation processes.

Existing FLL Configuration Methods and Approaches

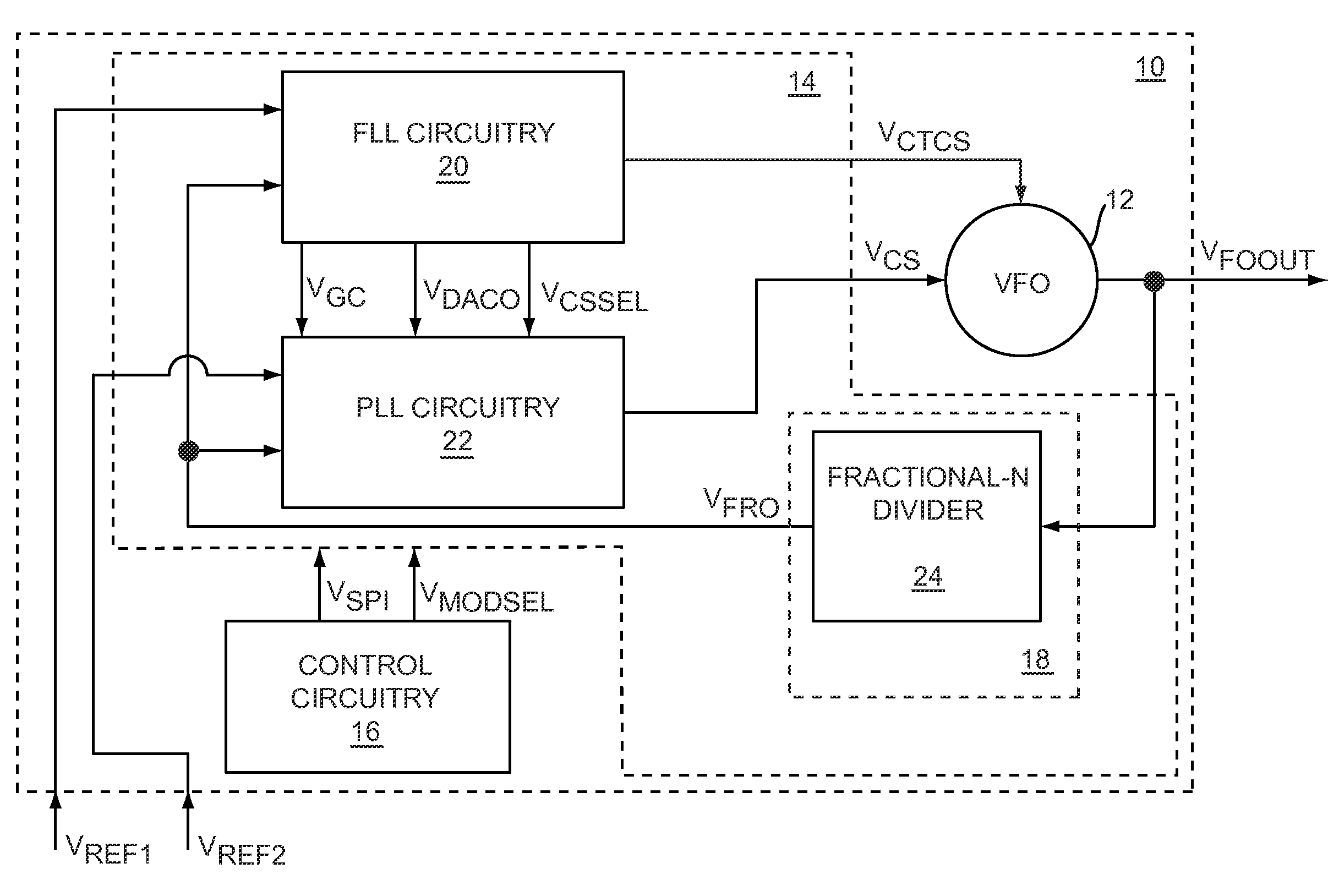

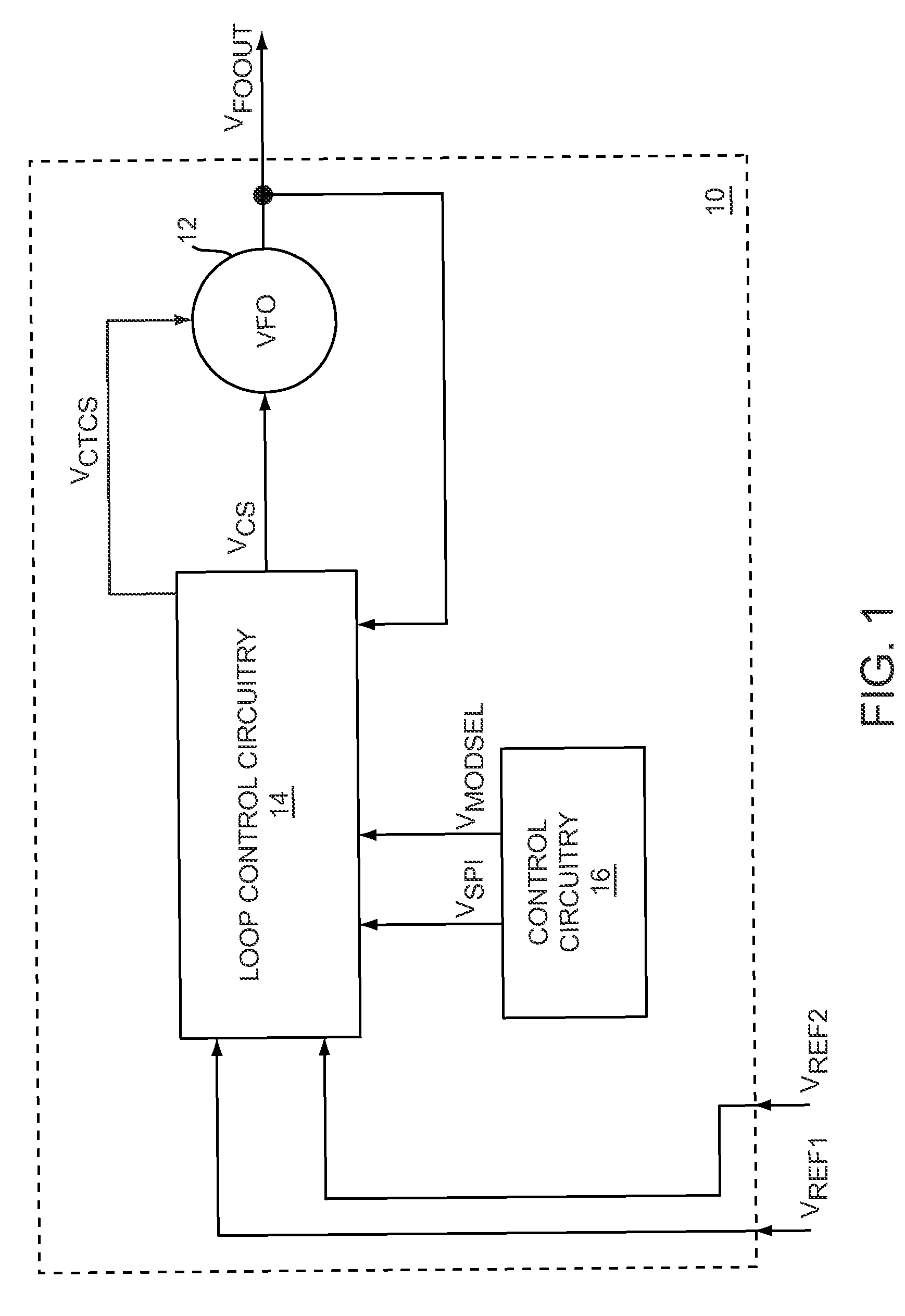

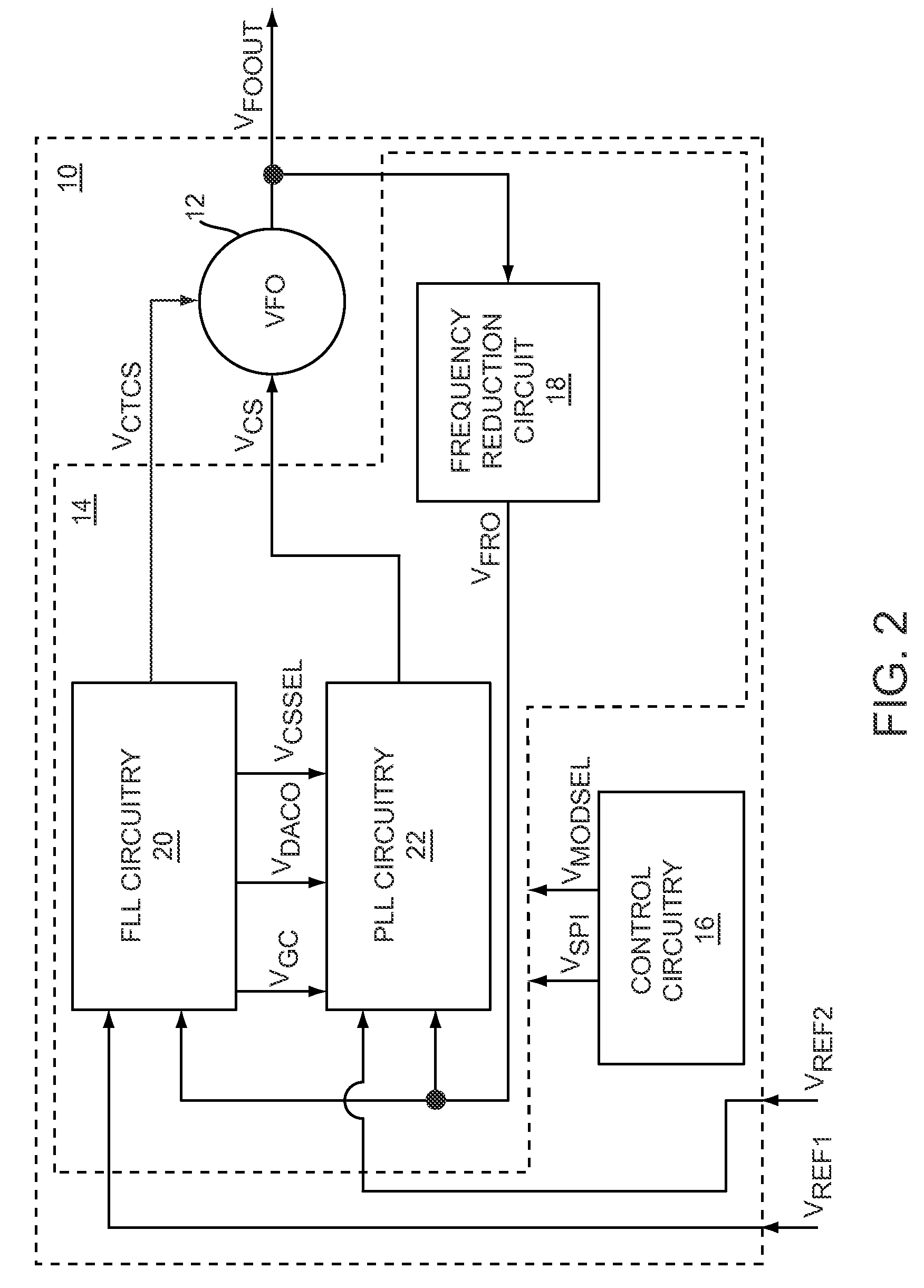

01 Frequency-locked loop circuit architecture and design

Frequency-locked loop (FLL) circuits provide an alternative to phase-locked loops for frequency synchronization applications. These circuits typically include a frequency detector, loop filter, and voltage-controlled oscillator arranged in a feedback configuration. The frequency detector compares input and output frequencies to generate an error signal that adjusts the oscillator frequency. FLL architectures offer advantages in certain applications such as faster lock times and improved stability under specific operating conditions.- Frequency-locked loop circuit architecture and design: Frequency-locked loop (FLL) circuits provide an alternative to phase-locked loops (PLLs) by locking to the frequency rather than the phase of an input signal. These circuits typically include a frequency detector, loop filter, and voltage-controlled oscillator (VCO) arranged in a feedback configuration. The architecture eliminates phase ambiguity issues and can provide faster lock times compared to traditional PLLs. Various circuit topologies and design methodologies have been developed to optimize performance parameters such as lock range, stability, and noise immunity.

- Frequency detection and comparison techniques: Frequency detection is a critical component in frequency-locked loop systems. Various techniques have been developed to accurately detect and compare the frequencies of input and reference signals. These methods include digital frequency discriminators, edge detection circuits, and counter-based frequency measurement systems. The frequency detector generates an error signal proportional to the frequency difference, which is then used to adjust the oscillator frequency. Advanced detection schemes improve accuracy, reduce dead zones, and enhance the dynamic range of the frequency-locked loop.

- Digital frequency-locked loop implementations: Digital implementations of frequency-locked loops utilize digital signal processing techniques and components such as digital frequency detectors, digital filters, and digitally-controlled oscillators. These systems offer advantages including programmability, reduced sensitivity to component variations, and easier integration with digital systems. Digital frequency-locked loops can be implemented using microprocessors, digital signal processors, or dedicated digital logic circuits. They are particularly useful in applications requiring precise frequency synthesis and clock recovery in digital communication systems.

- Frequency-locked loop applications in communication systems: Frequency-locked loops are widely used in communication systems for various applications including frequency synthesis, clock recovery, and carrier synchronization. In wireless communication systems, they enable accurate frequency tracking and demodulation of received signals. They are also employed in data transmission systems to recover clock signals from incoming data streams. The frequency-locked loop's ability to quickly acquire and maintain frequency lock makes it suitable for burst-mode communications and frequency-hopping systems where rapid frequency changes occur.

- Stability and performance optimization methods: Various techniques have been developed to optimize the stability and performance of frequency-locked loops. These include adaptive loop bandwidth control, multi-loop architectures, and advanced filtering techniques to reduce jitter and phase noise. Methods for improving acquisition time and extending the capture range have been implemented through intelligent frequency search algorithms and multi-stage locking processes. Compensation techniques address issues such as temperature variations, supply voltage fluctuations, and process variations to maintain consistent performance across different operating conditions.

02 Frequency detection and comparison techniques

Various methods are employed to detect and compare frequencies in frequency-locked loop systems. These techniques include digital frequency discriminators, edge detection circuits, and counter-based frequency measurement approaches. The frequency detector generates control signals proportional to the frequency difference between reference and feedback signals, enabling precise frequency tracking and lock acquisition.Expand Specific Solutions03 Loop filter and control signal processing

Loop filters in frequency-locked loops process the frequency error signals to generate stable control voltages for oscillator tuning. These filters determine the dynamic response characteristics including lock time, stability margins, and noise rejection. Various filter topologies including active and passive designs are utilized to optimize loop performance for specific applications such as communication systems and clock generation circuits.Expand Specific Solutions04 Voltage-controlled oscillator integration and frequency synthesis

Voltage-controlled oscillators serve as the tunable frequency source in frequency-locked loop systems. These oscillators convert control voltages into corresponding output frequencies across specified tuning ranges. Integration techniques include LC oscillators, ring oscillators, and digitally-controlled oscillator architectures. The oscillator design impacts overall loop performance including frequency range, tuning linearity, and phase noise characteristics.Expand Specific Solutions05 Applications in communication and clock recovery systems

Frequency-locked loops find widespread application in communication systems for carrier recovery, clock synchronization, and frequency synthesis. These systems utilize FLL techniques for demodulation, timing recovery in data transmission, and local oscillator generation. Implementation approaches include both analog and digital designs optimized for wireless communications, optical networks, and high-speed data interfaces.Expand Specific Solutions

Major Players in FLL and Adaptive Signal Processing

The frequency-locked loop (FLL) technology for adaptive signal processing represents a mature yet evolving market segment within the broader semiconductor and communications infrastructure industry. The competitive landscape is characterized by established technology giants including Samsung Electronics, MediaTek, Huawei Technologies, and Texas Instruments, who dominate through comprehensive product portfolios and extensive R&D capabilities. The market demonstrates significant scale, driven by 5G infrastructure deployment and IoT applications, with companies like Ericsson, NXP Semiconductors, and Skyworks Solutions providing specialized RF and signal processing solutions. Technology maturity varies across applications, with traditional implementations well-established while adaptive and AI-enhanced variants represent emerging frontiers. Academic institutions like Zhejiang University and Southeast University contribute fundamental research, while EDA companies such as Cadence Design Systems provide essential design tools. The competitive dynamics reflect a mix of horizontal integration by major semiconductor manufacturers and vertical specialization by companies like Cirrus Logic and Infineon Technologies, indicating a healthy, innovation-driven ecosystem.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung develops FLL solutions primarily for their mobile processors and memory controllers, focusing on low-power adaptive signal processing applications. Their FLL architecture utilizes a digitally-controlled oscillator with fine-grain frequency tuning capabilities, enabling precise frequency tracking for high-speed data interfaces. Samsung's implementation features adaptive loop gain control that responds to signal strength variations and automatically adjusts acquisition and tracking modes. The company's FLL design incorporates advanced jitter reduction techniques through predictive filtering algorithms and multi-phase clock generation. Their adaptive processing engine monitors phase error statistics and implements dynamic loop parameter optimization to maintain optimal performance across process, voltage, and temperature variations in semiconductor manufacturing.

Strengths: Optimized for mobile and low-power applications, excellent integration with memory interfaces. Weaknesses: Limited frequency range compared to dedicated RF solutions, primarily focused on digital applications.

Cadence Design Systems, Inc.

Technical Solution: Cadence provides comprehensive FLL design tools and IP blocks that enable engineers to configure adaptive frequency-locked loops for various signal processing applications. Their FLL IP features parameterizable architectures with configurable loop filters, phase detectors, and oscillator models that can be optimized for specific performance requirements. Cadence's adaptive FLL framework includes built-in calibration algorithms that automatically tune loop parameters during startup and operation. The company's design methodology incorporates advanced simulation capabilities for modeling FLL behavior under different noise conditions and process variations. Their adaptive signal processing approach includes automatic gain control, bandwidth optimization, and stability analysis tools that help designers achieve optimal FLL performance while meeting power and area constraints in integrated circuit implementations.

Strengths: Comprehensive design tools and simulation capabilities, flexible IP configuration options. Weaknesses: Requires significant design expertise to optimize, primarily a tool provider rather than silicon implementer.

Core Patents in Adaptive FLL Signal Processing

Frequency-locked loop calibration of a phase-locked loop gain

PatentInactiveUS7898343B1

Innovation

- A calibrated phase-locked loop (PLL) system with a calibration mode for measuring tuning gain and a PLL mode for normal operation, using frequency-locked loop (FLL) circuit elements for coarse tuning and PLL for high frequency accuracy, reducing phase lock times by regulating loop gain and pre-charging the PLL loop filter.

Digital frequency locked loop for wideband communications channels requiring extreme doppler compensation and low signal to noise ratio

PatentWO2020018202A1

Innovation

- A Digital Frequency Locked Loop apparatus utilizing a Discrete Fourier Transform (DFT) processor for non-data-aided carrier recovery, which provides coarse frequency correction by calculating instantaneous frequency error estimates through positive and negative frequency bin outputs, and a loop filter for smoothing, enabling resilient frequency locking even under harsh conditions.

Standards and Protocols for FLL Implementation

The implementation of Frequency-Locked Loop systems for adaptive signal processing requires adherence to established standards and protocols that ensure interoperability, performance consistency, and regulatory compliance across different applications and platforms. These standardization frameworks provide essential guidelines for system designers and engineers working with FLL configurations in various domains.

IEEE standards play a fundamental role in FLL implementation, particularly IEEE 802.11 for wireless communications and IEEE 1588 for precision time protocol applications. These standards define specific requirements for frequency synchronization accuracy, loop bandwidth specifications, and phase noise characteristics that FLL systems must meet. Additionally, the IEEE 802.16 standard addresses frequency synchronization in broadband wireless access systems, establishing protocols for initial frequency acquisition and tracking procedures.

International Telecommunication Union recommendations, specifically ITU-R F.1191 and ITU-T G.8262, provide comprehensive guidelines for frequency stability requirements in telecommunications infrastructure. These protocols specify Allan deviation limits, frequency accuracy tolerances, and holdover performance criteria that directly impact FLL design parameters. The standards also define test methodologies for validating FLL performance under various operating conditions.

3GPP specifications establish critical protocols for FLL implementation in cellular networks, including LTE and 5G systems. Release 15 and subsequent versions define frequency synchronization requirements for base stations and user equipment, specifying maximum frequency error limits and acquisition time constraints. These protocols ensure seamless handover procedures and maintain network stability during dynamic channel conditions.

Military and aerospace applications follow MIL-STD-188 series standards, which define stringent requirements for frequency stability and electromagnetic compatibility. These protocols address FLL performance in harsh environments, including temperature variations, vibration resistance, and jamming resilience. The standards specify frequency accuracy requirements ranging from parts per million to parts per billion, depending on mission-critical applications.

Industrial automation systems rely on IEC 61850 and IEC 62439 standards for time-sensitive networking applications. These protocols define synchronization accuracy requirements for power grid monitoring and control systems, where FLL implementations must maintain microsecond-level precision. The standards also address cybersecurity considerations and fault tolerance mechanisms essential for critical infrastructure applications.

Emerging protocols for Internet of Things and edge computing applications are being developed through organizations like the Industrial Internet Consortium and OpenFog Consortium. These frameworks address FLL implementation challenges in distributed systems with varying computational resources and network connectivity constraints, establishing adaptive synchronization protocols that can dynamically adjust loop parameters based on network conditions and application requirements.

IEEE standards play a fundamental role in FLL implementation, particularly IEEE 802.11 for wireless communications and IEEE 1588 for precision time protocol applications. These standards define specific requirements for frequency synchronization accuracy, loop bandwidth specifications, and phase noise characteristics that FLL systems must meet. Additionally, the IEEE 802.16 standard addresses frequency synchronization in broadband wireless access systems, establishing protocols for initial frequency acquisition and tracking procedures.

International Telecommunication Union recommendations, specifically ITU-R F.1191 and ITU-T G.8262, provide comprehensive guidelines for frequency stability requirements in telecommunications infrastructure. These protocols specify Allan deviation limits, frequency accuracy tolerances, and holdover performance criteria that directly impact FLL design parameters. The standards also define test methodologies for validating FLL performance under various operating conditions.

3GPP specifications establish critical protocols for FLL implementation in cellular networks, including LTE and 5G systems. Release 15 and subsequent versions define frequency synchronization requirements for base stations and user equipment, specifying maximum frequency error limits and acquisition time constraints. These protocols ensure seamless handover procedures and maintain network stability during dynamic channel conditions.

Military and aerospace applications follow MIL-STD-188 series standards, which define stringent requirements for frequency stability and electromagnetic compatibility. These protocols address FLL performance in harsh environments, including temperature variations, vibration resistance, and jamming resilience. The standards specify frequency accuracy requirements ranging from parts per million to parts per billion, depending on mission-critical applications.

Industrial automation systems rely on IEC 61850 and IEC 62439 standards for time-sensitive networking applications. These protocols define synchronization accuracy requirements for power grid monitoring and control systems, where FLL implementations must maintain microsecond-level precision. The standards also address cybersecurity considerations and fault tolerance mechanisms essential for critical infrastructure applications.

Emerging protocols for Internet of Things and edge computing applications are being developed through organizations like the Industrial Internet Consortium and OpenFog Consortium. These frameworks address FLL implementation challenges in distributed systems with varying computational resources and network connectivity constraints, establishing adaptive synchronization protocols that can dynamically adjust loop parameters based on network conditions and application requirements.

Performance Optimization Strategies for Adaptive FLL

Adaptive Frequency-Locked Loop (FLL) systems require sophisticated optimization strategies to maintain peak performance across varying signal conditions and operational environments. The optimization process encompasses multiple dimensions, including parameter tuning, algorithmic enhancements, and hardware-software co-design approaches that collectively determine system effectiveness.

Loop bandwidth optimization represents a fundamental strategy for adaptive FLL performance enhancement. Dynamic bandwidth adjustment algorithms enable the system to respond appropriately to different signal-to-noise ratios and Doppler shift scenarios. Narrow bandwidth configurations provide superior noise rejection capabilities during stable signal conditions, while wider bandwidths facilitate rapid acquisition and tracking of highly dynamic signals. Advanced implementations employ adaptive bandwidth control mechanisms that continuously monitor signal quality metrics and adjust loop parameters in real-time.

Discriminator optimization techniques significantly impact FLL tracking accuracy and stability. Modern adaptive systems utilize multiple discriminator architectures, including cross-product, arctangent, and extended range discriminators, each optimized for specific operational scenarios. Performance enhancement strategies involve discriminator switching algorithms that select the most appropriate discriminator type based on current signal characteristics and tracking requirements.

Filter design optimization plays a crucial role in achieving optimal noise suppression while maintaining tracking responsiveness. Advanced filter architectures incorporate Kalman filtering techniques, enabling optimal state estimation under varying noise conditions. Multi-stage filtering approaches combine different filter types to achieve superior performance across diverse operational scenarios, with adaptive filter coefficient adjustment based on real-time signal assessment.

Convergence acceleration strategies address the critical requirement for rapid signal acquisition in adaptive FLL systems. These techniques include intelligent initialization algorithms that leverage prior signal knowledge, multi-hypothesis tracking approaches for ambiguous signal scenarios, and parallel processing architectures that simultaneously evaluate multiple frequency hypotheses. Advanced implementations incorporate machine learning algorithms to predict optimal initialization parameters based on historical performance data.

Robustness enhancement strategies ensure consistent performance under adverse conditions, including multipath interference, jamming scenarios, and extreme Doppler environments. These approaches involve adaptive threshold management, outlier detection algorithms, and graceful degradation mechanisms that maintain basic functionality even under severe signal impairment conditions.

Loop bandwidth optimization represents a fundamental strategy for adaptive FLL performance enhancement. Dynamic bandwidth adjustment algorithms enable the system to respond appropriately to different signal-to-noise ratios and Doppler shift scenarios. Narrow bandwidth configurations provide superior noise rejection capabilities during stable signal conditions, while wider bandwidths facilitate rapid acquisition and tracking of highly dynamic signals. Advanced implementations employ adaptive bandwidth control mechanisms that continuously monitor signal quality metrics and adjust loop parameters in real-time.

Discriminator optimization techniques significantly impact FLL tracking accuracy and stability. Modern adaptive systems utilize multiple discriminator architectures, including cross-product, arctangent, and extended range discriminators, each optimized for specific operational scenarios. Performance enhancement strategies involve discriminator switching algorithms that select the most appropriate discriminator type based on current signal characteristics and tracking requirements.

Filter design optimization plays a crucial role in achieving optimal noise suppression while maintaining tracking responsiveness. Advanced filter architectures incorporate Kalman filtering techniques, enabling optimal state estimation under varying noise conditions. Multi-stage filtering approaches combine different filter types to achieve superior performance across diverse operational scenarios, with adaptive filter coefficient adjustment based on real-time signal assessment.

Convergence acceleration strategies address the critical requirement for rapid signal acquisition in adaptive FLL systems. These techniques include intelligent initialization algorithms that leverage prior signal knowledge, multi-hypothesis tracking approaches for ambiguous signal scenarios, and parallel processing architectures that simultaneously evaluate multiple frequency hypotheses. Advanced implementations incorporate machine learning algorithms to predict optimal initialization parameters based on historical performance data.

Robustness enhancement strategies ensure consistent performance under adverse conditions, including multipath interference, jamming scenarios, and extreme Doppler environments. These approaches involve adaptive threshold management, outlier detection algorithms, and graceful degradation mechanisms that maintain basic functionality even under severe signal impairment conditions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!