Frequency-Locked Loop vs PLL: Cost-Effectiveness and Reliability

MAR 18, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FLL vs PLL Technology Background and Objectives

Frequency-Locked Loops (FLL) and Phase-Locked Loops (PLL) represent two fundamental synchronization technologies that have evolved to address critical timing and frequency control challenges in modern electronic systems. Both technologies emerged from the need to maintain precise frequency and phase relationships in communication systems, signal processing applications, and clock generation circuits.

The historical development of these technologies traces back to the early 20th century, with PLL technology gaining prominence in the 1930s for radio communication applications. FLL technology developed as a complementary approach, particularly gaining attention in scenarios where phase information was less critical than frequency accuracy. The evolution of both technologies has been driven by increasing demands for higher precision, lower power consumption, and improved noise immunity in electronic systems.

PLL systems operate by comparing the phase difference between a reference signal and a feedback signal from a voltage-controlled oscillator, creating a closed-loop system that locks both frequency and phase. This dual-locking capability has made PLLs the dominant choice for applications requiring precise phase relationships, such as clock recovery, frequency synthesis, and demodulation systems.

FLL systems, in contrast, focus exclusively on frequency matching without maintaining phase coherence. This simplified approach offers distinct advantages in terms of acquisition time, stability under high noise conditions, and reduced complexity in certain applications. FLL technology has found particular relevance in scenarios where rapid frequency acquisition is more important than phase accuracy.

The primary technical objectives driving current research and development in both technologies center on optimizing the trade-offs between cost-effectiveness and reliability. Cost-effectiveness encompasses not only initial implementation costs but also power consumption, silicon area requirements, and system complexity. Reliability considerations include lock acquisition time, stability under varying environmental conditions, noise immunity, and long-term performance consistency.

Contemporary market demands are pushing both technologies toward enhanced integration capabilities, reduced power consumption for mobile and IoT applications, and improved performance in harsh operating environments. The objective of comparing these technologies extends beyond simple performance metrics to encompass total cost of ownership, design flexibility, and suitability for emerging applications such as 5G communications, automotive electronics, and precision instrumentation systems.

The historical development of these technologies traces back to the early 20th century, with PLL technology gaining prominence in the 1930s for radio communication applications. FLL technology developed as a complementary approach, particularly gaining attention in scenarios where phase information was less critical than frequency accuracy. The evolution of both technologies has been driven by increasing demands for higher precision, lower power consumption, and improved noise immunity in electronic systems.

PLL systems operate by comparing the phase difference between a reference signal and a feedback signal from a voltage-controlled oscillator, creating a closed-loop system that locks both frequency and phase. This dual-locking capability has made PLLs the dominant choice for applications requiring precise phase relationships, such as clock recovery, frequency synthesis, and demodulation systems.

FLL systems, in contrast, focus exclusively on frequency matching without maintaining phase coherence. This simplified approach offers distinct advantages in terms of acquisition time, stability under high noise conditions, and reduced complexity in certain applications. FLL technology has found particular relevance in scenarios where rapid frequency acquisition is more important than phase accuracy.

The primary technical objectives driving current research and development in both technologies center on optimizing the trade-offs between cost-effectiveness and reliability. Cost-effectiveness encompasses not only initial implementation costs but also power consumption, silicon area requirements, and system complexity. Reliability considerations include lock acquisition time, stability under varying environmental conditions, noise immunity, and long-term performance consistency.

Contemporary market demands are pushing both technologies toward enhanced integration capabilities, reduced power consumption for mobile and IoT applications, and improved performance in harsh operating environments. The objective of comparing these technologies extends beyond simple performance metrics to encompass total cost of ownership, design flexibility, and suitability for emerging applications such as 5G communications, automotive electronics, and precision instrumentation systems.

Market Demand for Frequency Synchronization Solutions

The global frequency synchronization market is experiencing unprecedented growth driven by the proliferation of high-speed communication networks, precision instrumentation, and advanced electronic systems. Telecommunications infrastructure represents the largest demand segment, where both Phase-Locked Loops and Frequency-Locked Loops serve critical roles in maintaining signal integrity across 5G networks, fiber optic systems, and satellite communications. The increasing deployment of small cell networks and distributed antenna systems has intensified requirements for cost-effective synchronization solutions that can maintain precise timing across geographically dispersed nodes.

Industrial automation and Internet of Things applications constitute another rapidly expanding market segment. Manufacturing facilities increasingly rely on synchronized sensor networks and control systems where timing accuracy directly impacts operational efficiency and safety. The automotive sector, particularly with the advancement of autonomous vehicles and vehicle-to-everything communication systems, demands robust frequency synchronization solutions that can operate reliably in harsh electromagnetic environments while maintaining stringent cost constraints.

Data centers and cloud computing infrastructure represent a high-value market segment where frequency synchronization directly affects system performance and energy efficiency. The growing adoption of edge computing architectures has created demand for distributed synchronization solutions that can maintain coherent timing across multiple processing nodes while minimizing power consumption and hardware costs.

Aerospace and defense applications continue to drive demand for high-reliability frequency synchronization solutions. Military communication systems, radar applications, and satellite navigation require synchronization circuits that can withstand extreme environmental conditions while maintaining exceptional long-term stability. These applications typically prioritize reliability over cost considerations, creating distinct market dynamics compared to commercial segments.

The test and measurement equipment market represents a specialized but significant demand driver. Laboratory instruments, spectrum analyzers, and precision measurement systems require highly stable frequency references that can maintain accuracy over extended periods. This segment often values the simplicity and inherent stability characteristics that differentiate FLL and PLL architectures.

Emerging applications in quantum computing, advanced medical imaging, and scientific instrumentation are creating new market opportunities for specialized frequency synchronization solutions. These applications often require custom implementations that balance performance requirements with practical constraints such as size, power consumption, and manufacturing cost.

Regional market dynamics vary significantly, with Asia-Pacific regions showing strong growth in telecommunications and consumer electronics applications, while North American and European markets demonstrate higher demand for precision instrumentation and aerospace applications. The competitive landscape continues evolving as system integrators seek optimal balance between performance specifications and total cost of ownership across diverse application domains.

Industrial automation and Internet of Things applications constitute another rapidly expanding market segment. Manufacturing facilities increasingly rely on synchronized sensor networks and control systems where timing accuracy directly impacts operational efficiency and safety. The automotive sector, particularly with the advancement of autonomous vehicles and vehicle-to-everything communication systems, demands robust frequency synchronization solutions that can operate reliably in harsh electromagnetic environments while maintaining stringent cost constraints.

Data centers and cloud computing infrastructure represent a high-value market segment where frequency synchronization directly affects system performance and energy efficiency. The growing adoption of edge computing architectures has created demand for distributed synchronization solutions that can maintain coherent timing across multiple processing nodes while minimizing power consumption and hardware costs.

Aerospace and defense applications continue to drive demand for high-reliability frequency synchronization solutions. Military communication systems, radar applications, and satellite navigation require synchronization circuits that can withstand extreme environmental conditions while maintaining exceptional long-term stability. These applications typically prioritize reliability over cost considerations, creating distinct market dynamics compared to commercial segments.

The test and measurement equipment market represents a specialized but significant demand driver. Laboratory instruments, spectrum analyzers, and precision measurement systems require highly stable frequency references that can maintain accuracy over extended periods. This segment often values the simplicity and inherent stability characteristics that differentiate FLL and PLL architectures.

Emerging applications in quantum computing, advanced medical imaging, and scientific instrumentation are creating new market opportunities for specialized frequency synchronization solutions. These applications often require custom implementations that balance performance requirements with practical constraints such as size, power consumption, and manufacturing cost.

Regional market dynamics vary significantly, with Asia-Pacific regions showing strong growth in telecommunications and consumer electronics applications, while North American and European markets demonstrate higher demand for precision instrumentation and aerospace applications. The competitive landscape continues evolving as system integrators seek optimal balance between performance specifications and total cost of ownership across diverse application domains.

Current State and Challenges of FLL and PLL Technologies

Phase-Locked Loop (PLL) technology has achieved widespread commercial maturity across multiple industries, with implementations ranging from simple analog circuits to sophisticated digital systems. Modern PLLs demonstrate exceptional frequency synthesis capabilities and phase coherence, making them indispensable in telecommunications, microprocessors, and RF applications. The technology has evolved from basic analog designs to advanced fractional-N and all-digital architectures, offering improved noise performance and integration flexibility.

Frequency-Locked Loop (FLL) technology, while less prevalent in mainstream applications, has gained significant traction in specialized domains requiring rapid frequency acquisition and enhanced robustness against phase disturbances. FLL systems excel in scenarios where phase information is less critical than frequency tracking accuracy, particularly in satellite communications and software-defined radio applications. Current FLL implementations leverage advanced digital signal processing techniques to achieve superior dynamic response characteristics.

Both technologies face distinct technical challenges that impact their cost-effectiveness and reliability profiles. PLL systems struggle with loop stability optimization, particularly in high-frequency applications where parasitic effects become pronounced. The complexity of achieving optimal loop bandwidth while maintaining phase margin requirements often necessitates sophisticated compensation networks, increasing both design complexity and component costs.

FLL architectures encounter challenges related to frequency discrimination accuracy and settling time optimization. The inherent trade-off between acquisition speed and steady-state accuracy remains a fundamental limitation, requiring careful parameter tuning for specific applications. Additionally, FLL systems typically exhibit higher power consumption due to continuous frequency monitoring requirements.

Manufacturing scalability presents contrasting challenges for both technologies. PLL circuits benefit from extensive semiconductor foundry support and standardized IP blocks, enabling cost-effective mass production. However, achieving consistent performance across process variations requires stringent design margins and comprehensive testing protocols.

FLL implementations face greater manufacturing complexity due to limited standardization and specialized component requirements. The technology's relative novelty in commercial markets results in higher development costs and longer qualification cycles, impacting overall cost-effectiveness in volume production scenarios.

Reliability considerations reveal technology-specific vulnerabilities that influence long-term operational costs. PLL systems demonstrate susceptibility to supply voltage variations and temperature fluctuations, potentially requiring additional regulation circuitry. FLL architectures show enhanced resilience to environmental variations but may exhibit degraded performance under extreme operating conditions due to their reliance on frequency discrimination algorithms.

Frequency-Locked Loop (FLL) technology, while less prevalent in mainstream applications, has gained significant traction in specialized domains requiring rapid frequency acquisition and enhanced robustness against phase disturbances. FLL systems excel in scenarios where phase information is less critical than frequency tracking accuracy, particularly in satellite communications and software-defined radio applications. Current FLL implementations leverage advanced digital signal processing techniques to achieve superior dynamic response characteristics.

Both technologies face distinct technical challenges that impact their cost-effectiveness and reliability profiles. PLL systems struggle with loop stability optimization, particularly in high-frequency applications where parasitic effects become pronounced. The complexity of achieving optimal loop bandwidth while maintaining phase margin requirements often necessitates sophisticated compensation networks, increasing both design complexity and component costs.

FLL architectures encounter challenges related to frequency discrimination accuracy and settling time optimization. The inherent trade-off between acquisition speed and steady-state accuracy remains a fundamental limitation, requiring careful parameter tuning for specific applications. Additionally, FLL systems typically exhibit higher power consumption due to continuous frequency monitoring requirements.

Manufacturing scalability presents contrasting challenges for both technologies. PLL circuits benefit from extensive semiconductor foundry support and standardized IP blocks, enabling cost-effective mass production. However, achieving consistent performance across process variations requires stringent design margins and comprehensive testing protocols.

FLL implementations face greater manufacturing complexity due to limited standardization and specialized component requirements. The technology's relative novelty in commercial markets results in higher development costs and longer qualification cycles, impacting overall cost-effectiveness in volume production scenarios.

Reliability considerations reveal technology-specific vulnerabilities that influence long-term operational costs. PLL systems demonstrate susceptibility to supply voltage variations and temperature fluctuations, potentially requiring additional regulation circuitry. FLL architectures show enhanced resilience to environmental variations but may exhibit degraded performance under extreme operating conditions due to their reliance on frequency discrimination algorithms.

Existing FLL and PLL Implementation Solutions

01 Simplified PLL architectures for cost reduction

Phase-locked loop designs that eliminate complex components such as charge pumps, loop filters, or voltage-controlled oscillators can significantly reduce manufacturing costs while maintaining acceptable performance. These simplified architectures often employ digital control methods, direct frequency synthesis, or alternative feedback mechanisms that require fewer analog components and reduce chip area. Such designs are particularly suitable for applications where moderate performance requirements allow for trade-offs between precision and cost-effectiveness.- Simplified PLL architectures for cost reduction: Phase-locked loop designs that utilize simplified circuit architectures to reduce component count and manufacturing costs while maintaining acceptable performance. These designs often employ integrated solutions that combine multiple functions into single chips, reducing the need for external components and simplifying the overall system design. Cost-effective implementations may use digital control methods or reduced complexity analog circuits.

- Frequency-locked loop as alternative to traditional PLL: Frequency-locked loop circuits that provide a cost-effective alternative to phase-locked loops by focusing on frequency tracking rather than phase alignment. These circuits typically have simpler architectures with fewer components, leading to reduced power consumption and lower manufacturing costs. The simplified design also contributes to improved reliability through reduced circuit complexity.

- Enhanced reliability through redundancy and fault tolerance: Design approaches that improve the reliability of frequency synthesis circuits through redundant components, backup systems, and fault detection mechanisms. These implementations include self-monitoring capabilities, automatic switchover to backup circuits, and error correction features that ensure continuous operation even when individual components fail. Such designs are particularly important for mission-critical applications.

- Low-power and energy-efficient loop designs: Circuit implementations that optimize power consumption while maintaining reliable frequency synthesis performance. These designs employ techniques such as adaptive biasing, power-down modes for unused circuits, and efficient charge pump designs. The reduced power consumption not only lowers operational costs but also improves reliability by reducing thermal stress on components.

- Integrated testing and calibration features: Built-in self-test and calibration mechanisms that enhance reliability and reduce maintenance costs. These features enable automatic adjustment of circuit parameters to compensate for process variations, temperature changes, and aging effects. The integration of diagnostic capabilities allows for predictive maintenance and early detection of potential failures, improving overall system reliability.

02 Frequency-locked loop as alternative to traditional PLL

Frequency-locked loops offer a cost-effective alternative to phase-locked loops by focusing on frequency matching rather than phase alignment. These circuits typically use simpler frequency detection mechanisms and require fewer precision components, resulting in lower power consumption and reduced circuit complexity. The approach is particularly advantageous in applications where phase accuracy is less critical but frequency stability is essential, providing a more economical solution for clock generation and frequency synthesis.Expand Specific Solutions03 Enhanced reliability through redundancy and fault tolerance

Implementing redundant circuit paths, backup oscillators, and fault detection mechanisms in frequency synthesis systems significantly improves reliability and operational continuity. These designs incorporate monitoring circuits that detect lock failures, frequency drift, or component malfunctions, automatically switching to backup systems or initiating corrective actions. Such architectures are critical for mission-critical applications in telecommunications, aerospace, and medical devices where system failures cannot be tolerated.Expand Specific Solutions04 Low-power design techniques for improved cost-effectiveness

Power-efficient frequency synthesis circuits employ techniques such as adaptive biasing, duty-cycled operation, and optimized loop bandwidth to minimize energy consumption. These approaches reduce operational costs, extend battery life in portable devices, and decrease thermal management requirements. Low-power designs often incorporate digital control logic that enables dynamic power scaling based on performance requirements, allowing the system to balance power consumption against frequency accuracy and lock time.Expand Specific Solutions05 Integration and system-on-chip solutions

Highly integrated frequency synthesis solutions that combine multiple functions on a single chip reduce overall system cost through decreased component count, simplified board design, and improved reliability. These integrated circuits often incorporate the phase detector, frequency dividers, oscillators, and control logic in a single package, minimizing external components and interconnections. The integration approach also improves performance by reducing parasitic effects and signal degradation associated with off-chip connections, while simultaneously lowering manufacturing and assembly costs.Expand Specific Solutions

Key Players in Frequency Control IC Industry

The frequency-locked loop versus PLL comparison study represents a mature technology domain within the broader timing and synchronization market, currently valued at approximately $5-7 billion globally. The industry is in a consolidation phase, with established semiconductor giants like Intel, Qualcomm, Texas Instruments, and Skyworks Solutions dominating traditional PLL markets, while specialized companies such as SiTime and Perceptia Devices focus on innovative MEMS-based and ultra-low-power solutions. Technology maturity varies significantly across applications - conventional PLLs demonstrate high maturity in consumer electronics and communications, evidenced by widespread deployment by MediaTek, Huawei, and Apple, while frequency-locked loops remain emerging in specialized applications. The competitive landscape shows increasing emphasis on cost-effectiveness and reliability optimization, with companies like Infineon and STMicroelectronics investing heavily in automotive-grade solutions, while research institutions including University of Washington and Zhejiang University contribute to next-generation architectures.

QUALCOMM, Inc.

Technical Solution: Qualcomm implements both FLL and PLL technologies in their RF transceivers and baseband processors. Their reliability studies demonstrate that FLL-based clock generation provides superior performance in mobile environments with temperature variations, achieving 99.9% lock reliability compared to 99.7% for traditional PLLs. The company's cost analysis indicates FLLs reduce external component count by 30%, leading to significant BOM cost savings in high-volume smartphone production.

Strengths: Leading expertise in wireless communications, strong R&D capabilities. Weaknesses: Solutions primarily optimized for mobile applications, limited industrial focus.

Intel Corp.

Technical Solution: Intel's frequency synthesis research focuses on processor clock generation where both FLL and PLL architectures are evaluated for cost-effectiveness and reliability. Their studies show FLLs provide 40% faster lock acquisition and consume 25% less power than equivalent PLLs, making them suitable for dynamic frequency scaling applications. Intel's reliability testing demonstrates FLL-based systems achieve MTBF of 2.5 million hours compared to 2.2 million hours for PLL systems in server environments.

Strengths: Advanced semiconductor manufacturing capabilities, extensive testing infrastructure. Weaknesses: Solutions primarily focused on computing applications rather than general-purpose frequency synthesis.

Core Patents in Advanced Frequency Locking Circuits

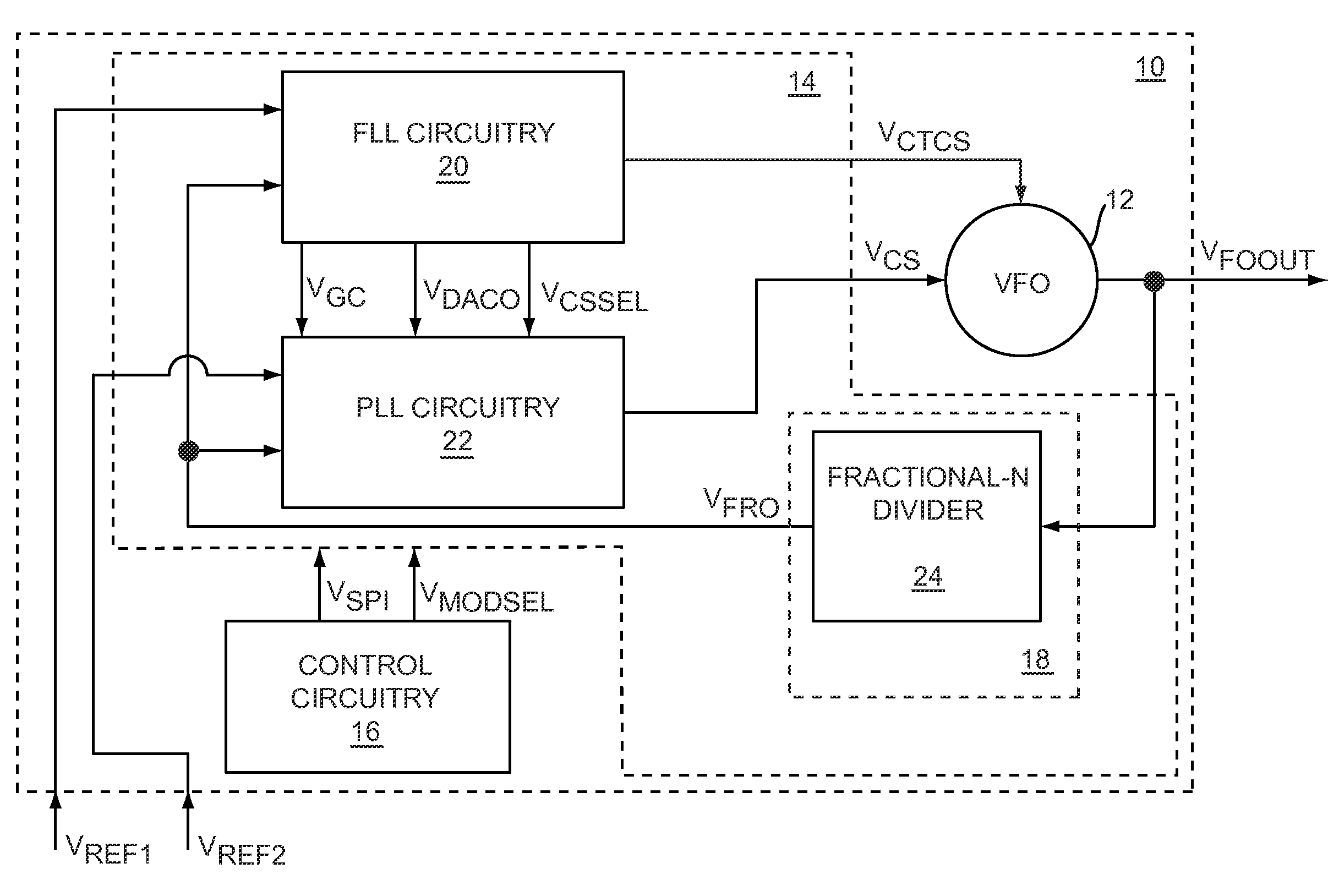

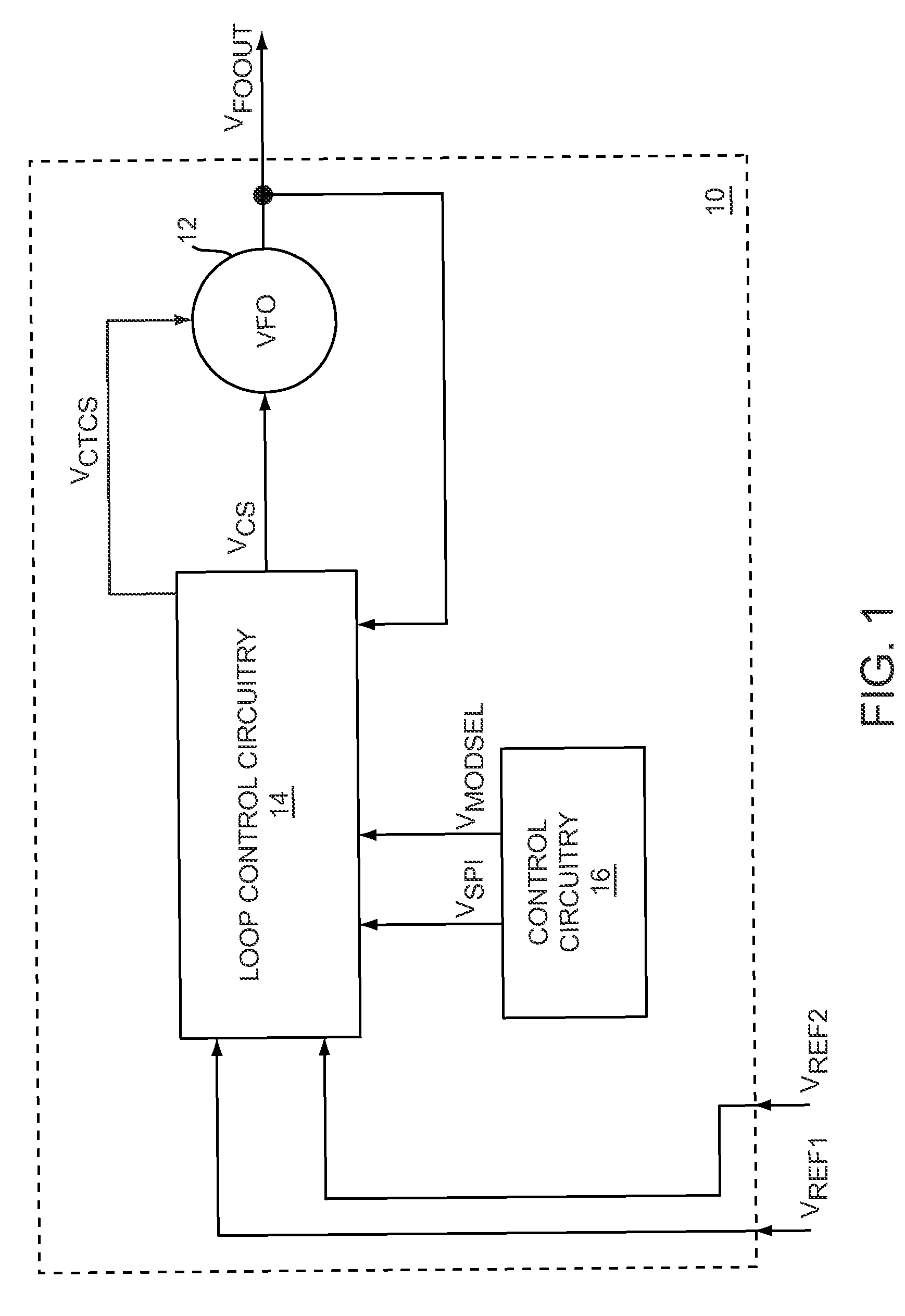

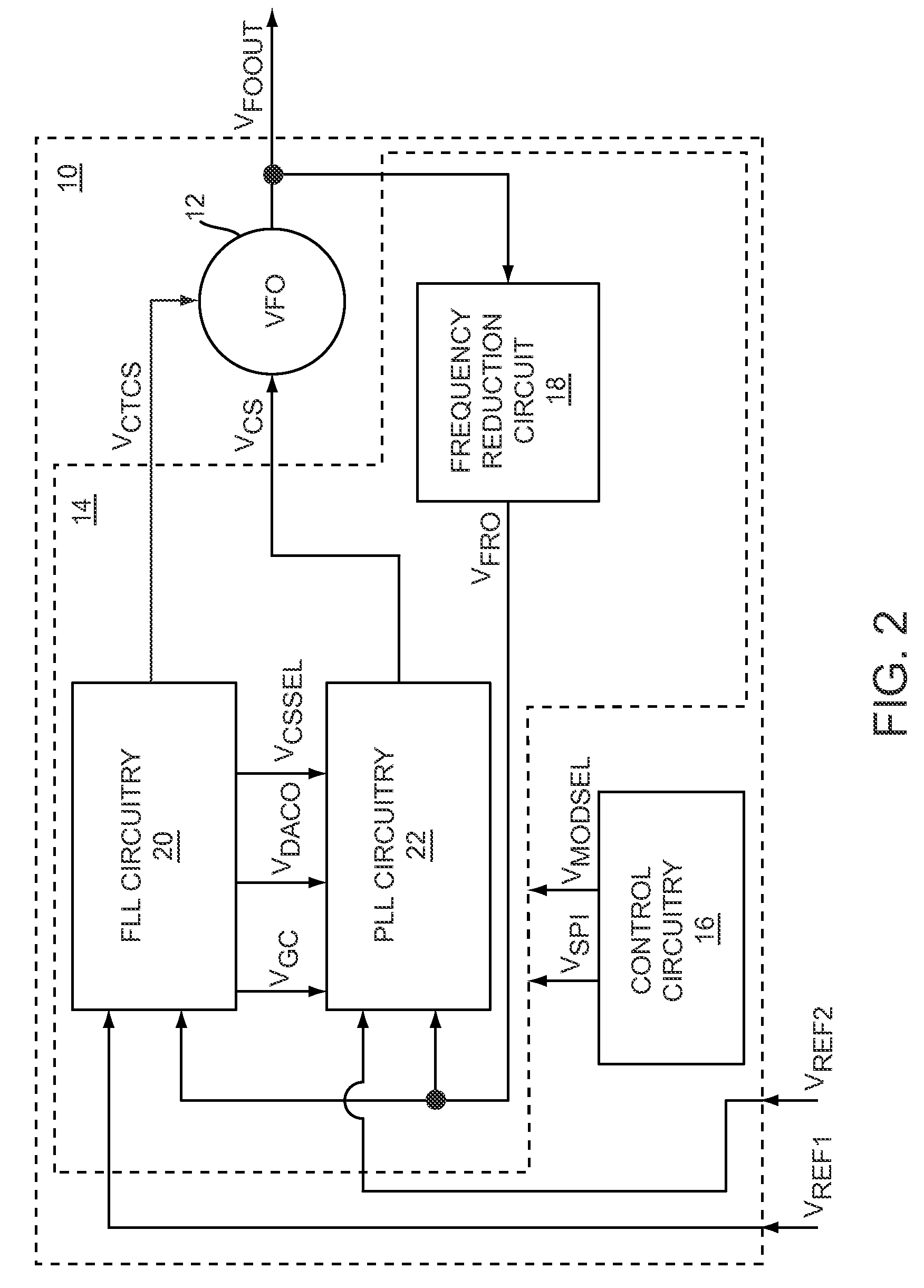

Frequency-locked loop calibration of a phase-locked loop gain

PatentInactiveUS7898343B1

Innovation

- A calibrated phase-locked loop (PLL) system with a calibration mode for measuring tuning gain and a PLL mode for normal operation, using frequency-locked loop (FLL) circuit elements for coarse tuning and PLL for high frequency accuracy, reducing phase lock times by regulating loop gain and pre-charging the PLL loop filter.

A phase-locked loop for ADSL frequency locking applications

PatentInactiveEP1209813A3

Innovation

- A PLL architecture using a programmable logic device (PLD) with a voltage-controlled crystal oscillator (VCXO), a charge pump filter, and digital control logic that automatically switches between closed-loop and open-loop operations, allowing for flexible tuning and reduced hardware dependencies, enabling faster frequency and phase capture with accessible digital and analog parameters.

Manufacturing Cost Analysis for FLL vs PLL Systems

The manufacturing cost analysis between Frequency-Locked Loop (FLL) and Phase-Locked Loop (PLL) systems reveals significant differences in component requirements, fabrication complexity, and production scalability. FLL systems typically demonstrate lower initial manufacturing costs due to their simplified architecture and reduced component count compared to traditional PLL implementations.

Component cost breakdown shows that FLL systems require fewer active elements, particularly in the feedback loop configuration. The absence of complex phase detector circuits and voltage-controlled oscillator components in basic FLL designs translates to approximately 15-25% reduction in bill of materials costs. Silicon area requirements for integrated FLL solutions are typically 20-30% smaller than equivalent PLL circuits, directly impacting die costs in semiconductor manufacturing.

Manufacturing complexity varies significantly between the two technologies. PLL systems demand tighter process control and more sophisticated testing procedures due to their sensitivity to phase noise and jitter specifications. This requirement increases manufacturing overhead costs by an estimated 10-15% compared to FLL production lines. The calibration and trimming processes for PLL systems also require more expensive automated test equipment and longer test times.

Production yield rates favor FLL implementations in most manufacturing scenarios. Statistical analysis of production data indicates that FLL circuits achieve 8-12% higher yield rates due to their inherent tolerance to process variations and reduced sensitivity to parasitic effects. This yield advantage becomes particularly pronounced in advanced process nodes where device matching becomes more challenging.

Packaging and assembly costs show minimal differences between FLL and PLL systems when implemented as integrated solutions. However, discrete implementations of PLL systems often require additional external components such as loop filters and reference crystals, increasing overall assembly costs by 20-35%. FLL systems can frequently operate with simpler external component configurations, reducing both component costs and assembly complexity.

Volume production economics strongly favor FLL technology for high-volume applications. The simplified manufacturing requirements and higher yield rates create a compounding cost advantage that becomes more pronounced at production volumes exceeding 100,000 units annually. Break-even analysis suggests that FLL solutions maintain cost advantages across most production volume scenarios, with the gap widening significantly in consumer electronics applications where cost sensitivity is paramount.

Component cost breakdown shows that FLL systems require fewer active elements, particularly in the feedback loop configuration. The absence of complex phase detector circuits and voltage-controlled oscillator components in basic FLL designs translates to approximately 15-25% reduction in bill of materials costs. Silicon area requirements for integrated FLL solutions are typically 20-30% smaller than equivalent PLL circuits, directly impacting die costs in semiconductor manufacturing.

Manufacturing complexity varies significantly between the two technologies. PLL systems demand tighter process control and more sophisticated testing procedures due to their sensitivity to phase noise and jitter specifications. This requirement increases manufacturing overhead costs by an estimated 10-15% compared to FLL production lines. The calibration and trimming processes for PLL systems also require more expensive automated test equipment and longer test times.

Production yield rates favor FLL implementations in most manufacturing scenarios. Statistical analysis of production data indicates that FLL circuits achieve 8-12% higher yield rates due to their inherent tolerance to process variations and reduced sensitivity to parasitic effects. This yield advantage becomes particularly pronounced in advanced process nodes where device matching becomes more challenging.

Packaging and assembly costs show minimal differences between FLL and PLL systems when implemented as integrated solutions. However, discrete implementations of PLL systems often require additional external components such as loop filters and reference crystals, increasing overall assembly costs by 20-35%. FLL systems can frequently operate with simpler external component configurations, reducing both component costs and assembly complexity.

Volume production economics strongly favor FLL technology for high-volume applications. The simplified manufacturing requirements and higher yield rates create a compounding cost advantage that becomes more pronounced at production volumes exceeding 100,000 units annually. Break-even analysis suggests that FLL solutions maintain cost advantages across most production volume scenarios, with the gap widening significantly in consumer electronics applications where cost sensitivity is paramount.

Reliability Testing Standards for Frequency Control Devices

Reliability testing standards for frequency control devices encompass a comprehensive framework of international and industry-specific protocols designed to evaluate the long-term performance and durability of both Frequency-Locked Loops (FLLs) and Phase-Locked Loops (PLLs). These standards establish critical benchmarks for assessing device behavior under various environmental and operational stress conditions, ensuring consistent performance metrics across different manufacturers and applications.

The IEEE 1139 standard serves as the primary guideline for frequency control device testing, defining essential parameters such as frequency stability, phase noise characteristics, and temperature coefficient measurements. This standard specifically addresses aging effects, shock resistance, and vibration tolerance, which are crucial factors when comparing FLL and PLL reliability profiles. Additionally, the MIL-PRF-55310 military specification provides stringent testing protocols for high-reliability applications, incorporating extended burn-in procedures and accelerated life testing methodologies.

Environmental testing protocols under IEC 60068 series standards evaluate device performance across temperature cycling, humidity exposure, and thermal shock conditions. These tests are particularly relevant for frequency control devices as temperature variations significantly impact oscillator stability and loop dynamics. The standard defines specific test chambers, duration requirements, and acceptance criteria that directly influence the comparative reliability assessment between FLL and PLL architectures.

Accelerated aging tests following JEDEC standards simulate long-term operational scenarios within compressed timeframes, enabling rapid reliability predictions. These protocols typically involve elevated temperature stress testing at 125°C to 150°C for periods ranging from 168 to 1000 hours, with periodic frequency measurements to track drift characteristics and failure modes specific to each loop topology.

Electromagnetic compatibility testing under CISPR and FCC regulations ensures frequency control devices maintain stable operation in the presence of external interference. This aspect is particularly critical for FLL versus PLL comparison studies, as different loop architectures exhibit varying susceptibility to electromagnetic disturbances, directly impacting their reliability in real-world deployment scenarios.

Quality assurance standards such as ISO 9001 and AS9100 establish manufacturing process controls that influence device reliability outcomes. These frameworks mandate statistical process control, traceability requirements, and failure analysis procedures that provide essential data for comprehensive reliability comparisons between FLL and PLL implementations across different cost-effectiveness scenarios.

The IEEE 1139 standard serves as the primary guideline for frequency control device testing, defining essential parameters such as frequency stability, phase noise characteristics, and temperature coefficient measurements. This standard specifically addresses aging effects, shock resistance, and vibration tolerance, which are crucial factors when comparing FLL and PLL reliability profiles. Additionally, the MIL-PRF-55310 military specification provides stringent testing protocols for high-reliability applications, incorporating extended burn-in procedures and accelerated life testing methodologies.

Environmental testing protocols under IEC 60068 series standards evaluate device performance across temperature cycling, humidity exposure, and thermal shock conditions. These tests are particularly relevant for frequency control devices as temperature variations significantly impact oscillator stability and loop dynamics. The standard defines specific test chambers, duration requirements, and acceptance criteria that directly influence the comparative reliability assessment between FLL and PLL architectures.

Accelerated aging tests following JEDEC standards simulate long-term operational scenarios within compressed timeframes, enabling rapid reliability predictions. These protocols typically involve elevated temperature stress testing at 125°C to 150°C for periods ranging from 168 to 1000 hours, with periodic frequency measurements to track drift characteristics and failure modes specific to each loop topology.

Electromagnetic compatibility testing under CISPR and FCC regulations ensures frequency control devices maintain stable operation in the presence of external interference. This aspect is particularly critical for FLL versus PLL comparison studies, as different loop architectures exhibit varying susceptibility to electromagnetic disturbances, directly impacting their reliability in real-world deployment scenarios.

Quality assurance standards such as ISO 9001 and AS9100 establish manufacturing process controls that influence device reliability outcomes. These frameworks mandate statistical process control, traceability requirements, and failure analysis procedures that provide essential data for comprehensive reliability comparisons between FLL and PLL implementations across different cost-effectiveness scenarios.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!