How to Implement Frequency-Locked Loop for Low-Power Consumption

MAR 18, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

FLL Technology Background and Low-Power Objectives

Frequency-Locked Loop (FLL) technology emerged as a critical timing and synchronization solution in the 1960s, initially developed for telecommunications and radar systems. Unlike Phase-Locked Loops (PLLs), FLLs focus exclusively on frequency tracking rather than phase alignment, making them inherently more stable in noisy environments and requiring less complex control mechanisms. This fundamental difference has positioned FLLs as an attractive alternative for applications where power efficiency takes precedence over phase precision.

The evolution of FLL technology has been closely intertwined with the advancement of low-power electronics. Early implementations relied on analog circuits with high power consumption, limiting their application in portable devices. The transition to digital and mixed-signal architectures in the 1990s marked a significant milestone, enabling more sophisticated control algorithms while reducing overall power requirements. Modern FLL implementations leverage advanced semiconductor processes and innovative circuit topologies to achieve sub-milliwatt operation.

Contemporary FLL systems address the growing demand for energy-efficient frequency synthesis in Internet of Things (IoT) devices, wireless sensor networks, and battery-powered communication systems. The technology has evolved to incorporate adaptive bandwidth control, dynamic power scaling, and intelligent sleep modes that can reduce power consumption by orders of magnitude compared to traditional PLL-based solutions.

The primary objective of low-power FLL implementation centers on achieving optimal frequency tracking performance while minimizing energy consumption across all operational modes. This involves developing architectures that can maintain frequency lock with minimal active circuitry, utilizing techniques such as duty-cycled operation, ultra-low-power oscillators, and efficient frequency detection algorithms. The target specifications typically include power consumption below 100 microwatts, lock acquisition times under 10 microseconds, and frequency accuracy within parts-per-million ranges.

Advanced low-power FLL designs aim to integrate seamlessly with power management systems, enabling dynamic performance scaling based on application requirements. The ultimate goal is to create frequency synthesis solutions that extend battery life in portable devices while maintaining the reliability and accuracy demanded by modern communication protocols and timing-critical applications.

The evolution of FLL technology has been closely intertwined with the advancement of low-power electronics. Early implementations relied on analog circuits with high power consumption, limiting their application in portable devices. The transition to digital and mixed-signal architectures in the 1990s marked a significant milestone, enabling more sophisticated control algorithms while reducing overall power requirements. Modern FLL implementations leverage advanced semiconductor processes and innovative circuit topologies to achieve sub-milliwatt operation.

Contemporary FLL systems address the growing demand for energy-efficient frequency synthesis in Internet of Things (IoT) devices, wireless sensor networks, and battery-powered communication systems. The technology has evolved to incorporate adaptive bandwidth control, dynamic power scaling, and intelligent sleep modes that can reduce power consumption by orders of magnitude compared to traditional PLL-based solutions.

The primary objective of low-power FLL implementation centers on achieving optimal frequency tracking performance while minimizing energy consumption across all operational modes. This involves developing architectures that can maintain frequency lock with minimal active circuitry, utilizing techniques such as duty-cycled operation, ultra-low-power oscillators, and efficient frequency detection algorithms. The target specifications typically include power consumption below 100 microwatts, lock acquisition times under 10 microseconds, and frequency accuracy within parts-per-million ranges.

Advanced low-power FLL designs aim to integrate seamlessly with power management systems, enabling dynamic performance scaling based on application requirements. The ultimate goal is to create frequency synthesis solutions that extend battery life in portable devices while maintaining the reliability and accuracy demanded by modern communication protocols and timing-critical applications.

Market Demand for Low-Power FLL Applications

The market demand for low-power frequency-locked loop applications has experienced substantial growth driven by the proliferation of battery-powered devices and energy-conscious system designs. Internet of Things devices represent the largest segment, where extended battery life directly correlates with deployment feasibility and maintenance costs. Wearable technology, wireless sensor networks, and smart home devices collectively form a significant portion of this demand, requiring FLL circuits that can operate efficiently under stringent power budgets.

Mobile communication systems constitute another major demand driver, particularly in 5G infrastructure and edge computing applications. Base stations and small cells require precise frequency synchronization while minimizing power consumption to reduce operational costs and thermal management complexity. The transition toward distributed network architectures has amplified the need for low-power timing solutions that can maintain synchronization accuracy across diverse deployment scenarios.

Automotive electronics present an emerging high-growth segment, where low-power FLL circuits enable advanced driver assistance systems and autonomous vehicle technologies. Electric vehicles particularly benefit from power-efficient frequency generation, as every milliwatt saved contributes to extended driving range. The automotive sector demands robust performance across temperature variations while maintaining minimal power consumption during standby modes.

Medical device applications drive specialized demand for ultra-low-power FLL implementations. Implantable devices, continuous monitoring systems, and portable diagnostic equipment require frequency stability with power consumption measured in microwatts. Regulatory requirements for medical devices create additional performance constraints while emphasizing reliability and longevity.

Industrial automation and smart manufacturing sectors increasingly adopt wireless sensor networks requiring distributed timing solutions. These applications demand FLL circuits capable of maintaining synchronization across large-scale deployments while operating on energy harvesting or long-life battery systems. The industrial segment values robustness and predictable performance over extended operational periods.

Consumer electronics continue expanding demand through smartwatches, fitness trackers, and portable audio devices. Market competition drives manufacturers to prioritize battery life as a key differentiator, creating sustained demand for power-efficient frequency generation solutions that enable extended usage between charging cycles.

Mobile communication systems constitute another major demand driver, particularly in 5G infrastructure and edge computing applications. Base stations and small cells require precise frequency synchronization while minimizing power consumption to reduce operational costs and thermal management complexity. The transition toward distributed network architectures has amplified the need for low-power timing solutions that can maintain synchronization accuracy across diverse deployment scenarios.

Automotive electronics present an emerging high-growth segment, where low-power FLL circuits enable advanced driver assistance systems and autonomous vehicle technologies. Electric vehicles particularly benefit from power-efficient frequency generation, as every milliwatt saved contributes to extended driving range. The automotive sector demands robust performance across temperature variations while maintaining minimal power consumption during standby modes.

Medical device applications drive specialized demand for ultra-low-power FLL implementations. Implantable devices, continuous monitoring systems, and portable diagnostic equipment require frequency stability with power consumption measured in microwatts. Regulatory requirements for medical devices create additional performance constraints while emphasizing reliability and longevity.

Industrial automation and smart manufacturing sectors increasingly adopt wireless sensor networks requiring distributed timing solutions. These applications demand FLL circuits capable of maintaining synchronization across large-scale deployments while operating on energy harvesting or long-life battery systems. The industrial segment values robustness and predictable performance over extended operational periods.

Consumer electronics continue expanding demand through smartwatches, fitness trackers, and portable audio devices. Market competition drives manufacturers to prioritize battery life as a key differentiator, creating sustained demand for power-efficient frequency generation solutions that enable extended usage between charging cycles.

Current FLL Power Consumption Challenges

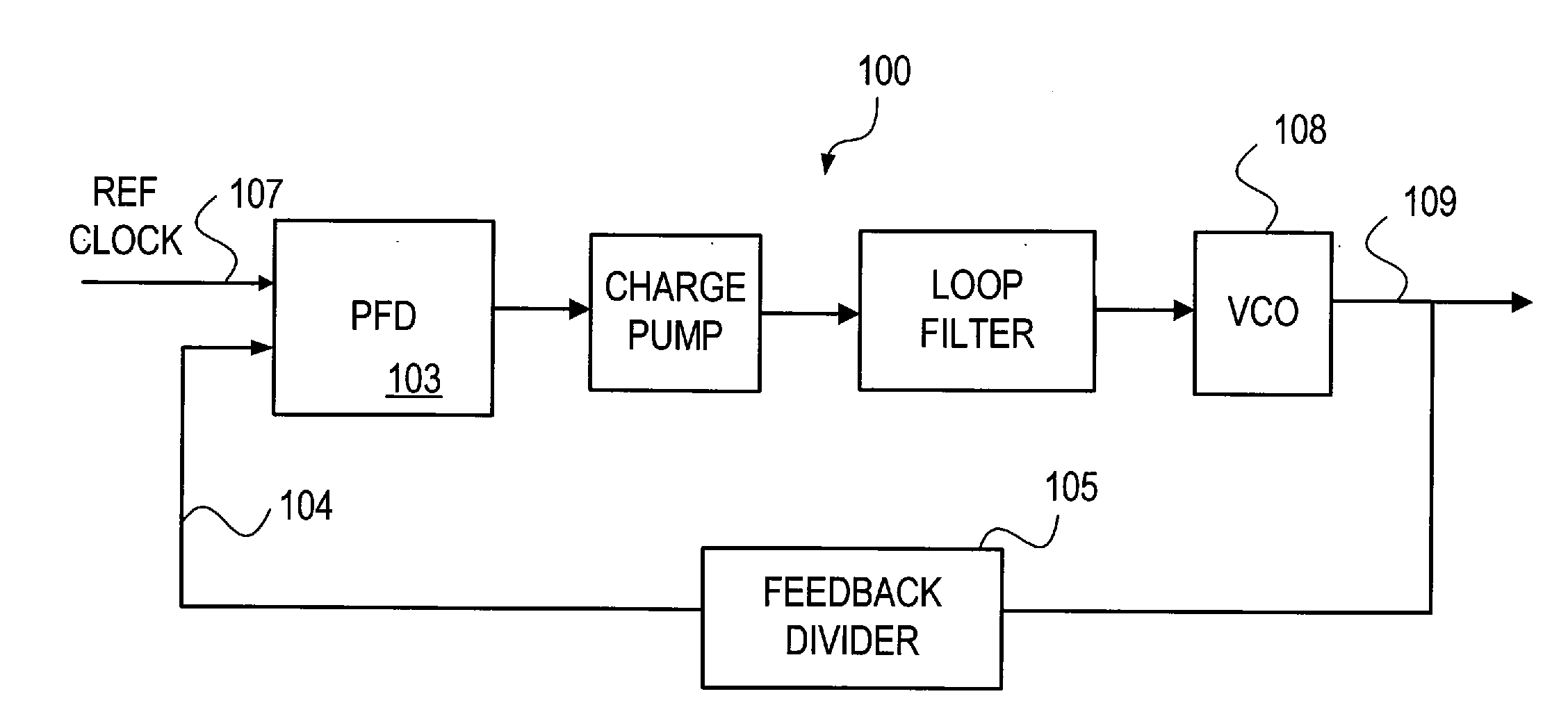

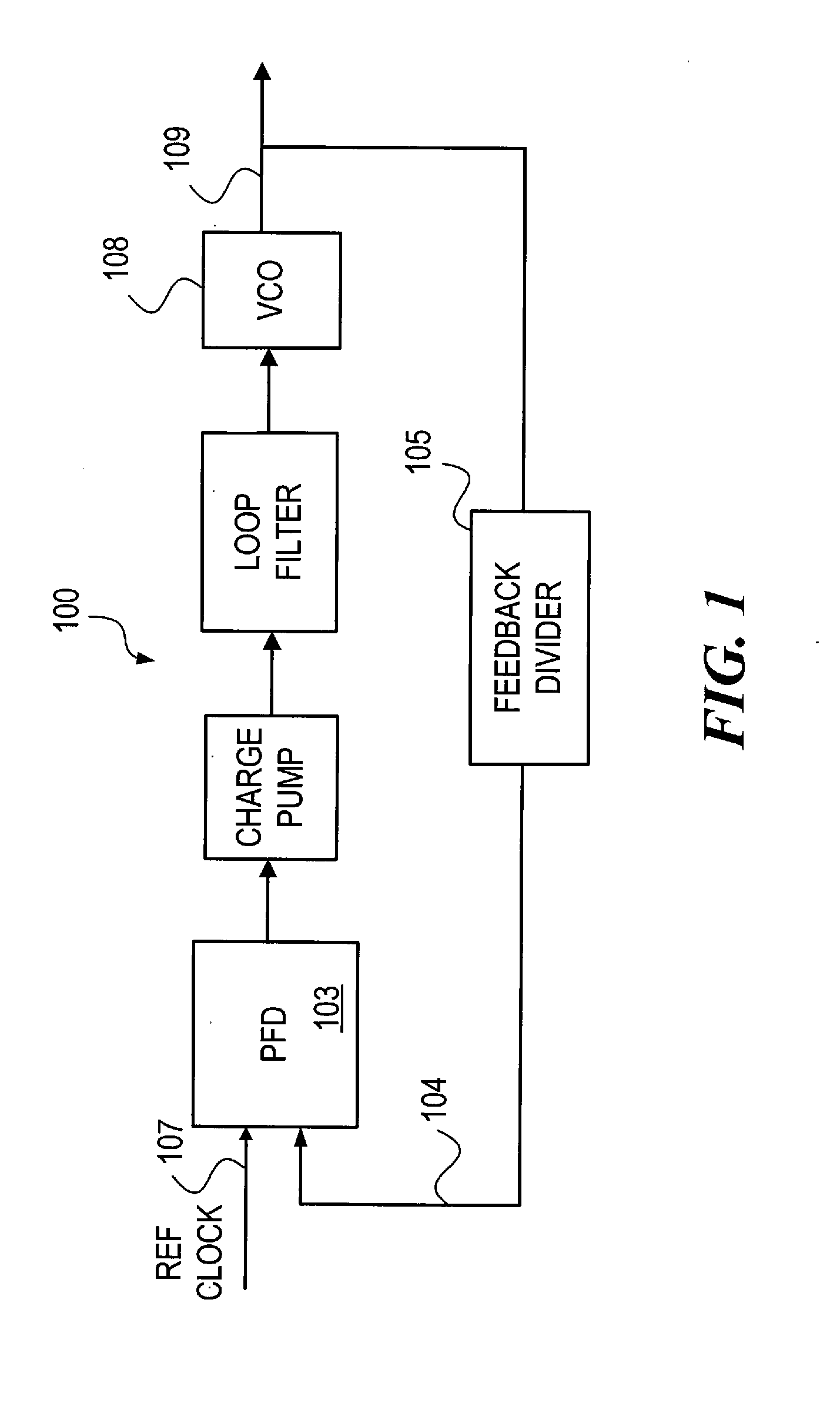

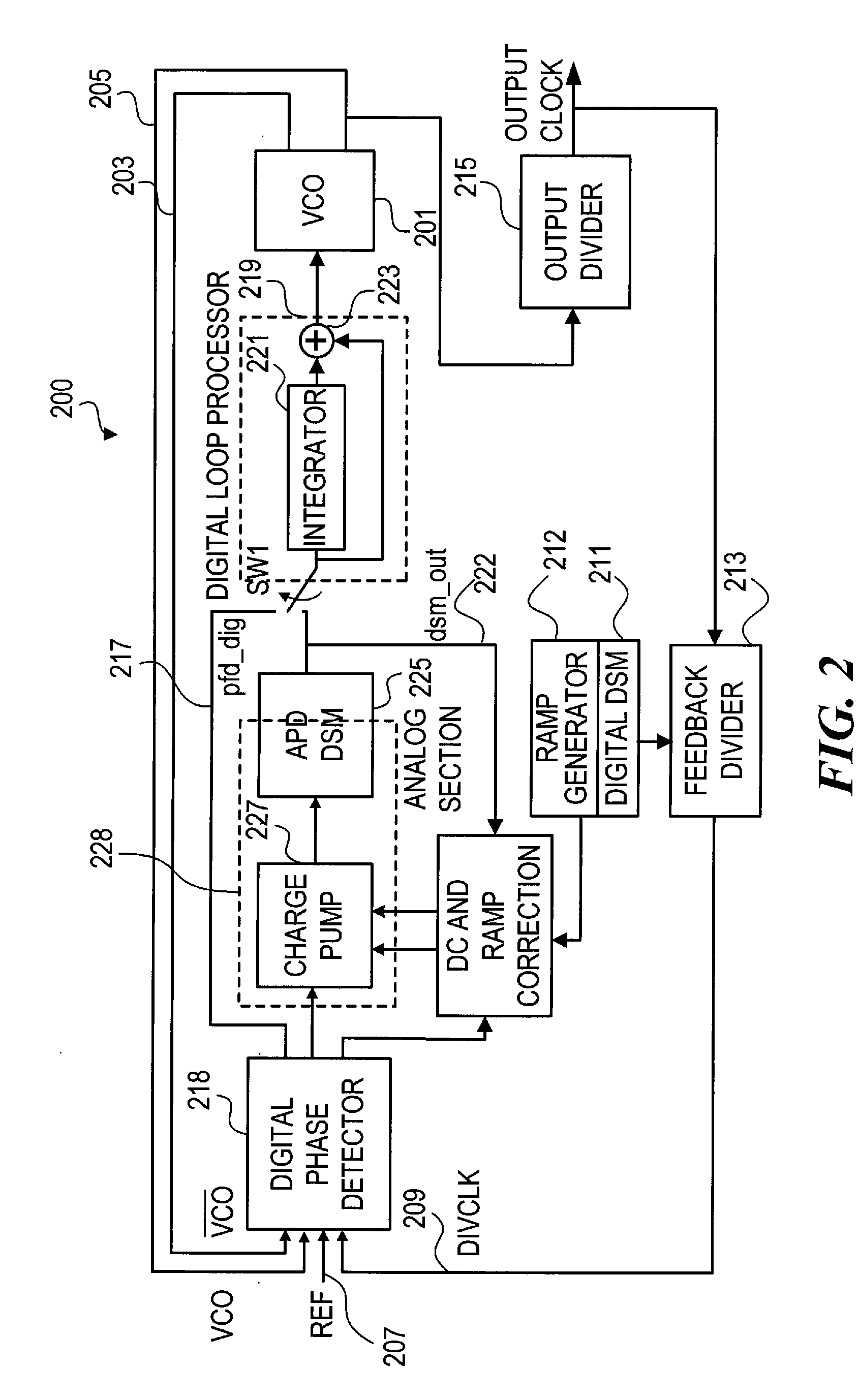

Frequency-Locked Loop circuits face significant power consumption challenges that limit their deployment in battery-powered and energy-constrained applications. Traditional FLL architectures typically consume power in the range of several milliwatts to tens of milliwatts, which proves prohibitive for ultra-low-power systems requiring sub-milliwatt operation. The primary power consumption bottlenecks stem from the continuous operation of analog components, including voltage-controlled oscillators, phase detectors, and charge pumps that must maintain constant bias currents.

The voltage-controlled oscillator represents the largest power consumer in conventional FLL designs, often accounting for 40-60% of total circuit power. High-frequency operation demands substantial bias currents to achieve adequate phase noise performance and frequency stability. Ring oscillators, while offering lower power consumption compared to LC oscillators, still require significant current to maintain oscillation across process, voltage, and temperature variations. The trade-off between power consumption and jitter performance creates a fundamental design constraint.

Phase detection and frequency comparison circuits contribute another major power consumption component. Traditional phase-frequency detectors require high-speed logic gates operating at reference frequencies, consuming dynamic power proportional to switching frequency. Charge pump circuits must maintain adequate current levels to drive loop filter capacitors, while operational amplifiers in the loop filter require continuous bias currents for stability and bandwidth requirements.

Reference clock distribution and buffering stages add additional power overhead, particularly in systems requiring multiple clock domains or high fan-out requirements. Clock buffers must provide sufficient drive strength while maintaining signal integrity, leading to increased static and dynamic power consumption. The cumulative effect of these distributed power consumers often exceeds the core FLL circuit power by significant margins.

Process variation sensitivity exacerbates power consumption challenges by requiring design margins that increase nominal operating currents. Temperature compensation circuits, essential for maintaining frequency accuracy across operating conditions, introduce additional power overhead through bias generation and monitoring circuits. Leakage current in advanced CMOS processes further compounds power consumption issues, particularly in always-on applications where FLL circuits must maintain lock during standby modes.

Supply voltage scaling limitations present another critical challenge, as analog circuit performance degrades rapidly below certain voltage thresholds. While digital circuits benefit from aggressive voltage scaling, FLL analog components require minimum operating voltages to maintain adequate signal-to-noise ratios and linearity. This voltage floor constraint prevents optimal power scaling and limits the effectiveness of dynamic voltage scaling techniques in mixed-signal FLL implementations.

The voltage-controlled oscillator represents the largest power consumer in conventional FLL designs, often accounting for 40-60% of total circuit power. High-frequency operation demands substantial bias currents to achieve adequate phase noise performance and frequency stability. Ring oscillators, while offering lower power consumption compared to LC oscillators, still require significant current to maintain oscillation across process, voltage, and temperature variations. The trade-off between power consumption and jitter performance creates a fundamental design constraint.

Phase detection and frequency comparison circuits contribute another major power consumption component. Traditional phase-frequency detectors require high-speed logic gates operating at reference frequencies, consuming dynamic power proportional to switching frequency. Charge pump circuits must maintain adequate current levels to drive loop filter capacitors, while operational amplifiers in the loop filter require continuous bias currents for stability and bandwidth requirements.

Reference clock distribution and buffering stages add additional power overhead, particularly in systems requiring multiple clock domains or high fan-out requirements. Clock buffers must provide sufficient drive strength while maintaining signal integrity, leading to increased static and dynamic power consumption. The cumulative effect of these distributed power consumers often exceeds the core FLL circuit power by significant margins.

Process variation sensitivity exacerbates power consumption challenges by requiring design margins that increase nominal operating currents. Temperature compensation circuits, essential for maintaining frequency accuracy across operating conditions, introduce additional power overhead through bias generation and monitoring circuits. Leakage current in advanced CMOS processes further compounds power consumption issues, particularly in always-on applications where FLL circuits must maintain lock during standby modes.

Supply voltage scaling limitations present another critical challenge, as analog circuit performance degrades rapidly below certain voltage thresholds. While digital circuits benefit from aggressive voltage scaling, FLL analog components require minimum operating voltages to maintain adequate signal-to-noise ratios and linearity. This voltage floor constraint prevents optimal power scaling and limits the effectiveness of dynamic voltage scaling techniques in mixed-signal FLL implementations.

Existing Low-Power FLL Implementation Methods

01 Low-power frequency-locked loop circuit design

Frequency-locked loop circuits can be designed with low-power consumption architectures by optimizing circuit topology and component selection. These designs focus on reducing static and dynamic power dissipation while maintaining frequency locking performance. Techniques include using current-starved oscillators, reducing supply voltage, and implementing power-down modes during idle periods. The low-power designs are particularly suitable for battery-operated devices and portable electronics.- Low-power frequency-locked loop circuit design: Frequency-locked loop circuits can be designed with low-power consumption architectures by optimizing circuit topology and component selection. These designs focus on reducing static and dynamic power dissipation while maintaining frequency locking performance. Techniques include using current-starved oscillators, reducing supply voltage, and implementing power-down modes during idle periods. The low-power designs are particularly suitable for battery-operated devices and portable electronics.

- Adaptive power management in frequency-locked loops: Adaptive power management techniques can be implemented in frequency-locked loop systems to dynamically adjust power consumption based on operating conditions. These methods monitor the loop's lock status and operational requirements, then adjust bias currents, enable/disable circuit blocks, or modify operating modes accordingly. This approach allows the system to consume minimal power when high performance is not required while providing full performance when needed.

- Frequency divider optimization for power reduction: The frequency divider in a frequency-locked loop can be optimized to reduce overall power consumption. This includes using efficient divider architectures such as dual-modulus prescalers, implementing clock gating techniques, and reducing switching activity. The optimization of frequency dividers is critical as they often operate at high frequencies and can contribute significantly to total power consumption.

- Phase detector and charge pump power optimization: The phase detector and charge pump circuits in frequency-locked loops can be designed with power-efficient architectures to minimize current consumption. Techniques include using tri-state phase detectors to reduce switching activity, optimizing charge pump current levels, and implementing current-mode logic. These optimizations reduce power consumption while maintaining adequate phase detection sensitivity and loop stability.

- Voltage-controlled oscillator power reduction techniques: Voltage-controlled oscillators in frequency-locked loops can employ various power reduction techniques including reduced swing operation, current reuse topologies, and optimized inductor-capacitor tank circuits. These methods decrease the power consumption of the oscillator core while maintaining sufficient output signal quality and frequency tuning range. The oscillator typically represents a significant portion of the total loop power consumption.

02 Adaptive power management in frequency-locked loops

Adaptive power management techniques can be implemented in frequency-locked loop systems to dynamically adjust power consumption based on operational requirements. These methods monitor the locking status and signal conditions to selectively enable or disable circuit blocks, adjust bias currents, or modify loop bandwidth. The adaptive approach allows the system to balance between power consumption and performance, reducing overall energy usage without compromising functionality.Expand Specific Solutions03 Frequency divider optimization for power reduction

The frequency divider in a frequency-locked loop can be optimized to reduce power consumption by employing efficient divider architectures and logic styles. Techniques include using dual-modulus prescalers, implementing dynamic logic circuits, and reducing the number of flip-flops in the divider chain. These optimizations minimize switching activity and reduce the overall power drawn by the frequency division stage, which is often a significant contributor to total power consumption.Expand Specific Solutions04 Phase detector and charge pump power optimization

The phase detector and charge pump circuits in frequency-locked loops can be designed with power-efficient architectures to minimize current consumption. Approaches include using tri-state phase detectors to reduce switching activity, implementing charge pumps with reduced leakage current, and optimizing the bias conditions of operational amplifiers. These techniques reduce the power consumption of the phase comparison and loop filter charging stages while maintaining adequate phase detection sensitivity.Expand Specific Solutions05 Voltage-controlled oscillator power efficiency

Voltage-controlled oscillators in frequency-locked loops can be designed for improved power efficiency through careful selection of oscillator topology and biasing schemes. Methods include using LC oscillators with high quality factor inductors, implementing class-C or class-D oscillator configurations, and optimizing transistor sizing for minimum power consumption at the required frequency range. These power-efficient oscillator designs reduce the continuous power drain that represents a major component of total frequency-locked loop power consumption.Expand Specific Solutions

Key Players in Low-Power FLL Solutions

The frequency-locked loop (FLL) for low-power consumption technology represents a mature segment within the broader timing and clock generation market, currently valued at approximately $5 billion globally. The industry has reached a stable development stage with established players demonstrating varying levels of technological sophistication. Major semiconductor companies like Intel Corp., Texas Instruments, Samsung Electronics, and Taiwan Semiconductor Manufacturing Co. lead with advanced process technologies and comprehensive product portfolios. Specialized timing solution providers such as SiTime Corp. and Silicon Laboratories have achieved significant market penetration through MEMS-based innovations and energy-efficient designs. Asian manufacturers including MediaTek, SK Hynix, and NXP Semiconductors contribute substantial manufacturing capabilities and cost-competitive solutions. The technology maturity is evidenced by widespread adoption across automotive, IoT, and mobile applications, with most companies offering production-ready FLL implementations optimized for specific power consumption requirements.

Intel Corp.

Technical Solution: Intel implements frequency-locked loop (FLL) technology through advanced clock generation and distribution systems integrated into their processor architectures. Their FLL designs utilize adaptive voltage and frequency scaling (AVFS) mechanisms that dynamically adjust operating frequencies based on workload demands while maintaining phase coherence with reference signals. The implementation incorporates digital control loops with sophisticated feedback mechanisms that monitor power consumption in real-time, enabling automatic frequency adjustments to optimize power efficiency. Intel's FLL solutions feature multi-domain clock management with independent frequency scaling for different processor cores and functional units, allowing selective power reduction in unused areas while maintaining performance in active regions.

Strengths: Mature semiconductor manufacturing capabilities, extensive R&D resources, proven track record in low-power processor design. Weaknesses: Higher cost compared to specialized FLL providers, complex integration requirements for third-party applications.

Texas Instruments Incorporated

Technical Solution: Texas Instruments develops frequency-locked loop solutions specifically optimized for ultra-low power applications in embedded systems and IoT devices. Their FLL architecture employs digitally-controlled oscillators (DCO) combined with phase-frequency detectors that achieve rapid lock times while minimizing power consumption during steady-state operation. The design incorporates power gating techniques and clock domain isolation to reduce leakage current, with typical power consumption in the micro-watt range during standby modes. TI's FLL implementations feature adaptive loop bandwidth control that automatically adjusts tracking performance based on environmental conditions and reference signal quality, ensuring stable operation across wide temperature and voltage ranges while maintaining optimal power efficiency.

Strengths: Specialized expertise in low-power analog and mixed-signal design, comprehensive portfolio of power management solutions, strong market presence in embedded applications. Weaknesses: Limited high-performance computing applications, smaller scale compared to major processor manufacturers.

Core Patents in Power-Efficient FLL Design

Frequency lock loop circuits, low voltage dropout regulator circuits, and related methods

PatentActiveUS20210111726A1

Innovation

- The implementation of FLL circuits with switched capacitor circuits to reduce the number of filtering components, and the use of a ratio-based current-sensing loop with frequency compensation in LDOs to achieve smooth handoffs and stable current limit control, reducing silicon area and improving power efficiency.

Dividerless PLL architecture

PatentActiveUS20090015338A1

Innovation

- The proposed PLL architecture employs a course fractional-N or integer divider for initial lock, which is then turned off, with an adaptive phase detector taking over to maintain frequency lock, using a digital delta sigma modulator to generate control signals and correct for errors, allowing the PLL to operate without a feedback divider in a low power mode.

Power Management Standards for FLL Systems

Power management standards for Frequency-Locked Loop (FLL) systems have evolved significantly to address the growing demand for energy-efficient electronic devices. These standards establish comprehensive frameworks that govern power consumption metrics, operational efficiency requirements, and performance benchmarks specifically tailored for FLL implementations in low-power applications.

The IEEE 1801 standard, commonly known as the Unified Power Format (UPF), provides fundamental guidelines for power-aware design methodologies that directly impact FLL system development. This standard defines power domains, supply networks, and retention strategies that are crucial for maintaining FLL stability while minimizing energy consumption. Additionally, the JEDEC standards, particularly JESD79 and JESD209 series, establish memory interface power management protocols that influence FLL design in system-on-chip applications.

International Electrotechnical Commission (IEC) standards, specifically IEC 62430 and IEC 62264, address power management requirements for embedded systems where FLL circuits are commonly deployed. These standards mandate specific power efficiency ratios and define acceptable power consumption thresholds for different operational modes, including active, standby, and sleep states that FLL systems must support.

The Advanced Configuration and Power Interface (ACPI) specification provides detailed power state definitions that FLL systems must accommodate. ACPI defines multiple power states from S0 to S5, each requiring different FLL operational parameters and power consumption levels. Modern FLL designs must seamlessly transition between these states while maintaining frequency lock integrity and minimizing wake-up latency.

Energy Star certification requirements have also influenced FLL power management standards, particularly for consumer electronics and computing devices. These requirements establish maximum power consumption limits during various operational scenarios, directly impacting FLL design specifications and implementation strategies.

Emerging standards such as the Power Management Bus (PMBus) protocol and the System Management Interface Forum (SMIF) specifications are increasingly relevant for FLL systems in distributed power architectures. These standards define communication protocols and power monitoring capabilities that enable dynamic power optimization and real-time performance adjustment in FLL implementations.

The IEEE 1801 standard, commonly known as the Unified Power Format (UPF), provides fundamental guidelines for power-aware design methodologies that directly impact FLL system development. This standard defines power domains, supply networks, and retention strategies that are crucial for maintaining FLL stability while minimizing energy consumption. Additionally, the JEDEC standards, particularly JESD79 and JESD209 series, establish memory interface power management protocols that influence FLL design in system-on-chip applications.

International Electrotechnical Commission (IEC) standards, specifically IEC 62430 and IEC 62264, address power management requirements for embedded systems where FLL circuits are commonly deployed. These standards mandate specific power efficiency ratios and define acceptable power consumption thresholds for different operational modes, including active, standby, and sleep states that FLL systems must support.

The Advanced Configuration and Power Interface (ACPI) specification provides detailed power state definitions that FLL systems must accommodate. ACPI defines multiple power states from S0 to S5, each requiring different FLL operational parameters and power consumption levels. Modern FLL designs must seamlessly transition between these states while maintaining frequency lock integrity and minimizing wake-up latency.

Energy Star certification requirements have also influenced FLL power management standards, particularly for consumer electronics and computing devices. These requirements establish maximum power consumption limits during various operational scenarios, directly impacting FLL design specifications and implementation strategies.

Emerging standards such as the Power Management Bus (PMBus) protocol and the System Management Interface Forum (SMIF) specifications are increasingly relevant for FLL systems in distributed power architectures. These standards define communication protocols and power monitoring capabilities that enable dynamic power optimization and real-time performance adjustment in FLL implementations.

Energy Harvesting Integration with FLL Circuits

Energy harvesting integration represents a paradigmatic shift in frequency-locked loop circuit design, enabling autonomous operation in ultra-low-power applications. This approach combines ambient energy collection mechanisms with FLL architectures to create self-sustaining systems that eliminate dependency on traditional power sources. The integration encompasses photovoltaic cells, thermoelectric generators, vibration harvesters, and radio frequency energy scavenging modules that can power FLL circuits continuously.

The fundamental challenge lies in matching the intermittent and variable nature of harvested energy with the stringent power requirements of frequency-locked loops. Energy harvesting sources typically provide power levels ranging from microwatts to milliwatts, necessitating sophisticated power management circuits that can efficiently store and regulate energy delivery. Advanced maximum power point tracking algorithms ensure optimal energy extraction from environmental sources while maintaining stable FLL operation.

Power conditioning circuits serve as critical interfaces between energy harvesters and FLL systems. These circuits incorporate ultra-low-power DC-DC converters, energy storage elements such as supercapacitors or thin-film batteries, and intelligent power gating mechanisms. The conditioning circuitry must handle wide input voltage variations while providing clean, regulated power to sensitive frequency synthesis components.

Adaptive power management strategies enable FLL circuits to dynamically adjust their operational parameters based on available harvested energy. During periods of abundant energy availability, the system can operate at higher performance levels with increased frequency accuracy and faster settling times. Conversely, when harvested energy is limited, the FLL enters power-saving modes with reduced update rates and simplified control algorithms while maintaining basic frequency locking functionality.

Circuit-level optimizations specifically target energy harvesting integration scenarios. Subthreshold operation techniques allow FLL components to function at supply voltages below traditional threshold levels, dramatically reducing power consumption. Clock gating and power island architectures enable selective activation of circuit blocks based on energy availability, while maintaining essential frequency reference generation.

The synergy between energy harvesting and FLL circuits opens new application domains including wireless sensor networks, IoT devices, and autonomous monitoring systems. These implementations demonstrate the feasibility of perpetual operation without battery replacement, significantly reducing maintenance costs and enabling deployment in remote or inaccessible locations where traditional power sources are impractical.

The fundamental challenge lies in matching the intermittent and variable nature of harvested energy with the stringent power requirements of frequency-locked loops. Energy harvesting sources typically provide power levels ranging from microwatts to milliwatts, necessitating sophisticated power management circuits that can efficiently store and regulate energy delivery. Advanced maximum power point tracking algorithms ensure optimal energy extraction from environmental sources while maintaining stable FLL operation.

Power conditioning circuits serve as critical interfaces between energy harvesters and FLL systems. These circuits incorporate ultra-low-power DC-DC converters, energy storage elements such as supercapacitors or thin-film batteries, and intelligent power gating mechanisms. The conditioning circuitry must handle wide input voltage variations while providing clean, regulated power to sensitive frequency synthesis components.

Adaptive power management strategies enable FLL circuits to dynamically adjust their operational parameters based on available harvested energy. During periods of abundant energy availability, the system can operate at higher performance levels with increased frequency accuracy and faster settling times. Conversely, when harvested energy is limited, the FLL enters power-saving modes with reduced update rates and simplified control algorithms while maintaining basic frequency locking functionality.

Circuit-level optimizations specifically target energy harvesting integration scenarios. Subthreshold operation techniques allow FLL components to function at supply voltages below traditional threshold levels, dramatically reducing power consumption. Clock gating and power island architectures enable selective activation of circuit blocks based on energy availability, while maintaining essential frequency reference generation.

The synergy between energy harvesting and FLL circuits opens new application domains including wireless sensor networks, IoT devices, and autonomous monitoring systems. These implementations demonstrate the feasibility of perpetual operation without battery replacement, significantly reducing maintenance costs and enabling deployment in remote or inaccessible locations where traditional power sources are impractical.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!