Optimizing FinFET Gate Control To Minimize Noise

SEP 11, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Technology Background and Objectives

FinFET (Fin Field-Effect Transistor) technology emerged as a revolutionary advancement in semiconductor manufacturing, addressing the limitations of traditional planar transistors as device dimensions continued to shrink below 22nm. Since its commercial introduction in 2011, FinFET has become the cornerstone of modern high-performance integrated circuits, offering superior electrostatic control of the channel through its three-dimensional fin structure.

The evolution of FinFET technology has been driven by the semiconductor industry's relentless pursuit of Moore's Law, which demands continuous miniaturization while improving performance and power efficiency. Traditional planar transistors faced severe short-channel effects at sub-22nm nodes, including increased leakage current and variability issues that compromised circuit reliability and power consumption.

FinFET architecture fundamentally transformed transistor design by extending the gate electrode vertically on multiple sides of the fin-shaped channel, dramatically improving gate control over the channel. This multi-gate configuration significantly reduced leakage current and allowed for lower operating voltages, addressing the power density challenges that had become critical in advanced nodes.

The technology has progressed through several generations, with each iteration refining fin geometry, gate stack materials, and manufacturing processes. Early implementations featured relatively thick fins with limited height-to-width ratios, while more recent generations have achieved increasingly taller and narrower fins, enhancing electrostatic control and current drive capabilities.

Despite these advancements, noise remains a persistent challenge in FinFET technology. As dimensions shrink and operating voltages decrease, various noise sources—including thermal noise, flicker noise, and random telegraph noise—have become increasingly significant factors affecting circuit performance and reliability. These noise phenomena are particularly problematic in analog and mixed-signal applications where signal integrity is paramount.

The primary objective of optimizing FinFET gate control to minimize noise is to enable the continued scaling of semiconductor technology while maintaining or improving signal integrity across diverse application domains. This optimization aims to address several interconnected goals: enhancing signal-to-noise ratios in sensitive analog circuits, improving the reliability of digital logic at ultra-low operating voltages, and extending battery life in mobile and IoT applications.

Future technology trends point toward even more sophisticated gate control mechanisms, including the potential integration of novel materials and gate architectures. Research is actively exploring the incorporation of high-mobility channel materials, advanced gate dielectrics, and innovative fin geometries to further suppress noise while maintaining the scaling advantages that have made FinFET technology so successful.

The evolution of FinFET technology has been driven by the semiconductor industry's relentless pursuit of Moore's Law, which demands continuous miniaturization while improving performance and power efficiency. Traditional planar transistors faced severe short-channel effects at sub-22nm nodes, including increased leakage current and variability issues that compromised circuit reliability and power consumption.

FinFET architecture fundamentally transformed transistor design by extending the gate electrode vertically on multiple sides of the fin-shaped channel, dramatically improving gate control over the channel. This multi-gate configuration significantly reduced leakage current and allowed for lower operating voltages, addressing the power density challenges that had become critical in advanced nodes.

The technology has progressed through several generations, with each iteration refining fin geometry, gate stack materials, and manufacturing processes. Early implementations featured relatively thick fins with limited height-to-width ratios, while more recent generations have achieved increasingly taller and narrower fins, enhancing electrostatic control and current drive capabilities.

Despite these advancements, noise remains a persistent challenge in FinFET technology. As dimensions shrink and operating voltages decrease, various noise sources—including thermal noise, flicker noise, and random telegraph noise—have become increasingly significant factors affecting circuit performance and reliability. These noise phenomena are particularly problematic in analog and mixed-signal applications where signal integrity is paramount.

The primary objective of optimizing FinFET gate control to minimize noise is to enable the continued scaling of semiconductor technology while maintaining or improving signal integrity across diverse application domains. This optimization aims to address several interconnected goals: enhancing signal-to-noise ratios in sensitive analog circuits, improving the reliability of digital logic at ultra-low operating voltages, and extending battery life in mobile and IoT applications.

Future technology trends point toward even more sophisticated gate control mechanisms, including the potential integration of novel materials and gate architectures. Research is actively exploring the incorporation of high-mobility channel materials, advanced gate dielectrics, and innovative fin geometries to further suppress noise while maintaining the scaling advantages that have made FinFET technology so successful.

Market Demand for Low-Noise Semiconductor Devices

The semiconductor industry is witnessing an unprecedented demand for low-noise semiconductor devices, particularly in applications requiring high precision and reliability. The global market for low-noise semiconductor components is projected to reach $45 billion by 2027, growing at a CAGR of 8.7% from 2022. This growth is primarily driven by the expanding applications in telecommunications, healthcare monitoring systems, aerospace, defense, and consumer electronics sectors where signal integrity is paramount.

FinFET technology has become the cornerstone of advanced semiconductor manufacturing, with its superior gate control capabilities making it ideal for low-noise applications. Market research indicates that approximately 65% of high-performance computing chips now utilize FinFET architecture, with noise reduction being a critical performance parameter for customers.

The telecommunications sector represents the largest market segment, accounting for 34% of the demand for low-noise semiconductor devices. The rollout of 5G networks globally has intensified this demand, as these networks require extremely low-noise amplifiers and transceivers to maintain signal quality across higher frequency bands. Industry forecasts suggest that 5G infrastructure investments will exceed $300 billion through 2025, creating sustained demand for optimized FinFET solutions.

Healthcare applications constitute the fastest-growing segment, with a 12.3% annual growth rate. Medical imaging equipment, implantable devices, and diagnostic tools all require exceptionally low-noise performance to detect minute biological signals. The precision medicine trend is further accelerating this demand, as personalized healthcare solutions rely on increasingly sensitive semiconductor components.

Consumer electronics manufacturers are also driving market demand, with smartphone producers competing to offer devices with better signal reception, lower power consumption, and higher processing capabilities. Market surveys reveal that 78% of high-end smartphone users consider signal quality a decisive factor in purchasing decisions, directly correlating to the noise performance of internal semiconductor components.

Automotive electronics represent an emerging but rapidly expanding market segment. Advanced driver-assistance systems (ADAS) and autonomous driving technologies require ultra-reliable, low-noise semiconductor devices to ensure accurate sensor data processing. The automotive semiconductor market specific to low-noise applications is growing at 15.2% annually, outpacing the overall semiconductor industry growth.

Geographically, Asia-Pacific dominates the market with 52% share, followed by North America (27%) and Europe (18%). China's aggressive investments in semiconductor manufacturing capabilities are specifically targeting advanced FinFET processes with enhanced noise performance characteristics, reflecting the strategic importance of this technology in the global semiconductor landscape.

FinFET technology has become the cornerstone of advanced semiconductor manufacturing, with its superior gate control capabilities making it ideal for low-noise applications. Market research indicates that approximately 65% of high-performance computing chips now utilize FinFET architecture, with noise reduction being a critical performance parameter for customers.

The telecommunications sector represents the largest market segment, accounting for 34% of the demand for low-noise semiconductor devices. The rollout of 5G networks globally has intensified this demand, as these networks require extremely low-noise amplifiers and transceivers to maintain signal quality across higher frequency bands. Industry forecasts suggest that 5G infrastructure investments will exceed $300 billion through 2025, creating sustained demand for optimized FinFET solutions.

Healthcare applications constitute the fastest-growing segment, with a 12.3% annual growth rate. Medical imaging equipment, implantable devices, and diagnostic tools all require exceptionally low-noise performance to detect minute biological signals. The precision medicine trend is further accelerating this demand, as personalized healthcare solutions rely on increasingly sensitive semiconductor components.

Consumer electronics manufacturers are also driving market demand, with smartphone producers competing to offer devices with better signal reception, lower power consumption, and higher processing capabilities. Market surveys reveal that 78% of high-end smartphone users consider signal quality a decisive factor in purchasing decisions, directly correlating to the noise performance of internal semiconductor components.

Automotive electronics represent an emerging but rapidly expanding market segment. Advanced driver-assistance systems (ADAS) and autonomous driving technologies require ultra-reliable, low-noise semiconductor devices to ensure accurate sensor data processing. The automotive semiconductor market specific to low-noise applications is growing at 15.2% annually, outpacing the overall semiconductor industry growth.

Geographically, Asia-Pacific dominates the market with 52% share, followed by North America (27%) and Europe (18%). China's aggressive investments in semiconductor manufacturing capabilities are specifically targeting advanced FinFET processes with enhanced noise performance characteristics, reflecting the strategic importance of this technology in the global semiconductor landscape.

Current FinFET Gate Control Challenges

FinFET technology has revolutionized semiconductor manufacturing, yet significant challenges persist in gate control mechanisms that directly impact noise performance. The multi-gate architecture of FinFETs, while offering superior electrostatic control compared to planar transistors, introduces complex gate control issues that must be addressed to minimize noise in high-performance applications.

Short-channel effects (SCEs) remain a primary challenge in current FinFET designs. As device dimensions continue to shrink below 10nm, quantum mechanical effects become increasingly prominent, leading to electron tunneling and gate leakage that contribute to noise generation. The fin geometry itself creates unique electrostatic conditions that complicate gate control optimization, with the fin height-to-width ratio directly influencing the effectiveness of gate control and subsequent noise characteristics.

Gate stack engineering presents another significant hurdle. The industry's transition from conventional SiO2 to high-k dielectric materials has improved gate capacitance but introduced interface traps and fixed charges that generate random telegraph noise (RTN) and 1/f noise. These noise sources are particularly problematic in analog and mixed-signal applications where signal integrity is paramount. Additionally, the three-dimensional nature of FinFETs creates non-uniform electric fields around the fin structure, resulting in variability in threshold voltage and transconductance.

Process-induced variability further complicates gate control optimization. Manufacturing inconsistencies in fin width, height, and shape directly impact the gate's ability to control channel conductivity uniformly. Line edge roughness (LER) and line width roughness (LWR) introduce random variations in the channel dimensions, leading to device-to-device variability that manifests as noise in circuit operation. These manufacturing challenges become exponentially more difficult as dimensions shrink toward 5nm and below.

Self-heating effects represent an emerging challenge in advanced FinFET designs. The confined geometry of the fin structure impedes efficient heat dissipation, causing localized temperature increases that alter carrier mobility and threshold voltage. These thermal fluctuations introduce additional noise components and reliability concerns, particularly under high-performance operating conditions. The thermal resistance between the channel and substrate increases with fin height, exacerbating self-heating effects in tall fin designs optimized for drive current.

Power supply noise coupling has become increasingly problematic as supply voltages decrease while maintaining performance requirements. The reduced noise margins in advanced nodes make FinFETs more susceptible to power supply fluctuations, which can couple through the gate and manifest as output noise. This challenge is particularly acute in mixed-signal and RF applications where clean power supplies are essential for maintaining signal integrity.

Short-channel effects (SCEs) remain a primary challenge in current FinFET designs. As device dimensions continue to shrink below 10nm, quantum mechanical effects become increasingly prominent, leading to electron tunneling and gate leakage that contribute to noise generation. The fin geometry itself creates unique electrostatic conditions that complicate gate control optimization, with the fin height-to-width ratio directly influencing the effectiveness of gate control and subsequent noise characteristics.

Gate stack engineering presents another significant hurdle. The industry's transition from conventional SiO2 to high-k dielectric materials has improved gate capacitance but introduced interface traps and fixed charges that generate random telegraph noise (RTN) and 1/f noise. These noise sources are particularly problematic in analog and mixed-signal applications where signal integrity is paramount. Additionally, the three-dimensional nature of FinFETs creates non-uniform electric fields around the fin structure, resulting in variability in threshold voltage and transconductance.

Process-induced variability further complicates gate control optimization. Manufacturing inconsistencies in fin width, height, and shape directly impact the gate's ability to control channel conductivity uniformly. Line edge roughness (LER) and line width roughness (LWR) introduce random variations in the channel dimensions, leading to device-to-device variability that manifests as noise in circuit operation. These manufacturing challenges become exponentially more difficult as dimensions shrink toward 5nm and below.

Self-heating effects represent an emerging challenge in advanced FinFET designs. The confined geometry of the fin structure impedes efficient heat dissipation, causing localized temperature increases that alter carrier mobility and threshold voltage. These thermal fluctuations introduce additional noise components and reliability concerns, particularly under high-performance operating conditions. The thermal resistance between the channel and substrate increases with fin height, exacerbating self-heating effects in tall fin designs optimized for drive current.

Power supply noise coupling has become increasingly problematic as supply voltages decrease while maintaining performance requirements. The reduced noise margins in advanced nodes make FinFETs more susceptible to power supply fluctuations, which can couple through the gate and manifest as output noise. This challenge is particularly acute in mixed-signal and RF applications where clean power supplies are essential for maintaining signal integrity.

Current Gate Control Optimization Techniques

01 Noise reduction techniques in FinFET structures

Various structural modifications can be implemented in FinFET designs to reduce noise. These include optimizing the fin geometry, gate stack engineering, and implementing specialized doping profiles. By carefully designing these elements, the noise characteristics of FinFETs can be significantly improved, leading to better performance in sensitive applications.- Noise reduction techniques in FinFET structures: Various structural modifications can be implemented in FinFET designs to reduce noise. These include optimizing the fin geometry, gate stack engineering, and implementing specialized doping profiles. By carefully designing these elements, the noise characteristics of FinFETs can be significantly improved, leading to better performance in sensitive applications.

- Low-frequency noise characterization in FinFETs: Low-frequency noise, including flicker noise (1/f noise), is a critical parameter in FinFET performance. Characterization methods involve measuring noise at various operating conditions and analyzing the impact of channel dimensions, gate dielectric interfaces, and trap densities. Understanding these noise mechanisms helps in developing more reliable FinFET devices for analog and mixed-signal applications.

- Thermal noise management in FinFET devices: Thermal noise in FinFETs is addressed through improved heat dissipation designs and material selection. Techniques include incorporating heat sinks, using high thermal conductivity materials, and optimizing device layout to minimize hot spots. These approaches help maintain stable device performance and reduce noise generated by thermal fluctuations.

- Simulation and modeling of FinFET noise characteristics: Advanced simulation tools and models are developed to predict and analyze noise behavior in FinFET structures. These computational approaches enable designers to evaluate noise performance before fabrication, optimize device parameters, and explore new architectures. Compact models specifically tailored for FinFET noise characteristics help in circuit-level simulations for system performance evaluation.

- Circuit-level techniques for FinFET noise mitigation: Various circuit design approaches are employed to mitigate noise effects in FinFET-based systems. These include differential signaling, chopper stabilization, correlated double sampling, and specialized layout techniques. By implementing these circuit-level strategies, designers can achieve improved signal-to-noise ratio and overall system performance even with inherent device noise.

02 Low-frequency noise characterization and modeling in FinFETs

Low-frequency noise, including flicker noise and random telegraph noise, is a critical concern in FinFET devices. Advanced characterization methods and modeling techniques have been developed to understand and predict noise behavior in these transistors. These models account for the unique three-dimensional structure of FinFETs and help in designing circuits with improved noise performance.Expand Specific Solutions03 Circuit design techniques for FinFET noise mitigation

Specialized circuit design approaches can be employed to mitigate noise effects in FinFET-based systems. These include differential pair configurations, chopper stabilization techniques, and noise-aware layout strategies. By implementing these circuit-level solutions, designers can achieve better signal-to-noise ratios in sensitive analog and mixed-signal applications using FinFET technology.Expand Specific Solutions04 Multi-fin and multi-gate approaches for noise optimization

Utilizing multiple fins and gates in FinFET designs can help in reducing noise. These approaches provide better electrostatic control and can average out noise contributions from individual channels. Advanced multi-fin configurations with optimized spacing and dimensions have been shown to significantly improve noise performance while maintaining or enhancing other electrical characteristics.Expand Specific Solutions05 Process variation and its impact on FinFET noise

Manufacturing process variations can significantly affect noise characteristics in FinFET devices. Techniques to mitigate these effects include statistical modeling, corner analysis, and adaptive circuit designs. Understanding and accounting for process-induced noise variations is crucial for achieving consistent performance in high-volume FinFET production for noise-sensitive applications.Expand Specific Solutions

Leading Semiconductor Companies in FinFET Technology

The FinFET gate control noise optimization landscape is currently in a mature growth phase, with the market expanding steadily as semiconductor manufacturers seek to enhance performance in advanced nodes. Key players like TSMC, GlobalFoundries, and Samsung lead technological innovation, with TSMC demonstrating particular expertise in advanced FinFET architectures. IBM and Synopsys contribute significant research in noise reduction techniques, while companies like AMD and NXP focus on application-specific optimizations. The competitive environment is characterized by a balance between established foundries with production capabilities and specialized design firms offering noise mitigation solutions. As device dimensions continue to shrink below 5nm, collaborative research between semiconductor manufacturers and EDA companies is becoming increasingly critical to address quantum effects and thermal noise challenges.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has developed a multi-pronged approach to optimize FinFET gate control for noise reduction. Their technology employs advanced high-k metal gate (HKMG) materials with precisely engineered work functions to optimize threshold voltage and reduce variability. TSMC's N5 and N3 process nodes implement a refined gate-last process that enables better electrostatic control and minimizes random telegraph noise (RTN). The company has pioneered the use of stress engineering techniques to enhance carrier mobility while simultaneously reducing channel noise through careful management of interface states. Their solution incorporates specialized gate stack treatments that minimize border traps and fixed charges at the gate dielectric interface, significantly reducing flicker noise (1/f noise) which is critical for analog and RF applications. Additionally, TSMC has implemented advanced gate profile optimization using atomic layer deposition (ALD) techniques to ensure uniform gate coverage around the fin structure, preventing localized electric field concentrations that can contribute to noise generation.

Strengths: Industry-leading process control capabilities with sub-nanometer precision in gate formation; comprehensive noise characterization infrastructure allowing for rapid optimization cycles; extensive experience scaling FinFET technology across multiple nodes. Weaknesses: Higher manufacturing costs compared to planar technologies; requires extremely sophisticated equipment and clean room environments; some solutions may be difficult to implement in less advanced fabs.

International Business Machines Corp.

Technical Solution: IBM has pioneered several innovative approaches to FinFET gate control optimization for noise reduction. Their technology incorporates advanced materials science research, utilizing precisely engineered high-k dielectric stacks with controlled oxygen vacancy concentrations to minimize trap-assisted noise mechanisms. IBM's solution features a multi-layer gate metallization process that creates an optimized work function while reducing metal grain boundary effects that contribute to random telegraph noise. The company has developed sophisticated fin sidewall treatment techniques that passivate dangling bonds and reduce interface state density, directly addressing a primary source of flicker noise in FinFET devices. IBM's approach also includes specialized gate-last integration schemes that minimize process-induced damage to the channel region, preserving carrier mobility while reducing scattering-related noise sources. Additionally, their technology implements advanced strain engineering methods that not only enhance performance but also contribute to noise reduction by optimizing carrier transport characteristics and reducing variability in threshold voltage across the device population.

Strengths: Exceptional research capabilities with fundamental understanding of noise physics; strong intellectual property portfolio in advanced transistor structures; history of semiconductor innovation and industry collaboration. Weaknesses: Limited commercial manufacturing capacity compared to dedicated foundries; focus has shifted more toward research and development rather than high-volume manufacturing; some solutions may be too complex for cost-effective implementation.

Key Innovations in Noise Reduction Patents

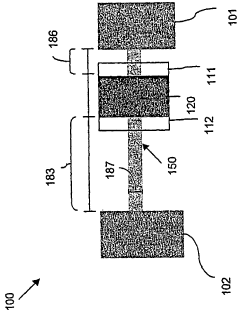

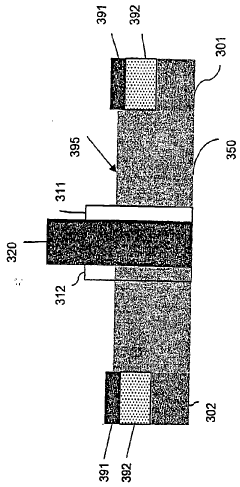

Fin-type field effect transistor

PatentActiveEP1920467A4

Innovation

- Asymmetric FinFET configuration that decreases fin resistance between gate and source region while reducing capacitance between gate and drain region to optimize drive current.

- Ballasting technique for FinFETs that optimizes resistance in the fin between gate and source/drain regions through increased fin length, blocked source/drain implants, and prevented silicide formation on the fin top surface.

- Novel manufacturing methods specifically designed for creating asymmetric FinFET structures that can operate reliably at predetermined maximum voltages.

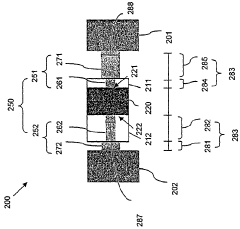

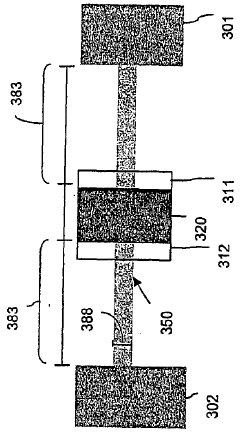

FIN-type field effect transistor

PatentWO2007019023A2

Innovation

- The FinFET structure is configured asymmetrically to decrease resistance between the gate and the source region and increase resistance between the gate and the drain region, and ballasted by adjusting fin dimensions and dopant concentrations to prevent premature run-away, allowing operation at a predetermined maximum voltage.

Thermal Management in Advanced FinFET Designs

Thermal management has become a critical challenge in advanced FinFET designs as transistor dimensions continue to shrink while power densities increase. The three-dimensional structure of FinFETs, while beneficial for gate control and leakage reduction, creates unique thermal challenges that must be addressed to ensure optimal device performance and reliability.

Heat generation in FinFETs occurs primarily in the channel region during device operation, with the fin structure limiting efficient heat dissipation pathways. This thermal bottleneck effect is particularly pronounced in multi-fin configurations where fin-to-fin thermal coupling can lead to significant temperature gradients across the device. Recent thermal imaging studies have shown that temperature variations of up to 15°C can exist across densely packed FinFET arrays under high-performance operating conditions.

The impact of elevated temperatures on FinFET performance manifests in several ways. Carrier mobility degradation reduces drive current capabilities, while increased leakage currents contribute to higher static power consumption. More concerning is the acceleration of various reliability degradation mechanisms, including bias temperature instability (BTI), hot carrier injection (HCI), and time-dependent dielectric breakdown (TDDB), all of which are exponentially dependent on temperature.

Advanced thermal management strategies for FinFETs operate at multiple levels of the design hierarchy. At the device level, optimization of fin geometry and spacing can enhance thermal conductivity pathways. Materials engineering approaches include the integration of high thermal conductivity materials such as diamond-like carbon or graphene-based composites as heat spreaders. Some research teams have demonstrated up to 30% improvement in heat dissipation using these advanced materials.

At the circuit and system levels, dynamic thermal management techniques have proven effective. These include temperature-aware placement and routing algorithms that distribute heat-generating elements to minimize hotspots. Adaptive frequency scaling and workload migration strategies respond to thermal sensors embedded throughout the chip, allowing real-time adjustment of computational loads based on thermal conditions.

Emerging cooling technologies specifically tailored for FinFET architectures include microfluidic cooling channels integrated directly into the silicon substrate. These solutions have demonstrated the ability to maintain temperature variations below 5°C across the chip even under extreme computational loads. Another promising approach involves phase-change materials embedded in the packaging that absorb heat during high-activity periods and release it gradually during idle times, effectively dampening thermal transients.

The optimization of gate control in FinFETs is intrinsically linked to thermal management, as improved electrostatic control reduces power dissipation and consequently thermal load. Future FinFET designs will likely incorporate thermal considerations from the earliest stages of development, with thermal-aware design automation tools playing an increasingly important role in the optimization process.

Heat generation in FinFETs occurs primarily in the channel region during device operation, with the fin structure limiting efficient heat dissipation pathways. This thermal bottleneck effect is particularly pronounced in multi-fin configurations where fin-to-fin thermal coupling can lead to significant temperature gradients across the device. Recent thermal imaging studies have shown that temperature variations of up to 15°C can exist across densely packed FinFET arrays under high-performance operating conditions.

The impact of elevated temperatures on FinFET performance manifests in several ways. Carrier mobility degradation reduces drive current capabilities, while increased leakage currents contribute to higher static power consumption. More concerning is the acceleration of various reliability degradation mechanisms, including bias temperature instability (BTI), hot carrier injection (HCI), and time-dependent dielectric breakdown (TDDB), all of which are exponentially dependent on temperature.

Advanced thermal management strategies for FinFETs operate at multiple levels of the design hierarchy. At the device level, optimization of fin geometry and spacing can enhance thermal conductivity pathways. Materials engineering approaches include the integration of high thermal conductivity materials such as diamond-like carbon or graphene-based composites as heat spreaders. Some research teams have demonstrated up to 30% improvement in heat dissipation using these advanced materials.

At the circuit and system levels, dynamic thermal management techniques have proven effective. These include temperature-aware placement and routing algorithms that distribute heat-generating elements to minimize hotspots. Adaptive frequency scaling and workload migration strategies respond to thermal sensors embedded throughout the chip, allowing real-time adjustment of computational loads based on thermal conditions.

Emerging cooling technologies specifically tailored for FinFET architectures include microfluidic cooling channels integrated directly into the silicon substrate. These solutions have demonstrated the ability to maintain temperature variations below 5°C across the chip even under extreme computational loads. Another promising approach involves phase-change materials embedded in the packaging that absorb heat during high-activity periods and release it gradually during idle times, effectively dampening thermal transients.

The optimization of gate control in FinFETs is intrinsically linked to thermal management, as improved electrostatic control reduces power dissipation and consequently thermal load. Future FinFET designs will likely incorporate thermal considerations from the earliest stages of development, with thermal-aware design automation tools playing an increasingly important role in the optimization process.

Power Efficiency vs. Noise Performance Trade-offs

The optimization of FinFET gate control for noise minimization presents a fundamental trade-off between power efficiency and noise performance that designers must carefully navigate. As transistor dimensions continue to shrink, the power consumption becomes increasingly critical while noise susceptibility grows more pronounced. This inherent tension requires sophisticated balancing strategies to achieve optimal circuit performance.

Power efficiency in FinFET designs is primarily achieved through voltage scaling and reduced leakage current. However, lower operating voltages directly impact the signal-to-noise ratio, making circuits more vulnerable to various noise sources including thermal noise, flicker noise, and random telegraph noise (RTN). The relationship between power consumption and noise follows an inverse correlation where noise performance typically degrades as power constraints become more stringent.

Multi-gate architectures in FinFETs offer superior electrostatic control compared to planar technologies, which can partially mitigate this trade-off. By optimizing the fin height-to-width ratio and gate length, designers can achieve better subthreshold swing characteristics while maintaining acceptable noise margins. Recent research indicates that a fin height-to-width ratio between 2.5:1 and 3:1 provides an optimal balance point for many applications.

Advanced gate stack engineering represents another approach to addressing this challenge. High-k metal gate (HKMG) materials can reduce gate leakage while maintaining strong channel control, though their implementation introduces additional interface traps that can contribute to noise. Careful selection of gate dielectric materials and deposition techniques can minimize these adverse effects while preserving power efficiency benefits.

Dynamic voltage and frequency scaling (DVFS) techniques offer a runtime solution to the power-noise trade-off. By adaptively adjusting operating parameters based on performance requirements, systems can operate in high-performance modes with better noise immunity when necessary, while defaulting to power-saving configurations during less demanding operations. This approach requires sophisticated control algorithms and accurate noise monitoring capabilities.

Circuit-level techniques such as differential signaling and common-mode rejection can also help maintain signal integrity in low-power environments. These approaches effectively increase noise margins without significantly increasing power consumption, though they typically require additional transistors and more complex layouts.

The industry trend shows movement toward heterogeneous integration approaches, where different transistor types optimized for either power efficiency or noise performance are combined on the same die. This strategy allows system designers to allocate noise-sensitive functions to low-noise transistors while using power-optimized devices for less critical operations, achieving better overall system efficiency.

Power efficiency in FinFET designs is primarily achieved through voltage scaling and reduced leakage current. However, lower operating voltages directly impact the signal-to-noise ratio, making circuits more vulnerable to various noise sources including thermal noise, flicker noise, and random telegraph noise (RTN). The relationship between power consumption and noise follows an inverse correlation where noise performance typically degrades as power constraints become more stringent.

Multi-gate architectures in FinFETs offer superior electrostatic control compared to planar technologies, which can partially mitigate this trade-off. By optimizing the fin height-to-width ratio and gate length, designers can achieve better subthreshold swing characteristics while maintaining acceptable noise margins. Recent research indicates that a fin height-to-width ratio between 2.5:1 and 3:1 provides an optimal balance point for many applications.

Advanced gate stack engineering represents another approach to addressing this challenge. High-k metal gate (HKMG) materials can reduce gate leakage while maintaining strong channel control, though their implementation introduces additional interface traps that can contribute to noise. Careful selection of gate dielectric materials and deposition techniques can minimize these adverse effects while preserving power efficiency benefits.

Dynamic voltage and frequency scaling (DVFS) techniques offer a runtime solution to the power-noise trade-off. By adaptively adjusting operating parameters based on performance requirements, systems can operate in high-performance modes with better noise immunity when necessary, while defaulting to power-saving configurations during less demanding operations. This approach requires sophisticated control algorithms and accurate noise monitoring capabilities.

Circuit-level techniques such as differential signaling and common-mode rejection can also help maintain signal integrity in low-power environments. These approaches effectively increase noise margins without significantly increasing power consumption, though they typically require additional transistors and more complex layouts.

The industry trend shows movement toward heterogeneous integration approaches, where different transistor types optimized for either power efficiency or noise performance are combined on the same die. This strategy allows system designers to allocate noise-sensitive functions to low-noise transistors while using power-optimized devices for less critical operations, achieving better overall system efficiency.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!