Signal Integrity vs Interface Standards

MAR 26, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Signal Integrity and Interface Standards Background and Objectives

Signal integrity and interface standards represent two fundamental yet interconnected pillars of modern electronic system design, each addressing critical aspects of reliable data transmission and system interoperability. Signal integrity focuses on maintaining the quality and fidelity of electrical signals as they propagate through various transmission media, while interface standards establish the protocols, specifications, and compatibility requirements that enable seamless communication between different system components.

The evolution of electronic systems has witnessed an exponential increase in operating frequencies, data rates, and system complexity, making the relationship between signal integrity and interface standards increasingly critical. As digital systems transition from megahertz to gigahertz frequencies and beyond, traditional design approaches that treated these domains separately have proven inadequate for addressing contemporary challenges.

Signal integrity encompasses the preservation of signal quality throughout the entire signal path, addressing phenomena such as reflection, crosstalk, electromagnetic interference, power delivery noise, and timing variations. These factors directly impact system performance, reliability, and the ability to meet stringent interface standard requirements. Conversely, interface standards define the electrical, mechanical, and protocol specifications that govern how signals should behave at connection points between different system elements.

The primary objective of integrating signal integrity considerations with interface standards compliance is to achieve optimal system performance while maintaining interoperability across diverse platforms and vendors. This integration aims to minimize signal degradation, reduce electromagnetic emissions, ensure timing closure, and maximize data throughput within the constraints defined by relevant industry standards.

Contemporary electronic systems face unprecedented challenges in balancing these requirements, particularly as interface standards continue to evolve toward higher speeds and lower power consumption. The objective extends beyond mere compliance to encompass predictive design methodologies that anticipate future standard requirements while maintaining robust signal integrity performance.

The strategic importance of this technological convergence lies in enabling next-generation applications including artificial intelligence accelerators, autonomous vehicles, 5G communications infrastructure, and high-performance computing systems. These applications demand unprecedented levels of signal fidelity while adhering to increasingly stringent interface specifications, making the optimization of both domains simultaneously a critical competitive advantage.

The evolution of electronic systems has witnessed an exponential increase in operating frequencies, data rates, and system complexity, making the relationship between signal integrity and interface standards increasingly critical. As digital systems transition from megahertz to gigahertz frequencies and beyond, traditional design approaches that treated these domains separately have proven inadequate for addressing contemporary challenges.

Signal integrity encompasses the preservation of signal quality throughout the entire signal path, addressing phenomena such as reflection, crosstalk, electromagnetic interference, power delivery noise, and timing variations. These factors directly impact system performance, reliability, and the ability to meet stringent interface standard requirements. Conversely, interface standards define the electrical, mechanical, and protocol specifications that govern how signals should behave at connection points between different system elements.

The primary objective of integrating signal integrity considerations with interface standards compliance is to achieve optimal system performance while maintaining interoperability across diverse platforms and vendors. This integration aims to minimize signal degradation, reduce electromagnetic emissions, ensure timing closure, and maximize data throughput within the constraints defined by relevant industry standards.

Contemporary electronic systems face unprecedented challenges in balancing these requirements, particularly as interface standards continue to evolve toward higher speeds and lower power consumption. The objective extends beyond mere compliance to encompass predictive design methodologies that anticipate future standard requirements while maintaining robust signal integrity performance.

The strategic importance of this technological convergence lies in enabling next-generation applications including artificial intelligence accelerators, autonomous vehicles, 5G communications infrastructure, and high-performance computing systems. These applications demand unprecedented levels of signal fidelity while adhering to increasingly stringent interface specifications, making the optimization of both domains simultaneously a critical competitive advantage.

Market Demand for High-Speed Interface Solutions

The global demand for high-speed interface solutions has experienced unprecedented growth driven by the exponential increase in data generation and transmission requirements across multiple industries. Data centers, telecommunications infrastructure, and consumer electronics sectors are pushing the boundaries of traditional interface capabilities, creating substantial market opportunities for advanced signal integrity solutions.

Enterprise data centers represent the largest segment of demand, where the transition to cloud computing and artificial intelligence workloads necessitates interfaces capable of handling massive data throughput with minimal latency. The proliferation of high-performance computing applications, machine learning accelerators, and distributed storage systems has created an urgent need for interface standards that can maintain signal integrity at increasingly higher frequencies and data rates.

The telecommunications sector is experiencing a parallel transformation with the global rollout of 5G networks and the early development of 6G technologies. These next-generation wireless systems require backhaul and fronthaul connections that can support dramatically increased bandwidth while maintaining strict timing and synchronization requirements. The challenge of preserving signal quality across longer distances and through more complex network topologies has intensified the focus on advanced interface design methodologies.

Consumer electronics markets are simultaneously driving demand through the adoption of high-resolution displays, virtual reality systems, and gaming platforms that require real-time processing of large data streams. The automotive industry has emerged as another significant demand driver, with autonomous vehicles and advanced driver assistance systems requiring reliable high-speed communication between sensors, processors, and control units under challenging environmental conditions.

The semiconductor industry itself has become a major consumer of high-speed interface solutions as chip-to-chip communication speeds continue to escalate. Advanced packaging technologies, including chiplet architectures and heterogeneous integration approaches, demand interface standards that can maintain signal integrity across diverse materials and form factors while supporting the economic benefits of modular design approaches.

Market dynamics indicate that traditional interface standards are reaching fundamental physical limitations, creating opportunities for innovative solutions that address the growing gap between required performance and achievable signal integrity. The convergence of multiple high-growth application areas suggests sustained long-term demand for breakthrough interface technologies.

Enterprise data centers represent the largest segment of demand, where the transition to cloud computing and artificial intelligence workloads necessitates interfaces capable of handling massive data throughput with minimal latency. The proliferation of high-performance computing applications, machine learning accelerators, and distributed storage systems has created an urgent need for interface standards that can maintain signal integrity at increasingly higher frequencies and data rates.

The telecommunications sector is experiencing a parallel transformation with the global rollout of 5G networks and the early development of 6G technologies. These next-generation wireless systems require backhaul and fronthaul connections that can support dramatically increased bandwidth while maintaining strict timing and synchronization requirements. The challenge of preserving signal quality across longer distances and through more complex network topologies has intensified the focus on advanced interface design methodologies.

Consumer electronics markets are simultaneously driving demand through the adoption of high-resolution displays, virtual reality systems, and gaming platforms that require real-time processing of large data streams. The automotive industry has emerged as another significant demand driver, with autonomous vehicles and advanced driver assistance systems requiring reliable high-speed communication between sensors, processors, and control units under challenging environmental conditions.

The semiconductor industry itself has become a major consumer of high-speed interface solutions as chip-to-chip communication speeds continue to escalate. Advanced packaging technologies, including chiplet architectures and heterogeneous integration approaches, demand interface standards that can maintain signal integrity across diverse materials and form factors while supporting the economic benefits of modular design approaches.

Market dynamics indicate that traditional interface standards are reaching fundamental physical limitations, creating opportunities for innovative solutions that address the growing gap between required performance and achievable signal integrity. The convergence of multiple high-growth application areas suggests sustained long-term demand for breakthrough interface technologies.

Current State and Challenges in SI and Interface Design

The current landscape of signal integrity and interface design presents a complex interplay between evolving performance demands and standardization requirements. Modern electronic systems operate at increasingly higher frequencies, with data rates reaching beyond 100 Gbps in advanced applications, creating unprecedented challenges for maintaining signal quality while adhering to established interface protocols.

Signal integrity issues have become more pronounced as semiconductor geometries shrink and operating frequencies increase. Crosstalk, power delivery noise, and electromagnetic interference now significantly impact system performance at frequencies where traditional design approaches prove inadequate. Simultaneously, interface standards must evolve to accommodate these higher performance requirements while maintaining backward compatibility and interoperability across diverse platforms.

The geographical distribution of expertise reveals distinct regional strengths. North American companies lead in high-speed digital design methodologies and advanced simulation tools, while Asian manufacturers excel in high-volume production techniques and cost-effective implementation strategies. European organizations contribute significantly to automotive and industrial interface standards, particularly in harsh environment applications.

Current technical constraints center on the fundamental physics limitations of copper interconnects and the increasing complexity of multi-gigabit interface implementations. Power consumption has emerged as a critical bottleneck, with signal conditioning circuits consuming substantial energy to maintain acceptable bit error rates. The challenge intensifies when considering the need for robust operation across temperature variations and manufacturing tolerances.

Interface standardization bodies face the ongoing challenge of balancing innovation speed with stability requirements. Standards like PCIe, USB, and Ethernet must evolve rapidly enough to support emerging applications while providing sufficient specification maturity for reliable product development cycles. This creates tension between early adopters seeking cutting-edge performance and mainstream manufacturers requiring proven, stable specifications.

Manufacturing variability presents another significant challenge, as tighter signal integrity margins reduce tolerance for process variations. Advanced packaging technologies, including chiplet architectures and 3D integration, introduce new signal integrity considerations that existing interface standards struggle to address comprehensively.

The convergence of artificial intelligence workloads and edge computing applications demands interface solutions that can handle both high-bandwidth data movement and low-latency control signaling, creating new requirements that challenge traditional interface design paradigms and standardization approaches.

Signal integrity issues have become more pronounced as semiconductor geometries shrink and operating frequencies increase. Crosstalk, power delivery noise, and electromagnetic interference now significantly impact system performance at frequencies where traditional design approaches prove inadequate. Simultaneously, interface standards must evolve to accommodate these higher performance requirements while maintaining backward compatibility and interoperability across diverse platforms.

The geographical distribution of expertise reveals distinct regional strengths. North American companies lead in high-speed digital design methodologies and advanced simulation tools, while Asian manufacturers excel in high-volume production techniques and cost-effective implementation strategies. European organizations contribute significantly to automotive and industrial interface standards, particularly in harsh environment applications.

Current technical constraints center on the fundamental physics limitations of copper interconnects and the increasing complexity of multi-gigabit interface implementations. Power consumption has emerged as a critical bottleneck, with signal conditioning circuits consuming substantial energy to maintain acceptable bit error rates. The challenge intensifies when considering the need for robust operation across temperature variations and manufacturing tolerances.

Interface standardization bodies face the ongoing challenge of balancing innovation speed with stability requirements. Standards like PCIe, USB, and Ethernet must evolve rapidly enough to support emerging applications while providing sufficient specification maturity for reliable product development cycles. This creates tension between early adopters seeking cutting-edge performance and mainstream manufacturers requiring proven, stable specifications.

Manufacturing variability presents another significant challenge, as tighter signal integrity margins reduce tolerance for process variations. Advanced packaging technologies, including chiplet architectures and 3D integration, introduce new signal integrity considerations that existing interface standards struggle to address comprehensively.

The convergence of artificial intelligence workloads and edge computing applications demands interface solutions that can handle both high-bandwidth data movement and low-latency control signaling, creating new requirements that challenge traditional interface design paradigms and standardization approaches.

Current SI Solutions for Interface Standards Compliance

01 Signal integrity testing and measurement techniques

Various methods and systems are employed to test and measure signal integrity in electronic circuits and communication systems. These techniques involve analyzing signal quality, detecting distortions, measuring timing parameters, and evaluating transmission characteristics. Advanced testing equipment and methodologies enable accurate assessment of signal degradation, jitter, crosstalk, and other integrity issues. Automated testing systems can perform comprehensive signal integrity analysis across multiple channels and interfaces to ensure compliance with performance specifications.- Signal integrity testing and measurement techniques: Various methods and systems are employed to test and measure signal integrity in electronic circuits and communication systems. These techniques involve analyzing signal quality, detecting distortions, measuring timing parameters, and evaluating transmission characteristics. Advanced testing equipment and methodologies enable accurate assessment of signal degradation, jitter, crosstalk, and other integrity issues. Automated testing systems can perform comprehensive signal integrity analysis across multiple channels and interfaces to ensure compliance with performance specifications.

- Impedance matching and termination circuits: Proper impedance matching and termination are critical for maintaining signal integrity in high-speed interfaces. Techniques include implementing termination resistors, adjustable impedance circuits, and adaptive matching networks to minimize signal reflections and ensure optimal power transfer. These solutions address impedance discontinuities at interface boundaries and along transmission lines. Various circuit topologies and control mechanisms enable dynamic adjustment of impedance characteristics to accommodate different operating conditions and interface standards.

- Differential signaling and noise reduction: Differential signaling techniques are widely used to improve signal integrity and reduce electromagnetic interference in high-speed data transmission. These methods involve transmitting signals as voltage differences between paired conductors, providing inherent noise immunity and common-mode rejection. Circuit designs incorporate differential drivers, receivers, and balanced transmission lines to maintain signal quality. Additional noise reduction techniques include shielding, filtering, and ground plane optimization to minimize crosstalk and external interference effects.

- Interface protocol compliance and standardization: Ensuring compliance with established interface standards is essential for interoperability and reliable communication between devices. This involves implementing protocol-specific electrical characteristics, timing requirements, and signaling conventions as defined by industry standards. Compliance testing verifies adherence to specifications for voltage levels, rise/fall times, setup and hold times, and other critical parameters. Design methodologies incorporate standard-compliant transceivers, controllers, and physical layer implementations to guarantee compatibility across different manufacturers and system configurations.

- Equalization and signal conditioning techniques: Equalization and signal conditioning methods compensate for signal degradation caused by transmission medium characteristics and frequency-dependent losses. These techniques include pre-emphasis, de-emphasis, continuous-time linear equalization, and decision feedback equalization to restore signal quality at the receiver. Adaptive equalization algorithms automatically adjust compensation parameters based on channel conditions and received signal characteristics. Additional conditioning methods involve clock recovery, data retiming, and amplitude restoration to ensure reliable data detection and minimize bit error rates.

02 Impedance matching and termination circuits

Proper impedance matching and termination are critical for maintaining signal integrity in high-speed interfaces. Techniques include implementing termination resistors, active termination circuits, and adaptive impedance control mechanisms. These solutions minimize signal reflections, reduce ringing, and improve signal quality at transmission line endpoints. Various circuit topologies and control methods enable dynamic adjustment of impedance characteristics to match different interface standards and operating conditions.Expand Specific Solutions03 Differential signaling and noise reduction

Differential signaling techniques are widely used to enhance signal integrity and reduce electromagnetic interference in high-speed data transmission. These methods involve transmitting signals as voltage differences between paired conductors, providing improved noise immunity and common-mode rejection. Circuit designs incorporate differential drivers, receivers, and balanced transmission lines to maintain signal quality. Additional noise reduction techniques include shielding, filtering, and ground plane optimization to minimize crosstalk and external interference.Expand Specific Solutions04 Interface protocol compliance and standardization

Ensuring compliance with established interface standards is essential for interoperability and reliable communication between devices. This involves implementing specific electrical characteristics, timing requirements, and protocol specifications defined by industry standards. Compliance testing verifies that devices meet voltage levels, rise/fall times, setup and hold times, and other parameters specified by standards organizations. Design methodologies incorporate standard-compliant transceivers, controllers, and physical layer implementations to guarantee compatibility across different manufacturers and platforms.Expand Specific Solutions05 Equalization and signal conditioning techniques

Equalization and signal conditioning methods are employed to compensate for signal degradation in high-speed transmission channels. These techniques include pre-emphasis, de-emphasis, continuous-time linear equalization, and decision feedback equalization. Adaptive algorithms adjust equalization parameters based on channel characteristics to optimize signal quality. Signal conditioning circuits also incorporate amplification, filtering, and waveform shaping to restore signal integrity and extend transmission distances while maintaining data accuracy.Expand Specific Solutions

Key Players in Interface and SI Solution Industry

The signal integrity versus interface standards landscape represents a mature yet rapidly evolving market driven by increasing data rates and connectivity demands across computing, telecommunications, and automotive sectors. The industry demonstrates strong technical maturity with established players like Intel, NVIDIA, and Qualcomm leading processor and GPU innovations, while Rambus specializes in high-speed memory interfaces. Asian manufacturers including TSMC, MediaTek, and Huawei contribute significant foundry and system-level expertise. The competitive environment spans from semiconductor giants like Intel and NVIDIA developing cutting-edge interface standards, to specialized companies like Rambus and Lattice Semiconductor focusing on signal integrity solutions, indicating a multi-billion dollar market with diverse technological approaches addressing the fundamental challenge of maintaining signal quality while advancing interface performance standards.

Intel Corp.

Technical Solution: Intel has developed comprehensive signal integrity solutions including advanced package technologies like EMIB (Embedded Multi-die Interconnect Bridge) and Foveros 3D packaging to address high-speed interface challenges. Their approach integrates sophisticated modeling tools and design methodologies to ensure signal quality across multiple interface standards including PCIe, DDR, and CXL. Intel's signal integrity framework encompasses pre-silicon simulation, post-silicon validation, and real-time monitoring capabilities to maintain interface compliance while optimizing performance across their processor and chipset portfolio.

Strengths: Industry-leading packaging technology and comprehensive SI tools. Weaknesses: High complexity and cost for implementation.

Rambus, Inc.

Technical Solution: Rambus specializes in high-speed interface IP and memory solutions with advanced signal integrity technologies. Their approach focuses on developing proprietary interface standards and signal conditioning techniques that enable data rates exceeding traditional limitations. Rambus implements sophisticated equalization, clock data recovery, and adaptive signal processing to maintain signal integrity across various interface protocols including their own innovations and industry standards like GDDR and HBM. Their solutions integrate hardware-based signal integrity features with software-defined optimization algorithms.

Strengths: Specialized expertise in high-speed interfaces and memory technologies. Weaknesses: Limited to specific market segments and proprietary solutions.

Core Innovations in SI-Interface Co-design Technologies

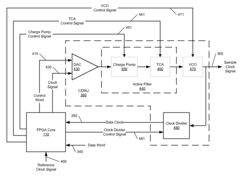

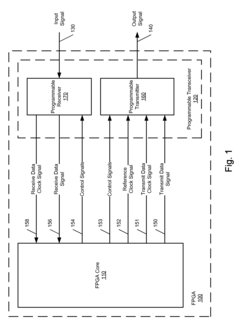

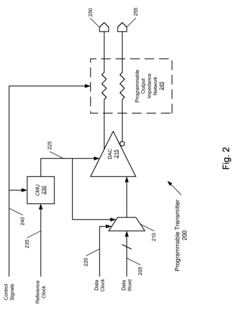

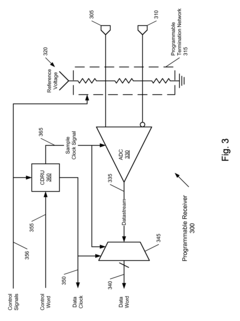

Method and system for programmable input/output transceiver wherein transceiver in configurable to support a plurality of interface standards

PatentInactiveUS7685340B1

Innovation

- A programmable transceiver system integrated with a field-programmable gate array (FPGA) fabric that can be configured to support multiple interface standards, including USB, IEEE 1394, and Ethernet, by using flexible analog front ends, programmable impedance networks, clock generation and recovery units, and digital signal processing techniques.

Optimizing transmitter settings for in-band electrical interface between host device and optical module using out-of-band electrical interface

PatentPendingUS20240323064A1

Innovation

- The method involves systematically testing different FIR filter settings at the host transmitter, measuring signal integrity with the optical module, and configuring the best setting for optimal signal integrity, utilizing Auto-Negotiation and Link Training protocols and CMIS for module configuration and control.

Industry Standards and Compliance Requirements

Signal integrity and interface standards operate within a comprehensive framework of industry standards and compliance requirements that ensure interoperability, reliability, and performance across diverse electronic systems. These regulatory frameworks establish the foundation for consistent implementation of high-speed digital interfaces while maintaining signal quality standards across different manufacturers and applications.

The Institute of Electrical and Electronics Engineers (IEEE) serves as a primary standards body, developing critical specifications such as IEEE 802.3 for Ethernet communications and IEEE 1394 for high-speed serial bus interfaces. These standards define electrical characteristics, timing requirements, and signal integrity parameters that must be maintained across all compliant implementations. Additionally, the Joint Electron Device Engineering Council (JEDEC) establishes memory interface standards including DDR, LPDDR, and emerging memory technologies, specifying voltage levels, timing margins, and signal integrity requirements.

International Electrotechnical Commission (IEC) standards provide global harmonization for electronic interface specifications, while regional bodies like the Federal Communications Commission (FCC) in the United States and the European Telecommunications Standards Institute (ETSI) establish electromagnetic compatibility and interference requirements. These regulations directly impact signal integrity design by mandating specific emission limits and immunity thresholds that influence circuit topology and shielding strategies.

Compliance testing requirements encompass both pre-compliance verification during development phases and formal certification processes. Eye diagram analysis, jitter measurements, and bit error rate testing form core compliance methodologies, with specific test conditions and acceptance criteria defined within each standard. Advanced measurement techniques including time domain reflectometry and vector network analysis are mandated for characterizing transmission line behavior and impedance matching.

Emerging standards such as PCIe 6.0, USB4, and DDR5 introduce increasingly stringent signal integrity requirements, demanding enhanced design methodologies and measurement capabilities. These evolving specifications require continuous adaptation of compliance frameworks to address higher data rates, lower voltage swings, and more complex modulation schemes while maintaining backward compatibility with existing interface ecosystems.

The Institute of Electrical and Electronics Engineers (IEEE) serves as a primary standards body, developing critical specifications such as IEEE 802.3 for Ethernet communications and IEEE 1394 for high-speed serial bus interfaces. These standards define electrical characteristics, timing requirements, and signal integrity parameters that must be maintained across all compliant implementations. Additionally, the Joint Electron Device Engineering Council (JEDEC) establishes memory interface standards including DDR, LPDDR, and emerging memory technologies, specifying voltage levels, timing margins, and signal integrity requirements.

International Electrotechnical Commission (IEC) standards provide global harmonization for electronic interface specifications, while regional bodies like the Federal Communications Commission (FCC) in the United States and the European Telecommunications Standards Institute (ETSI) establish electromagnetic compatibility and interference requirements. These regulations directly impact signal integrity design by mandating specific emission limits and immunity thresholds that influence circuit topology and shielding strategies.

Compliance testing requirements encompass both pre-compliance verification during development phases and formal certification processes. Eye diagram analysis, jitter measurements, and bit error rate testing form core compliance methodologies, with specific test conditions and acceptance criteria defined within each standard. Advanced measurement techniques including time domain reflectometry and vector network analysis are mandated for characterizing transmission line behavior and impedance matching.

Emerging standards such as PCIe 6.0, USB4, and DDR5 introduce increasingly stringent signal integrity requirements, demanding enhanced design methodologies and measurement capabilities. These evolving specifications require continuous adaptation of compliance frameworks to address higher data rates, lower voltage swings, and more complex modulation schemes while maintaining backward compatibility with existing interface ecosystems.

SI Testing and Validation Methodologies

Signal integrity testing and validation methodologies have evolved into sophisticated frameworks that ensure electronic systems meet both performance requirements and interface standard compliance. These methodologies encompass a comprehensive range of measurement techniques, simulation approaches, and validation protocols designed to characterize signal behavior across various operating conditions and interface specifications.

Time-domain reflectometry (TDR) and time-domain transmission (TDT) measurements form the foundation of SI validation, enabling engineers to identify impedance discontinuities, crosstalk effects, and transmission line characteristics. Vector network analyzers (VNAs) provide frequency-domain analysis capabilities, measuring S-parameters that quantify signal transmission and reflection properties across wide bandwidth ranges. These measurements are essential for validating compliance with interface standards such as PCIe, DDR, USB, and high-speed serial protocols.

Eye diagram analysis represents a critical validation methodology for digital signal assessment, providing visual representation of signal quality metrics including jitter, noise, and timing margins. Statistical eye measurements, combined with bit error rate testing, offer quantitative assessment of signal integrity performance against interface standard specifications. Advanced oscilloscopes with real-time eye diagram capabilities enable comprehensive characterization of signal degradation mechanisms.

Simulation-based validation methodologies leverage electromagnetic field solvers and circuit simulators to predict signal behavior before physical implementation. SPICE-based simulations, coupled with 3D electromagnetic modeling, provide accurate prediction of signal integrity effects including crosstalk, power delivery network interactions, and package-level parasitic effects. These simulation approaches enable early identification of potential compliance issues with interface standards.

Compliance testing methodologies specifically address interface standard requirements through standardized test procedures and measurement setups. Automated test equipment (ATE) systems provide repeatable validation of electrical parameters, timing specifications, and protocol compliance. Calibration standards and reference measurement techniques ensure measurement accuracy and traceability to international standards, enabling reliable assessment of signal integrity performance against interface specifications.

Time-domain reflectometry (TDR) and time-domain transmission (TDT) measurements form the foundation of SI validation, enabling engineers to identify impedance discontinuities, crosstalk effects, and transmission line characteristics. Vector network analyzers (VNAs) provide frequency-domain analysis capabilities, measuring S-parameters that quantify signal transmission and reflection properties across wide bandwidth ranges. These measurements are essential for validating compliance with interface standards such as PCIe, DDR, USB, and high-speed serial protocols.

Eye diagram analysis represents a critical validation methodology for digital signal assessment, providing visual representation of signal quality metrics including jitter, noise, and timing margins. Statistical eye measurements, combined with bit error rate testing, offer quantitative assessment of signal integrity performance against interface standard specifications. Advanced oscilloscopes with real-time eye diagram capabilities enable comprehensive characterization of signal degradation mechanisms.

Simulation-based validation methodologies leverage electromagnetic field solvers and circuit simulators to predict signal behavior before physical implementation. SPICE-based simulations, coupled with 3D electromagnetic modeling, provide accurate prediction of signal integrity effects including crosstalk, power delivery network interactions, and package-level parasitic effects. These simulation approaches enable early identification of potential compliance issues with interface standards.

Compliance testing methodologies specifically address interface standard requirements through standardized test procedures and measurement setups. Automated test equipment (ATE) systems provide repeatable validation of electrical parameters, timing specifications, and protocol compliance. Calibration standards and reference measurement techniques ensure measurement accuracy and traceability to international standards, enabling reliable assessment of signal integrity performance against interface specifications.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!