Achieving CMOS Battery Optimization in Expansive Data Processing Architectures

JUL 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

CMOS Battery Evolution

The evolution of CMOS battery technology in expansive data processing architectures has been marked by significant advancements over the past decades. Initially, CMOS batteries were primarily used to maintain basic system settings and real-time clock functions in computer systems. However, as data processing architectures became more complex and power-hungry, the role of CMOS batteries expanded to support critical functions in large-scale computing environments.

In the early stages, CMOS batteries were simple coin cell batteries with limited capacity and lifespan. These batteries were sufficient for maintaining BIOS settings and system time in personal computers but fell short in meeting the demands of enterprise-level data processing systems. As the scale and complexity of data processing architectures grew, so did the need for more robust and long-lasting CMOS battery solutions.

The mid-2000s saw a shift towards lithium-ion CMOS batteries, which offered higher energy density and longer lifespan compared to their predecessors. This transition was crucial in supporting the increasing power requirements of expanding data centers and high-performance computing systems. The improved capacity allowed for extended backup times and reduced the frequency of battery replacements, leading to enhanced system reliability and reduced maintenance costs.

Another significant development in CMOS battery evolution was the integration of smart charging and power management systems. These innovations enabled more efficient use of battery power and extended the overall lifespan of CMOS batteries in data processing environments. Advanced monitoring capabilities were introduced, allowing system administrators to track battery health and predict replacement needs proactively.

Recent years have witnessed the emergence of ultra-low-power CMOS designs, which have dramatically reduced the power consumption of memory cells and other critical components. This development has eased the burden on CMOS batteries, allowing for smaller form factors and even longer operational lifespans. Additionally, the integration of energy harvesting technologies has begun to supplement CMOS batteries in some cutting-edge systems, further extending their operational life and reducing reliance on traditional battery power.

The latest trend in CMOS battery evolution focuses on sustainability and environmental considerations. Manufacturers are now developing eco-friendly CMOS battery solutions that minimize the use of harmful materials and improve recyclability. This shift aligns with the growing emphasis on green computing and sustainable data center practices.

As data processing architectures continue to expand and evolve, CMOS battery technology is expected to advance further. Future developments may include the integration of solid-state battery technology, offering even higher energy density and improved safety. Additionally, research into novel materials and nanotechnology could lead to breakthroughs in CMOS battery performance and longevity, ensuring that these critical components can keep pace with the ever-growing demands of modern computing infrastructures.

In the early stages, CMOS batteries were simple coin cell batteries with limited capacity and lifespan. These batteries were sufficient for maintaining BIOS settings and system time in personal computers but fell short in meeting the demands of enterprise-level data processing systems. As the scale and complexity of data processing architectures grew, so did the need for more robust and long-lasting CMOS battery solutions.

The mid-2000s saw a shift towards lithium-ion CMOS batteries, which offered higher energy density and longer lifespan compared to their predecessors. This transition was crucial in supporting the increasing power requirements of expanding data centers and high-performance computing systems. The improved capacity allowed for extended backup times and reduced the frequency of battery replacements, leading to enhanced system reliability and reduced maintenance costs.

Another significant development in CMOS battery evolution was the integration of smart charging and power management systems. These innovations enabled more efficient use of battery power and extended the overall lifespan of CMOS batteries in data processing environments. Advanced monitoring capabilities were introduced, allowing system administrators to track battery health and predict replacement needs proactively.

Recent years have witnessed the emergence of ultra-low-power CMOS designs, which have dramatically reduced the power consumption of memory cells and other critical components. This development has eased the burden on CMOS batteries, allowing for smaller form factors and even longer operational lifespans. Additionally, the integration of energy harvesting technologies has begun to supplement CMOS batteries in some cutting-edge systems, further extending their operational life and reducing reliance on traditional battery power.

The latest trend in CMOS battery evolution focuses on sustainability and environmental considerations. Manufacturers are now developing eco-friendly CMOS battery solutions that minimize the use of harmful materials and improve recyclability. This shift aligns with the growing emphasis on green computing and sustainable data center practices.

As data processing architectures continue to expand and evolve, CMOS battery technology is expected to advance further. Future developments may include the integration of solid-state battery technology, offering even higher energy density and improved safety. Additionally, research into novel materials and nanotechnology could lead to breakthroughs in CMOS battery performance and longevity, ensuring that these critical components can keep pace with the ever-growing demands of modern computing infrastructures.

Data Center Power Needs

Data centers are at the forefront of modern technological infrastructure, serving as the backbone for cloud computing, big data analytics, and artificial intelligence applications. As these facilities continue to expand in size and complexity, their power requirements have grown exponentially, creating significant challenges for energy management and sustainability. The increasing demand for data processing and storage has led to a surge in power consumption, making energy efficiency a critical concern for data center operators and designers.

The power needs of data centers are multifaceted, encompassing various components such as servers, storage systems, networking equipment, and cooling infrastructure. Servers, being the primary workhorses of data centers, consume a substantial portion of the overall power budget. As processing demands intensify, the power density of server racks has increased dramatically, necessitating more efficient power delivery and thermal management solutions.

Cooling systems represent another major power consumer in data centers, often accounting for up to 40% of the total energy usage. The heat generated by densely packed computing equipment requires sophisticated cooling strategies to maintain optimal operating temperatures. This has led to the development of advanced cooling technologies, including liquid cooling and free air cooling, which aim to reduce the energy overhead associated with thermal management.

Power distribution and conversion within data centers also contribute significantly to overall energy consumption. The need for reliable and efficient power delivery systems has driven innovations in power supply units, voltage regulators, and distribution architectures. Uninterruptible power supplies (UPS) and backup generators add another layer of complexity to the power infrastructure, ensuring continuous operation during grid failures but also introducing additional energy losses.

The scale of modern data centers has pushed power requirements into the megawatt range, with some hyperscale facilities consuming as much electricity as small cities. This level of energy consumption has far-reaching implications, not only for operational costs but also for environmental sustainability. As a result, there is a growing emphasis on renewable energy sources and green data center designs to mitigate the carbon footprint of these facilities.

The optimization of CMOS battery technology in expansive data processing architectures is becoming increasingly crucial in addressing these power challenges. By improving the energy efficiency of fundamental computing components, data centers can potentially reduce their overall power consumption while maintaining or even enhancing performance. This focus on low-level hardware optimization aligns with broader industry efforts to create more sustainable and cost-effective data center operations.

The power needs of data centers are multifaceted, encompassing various components such as servers, storage systems, networking equipment, and cooling infrastructure. Servers, being the primary workhorses of data centers, consume a substantial portion of the overall power budget. As processing demands intensify, the power density of server racks has increased dramatically, necessitating more efficient power delivery and thermal management solutions.

Cooling systems represent another major power consumer in data centers, often accounting for up to 40% of the total energy usage. The heat generated by densely packed computing equipment requires sophisticated cooling strategies to maintain optimal operating temperatures. This has led to the development of advanced cooling technologies, including liquid cooling and free air cooling, which aim to reduce the energy overhead associated with thermal management.

Power distribution and conversion within data centers also contribute significantly to overall energy consumption. The need for reliable and efficient power delivery systems has driven innovations in power supply units, voltage regulators, and distribution architectures. Uninterruptible power supplies (UPS) and backup generators add another layer of complexity to the power infrastructure, ensuring continuous operation during grid failures but also introducing additional energy losses.

The scale of modern data centers has pushed power requirements into the megawatt range, with some hyperscale facilities consuming as much electricity as small cities. This level of energy consumption has far-reaching implications, not only for operational costs but also for environmental sustainability. As a result, there is a growing emphasis on renewable energy sources and green data center designs to mitigate the carbon footprint of these facilities.

The optimization of CMOS battery technology in expansive data processing architectures is becoming increasingly crucial in addressing these power challenges. By improving the energy efficiency of fundamental computing components, data centers can potentially reduce their overall power consumption while maintaining or even enhancing performance. This focus on low-level hardware optimization aligns with broader industry efforts to create more sustainable and cost-effective data center operations.

CMOS Battery Challenges

CMOS battery technology faces significant challenges in expansive data processing architectures, primarily due to the increasing power demands and complexity of modern computing systems. One of the key issues is the limited energy density of current CMOS batteries, which struggle to keep pace with the growing energy requirements of advanced data processing units. This limitation often results in shorter battery life and reduced overall system performance.

Another major challenge is the thermal management of CMOS batteries in high-performance computing environments. As data processing architectures become more powerful and compact, heat generation becomes a critical concern. Excessive heat can lead to decreased battery efficiency, accelerated degradation, and potential safety risks. Developing effective cooling solutions without compromising the form factor of devices remains a significant hurdle.

The scaling of CMOS technology also presents challenges for battery optimization. As transistor sizes continue to shrink, power leakage becomes more pronounced, leading to increased power consumption even when devices are in standby mode. This phenomenon, known as static power dissipation, puts additional strain on battery resources and complicates power management strategies.

Furthermore, the integration of CMOS batteries with advanced data processing architectures poses design and manufacturing challenges. Ensuring seamless compatibility between battery systems and complex chip designs while maintaining optimal performance and reliability requires sophisticated engineering solutions. This integration challenge is further compounded by the need for flexible and adaptable power delivery systems that can accommodate varying workloads and power states in modern computing environments.

The demand for faster charging capabilities in CMOS batteries also presents significant technical hurdles. While rapid charging is highly desirable for user convenience, it can lead to increased stress on battery components, potentially reducing their lifespan and reliability. Balancing fast charging capabilities with long-term battery health and safety remains an ongoing challenge for researchers and engineers.

Lastly, the environmental impact and sustainability of CMOS battery production and disposal are becoming increasingly important considerations. As the demand for high-performance computing devices grows, so does the need for more environmentally friendly battery technologies. Developing CMOS batteries with reduced environmental footprints, improved recyclability, and longer lifespans is crucial for addressing these sustainability challenges in expansive data processing architectures.

Another major challenge is the thermal management of CMOS batteries in high-performance computing environments. As data processing architectures become more powerful and compact, heat generation becomes a critical concern. Excessive heat can lead to decreased battery efficiency, accelerated degradation, and potential safety risks. Developing effective cooling solutions without compromising the form factor of devices remains a significant hurdle.

The scaling of CMOS technology also presents challenges for battery optimization. As transistor sizes continue to shrink, power leakage becomes more pronounced, leading to increased power consumption even when devices are in standby mode. This phenomenon, known as static power dissipation, puts additional strain on battery resources and complicates power management strategies.

Furthermore, the integration of CMOS batteries with advanced data processing architectures poses design and manufacturing challenges. Ensuring seamless compatibility between battery systems and complex chip designs while maintaining optimal performance and reliability requires sophisticated engineering solutions. This integration challenge is further compounded by the need for flexible and adaptable power delivery systems that can accommodate varying workloads and power states in modern computing environments.

The demand for faster charging capabilities in CMOS batteries also presents significant technical hurdles. While rapid charging is highly desirable for user convenience, it can lead to increased stress on battery components, potentially reducing their lifespan and reliability. Balancing fast charging capabilities with long-term battery health and safety remains an ongoing challenge for researchers and engineers.

Lastly, the environmental impact and sustainability of CMOS battery production and disposal are becoming increasingly important considerations. As the demand for high-performance computing devices grows, so does the need for more environmentally friendly battery technologies. Developing CMOS batteries with reduced environmental footprints, improved recyclability, and longer lifespans is crucial for addressing these sustainability challenges in expansive data processing architectures.

Current Optimization

01 Power management techniques for CMOS batteries

Various power management techniques are employed to optimize CMOS battery life. These include implementing low-power modes, intelligent power distribution, and dynamic voltage scaling. Such techniques help reduce overall power consumption and extend battery life in CMOS-based systems.- Power management techniques for CMOS batteries: Various power management techniques are employed to optimize CMOS battery life. These include implementing low-power modes, intelligent power distribution, and dynamic voltage scaling. Such techniques help reduce overall power consumption and extend battery longevity in CMOS-based systems.

- Battery monitoring and charging systems: Advanced monitoring and charging systems are developed to optimize CMOS battery performance. These systems include real-time battery status tracking, adaptive charging algorithms, and predictive maintenance features. By accurately monitoring and efficiently charging CMOS batteries, their lifespan and reliability are significantly improved.

- Thermal management for CMOS batteries: Thermal management solutions are implemented to optimize CMOS battery performance and longevity. These include advanced cooling systems, temperature-sensitive charging protocols, and thermal insulation techniques. Effective thermal management helps prevent battery degradation and ensures optimal operation across various environmental conditions.

- Energy harvesting and self-powering techniques: Innovative energy harvesting and self-powering techniques are developed to supplement or replace traditional CMOS batteries. These include integrating solar cells, piezoelectric elements, or thermoelectric generators into CMOS systems. Such techniques aim to extend operational life and reduce reliance on external power sources.

- Advanced materials and battery chemistry: Research into advanced materials and battery chemistry aims to enhance CMOS battery performance. This includes developing new electrode materials, electrolytes, and battery architectures specifically tailored for CMOS applications. These advancements lead to increased energy density, faster charging times, and improved overall battery efficiency.

02 Battery monitoring and charging optimization

Advanced monitoring systems are used to track CMOS battery health and charge levels. Optimized charging algorithms are implemented to maximize battery lifespan and efficiency. These systems can also predict battery failure and schedule maintenance accordingly.Expand Specific Solutions03 Thermal management for CMOS batteries

Effective thermal management strategies are crucial for optimizing CMOS battery performance and longevity. This includes implementing cooling systems, heat dissipation techniques, and temperature-aware power management to prevent overheating and maintain optimal operating conditions.Expand Specific Solutions04 Integration of energy harvesting technologies

Incorporating energy harvesting technologies into CMOS battery systems can help extend battery life and improve overall efficiency. This may include harvesting energy from ambient light, motion, or heat to supplement the primary battery power source.Expand Specific Solutions05 Advanced materials and battery chemistry improvements

Research into new materials and battery chemistries aims to enhance CMOS battery performance. This includes developing high-capacity electrode materials, solid-state electrolytes, and nanostructured components to improve energy density, charge/discharge rates, and overall battery lifespan.Expand Specific Solutions

Key CMOS Battery Players

The CMOS battery optimization in expansive data processing architectures is a rapidly evolving field, currently in its growth phase. The market is expanding due to increasing demand for energy-efficient computing solutions in data centers and enterprise environments. While the technology is advancing, it's not yet fully mature, with ongoing research and development efforts. Key players like IBM, Intel, and AMD are at the forefront, leveraging their expertise in semiconductor design and manufacturing. Taiwan Semiconductor Manufacturing Co. and GlobalFoundries are also significant contributors, providing advanced fabrication capabilities. Emerging companies like Trispace Technologies are introducing innovative solutions, indicating a dynamic and competitive landscape.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC has made significant strides in CMOS battery optimization for expansive data processing architectures through their advanced process nodes. Their 5nm and 3nm technologies offer substantial improvements in power efficiency, with up to 30% reduction in power consumption compared to previous generations[1]. TSMC has also developed ultra-low power (ULP) process variants specifically designed for battery-powered devices, incorporating high-k metal gate (HKMG) technology and fully depleted silicon-on-insulator (FD-SOI) designs[2]. These innovations allow for lower operating voltages and reduced leakage current, crucial for extending battery life in large-scale data processing systems. Furthermore, TSMC's 3D IC and advanced packaging technologies enable the integration of power management ICs (PMICs) directly with processing units, optimizing power delivery and reducing overall system power consumption[3].

Strengths: Cutting-edge process nodes, specialized ULP variants, and advanced packaging for power optimization. Weaknesses: Requires significant investment in new manufacturing equipment and processes.

Advanced Micro Devices, Inc.

Technical Solution: AMD has developed innovative CMOS battery optimization techniques for expansive data processing architectures. Their Zen architecture incorporates advanced power management features, including Precision Boost 2 and Extended Frequency Range (XFR) technologies, which dynamically adjust clock speeds and voltages to optimize performance and power efficiency[1]. AMD's Infinity Fabric interconnect technology allows for efficient communication between chiplets, reducing power consumption in multi-chip module (MCM) designs[2]. The company has also implemented fine-grained clock gating and power gating techniques to minimize idle power consumption[3]. AMD's SmartShift technology dynamically shifts power between the CPU and GPU in mobile platforms, optimizing overall system performance and battery life[4]. Additionally, AMD has introduced platform-level power management features like Modern Standby and S0ix low-power idle states, further enhancing battery life in always-on, always-connected scenarios[5].

Strengths: Efficient MCM designs, dynamic power shifting, and advanced idle state management. Weaknesses: Some features may be limited to specific hardware configurations.

Innovative CMOS Power

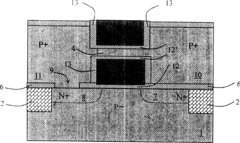

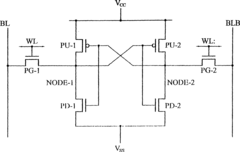

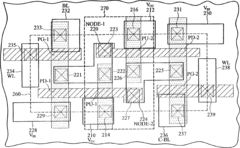

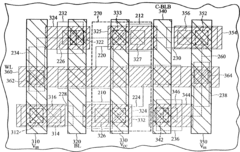

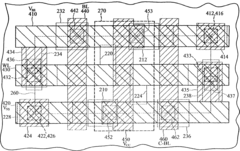

A CMOS integrated circuit and method for making same

PatentInactiveCN1299364C

Innovation

- A stacked CMOS structure is adopted, in which the pMOS device is located on top of the nMOS device and shares the same gate electrode. The pMOS device has a self-aligned double gate or gate-all-around structure, with thick source and drain regions and thin channel regions. It is formed through specific preparation methods such as The three-layer film of silicon dioxide, silicon and silicon dioxide, sidewall protection and polysilicon doping and other steps achieve self-alignment and area sharing of the device.

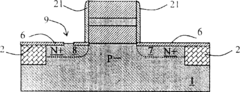

Memory cell and forming method thereof

PatentInactiveCN1622333A

Innovation

- Design a memory cell layout, including p-well area and n-well area, with at least one NMOS and PMOS transistor, the long side is at least twice the short side, and optimize the transistor through specific metal layer and via plug structure Layout to reduce charge carrier effects.

Thermal Management

Thermal management is a critical aspect of CMOS battery optimization in expansive data processing architectures. As data processing demands continue to increase, the heat generated by CMOS circuits becomes a significant challenge. Effective thermal management is essential to maintain optimal performance, extend battery life, and ensure the reliability of the system.

One of the primary approaches to thermal management in CMOS circuits is the implementation of dynamic voltage and frequency scaling (DVFS). This technique allows for real-time adjustments of the operating voltage and clock frequency based on the workload and thermal conditions. By reducing the voltage and frequency during periods of low activity or high temperatures, DVFS can significantly decrease power consumption and heat generation.

Another important strategy is the use of advanced packaging technologies. Three-dimensional integrated circuits (3D-ICs) and through-silicon vias (TSVs) enable more efficient heat dissipation by reducing the distance between heat-generating components and cooling solutions. These technologies also allow for the integration of dedicated thermal management layers, which can include micro-fluidic channels or phase-change materials for enhanced heat removal.

Active cooling solutions play a crucial role in thermal management for high-performance CMOS systems. Thermoelectric coolers (TECs) and micro-channel liquid cooling systems can provide localized cooling to hotspots on the chip. These active cooling methods can be dynamically controlled to respond to changing thermal conditions, ensuring optimal performance while minimizing energy consumption.

The design of the chip layout itself is also a key factor in thermal management. Techniques such as thermal-aware floorplanning and power gating can help distribute heat more evenly across the chip and reduce hotspots. Additionally, the use of low-power design techniques, such as clock gating and power gating, can significantly reduce overall heat generation.

Emerging technologies like graphene-based heat spreaders and carbon nanotube thermal interfaces show promise for future thermal management solutions. These materials offer superior thermal conductivity compared to traditional materials, potentially enabling more efficient heat dissipation in compact CMOS designs.

Thermal sensors and intelligent control systems are essential components of modern thermal management strategies. By continuously monitoring temperature across the chip, these systems can dynamically adjust cooling mechanisms and power management strategies to maintain optimal operating conditions. Machine learning algorithms are increasingly being employed to predict thermal behavior and proactively manage heat dissipation.

One of the primary approaches to thermal management in CMOS circuits is the implementation of dynamic voltage and frequency scaling (DVFS). This technique allows for real-time adjustments of the operating voltage and clock frequency based on the workload and thermal conditions. By reducing the voltage and frequency during periods of low activity or high temperatures, DVFS can significantly decrease power consumption and heat generation.

Another important strategy is the use of advanced packaging technologies. Three-dimensional integrated circuits (3D-ICs) and through-silicon vias (TSVs) enable more efficient heat dissipation by reducing the distance between heat-generating components and cooling solutions. These technologies also allow for the integration of dedicated thermal management layers, which can include micro-fluidic channels or phase-change materials for enhanced heat removal.

Active cooling solutions play a crucial role in thermal management for high-performance CMOS systems. Thermoelectric coolers (TECs) and micro-channel liquid cooling systems can provide localized cooling to hotspots on the chip. These active cooling methods can be dynamically controlled to respond to changing thermal conditions, ensuring optimal performance while minimizing energy consumption.

The design of the chip layout itself is also a key factor in thermal management. Techniques such as thermal-aware floorplanning and power gating can help distribute heat more evenly across the chip and reduce hotspots. Additionally, the use of low-power design techniques, such as clock gating and power gating, can significantly reduce overall heat generation.

Emerging technologies like graphene-based heat spreaders and carbon nanotube thermal interfaces show promise for future thermal management solutions. These materials offer superior thermal conductivity compared to traditional materials, potentially enabling more efficient heat dissipation in compact CMOS designs.

Thermal sensors and intelligent control systems are essential components of modern thermal management strategies. By continuously monitoring temperature across the chip, these systems can dynamically adjust cooling mechanisms and power management strategies to maintain optimal operating conditions. Machine learning algorithms are increasingly being employed to predict thermal behavior and proactively manage heat dissipation.

Energy Efficiency Regs

Energy efficiency regulations play a crucial role in shaping the landscape of CMOS battery optimization in expansive data processing architectures. These regulations are designed to address the growing concern over energy consumption in large-scale computing systems and data centers. The primary objective is to reduce power consumption, minimize environmental impact, and improve overall system performance.

In recent years, governments and international organizations have implemented stringent energy efficiency standards for electronic devices and data processing equipment. The U.S. Environmental Protection Agency's ENERGY STAR program, for instance, sets specific power consumption limits for servers and data center equipment. Similarly, the European Union's Ecodesign Directive mandates energy efficiency requirements for various electronic products, including those used in data processing architectures.

These regulations have a significant impact on the design and development of CMOS batteries and associated power management systems. Manufacturers are compelled to innovate and implement advanced power-saving techniques to meet these standards. This has led to the development of more efficient CMOS battery technologies, such as low-leakage designs and adaptive voltage scaling mechanisms.

One key aspect of energy efficiency regulations is the emphasis on idle power consumption. Many data processing systems spend a considerable amount of time in idle or low-activity states, and regulations now require manufacturers to optimize power consumption during these periods. This has resulted in the implementation of sophisticated power gating techniques and dynamic power management strategies in CMOS battery designs.

Furthermore, energy efficiency regulations often include requirements for power supply efficiency. This has led to improvements in voltage regulator designs and power distribution networks within expansive data processing architectures. Manufacturers are now focusing on reducing power losses in these components to meet regulatory standards and improve overall system efficiency.

The impact of these regulations extends beyond individual components to encompass entire system architectures. Data center operators are now required to report and improve their Power Usage Effectiveness (PUE) metrics, which has driven innovations in cooling systems, power distribution, and overall data center design. This holistic approach to energy efficiency has indirectly influenced CMOS battery optimization strategies, as designers must consider the broader context of system-level power management.

As energy efficiency regulations continue to evolve, they are likely to drive further innovations in CMOS battery technology and power management systems. Future regulations may focus on more granular aspects of power consumption, such as dynamic power scaling and energy-aware task scheduling. This will require even more sophisticated approaches to CMOS battery design and integration within expansive data processing architectures.

In recent years, governments and international organizations have implemented stringent energy efficiency standards for electronic devices and data processing equipment. The U.S. Environmental Protection Agency's ENERGY STAR program, for instance, sets specific power consumption limits for servers and data center equipment. Similarly, the European Union's Ecodesign Directive mandates energy efficiency requirements for various electronic products, including those used in data processing architectures.

These regulations have a significant impact on the design and development of CMOS batteries and associated power management systems. Manufacturers are compelled to innovate and implement advanced power-saving techniques to meet these standards. This has led to the development of more efficient CMOS battery technologies, such as low-leakage designs and adaptive voltage scaling mechanisms.

One key aspect of energy efficiency regulations is the emphasis on idle power consumption. Many data processing systems spend a considerable amount of time in idle or low-activity states, and regulations now require manufacturers to optimize power consumption during these periods. This has resulted in the implementation of sophisticated power gating techniques and dynamic power management strategies in CMOS battery designs.

Furthermore, energy efficiency regulations often include requirements for power supply efficiency. This has led to improvements in voltage regulator designs and power distribution networks within expansive data processing architectures. Manufacturers are now focusing on reducing power losses in these components to meet regulatory standards and improve overall system efficiency.

The impact of these regulations extends beyond individual components to encompass entire system architectures. Data center operators are now required to report and improve their Power Usage Effectiveness (PUE) metrics, which has driven innovations in cooling systems, power distribution, and overall data center design. This holistic approach to energy efficiency has indirectly influenced CMOS battery optimization strategies, as designers must consider the broader context of system-level power management.

As energy efficiency regulations continue to evolve, they are likely to drive further innovations in CMOS battery technology and power management systems. Future regulations may focus on more granular aspects of power consumption, such as dynamic power scaling and energy-aware task scheduling. This will require even more sophisticated approaches to CMOS battery design and integration within expansive data processing architectures.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!