Optimizing CMOS Battery Use in High-performance Connectivity Solutions

JUL 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

CMOS Battery Evolution

The evolution of CMOS battery technology in high-performance connectivity solutions has been marked by significant advancements aimed at optimizing power consumption and extending device longevity. Initially, CMOS batteries were primarily used to maintain basic system settings and real-time clock functions in computing devices. However, as connectivity solutions became more sophisticated, the role of CMOS batteries expanded to support a wider range of critical functions.

In the early stages of development, CMOS batteries were relatively large and had limited capacity, often requiring frequent replacements. The focus was primarily on maintaining minimal functionality during power-off states. As the demand for more compact and energy-efficient devices grew, manufacturers began to explore ways to reduce the size of CMOS batteries while improving their performance.

The introduction of lithium-ion technology marked a significant milestone in CMOS battery evolution. These batteries offered higher energy density and longer lifespan compared to their predecessors, allowing for smaller form factors and extended periods between replacements. This advancement was particularly crucial for portable devices and embedded systems where space and maintenance accessibility were limited.

As connectivity solutions became more complex, the power requirements for maintaining system states and configurations during standby modes increased. This led to the development of more sophisticated power management systems that worked in tandem with CMOS batteries. These systems implemented intelligent power-gating techniques and dynamic voltage scaling to minimize energy consumption during idle periods.

Recent years have seen a shift towards integrating CMOS battery functionality with other power management components. This integration has resulted in more efficient use of available energy and reduced overall system complexity. Advanced power management ICs now incorporate CMOS battery backup circuits, voltage regulators, and intelligent charging systems within a single package.

The latest trend in CMOS battery evolution focuses on enhancing sustainability and environmental friendliness. Manufacturers are exploring alternative materials and chemistries that offer improved performance while reducing environmental impact. This includes the development of solid-state CMOS batteries that promise higher energy density, faster charging capabilities, and improved safety profiles.

Looking ahead, the evolution of CMOS batteries in high-performance connectivity solutions is likely to continue along the path of miniaturization, increased energy density, and smarter power management. Emerging technologies such as energy harvesting and ultra-low-power circuit design are expected to complement CMOS batteries, further extending the operational life of connected devices and reducing the reliance on battery replacements.

In the early stages of development, CMOS batteries were relatively large and had limited capacity, often requiring frequent replacements. The focus was primarily on maintaining minimal functionality during power-off states. As the demand for more compact and energy-efficient devices grew, manufacturers began to explore ways to reduce the size of CMOS batteries while improving their performance.

The introduction of lithium-ion technology marked a significant milestone in CMOS battery evolution. These batteries offered higher energy density and longer lifespan compared to their predecessors, allowing for smaller form factors and extended periods between replacements. This advancement was particularly crucial for portable devices and embedded systems where space and maintenance accessibility were limited.

As connectivity solutions became more complex, the power requirements for maintaining system states and configurations during standby modes increased. This led to the development of more sophisticated power management systems that worked in tandem with CMOS batteries. These systems implemented intelligent power-gating techniques and dynamic voltage scaling to minimize energy consumption during idle periods.

Recent years have seen a shift towards integrating CMOS battery functionality with other power management components. This integration has resulted in more efficient use of available energy and reduced overall system complexity. Advanced power management ICs now incorporate CMOS battery backup circuits, voltage regulators, and intelligent charging systems within a single package.

The latest trend in CMOS battery evolution focuses on enhancing sustainability and environmental friendliness. Manufacturers are exploring alternative materials and chemistries that offer improved performance while reducing environmental impact. This includes the development of solid-state CMOS batteries that promise higher energy density, faster charging capabilities, and improved safety profiles.

Looking ahead, the evolution of CMOS batteries in high-performance connectivity solutions is likely to continue along the path of miniaturization, increased energy density, and smarter power management. Emerging technologies such as energy harvesting and ultra-low-power circuit design are expected to complement CMOS batteries, further extending the operational life of connected devices and reducing the reliance on battery replacements.

Market Demand Analysis

The market demand for optimizing CMOS battery use in high-performance connectivity solutions has been steadily increasing in recent years. This growth is primarily driven by the proliferation of Internet of Things (IoT) devices, wearable technology, and the ongoing expansion of 5G networks. As these technologies become more prevalent, the need for efficient power management in connectivity solutions has become paramount.

In the IoT sector, the global market size is projected to reach $1.6 trillion by 2025, with a compound annual growth rate (CAGR) of 10.53% from 2021 to 2025. A significant portion of this growth is attributed to the demand for low-power, high-performance connectivity solutions that can extend battery life in IoT devices. This trend is particularly evident in smart home applications, industrial IoT, and healthcare monitoring systems, where long-term operation without frequent battery replacements is crucial.

The wearable technology market is another key driver for optimized CMOS battery use. With a projected market value of $265.4 billion by 2026 and a CAGR of 18.0% from 2021 to 2026, wearables are becoming increasingly sophisticated, requiring more powerful connectivity solutions while maintaining extended battery life. Smartwatches, fitness trackers, and augmented reality glasses are at the forefront of this demand, pushing manufacturers to develop more energy-efficient CMOS technologies.

The rollout of 5G networks worldwide has also significantly impacted the market demand for optimized CMOS battery solutions. As 5G-enabled devices become more common, there is a growing need for power-efficient connectivity chips that can handle high-speed data transmission without draining battery life. The global 5G chipset market is expected to reach $67.2 billion by 2027, with a CAGR of 69.4% from 2020 to 2027, highlighting the immense potential for optimized CMOS solutions in this space.

In the automotive sector, the increasing adoption of connected car technologies and autonomous driving systems has created a new market for high-performance, low-power connectivity solutions. The global connected car market is forecasted to grow at a CAGR of 17.1% from 2021 to 2028, reaching a value of $191.83 billion by 2028. This growth is driving demand for CMOS technologies that can provide reliable connectivity while minimizing power consumption in vehicles.

The enterprise and industrial sectors are also contributing to the market demand for optimized CMOS battery solutions. With the rise of edge computing and industrial IoT applications, there is a growing need for connectivity solutions that can operate efficiently in remote or harsh environments where power sources may be limited. This trend is particularly evident in sectors such as agriculture, manufacturing, and logistics, where battery-powered sensors and communication devices are increasingly deployed.

As environmental concerns and energy efficiency regulations become more stringent, there is an additional push towards developing more power-efficient connectivity solutions. This trend is not only driven by consumer demand for longer-lasting devices but also by corporate sustainability goals and government initiatives aimed at reducing electronic waste and energy consumption.

In the IoT sector, the global market size is projected to reach $1.6 trillion by 2025, with a compound annual growth rate (CAGR) of 10.53% from 2021 to 2025. A significant portion of this growth is attributed to the demand for low-power, high-performance connectivity solutions that can extend battery life in IoT devices. This trend is particularly evident in smart home applications, industrial IoT, and healthcare monitoring systems, where long-term operation without frequent battery replacements is crucial.

The wearable technology market is another key driver for optimized CMOS battery use. With a projected market value of $265.4 billion by 2026 and a CAGR of 18.0% from 2021 to 2026, wearables are becoming increasingly sophisticated, requiring more powerful connectivity solutions while maintaining extended battery life. Smartwatches, fitness trackers, and augmented reality glasses are at the forefront of this demand, pushing manufacturers to develop more energy-efficient CMOS technologies.

The rollout of 5G networks worldwide has also significantly impacted the market demand for optimized CMOS battery solutions. As 5G-enabled devices become more common, there is a growing need for power-efficient connectivity chips that can handle high-speed data transmission without draining battery life. The global 5G chipset market is expected to reach $67.2 billion by 2027, with a CAGR of 69.4% from 2020 to 2027, highlighting the immense potential for optimized CMOS solutions in this space.

In the automotive sector, the increasing adoption of connected car technologies and autonomous driving systems has created a new market for high-performance, low-power connectivity solutions. The global connected car market is forecasted to grow at a CAGR of 17.1% from 2021 to 2028, reaching a value of $191.83 billion by 2028. This growth is driving demand for CMOS technologies that can provide reliable connectivity while minimizing power consumption in vehicles.

The enterprise and industrial sectors are also contributing to the market demand for optimized CMOS battery solutions. With the rise of edge computing and industrial IoT applications, there is a growing need for connectivity solutions that can operate efficiently in remote or harsh environments where power sources may be limited. This trend is particularly evident in sectors such as agriculture, manufacturing, and logistics, where battery-powered sensors and communication devices are increasingly deployed.

As environmental concerns and energy efficiency regulations become more stringent, there is an additional push towards developing more power-efficient connectivity solutions. This trend is not only driven by consumer demand for longer-lasting devices but also by corporate sustainability goals and government initiatives aimed at reducing electronic waste and energy consumption.

Technical Challenges

The optimization of CMOS battery use in high-performance connectivity solutions faces several significant technical challenges. One of the primary obstacles is the inherent trade-off between power consumption and performance. As connectivity solutions demand higher data rates and more complex signal processing, the power requirements increase substantially, putting strain on battery life and thermal management.

Another critical challenge lies in the miniaturization of devices. As connectivity solutions become more compact and integrated into smaller form factors, the available space for batteries diminishes. This constraint necessitates the development of more energy-dense power sources and highly efficient power management systems, which presents significant engineering hurdles.

The dynamic nature of connectivity workloads also poses a substantial challenge. High-performance connectivity solutions often experience rapid transitions between high-power active states and low-power idle states. Designing CMOS circuits that can quickly and efficiently switch between these modes while maintaining optimal performance is a complex task that requires advanced power gating techniques and sophisticated control algorithms.

Interference management presents another significant technical hurdle. As devices incorporate multiple wireless technologies (e.g., Wi-Fi, Bluetooth, cellular), the potential for interference increases. Mitigating this interference while maintaining low power consumption requires innovative circuit design and signal processing techniques, which can be particularly challenging within the constraints of battery-powered devices.

Temperature management is a critical concern in optimizing CMOS battery use. High-performance connectivity solutions generate considerable heat, which can negatively impact battery life and overall system reliability. Developing effective thermal management solutions that do not significantly increase power consumption or device size is a complex engineering challenge.

The variability in manufacturing processes and operating conditions also complicates CMOS battery optimization. Variations in transistor characteristics and environmental factors can lead to unpredictable power consumption patterns. Designing robust systems that maintain optimal performance across a wide range of conditions while minimizing battery drain requires advanced adaptive techniques and sophisticated power modeling.

Lastly, the challenge of balancing long-term reliability with power efficiency is significant. Aggressive power-saving techniques can sometimes lead to increased stress on CMOS components, potentially reducing their lifespan. Finding the optimal balance between power efficiency and long-term reliability requires extensive testing and innovative circuit design approaches.

Another critical challenge lies in the miniaturization of devices. As connectivity solutions become more compact and integrated into smaller form factors, the available space for batteries diminishes. This constraint necessitates the development of more energy-dense power sources and highly efficient power management systems, which presents significant engineering hurdles.

The dynamic nature of connectivity workloads also poses a substantial challenge. High-performance connectivity solutions often experience rapid transitions between high-power active states and low-power idle states. Designing CMOS circuits that can quickly and efficiently switch between these modes while maintaining optimal performance is a complex task that requires advanced power gating techniques and sophisticated control algorithms.

Interference management presents another significant technical hurdle. As devices incorporate multiple wireless technologies (e.g., Wi-Fi, Bluetooth, cellular), the potential for interference increases. Mitigating this interference while maintaining low power consumption requires innovative circuit design and signal processing techniques, which can be particularly challenging within the constraints of battery-powered devices.

Temperature management is a critical concern in optimizing CMOS battery use. High-performance connectivity solutions generate considerable heat, which can negatively impact battery life and overall system reliability. Developing effective thermal management solutions that do not significantly increase power consumption or device size is a complex engineering challenge.

The variability in manufacturing processes and operating conditions also complicates CMOS battery optimization. Variations in transistor characteristics and environmental factors can lead to unpredictable power consumption patterns. Designing robust systems that maintain optimal performance across a wide range of conditions while minimizing battery drain requires advanced adaptive techniques and sophisticated power modeling.

Lastly, the challenge of balancing long-term reliability with power efficiency is significant. Aggressive power-saving techniques can sometimes lead to increased stress on CMOS components, potentially reducing their lifespan. Finding the optimal balance between power efficiency and long-term reliability requires extensive testing and innovative circuit design approaches.

Current Solutions

01 Power management techniques for CMOS battery

Various power management techniques are employed to optimize CMOS battery usage. These include implementing low-power modes, intelligent power distribution, and dynamic voltage scaling. Such techniques help extend battery life by reducing power consumption during periods of inactivity or low system demand.- Power management techniques for CMOS battery: Various power management techniques are employed to optimize CMOS battery usage. These include implementing low-power modes, intelligent power distribution, and dynamic voltage scaling. Such techniques help extend battery life by reducing power consumption during periods of inactivity or low computational demand.

- Battery monitoring and charging optimization: Advanced monitoring systems are used to track battery health, charge levels, and usage patterns. This data is utilized to optimize charging cycles, predict battery life, and implement smart charging algorithms. These methods help maintain battery efficiency and prolong its overall lifespan.

- CMOS circuit design for power efficiency: Innovative CMOS circuit designs focus on reducing power leakage and improving energy efficiency. Techniques such as clock gating, power gating, and substrate biasing are implemented to minimize unnecessary power consumption in CMOS-based systems, thereby optimizing battery usage.

- Thermal management for battery optimization: Effective thermal management strategies are employed to maintain optimal operating temperatures for CMOS batteries. This includes the use of advanced cooling systems, thermal sensors, and temperature-aware power management algorithms. Proper thermal control helps prevent battery degradation and improves overall performance and longevity.

- Integration of energy harvesting technologies: Energy harvesting technologies are integrated into CMOS systems to supplement battery power. These may include solar cells, piezoelectric elements, or thermoelectric generators. By capturing and utilizing ambient energy, the overall reliance on the CMOS battery is reduced, leading to improved battery life and system sustainability.

02 Battery monitoring and charging optimization

Advanced monitoring systems are used to track battery health, charge levels, and usage patterns. This data is utilized to optimize charging cycles, predict battery life, and implement smart charging algorithms. These methods help maintain battery efficiency and prolong its overall lifespan.Expand Specific Solutions03 CMOS circuit design for power efficiency

Innovative CMOS circuit designs focus on reducing power leakage and improving energy efficiency. This includes the use of advanced transistor technologies, optimized logic gates, and power-aware layout techniques. These design strategies contribute to minimizing the power draw on the CMOS battery.Expand Specific Solutions04 Thermal management for battery preservation

Implementing effective thermal management solutions helps maintain optimal operating temperatures for CMOS batteries. This includes the use of heat dissipation techniques, thermal sensors, and adaptive cooling systems. Proper thermal management contributes to improved battery performance and longevity.Expand Specific Solutions05 Integration of energy harvesting technologies

Incorporating energy harvesting technologies into CMOS systems can help supplement battery power and extend operational life. This may include the use of solar cells, piezoelectric elements, or other ambient energy sources to recharge or support the CMOS battery, reducing its overall load and improving longevity.Expand Specific Solutions

Key Industry Players

The optimization of CMOS battery use in high-performance connectivity solutions is currently in a mature stage of development, with a significant market size driven by the increasing demand for energy-efficient devices. The technology's maturity is evident from the involvement of major players across various sectors. Companies like Qualcomm, Renesas Electronics, and IBM are at the forefront, leveraging their expertise in semiconductor and connectivity solutions. Other key contributors include Samsung Electronics, Intel, and Taiwan Semiconductor Manufacturing Co., each bringing unique capabilities to advance CMOS battery optimization. The competitive landscape is diverse, with both established tech giants and specialized firms like EVE Energy contributing to innovation in this field.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed advanced power management techniques for CMOS batteries in high-performance connectivity solutions. Their approach includes dynamic voltage and frequency scaling (DVFS) to optimize power consumption based on workload[1]. They've also implemented a sophisticated sleep mode system that can rapidly wake up specific components as needed, reducing overall power draw[3]. Qualcomm's solution incorporates intelligent battery monitoring and predictive algorithms to extend battery life in devices like smartphones and IoT devices[5]. Their latest chipsets feature dedicated low-power islands for always-on connectivity features, allowing main processors to remain in deep sleep states for longer periods[7].

Strengths: Industry-leading power efficiency, extensive experience in mobile connectivity. Weaknesses: Solutions may be optimized primarily for mobile devices, potentially limiting applicability in other domains.

Renesas Electronics Corp.

Technical Solution: Renesas has focused on optimizing CMOS battery use through their innovative RE Family of microcontrollers. These MCUs feature ultra-low power consumption modes, with some variants achieving as low as 0.2 µA/MHz in active mode and 0.1 µA in sleep mode[2]. Renesas has implemented advanced power gating techniques to isolate unused circuit blocks, significantly reducing leakage current[4]. Their solutions also incorporate adaptive clocking mechanisms that adjust system frequency based on required performance, further optimizing power consumption. Renesas has developed specialized power management ICs (PMICs) that work in conjunction with their MCUs to provide highly efficient power delivery and battery management for a wide range of applications, from wearables to industrial IoT devices[6].

Strengths: Expertise in ultra-low power microcontrollers, wide range of applications. Weaknesses: May have less focus on high-performance connectivity compared to pure communications companies.

Core Innovations

CMOS device integration for low external resistance

PatentInactiveUS20040188766A1

Innovation

- The introduction of a first silicide region with a lesser thickness, positioned closer to the channel, and a second silicide region with greater thickness, providing low sheet resistance interconnects, allows for reduced external resistance by minimizing the electron path and avoiding the disadvantages of conventional silicide spacing, while maintaining low resistance contacts.

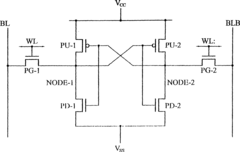

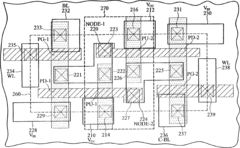

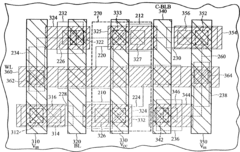

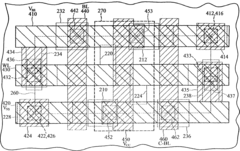

Memory cell and forming method thereof

PatentInactiveCN1622333A

Innovation

- Design a memory cell layout, including p-well area and n-well area, with at least one NMOS and PMOS transistor, the long side is at least twice the short side, and optimize the transistor through specific metal layer and via plug structure Layout to reduce charge carrier effects.

Power Management

Power management is a critical aspect of optimizing CMOS battery use in high-performance connectivity solutions. Effective power management strategies are essential for maximizing battery life, reducing energy consumption, and maintaining optimal performance in connected devices.

One key approach to power management in CMOS-based connectivity solutions is dynamic voltage and frequency scaling (DVFS). This technique involves adjusting the operating voltage and clock frequency of the system based on workload demands. By reducing voltage and frequency during periods of low activity, significant power savings can be achieved without compromising performance when needed.

Another important strategy is power gating, which involves selectively shutting down unused circuit blocks or components when they are not in use. This technique helps minimize static power consumption and can be particularly effective in complex connectivity solutions with multiple functional units.

Adaptive power management algorithms play a crucial role in optimizing battery use. These algorithms continuously monitor system parameters such as workload, temperature, and battery status to make real-time decisions on power allocation. By dynamically adjusting power consumption based on current conditions, these algorithms can significantly extend battery life while maintaining performance.

Low-power design techniques at the circuit level are also essential for optimizing CMOS battery use. These include the use of multi-threshold CMOS (MTCMOS) technology, which employs transistors with different threshold voltages to balance performance and power consumption. Additionally, clock gating and power-aware logic synthesis techniques can help reduce dynamic power consumption in high-performance connectivity solutions.

Energy harvesting technologies are increasingly being integrated into power management systems for CMOS-based devices. These technologies can capture and convert ambient energy sources such as light, heat, or motion into electrical energy, supplementing battery power and extending overall device runtime.

Efficient power distribution and regulation within the system are crucial for minimizing power losses. Advanced power management integrated circuits (PMICs) can provide precise voltage regulation, power sequencing, and battery charging capabilities, ensuring optimal power delivery to various system components.

Lastly, implementing intelligent sleep modes and wake-up mechanisms can significantly reduce power consumption during periods of inactivity. By carefully managing the transition between active and low-power states, connectivity solutions can maintain responsiveness while minimizing unnecessary power drain.

One key approach to power management in CMOS-based connectivity solutions is dynamic voltage and frequency scaling (DVFS). This technique involves adjusting the operating voltage and clock frequency of the system based on workload demands. By reducing voltage and frequency during periods of low activity, significant power savings can be achieved without compromising performance when needed.

Another important strategy is power gating, which involves selectively shutting down unused circuit blocks or components when they are not in use. This technique helps minimize static power consumption and can be particularly effective in complex connectivity solutions with multiple functional units.

Adaptive power management algorithms play a crucial role in optimizing battery use. These algorithms continuously monitor system parameters such as workload, temperature, and battery status to make real-time decisions on power allocation. By dynamically adjusting power consumption based on current conditions, these algorithms can significantly extend battery life while maintaining performance.

Low-power design techniques at the circuit level are also essential for optimizing CMOS battery use. These include the use of multi-threshold CMOS (MTCMOS) technology, which employs transistors with different threshold voltages to balance performance and power consumption. Additionally, clock gating and power-aware logic synthesis techniques can help reduce dynamic power consumption in high-performance connectivity solutions.

Energy harvesting technologies are increasingly being integrated into power management systems for CMOS-based devices. These technologies can capture and convert ambient energy sources such as light, heat, or motion into electrical energy, supplementing battery power and extending overall device runtime.

Efficient power distribution and regulation within the system are crucial for minimizing power losses. Advanced power management integrated circuits (PMICs) can provide precise voltage regulation, power sequencing, and battery charging capabilities, ensuring optimal power delivery to various system components.

Lastly, implementing intelligent sleep modes and wake-up mechanisms can significantly reduce power consumption during periods of inactivity. By carefully managing the transition between active and low-power states, connectivity solutions can maintain responsiveness while minimizing unnecessary power drain.

Connectivity Impact

The impact of connectivity on CMOS battery optimization in high-performance solutions is multifaceted and significant. As devices become increasingly interconnected, the demand for efficient power management grows exponentially. Connectivity features, such as Wi-Fi, Bluetooth, and cellular networks, are major contributors to battery drain in modern devices. This necessitates a delicate balance between maintaining robust connectivity and preserving battery life.

In high-performance connectivity solutions, CMOS batteries play a crucial role in maintaining system integrity and real-time clock functions. However, the constant need for connectivity puts additional strain on these power sources. The challenge lies in optimizing CMOS battery usage while ensuring uninterrupted connectivity performance.

One key aspect of this optimization is the implementation of intelligent power management systems. These systems can dynamically adjust power allocation based on connectivity requirements, reducing unnecessary battery drain during periods of low activity. Advanced algorithms can predict usage patterns and optimize power distribution accordingly, significantly extending CMOS battery life without compromising connectivity.

The integration of low-power connectivity protocols has also become a focal point in addressing this challenge. Technologies such as Bluetooth Low Energy (BLE) and Wi-Fi HaLow offer reduced power consumption while maintaining adequate connectivity ranges. By leveraging these protocols, devices can minimize the power draw on CMOS batteries during standby and low-activity periods.

Furthermore, the development of energy-harvesting technologies presents promising opportunities for supplementing CMOS battery power in connectivity solutions. Techniques such as RF energy harvesting from ambient signals or piezoelectric energy generation from device vibrations can provide auxiliary power sources, reducing the overall load on the CMOS battery.

The impact of connectivity on CMOS battery optimization also extends to the realm of network infrastructure. As 5G networks become more prevalent, the increased data rates and lower latency offer potential for more efficient device-to-network communications. This can lead to reduced power consumption in connected devices, indirectly benefiting CMOS battery life.

In conclusion, the optimization of CMOS battery use in high-performance connectivity solutions requires a holistic approach. It involves not only enhancing battery technology but also improving power management systems, adopting energy-efficient connectivity protocols, and leveraging emerging technologies like energy harvesting. The successful integration of these elements will be crucial in meeting the growing demands of connected devices while maximizing battery longevity.

In high-performance connectivity solutions, CMOS batteries play a crucial role in maintaining system integrity and real-time clock functions. However, the constant need for connectivity puts additional strain on these power sources. The challenge lies in optimizing CMOS battery usage while ensuring uninterrupted connectivity performance.

One key aspect of this optimization is the implementation of intelligent power management systems. These systems can dynamically adjust power allocation based on connectivity requirements, reducing unnecessary battery drain during periods of low activity. Advanced algorithms can predict usage patterns and optimize power distribution accordingly, significantly extending CMOS battery life without compromising connectivity.

The integration of low-power connectivity protocols has also become a focal point in addressing this challenge. Technologies such as Bluetooth Low Energy (BLE) and Wi-Fi HaLow offer reduced power consumption while maintaining adequate connectivity ranges. By leveraging these protocols, devices can minimize the power draw on CMOS batteries during standby and low-activity periods.

Furthermore, the development of energy-harvesting technologies presents promising opportunities for supplementing CMOS battery power in connectivity solutions. Techniques such as RF energy harvesting from ambient signals or piezoelectric energy generation from device vibrations can provide auxiliary power sources, reducing the overall load on the CMOS battery.

The impact of connectivity on CMOS battery optimization also extends to the realm of network infrastructure. As 5G networks become more prevalent, the increased data rates and lower latency offer potential for more efficient device-to-network communications. This can lead to reduced power consumption in connected devices, indirectly benefiting CMOS battery life.

In conclusion, the optimization of CMOS battery use in high-performance connectivity solutions requires a holistic approach. It involves not only enhancing battery technology but also improving power management systems, adopting energy-efficient connectivity protocols, and leveraging emerging technologies like energy harvesting. The successful integration of these elements will be crucial in meeting the growing demands of connected devices while maximizing battery longevity.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!