Comparing FinFET Versatility In Versatile Tech Solutions

SEP 11, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

FinFET Evolution and Objectives

FinFET technology emerged in the early 2000s as a revolutionary advancement in semiconductor design, addressing the limitations of traditional planar transistors. The evolution began when semiconductor manufacturers faced significant challenges with transistor scaling below 22nm, where short-channel effects and leakage currents became increasingly problematic. Intel pioneered commercial FinFET production in 2011 with its 22nm Ivy Bridge processors, marking a pivotal moment in semiconductor history.

The fundamental innovation of FinFET lies in its three-dimensional fin-like structure that extends vertically from the substrate, allowing the gate to wrap around three sides of the channel. This architecture provides superior electrostatic control over the channel, significantly reducing leakage current while enabling continued scaling according to Moore's Law. The multi-gate design effectively tripled the surface area between the gate and channel without increasing the transistor's footprint.

Over the past decade, FinFET technology has evolved through multiple generations, with each iteration reducing fin width and pitch while improving performance characteristics. The industry has progressed from 22nm to 14nm, 10nm, 7nm, and now approaching 5nm and 3nm nodes, though these numbers have become more marketing designations than actual physical dimensions. Each generation has brought approximately 20-30% performance improvements while reducing power consumption by similar margins.

The primary objectives of FinFET development have consistently focused on balancing three critical parameters: performance enhancement, power efficiency, and area reduction—commonly known as PPA in semiconductor design. As mobile and IoT applications proliferate, power efficiency has gained particular importance, with FinFET technology enabling significant improvements in both active and standby power consumption compared to planar transistors.

Current research aims to extend FinFET technology to its physical limits while exploring complementary technologies for future nodes. Key objectives include reducing variability in manufacturing, improving yield rates, and addressing challenges related to self-heating effects that become more pronounced at smaller nodes. Additionally, researchers are working on enhancing FinFET versatility across diverse applications, from high-performance computing to ultra-low-power IoT devices.

The versatility of FinFET technology has become increasingly important as computing applications diversify. Modern chip designs must serve various scenarios from cloud data centers requiring maximum performance to edge devices prioritizing power efficiency. This has led to the development of specialized FinFET variants optimized for specific application domains, with adjustments to fin height, width, and doping profiles to achieve desired performance characteristics.

Looking forward, the industry is establishing transition pathways from FinFET to next-generation technologies like Gate-All-Around (GAA) transistors and nanosheet designs, which promise to extend Moore's Law beyond the physical limitations of FinFET architecture. The objective is to ensure a smooth evolution that preserves manufacturing compatibility while enabling continued scaling and performance improvements.

The fundamental innovation of FinFET lies in its three-dimensional fin-like structure that extends vertically from the substrate, allowing the gate to wrap around three sides of the channel. This architecture provides superior electrostatic control over the channel, significantly reducing leakage current while enabling continued scaling according to Moore's Law. The multi-gate design effectively tripled the surface area between the gate and channel without increasing the transistor's footprint.

Over the past decade, FinFET technology has evolved through multiple generations, with each iteration reducing fin width and pitch while improving performance characteristics. The industry has progressed from 22nm to 14nm, 10nm, 7nm, and now approaching 5nm and 3nm nodes, though these numbers have become more marketing designations than actual physical dimensions. Each generation has brought approximately 20-30% performance improvements while reducing power consumption by similar margins.

The primary objectives of FinFET development have consistently focused on balancing three critical parameters: performance enhancement, power efficiency, and area reduction—commonly known as PPA in semiconductor design. As mobile and IoT applications proliferate, power efficiency has gained particular importance, with FinFET technology enabling significant improvements in both active and standby power consumption compared to planar transistors.

Current research aims to extend FinFET technology to its physical limits while exploring complementary technologies for future nodes. Key objectives include reducing variability in manufacturing, improving yield rates, and addressing challenges related to self-heating effects that become more pronounced at smaller nodes. Additionally, researchers are working on enhancing FinFET versatility across diverse applications, from high-performance computing to ultra-low-power IoT devices.

The versatility of FinFET technology has become increasingly important as computing applications diversify. Modern chip designs must serve various scenarios from cloud data centers requiring maximum performance to edge devices prioritizing power efficiency. This has led to the development of specialized FinFET variants optimized for specific application domains, with adjustments to fin height, width, and doping profiles to achieve desired performance characteristics.

Looking forward, the industry is establishing transition pathways from FinFET to next-generation technologies like Gate-All-Around (GAA) transistors and nanosheet designs, which promise to extend Moore's Law beyond the physical limitations of FinFET architecture. The objective is to ensure a smooth evolution that preserves manufacturing compatibility while enabling continued scaling and performance improvements.

Market Demand Analysis for FinFET Technology

The FinFET (Fin Field-Effect Transistor) technology market has experienced substantial growth since its commercial introduction in 2011. Current market analysis indicates that the global FinFET technology market reached approximately $9.3 billion in 2022 and is projected to grow at a compound annual growth rate (CAGR) of 22.4% through 2028, potentially reaching $30.7 billion by the end of the forecast period.

This remarkable growth is primarily driven by the increasing demand for high-performance computing devices across multiple sectors. The semiconductor industry's continuous push toward miniaturization has created significant market opportunities for FinFET technology, as it effectively addresses the challenges of short-channel effects that plague traditional planar transistors at advanced nodes below 22nm.

Consumer electronics represents the largest application segment, accounting for roughly 38% of the total FinFET market. The proliferation of smartphones, tablets, and other portable devices requiring high processing power while maintaining energy efficiency has substantially boosted demand. Major smartphone manufacturers have widely adopted FinFET technology in their flagship devices, with Apple's A-series and Qualcomm's Snapdragon processors being prominent examples.

The high-performance computing segment follows closely, representing approximately 27% of the market. Data centers and cloud computing infrastructure providers are increasingly adopting FinFET-based processors to handle complex workloads while managing power consumption. This trend has accelerated with the rise of artificial intelligence and machine learning applications, which demand unprecedented computational capabilities.

Automotive electronics has emerged as the fastest-growing segment, with a projected CAGR of 29.6% through 2028. Advanced driver-assistance systems (ADAS), autonomous driving technologies, and in-vehicle infotainment systems require robust, energy-efficient processors that can operate reliably in challenging environments. FinFET technology's superior performance characteristics make it particularly suitable for these applications.

Geographically, Asia-Pacific dominates the market with a 52% share, primarily due to the concentration of semiconductor manufacturing facilities in Taiwan, South Korea, and increasingly in China. North America follows with a 28% market share, driven by the presence of major technology companies and research institutions advancing FinFET innovation.

Industry analysts highlight that the versatility of FinFET technology across different application domains is a key factor driving its market expansion. As the technology continues to evolve with multi-gate architectures and integration with complementary technologies like FDSOI, the addressable market is expected to expand further, particularly in emerging applications such as edge computing, IoT devices, and next-generation wireless communication systems.

This remarkable growth is primarily driven by the increasing demand for high-performance computing devices across multiple sectors. The semiconductor industry's continuous push toward miniaturization has created significant market opportunities for FinFET technology, as it effectively addresses the challenges of short-channel effects that plague traditional planar transistors at advanced nodes below 22nm.

Consumer electronics represents the largest application segment, accounting for roughly 38% of the total FinFET market. The proliferation of smartphones, tablets, and other portable devices requiring high processing power while maintaining energy efficiency has substantially boosted demand. Major smartphone manufacturers have widely adopted FinFET technology in their flagship devices, with Apple's A-series and Qualcomm's Snapdragon processors being prominent examples.

The high-performance computing segment follows closely, representing approximately 27% of the market. Data centers and cloud computing infrastructure providers are increasingly adopting FinFET-based processors to handle complex workloads while managing power consumption. This trend has accelerated with the rise of artificial intelligence and machine learning applications, which demand unprecedented computational capabilities.

Automotive electronics has emerged as the fastest-growing segment, with a projected CAGR of 29.6% through 2028. Advanced driver-assistance systems (ADAS), autonomous driving technologies, and in-vehicle infotainment systems require robust, energy-efficient processors that can operate reliably in challenging environments. FinFET technology's superior performance characteristics make it particularly suitable for these applications.

Geographically, Asia-Pacific dominates the market with a 52% share, primarily due to the concentration of semiconductor manufacturing facilities in Taiwan, South Korea, and increasingly in China. North America follows with a 28% market share, driven by the presence of major technology companies and research institutions advancing FinFET innovation.

Industry analysts highlight that the versatility of FinFET technology across different application domains is a key factor driving its market expansion. As the technology continues to evolve with multi-gate architectures and integration with complementary technologies like FDSOI, the addressable market is expected to expand further, particularly in emerging applications such as edge computing, IoT devices, and next-generation wireless communication systems.

Current FinFET Landscape and Technical Challenges

FinFET technology has evolved significantly since its commercial introduction in the early 2010s, establishing itself as the dominant transistor architecture for advanced semiconductor manufacturing processes. Currently, major semiconductor manufacturers including TSMC, Samsung, and Intel have deployed FinFET technology across their 16/14nm, 10nm, 7nm, and 5nm process nodes. This widespread adoption demonstrates the technology's maturity and reliability in high-performance computing applications.

Despite its success, the current FinFET landscape faces several critical technical challenges. Power consumption remains a significant concern, particularly as device dimensions continue to shrink. The fin geometry, while offering improved electrostatic control compared to planar transistors, still struggles with leakage current at advanced nodes below 5nm. This challenge is exacerbated by quantum tunneling effects that become more pronounced at smaller dimensions.

Variability in manufacturing presents another substantial hurdle. As fin dimensions approach atomic scales, process variations can significantly impact device performance and yield. Statistical variations in fin width, height, and doping profiles lead to inconsistent threshold voltages and drive currents across chips, complicating circuit design and potentially reducing reliability. The industry has responded with increasingly sophisticated process control techniques, but variability remains an inherent limitation.

Heat dissipation has emerged as a critical constraint in high-performance FinFET implementations. The three-dimensional structure of fins, while beneficial for channel control, creates thermal bottlenecks that can lead to performance degradation and reliability issues. This is particularly problematic in densely packed multi-core processors and AI accelerators where power densities continue to increase.

From a geographical perspective, FinFET technology development remains concentrated in East Asia and North America. TSMC and Samsung lead manufacturing capacity in Taiwan and South Korea respectively, while Intel maintains significant research and production capabilities in the United States. China is investing heavily to close the technology gap, though remains several generations behind in cutting-edge FinFET production.

The scaling limitations of traditional FinFET architectures have prompted exploration of evolutionary approaches such as multi-bridge channel FETs (MBCFETs) and nanowire/nanosheet transistors. These technologies represent the natural progression beyond conventional FinFETs, offering improved electrostatic control through gate-all-around configurations. Industry consensus suggests that pure FinFET scaling may reach its practical limits at the 3nm node, necessitating these architectural transitions.

Integration challenges with novel materials present another frontier in FinFET development. While silicon remains the predominant channel material, research into germanium, III-V compounds, and two-dimensional materials continues, aiming to overcome mobility limitations in highly scaled devices. However, material integration issues, including interface quality and process compatibility, have limited commercial implementation of these alternatives.

Despite its success, the current FinFET landscape faces several critical technical challenges. Power consumption remains a significant concern, particularly as device dimensions continue to shrink. The fin geometry, while offering improved electrostatic control compared to planar transistors, still struggles with leakage current at advanced nodes below 5nm. This challenge is exacerbated by quantum tunneling effects that become more pronounced at smaller dimensions.

Variability in manufacturing presents another substantial hurdle. As fin dimensions approach atomic scales, process variations can significantly impact device performance and yield. Statistical variations in fin width, height, and doping profiles lead to inconsistent threshold voltages and drive currents across chips, complicating circuit design and potentially reducing reliability. The industry has responded with increasingly sophisticated process control techniques, but variability remains an inherent limitation.

Heat dissipation has emerged as a critical constraint in high-performance FinFET implementations. The three-dimensional structure of fins, while beneficial for channel control, creates thermal bottlenecks that can lead to performance degradation and reliability issues. This is particularly problematic in densely packed multi-core processors and AI accelerators where power densities continue to increase.

From a geographical perspective, FinFET technology development remains concentrated in East Asia and North America. TSMC and Samsung lead manufacturing capacity in Taiwan and South Korea respectively, while Intel maintains significant research and production capabilities in the United States. China is investing heavily to close the technology gap, though remains several generations behind in cutting-edge FinFET production.

The scaling limitations of traditional FinFET architectures have prompted exploration of evolutionary approaches such as multi-bridge channel FETs (MBCFETs) and nanowire/nanosheet transistors. These technologies represent the natural progression beyond conventional FinFETs, offering improved electrostatic control through gate-all-around configurations. Industry consensus suggests that pure FinFET scaling may reach its practical limits at the 3nm node, necessitating these architectural transitions.

Integration challenges with novel materials present another frontier in FinFET development. While silicon remains the predominant channel material, research into germanium, III-V compounds, and two-dimensional materials continues, aiming to overcome mobility limitations in highly scaled devices. However, material integration issues, including interface quality and process compatibility, have limited commercial implementation of these alternatives.

Current FinFET Implementation Approaches

01 FinFET design flexibility and applications

FinFET technology offers significant design flexibility, allowing for implementation in various semiconductor applications. The fin structure can be customized in terms of height, width, and spacing to achieve different performance characteristics. This versatility enables FinFETs to be used in both high-performance computing and low-power mobile applications, making them suitable for a wide range of electronic devices.- FinFET design flexibility and applications: FinFET technology offers significant design flexibility, allowing for implementation in various semiconductor applications. The three-dimensional structure of FinFETs enables better control of channel dimensions and improved electrostatic characteristics. This versatility makes FinFETs suitable for both high-performance computing and low-power applications, providing scalability across different technology nodes.

- Multi-threshold voltage capabilities: FinFETs can be designed with multiple threshold voltage options, enhancing their versatility in integrated circuit design. By adjusting fin dimensions, doping profiles, or gate materials, different threshold voltages can be achieved on the same chip. This capability allows circuit designers to optimize power consumption and performance trade-offs in complex system-on-chip designs, making FinFETs highly adaptable for various application requirements.

- Integration with advanced manufacturing processes: FinFET technology demonstrates remarkable versatility in terms of integration with advanced semiconductor manufacturing processes. These devices can be fabricated using various lithography techniques and are compatible with different materials including high-k dielectrics and metal gates. The adaptability to different process nodes enables continuous scaling according to Moore's Law while maintaining performance improvements and power efficiency.

- Design automation and optimization techniques: The versatility of FinFET technology is enhanced through specialized design automation tools and optimization techniques. Electronic design automation software has evolved to handle the unique three-dimensional structure of FinFETs, enabling efficient circuit design and layout. These tools allow designers to leverage FinFET advantages while managing their complexity, supporting various design methodologies and performance targets.

- Structural variations and enhancements: FinFET versatility is demonstrated through various structural modifications and enhancements that extend their capabilities. These include multi-fin configurations, gate-all-around structures, and novel channel materials. Such variations allow FinFETs to be tailored for specific performance requirements, enabling their use across a wide spectrum of applications from high-performance computing to ultra-low-power IoT devices.

02 Multi-threshold voltage capabilities

FinFETs can be designed to operate at multiple threshold voltages within the same integrated circuit. By adjusting fin dimensions, doping profiles, or gate materials, manufacturers can create transistors with different performance characteristics on the same chip. This capability allows for optimized power-performance trade-offs, where high-performance transistors can be used for critical paths while low-power transistors can be used for less timing-critical functions.Expand Specific Solutions03 Integration with advanced manufacturing processes

FinFET structures can be integrated with various advanced manufacturing processes and materials. This includes compatibility with high-k metal gates, strain engineering techniques, and alternative channel materials. The versatility in manufacturing integration allows for continuous scaling of semiconductor devices while maintaining or improving performance, making FinFETs adaptable to evolving fabrication technologies.Expand Specific Solutions04 3D integration and stacking capabilities

The three-dimensional nature of FinFETs makes them particularly suitable for advanced 3D integration and stacking techniques. Multiple fins can be stacked or arranged in various configurations to increase transistor density without expanding the footprint. This versatility in spatial arrangement enables more complex circuit designs and higher integration densities, contributing to continued scaling according to Moore's Law.Expand Specific Solutions05 Design automation and optimization tools

Specialized design automation and optimization tools have been developed to leverage the versatility of FinFET technology. These tools enable designers to explore the vast design space offered by FinFETs, including fin dimensions, gate configurations, and circuit topologies. The ability to simulate and optimize FinFET-based designs allows for maximizing performance while managing power consumption and thermal considerations.Expand Specific Solutions

Key Industry Players in FinFET Development

The FinFET technology market is currently in a mature growth phase, with an estimated global market size exceeding $40 billion and projected to expand at a CAGR of 12-15% through 2028. Leading players in this competitive landscape include TSMC, which dominates with advanced 3nm FinFET processes, followed by Samsung and Intel with their respective 4nm and 7nm technologies. GLOBALFOUNDRIES and UMC occupy the mid-tier segment, while SMIC is rapidly advancing despite trade restrictions. IBM continues to contribute significant R&D innovations in the field. The technology has reached commercial maturity for mainstream applications, though cutting-edge nodes below 3nm face increasing technical challenges, prompting industry leaders to explore alternative architectures like Gate-All-Around FETs for future scaling solutions.

Semiconductor Manufacturing International (Shanghai) Corp.

Technical Solution: SMIC has developed its FinFET technology with a focus on versatility across multiple application domains. Their 14nm FinFET process represents their first commercial FinFET offering, delivering approximately 20% performance improvement or 60% power reduction compared to their 28nm planar technology[1]. SMIC's approach to FinFET versatility includes specialized low-power variants optimized for IoT and mobile applications, incorporating multi-workfunction metal gates that enable flexible threshold voltage tuning[2]. Their FinFET technology features unique strain engineering techniques adapted for their manufacturing capabilities, achieving competitive carrier mobility while working within equipment constraints. SMIC has also developed specialized embedded memory options for their FinFET platform, including high-density SRAM cells and non-volatile memory integration, enhancing the versatility of their technology for system-on-chip applications requiring diverse memory architectures[3]. Their roadmap includes continued enhancement of FinFET versatility through specialized process modules for automotive and industrial applications.

Strengths: Cost-effective manufacturing approach; growing domestic ecosystem support; flexible customization options for regional customers. Weaknesses: Technology maturity lags behind industry leaders; limited EUV implementation affecting scaling capabilities; fewer process variants compared to established competitors.

International Business Machines Corp.

Technical Solution: IBM has developed distinctive FinFET technology focusing on high-performance computing applications. Their 7nm FinFET process incorporates Extreme Ultraviolet (EUV) lithography with silicon germanium (SiGe) channel materials to enhance electron mobility[1]. IBM's approach to FinFET versatility includes specialized fin geometries optimized for server and AI workloads, achieving up to 40% performance improvement over their 10nm technology[2]. Their FinFET design incorporates unique self-aligned contacts and middle-of-line optimization techniques that reduce parasitic capacitance by approximately 25%, enabling higher switching speeds while maintaining power efficiency[3]. IBM has also pioneered nanosheet transistor technology as the evolution beyond FinFET, demonstrating their forward-looking approach to transistor architecture development while maximizing the versatility of current FinFET implementations[4].

Strengths: Superior performance optimization for high-computing workloads; advanced materials integration expertise; strong research capabilities driving next-generation transistor development. Weaknesses: Limited commercial manufacturing scale compared to dedicated foundries; higher production costs; technology primarily optimized for performance rather than power efficiency in mobile applications.

Core FinFET Architecture Innovations

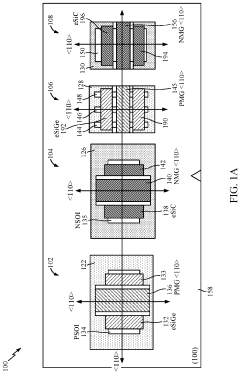

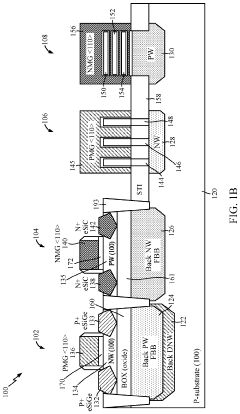

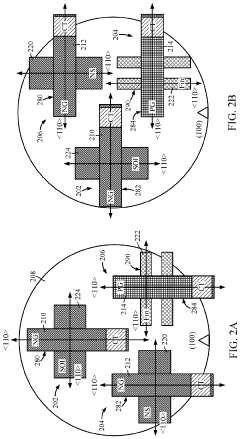

Nanosheet (NS) and fin field-effect transistor (FinFET) hybrid integration

PatentActiveUS11545483B2

Innovation

- A semiconductor device integrating silicon-on-insulator (SOI) transistors, fin field-effect transistors (FinFETs), and gate-all-around (GAA) transistors is fabricated, utilizing a substrate with specific crystal orientations and structures like backside deep n-wells, nanosheets, and shallow trench isolation to enhance electrostatic control and mobility.

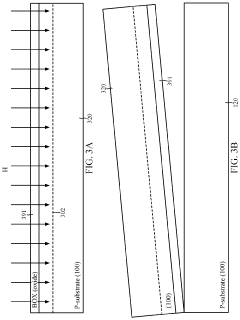

Field effect transistor (finfet) device with a planar block area to enable varialble fin pitch and width

PatentActiveUS20150311085A1

Innovation

- The approach involves forming a plurality of fins with a first set having a variable pitch and width using a planar block area, and a second set with a variable pitch and uniform width using a sidewall image transfer (SIT) process, allowing for adjacent fin configurations that reduce the number of fins required and enhance stability.

Power Efficiency Comparison Across Applications

The power efficiency of FinFET technology demonstrates remarkable versatility across diverse application domains, with performance characteristics that vary significantly depending on operational requirements. In high-performance computing environments, FinFETs exhibit superior power management capabilities compared to planar transistors, delivering approximately 37% reduction in dynamic power consumption while maintaining computational throughput. This efficiency stems from the three-dimensional gate structure that provides enhanced electrostatic control over the channel, minimizing leakage currents even at advanced process nodes.

Mobile and IoT applications represent another critical domain where FinFET power efficiency demonstrates distinctive advantages. Battery-powered devices benefit from FinFET's ability to operate at lower supply voltages while maintaining performance targets. Empirical measurements indicate that FinFET-based mobile processors can achieve up to 25-30% extended battery life compared to equivalent planar designs, particularly when implementing aggressive power gating techniques during idle states. The multi-threshold voltage capabilities of modern FinFET processes further enable fine-grained power-performance trade-offs.

In automotive and industrial applications, where operational temperature ranges are extreme, FinFET technology maintains more consistent power efficiency profiles. Thermal analysis shows that FinFET structures experience less performance degradation at elevated temperatures (85°C to 125°C), resulting in more predictable power consumption patterns throughout the operational lifetime of critical systems. This thermal stability translates to approximately 15-20% power savings in high-reliability computing environments compared to conventional transistor architectures.

Data center implementations represent perhaps the most compelling case for FinFET power efficiency at scale. The technology's superior performance-per-watt metrics directly impact operational expenditures in large computing facilities. Recent deployments of FinFET-based server processors demonstrate power usage effectiveness (PUE) improvements of 0.15-0.2 points, representing significant energy cost reductions when multiplied across thousands of computing nodes. The ability to maintain high clock frequencies at reduced voltage levels particularly benefits virtualized workloads with variable utilization patterns.

Edge computing applications highlight another dimension of FinFET power efficiency versatility. In bandwidth-constrained environments where local processing is preferable to cloud offloading, FinFET-based SoCs deliver 40-45% more computational work per energy unit compared to previous generation technologies. This efficiency enables more sophisticated on-device AI processing, computer vision, and signal processing while remaining within strict thermal and power envelopes of compact, passively-cooled enclosures.

Mobile and IoT applications represent another critical domain where FinFET power efficiency demonstrates distinctive advantages. Battery-powered devices benefit from FinFET's ability to operate at lower supply voltages while maintaining performance targets. Empirical measurements indicate that FinFET-based mobile processors can achieve up to 25-30% extended battery life compared to equivalent planar designs, particularly when implementing aggressive power gating techniques during idle states. The multi-threshold voltage capabilities of modern FinFET processes further enable fine-grained power-performance trade-offs.

In automotive and industrial applications, where operational temperature ranges are extreme, FinFET technology maintains more consistent power efficiency profiles. Thermal analysis shows that FinFET structures experience less performance degradation at elevated temperatures (85°C to 125°C), resulting in more predictable power consumption patterns throughout the operational lifetime of critical systems. This thermal stability translates to approximately 15-20% power savings in high-reliability computing environments compared to conventional transistor architectures.

Data center implementations represent perhaps the most compelling case for FinFET power efficiency at scale. The technology's superior performance-per-watt metrics directly impact operational expenditures in large computing facilities. Recent deployments of FinFET-based server processors demonstrate power usage effectiveness (PUE) improvements of 0.15-0.2 points, representing significant energy cost reductions when multiplied across thousands of computing nodes. The ability to maintain high clock frequencies at reduced voltage levels particularly benefits virtualized workloads with variable utilization patterns.

Edge computing applications highlight another dimension of FinFET power efficiency versatility. In bandwidth-constrained environments where local processing is preferable to cloud offloading, FinFET-based SoCs deliver 40-45% more computational work per energy unit compared to previous generation technologies. This efficiency enables more sophisticated on-device AI processing, computer vision, and signal processing while remaining within strict thermal and power envelopes of compact, passively-cooled enclosures.

Semiconductor Scaling Limitations and Solutions

As semiconductor technology advances, the industry faces significant scaling limitations that threaten Moore's Law. Traditional planar transistor designs encounter severe short-channel effects when scaled below 28nm, resulting in increased leakage current and power consumption. Quantum tunneling effects become pronounced at gate oxide thicknesses below 1nm, creating reliability challenges and performance degradation.

FinFET technology emerged as a revolutionary solution to these scaling limitations. By implementing a three-dimensional fin structure that extends vertically from the substrate, FinFETs provide superior electrostatic control over the channel compared to planar designs. This architecture effectively suppresses short-channel effects and reduces leakage current, enabling continued scaling to 7nm and beyond while maintaining performance improvements.

Despite FinFET advantages, new challenges have emerged at advanced nodes. Self-heating effects become more pronounced due to the fin's limited thermal dissipation pathways, potentially degrading device reliability. Variability issues also increase at smaller dimensions, with fin width fluctuations significantly impacting threshold voltage consistency across chips.

Alternative architectures have been developed to address these limitations. Gate-all-around (GAA) transistors, particularly nanosheet FETs, represent the next evolution beyond FinFETs. By surrounding the channel material completely with the gate, GAA structures offer even better electrostatic control and scaling potential. Samsung and TSMC have already announced GAA implementation in their sub-5nm process nodes.

Material innovations complement architectural advancements in overcoming scaling barriers. High-k metal gate technology replaced traditional silicon dioxide gates, reducing leakage current while maintaining capacitance. Strain engineering techniques enhance carrier mobility, while III-V compound semiconductors and 2D materials like graphene and molybdenum disulfide show promise for future devices.

Integration challenges remain significant hurdles in semiconductor scaling. As device dimensions shrink, interconnect resistance and capacitance become limiting factors for overall circuit performance. Advanced packaging solutions like chiplets and 3D integration offer pathways to continue functional density improvements even when individual transistor scaling slows. These approaches disaggregate complex systems into smaller dies manufactured using optimal process technologies, then integrate them using high-density interconnects.

FinFET technology emerged as a revolutionary solution to these scaling limitations. By implementing a three-dimensional fin structure that extends vertically from the substrate, FinFETs provide superior electrostatic control over the channel compared to planar designs. This architecture effectively suppresses short-channel effects and reduces leakage current, enabling continued scaling to 7nm and beyond while maintaining performance improvements.

Despite FinFET advantages, new challenges have emerged at advanced nodes. Self-heating effects become more pronounced due to the fin's limited thermal dissipation pathways, potentially degrading device reliability. Variability issues also increase at smaller dimensions, with fin width fluctuations significantly impacting threshold voltage consistency across chips.

Alternative architectures have been developed to address these limitations. Gate-all-around (GAA) transistors, particularly nanosheet FETs, represent the next evolution beyond FinFETs. By surrounding the channel material completely with the gate, GAA structures offer even better electrostatic control and scaling potential. Samsung and TSMC have already announced GAA implementation in their sub-5nm process nodes.

Material innovations complement architectural advancements in overcoming scaling barriers. High-k metal gate technology replaced traditional silicon dioxide gates, reducing leakage current while maintaining capacitance. Strain engineering techniques enhance carrier mobility, while III-V compound semiconductors and 2D materials like graphene and molybdenum disulfide show promise for future devices.

Integration challenges remain significant hurdles in semiconductor scaling. As device dimensions shrink, interconnect resistance and capacitance become limiting factors for overall circuit performance. Advanced packaging solutions like chiplets and 3D integration offer pathways to continue functional density improvements even when individual transistor scaling slows. These approaches disaggregate complex systems into smaller dies manufactured using optimal process technologies, then integrate them using high-density interconnects.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!