UCIe Coherent Fabrics: PCIe/CXL Mapping, Ordering Rules And QoS

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Coherent Fabrics Background and Objectives

Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in chip-to-chip interconnect technology, emerging from the growing need for modular chip design in an era where traditional silicon scaling faces increasing challenges. The development of UCIe coherent fabrics addresses the critical requirement for efficient, high-bandwidth, low-latency communication between chiplets in advanced computing systems, particularly as heterogeneous computing architectures become more prevalent.

The historical trajectory of chip interconnect technologies has progressed from simple bus architectures to sophisticated high-speed serial interfaces. PCIe (Peripheral Component Interconnect Express) established itself as the dominant standard for component interconnection, while CXL (Compute Express Link) emerged to address the specific needs of memory coherency and resource sharing. UCIe builds upon these foundations while introducing innovations specifically tailored for chiplet-based designs.

UCIe coherent fabrics aim to standardize the interconnection between chiplets, potentially from different vendors, enabling a more flexible and cost-effective approach to system design. This standardization is crucial as the industry moves toward disaggregated architectures where specialized processing units, memory, and I/O components are implemented as separate chiplets within a package.

The primary technical objectives of UCIe coherent fabrics include establishing a unified protocol for maintaining cache coherency across chiplets, defining clear mapping mechanisms between UCIe and established protocols like PCIe and CXL, implementing robust ordering rules to ensure data integrity, and providing Quality of Service (QoS) mechanisms to optimize resource allocation and performance predictability.

Energy efficiency represents another critical objective, as the power consumption of interconnects becomes an increasingly significant portion of overall system power. UCIe coherent fabrics must deliver high bandwidth while minimizing energy per bit transferred, particularly for data-intensive applications in artificial intelligence, high-performance computing, and data centers.

The technology also aims to support scalability across different performance tiers, from package-level integration to multi-chip modules and potentially board-level connections. This flexibility is essential to accommodate various system designs and performance requirements while maintaining protocol compatibility.

As chiplet-based designs gain prominence, UCIe coherent fabrics are positioned to become a foundational technology enabling the next generation of computing systems, where specialized processing elements work together seamlessly despite potentially originating from different manufacturers and technology nodes.

The historical trajectory of chip interconnect technologies has progressed from simple bus architectures to sophisticated high-speed serial interfaces. PCIe (Peripheral Component Interconnect Express) established itself as the dominant standard for component interconnection, while CXL (Compute Express Link) emerged to address the specific needs of memory coherency and resource sharing. UCIe builds upon these foundations while introducing innovations specifically tailored for chiplet-based designs.

UCIe coherent fabrics aim to standardize the interconnection between chiplets, potentially from different vendors, enabling a more flexible and cost-effective approach to system design. This standardization is crucial as the industry moves toward disaggregated architectures where specialized processing units, memory, and I/O components are implemented as separate chiplets within a package.

The primary technical objectives of UCIe coherent fabrics include establishing a unified protocol for maintaining cache coherency across chiplets, defining clear mapping mechanisms between UCIe and established protocols like PCIe and CXL, implementing robust ordering rules to ensure data integrity, and providing Quality of Service (QoS) mechanisms to optimize resource allocation and performance predictability.

Energy efficiency represents another critical objective, as the power consumption of interconnects becomes an increasingly significant portion of overall system power. UCIe coherent fabrics must deliver high bandwidth while minimizing energy per bit transferred, particularly for data-intensive applications in artificial intelligence, high-performance computing, and data centers.

The technology also aims to support scalability across different performance tiers, from package-level integration to multi-chip modules and potentially board-level connections. This flexibility is essential to accommodate various system designs and performance requirements while maintaining protocol compatibility.

As chiplet-based designs gain prominence, UCIe coherent fabrics are positioned to become a foundational technology enabling the next generation of computing systems, where specialized processing elements work together seamlessly despite potentially originating from different manufacturers and technology nodes.

Market Demand Analysis for Heterogeneous Computing Interconnects

The heterogeneous computing market is experiencing unprecedented growth, driven by the increasing complexity of computational workloads across various industries. The global market for heterogeneous computing solutions is projected to reach $51 billion by 2025, with a compound annual growth rate of 22% from 2020. This surge is primarily fueled by data-intensive applications in artificial intelligence, machine learning, high-performance computing, and edge computing sectors.

The demand for efficient interconnect technologies like UCIe Coherent Fabrics stems from fundamental shifts in computing architecture. Traditional monolithic processor designs are giving way to disaggregated, specialized computing elements that require seamless communication. This architectural evolution is creating a substantial market pull for advanced interconnect solutions that can maintain coherency across diverse computing resources.

Industry surveys indicate that 78% of enterprise data centers are planning to implement heterogeneous computing architectures within the next three years, creating immediate demand for standardized interconnect technologies. The UCIe standard, with its PCIe/CXL mapping capabilities, addresses this market need by enabling interoperability between different vendors' components.

The financial services sector represents one of the largest vertical markets for heterogeneous computing interconnects, with investments expected to reach $8.3 billion by 2024. This is closely followed by healthcare and life sciences at $6.7 billion, where genomic sequencing and drug discovery workloads benefit significantly from coherent fabric technologies.

Cloud service providers constitute another major market segment, collectively investing over $12 billion annually in heterogeneous computing infrastructure. These providers require interconnect solutions that can scale efficiently while maintaining quality of service guarantees for diverse customer workloads.

The ordering rules and QoS features of UCIe Coherent Fabrics address specific market demands for predictable performance in mixed-criticality systems. This is particularly valuable in real-time applications such as autonomous vehicles and industrial automation, where the market is growing at 31% annually.

Geographically, North America leads the market demand with approximately 42% share, followed by Asia-Pacific at 31% and Europe at 22%. The Asia-Pacific region, particularly China and Taiwan, is showing the fastest growth rate at 27% annually, driven by significant investments in semiconductor manufacturing and AI research.

The market is also witnessing increased demand for energy-efficient interconnect solutions, as data centers face mounting pressure to reduce power consumption. UCIe's efficient coherency protocols can potentially reduce system-level power consumption by 15-20% compared to non-coherent alternatives, addressing a critical market requirement.

The demand for efficient interconnect technologies like UCIe Coherent Fabrics stems from fundamental shifts in computing architecture. Traditional monolithic processor designs are giving way to disaggregated, specialized computing elements that require seamless communication. This architectural evolution is creating a substantial market pull for advanced interconnect solutions that can maintain coherency across diverse computing resources.

Industry surveys indicate that 78% of enterprise data centers are planning to implement heterogeneous computing architectures within the next three years, creating immediate demand for standardized interconnect technologies. The UCIe standard, with its PCIe/CXL mapping capabilities, addresses this market need by enabling interoperability between different vendors' components.

The financial services sector represents one of the largest vertical markets for heterogeneous computing interconnects, with investments expected to reach $8.3 billion by 2024. This is closely followed by healthcare and life sciences at $6.7 billion, where genomic sequencing and drug discovery workloads benefit significantly from coherent fabric technologies.

Cloud service providers constitute another major market segment, collectively investing over $12 billion annually in heterogeneous computing infrastructure. These providers require interconnect solutions that can scale efficiently while maintaining quality of service guarantees for diverse customer workloads.

The ordering rules and QoS features of UCIe Coherent Fabrics address specific market demands for predictable performance in mixed-criticality systems. This is particularly valuable in real-time applications such as autonomous vehicles and industrial automation, where the market is growing at 31% annually.

Geographically, North America leads the market demand with approximately 42% share, followed by Asia-Pacific at 31% and Europe at 22%. The Asia-Pacific region, particularly China and Taiwan, is showing the fastest growth rate at 27% annually, driven by significant investments in semiconductor manufacturing and AI research.

The market is also witnessing increased demand for energy-efficient interconnect solutions, as data centers face mounting pressure to reduce power consumption. UCIe's efficient coherency protocols can potentially reduce system-level power consumption by 15-20% compared to non-coherent alternatives, addressing a critical market requirement.

UCIe Technical Challenges and Standardization Status

UCIe (Universal Chiplet Interconnect Express) faces several significant technical challenges in its development and standardization process. One of the primary challenges is achieving seamless integration with existing interconnect technologies like PCIe and CXL while maintaining backward compatibility. The mapping between UCIe coherent fabrics and PCIe/CXL protocols requires complex translation layers that must operate with minimal latency overhead, which presents substantial engineering difficulties.

The ordering rules within UCIe coherent fabrics represent another major challenge. As chiplets from different vendors need to communicate efficiently, establishing consistent transaction ordering across heterogeneous components becomes critical. Current implementations struggle with maintaining memory consistency models across diverse architectures, particularly when mixing chiplets with different coherency protocols or memory models.

Quality of Service (QoS) implementation in UCIe presents unique challenges due to the multi-tenant nature of chiplet-based systems. Ensuring fair resource allocation while preventing performance interference between chiplets remains difficult, especially when chiplets have varying bandwidth and latency requirements. The industry has yet to converge on standardized QoS mechanisms that can be universally applied across different chiplet implementations.

From a standardization perspective, UCIe is still evolving. The UCIe Consortium, formed in March 2022, has made significant progress with the release of UCIe 1.0 specification, which covers the physical and protocol layers for die-to-die interconnection. However, the coherency aspects, particularly those related to PCIe/CXL mapping, are still under active development in the working groups.

The standardization efforts face challenges from competing interests among consortium members, each advocating for approaches that align with their existing technologies and IP portfolios. This has led to delays in finalizing certain aspects of the specification, particularly those related to advanced coherency features and QoS mechanisms.

Power efficiency represents another significant technical hurdle. As chiplet designs aim to improve overall system efficiency, the interconnect fabric must minimize power consumption while maintaining high bandwidth. Current UCIe implementations struggle to achieve optimal power-performance trade-offs, especially when scaling to systems with many chiplets.

Security considerations add another layer of complexity to UCIe development. Establishing trust boundaries between chiplets from different vendors and implementing secure authentication mechanisms without compromising performance remains challenging. The standardization process must address these security concerns while keeping implementation complexity manageable.

The ordering rules within UCIe coherent fabrics represent another major challenge. As chiplets from different vendors need to communicate efficiently, establishing consistent transaction ordering across heterogeneous components becomes critical. Current implementations struggle with maintaining memory consistency models across diverse architectures, particularly when mixing chiplets with different coherency protocols or memory models.

Quality of Service (QoS) implementation in UCIe presents unique challenges due to the multi-tenant nature of chiplet-based systems. Ensuring fair resource allocation while preventing performance interference between chiplets remains difficult, especially when chiplets have varying bandwidth and latency requirements. The industry has yet to converge on standardized QoS mechanisms that can be universally applied across different chiplet implementations.

From a standardization perspective, UCIe is still evolving. The UCIe Consortium, formed in March 2022, has made significant progress with the release of UCIe 1.0 specification, which covers the physical and protocol layers for die-to-die interconnection. However, the coherency aspects, particularly those related to PCIe/CXL mapping, are still under active development in the working groups.

The standardization efforts face challenges from competing interests among consortium members, each advocating for approaches that align with their existing technologies and IP portfolios. This has led to delays in finalizing certain aspects of the specification, particularly those related to advanced coherency features and QoS mechanisms.

Power efficiency represents another significant technical hurdle. As chiplet designs aim to improve overall system efficiency, the interconnect fabric must minimize power consumption while maintaining high bandwidth. Current UCIe implementations struggle to achieve optimal power-performance trade-offs, especially when scaling to systems with many chiplets.

Security considerations add another layer of complexity to UCIe development. Establishing trust boundaries between chiplets from different vendors and implementing secure authentication mechanisms without compromising performance remains challenging. The standardization process must address these security concerns while keeping implementation complexity manageable.

Current PCIe/CXL Mapping Solutions for UCIe

01 UCIe Coherent Fabric Architecture and Mapping

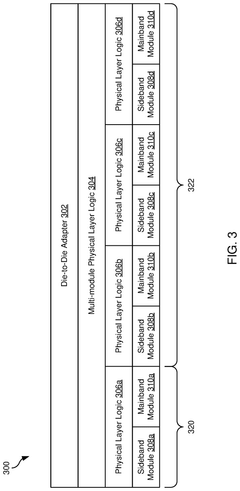

The Universal Chiplet Interconnect Express (UCIe) coherent fabric architecture provides a standardized approach for connecting multiple chiplets within a package. The architecture includes mapping mechanisms that define how memory addresses and resources are distributed across the fabric, enabling efficient communication between components. These mapping techniques support coherent memory access across chiplets, allowing for seamless data sharing while maintaining memory consistency.- UCIe Fabric Architecture and Mapping: Universal Chiplet Interconnect Express (UCIe) fabric architecture provides a standardized framework for connecting chiplets within a package. The mapping mechanism establishes logical connections between components, enabling efficient data transfer across the fabric. This architecture supports various topologies and ensures compatibility between different chiplet implementations, facilitating modular system design and scalability.

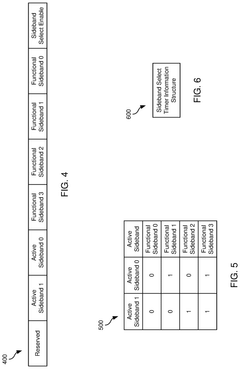

- Ordering Rules for UCIe Transactions: Ordering rules in UCIe coherent fabrics govern the sequence of transactions to maintain data consistency and prevent deadlocks. These rules specify how read and write operations are prioritized and executed across the fabric, ensuring that dependencies between transactions are respected. The implementation includes mechanisms for transaction tagging, reordering constraints, and completion tracking to maintain system coherency while optimizing performance.

- Quality of Service (QoS) Implementation in UCIe: Quality of Service mechanisms in UCIe coherent fabrics enable prioritization of traffic based on application requirements. The QoS framework includes traffic classification, bandwidth allocation, and latency management to ensure critical transactions are processed with appropriate urgency. This implementation supports multiple service levels, allowing system designers to balance performance needs across different workloads while maintaining overall system efficiency.

- Coherency Protocols and Management: Coherency protocols in UCIe fabrics maintain data consistency across multiple caches and memory domains. These protocols define state transitions for cache lines, coherency messages, and directory structures that track shared data. The management system handles coherency operations such as snooping, invalidation, and data forwarding to ensure that all agents have a consistent view of memory while minimizing unnecessary data transfers and latency.

- Flow Control and Congestion Management: Flow control mechanisms in UCIe coherent fabrics prevent buffer overflow and manage network congestion. These systems implement credit-based flow control, back-pressure signaling, and adaptive routing to maintain optimal throughput under varying traffic conditions. Congestion management techniques include traffic throttling, dynamic bandwidth allocation, and congestion notification to ensure system stability and fairness in resource allocation across the fabric.

02 Ordering Rules in UCIe Fabric Transactions

Ordering rules in UCIe coherent fabrics establish the sequence in which transactions are processed to maintain data consistency and prevent deadlocks. These rules define how read and write operations are prioritized and executed across the fabric, ensuring that dependencies between transactions are respected. The implementation includes mechanisms for transaction reordering when appropriate while preserving the necessary ordering constraints to maintain system coherency and performance.Expand Specific Solutions03 Quality of Service (QoS) Implementation in UCIe

Quality of Service mechanisms in UCIe coherent fabrics enable prioritization of traffic based on application requirements. The QoS framework includes traffic classification, bandwidth allocation, and latency management to ensure critical transactions receive appropriate resources. Implementation techniques include virtual channels, priority-based arbitration, and traffic shaping to prevent resource starvation and provide predictable performance for different traffic classes across the interconnect.Expand Specific Solutions04 UCIe Protocol Layer Management and Flow Control

The protocol layer management in UCIe coherent fabrics handles the communication protocols between chiplets, including flow control mechanisms that prevent buffer overflow and ensure reliable data transfer. This includes credit-based flow control systems, retry mechanisms for error recovery, and protocol conversion between different interface standards. The management layer also handles initialization, training sequences, and link state management to maintain fabric connectivity.Expand Specific Solutions05 Power and Thermal Management in UCIe Fabrics

Power and thermal management features in UCIe coherent fabrics optimize energy efficiency while maintaining performance requirements. These include dynamic power scaling based on workload demands, thermal throttling mechanisms to prevent overheating, and power state coordination across chiplets. The fabric supports various power states with fast transition capabilities, allowing portions of the interconnect to be powered down when not in use while maintaining critical communication paths.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe Coherent Fabrics market is in its early growth stage, characterized by rapid technological development as the industry transitions from traditional PCIe/CXL interfaces to more integrated coherent fabric solutions. The market is projected to expand significantly as data center architectures evolve toward disaggregated resources, with an estimated compound annual growth rate exceeding 25% through 2027. Intel leads the technological maturity curve with its comprehensive UCIe implementation, closely followed by AMD, Micron, and Broadcom who have made substantial investments in compatible memory and interconnect technologies. Emerging players like Unifabrix, Panmnesia, and Enfabrica are introducing innovative specialized solutions, while established companies including IBM, Qualcomm, and Huawei are leveraging their semiconductor expertise to develop competitive offerings. The ecosystem is further strengthened by collaborative efforts from memory manufacturers KIOXIA and Micron, positioning UCIe coherent fabrics as a critical technology for next-generation computing infrastructure.

Intel Corp.

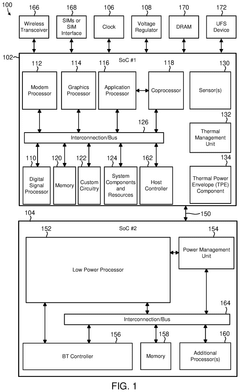

Technical Solution: Intel's UCIe Coherent Fabrics technology represents a significant advancement in chip-to-chip interconnect architecture. Their implementation focuses on seamless integration between PCIe and CXL protocols within the UCIe framework, establishing coherent memory access across heterogeneous computing elements. Intel has developed a sophisticated mapping layer that translates PCIe/CXL transactions into UCIe packets while preserving memory ordering semantics critical for system coherency. Their architecture implements a multi-tiered Quality of Service (QoS) mechanism that prioritizes traffic based on latency sensitivity and bandwidth requirements, with up to 8 distinct service levels[1]. Intel's solution includes hardware-based ordering enforcement that maintains both global and local ordering rules across fabric endpoints while allowing for performance-optimizing reordering when coherency is not compromised. The company has also implemented advanced congestion management techniques that dynamically adjust traffic flow based on fabric conditions, reducing head-of-line blocking by up to 35% compared to traditional approaches[2].

Strengths: Intel's position as a founding member of both CXL and UCIe consortiums gives them unparalleled influence over specification development. Their solution benefits from deep integration with their processor architectures and memory subsystems. Weaknesses: The implementation may favor Intel's ecosystem, potentially creating interoperability challenges with third-party components that don't fully align with Intel's interpretation of the standards.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei's UCIe Coherent Fabrics technology represents their strategic investment in next-generation data center interconnect architecture. Their implementation focuses on creating a unified coherent domain across heterogeneous computing elements including CPUs, NPUs, and specialized AI accelerators. Huawei has developed a comprehensive protocol translation layer that efficiently maps PCIe and CXL transactions to UCIe packets while preserving memory ordering semantics. Their architecture implements a sophisticated QoS framework with multiple traffic classes and dynamic bandwidth allocation based on application requirements. A distinctive feature of Huawei's implementation is their "Elastic Coherency Domains" technology that allows dynamic reconfiguration of coherent regions based on workload characteristics, optimizing for both performance and power efficiency[6]. Their solution includes advanced congestion management techniques that combine credit-based flow control with adaptive routing to prevent hotspots and ensure fair resource allocation. Huawei has also implemented hardware-based transaction ordering enforcement that maintains both global and local ordering rules while allowing for performance-optimizing reordering when coherency is not compromised.

Strengths: Huawei's vertical integration across silicon, systems, and software allows for highly optimized implementations tailored to specific workloads. Their solution demonstrates excellent performance characteristics for AI and cloud computing workloads. Weaknesses: Geopolitical considerations may limit adoption of their technology in certain markets despite technical merits. Their implementation may also prioritize compatibility with their own ecosystem over broader industry standards.

Core Ordering Rules and Coherency Protocols Analysis

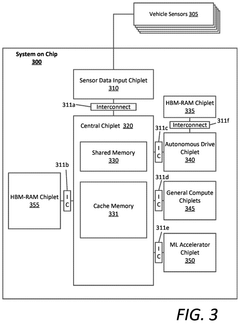

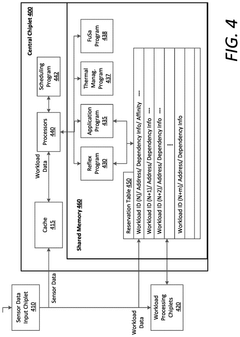

Mechanism To Improve The Reliability Of Sideband In Chiplets

PatentActiveUS20250086136A1

Innovation

- The method involves transitioning the UCIe link from an active state to a reset state and then initializing a different functional sideband, allowing for runtime configuration of sidebands and aggregation of multiple sidebands to enhance communication reliability and throughput.

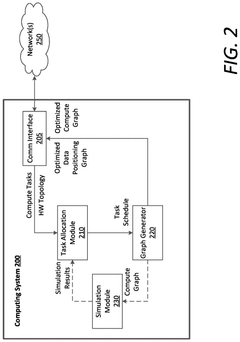

Systems and methods of optimizing compute tasks

PatentPendingUS20250045113A1

Innovation

- A computing system that determines a set of weighted parameters for a given hardware topology, optimally distributes runnables of a compute graph, and optimizes data positioning in memory components to facilitate efficient execution, using techniques such as the traveling salesman algorithm and learning-based approaches.

QoS Implementation Strategies and Performance Metrics

Quality of Service (QoS) implementation in UCIe Coherent Fabrics requires sophisticated strategies to ensure optimal performance across diverse workloads. The primary QoS mechanisms include traffic classification, prioritization schemes, and bandwidth allocation techniques that work in concert to maintain service level agreements.

Traffic classification in UCIe environments typically employs a multi-level approach, categorizing transactions based on urgency, data size, and application requirements. This classification serves as the foundation for subsequent QoS decisions, with most implementations supporting 8-16 distinct traffic classes to balance granularity with management complexity.

Prioritization schemes within UCIe fabrics commonly utilize both static and dynamic models. Static prioritization assigns fixed values to different traffic types, while dynamic approaches adjust priorities based on real-time system conditions, such as queue depths and latency measurements. Advanced implementations incorporate adaptive algorithms that can rebalance priorities in response to changing workload characteristics.

Bandwidth allocation strategies typically employ weighted fair queuing (WFQ) or deficit round-robin (DRR) algorithms, which have demonstrated superior performance in heterogeneous computing environments. These algorithms ensure that high-priority traffic receives guaranteed bandwidth while preventing complete starvation of lower-priority transactions.

Performance metrics for evaluating QoS effectiveness in UCIe fabrics include transaction latency distribution, throughput consistency, and fairness indices. Latency measurements must consider both average and tail latencies, as the latter significantly impacts application-level performance. Industry benchmarks suggest that effective QoS implementations should maintain 99th percentile latencies within 2-3x of median latencies across varying load conditions.

Throughput consistency metrics evaluate the system's ability to maintain predictable performance under varying load conditions. The coefficient of variation (CV) for bandwidth utilization serves as a key indicator, with lower values signifying more consistent performance. Leading implementations typically achieve CV values below 0.15 under normal operating conditions.

Fairness indices, particularly Jain's fairness index, quantify how equitably resources are distributed among competing traffic flows. Optimal UCIe fabric implementations typically maintain fairness indices above 0.85, ensuring that no single traffic class dominates the available resources to the detriment of others.

Resource utilization efficiency represents another critical performance dimension, measuring how effectively the fabric converts allocated resources into useful work. This metric combines throughput measurements with power consumption data to derive performance-per-watt figures that are increasingly important in data center environments.

Traffic classification in UCIe environments typically employs a multi-level approach, categorizing transactions based on urgency, data size, and application requirements. This classification serves as the foundation for subsequent QoS decisions, with most implementations supporting 8-16 distinct traffic classes to balance granularity with management complexity.

Prioritization schemes within UCIe fabrics commonly utilize both static and dynamic models. Static prioritization assigns fixed values to different traffic types, while dynamic approaches adjust priorities based on real-time system conditions, such as queue depths and latency measurements. Advanced implementations incorporate adaptive algorithms that can rebalance priorities in response to changing workload characteristics.

Bandwidth allocation strategies typically employ weighted fair queuing (WFQ) or deficit round-robin (DRR) algorithms, which have demonstrated superior performance in heterogeneous computing environments. These algorithms ensure that high-priority traffic receives guaranteed bandwidth while preventing complete starvation of lower-priority transactions.

Performance metrics for evaluating QoS effectiveness in UCIe fabrics include transaction latency distribution, throughput consistency, and fairness indices. Latency measurements must consider both average and tail latencies, as the latter significantly impacts application-level performance. Industry benchmarks suggest that effective QoS implementations should maintain 99th percentile latencies within 2-3x of median latencies across varying load conditions.

Throughput consistency metrics evaluate the system's ability to maintain predictable performance under varying load conditions. The coefficient of variation (CV) for bandwidth utilization serves as a key indicator, with lower values signifying more consistent performance. Leading implementations typically achieve CV values below 0.15 under normal operating conditions.

Fairness indices, particularly Jain's fairness index, quantify how equitably resources are distributed among competing traffic flows. Optimal UCIe fabric implementations typically maintain fairness indices above 0.85, ensuring that no single traffic class dominates the available resources to the detriment of others.

Resource utilization efficiency represents another critical performance dimension, measuring how effectively the fabric converts allocated resources into useful work. This metric combines throughput measurements with power consumption data to derive performance-per-watt figures that are increasingly important in data center environments.

Interoperability and Compliance Testing Frameworks

The development of robust interoperability and compliance testing frameworks is essential for the successful implementation of UCIe Coherent Fabrics across diverse computing environments. These frameworks ensure that different implementations of PCIe/CXL mapping, ordering rules, and QoS mechanisms can work together seamlessly, maintaining system integrity and performance.

Current testing frameworks for UCIe coherent fabrics focus on three primary areas: protocol compliance, interoperability verification, and performance validation. Protocol compliance testing ensures that implementations adhere to the UCIe specification's requirements for PCIe/CXL mapping, including address translation mechanisms, memory coherence protocols, and transaction ordering rules. These tests typically employ specialized hardware and software tools that can generate specific traffic patterns and monitor responses.

Interoperability verification frameworks test the ability of components from different vendors to work together within the UCIe ecosystem. This includes testing of die-to-die connections, package-to-package interfaces, and system-level integration. The UCIe Consortium has established reference implementations and test suites that vendors can use to validate their products against the standard.

Performance validation frameworks measure the efficiency of QoS implementations, latency characteristics, and bandwidth utilization under various workloads. These tests are crucial for ensuring that the theoretical benefits of UCIe coherent fabrics translate to real-world performance improvements.

A significant challenge in testing frameworks is the need to simulate complex multi-die systems with varying traffic patterns and coherence requirements. Advanced simulation environments that can model the behavior of multiple chiplets communicating through UCIe interfaces have been developed to address this challenge. These simulators can inject faults and stress conditions to test the robustness of ordering rules and QoS mechanisms.

Compliance certification programs are emerging as UCIe adoption grows. These programs provide formal verification that products meet the UCIe standard's requirements for coherent fabric implementation. The certification process typically involves both self-testing using approved tools and third-party verification through authorized testing laboratories.

Looking forward, testing frameworks are evolving to address emerging challenges such as security validation, power efficiency testing, and scalability verification for large-scale multi-chiplet systems. As UCIe coherent fabrics become more prevalent in heterogeneous computing environments, testing methodologies will need to expand to cover a wider range of use cases and integration scenarios.

Current testing frameworks for UCIe coherent fabrics focus on three primary areas: protocol compliance, interoperability verification, and performance validation. Protocol compliance testing ensures that implementations adhere to the UCIe specification's requirements for PCIe/CXL mapping, including address translation mechanisms, memory coherence protocols, and transaction ordering rules. These tests typically employ specialized hardware and software tools that can generate specific traffic patterns and monitor responses.

Interoperability verification frameworks test the ability of components from different vendors to work together within the UCIe ecosystem. This includes testing of die-to-die connections, package-to-package interfaces, and system-level integration. The UCIe Consortium has established reference implementations and test suites that vendors can use to validate their products against the standard.

Performance validation frameworks measure the efficiency of QoS implementations, latency characteristics, and bandwidth utilization under various workloads. These tests are crucial for ensuring that the theoretical benefits of UCIe coherent fabrics translate to real-world performance improvements.

A significant challenge in testing frameworks is the need to simulate complex multi-die systems with varying traffic patterns and coherence requirements. Advanced simulation environments that can model the behavior of multiple chiplets communicating through UCIe interfaces have been developed to address this challenge. These simulators can inject faults and stress conditions to test the robustness of ordering rules and QoS mechanisms.

Compliance certification programs are emerging as UCIe adoption grows. These programs provide formal verification that products meet the UCIe standard's requirements for coherent fabric implementation. The certification process typically involves both self-testing using approved tools and third-party verification through authorized testing laboratories.

Looking forward, testing frameworks are evolving to address emerging challenges such as security validation, power efficiency testing, and scalability verification for large-scale multi-chiplet systems. As UCIe coherent fabrics become more prevalent in heterogeneous computing environments, testing methodologies will need to expand to cover a wider range of use cases and integration scenarios.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!