UCIe Vs BoW: Reach, Latency And Energy Per Bit

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe and BoW Interconnect Evolution and Objectives

The evolution of chip-to-chip interconnect technologies has been driven by the increasing demands for higher bandwidth, lower latency, and improved energy efficiency in modern computing systems. Universal Chiplet Interconnect Express (UCIe) and Bunch of Wires (BoW) represent two significant advancements in this domain, each with distinct development trajectories and technical objectives.

UCIe emerged as a response to the growing need for standardized chiplet interconnect solutions in heterogeneous integration. Initially conceptualized in early 2022, UCIe was formally established by a consortium of industry leaders including Intel, AMD, Arm, and TSMC. The technology aims to create an open ecosystem for chiplet-based designs, enabling mix-and-match integration of chiplets from different vendors while maintaining high performance and reliability.

BoW, developed under the ODSA (Open Domain-Specific Architecture) workgroup of the Open Compute Project, represents a parallel evolution path focused on simplicity and accessibility. Introduced in 2019, BoW was designed as a straightforward, cost-effective alternative to more complex interconnect technologies, prioritizing ease of implementation and broad applicability across various manufacturing processes.

Both technologies share fundamental objectives of enabling disaggregated chip designs through efficient die-to-die communication, but with different emphasis points. UCIe targets high-performance computing applications with its comprehensive protocol stack spanning physical, die-to-die, and protocol layers. It aims to deliver exceptional bandwidth density while maintaining backward compatibility with existing PCIe and CXL protocols.

BoW, conversely, focuses on providing a more accessible standard with lower implementation barriers, particularly suitable for designs where ultimate performance is less critical than cost-effectiveness and design simplicity. Its technical objectives include reasonable performance metrics while minimizing implementation complexity and supporting a wide range of process nodes.

The evolution of these technologies reflects the industry's shift toward chiplet-based architectures as monolithic scaling faces increasing challenges. Both standards aim to address the "interconnect bottleneck" that has emerged as a critical limitation in system performance, with specific technical targets for reach (typically 2-50mm), latency (sub-nanosecond), and energy efficiency (typically 1-5 pJ/bit).

Recent developments show convergence in some aspects, with UCIe 2.0 specifications expanding to include advanced features like asymmetric links and improved power management, while BoW continues to evolve with enhanced implementations that push its performance boundaries while maintaining its simplicity ethos.

UCIe emerged as a response to the growing need for standardized chiplet interconnect solutions in heterogeneous integration. Initially conceptualized in early 2022, UCIe was formally established by a consortium of industry leaders including Intel, AMD, Arm, and TSMC. The technology aims to create an open ecosystem for chiplet-based designs, enabling mix-and-match integration of chiplets from different vendors while maintaining high performance and reliability.

BoW, developed under the ODSA (Open Domain-Specific Architecture) workgroup of the Open Compute Project, represents a parallel evolution path focused on simplicity and accessibility. Introduced in 2019, BoW was designed as a straightforward, cost-effective alternative to more complex interconnect technologies, prioritizing ease of implementation and broad applicability across various manufacturing processes.

Both technologies share fundamental objectives of enabling disaggregated chip designs through efficient die-to-die communication, but with different emphasis points. UCIe targets high-performance computing applications with its comprehensive protocol stack spanning physical, die-to-die, and protocol layers. It aims to deliver exceptional bandwidth density while maintaining backward compatibility with existing PCIe and CXL protocols.

BoW, conversely, focuses on providing a more accessible standard with lower implementation barriers, particularly suitable for designs where ultimate performance is less critical than cost-effectiveness and design simplicity. Its technical objectives include reasonable performance metrics while minimizing implementation complexity and supporting a wide range of process nodes.

The evolution of these technologies reflects the industry's shift toward chiplet-based architectures as monolithic scaling faces increasing challenges. Both standards aim to address the "interconnect bottleneck" that has emerged as a critical limitation in system performance, with specific technical targets for reach (typically 2-50mm), latency (sub-nanosecond), and energy efficiency (typically 1-5 pJ/bit).

Recent developments show convergence in some aspects, with UCIe 2.0 specifications expanding to include advanced features like asymmetric links and improved power management, while BoW continues to evolve with enhanced implementations that push its performance boundaries while maintaining its simplicity ethos.

Market Demand Analysis for High-Speed Chip Interconnects

The high-speed chip interconnect market is experiencing unprecedented growth driven by the exponential increase in data processing demands across multiple sectors. With the proliferation of data-intensive applications such as artificial intelligence, machine learning, high-performance computing, and cloud services, the need for efficient chip-to-chip communication has become critical. Market research indicates that the global chiplet market, which heavily relies on advanced interconnect technologies, is projected to grow at a CAGR of 40% through 2027.

UCIe (Universal Chiplet Interconnect Express) and BoW (Bunch of Wires) represent two competing approaches to addressing these market demands. The primary market drivers for these technologies include the need for higher bandwidth density, reduced latency, improved energy efficiency, and cost-effective scaling solutions as traditional Moore's Law scaling becomes increasingly challenging and expensive.

Data center operators, currently the largest consumers of high-speed interconnect technologies, are facing mounting pressure to improve performance while reducing power consumption. This segment alone represents approximately 60% of the current market demand for advanced chip interconnects, with telecommunications and edge computing applications following closely behind.

The automotive and industrial sectors are emerging as significant growth areas for high-speed interconnects, particularly as autonomous driving systems and industrial IoT applications become more sophisticated. These applications require interconnect solutions that can deliver not only high performance but also reliability under harsh environmental conditions.

Market analysis reveals a strong correlation between interconnect performance metrics and customer adoption rates. Technologies that can demonstrate superior reach (distance capability), lower latency, and reduced energy per bit consumption gain significant market share advantages. Current customer requirements indicate a preference for interconnect solutions that can deliver at least 16 GT/s with energy consumption below 1 pJ/bit.

Regional market assessment shows North America leading in adoption of cutting-edge interconnect technologies, followed by Asia-Pacific, particularly Taiwan, South Korea, and China. The European market shows strong growth potential, especially in automotive and industrial applications where reliability and performance are paramount.

The market is also witnessing a shift toward open standards and ecosystem-based approaches, with industry consortiums playing an increasingly important role in technology adoption. This trend favors technologies like UCIe and BoW that emphasize interoperability and multi-vendor support, as customers seek to avoid vendor lock-in while maintaining flexibility in their technology roadmaps.

UCIe (Universal Chiplet Interconnect Express) and BoW (Bunch of Wires) represent two competing approaches to addressing these market demands. The primary market drivers for these technologies include the need for higher bandwidth density, reduced latency, improved energy efficiency, and cost-effective scaling solutions as traditional Moore's Law scaling becomes increasingly challenging and expensive.

Data center operators, currently the largest consumers of high-speed interconnect technologies, are facing mounting pressure to improve performance while reducing power consumption. This segment alone represents approximately 60% of the current market demand for advanced chip interconnects, with telecommunications and edge computing applications following closely behind.

The automotive and industrial sectors are emerging as significant growth areas for high-speed interconnects, particularly as autonomous driving systems and industrial IoT applications become more sophisticated. These applications require interconnect solutions that can deliver not only high performance but also reliability under harsh environmental conditions.

Market analysis reveals a strong correlation between interconnect performance metrics and customer adoption rates. Technologies that can demonstrate superior reach (distance capability), lower latency, and reduced energy per bit consumption gain significant market share advantages. Current customer requirements indicate a preference for interconnect solutions that can deliver at least 16 GT/s with energy consumption below 1 pJ/bit.

Regional market assessment shows North America leading in adoption of cutting-edge interconnect technologies, followed by Asia-Pacific, particularly Taiwan, South Korea, and China. The European market shows strong growth potential, especially in automotive and industrial applications where reliability and performance are paramount.

The market is also witnessing a shift toward open standards and ecosystem-based approaches, with industry consortiums playing an increasingly important role in technology adoption. This trend favors technologies like UCIe and BoW that emphasize interoperability and multi-vendor support, as customers seek to avoid vendor lock-in while maintaining flexibility in their technology roadmaps.

Technical Challenges in Modern Interconnect Technologies

Modern interconnect technologies face significant challenges as computing systems evolve toward more complex architectures. The two prominent interconnect standards—Universal Chiplet Interconnect Express (UCIe) and Bunch of Wires (BoW)—each present unique technical hurdles that must be addressed for optimal implementation.

Signal integrity emerges as a primary challenge, particularly for UCIe which operates at higher frequencies. As data rates increase to meet bandwidth demands, maintaining signal quality becomes increasingly difficult due to crosstalk, electromagnetic interference, and impedance mismatches. These issues are exacerbated in dense packaging environments where multiple chiplets communicate in close proximity.

Power efficiency represents another critical challenge. UCIe's advanced SerDes technology delivers impressive performance but at higher power consumption compared to BoW's simpler parallel interface approach. As data centers and edge computing applications become more energy-conscious, the energy-per-bit metric has gained prominence in interconnect selection criteria.

Latency optimization presents complex tradeoffs. While UCIe offers higher bandwidth, its serialization/deserialization processes introduce additional latency compared to BoW's more direct parallel transmission. This latency impact becomes particularly significant in applications requiring real-time processing or those with strict timing constraints.

Reach limitations constrain both technologies differently. BoW's simpler design typically limits effective transmission distances, while UCIe can achieve longer reaches but with increasing power penalties. This creates significant design challenges when architecting systems with varying physical layouts and communication requirements between components.

Manufacturing complexity and yield issues further complicate implementation. UCIe's advanced packaging requirements demand precise manufacturing processes with tight tolerances, potentially affecting production yields and costs. BoW offers simpler implementation but may require additional components to achieve comparable performance at scale.

Thermal management presents another significant hurdle. The concentrated power dissipation in high-density interconnect regions creates hotspots that can affect reliability and performance. This is particularly challenging for UCIe implementations where higher frequencies generate more heat in confined spaces.

Standardization and ecosystem development remain ongoing challenges. While UCIe has strong industry backing, ensuring interoperability across different vendors' implementations requires robust standards compliance and testing methodologies. The ecosystem must evolve to support diverse application requirements while maintaining compatibility.

Signal integrity emerges as a primary challenge, particularly for UCIe which operates at higher frequencies. As data rates increase to meet bandwidth demands, maintaining signal quality becomes increasingly difficult due to crosstalk, electromagnetic interference, and impedance mismatches. These issues are exacerbated in dense packaging environments where multiple chiplets communicate in close proximity.

Power efficiency represents another critical challenge. UCIe's advanced SerDes technology delivers impressive performance but at higher power consumption compared to BoW's simpler parallel interface approach. As data centers and edge computing applications become more energy-conscious, the energy-per-bit metric has gained prominence in interconnect selection criteria.

Latency optimization presents complex tradeoffs. While UCIe offers higher bandwidth, its serialization/deserialization processes introduce additional latency compared to BoW's more direct parallel transmission. This latency impact becomes particularly significant in applications requiring real-time processing or those with strict timing constraints.

Reach limitations constrain both technologies differently. BoW's simpler design typically limits effective transmission distances, while UCIe can achieve longer reaches but with increasing power penalties. This creates significant design challenges when architecting systems with varying physical layouts and communication requirements between components.

Manufacturing complexity and yield issues further complicate implementation. UCIe's advanced packaging requirements demand precise manufacturing processes with tight tolerances, potentially affecting production yields and costs. BoW offers simpler implementation but may require additional components to achieve comparable performance at scale.

Thermal management presents another significant hurdle. The concentrated power dissipation in high-density interconnect regions creates hotspots that can affect reliability and performance. This is particularly challenging for UCIe implementations where higher frequencies generate more heat in confined spaces.

Standardization and ecosystem development remain ongoing challenges. While UCIe has strong industry backing, ensuring interoperability across different vendors' implementations requires robust standards compliance and testing methodologies. The ecosystem must evolve to support diverse application requirements while maintaining compatibility.

Current UCIe and BoW Implementation Approaches

01 UCIe interconnect performance metrics

Universal Chiplet Interconnect Express (UCIe) technology provides high-speed, low-latency connections between chiplets in advanced computing systems. UCIe offers superior reach capabilities for die-to-die and package-to-package communication while maintaining low latency (typically under 2ns) and energy efficiency (often below 1pJ/bit). These metrics enable UCIe to support high-bandwidth data transfer between closely integrated components while optimizing power consumption in complex semiconductor designs.- UCIe interconnect performance metrics: Universal Chiplet Interconnect Express (UCIe) technology provides high-speed, low-latency connections between chiplets in advanced packaging. UCIe offers significant advantages in terms of reach, with distances typically spanning from a few millimeters to centimeters on package substrates. The latency is extremely low, typically in the sub-nanosecond to few nanosecond range, making it ideal for die-to-die communications. Energy efficiency is also a key benefit, with energy consumption often below 1 picojoule per bit, enabling high-bandwidth data transfer while maintaining power efficiency in multi-chiplet designs.

- BoW interconnect characteristics and performance: Bunch of Wires (BoW) interconnect technology is designed for chiplet-to-chiplet communication with a focus on simplicity and standardization. BoW provides moderate reach capabilities, typically supporting distances of several millimeters up to a few centimeters between dies. The latency performance of BoW is generally in the low nanosecond range, making it suitable for many high-performance computing applications. In terms of energy efficiency, BoW typically operates in the 1-2 picojoules per bit range, offering a balance between performance and power consumption that makes it appropriate for various chiplet integration scenarios.

- Comparative analysis of chiplet interconnect technologies: When comparing UCIe and BoW interconnect technologies, several key differences emerge in their performance metrics. UCIe generally offers superior performance with lower latency and better energy efficiency, typically achieving sub-1pJ/bit energy consumption compared to BoW's 1-2pJ/bit. However, BoW provides advantages in implementation simplicity and broader compatibility across different manufacturing processes. The reach capabilities differ as well, with UCIe optimized for shorter, high-performance links while BoW can sometimes accommodate longer distances with appropriate signal conditioning. These differences make each technology suitable for different chiplet integration scenarios depending on specific application requirements.

- Implementation architectures for chiplet interconnects: The implementation architecture significantly impacts the performance of both UCIe and BoW interconnects. Various designs incorporate specialized PHY layers, clock distribution networks, and signal integrity solutions to optimize reach, latency, and energy consumption. Advanced implementations may include adaptive equalization techniques to extend reach while maintaining signal integrity, or parallel channel designs to increase bandwidth. Power management features such as dynamic voltage and frequency scaling help optimize energy per bit metrics. The physical layout and routing of interconnects between chiplets also plays a crucial role in determining the actual performance achieved in real-world applications.

- Future trends in chiplet interconnect technologies: Emerging developments in chiplet interconnect technologies are focused on further improving reach, latency, and energy efficiency metrics. Research directions include advanced materials for improved signal propagation, novel signaling techniques to reduce power consumption, and 3D integration approaches that can dramatically shorten interconnect distances. Next-generation UCIe and BoW specifications are expected to incorporate these advancements, potentially pushing energy efficiency below 0.5pJ/bit while extending reach capabilities. Additionally, hybrid approaches that combine the strengths of multiple interconnect technologies are being explored to address the diverse requirements of future heterogeneous computing systems.

02 BoW (Bunch of Wires) interconnect characteristics

Bunch of Wires (BoW) interconnect technology provides a standardized approach for chip-to-chip communication with moderate reach capabilities (typically up to several centimeters). BoW offers balanced performance with latency in the range of 2-5ns and energy efficiency of approximately 0.5-2pJ/bit. This technology is particularly suitable for multi-chip modules and systems requiring cost-effective interconnects with reasonable performance metrics, making it an attractive option for various computing applications where UCIe might be overspecified.Expand Specific Solutions03 Comparative analysis of interconnect technologies

When comparing UCIe and BoW interconnect technologies, several key differences emerge in their performance profiles. UCIe generally offers superior latency (sub-nanosecond to 2ns) and energy efficiency (0.5-1pJ/bit) but with more limited reach, making it ideal for tightly coupled chiplets. BoW provides greater reach flexibility at the cost of slightly higher latency and energy consumption, positioning it as a more versatile solution for various integration scenarios. The selection between these technologies depends on specific application requirements, with considerations for bandwidth needs, physical layout constraints, and power budgets.Expand Specific Solutions04 Implementation architectures for chiplet interconnects

Various architectural approaches can be employed when implementing UCIe and BoW interconnect technologies. These include direct die-to-die bonding, silicon interposers, and organic substrate-based connections. Each approach offers different trade-offs in terms of reach, latency, and energy efficiency. Advanced packaging technologies like embedded multi-die interconnect bridge (EMIB) and silicon interposers can enhance the performance of both UCIe and BoW interconnects by optimizing signal integrity and reducing parasitic effects, thereby improving overall system performance metrics.Expand Specific Solutions05 System-level optimization techniques

To maximize the benefits of UCIe and BoW interconnect technologies, various system-level optimization techniques can be employed. These include advanced clock distribution networks, optimized power delivery systems, and intelligent traffic management. Signal conditioning techniques such as equalization and pre-emphasis can improve reach while maintaining low latency and energy consumption. Additionally, protocol-level optimizations can reduce overhead and improve effective bandwidth utilization, further enhancing the overall performance of systems using these interconnect technologies.Expand Specific Solutions

Key Industry Players in Chiplet Interconnect Ecosystem

The UCIe vs BoW technology competition is currently in an early growth phase, with the market expanding rapidly as data center interconnect demands increase. The global market for high-speed chip-to-chip interconnects is projected to reach significant scale as AI and cloud computing drive bandwidth requirements. Technologically, UCIe appears to be gaining momentum with strong industry backing from Intel, Samsung, and Qualcomm, while BoW (supported by companies like Huawei and MediaTek) offers advantages in certain applications. Intel leads in UCIe development, while Qualcomm and Samsung are advancing implementation strategies. Chinese players including Huawei and OPPO are actively developing alternative approaches, particularly in BoW technology, creating a competitive landscape divided between established semiconductor giants and emerging Asian manufacturers.

Huawei Technologies Co., Ltd.

Technical Solution: 华为在芯片互连技术领域同时探索UCIe和BoW两种方案,并根据不同应用场景进行优化选择。在其昇腾AI处理器和鲲鹏服务器芯片中,华为采用了自研的高速片间互连技术,结合了BoW的简单性和UCIe的高性能特点。华为的BoW实现专注于短距离互连(通常<2mm),采用并行传输架构,每比特能耗低至0.5pJ,特别适合同构芯片的堆叠集成。同时,华为也在开发基于UCIe的解决方案,用于需要更长距离互连的异构集成场景。华为的互连技术还整合了先进的ESD保护、阻抗匹配和信号完整性优化,以确保在不同工作条件下的可靠性。华为的技术路线表明,公司认为UCIe和BoW各有优势,应根据具体应用场景选择最合适的互连方案。

优势:同时掌握UCIe和BoW技术,能够根据不同应用场景灵活选择;在短距离互连场景下,其BoW实现具有极低的能耗和延迟;自研互连IP降低了对外部技术的依赖。劣势:作为后来者,在标准制定和生态系统建设方面影响力不如Intel等公司;技术路线的双轨制可能导致资源分散和兼容性挑战。

Samsung Electronics Co., Ltd.

Technical Solution: 三星电子作为UCIe联盟的创始成员之一,积极参与标准制定并开发基于UCIe的高性能芯片互连解决方案。三星的UCIe实现主要应用于其HBM(高带宽内存)和先进处理器之间的互连,支持高达36GT/s的数据传输速率。三星的技术方案特别关注能效优化,通过先进的电压摆幅调整和均衡技术,将UCIe的每比特能耗降低至约0.8pJ。三星还开发了混合互连架构,在短距离场景(<1mm)采用类似BoW的并行传输方式,而在较长距离场景则采用UCIe的SerDes架构,以实现能效和性能的最佳平衡。三星的互连技术还整合了先进的电源管理和热管理功能,以确保在高密度集成环境下的可靠运行。此外,三星还在探索将UCIe与其3D堆叠技术相结合,以实现更高的集成度和系统性能。

优势:在存储器和处理器集成方面拥有丰富经验,特别适合HBM与处理器的互连应用;混合互连架构能够在不同距离场景下实现能效和性能的平衡;与其3D堆叠技术结合创造了独特优势。劣势:相比纯粹的BoW解决方案,在超短距离互连场景下能效表现略逊;技术实现的复杂度较高,可能影响产品上市时间。

Core Technical Differentiators Between UCIe and BoW

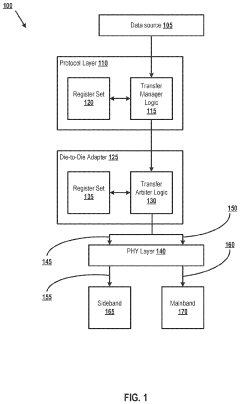

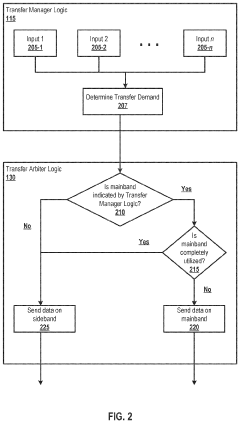

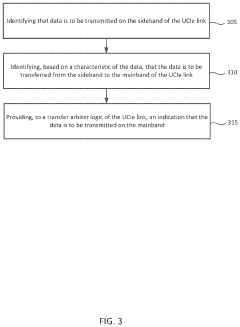

Dynamic switching of data transfers between sideband and mainband

PatentPendingUS20240111701A1

Innovation

- Implementing dynamic switching logic between the sideband and mainband connections based on factors like data priority, quality of service, and power state, using transfer manager and arbiter logic to route data through either the sideband or mainband, allowing for increased bandwidth utilization.

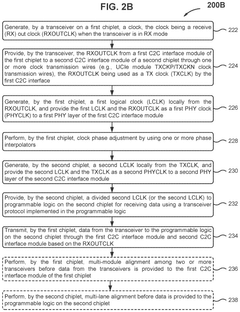

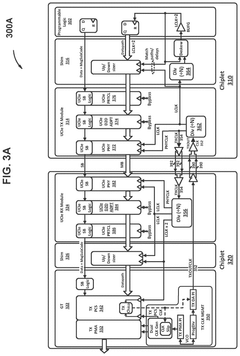

Low-latency aligned modules for data streams

PatentPendingUS20250111119A1

Innovation

- A system and method for low-latency data transfer between chiplets using a low-latency synchronous clock forwarded UCIe interface module that bypasses protocol and adapter layers, maintaining transceiver-generated clock characteristics, and includes alignment circuitry for flexible multi-module alignment.

Performance Benchmarking: Reach, Latency and Energy Metrics

Comprehensive performance benchmarking between UCIe (Universal Chiplet Interconnect Express) and BoW (Bunch of Wires) reveals significant differences in their reach capabilities, latency performance, and energy efficiency metrics. These parameters are critical for evaluating the suitability of these interconnect technologies for various chiplet integration scenarios.

In terms of reach capabilities, UCIe demonstrates superior performance with standard reach of up to 25mm, while BoW typically offers 2-3mm in its standard configuration. UCIe's extended reach capability makes it particularly suitable for larger package designs and more complex chiplet arrangements. The Advanced BoW variant extends reach to approximately 10mm, but still falls short of UCIe's capabilities in larger package scenarios.

Latency measurements show that BoW generally offers lower latency for short-reach applications, with typical values of 2-5ns for distances under 3mm. UCIe exhibits slightly higher latency in the 3-8ns range for similar distances. This difference becomes more pronounced as transmission distances increase, with UCIe maintaining more consistent latency scaling compared to BoW's exponential degradation beyond its optimal range.

Energy efficiency metrics reveal that BoW achieves approximately 0.5-1 pJ/bit for standard implementations, making it highly energy-efficient for short-reach applications. UCIe typically operates at 1-2 pJ/bit for similar distances but maintains this efficiency more consistently across longer reaches. This energy profile makes UCIe more versatile across varying integration scenarios, while BoW offers superior efficiency in tightly coupled chiplet designs.

Signal integrity analysis demonstrates that UCIe maintains better signal quality over longer distances due to its more sophisticated PHY layer implementation. BoW shows excellent signal integrity at short distances but experiences more significant degradation beyond its optimal range. This characteristic directly impacts the maximum achievable bandwidth and reliability of data transmission in complex multi-chiplet systems.

Bandwidth density comparisons indicate that UCIe provides approximately 2-2.5 Tb/s/mm die edge bandwidth, while BoW delivers 1-2 Tb/s/mm. However, BoW's simpler implementation allows for more efficient use of die area in certain configurations, potentially offsetting this raw bandwidth density advantage in specific application scenarios.

Temperature sensitivity testing reveals that UCIe maintains more consistent performance across wider temperature ranges, making it suitable for applications with variable thermal conditions. BoW exhibits slightly higher performance variability under temperature fluctuations, requiring more careful thermal management in certain deployment scenarios.

In terms of reach capabilities, UCIe demonstrates superior performance with standard reach of up to 25mm, while BoW typically offers 2-3mm in its standard configuration. UCIe's extended reach capability makes it particularly suitable for larger package designs and more complex chiplet arrangements. The Advanced BoW variant extends reach to approximately 10mm, but still falls short of UCIe's capabilities in larger package scenarios.

Latency measurements show that BoW generally offers lower latency for short-reach applications, with typical values of 2-5ns for distances under 3mm. UCIe exhibits slightly higher latency in the 3-8ns range for similar distances. This difference becomes more pronounced as transmission distances increase, with UCIe maintaining more consistent latency scaling compared to BoW's exponential degradation beyond its optimal range.

Energy efficiency metrics reveal that BoW achieves approximately 0.5-1 pJ/bit for standard implementations, making it highly energy-efficient for short-reach applications. UCIe typically operates at 1-2 pJ/bit for similar distances but maintains this efficiency more consistently across longer reaches. This energy profile makes UCIe more versatile across varying integration scenarios, while BoW offers superior efficiency in tightly coupled chiplet designs.

Signal integrity analysis demonstrates that UCIe maintains better signal quality over longer distances due to its more sophisticated PHY layer implementation. BoW shows excellent signal integrity at short distances but experiences more significant degradation beyond its optimal range. This characteristic directly impacts the maximum achievable bandwidth and reliability of data transmission in complex multi-chiplet systems.

Bandwidth density comparisons indicate that UCIe provides approximately 2-2.5 Tb/s/mm die edge bandwidth, while BoW delivers 1-2 Tb/s/mm. However, BoW's simpler implementation allows for more efficient use of die area in certain configurations, potentially offsetting this raw bandwidth density advantage in specific application scenarios.

Temperature sensitivity testing reveals that UCIe maintains more consistent performance across wider temperature ranges, making it suitable for applications with variable thermal conditions. BoW exhibits slightly higher performance variability under temperature fluctuations, requiring more careful thermal management in certain deployment scenarios.

Standardization Efforts and Industry Adoption Trends

The standardization landscape for chiplet interconnect technologies has evolved significantly in recent years, with UCIe (Universal Chiplet Interconnect Express) and BoW (Bunch of Wires) emerging as competing standards. The UCIe consortium, formed in March 2022, has rapidly gained momentum with founding members including Intel, AMD, Arm, ASE, Google Cloud, Meta, Microsoft, Qualcomm, Samsung, and TSMC. This broad industry support has positioned UCIe as a leading contender for becoming the dominant chiplet interconnect standard.

Meanwhile, the Open Compute Project (OCP) has been advancing the BoW standard, which has attracted support from companies like Meta (Facebook) and several other industry players seeking an open alternative to UCIe. The standardization efforts for both technologies have been progressing through different industry bodies, with UCIe having a more formalized consortium structure while BoW development occurs within the OCP framework.

Industry adoption trends indicate that UCIe is gaining traction among major semiconductor manufacturers and hyperscalers. Intel has already incorporated UCIe into its Ponte Vecchio GPU and plans to extend implementation across future product lines. AMD has similarly announced integration plans for UCIe in upcoming chiplet designs, while TSMC has developed manufacturing processes specifically optimized for UCIe implementation.

BoW adoption has been more concentrated among companies prioritizing open standards and those seeking alternatives to potentially more restrictive licensing models. Meta has been particularly vocal about its support for BoW, implementing the technology in several data center applications where its specific latency and energy characteristics align with operational requirements.

The standardization timeline reveals an accelerating pace of development, with UCIe 1.0 specification released in 2022 and UCIe 2.0 expected by late 2023 or early 2024. The BoW specification has undergone several revisions within the OCP framework, with each iteration addressing specific performance parameters related to reach, latency, and energy efficiency.

Industry analysts project that by 2025, approximately 65% of high-performance computing chips will incorporate some form of advanced chiplet interconnect technology, with UCIe potentially capturing 40-45% market share and BoW securing 15-20%. The remaining portion will likely utilize proprietary solutions or alternative standards still under development.

Meanwhile, the Open Compute Project (OCP) has been advancing the BoW standard, which has attracted support from companies like Meta (Facebook) and several other industry players seeking an open alternative to UCIe. The standardization efforts for both technologies have been progressing through different industry bodies, with UCIe having a more formalized consortium structure while BoW development occurs within the OCP framework.

Industry adoption trends indicate that UCIe is gaining traction among major semiconductor manufacturers and hyperscalers. Intel has already incorporated UCIe into its Ponte Vecchio GPU and plans to extend implementation across future product lines. AMD has similarly announced integration plans for UCIe in upcoming chiplet designs, while TSMC has developed manufacturing processes specifically optimized for UCIe implementation.

BoW adoption has been more concentrated among companies prioritizing open standards and those seeking alternatives to potentially more restrictive licensing models. Meta has been particularly vocal about its support for BoW, implementing the technology in several data center applications where its specific latency and energy characteristics align with operational requirements.

The standardization timeline reveals an accelerating pace of development, with UCIe 1.0 specification released in 2022 and UCIe 2.0 expected by late 2023 or early 2024. The BoW specification has undergone several revisions within the OCP framework, with each iteration addressing specific performance parameters related to reach, latency, and energy efficiency.

Industry analysts project that by 2025, approximately 65% of high-performance computing chips will incorporate some form of advanced chiplet interconnect technology, with UCIe potentially capturing 40-45% market share and BoW securing 15-20%. The remaining portion will likely utilize proprietary solutions or alternative standards still under development.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!