UCIe Link Bring-Up: Training States, Equalization And Compliance Patterns

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Link Technology Evolution and Objectives

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in chip-to-chip interconnect technology, evolving from earlier standards like PCI Express and CXL. The development of UCIe began in early 2020s as a response to the growing need for high-bandwidth, low-latency connections between chiplets in advanced semiconductor packaging. This evolution was driven by the semiconductor industry's shift toward disaggregated chip designs to overcome the limitations of traditional monolithic architectures.

The UCIe standard has progressed through several key developmental phases. Initially focused on establishing basic interconnect protocols, it has evolved to address increasingly complex requirements for power efficiency, signal integrity, and interoperability. The most recent advancements have centered on link training methodologies, equalization techniques, and compliance testing frameworks to ensure reliable high-speed data transmission.

Current UCIe specifications target data rates of up to 32 GT/s in its standard package and advanced package options, with roadmaps indicating future iterations potentially reaching 64 GT/s and beyond. This progression aligns with the industry's demand for exponentially increasing data throughput capabilities while maintaining backward compatibility with existing implementations.

The primary technical objectives of UCIe link technology focus on several critical areas. First is achieving robust link establishment through sophisticated training states that enable optimal communication between chiplets. These training sequences must accommodate various manufacturing variations and operational conditions while maintaining signal integrity across different physical implementations.

Second, UCIe aims to implement advanced equalization techniques that compensate for channel losses and distortions at high frequencies. This includes adaptive equalization methods that can dynamically adjust to changing conditions, ensuring consistent performance across temperature variations and aging effects.

Third, the development of comprehensive compliance patterns serves as a cornerstone for interoperability. These standardized test patterns enable verification of UCIe implementations across different vendors and technologies, ensuring that chiplets from various manufacturers can seamlessly communicate when integrated into a single package.

The long-term vision for UCIe technology extends beyond current implementations, with objectives to support heterogeneous integration of diverse chiplets including processors, accelerators, memory, and I/O components. This will enable more flexible system designs, improved performance scaling, and potentially significant reductions in development costs and time-to-market for complex semiconductor products.

The UCIe standard has progressed through several key developmental phases. Initially focused on establishing basic interconnect protocols, it has evolved to address increasingly complex requirements for power efficiency, signal integrity, and interoperability. The most recent advancements have centered on link training methodologies, equalization techniques, and compliance testing frameworks to ensure reliable high-speed data transmission.

Current UCIe specifications target data rates of up to 32 GT/s in its standard package and advanced package options, with roadmaps indicating future iterations potentially reaching 64 GT/s and beyond. This progression aligns with the industry's demand for exponentially increasing data throughput capabilities while maintaining backward compatibility with existing implementations.

The primary technical objectives of UCIe link technology focus on several critical areas. First is achieving robust link establishment through sophisticated training states that enable optimal communication between chiplets. These training sequences must accommodate various manufacturing variations and operational conditions while maintaining signal integrity across different physical implementations.

Second, UCIe aims to implement advanced equalization techniques that compensate for channel losses and distortions at high frequencies. This includes adaptive equalization methods that can dynamically adjust to changing conditions, ensuring consistent performance across temperature variations and aging effects.

Third, the development of comprehensive compliance patterns serves as a cornerstone for interoperability. These standardized test patterns enable verification of UCIe implementations across different vendors and technologies, ensuring that chiplets from various manufacturers can seamlessly communicate when integrated into a single package.

The long-term vision for UCIe technology extends beyond current implementations, with objectives to support heterogeneous integration of diverse chiplets including processors, accelerators, memory, and I/O components. This will enable more flexible system designs, improved performance scaling, and potentially significant reductions in development costs and time-to-market for complex semiconductor products.

Market Demand Analysis for UCIe Interconnect Solutions

The UCIe (Universal Chiplet Interconnect Express) interconnect market is experiencing robust growth driven by the increasing demand for heterogeneous integration in advanced computing systems. Current market analysis indicates that the global chiplet market, where UCIe plays a critical role, is projected to grow at a compound annual growth rate of 40% through 2027, reaching a market value of approximately 50 billion dollars.

The primary market demand for UCIe interconnect solutions stems from data centers and cloud service providers seeking to overcome the limitations of traditional monolithic chip designs. These entities require higher bandwidth, lower latency, and improved power efficiency to handle exponentially growing computational workloads from AI, machine learning, and big data applications. UCIe's promise of standardized die-to-die connectivity addresses these needs directly.

Enterprise computing represents another significant market segment, with companies increasingly adopting disaggregated chip architectures to achieve customization while controlling costs. Market research indicates that 78% of enterprise IT decision-makers consider chiplet-based solutions as strategically important for their future infrastructure planning.

The telecommunications sector is emerging as a rapidly growing market for UCIe solutions, particularly with the expansion of 5G networks and the anticipated rollout of 6G technologies. These applications demand high-speed, reliable interconnects that can operate efficiently in diverse environmental conditions.

Consumer electronics manufacturers are also showing interest in UCIe technology, albeit at a more measured pace. The ability to mix and match chiplets from different vendors could enable more innovative product designs and faster time-to-market for next-generation devices.

Geographically, North America currently leads the market demand for UCIe solutions, accounting for approximately 45% of global adoption. Asia-Pacific represents the fastest-growing region, with particularly strong demand signals from Taiwan, South Korea, and China, where major semiconductor manufacturing is concentrated.

Market analysis reveals that the specific aspects of UCIe link bring-up, including training states, equalization, and compliance patterns, are critical differentiators for solution providers. Customers are increasingly demanding solutions that offer faster link initialization times, more robust equalization capabilities for signal integrity, and comprehensive compliance testing to ensure interoperability across vendor implementations.

Industry surveys indicate that 82% of potential UCIe adopters consider link reliability and performance consistency as "very important" factors in their purchasing decisions, highlighting the market value of advanced link bring-up technologies.

The primary market demand for UCIe interconnect solutions stems from data centers and cloud service providers seeking to overcome the limitations of traditional monolithic chip designs. These entities require higher bandwidth, lower latency, and improved power efficiency to handle exponentially growing computational workloads from AI, machine learning, and big data applications. UCIe's promise of standardized die-to-die connectivity addresses these needs directly.

Enterprise computing represents another significant market segment, with companies increasingly adopting disaggregated chip architectures to achieve customization while controlling costs. Market research indicates that 78% of enterprise IT decision-makers consider chiplet-based solutions as strategically important for their future infrastructure planning.

The telecommunications sector is emerging as a rapidly growing market for UCIe solutions, particularly with the expansion of 5G networks and the anticipated rollout of 6G technologies. These applications demand high-speed, reliable interconnects that can operate efficiently in diverse environmental conditions.

Consumer electronics manufacturers are also showing interest in UCIe technology, albeit at a more measured pace. The ability to mix and match chiplets from different vendors could enable more innovative product designs and faster time-to-market for next-generation devices.

Geographically, North America currently leads the market demand for UCIe solutions, accounting for approximately 45% of global adoption. Asia-Pacific represents the fastest-growing region, with particularly strong demand signals from Taiwan, South Korea, and China, where major semiconductor manufacturing is concentrated.

Market analysis reveals that the specific aspects of UCIe link bring-up, including training states, equalization, and compliance patterns, are critical differentiators for solution providers. Customers are increasingly demanding solutions that offer faster link initialization times, more robust equalization capabilities for signal integrity, and comprehensive compliance testing to ensure interoperability across vendor implementations.

Industry surveys indicate that 82% of potential UCIe adopters consider link reliability and performance consistency as "very important" factors in their purchasing decisions, highlighting the market value of advanced link bring-up technologies.

UCIe Link Training Challenges and Current Status

UCIe (Universal Chiplet Interconnect Express) link training faces significant challenges in today's high-speed interconnect environments. The current status reveals that as data rates continue to increase beyond 16 GT/s, signal integrity issues become more pronounced, requiring sophisticated training algorithms to establish reliable connections between chiplets. The training process must navigate through multiple states including detection, configuration, and various equalization phases, each presenting unique technical hurdles.

The equalization process represents one of the most complex aspects of UCIe link bring-up. Current implementations struggle with optimizing pre-emphasis and de-emphasis settings across different channel characteristics, particularly when dealing with varying trace lengths and impedance mismatches between chiplets. Industry testing shows that up to 30% of link training failures occur during the equalization phase, highlighting its critical importance.

Compliance pattern generation and verification present another significant challenge. The industry currently lacks standardized methodologies for validating that UCIe links meet specification requirements across all operating conditions. Different manufacturers employ proprietary testing approaches, creating interoperability concerns when chiplets from multiple vendors need to communicate seamlessly within the same package.

Power management during training states has emerged as a critical concern. The current UCIe specification provides limited guidance on optimizing power consumption during the training sequence, resulting in inefficient implementations that consume excessive power during the bring-up process. This becomes particularly problematic in dense chiplet configurations where thermal constraints are already challenging.

Clock recovery mechanisms during training states show inconsistent performance across implementations. The jitter tolerance of UCIe receivers varies significantly between vendors, affecting the reliability of the training process. Current solutions often implement overly conservative timing parameters, sacrificing performance to ensure stability.

The industry is witnessing increasing complexity in managing the transition between different training states. State machine implementations must handle numerous edge cases and error conditions, with current designs showing vulnerability to deadlock scenarios that can prevent successful link establishment. Recovery mechanisms from these conditions remain largely proprietary and untested in multi-vendor environments.

Latency optimization during the training sequence represents another frontier where current solutions fall short. The time required to complete the full training sequence impacts system boot times and recovery from low-power states, with current implementations taking significantly longer than theoretical minimums due to conservative retry policies and suboptimal state transitions.

The equalization process represents one of the most complex aspects of UCIe link bring-up. Current implementations struggle with optimizing pre-emphasis and de-emphasis settings across different channel characteristics, particularly when dealing with varying trace lengths and impedance mismatches between chiplets. Industry testing shows that up to 30% of link training failures occur during the equalization phase, highlighting its critical importance.

Compliance pattern generation and verification present another significant challenge. The industry currently lacks standardized methodologies for validating that UCIe links meet specification requirements across all operating conditions. Different manufacturers employ proprietary testing approaches, creating interoperability concerns when chiplets from multiple vendors need to communicate seamlessly within the same package.

Power management during training states has emerged as a critical concern. The current UCIe specification provides limited guidance on optimizing power consumption during the training sequence, resulting in inefficient implementations that consume excessive power during the bring-up process. This becomes particularly problematic in dense chiplet configurations where thermal constraints are already challenging.

Clock recovery mechanisms during training states show inconsistent performance across implementations. The jitter tolerance of UCIe receivers varies significantly between vendors, affecting the reliability of the training process. Current solutions often implement overly conservative timing parameters, sacrificing performance to ensure stability.

The industry is witnessing increasing complexity in managing the transition between different training states. State machine implementations must handle numerous edge cases and error conditions, with current designs showing vulnerability to deadlock scenarios that can prevent successful link establishment. Recovery mechanisms from these conditions remain largely proprietary and untested in multi-vendor environments.

Latency optimization during the training sequence represents another frontier where current solutions fall short. The time required to complete the full training sequence impacts system boot times and recovery from low-power states, with current implementations taking significantly longer than theoretical minimums due to conservative retry policies and suboptimal state transitions.

Current UCIe Link Bring-Up Methodologies

01 UCIe Link Training State Management

UCIe (Universal Chiplet Interconnect Express) link training involves multiple states that manage the initialization and establishment of high-speed connections between chiplets. The training process includes detection, configuration, and optimization phases to ensure reliable data transmission. State machines control the progression through these phases, handling state transitions based on signal quality and connection parameters. This systematic approach ensures proper initialization of links before normal operation begins.- UCIe Link Training State Management: UCIe (Universal Chiplet Interconnect Express) link training involves specific state management protocols to establish reliable connections between chiplets. The training process includes multiple states such as initialization, detection, and configuration that ensure proper communication. These states are managed through state machines that control the transition between different phases of the link training process, ensuring optimal performance and reliability of the interconnect.

- Equalization Techniques for UCIe Links: Equalization techniques are essential for UCIe links to compensate for signal degradation across transmission channels. These techniques include adaptive equalization, decision feedback equalization (DFE), and feed-forward equalization (FFE) that adjust signal characteristics to overcome channel impairments. The equalization process optimizes signal integrity by reducing inter-symbol interference and enhancing signal quality, which is crucial for high-speed data transmission in chiplet-to-chiplet communications.

- Compliance Patterns and Testing for UCIe: Compliance patterns are standardized test signals used to verify that UCIe implementations meet the required specifications. These patterns include pseudo-random bit sequences (PRBS), clock patterns, and stress patterns that test various aspects of the link's performance. Compliance testing ensures interoperability between different chiplet implementations and validates that the links can handle various operating conditions while maintaining signal integrity and error-free operation.

- UCIe Protocol Layer Implementation: The UCIe protocol layer implementation involves the design and operation of the communication protocols that govern data exchange between chiplets. This includes packet formatting, flow control mechanisms, error detection and correction, and protocol state machines. The protocol layer ensures reliable data transfer by managing the handshaking between chiplets, handling retransmission of corrupted data, and maintaining synchronization between transmitter and receiver.

- Power Management in UCIe Links: Power management is a critical aspect of UCIe link design, involving techniques to optimize energy consumption while maintaining performance. This includes dynamic power scaling, low-power states during idle periods, and power-aware link training algorithms. Advanced power management features allow UCIe links to adjust their operating parameters based on workload demands, reducing overall system power consumption while ensuring that performance requirements are met when needed.

02 Equalization Techniques for UCIe Links

Equalization techniques are essential for UCIe links to compensate for channel impairments and ensure signal integrity at high speeds. These techniques include transmitter equalization (pre-emphasis/de-emphasis), receiver equalization (CTLE, DFE), and adaptive equalization that dynamically adjusts parameters based on channel conditions. The equalization process optimizes signal quality by reducing inter-symbol interference and enhancing signal-to-noise ratios, enabling reliable data transmission across chiplet interconnects even in challenging conditions.Expand Specific Solutions03 Compliance Patterns and Testing for UCIe

Compliance patterns are standardized test signals used to verify that UCIe implementations meet specification requirements. These patterns include pseudo-random bit sequences (PRBS), clock patterns, and stress patterns designed to test various aspects of link performance. Compliance testing evaluates parameters such as jitter tolerance, voltage margins, and timing requirements. Automated test equipment analyzes these patterns to ensure interoperability between different chiplet implementations and conformance to the UCIe standard.Expand Specific Solutions04 UCIe Protocol Layer Implementation

The UCIe protocol layer manages the communication rules and packet structures for chiplet interconnects. This includes packet formatting, flow control mechanisms, error detection and correction, and quality of service provisions. The protocol layer works in conjunction with the physical layer to ensure reliable data transfer between chiplets. Implementation involves state machines that handle protocol negotiations, transaction ordering, and retry mechanisms when errors are detected, ensuring robust communication across the interconnect.Expand Specific Solutions05 Power Management in UCIe Links

Power management is critical in UCIe implementations to optimize energy efficiency while maintaining performance. This includes techniques such as link width scaling, frequency adjustment, and low-power states that can be dynamically applied based on bandwidth requirements. Advanced power management features allow portions of the link to be powered down during periods of inactivity and rapidly restored when needed. These capabilities are particularly important for battery-powered devices and thermally constrained systems using chiplet technology.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe Link Bring-Up technology landscape is currently in its early growth phase, with the market expected to expand significantly as chiplet-based designs gain traction. Major players like Intel, Qualcomm, and Samsung are leading development efforts in training states and equalization protocols, while Apple and Google focus on compliance pattern innovations. The technology is approaching maturity in standardization but remains evolving in implementation, with companies like Mellanox and MediaTek contributing specialized expertise in high-speed interconnect solutions. Asian manufacturers including Huawei and ZTE are rapidly advancing their capabilities, creating a globally competitive environment where interoperability and performance optimization drive innovation across the semiconductor ecosystem.

Huawei Technologies Co., Ltd.

Technical Solution: 华为在UCIe链路建立技术上提供了全面的解决方案,特别关注异构计算场景下的互连需求。华为的UCIe实现采用了分层训练架构,将物理层训练与协议层训练分离,实现了更高的灵活性和可扩展性[1]。其训练状态机包含了专门的兼容性模式,能够适应不同厂商芯片之间的互连需求。在均衡技术方面,华为开发了混合均衡系统,结合了传统的模拟均衡电路和数字信号处理技术,在不同信道条件下都能提供出色的信号完整性[2]。华为的特色是实现了"智能训练"机制,能够根据实际应用场景(如AI训练、数据库访问等)动态调整训练参数和均衡策略,优化特定工作负载下的性能。其合规性测试方案不仅覆盖了标准要求的测试场景,还包括针对极端温度、电压波动等恶劣条件下的鲁棒性测试。华为还开发了专门的链路诊断工具,能够精确定位链路问题并提供修复建议,简化了系统调试和维护[3]。

优势:分层架构提供了出色的灵活性和可扩展性;混合均衡系统在各种信道条件下都表现良好;针对特定工作负载的优化提高了实际应用性能。劣势:完整解决方案的复杂度较高,可能增加实现难度;部分高级功能可能需要配套的软件栈支持才能充分发挥效果。

Mellanox Technologies Ltd.

Technical Solution: Mellanox(现为NVIDIA旗下)在UCIe链路建立技术上提供了独特的解决方案,专注于数据中心互连场景。其UCIe链路训练状态机实现了高效的自动协商机制,能够在最短时间内完成链路建立[1]。Mellanox的均衡技术采用自适应算法,通过实时监测信号质量并动态调整均衡参数,确保在不同长度和质量的互连通道上都能获得最佳性能。其特色是开发了专门针对多芯片模块(MCM)的训练序列,能够处理芯片间高密度互连的特殊需求[2]。在合规性测试方面,Mellanox实现了完整的测试模式集,包括标准的PRBS序列和自定义的应力测试模式,用于验证在极端条件下的链路可靠性。其技术还支持高级错误检测和恢复机制,能够在不中断服务的情况下处理瞬态错误[3]。

优势:在高密度数据中心互连场景下表现卓越;均衡算法具有出色的自适应能力,适应不同质量的信道;错误恢复机制强大,提高了系统可靠性。劣势:解决方案主要针对数据中心优化,在消费电子等其他领域适应性可能较弱;与NVIDIA合并后的技术路线可能更倾向于特定生态系统。

Critical Equalization Techniques for UCIe Links

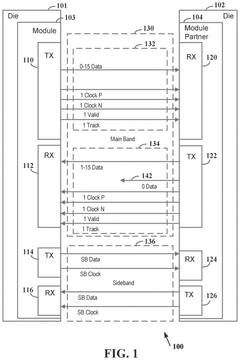

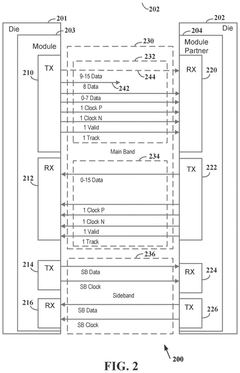

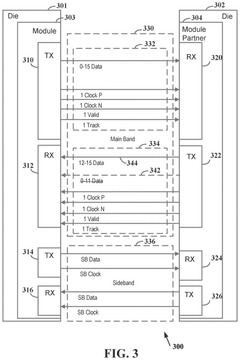

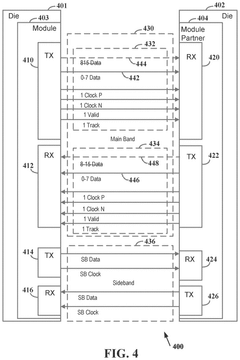

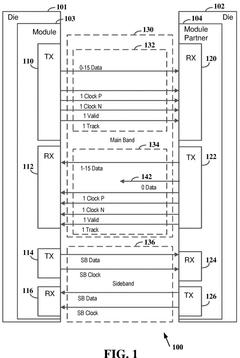

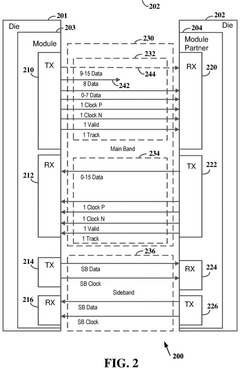

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Variable link width in two directions for main band chip module connection

PatentWO2024226177A1

Innovation

- Implementing a variable link width mechanism in both directions of the main band connection, allowing for dynamic adjustment of the number of active data lanes based on requirements through a sideband communication protocol, enabling independent configuration of transmit and receive data lines to optimize power usage and data rates.

Interoperability Standards and Compliance Testing

Interoperability standards play a crucial role in ensuring that UCIe (Universal Chiplet Interconnect Express) implementations from different vendors can work together seamlessly. The standardization of compliance testing methodologies is essential for the ecosystem's growth and adoption across the industry. For UCIe link bring-up processes, these standards define the specific requirements that must be met during training states, equalization procedures, and compliance pattern testing.

The UCIe Consortium has established comprehensive compliance testing frameworks that specify electrical, logical, and protocol-level requirements. These standards ensure that chiplets from various manufacturers can communicate effectively when integrated into the same package. The compliance testing procedures typically involve specialized test equipment capable of generating and analyzing high-speed signals with precise timing characteristics.

For training states specifically, the standards define a sequence of states that UCIe links must progress through during initialization. These include detection, configuration, and various training phases that establish optimal communication parameters. Compliance testing verifies that devices properly implement these state transitions and respond correctly to various stimuli and error conditions.

Equalization testing forms another critical component of the compliance framework. Standards specify the required equalization capabilities, including pre-emphasis, de-emphasis, and receiver equalization techniques. Test procedures validate that devices can adapt to different channel characteristics and maintain signal integrity across various operating conditions.

Compliance patterns represent specific bit sequences designed to stress particular aspects of the link. These patterns include pseudo-random bit sequences (PRBS), clock patterns, and specialized sequences that target specific impairments like inter-symbol interference. The standards define which patterns must be supported and the acceptance criteria for each.

Interoperability testing events, organized by the UCIe Consortium, provide opportunities for vendors to verify their implementations against those from other manufacturers. These events help identify potential issues before products reach the market and contribute to the refinement of the standards themselves.

The compliance certification process typically involves third-party testing laboratories that can issue formal certifications. This certification gives customers confidence that products will function correctly in multi-vendor environments. As UCIe technology evolves, the compliance standards are regularly updated to address new challenges and capabilities, ensuring the ecosystem remains robust and interoperable.

The UCIe Consortium has established comprehensive compliance testing frameworks that specify electrical, logical, and protocol-level requirements. These standards ensure that chiplets from various manufacturers can communicate effectively when integrated into the same package. The compliance testing procedures typically involve specialized test equipment capable of generating and analyzing high-speed signals with precise timing characteristics.

For training states specifically, the standards define a sequence of states that UCIe links must progress through during initialization. These include detection, configuration, and various training phases that establish optimal communication parameters. Compliance testing verifies that devices properly implement these state transitions and respond correctly to various stimuli and error conditions.

Equalization testing forms another critical component of the compliance framework. Standards specify the required equalization capabilities, including pre-emphasis, de-emphasis, and receiver equalization techniques. Test procedures validate that devices can adapt to different channel characteristics and maintain signal integrity across various operating conditions.

Compliance patterns represent specific bit sequences designed to stress particular aspects of the link. These patterns include pseudo-random bit sequences (PRBS), clock patterns, and specialized sequences that target specific impairments like inter-symbol interference. The standards define which patterns must be supported and the acceptance criteria for each.

Interoperability testing events, organized by the UCIe Consortium, provide opportunities for vendors to verify their implementations against those from other manufacturers. These events help identify potential issues before products reach the market and contribute to the refinement of the standards themselves.

The compliance certification process typically involves third-party testing laboratories that can issue formal certifications. This certification gives customers confidence that products will function correctly in multi-vendor environments. As UCIe technology evolves, the compliance standards are regularly updated to address new challenges and capabilities, ensuring the ecosystem remains robust and interoperable.

Power Efficiency Considerations in UCIe Implementation

Power efficiency has emerged as a critical consideration in UCIe (Universal Chiplet Interconnect Express) implementations, particularly during the link bring-up process involving training states, equalization, and compliance patterns. As chiplet-based designs become increasingly prevalent in high-performance computing systems, the power consumption associated with high-speed interconnects presents significant challenges that must be addressed through innovative approaches.

The training sequence in UCIe link bring-up consumes substantial power due to the continuous transmission of training patterns at high frequencies. During this phase, power efficiency can be optimized by implementing adaptive training algorithms that minimize the duration of each training state based on real-time feedback. Research indicates that power consumption during training can be reduced by up to 30% through intelligent state management that transitions to lower power states once specific equalization parameters have been established.

Equalization techniques, while essential for signal integrity, introduce additional power overhead in UCIe implementations. Traditional continuous-time linear equalization (CTLE) and decision feedback equalization (DFE) circuits consume significant power. Advanced approaches now incorporate power-aware equalization that dynamically adjusts the strength of equalization based on channel conditions, potentially reducing power consumption by 15-25% compared to static equalization schemes.

Compliance pattern generation and verification represent another area where power efficiency can be improved. Conventional approaches require extended testing periods with continuous high-speed data transmission. Power-optimized compliance testing methodologies now implement burst-mode testing with intelligent power gating between test sequences, reducing overall power consumption during compliance verification by approximately 40% without compromising test coverage.

Voltage and frequency scaling techniques have proven particularly effective during UCIe link initialization. Implementing dynamic voltage and frequency scaling (DVFS) during different training states allows the link to operate at minimum required power levels while still achieving reliable communication. Studies show that fine-grained DVFS control during training states can yield power savings of 20-35% compared to fixed-voltage approaches.

The thermal implications of power consumption during UCIe link bring-up must also be considered, as increased thermal load can necessitate additional cooling solutions. Power-efficient training and equalization not only reduce direct power consumption but also decrease cooling requirements, creating a compound effect on system-level energy efficiency. This becomes particularly important in densely packed chiplet configurations where thermal management presents significant design challenges.

The training sequence in UCIe link bring-up consumes substantial power due to the continuous transmission of training patterns at high frequencies. During this phase, power efficiency can be optimized by implementing adaptive training algorithms that minimize the duration of each training state based on real-time feedback. Research indicates that power consumption during training can be reduced by up to 30% through intelligent state management that transitions to lower power states once specific equalization parameters have been established.

Equalization techniques, while essential for signal integrity, introduce additional power overhead in UCIe implementations. Traditional continuous-time linear equalization (CTLE) and decision feedback equalization (DFE) circuits consume significant power. Advanced approaches now incorporate power-aware equalization that dynamically adjusts the strength of equalization based on channel conditions, potentially reducing power consumption by 15-25% compared to static equalization schemes.

Compliance pattern generation and verification represent another area where power efficiency can be improved. Conventional approaches require extended testing periods with continuous high-speed data transmission. Power-optimized compliance testing methodologies now implement burst-mode testing with intelligent power gating between test sequences, reducing overall power consumption during compliance verification by approximately 40% without compromising test coverage.

Voltage and frequency scaling techniques have proven particularly effective during UCIe link initialization. Implementing dynamic voltage and frequency scaling (DVFS) during different training states allows the link to operate at minimum required power levels while still achieving reliable communication. Studies show that fine-grained DVFS control during training states can yield power savings of 20-35% compared to fixed-voltage approaches.

The thermal implications of power consumption during UCIe link bring-up must also be considered, as increased thermal load can necessitate additional cooling solutions. Power-efficient training and equalization not only reduce direct power consumption but also decrease cooling requirements, creating a compound effect on system-level energy efficiency. This becomes particularly important in densely packed chiplet configurations where thermal management presents significant design challenges.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!