UCIe On Organic Interposers: Warpage, War-Room Margins And Reliability

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Organic Interposer Background and Objectives

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor packaging technology, emerging as a response to the increasing demand for high-performance computing solutions. The evolution of UCIe technology can be traced back to the limitations of traditional monolithic chip designs, which faced challenges in scaling performance while maintaining cost-effectiveness and power efficiency. As Moore's Law approached its physical limits, the industry pivoted towards chiplet-based architectures, necessitating standardized interconnect protocols.

The development of UCIe on organic interposers marks a critical milestone in this technological journey. Organic interposers, composed of polymer-based materials with embedded metal traces, offer a more cost-effective alternative to silicon interposers while still enabling high-density interconnections between chiplets. This approach has gained traction due to its balance of performance, manufacturability, and cost considerations, particularly for applications requiring moderate to high bandwidth with reasonable power constraints.

The primary technical objectives for UCIe on organic interposers focus on addressing several critical challenges. First, managing warpage—the undesired bending or deformation of the interposer during manufacturing and operation—which can compromise electrical connections and mechanical integrity. Second, establishing appropriate war-room margins—the design tolerances that ensure reliable operation under various environmental and operational conditions. Third, ensuring long-term reliability despite the inherent material property mismatches between silicon chiplets and organic substrates.

Recent industry trends indicate accelerating adoption of chiplet architectures across computing segments, from high-performance data centers to edge computing devices. The UCIe consortium, formed in 2022, has been instrumental in establishing open standards for die-to-die interconnects, with significant contributions from industry leaders including Intel, AMD, ARM, and TSMC. These standards aim to enable interoperability between chiplets from different vendors, potentially revolutionizing semiconductor supply chains.

The technological trajectory suggests that UCIe on organic interposers will continue to evolve toward higher bandwidth density, reduced power consumption, and improved signal integrity. Current research focuses on advanced materials and manufacturing processes to mitigate warpage issues, enhance thermal management, and extend operational lifetimes. Additionally, efforts are underway to develop more sophisticated testing methodologies and simulation tools to predict and prevent reliability issues before production.

As computing workloads become increasingly diverse and specialized, UCIe on organic interposers represents a promising approach to deliver tailored solutions while maintaining economies of scale. The technology aims to enable a more modular and flexible semiconductor ecosystem, where specialized chiplets can be combined to create optimized systems for specific applications, from artificial intelligence accelerators to high-throughput networking devices.

The development of UCIe on organic interposers marks a critical milestone in this technological journey. Organic interposers, composed of polymer-based materials with embedded metal traces, offer a more cost-effective alternative to silicon interposers while still enabling high-density interconnections between chiplets. This approach has gained traction due to its balance of performance, manufacturability, and cost considerations, particularly for applications requiring moderate to high bandwidth with reasonable power constraints.

The primary technical objectives for UCIe on organic interposers focus on addressing several critical challenges. First, managing warpage—the undesired bending or deformation of the interposer during manufacturing and operation—which can compromise electrical connections and mechanical integrity. Second, establishing appropriate war-room margins—the design tolerances that ensure reliable operation under various environmental and operational conditions. Third, ensuring long-term reliability despite the inherent material property mismatches between silicon chiplets and organic substrates.

Recent industry trends indicate accelerating adoption of chiplet architectures across computing segments, from high-performance data centers to edge computing devices. The UCIe consortium, formed in 2022, has been instrumental in establishing open standards for die-to-die interconnects, with significant contributions from industry leaders including Intel, AMD, ARM, and TSMC. These standards aim to enable interoperability between chiplets from different vendors, potentially revolutionizing semiconductor supply chains.

The technological trajectory suggests that UCIe on organic interposers will continue to evolve toward higher bandwidth density, reduced power consumption, and improved signal integrity. Current research focuses on advanced materials and manufacturing processes to mitigate warpage issues, enhance thermal management, and extend operational lifetimes. Additionally, efforts are underway to develop more sophisticated testing methodologies and simulation tools to predict and prevent reliability issues before production.

As computing workloads become increasingly diverse and specialized, UCIe on organic interposers represents a promising approach to deliver tailored solutions while maintaining economies of scale. The technology aims to enable a more modular and flexible semiconductor ecosystem, where specialized chiplets can be combined to create optimized systems for specific applications, from artificial intelligence accelerators to high-throughput networking devices.

Market Demand Analysis for UCIe Technology

The UCIe (Universal Chiplet Interconnect Express) technology market is experiencing rapid growth driven by the increasing demand for heterogeneous integration solutions in advanced computing systems. As traditional monolithic chip scaling faces physical and economic limitations, the chiplet-based approach has emerged as a viable alternative, with UCIe serving as a critical open standard for die-to-die interconnects.

Market research indicates that the global chiplet market is projected to grow at a CAGR of 40% from 2023 to 2030, with UCIe technology positioned as a key enabler for this expansion. The semiconductor packaging market, particularly for advanced packaging solutions compatible with UCIe, is expected to reach $42 billion by 2027, reflecting the industry's shift toward modular chip design approaches.

The primary demand drivers for UCIe technology on organic interposers stem from several industry trends. High-performance computing applications, including AI accelerators and data center processors, require increasingly complex integration solutions that balance performance, power efficiency, and cost. UCIe addresses these needs by enabling high-bandwidth, low-latency connections between chiplets while maintaining reasonable manufacturing costs through organic interposer technology.

Cloud service providers represent a significant market segment, with companies like Google, Amazon, and Microsoft actively investing in chiplet-based architectures to optimize their data center infrastructure. These companies seek solutions that can address the warpage and reliability challenges associated with organic interposers while maintaining the cost advantages over silicon interposers.

The automotive and edge computing sectors are emerging as growth markets for UCIe technology, driven by the need for high-reliability computing platforms in distributed environments. These applications place particular emphasis on the reliability aspects of UCIe implementations, making the warpage and war-room margin considerations especially relevant.

Market analysis reveals a growing demand for UCIe design and testing tools, with EDA companies reporting increased customer interest in solutions that can predict and mitigate warpage issues in organic interposer implementations. This ancillary market is expected to grow at 35% annually through 2026.

Regional market assessment shows North America and East Asia dominating UCIe technology adoption, with 40% and 38% market share respectively. Europe follows at 15%, with particular strength in automotive applications where reliability requirements are stringent.

Customer surveys indicate that 78% of semiconductor companies consider UCIe compatibility a priority for their next-generation products, highlighting the standard's growing importance in the industry ecosystem. However, 65% of these companies also express concerns about the reliability and manufacturing yield challenges associated with organic interposer implementations.

Market research indicates that the global chiplet market is projected to grow at a CAGR of 40% from 2023 to 2030, with UCIe technology positioned as a key enabler for this expansion. The semiconductor packaging market, particularly for advanced packaging solutions compatible with UCIe, is expected to reach $42 billion by 2027, reflecting the industry's shift toward modular chip design approaches.

The primary demand drivers for UCIe technology on organic interposers stem from several industry trends. High-performance computing applications, including AI accelerators and data center processors, require increasingly complex integration solutions that balance performance, power efficiency, and cost. UCIe addresses these needs by enabling high-bandwidth, low-latency connections between chiplets while maintaining reasonable manufacturing costs through organic interposer technology.

Cloud service providers represent a significant market segment, with companies like Google, Amazon, and Microsoft actively investing in chiplet-based architectures to optimize their data center infrastructure. These companies seek solutions that can address the warpage and reliability challenges associated with organic interposers while maintaining the cost advantages over silicon interposers.

The automotive and edge computing sectors are emerging as growth markets for UCIe technology, driven by the need for high-reliability computing platforms in distributed environments. These applications place particular emphasis on the reliability aspects of UCIe implementations, making the warpage and war-room margin considerations especially relevant.

Market analysis reveals a growing demand for UCIe design and testing tools, with EDA companies reporting increased customer interest in solutions that can predict and mitigate warpage issues in organic interposer implementations. This ancillary market is expected to grow at 35% annually through 2026.

Regional market assessment shows North America and East Asia dominating UCIe technology adoption, with 40% and 38% market share respectively. Europe follows at 15%, with particular strength in automotive applications where reliability requirements are stringent.

Customer surveys indicate that 78% of semiconductor companies consider UCIe compatibility a priority for their next-generation products, highlighting the standard's growing importance in the industry ecosystem. However, 65% of these companies also express concerns about the reliability and manufacturing yield challenges associated with organic interposer implementations.

Technical Challenges in Organic Interposer Implementation

The implementation of UCIe (Universal Chiplet Interconnect Express) on organic interposers presents several significant technical challenges that must be addressed to ensure reliable and high-performance chiplet integration. The primary challenge stems from the inherent material properties of organic substrates, which exhibit greater coefficient of thermal expansion (CTE) mismatch with silicon compared to silicon or glass interposers. This mismatch creates substantial warpage issues during thermal cycling, threatening both manufacturing yield and long-term reliability.

Warpage management represents perhaps the most critical challenge, as organic interposers tend to deform during the assembly process when exposed to high reflow temperatures. This warpage can lead to connection failures between chiplets and the interposer, particularly as bump pitches decrease to accommodate higher bandwidth requirements specified by the UCIe standard. Current industry data indicates warpage values of 75-100μm for larger organic interposers, significantly exceeding the acceptable threshold of 50μm for reliable assembly.

Signal integrity challenges also emerge prominently when implementing UCIe on organic substrates. The relatively high dielectric loss tangent of organic materials (typically 0.01-0.02 compared to <0.001 for silicon) creates signal attenuation issues, particularly at the high frequencies (8-16 GT/s) required by UCIe. This necessitates more sophisticated signal conditioning techniques and potentially shorter transmission lines, limiting design flexibility.

The "war-room margins" - the engineering tolerances required to ensure manufacturability - become exceptionally tight when implementing UCIe on organic interposers. These margins must account for manufacturing variations, thermal expansion differences, and alignment precision. Current manufacturing capabilities struggle to maintain the <2μm alignment accuracy required for advanced UCIe implementations, particularly when organic substrate warpage is factored in.

Reliability concerns extend beyond initial manufacturing to long-term performance. Thermal cycling reliability is particularly challenging, with organic interposers typically supporting fewer cycles (500-1000) before failure compared to silicon alternatives (3000+). The different expansion rates between organic materials and silicon chiplets create cyclic stress at interconnection points, leading to potential solder joint fatigue and eventual failure.

Moisture sensitivity presents another significant challenge, as organic materials can absorb humidity from the environment, leading to dimensional changes and potential delamination during assembly or operation. This necessitates strict handling protocols and potentially more robust moisture barrier layers, adding complexity to the manufacturing process.

Warpage management represents perhaps the most critical challenge, as organic interposers tend to deform during the assembly process when exposed to high reflow temperatures. This warpage can lead to connection failures between chiplets and the interposer, particularly as bump pitches decrease to accommodate higher bandwidth requirements specified by the UCIe standard. Current industry data indicates warpage values of 75-100μm for larger organic interposers, significantly exceeding the acceptable threshold of 50μm for reliable assembly.

Signal integrity challenges also emerge prominently when implementing UCIe on organic substrates. The relatively high dielectric loss tangent of organic materials (typically 0.01-0.02 compared to <0.001 for silicon) creates signal attenuation issues, particularly at the high frequencies (8-16 GT/s) required by UCIe. This necessitates more sophisticated signal conditioning techniques and potentially shorter transmission lines, limiting design flexibility.

The "war-room margins" - the engineering tolerances required to ensure manufacturability - become exceptionally tight when implementing UCIe on organic interposers. These margins must account for manufacturing variations, thermal expansion differences, and alignment precision. Current manufacturing capabilities struggle to maintain the <2μm alignment accuracy required for advanced UCIe implementations, particularly when organic substrate warpage is factored in.

Reliability concerns extend beyond initial manufacturing to long-term performance. Thermal cycling reliability is particularly challenging, with organic interposers typically supporting fewer cycles (500-1000) before failure compared to silicon alternatives (3000+). The different expansion rates between organic materials and silicon chiplets create cyclic stress at interconnection points, leading to potential solder joint fatigue and eventual failure.

Moisture sensitivity presents another significant challenge, as organic materials can absorb humidity from the environment, leading to dimensional changes and potential delamination during assembly or operation. This necessitates strict handling protocols and potentially more robust moisture barrier layers, adding complexity to the manufacturing process.

Current Warpage Management Solutions

01 Warpage control in organic interposers for UCIe

Warpage is a critical issue in organic interposers used for Universal Chiplet Interconnect Express (UCIe) implementations. Various techniques are employed to control and mitigate warpage, including optimized material selection, balanced layer stacking, and thermal management strategies. These approaches help maintain the planarity of the interposer during manufacturing and operation, ensuring reliable interconnections between chiplets and preventing stress-induced failures in the UCIe interface.- Warpage control in organic interposers for UCIe: Warpage is a critical issue in organic interposers used for Universal Chiplet Interconnect Express (UCIe) implementations. Various techniques are employed to control and mitigate warpage, including optimized material selection, balanced layer stacking, and thermal management strategies. These approaches help maintain the planarity of the interposer during manufacturing and operation, ensuring reliable connections between chiplets and preventing signal integrity issues in high-speed UCIe interfaces.

- Reliability testing and qualification for UCIe implementations: Reliability testing methodologies specific to UCIe implementations on organic interposers involve comprehensive stress testing under various environmental conditions. These include thermal cycling, humidity testing, mechanical stress testing, and accelerated aging tests to ensure long-term performance stability. Advanced reliability models are developed to predict potential failure modes and establish qualification standards for UCIe-compliant chiplet interconnects, focusing on maintaining signal integrity and mechanical robustness throughout the product lifecycle.

- War-room margin optimization for UCIe interfaces: War-room margin optimization involves establishing design tolerances and operational margins for UCIe interfaces on organic interposers. This includes signal integrity analysis, power integrity considerations, and timing margin calculations to ensure robust operation under various conditions. Advanced simulation tools are used to model the electrical performance of UCIe interfaces, accounting for manufacturing variations, environmental factors, and aging effects. These margins are critical for ensuring interoperability between chiplets from different vendors while maintaining the high-speed data transfer rates specified by the UCIe standard.

- Thermal management solutions for UCIe on organic interposers: Effective thermal management is essential for UCIe implementations on organic interposers due to the high power density and heat generation in advanced chiplet designs. Various cooling solutions are employed, including integrated heat spreaders, thermal interface materials with optimized properties, and active cooling mechanisms. Thermal design considerations must account for the different thermal expansion coefficients of materials used in the package to prevent stress-induced warpage and maintain reliable interconnections between chiplets during thermal cycling.

- Manufacturing process optimization for UCIe organic interposers: Manufacturing process optimization for UCIe organic interposers focuses on achieving high yield and consistency in production. This includes advanced lamination techniques, precise alignment methods, and specialized curing processes to minimize warpage. Process control parameters are carefully monitored and adjusted to maintain dimensional stability throughout the manufacturing flow. Post-processing treatments and inspection methodologies are implemented to verify compliance with UCIe specifications, ensuring that the finished interposers meet the stringent requirements for high-density, high-speed chiplet interconnections.

02 War-room margins and design tolerances for UCIe implementations

War-room margins refer to the design tolerances and safety factors incorporated into UCIe implementations to ensure reliable operation under various conditions. These margins account for manufacturing variations, thermal cycling, and other environmental factors that could affect the performance of chiplet interconnects on organic interposers. Advanced simulation tools and testing methodologies are used to establish appropriate margins that balance performance requirements with reliability considerations.Expand Specific Solutions03 Reliability testing and qualification for UCIe on organic interposers

Ensuring the reliability of UCIe implementations on organic interposers requires comprehensive testing and qualification procedures. These include thermal cycling tests, mechanical stress tests, and electrical performance verification under various operating conditions. Advanced failure analysis techniques are employed to identify potential failure modes and develop mitigation strategies. Long-term reliability models help predict the expected lifetime of UCIe interconnects on organic substrates.Expand Specific Solutions04 Thermal management solutions for UCIe organic interposer packages

Thermal management is crucial for maintaining the reliability of UCIe implementations on organic interposers. Various cooling solutions are employed, including integrated heat spreaders, thermal interface materials, and advanced cooling structures. These solutions help dissipate heat generated during operation, preventing thermal-induced warpage and ensuring stable electrical connections between chiplets. Thermal design considerations must account for the different expansion coefficients of materials used in the package.Expand Specific Solutions05 Advanced materials and manufacturing processes for UCIe organic interposers

The development of advanced materials and manufacturing processes is essential for improving the performance and reliability of UCIe implementations on organic interposers. These include low-CTE (Coefficient of Thermal Expansion) substrate materials, novel dielectric formulations, and precision manufacturing techniques. Additive manufacturing approaches and laser-assisted bonding methods enable finer interconnect pitches while maintaining structural integrity. These advancements help address warpage issues and improve the overall reliability of chiplet-based systems.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe on organic interposers market is currently in an early growth phase, characterized by rapid technological development and increasing industry adoption. The market size is expanding as chiplet-based designs gain traction, with projections indicating significant growth over the next five years. Regarding technical maturity, leading semiconductor manufacturers like Intel, TSMC, and Samsung Electronics are at the forefront, having developed advanced solutions addressing warpage challenges and reliability concerns. Qualcomm and Huawei are making substantial investments in this space, while packaging specialists including JCET Group and ASE are developing complementary technologies. Companies like Micron and STMicroelectronics are focusing on memory integration aspects, while materials suppliers such as Ajinomoto and IBIDEN are working on organic substrate innovations to improve thermal performance and reduce warpage issues.

QUALCOMM, Inc.

Technical Solution: 高通针对UCIe有机基板互连开发了面向移动和边缘计算的优化方案。其技术方案特别关注低功耗场景下的互连可靠性和热管理,通过创新的基板设计和材料选择来应对移动设备特有的热循环和机械应力挑战。高通的方案整合了其在SoC设计领域的丰富经验,为UCIe实现提供了系统级优化。其技术特别关注有机基板在薄型封装中的翘曲控制,开发了专有的基板补偿技术来平衡不同材料层的内应力。高通还建立了详细的"War-Room Margins"分析框架,通过实时监测和反馈系统来确保生产过程中的一致性。在可靠性方面,高通实施了全面的环境测试方案,包括温度循环、湿度和机械冲击测试,以验证其UCIe实现在移动设备典型使用场景下的长期稳定性。其技术方案还包括针对异构集成的优化,支持将AI加速器、射频和传感器等多种功能模块通过UCIe互连整合到单一封装中。

优势:在移动平台上拥有丰富的系统集成经验,其UCIe实现在功耗效率和热管理方面表现出色。拥有广泛的移动生态系统支持,有利于技术推广。劣势:其技术方案主要针对移动场景优化,在高性能计算等领域可能需要进一步适配。在某些先进封装技术上依赖外部合作伙伴,可能影响技术路线的独立性。

Huawei Technologies Co., Ltd.

Technical Solution: 华为在UCIe有机基板技术上采取了系统化的解决方案,特别是针对高端服务器和AI加速器应用场景。其技术方案基于自研的"鲲鹏"和"昇腾"芯片架构,开发了适配UCIe标准的互连技术。华为特别关注有机基板在高功耗场景下的热管理和翘曲控制,通过创新的散热设计和基板材料选择来优化系统可靠性。其技术方案包括多层次的设计余量策略,通过精确的热-机械模拟和实测数据建立了全面的"War-Room Margins"参数库。华为还开发了专有的基板应力释放技术,通过优化层叠结构和材料界面来减少热循环导致的累积应力。在可靠性方面,华为实施了加速老化测试方法,模拟极端工作条件下的长期性能,确保UCIe互连在整个产品生命周期内的稳定性。其技术方案还包括针对不同应用场景的UCIe实现变体,以平衡性能、功耗和成本需求。

优势:拥有从芯片到系统的全栈优化能力,能够根据应用需求定制UCIe实现。其在高性能计算领域的经验使其技术方案在功耗效率方面表现突出。劣势:受国际贸易限制影响,在某些关键材料和设备获取上可能面临挑战,可能导致技术路线选择受限。在全球标准制定参与度方面相对弱势。

Critical Patents and Research on Organic Interposer Reliability

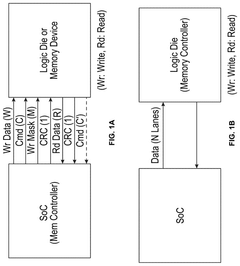

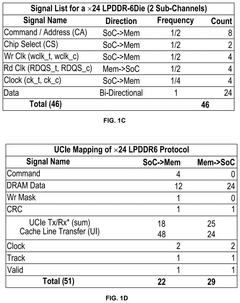

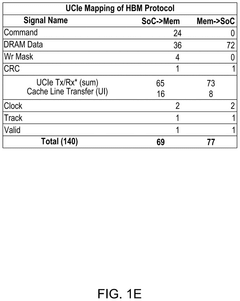

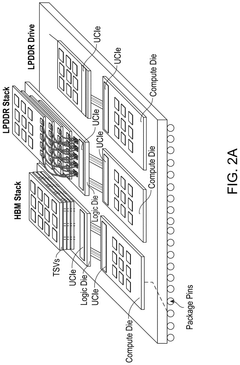

On-package memory with universal chiplet interconnect express

PatentPendingUS20250123990A1

Innovation

- The implementation of Universal Chiplet Interconnect Express (UCIe) enhances memory interfacing by standardizing connections between processors and various memory types, optimizing communication, and integrating memory controllers on the same package to increase bandwidth and reduce latency.

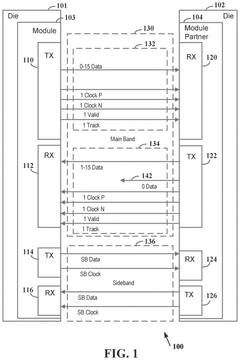

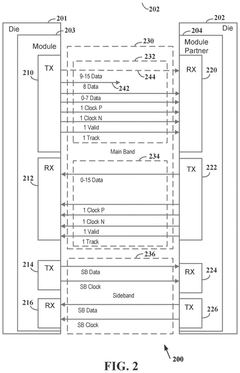

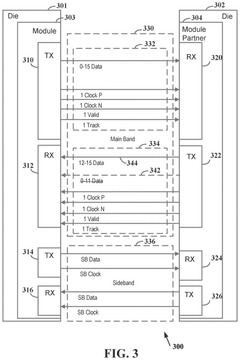

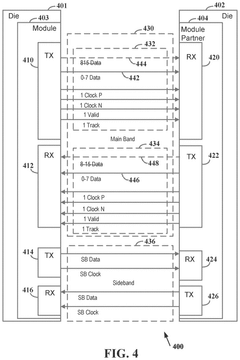

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Thermal Management Strategies for UCIe Packages

Thermal management represents a critical challenge for UCIe (Universal Chiplet Interconnect Express) packages implemented on organic interposers. As chiplet integration densities increase and power requirements grow, effective heat dissipation becomes essential for maintaining system reliability and performance. The thermal challenges are particularly pronounced due to the warpage characteristics of organic interposers under thermal stress.

Current thermal management strategies for UCIe packages employ multi-layered approaches. At the package level, advanced thermal interface materials (TIMs) with enhanced thermal conductivity are being deployed between the die and heat spreader. These materials typically achieve thermal conductivity values between 5-15 W/mK, significantly improving heat transfer efficiency while accommodating the warpage-induced gaps that may form during thermal cycling.

Active cooling solutions have evolved specifically for UCIe implementations, with liquid cooling gaining prominence for high-performance applications. Microfluidic cooling channels integrated within or adjacent to the interposer structure can extract heat directly from hotspots, achieving thermal resistances below 0.1°C/W in advanced implementations. This approach helps mitigate the thermal expansion mismatch between silicon chiplets and organic substrates.

Thermal-aware design methodologies have become essential in the UCIe ecosystem. Sophisticated thermal simulation tools now incorporate warpage models to predict thermal behavior under various operating conditions. These simulations account for the non-linear thermal expansion characteristics of organic interposers, enabling designers to optimize chiplet placement and routing to minimize thermal gradients and associated reliability risks.

Novel materials integration represents another frontier in thermal management for UCIe packages. Embedded thermal vias and metal-filled through-holes strategically placed within the organic interposer can create dedicated thermal pathways with conductivity values exceeding 50 W/mK. Additionally, graphene-enhanced composites are being explored as next-generation interposer materials, potentially offering up to 3x improvement in in-plane thermal conductivity compared to conventional organic substrates.

Industry benchmarks indicate that effective thermal management strategies can maintain junction temperatures below 85°C even in high-power UCIe implementations exceeding 500W. However, these solutions must be carefully balanced against manufacturing complexity, cost considerations, and potential impacts on electrical performance and signal integrity within the UCIe interface specifications.

Current thermal management strategies for UCIe packages employ multi-layered approaches. At the package level, advanced thermal interface materials (TIMs) with enhanced thermal conductivity are being deployed between the die and heat spreader. These materials typically achieve thermal conductivity values between 5-15 W/mK, significantly improving heat transfer efficiency while accommodating the warpage-induced gaps that may form during thermal cycling.

Active cooling solutions have evolved specifically for UCIe implementations, with liquid cooling gaining prominence for high-performance applications. Microfluidic cooling channels integrated within or adjacent to the interposer structure can extract heat directly from hotspots, achieving thermal resistances below 0.1°C/W in advanced implementations. This approach helps mitigate the thermal expansion mismatch between silicon chiplets and organic substrates.

Thermal-aware design methodologies have become essential in the UCIe ecosystem. Sophisticated thermal simulation tools now incorporate warpage models to predict thermal behavior under various operating conditions. These simulations account for the non-linear thermal expansion characteristics of organic interposers, enabling designers to optimize chiplet placement and routing to minimize thermal gradients and associated reliability risks.

Novel materials integration represents another frontier in thermal management for UCIe packages. Embedded thermal vias and metal-filled through-holes strategically placed within the organic interposer can create dedicated thermal pathways with conductivity values exceeding 50 W/mK. Additionally, graphene-enhanced composites are being explored as next-generation interposer materials, potentially offering up to 3x improvement in in-plane thermal conductivity compared to conventional organic substrates.

Industry benchmarks indicate that effective thermal management strategies can maintain junction temperatures below 85°C even in high-power UCIe implementations exceeding 500W. However, these solutions must be carefully balanced against manufacturing complexity, cost considerations, and potential impacts on electrical performance and signal integrity within the UCIe interface specifications.

Manufacturing Process Optimization for Yield Improvement

The optimization of manufacturing processes for UCIe (Universal Chiplet Interconnect Express) on organic interposers represents a critical challenge in advanced packaging technologies. Current yield rates are significantly impacted by warpage issues, which occur during thermal processing when different materials with varying coefficients of thermal expansion interact. To address this challenge, several process optimizations have been implemented across the manufacturing workflow.

Material selection has emerged as a fundamental consideration, with advanced organic substrate materials demonstrating improved thermal stability and reduced warpage characteristics. Manufacturers have begun incorporating modified resin systems with lower cure shrinkage and tailored glass transition temperatures to better match silicon expansion properties.

Process parameter optimization has yielded substantial improvements through the implementation of dynamic thermal profiles. By controlling ramp rates and introducing intermediate temperature holds during lamination and curing processes, stress accumulation can be minimized. Data from production lines indicates that optimized thermal profiles can reduce warpage by 15-20% compared to standard processing conditions.

Advanced simulation tools have become essential for predicting and mitigating warpage issues before physical manufacturing. Finite element analysis (FEA) models incorporating material viscoelastic properties and process-induced stresses enable virtual process optimization, reducing costly trial-and-error approaches. These simulation capabilities have shortened development cycles by approximately 30% while improving first-pass yield rates.

In-line metrology integration represents another significant advancement, with optical measurement systems now deployed at critical process steps to provide real-time warpage data. This enables adaptive process control where parameters can be adjusted based on measured warpage trends, preventing downstream assembly issues. Manufacturers implementing these systems report detection and correction of process drift before it impacts yield.

Post-processing techniques have also been developed to address residual warpage in completed assemblies. Controlled stress relief through optimized thermal annealing has demonstrated the ability to reduce final warpage by up to 25% in certain package configurations. This approach is particularly valuable for larger interposer designs where warpage sensitivity increases exponentially with size.

Equipment modifications have further contributed to yield improvements, with specialized fixtures and handling systems designed to maintain flatness during critical process steps. Vacuum-assisted holding fixtures and precision alignment systems help preserve the geometric integrity of organic interposers throughout the manufacturing process.

Material selection has emerged as a fundamental consideration, with advanced organic substrate materials demonstrating improved thermal stability and reduced warpage characteristics. Manufacturers have begun incorporating modified resin systems with lower cure shrinkage and tailored glass transition temperatures to better match silicon expansion properties.

Process parameter optimization has yielded substantial improvements through the implementation of dynamic thermal profiles. By controlling ramp rates and introducing intermediate temperature holds during lamination and curing processes, stress accumulation can be minimized. Data from production lines indicates that optimized thermal profiles can reduce warpage by 15-20% compared to standard processing conditions.

Advanced simulation tools have become essential for predicting and mitigating warpage issues before physical manufacturing. Finite element analysis (FEA) models incorporating material viscoelastic properties and process-induced stresses enable virtual process optimization, reducing costly trial-and-error approaches. These simulation capabilities have shortened development cycles by approximately 30% while improving first-pass yield rates.

In-line metrology integration represents another significant advancement, with optical measurement systems now deployed at critical process steps to provide real-time warpage data. This enables adaptive process control where parameters can be adjusted based on measured warpage trends, preventing downstream assembly issues. Manufacturers implementing these systems report detection and correction of process drift before it impacts yield.

Post-processing techniques have also been developed to address residual warpage in completed assemblies. Controlled stress relief through optimized thermal annealing has demonstrated the ability to reduce final warpage by up to 25% in certain package configurations. This approach is particularly valuable for larger interposer designs where warpage sensitivity increases exponentially with size.

Equipment modifications have further contributed to yield improvements, with specialized fixtures and handling systems designed to maintain flatness during critical process steps. Vacuum-assisted holding fixtures and precision alignment systems help preserve the geometric integrity of organic interposers throughout the manufacturing process.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!