UCIe Thermal Co-Design: Hot-Spot Sharing, Keep-Outs And ΔT Limits

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Thermal Integration Background and Objectives

Universal Chiplet Interconnect Express (UCIe) has emerged as a critical open standard for chiplet integration in the semiconductor industry. The evolution of this technology represents a significant shift from traditional monolithic chip designs to more modular, heterogeneous integration approaches. UCIe addresses the growing need for high-bandwidth, low-latency, and energy-efficient interconnects between chiplets in advanced packaging solutions, which has become increasingly important as Moore's Law faces physical limitations.

The thermal management aspects of UCIe integration present unique challenges that have not been adequately addressed in previous interconnect standards. As chiplets from different manufacturers with varying thermal characteristics are integrated into a single package, the complexity of thermal management increases exponentially. Hot-spot sharing between adjacent chiplets, thermal keep-out zones, and temperature gradient (ΔT) limits have become critical considerations that directly impact system reliability, performance, and lifespan.

Historically, thermal management in integrated circuits has evolved from simple heat sink solutions to sophisticated liquid cooling systems. However, the advent of chiplet-based designs introduces new thermal challenges at the package level that require innovative co-design approaches. The industry has recognized that thermal considerations must be addressed early in the design process rather than as an afterthought, leading to the development of thermal co-design methodologies specifically for chiplet integration.

The primary objective of UCIe thermal co-design is to establish standardized methodologies and specifications for managing thermal interactions between chiplets. This includes developing protocols for sharing thermal data between chiplet vendors, defining standardized interfaces for thermal management, and establishing guidelines for thermal keep-out zones to prevent thermal coupling between sensitive components.

Another key goal is to quantify and standardize acceptable temperature gradient limits across chiplet interfaces to ensure reliable electrical connections and prevent thermomechanical stress that could lead to package failures. The industry aims to develop predictive thermal modeling techniques that can accurately simulate the complex thermal interactions in multi-chiplet packages during the design phase.

Furthermore, UCIe thermal integration seeks to enable dynamic thermal management capabilities that can respond to changing workloads and environmental conditions in real-time. This requires standardized interfaces for thermal sensors, controllers, and cooling solutions that can work together seamlessly across chiplets from different vendors.

The ultimate objective is to create a thermal design ecosystem around UCIe that enables chiplet vendors to develop products independently while ensuring thermal compatibility when integrated into a single package. This would significantly reduce time-to-market for new products and enable more flexible and cost-effective system designs across various application domains, from high-performance computing to mobile devices.

The thermal management aspects of UCIe integration present unique challenges that have not been adequately addressed in previous interconnect standards. As chiplets from different manufacturers with varying thermal characteristics are integrated into a single package, the complexity of thermal management increases exponentially. Hot-spot sharing between adjacent chiplets, thermal keep-out zones, and temperature gradient (ΔT) limits have become critical considerations that directly impact system reliability, performance, and lifespan.

Historically, thermal management in integrated circuits has evolved from simple heat sink solutions to sophisticated liquid cooling systems. However, the advent of chiplet-based designs introduces new thermal challenges at the package level that require innovative co-design approaches. The industry has recognized that thermal considerations must be addressed early in the design process rather than as an afterthought, leading to the development of thermal co-design methodologies specifically for chiplet integration.

The primary objective of UCIe thermal co-design is to establish standardized methodologies and specifications for managing thermal interactions between chiplets. This includes developing protocols for sharing thermal data between chiplet vendors, defining standardized interfaces for thermal management, and establishing guidelines for thermal keep-out zones to prevent thermal coupling between sensitive components.

Another key goal is to quantify and standardize acceptable temperature gradient limits across chiplet interfaces to ensure reliable electrical connections and prevent thermomechanical stress that could lead to package failures. The industry aims to develop predictive thermal modeling techniques that can accurately simulate the complex thermal interactions in multi-chiplet packages during the design phase.

Furthermore, UCIe thermal integration seeks to enable dynamic thermal management capabilities that can respond to changing workloads and environmental conditions in real-time. This requires standardized interfaces for thermal sensors, controllers, and cooling solutions that can work together seamlessly across chiplets from different vendors.

The ultimate objective is to create a thermal design ecosystem around UCIe that enables chiplet vendors to develop products independently while ensuring thermal compatibility when integrated into a single package. This would significantly reduce time-to-market for new products and enable more flexible and cost-effective system designs across various application domains, from high-performance computing to mobile devices.

Market Demand for Advanced Chiplet Interconnect Solutions

The global chiplet market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. As traditional monolithic chip designs reach their physical and economic limits, chiplet-based architectures have emerged as a compelling alternative, offering improved yield, cost efficiency, and design flexibility. Market research indicates that the chiplet market is projected to grow at a CAGR of over 40% from 2022 to 2028, reaching tens of billions of dollars by the end of the forecast period.

The demand for advanced chiplet interconnect solutions, particularly those addressing thermal management challenges like UCIe Thermal Co-Design, is primarily fueled by data centers and cloud service providers. These entities require increasingly powerful computing capabilities while managing power consumption and heat dissipation effectively. The hyperscalers' continuous expansion of AI and machine learning infrastructure has created substantial demand for heterogeneous integration solutions that can efficiently handle thermal constraints.

Telecommunications and networking equipment manufacturers represent another significant market segment, as they transition to 5G and prepare for 6G technologies. These applications demand high-bandwidth, low-latency processing capabilities that can operate reliably under varying thermal conditions, making thermal co-design aspects of UCIe particularly relevant.

Consumer electronics manufacturers are also showing growing interest in chiplet technologies as they seek to deliver enhanced performance in compact form factors. Smartphones, tablets, and wearable devices benefit from the power efficiency and thermal management capabilities that advanced chiplet interconnect solutions provide, allowing for longer battery life and improved user experience.

The automotive sector presents an emerging market opportunity, particularly with the rise of autonomous vehicles and advanced driver assistance systems. These applications require robust computing platforms that can operate reliably under extreme temperature conditions, making thermal co-design considerations essential for ensuring system reliability and longevity.

Geographically, North America currently leads the market for advanced chiplet interconnect solutions, followed by Asia-Pacific and Europe. However, the Asia-Pacific region is expected to witness the highest growth rate due to the strong presence of semiconductor manufacturing facilities and increasing investments in advanced packaging technologies.

Customer requirements are increasingly focused on thermal efficiency, with system integrators demanding comprehensive thermal co-design capabilities that address hot-spot sharing, thermal keep-out zones, and precise ΔT limits. This trend is driving semiconductor companies to prioritize thermal management features in their chiplet interconnect strategies, positioning UCIe Thermal Co-Design as a critical differentiator in the competitive landscape.

The demand for advanced chiplet interconnect solutions, particularly those addressing thermal management challenges like UCIe Thermal Co-Design, is primarily fueled by data centers and cloud service providers. These entities require increasingly powerful computing capabilities while managing power consumption and heat dissipation effectively. The hyperscalers' continuous expansion of AI and machine learning infrastructure has created substantial demand for heterogeneous integration solutions that can efficiently handle thermal constraints.

Telecommunications and networking equipment manufacturers represent another significant market segment, as they transition to 5G and prepare for 6G technologies. These applications demand high-bandwidth, low-latency processing capabilities that can operate reliably under varying thermal conditions, making thermal co-design aspects of UCIe particularly relevant.

Consumer electronics manufacturers are also showing growing interest in chiplet technologies as they seek to deliver enhanced performance in compact form factors. Smartphones, tablets, and wearable devices benefit from the power efficiency and thermal management capabilities that advanced chiplet interconnect solutions provide, allowing for longer battery life and improved user experience.

The automotive sector presents an emerging market opportunity, particularly with the rise of autonomous vehicles and advanced driver assistance systems. These applications require robust computing platforms that can operate reliably under extreme temperature conditions, making thermal co-design considerations essential for ensuring system reliability and longevity.

Geographically, North America currently leads the market for advanced chiplet interconnect solutions, followed by Asia-Pacific and Europe. However, the Asia-Pacific region is expected to witness the highest growth rate due to the strong presence of semiconductor manufacturing facilities and increasing investments in advanced packaging technologies.

Customer requirements are increasingly focused on thermal efficiency, with system integrators demanding comprehensive thermal co-design capabilities that address hot-spot sharing, thermal keep-out zones, and precise ΔT limits. This trend is driving semiconductor companies to prioritize thermal management features in their chiplet interconnect strategies, positioning UCIe Thermal Co-Design as a critical differentiator in the competitive landscape.

UCIe Thermal Challenges and Current Limitations

The UCIe (Universal Chiplet Interconnect Express) standard faces significant thermal challenges that currently limit its full potential in heterogeneous integration. As chiplets become more densely packed within a package, thermal management becomes increasingly complex. The primary limitation stems from the difficulty in effectively dissipating heat from multiple chiplets operating in close proximity, creating thermal coupling effects that can compromise performance and reliability.

Hot-spot management represents one of the most critical challenges. When multiple high-performance chiplets are integrated, localized hot spots can form where thermal densities exceed 500W/cm², far surpassing traditional cooling solutions' capabilities. Current thermal interface materials (TIMs) exhibit insufficient thermal conductivity (typically 2-8 W/m·K) to efficiently transfer heat from these concentrated areas to heat spreaders or heat sinks.

Temperature gradient (ΔT) limitations across the package present another significant constraint. The UCIe specification currently lacks comprehensive guidelines for managing temperature differentials between adjacent chiplets. These differentials can reach 20-30°C in advanced designs, causing mechanical stress at interfaces and potentially compromising signal integrity across high-speed UCIe links operating at 16-32 GT/s.

Keep-out zones, areas where certain components cannot be placed due to thermal considerations, further restrict design flexibility. Current UCIe implementations often require substantial keep-out zones around high-power components, reducing the effective integration density and limiting the architectural advantages of chiplet-based designs. These zones typically consume 15-25% of the package area in complex multi-chiplet designs.

The thermal modeling tools and methodologies for UCIe implementations also present limitations. Current simulation approaches struggle to accurately predict the complex thermal interactions between multiple chiplets with different power profiles and thermal characteristics. This modeling gap leads to conservative designs with excessive thermal margins, undermining the density and performance benefits of UCIe.

Additionally, cooling solutions for UCIe packages face constraints in terms of z-height limitations and thermal solution weight. As data centers demand higher compute density, the physical dimensions of cooling solutions become increasingly restricted, limiting the thermal dissipation capability for high-power UCIe implementations to approximately 350-450W per package without liquid cooling.

These thermal challenges collectively represent a significant barrier to the broader adoption of UCIe technology, particularly for high-performance computing applications where thermal management is already a critical constraint on system design and performance scaling.

Hot-spot management represents one of the most critical challenges. When multiple high-performance chiplets are integrated, localized hot spots can form where thermal densities exceed 500W/cm², far surpassing traditional cooling solutions' capabilities. Current thermal interface materials (TIMs) exhibit insufficient thermal conductivity (typically 2-8 W/m·K) to efficiently transfer heat from these concentrated areas to heat spreaders or heat sinks.

Temperature gradient (ΔT) limitations across the package present another significant constraint. The UCIe specification currently lacks comprehensive guidelines for managing temperature differentials between adjacent chiplets. These differentials can reach 20-30°C in advanced designs, causing mechanical stress at interfaces and potentially compromising signal integrity across high-speed UCIe links operating at 16-32 GT/s.

Keep-out zones, areas where certain components cannot be placed due to thermal considerations, further restrict design flexibility. Current UCIe implementations often require substantial keep-out zones around high-power components, reducing the effective integration density and limiting the architectural advantages of chiplet-based designs. These zones typically consume 15-25% of the package area in complex multi-chiplet designs.

The thermal modeling tools and methodologies for UCIe implementations also present limitations. Current simulation approaches struggle to accurately predict the complex thermal interactions between multiple chiplets with different power profiles and thermal characteristics. This modeling gap leads to conservative designs with excessive thermal margins, undermining the density and performance benefits of UCIe.

Additionally, cooling solutions for UCIe packages face constraints in terms of z-height limitations and thermal solution weight. As data centers demand higher compute density, the physical dimensions of cooling solutions become increasingly restricted, limiting the thermal dissipation capability for high-power UCIe implementations to approximately 350-450W per package without liquid cooling.

These thermal challenges collectively represent a significant barrier to the broader adoption of UCIe technology, particularly for high-performance computing applications where thermal management is already a critical constraint on system design and performance scaling.

Current Hot-Spot Management and Thermal Keep-Out Approaches

01 Thermal management solutions for chiplet interconnects

Various thermal management solutions are implemented in UCIe architectures to address heat dissipation challenges. These include specialized thermal interface materials, heat spreaders, and cooling structures designed specifically for chiplet-based designs. These solutions help manage hot spots and maintain temperature differentials within acceptable limits, ensuring reliable operation of interconnected chiplets with different thermal characteristics.- Thermal management solutions for chiplet interconnects: Various thermal management solutions are implemented in UCIe architectures to address heat dissipation challenges. These include specialized thermal interface materials, heat spreaders, and cooling structures designed specifically for multi-chiplet packages. These solutions help manage hot spots and maintain temperature gradients within acceptable ΔT limits across the package, ensuring reliable operation of high-performance chiplet-based systems.

- Hot-spot sharing and thermal distribution techniques: Advanced algorithms and physical designs enable effective hot-spot sharing between chiplets in UCIe implementations. These techniques include dynamic thermal load balancing, strategic placement of high-heat components, and thermal-aware floorplanning. By distributing thermal loads across the package, these approaches prevent localized overheating and maintain more uniform temperature profiles across the chiplet assembly.

- Thermal keep-out zones and boundary management: UCIe specifications define thermal keep-out zones to prevent thermal interference between chiplets. These designated areas restrict placement of high-heat components near sensitive elements or interconnect boundaries. Implementation of thermal boundaries and buffer zones helps maintain thermal isolation where needed and prevents thermal coupling effects that could compromise signal integrity or reliability of the chiplet interconnects.

- Temperature differential (ΔT) monitoring and control systems: Sophisticated temperature monitoring and control systems are employed to maintain temperature differentials within UCIe specification limits. These systems include distributed temperature sensors, real-time thermal monitoring, and adaptive thermal management algorithms. By continuously monitoring temperature gradients across chiplets and interconnects, these systems can trigger appropriate cooling responses or workload adjustments to prevent thermal-related failures.

- Integration of cooling structures with UCIe packaging: Innovative cooling structures are integrated directly into UCIe packaging designs to address thermal challenges. These include embedded microfluidic cooling channels, integrated vapor chambers, and specialized heat sink designs optimized for chiplet architectures. The cooling structures are designed to work with the unique thermal characteristics of UCIe implementations, targeting hot spots while maintaining overall package thermal requirements and ensuring reliable high-speed interconnect operation.

02 Hot-spot sharing and thermal coupling between chiplets

UCIe implementations include mechanisms for thermal coupling and hot-spot sharing between adjacent chiplets. These designs account for heat transfer between chiplets through the interconnect, allowing for more efficient thermal management across the entire package. Thermal models and simulations are used to predict heat flow patterns and optimize chiplet placement to prevent thermal bottlenecks and maintain ΔT limits within specification.Expand Specific Solutions03 Thermal keep-out zones and layout optimization

UCIe designs incorporate thermal keep-out zones to prevent critical components from being placed near high-temperature areas. These zones are strategically defined based on thermal simulations and testing to ensure that temperature-sensitive elements are protected from thermal interference. Layout optimization techniques are employed to arrange chiplets and interconnects in ways that minimize thermal hotspots and maintain uniform temperature distribution.Expand Specific Solutions04 Dynamic thermal management and temperature monitoring

Advanced UCIe implementations feature dynamic thermal management systems that continuously monitor temperature across chiplets and adjust performance parameters accordingly. These systems include embedded temperature sensors, thermal feedback loops, and adaptive algorithms that can throttle specific chiplets or redistribute workloads to maintain temperature differentials within safe limits. This approach helps prevent thermal runaway conditions while maximizing overall system performance.Expand Specific Solutions05 Thermal interface materials and heat dissipation structures

Specialized thermal interface materials and heat dissipation structures are developed specifically for UCIe implementations. These include advanced thermal greases, phase-change materials, and integrated heat spreaders designed to efficiently transfer heat away from chiplet interconnect areas. Novel cooling solutions such as microfluidic channels, vapor chambers, and integrated heat pipes are employed to manage thermal challenges in densely packed chiplet arrangements while maintaining strict ΔT limits required by the UCIe specification.Expand Specific Solutions

Leading Companies in UCIe Ecosystem and Thermal Solutions

The UCIe Thermal Co-Design market is in its early growth phase, characterized by increasing adoption of chiplet-based architectures requiring advanced thermal management solutions. The market is expanding rapidly as high-performance computing demands intensify, with projections suggesting significant growth over the next five years. Technologically, the field is maturing with key players developing sophisticated thermal solutions. Intel leads with comprehensive UCIe thermal design methodologies, while NVIDIA, AMD, and TSMC contribute significant innovations in hot-spot management and thermal interface materials. Companies like IBM and Qualcomm are advancing thermal co-design frameworks, while specialized cooling solutions providers such as Vertiv and Munters offer complementary technologies. The ecosystem is evolving toward standardized approaches for thermal design constraints and hot-spot sharing protocols.

Intel Corp.

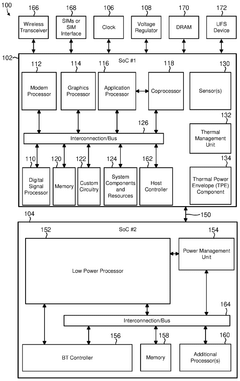

Technical Solution: Intel has pioneered comprehensive UCIe thermal co-design solutions focusing on hot-spot sharing, keep-out zones, and temperature gradient management. Their approach integrates advanced thermal interface materials (TIMs) with microchannel liquid cooling systems specifically designed for chiplet architectures. Intel's UCIe implementation includes dynamic thermal management algorithms that monitor and redistribute computational loads based on real-time temperature data across the package. Their solution incorporates silicon photonics integration to reduce thermal density while maintaining high bandwidth between chiplets. Intel has developed specialized thermal simulation tools that model heat transfer across die-to-die interfaces with particular attention to thermal boundary conditions at interconnect points, allowing for precise prediction of thermal gradients and identification of potential hot spots before physical implementation.

Strengths: Industry-leading expertise in heterogeneous integration; extensive manufacturing infrastructure optimized for chiplet production; proprietary thermal modeling tools. Weaknesses: Higher implementation costs compared to traditional packaging; requires significant design modifications to existing chip architectures; thermal management overhead may impact overall system performance.

Advanced Micro Devices, Inc.

Technical Solution: AMD has developed a comprehensive UCIe thermal co-design strategy focusing on optimizing thermal performance across heterogeneous chiplet architectures. Their approach implements a distributed thermal management system that treats the entire package as a unified thermal domain while respecting individual chiplet thermal constraints. AMD's solution incorporates specialized thermal interface materials with variable thermal conductivity properties that adapt to different thermal loads across the package. They've implemented a hierarchical thermal control system that manages temperature gradients between chiplets through dynamic frequency scaling and workload migration. AMD's thermal co-design methodology includes detailed thermal keep-out zones around high-speed SerDes lanes and sensitive analog circuits to prevent thermal interference. Their implementation leverages advanced packaging technologies like silicon interposers with integrated thermal vias strategically positioned to facilitate heat transfer away from critical hot spots.

Strengths: Extensive experience with chiplet architecture implementation; proven track record in heterogeneous integration; efficient thermal management algorithms. Weaknesses: More conservative thermal design limits compared to competitors; higher reliance on software-based thermal management; thermal solutions may require more physical space within package.

Critical Thermal Co-Design Patents and Technical Literature

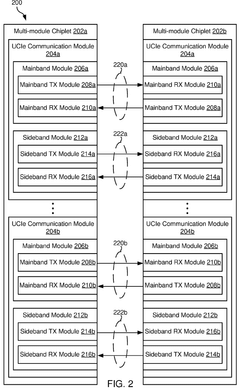

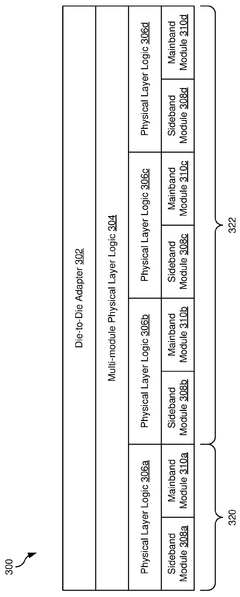

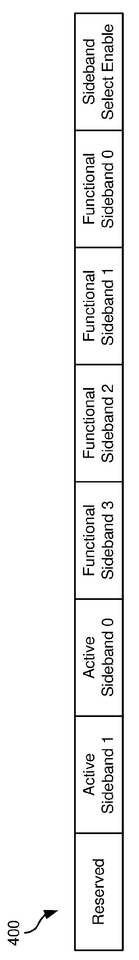

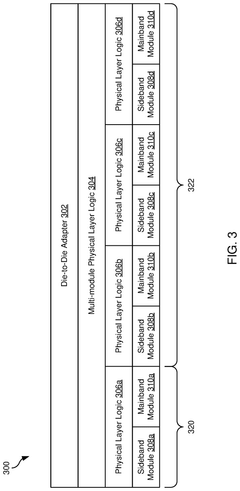

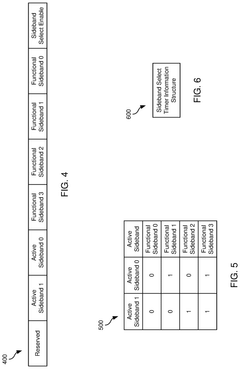

Mechanism to improve the reliability of sideband in chiplets

PatentWO2025058796A1

Innovation

- The method involves configuring UCIe links between multi-module chiplets to enable runtime selection and aggregation of sidebands, allowing for the use of different or additional sidebands beyond the initially active one, thereby reducing hardware stress and enhancing communication reliability.

Mechanism To Improve The Reliability Of Sideband In Chiplets

PatentActiveUS20250086136A1

Innovation

- The method involves transitioning the UCIe link from an active state to a reset state and then initializing a different functional sideband, allowing for runtime configuration of sidebands and aggregation of multiple sidebands to enhance communication reliability and throughput.

Industry Standards and Compliance Requirements for UCIe

The Universal Chiplet Interconnect Express (UCIe) standard operates within a complex ecosystem of industry regulations and technical specifications. Compliance with these standards is essential for ensuring interoperability, reliability, and market acceptance of UCIe-based chiplet designs, particularly when addressing thermal management challenges.

The Joint Electron Device Engineering Council (JEDEC) provides foundational thermal testing methodologies that UCIe implementations must adhere to. JEDEC standards JEP153 and JESD51-14 specifically outline thermal testing procedures for integrated circuits and multi-chip packages, which directly impact how hot-spot sharing and thermal keep-out zones must be managed in UCIe designs.

The International Electrotechnical Commission (IEC) contributes complementary standards that govern safety aspects of electronic components under thermal stress. IEC 60749-34 addresses thermal resistance measurements, while IEC 62830 series covers thermal energy harvesting, both of which influence UCIe thermal co-design parameters and ΔT limit specifications.

For UCIe implementations in data center environments, compliance with ASHRAE (American Society of Heating, Refrigerating and Air-Conditioning Engineers) thermal guidelines is mandatory. These guidelines establish acceptable temperature ranges and cooling requirements that directly constrain the permissible ΔT limits in high-density computing applications utilizing UCIe technology.

The UCIe Consortium itself has established specific thermal compliance requirements through its UCIe 1.0 specification. This includes detailed parameters for thermal interface materials, maximum junction temperatures, and thermal resistance budgets across die-to-die interfaces. The specification mandates reporting of thermal maps and hot-spot locations to enable effective co-design between chiplet providers.

Energy efficiency regulations, including ENERGY STAR for servers and the European Ecodesign Directive, indirectly impact UCIe thermal design by establishing power consumption limits. These regulations necessitate sophisticated thermal management strategies to maintain performance while adhering to power constraints, directly influencing how thermal keep-out zones must be designed.

Military and aerospace applications of UCIe technology must comply with MIL-STD-810H environmental testing standards, which include rigorous thermal cycling requirements. These standards impose stricter ΔT limits and thermal reliability metrics than commercial applications, affecting how thermal co-design must be approached for these specialized markets.

The Restriction of Hazardous Substances (RoHS) directive impacts material selection for thermal interface materials in UCIe implementations, limiting options for thermal conductivity enhancement and potentially affecting thermal performance parameters. Compliance with RoHS while maintaining optimal thermal characteristics represents a significant design challenge.

The Joint Electron Device Engineering Council (JEDEC) provides foundational thermal testing methodologies that UCIe implementations must adhere to. JEDEC standards JEP153 and JESD51-14 specifically outline thermal testing procedures for integrated circuits and multi-chip packages, which directly impact how hot-spot sharing and thermal keep-out zones must be managed in UCIe designs.

The International Electrotechnical Commission (IEC) contributes complementary standards that govern safety aspects of electronic components under thermal stress. IEC 60749-34 addresses thermal resistance measurements, while IEC 62830 series covers thermal energy harvesting, both of which influence UCIe thermal co-design parameters and ΔT limit specifications.

For UCIe implementations in data center environments, compliance with ASHRAE (American Society of Heating, Refrigerating and Air-Conditioning Engineers) thermal guidelines is mandatory. These guidelines establish acceptable temperature ranges and cooling requirements that directly constrain the permissible ΔT limits in high-density computing applications utilizing UCIe technology.

The UCIe Consortium itself has established specific thermal compliance requirements through its UCIe 1.0 specification. This includes detailed parameters for thermal interface materials, maximum junction temperatures, and thermal resistance budgets across die-to-die interfaces. The specification mandates reporting of thermal maps and hot-spot locations to enable effective co-design between chiplet providers.

Energy efficiency regulations, including ENERGY STAR for servers and the European Ecodesign Directive, indirectly impact UCIe thermal design by establishing power consumption limits. These regulations necessitate sophisticated thermal management strategies to maintain performance while adhering to power constraints, directly influencing how thermal keep-out zones must be designed.

Military and aerospace applications of UCIe technology must comply with MIL-STD-810H environmental testing standards, which include rigorous thermal cycling requirements. These standards impose stricter ΔT limits and thermal reliability metrics than commercial applications, affecting how thermal co-design must be approached for these specialized markets.

The Restriction of Hazardous Substances (RoHS) directive impacts material selection for thermal interface materials in UCIe implementations, limiting options for thermal conductivity enhancement and potentially affecting thermal performance parameters. Compliance with RoHS while maintaining optimal thermal characteristics represents a significant design challenge.

Power-Thermal Trade-offs in Chiplet Design

The power-thermal relationship in chiplet design represents a critical engineering challenge that directly impacts system performance, reliability, and cost. As UCIe (Universal Chiplet Interconnect Express) adoption accelerates, designers must navigate complex trade-offs between power consumption and thermal management across multiple integrated dies.

Power density in advanced chiplet designs has reached unprecedented levels, with some high-performance computing chiplets exceeding 500W/cm² at hotspots. This creates significant thermal management challenges that cannot be addressed through traditional cooling solutions alone. The heterogeneous integration of multiple chiplets with varying power profiles further complicates thermal design considerations.

Thermal constraints often become the limiting factor in chiplet performance scaling. When thermal limits are reached, frequency throttling occurs, negating potential performance gains from advanced process nodes. This creates a fundamental tension between power delivery capabilities and thermal dissipation limits. UCIe implementations must carefully balance these competing requirements through co-design approaches.

The thermal coupling between adjacent chiplets introduces additional complexity. Hot-spot sharing across chiplet boundaries can create thermal gradients that affect signal integrity in high-speed UCIe links. Research indicates that temperature differentials exceeding 20°C between communicating chiplets can increase bit error rates by up to 30% in 32GT/s UCIe implementations.

Power-thermal optimization strategies include dynamic power allocation between chiplets, thermal-aware floorplanning with strategic keep-out zones, and adaptive cooling solutions. Advanced thermal interface materials (TIMs) with conductivity exceeding 20W/m·K are being developed specifically for chiplet applications to reduce thermal resistance between dies and heat spreaders.

The economic implications of these trade-offs are substantial. Over-designing cooling solutions increases product cost, while under-designing risks performance degradation. Industry data suggests that optimizing the power-thermal envelope can reduce total system cost by 8-15% compared to conservative thermal designs, while maintaining reliability targets.

Future chiplet designs will likely incorporate more sophisticated power-thermal co-optimization techniques, including AI-driven thermal prediction models and dynamic thermal management systems that can anticipate and mitigate hotspots before they impact performance. These approaches will be essential as UCIe adoption expands into more diverse application domains with varying thermal constraints and cooling capabilities.

Power density in advanced chiplet designs has reached unprecedented levels, with some high-performance computing chiplets exceeding 500W/cm² at hotspots. This creates significant thermal management challenges that cannot be addressed through traditional cooling solutions alone. The heterogeneous integration of multiple chiplets with varying power profiles further complicates thermal design considerations.

Thermal constraints often become the limiting factor in chiplet performance scaling. When thermal limits are reached, frequency throttling occurs, negating potential performance gains from advanced process nodes. This creates a fundamental tension between power delivery capabilities and thermal dissipation limits. UCIe implementations must carefully balance these competing requirements through co-design approaches.

The thermal coupling between adjacent chiplets introduces additional complexity. Hot-spot sharing across chiplet boundaries can create thermal gradients that affect signal integrity in high-speed UCIe links. Research indicates that temperature differentials exceeding 20°C between communicating chiplets can increase bit error rates by up to 30% in 32GT/s UCIe implementations.

Power-thermal optimization strategies include dynamic power allocation between chiplets, thermal-aware floorplanning with strategic keep-out zones, and adaptive cooling solutions. Advanced thermal interface materials (TIMs) with conductivity exceeding 20W/m·K are being developed specifically for chiplet applications to reduce thermal resistance between dies and heat spreaders.

The economic implications of these trade-offs are substantial. Over-designing cooling solutions increases product cost, while under-designing risks performance degradation. Industry data suggests that optimizing the power-thermal envelope can reduce total system cost by 8-15% compared to conservative thermal designs, while maintaining reliability targets.

Future chiplet designs will likely incorporate more sophisticated power-thermal co-optimization techniques, including AI-driven thermal prediction models and dynamic thermal management systems that can anticipate and mitigate hotspots before they impact performance. These approaches will be essential as UCIe adoption expands into more diverse application domains with varying thermal constraints and cooling capabilities.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!