UCIe Testability: Loopback, PRBS, BIST Hooks And Production Screening

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Testing Background and Objectives

Universal Chiplet Interconnect Express (UCIe) has emerged as a critical open standard for chiplet interconnection in the semiconductor industry. The evolution of UCIe technology represents a significant shift from traditional monolithic chip designs to more modular, heterogeneous integration approaches. This transition has been driven by the increasing challenges in semiconductor scaling according to Moore's Law and the growing demand for specialized computing solutions across various applications.

The development of UCIe can be traced back to the broader industry recognition that chiplet-based designs offer advantages in terms of manufacturing yield, design flexibility, and cost optimization. The standard was officially introduced in March 2022 by a consortium of leading semiconductor companies, including Intel, AMD, Arm, TSMC, and Samsung, among others. This collaborative effort aimed to establish a unified approach to chiplet interconnection that would enable interoperability across different vendors and technologies.

UCIe testing capabilities have evolved alongside the standard itself, with increasing emphasis on ensuring reliable high-speed communication between chiplets. The initial UCIe 1.0 specification focused on establishing the fundamental physical and protocol layers, while subsequent iterations have enhanced the testing frameworks to address the complexities of multi-vendor chiplet ecosystems.

The primary objectives of UCIe testability are multifaceted. First, to ensure signal integrity across the die-to-die interfaces operating at high data rates (up to 16 GT/s in UCIe 1.0, with higher rates anticipated in future versions). Second, to provide comprehensive validation mechanisms that can be implemented across different manufacturing processes and packaging technologies. Third, to establish standardized testing methodologies that facilitate interoperability verification between chiplets from different vendors.

The specific testing mechanisms of loopback testing, Pseudo-Random Binary Sequence (PRBS) generation and checking, Built-In Self-Test (BIST) hooks, and production screening represent critical components of the UCIe testing ecosystem. These mechanisms collectively address the challenges of validating high-speed serial links between chiplets, detecting manufacturing defects, and ensuring performance consistency across mass-produced chiplet-based systems.

As the semiconductor industry continues to embrace chiplet architectures, the importance of robust testing methodologies becomes increasingly pronounced. The UCIe testing framework aims to balance comprehensive validation capabilities with practical implementation considerations, recognizing that effective testing is essential for the broader adoption of chiplet-based designs across computing, networking, storage, and other application domains.

The development of UCIe can be traced back to the broader industry recognition that chiplet-based designs offer advantages in terms of manufacturing yield, design flexibility, and cost optimization. The standard was officially introduced in March 2022 by a consortium of leading semiconductor companies, including Intel, AMD, Arm, TSMC, and Samsung, among others. This collaborative effort aimed to establish a unified approach to chiplet interconnection that would enable interoperability across different vendors and technologies.

UCIe testing capabilities have evolved alongside the standard itself, with increasing emphasis on ensuring reliable high-speed communication between chiplets. The initial UCIe 1.0 specification focused on establishing the fundamental physical and protocol layers, while subsequent iterations have enhanced the testing frameworks to address the complexities of multi-vendor chiplet ecosystems.

The primary objectives of UCIe testability are multifaceted. First, to ensure signal integrity across the die-to-die interfaces operating at high data rates (up to 16 GT/s in UCIe 1.0, with higher rates anticipated in future versions). Second, to provide comprehensive validation mechanisms that can be implemented across different manufacturing processes and packaging technologies. Third, to establish standardized testing methodologies that facilitate interoperability verification between chiplets from different vendors.

The specific testing mechanisms of loopback testing, Pseudo-Random Binary Sequence (PRBS) generation and checking, Built-In Self-Test (BIST) hooks, and production screening represent critical components of the UCIe testing ecosystem. These mechanisms collectively address the challenges of validating high-speed serial links between chiplets, detecting manufacturing defects, and ensuring performance consistency across mass-produced chiplet-based systems.

As the semiconductor industry continues to embrace chiplet architectures, the importance of robust testing methodologies becomes increasingly pronounced. The UCIe testing framework aims to balance comprehensive validation capabilities with practical implementation considerations, recognizing that effective testing is essential for the broader adoption of chiplet-based designs across computing, networking, storage, and other application domains.

Market Demand for Advanced Interconnect Testing Solutions

The demand for advanced interconnect testing solutions has surged dramatically in recent years, driven primarily by the increasing complexity of semiconductor designs and the growing adoption of chiplet architectures. The Universal Chiplet Interconnect Express (UCIe) standard represents a critical advancement in this domain, necessitating sophisticated testing methodologies to ensure reliable high-speed connections between chiplets.

Market research indicates that the semiconductor test equipment market is projected to grow at a compound annual growth rate of 4.5% through 2028, with interconnect testing solutions representing a rapidly expanding segment. This growth is particularly pronounced in data centers and high-performance computing applications, where the need for reliable, high-bandwidth chip-to-chip communication is paramount.

The push toward heterogeneous integration has created significant demand for comprehensive testing solutions that can validate the integrity of die-to-die interfaces. Industry surveys reveal that approximately 85% of semiconductor manufacturers consider advanced interconnect testing capabilities essential for their chiplet-based designs, highlighting the critical nature of UCIe testability features such as loopback testing, Pseudo-Random Binary Sequence (PRBS) generation, and Built-In Self-Test (BIST) mechanisms.

From a geographical perspective, North America and East Asia dominate the demand landscape, with major semiconductor manufacturers and hyperscalers investing heavily in testing infrastructure to support their chiplet integration strategies. The market is particularly robust in regions with concentrated semiconductor manufacturing capabilities, such as Taiwan, South Korea, and the United States.

Customer requirements are increasingly focused on testing solutions that can operate at higher speeds while maintaining accuracy and reliability. The transition to UCIe's advanced interconnect technologies, with data rates exceeding 16 GT/s, has created specific demands for testing equipment capable of validating these high-speed interfaces. Production screening requirements have become more stringent, with manufacturers seeking comprehensive test coverage to identify potential interconnect failures before final assembly.

The economic implications of inadequate testing are substantial, with the cost of detecting and replacing faulty components increasing exponentially at each stage of the production process. This economic reality has driven demand for more sophisticated in-line testing capabilities, particularly BIST hooks that enable efficient production screening without requiring expensive external test equipment.

Industry analysts note that the market is increasingly segmented between high-end, comprehensive testing solutions for cutting-edge applications and more cost-effective options for mainstream production environments. This bifurcation reflects the diverse needs of semiconductor manufacturers operating at different technology nodes and serving various end markets.

Market research indicates that the semiconductor test equipment market is projected to grow at a compound annual growth rate of 4.5% through 2028, with interconnect testing solutions representing a rapidly expanding segment. This growth is particularly pronounced in data centers and high-performance computing applications, where the need for reliable, high-bandwidth chip-to-chip communication is paramount.

The push toward heterogeneous integration has created significant demand for comprehensive testing solutions that can validate the integrity of die-to-die interfaces. Industry surveys reveal that approximately 85% of semiconductor manufacturers consider advanced interconnect testing capabilities essential for their chiplet-based designs, highlighting the critical nature of UCIe testability features such as loopback testing, Pseudo-Random Binary Sequence (PRBS) generation, and Built-In Self-Test (BIST) mechanisms.

From a geographical perspective, North America and East Asia dominate the demand landscape, with major semiconductor manufacturers and hyperscalers investing heavily in testing infrastructure to support their chiplet integration strategies. The market is particularly robust in regions with concentrated semiconductor manufacturing capabilities, such as Taiwan, South Korea, and the United States.

Customer requirements are increasingly focused on testing solutions that can operate at higher speeds while maintaining accuracy and reliability. The transition to UCIe's advanced interconnect technologies, with data rates exceeding 16 GT/s, has created specific demands for testing equipment capable of validating these high-speed interfaces. Production screening requirements have become more stringent, with manufacturers seeking comprehensive test coverage to identify potential interconnect failures before final assembly.

The economic implications of inadequate testing are substantial, with the cost of detecting and replacing faulty components increasing exponentially at each stage of the production process. This economic reality has driven demand for more sophisticated in-line testing capabilities, particularly BIST hooks that enable efficient production screening without requiring expensive external test equipment.

Industry analysts note that the market is increasingly segmented between high-end, comprehensive testing solutions for cutting-edge applications and more cost-effective options for mainstream production environments. This bifurcation reflects the diverse needs of semiconductor manufacturers operating at different technology nodes and serving various end markets.

UCIe Testability Challenges and Limitations

Despite the significant advancements in UCIe (Universal Chiplet Interconnect Express) technology, several critical challenges and limitations persist in its testability framework. The implementation of comprehensive testing mechanisms such as loopback testing, Pseudo-Random Binary Sequence (PRBS) generation, Built-In Self-Test (BIST) hooks, and production screening faces substantial technical hurdles that require innovative solutions.

One of the primary challenges lies in the high-speed nature of UCIe interfaces, which operate at data rates exceeding 16 GT/s. At these speeds, signal integrity issues become pronounced, making accurate testing extremely difficult. Traditional testing methodologies often fail to capture transient anomalies that may occur during actual operation, leading to potential reliability issues in deployed systems.

The miniaturization of chiplet designs further complicates testability. With die-to-die interconnects becoming increasingly dense and compact, physical access for testing probes becomes severely limited. This physical constraint necessitates greater reliance on built-in test structures, which themselves consume valuable silicon area and power resources—creating a challenging design trade-off between testability and performance.

Power management during testing represents another significant challenge. The high-speed SerDes (Serializer/Deserializer) components in UCIe interfaces consume substantial power during operation. When multiple lanes are simultaneously tested using PRBS patterns or loopback configurations, thermal issues can arise that potentially affect test accuracy or even damage the device under test.

Interoperability testing between chiplets from different vendors presents unique difficulties. Despite the standardization efforts of UCIe, subtle implementation differences can lead to compatibility issues that are difficult to detect through standard testing protocols. This challenge is particularly acute in multi-vendor chiplet ecosystems where components must seamlessly integrate despite being manufactured through different processes.

The latency sensitivity of modern applications adds another layer of complexity. Testing methodologies must not only verify data integrity but also ensure that timing requirements are met across various operating conditions. BIST implementations must be sophisticated enough to detect marginal timing violations that could lead to system failures under specific workloads or environmental conditions.

Production screening at scale introduces economic constraints that limit test coverage. Comprehensive testing of all possible failure modes would be prohibitively expensive and time-consuming in high-volume manufacturing environments. Consequently, test engineers must make difficult decisions regarding test coverage versus production throughput, potentially leaving certain failure modes undetected.

Finally, the evolving nature of the UCIe standard itself creates a moving target for test development. As the specification continues to mature and incorporate new features, testing methodologies must adapt accordingly, requiring continuous investment in test infrastructure development and validation.

One of the primary challenges lies in the high-speed nature of UCIe interfaces, which operate at data rates exceeding 16 GT/s. At these speeds, signal integrity issues become pronounced, making accurate testing extremely difficult. Traditional testing methodologies often fail to capture transient anomalies that may occur during actual operation, leading to potential reliability issues in deployed systems.

The miniaturization of chiplet designs further complicates testability. With die-to-die interconnects becoming increasingly dense and compact, physical access for testing probes becomes severely limited. This physical constraint necessitates greater reliance on built-in test structures, which themselves consume valuable silicon area and power resources—creating a challenging design trade-off between testability and performance.

Power management during testing represents another significant challenge. The high-speed SerDes (Serializer/Deserializer) components in UCIe interfaces consume substantial power during operation. When multiple lanes are simultaneously tested using PRBS patterns or loopback configurations, thermal issues can arise that potentially affect test accuracy or even damage the device under test.

Interoperability testing between chiplets from different vendors presents unique difficulties. Despite the standardization efforts of UCIe, subtle implementation differences can lead to compatibility issues that are difficult to detect through standard testing protocols. This challenge is particularly acute in multi-vendor chiplet ecosystems where components must seamlessly integrate despite being manufactured through different processes.

The latency sensitivity of modern applications adds another layer of complexity. Testing methodologies must not only verify data integrity but also ensure that timing requirements are met across various operating conditions. BIST implementations must be sophisticated enough to detect marginal timing violations that could lead to system failures under specific workloads or environmental conditions.

Production screening at scale introduces economic constraints that limit test coverage. Comprehensive testing of all possible failure modes would be prohibitively expensive and time-consuming in high-volume manufacturing environments. Consequently, test engineers must make difficult decisions regarding test coverage versus production throughput, potentially leaving certain failure modes undetected.

Finally, the evolving nature of the UCIe standard itself creates a moving target for test development. As the specification continues to mature and incorporate new features, testing methodologies must adapt accordingly, requiring continuous investment in test infrastructure development and validation.

Current UCIe Loopback, PRBS, and BIST Implementation Approaches

01 UCIe Testing Infrastructure and Methods

Testing infrastructure and methodologies specifically designed for Universal Chiplet Interconnect Express (UCIe) interfaces. These include built-in self-test (BIST) mechanisms, test access ports, and specialized test patterns that can verify the integrity and performance of UCIe connections between chiplets. The testing methods enable validation of high-speed data transmission, signal integrity, and compliance with UCIe specifications.- UCIe Testing Infrastructure and Methods: Testing infrastructure and methodologies specifically designed for Universal Chiplet Interconnect Express (UCIe) interfaces. These include built-in self-test (BIST) mechanisms, test access ports, and specialized test patterns that verify the integrity and performance of UCIe connections between chiplets. The testing methods ensure proper signal integrity, timing parameters, and protocol compliance across the high-speed die-to-die interconnects.

- Boundary Scan and JTAG Integration for UCIe: Implementation of boundary scan techniques and JTAG (Joint Test Action Group) integration specifically adapted for UCIe interfaces. These approaches enable comprehensive testing of interconnections between chiplets without requiring direct physical access to each connection. The boundary scan cells and JTAG controllers are optimized for the high-speed, low-power requirements of UCIe, allowing for efficient testing during manufacturing and in-field diagnostics.

- Loopback Testing for UCIe Interfaces: Loopback testing mechanisms specifically designed for UCIe interfaces that allow transmitted signals to be routed back to the sender for verification. These techniques enable testing of both the physical layer and protocol layer of UCIe connections without requiring external test equipment. The loopback paths can be configured at various points in the signal chain to isolate different components of the interconnect for targeted testing.

- Automated Test Pattern Generation for UCIe: Specialized automated test pattern generation techniques for UCIe interfaces that create optimized test vectors to detect manufacturing defects and verify operational parameters. These patterns are designed to exercise the full range of UCIe functionality, including different speed grades, power states, and protocol features. The test patterns can be applied during wafer testing, package testing, and system-level validation to ensure comprehensive coverage.

- UCIe Compliance and Interoperability Testing: Methods and systems for verifying compliance with the UCIe specification and ensuring interoperability between chiplets from different vendors. These include standardized test suites, reference designs, and validation methodologies that verify all aspects of the UCIe standard including electrical characteristics, protocol behavior, and power management. Compliance testing ensures that chiplets can reliably communicate across the UCIe interface regardless of their source or manufacturing process.

02 Boundary Scan and JTAG Integration for UCIe

Integration of boundary scan techniques and JTAG (Joint Test Action Group) protocols with UCIe interfaces to facilitate testing. These approaches allow for standardized testing of interconnects between chiplets without requiring direct physical access to the connection points. The implementation includes test cells, scan chains, and test controllers specifically adapted for the high-speed, low-latency requirements of UCIe interfaces.Expand Specific Solutions03 Die-to-Die Interface Validation for UCIe

Specialized validation techniques for die-to-die (D2D) interfaces implementing UCIe standards. These techniques focus on verifying the electrical and logical characteristics of connections between chiplets, including signal integrity, timing parameters, and protocol compliance. The validation methods incorporate loopback testing, eye diagram analysis, and bit error rate testing to ensure reliable operation of UCIe interfaces under various operating conditions.Expand Specific Solutions04 UCIe Compliance and Interoperability Testing

Testing methodologies focused on ensuring compliance with UCIe specifications and interoperability between chiplets from different manufacturers. These approaches include standardized test suites, reference designs, and validation platforms that can verify adherence to UCIe electrical, physical, and protocol requirements. The testing frameworks enable certification of UCIe implementations and help ensure seamless integration of chiplets in heterogeneous systems.Expand Specific Solutions05 Automated Test Equipment for UCIe Validation

Specialized automated test equipment (ATE) and software tools designed for UCIe validation in manufacturing and development environments. These systems incorporate high-speed signal generators, analyzers, and automated test pattern generation to efficiently validate UCIe implementations. The equipment supports both wafer-level and package-level testing of chiplets with UCIe interfaces, enabling high-volume production testing and detailed characterization of performance parameters.Expand Specific Solutions

Key Industry Players in UCIe Testing Ecosystem

The UCIe testability market is in its early growth phase, characterized by increasing adoption of advanced testing methodologies for high-speed interconnects. The market is expanding rapidly as chiplet architectures gain prominence, with projections suggesting significant growth over the next five years. Technologically, UCIe testability solutions are evolving from basic loopback testing to sophisticated BIST implementations. Intel leads the ecosystem as a founding member of the UCIe consortium, with significant contributions from proteanTecs, Advantest, and Teradyne in test solutions. Other key players include IBM, Samsung, and NXP developing compatible technologies, while test equipment manufacturers like Rohde & Schwarz and Viavi Solutions provide specialized instrumentation for production screening applications.

Intel Corp.

Technical Solution: Intel's UCIe testability solution integrates comprehensive testing mechanisms including advanced loopback testing, PRBS (Pseudo-Random Binary Sequence) pattern generation, and Built-In Self-Test (BIST) capabilities. Their approach implements both near-end and far-end loopback modes to validate signal integrity across different segments of the interconnect. Intel has developed specialized PRBS generators that can produce patterns up to PRBS31, allowing for thorough stress testing of high-speed SerDes links within the UCIe framework. Their BIST architecture incorporates programmable error counters and detection mechanisms that can identify and categorize various types of transmission errors. For production screening, Intel employs a multi-phase testing methodology that includes wafer-level testing, package-level validation, and system-level verification to ensure UCIe compliance across their chiplet ecosystem.

Strengths: Intel's position as a founding member of the UCIe consortium gives them deep technical expertise and influence over standards development. Their extensive manufacturing infrastructure allows for comprehensive testing across multiple stages of production. Weaknesses: Their testing solutions may be optimized primarily for their own chiplet ecosystem, potentially limiting interoperability with third-party components.

proteanTecs Ltd.

Technical Solution: proteanTecs has developed an advanced UCIe testability solution centered around their Deep Data analytics platform specifically designed for heterogeneous integration challenges. Their approach embeds on-die Agents (monitoring circuits) within chiplets that continuously monitor UCIe interface performance parameters. These Agents collect real-time data on signal integrity, timing margins, and power consumption across the UCIe links. For loopback testing, proteanTecs implements both standard and enhanced loopback modes with parametric measurement capabilities that go beyond simple pass/fail results. Their PRBS testing infrastructure includes customizable pattern generators with error injection capabilities to simulate various stress conditions. The company's BIST implementation features machine learning algorithms that analyze test results to predict potential failures before they occur. For production screening, proteanTecs employs a unique approach called "Chip Telemetry" that combines electrical measurements with advanced analytics to identify marginal devices that might pass traditional testing but fail in the field.

Strengths: proteanTecs' solution provides deeper visibility into UCIe link health through continuous monitoring and predictive analytics, potentially reducing field failures. Their approach enables lifetime monitoring beyond initial production testing. Weaknesses: The embedded monitoring circuits require additional die area and power, which may impact overall system efficiency and cost structure.

Critical UCIe Testing Patents and Technical Literature

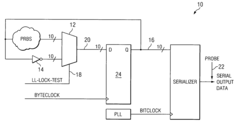

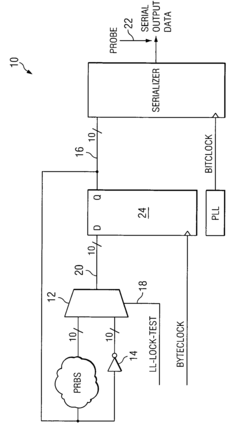

Method of testing phase lock loop status during a Serializer/Deserializer internal loopback built-in self-test

PatentInactiveUS7146284B2

Innovation

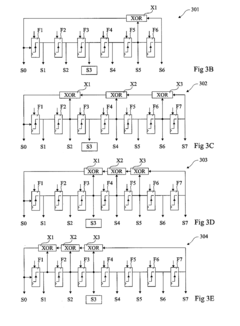

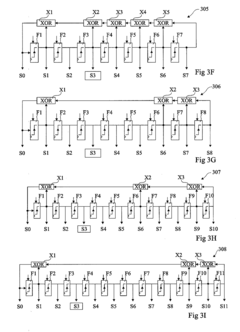

- A modified pseudo random binary sequence (PRBS) generator is configured to produce a low-frequency data pattern that can be verified on the test probe, using additional multiplexers and inverters to generate a low-frequency serial output signal, allowing PLL lock status verification during internal loopback BIST.

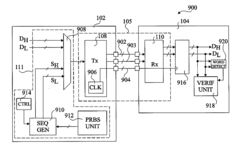

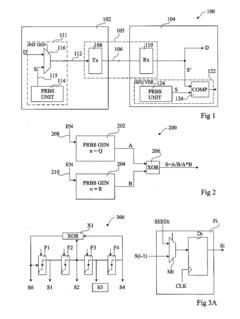

Circuitry for built-in self-test

PatentInactiveUS20110302471A1

Innovation

- A method and circuitry that generates a test sequence by duplicating a bit sequence and combining it with another sequence using an XOR operation, allowing for variable stress levels and efficient transmission over data connections, thereby reducing the need for duplicate PRBS generators and enhancing flexibility.

Production Yield Optimization Strategies

Production yield optimization represents a critical aspect of UCIe (Universal Chiplet Interconnect Express) implementation, particularly concerning testability features such as Loopback, PRBS (Pseudo-Random Binary Sequence), and BIST (Built-In Self-Test) hooks. Effective yield management strategies can significantly reduce manufacturing costs while ensuring high-quality chiplet interconnects.

The foundation of yield optimization begins with comprehensive Design for Testability (DFT) implementation. UCIe designs must incorporate sufficient test points and access mechanisms that enable thorough testing without compromising performance. Strategic placement of loopback paths at critical interface points allows for efficient signal integrity verification without requiring external test equipment for every connection.

Statistical Process Control (SPC) methodologies tailored specifically for UCIe manufacturing provide early detection of process drift. By continuously monitoring key electrical parameters such as signal eye height, jitter, and bit error rates during PRBS testing, manufacturers can identify and address process variations before they impact yield significantly. This proactive approach reduces scrap rates and rework requirements.

Adaptive test flows represent another crucial strategy for UCIe yield optimization. Rather than applying identical test sequences to all devices, test programs can dynamically adjust based on initial characterization results. For instance, if a chiplet passes basic loopback tests with substantial margin, certain detailed BIST sequences might be abbreviated, improving throughput without compromising quality assurance.

Binning strategies specifically designed for UCIe implementations allow manufacturers to maximize usable output. Not all chiplets need to operate at the highest performance tier. By categorizing products based on speed grades, power consumption profiles, or lane counts, manufacturers can salvage partially functional units that would otherwise be discarded, significantly improving economic yield.

Multi-site testing capabilities, when properly implemented with UCIe test hooks, can dramatically increase throughput. The parallel testing architecture must be carefully designed to avoid signal integrity issues while maximizing the number of devices under test simultaneously. Advanced test equipment with multiple independent channels becomes essential for this approach.

Failure analysis feedback loops complete the yield optimization ecosystem. When BIST or PRBS tests identify defects, automated systems should capture comprehensive diagnostic data for rapid root cause analysis. This information must flow back to design and process engineering teams to implement corrective actions, creating a continuous improvement cycle that progressively enhances yield metrics over the product lifecycle.

The foundation of yield optimization begins with comprehensive Design for Testability (DFT) implementation. UCIe designs must incorporate sufficient test points and access mechanisms that enable thorough testing without compromising performance. Strategic placement of loopback paths at critical interface points allows for efficient signal integrity verification without requiring external test equipment for every connection.

Statistical Process Control (SPC) methodologies tailored specifically for UCIe manufacturing provide early detection of process drift. By continuously monitoring key electrical parameters such as signal eye height, jitter, and bit error rates during PRBS testing, manufacturers can identify and address process variations before they impact yield significantly. This proactive approach reduces scrap rates and rework requirements.

Adaptive test flows represent another crucial strategy for UCIe yield optimization. Rather than applying identical test sequences to all devices, test programs can dynamically adjust based on initial characterization results. For instance, if a chiplet passes basic loopback tests with substantial margin, certain detailed BIST sequences might be abbreviated, improving throughput without compromising quality assurance.

Binning strategies specifically designed for UCIe implementations allow manufacturers to maximize usable output. Not all chiplets need to operate at the highest performance tier. By categorizing products based on speed grades, power consumption profiles, or lane counts, manufacturers can salvage partially functional units that would otherwise be discarded, significantly improving economic yield.

Multi-site testing capabilities, when properly implemented with UCIe test hooks, can dramatically increase throughput. The parallel testing architecture must be carefully designed to avoid signal integrity issues while maximizing the number of devices under test simultaneously. Advanced test equipment with multiple independent channels becomes essential for this approach.

Failure analysis feedback loops complete the yield optimization ecosystem. When BIST or PRBS tests identify defects, automated systems should capture comprehensive diagnostic data for rapid root cause analysis. This information must flow back to design and process engineering teams to implement corrective actions, creating a continuous improvement cycle that progressively enhances yield metrics over the product lifecycle.

Test Coverage and Quality Metrics

Comprehensive test coverage and quality metrics are essential components of UCIe testability strategy, providing quantifiable measures to evaluate the effectiveness of testing methodologies. For UCIe interfaces, coverage metrics must span multiple dimensions including physical layer parameters, protocol compliance, and system-level functionality. The primary coverage domains include DC parametric testing, AC timing verification, and functional protocol testing across different operating conditions.

Test coverage for UCIe loopback mechanisms should achieve at least 95% of all possible data paths to ensure robust interconnect validation. This includes both near-end and far-end loopback configurations, with metrics tracking the percentage of successfully tested lanes and the bit error detection capability. Quality metrics for PRBS testing typically measure the Bit Error Rate (BER) performance, with industry standards requiring BER levels below 10^-12 for production qualification.

Built-In Self-Test (BIST) coverage metrics focus on fault detection capabilities, measuring the percentage of potential defects that can be identified through automated testing. Advanced UCIe implementations should target BIST coverage exceeding 90% of common failure modes, including stuck-at faults, crosstalk issues, and impedance mismatches. The quality of BIST implementations is further evaluated through false positive/negative rates, which should remain below 0.1% for production-grade systems.

Production screening metrics incorporate yield analysis, with particular attention to parametric distributions that indicate process stability. Statistical Process Control (SPC) methods are applied to monitor key parameters such as voltage margins, timing margins, and signal integrity measurements. Quality metrics for production screening include Defects Per Million (DPM) rates, with leading manufacturers targeting DPM levels below 100 for UCIe interfaces.

Test coverage correlation between different test methodologies provides important validation of the overall test strategy. Cross-verification between loopback tests, PRBS pattern testing, and BIST results should demonstrate at least 85% correlation to ensure consistent quality assessment. Discrepancies between test methodologies require thorough investigation to identify potential coverage gaps or measurement inconsistencies.

Time-domain and frequency-domain coverage metrics complement each other in UCIe testing. Eye diagram measurements quantify signal quality through metrics like eye height, eye width, and jitter components, while frequency-domain analysis evaluates channel characteristics through insertion loss, return loss, and crosstalk measurements. A comprehensive test strategy must achieve balanced coverage across both domains to ensure robust performance across all operating conditions.

Test coverage for UCIe loopback mechanisms should achieve at least 95% of all possible data paths to ensure robust interconnect validation. This includes both near-end and far-end loopback configurations, with metrics tracking the percentage of successfully tested lanes and the bit error detection capability. Quality metrics for PRBS testing typically measure the Bit Error Rate (BER) performance, with industry standards requiring BER levels below 10^-12 for production qualification.

Built-In Self-Test (BIST) coverage metrics focus on fault detection capabilities, measuring the percentage of potential defects that can be identified through automated testing. Advanced UCIe implementations should target BIST coverage exceeding 90% of common failure modes, including stuck-at faults, crosstalk issues, and impedance mismatches. The quality of BIST implementations is further evaluated through false positive/negative rates, which should remain below 0.1% for production-grade systems.

Production screening metrics incorporate yield analysis, with particular attention to parametric distributions that indicate process stability. Statistical Process Control (SPC) methods are applied to monitor key parameters such as voltage margins, timing margins, and signal integrity measurements. Quality metrics for production screening include Defects Per Million (DPM) rates, with leading manufacturers targeting DPM levels below 100 for UCIe interfaces.

Test coverage correlation between different test methodologies provides important validation of the overall test strategy. Cross-verification between loopback tests, PRBS pattern testing, and BIST results should demonstrate at least 85% correlation to ensure consistent quality assessment. Discrepancies between test methodologies require thorough investigation to identify potential coverage gaps or measurement inconsistencies.

Time-domain and frequency-domain coverage metrics complement each other in UCIe testing. Eye diagram measurements quantify signal quality through metrics like eye height, eye width, and jitter components, while frequency-domain analysis evaluates channel characteristics through insertion loss, return loss, and crosstalk measurements. A comprehensive test strategy must achieve balanced coverage across both domains to ensure robust performance across all operating conditions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!