ARM Architecture in Augmented Reality: Performance Tuning

MAR 25, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

ARM AR Performance Background and Objectives

ARM architecture has emerged as a dominant force in mobile computing, fundamentally reshaping the landscape of augmented reality applications. The evolution from traditional x86 processors to ARM-based systems represents a paradigm shift driven by the critical demands of AR workloads: real-time processing, energy efficiency, and thermal management. ARM's reduced instruction set computing philosophy aligns perfectly with AR requirements, where millisecond-level latency and sustained performance are non-negotiable.

The historical trajectory of ARM in AR began with early mobile AR experiments on smartphones, where developers quickly discovered that traditional performance optimization techniques were insufficient. ARM processors, initially designed for embedded systems, have undergone significant architectural enhancements to support complex AR computations including simultaneous localization and mapping, object recognition, and real-time rendering.

Current AR applications demand unprecedented computational capabilities while maintaining strict power consumption limits. ARM's heterogeneous computing approach, featuring big.LITTLE core configurations and specialized processing units, provides the architectural foundation necessary for AR workloads. The integration of dedicated neural processing units and advanced GPU architectures within ARM system-on-chips has created new possibilities for on-device AR processing.

The primary technical objective centers on achieving consistent 60-90 FPS rendering performance while maintaining sub-20ms motion-to-photon latency across diverse AR scenarios. This requires sophisticated performance tuning strategies that leverage ARM's unique architectural features, including dynamic voltage and frequency scaling, cache optimization, and thermal throttling management.

Secondary objectives encompass maximizing battery life through intelligent workload distribution across ARM's heterogeneous cores, optimizing memory bandwidth utilization for large AR datasets, and implementing predictive performance scaling based on application demands. These objectives directly address the fundamental challenge of delivering desktop-class AR experiences on mobile ARM platforms.

The convergence of ARM architecture evolution and AR application requirements has created a unique optimization landscape where traditional performance metrics must be balanced against power consumption, thermal constraints, and user experience quality. Understanding this complex interplay forms the foundation for effective ARM-based AR performance tuning strategies.

The historical trajectory of ARM in AR began with early mobile AR experiments on smartphones, where developers quickly discovered that traditional performance optimization techniques were insufficient. ARM processors, initially designed for embedded systems, have undergone significant architectural enhancements to support complex AR computations including simultaneous localization and mapping, object recognition, and real-time rendering.

Current AR applications demand unprecedented computational capabilities while maintaining strict power consumption limits. ARM's heterogeneous computing approach, featuring big.LITTLE core configurations and specialized processing units, provides the architectural foundation necessary for AR workloads. The integration of dedicated neural processing units and advanced GPU architectures within ARM system-on-chips has created new possibilities for on-device AR processing.

The primary technical objective centers on achieving consistent 60-90 FPS rendering performance while maintaining sub-20ms motion-to-photon latency across diverse AR scenarios. This requires sophisticated performance tuning strategies that leverage ARM's unique architectural features, including dynamic voltage and frequency scaling, cache optimization, and thermal throttling management.

Secondary objectives encompass maximizing battery life through intelligent workload distribution across ARM's heterogeneous cores, optimizing memory bandwidth utilization for large AR datasets, and implementing predictive performance scaling based on application demands. These objectives directly address the fundamental challenge of delivering desktop-class AR experiences on mobile ARM platforms.

The convergence of ARM architecture evolution and AR application requirements has created a unique optimization landscape where traditional performance metrics must be balanced against power consumption, thermal constraints, and user experience quality. Understanding this complex interplay forms the foundation for effective ARM-based AR performance tuning strategies.

Market Demand for ARM-based AR Solutions

The global augmented reality market has experienced unprecedented growth, with ARM-based processors emerging as the dominant architecture for mobile AR applications. This surge is primarily driven by the proliferation of smartphones and tablets equipped with ARM System-on-Chip solutions, which offer an optimal balance between computational performance and power efficiency essential for AR experiences.

Consumer demand for ARM-based AR solutions spans multiple sectors, with mobile gaming representing the largest market segment. Popular AR games and social media filters have demonstrated the mass-market appeal of ARM-powered AR experiences, creating substantial demand for enhanced performance optimization. The accessibility of ARM-based devices has democratized AR technology, making it available to billions of users worldwide rather than limiting it to specialized hardware.

Enterprise applications constitute another significant demand driver for ARM-based AR solutions. Industries including manufacturing, healthcare, education, and retail are increasingly adopting ARM-powered tablets and mobile devices for AR-enabled training, maintenance, and customer engagement applications. The portability and battery life advantages of ARM architecture make these devices particularly suitable for field operations and extended use scenarios.

The automotive sector presents emerging opportunities for ARM-based AR implementations, particularly in heads-up displays and navigation systems. As vehicles become increasingly connected and autonomous, the demand for energy-efficient processing solutions that can handle real-time AR overlays continues to expand. ARM processors offer the thermal management and power consumption characteristics necessary for automotive integration.

Market research indicates strong growth potential in wearable AR devices powered by ARM architecture. Smart glasses and mixed reality headsets require the low-power, high-performance characteristics that ARM processors provide. The miniaturization capabilities of ARM designs enable manufacturers to create lighter, more comfortable wearable devices while maintaining sufficient processing power for complex AR applications.

Healthcare applications represent a specialized but growing market segment, where ARM-based AR solutions enable surgical guidance, medical training, and patient care applications. The reliability and power efficiency of ARM architecture align well with the stringent requirements of medical device applications, driving sustained demand in this sector.

Consumer demand for ARM-based AR solutions spans multiple sectors, with mobile gaming representing the largest market segment. Popular AR games and social media filters have demonstrated the mass-market appeal of ARM-powered AR experiences, creating substantial demand for enhanced performance optimization. The accessibility of ARM-based devices has democratized AR technology, making it available to billions of users worldwide rather than limiting it to specialized hardware.

Enterprise applications constitute another significant demand driver for ARM-based AR solutions. Industries including manufacturing, healthcare, education, and retail are increasingly adopting ARM-powered tablets and mobile devices for AR-enabled training, maintenance, and customer engagement applications. The portability and battery life advantages of ARM architecture make these devices particularly suitable for field operations and extended use scenarios.

The automotive sector presents emerging opportunities for ARM-based AR implementations, particularly in heads-up displays and navigation systems. As vehicles become increasingly connected and autonomous, the demand for energy-efficient processing solutions that can handle real-time AR overlays continues to expand. ARM processors offer the thermal management and power consumption characteristics necessary for automotive integration.

Market research indicates strong growth potential in wearable AR devices powered by ARM architecture. Smart glasses and mixed reality headsets require the low-power, high-performance characteristics that ARM processors provide. The miniaturization capabilities of ARM designs enable manufacturers to create lighter, more comfortable wearable devices while maintaining sufficient processing power for complex AR applications.

Healthcare applications represent a specialized but growing market segment, where ARM-based AR solutions enable surgical guidance, medical training, and patient care applications. The reliability and power efficiency of ARM architecture align well with the stringent requirements of medical device applications, driving sustained demand in this sector.

Current ARM AR Performance Bottlenecks and Challenges

ARM-based processors in augmented reality applications face significant computational bottlenecks that directly impact user experience and system performance. The primary challenge stems from the intensive parallel processing requirements of AR workloads, which demand simultaneous execution of computer vision algorithms, 3D rendering, sensor fusion, and real-time tracking operations. Current ARM architectures, while energy-efficient, struggle to maintain consistent frame rates above 60 FPS when handling complex AR scenes with multiple virtual objects and high-resolution textures.

Memory bandwidth limitations represent another critical bottleneck in ARM AR implementations. The unified memory architecture, though beneficial for power consumption, creates contention between CPU and GPU operations when processing large datasets typical in AR applications. This becomes particularly problematic during simultaneous SLAM processing and graphics rendering, where memory access patterns can cause significant performance degradation and increased latency.

Thermal management poses substantial challenges for sustained AR performance on ARM devices. The continuous operation of multiple processing units generates heat that triggers thermal throttling mechanisms, leading to dynamic frequency scaling that compromises real-time performance guarantees. This thermal constraint becomes more severe in mobile form factors where heat dissipation capabilities are limited, directly affecting the stability of tracking algorithms and rendering quality.

Power efficiency requirements create additional performance constraints unique to ARM AR systems. The need to balance computational performance with battery life forces developers to implement aggressive power management strategies that can introduce performance variability. Dynamic voltage and frequency scaling, while essential for thermal management, creates unpredictable execution times that complicate real-time AR pipeline optimization.

Cache hierarchy limitations in current ARM designs present specific challenges for AR workloads characterized by irregular memory access patterns. Computer vision algorithms and 3D graphics operations exhibit poor cache locality, leading to frequent cache misses that significantly impact performance. The relatively smaller cache sizes compared to x86 architectures exacerbate this issue, particularly when processing high-resolution camera feeds and complex 3D models simultaneously.

Instruction set architecture constraints further limit optimization opportunities for AR-specific operations. While ARM processors include NEON SIMD extensions, the instruction width and available operations are insufficient for optimal implementation of certain computer vision kernels and matrix operations critical to AR applications. This limitation necessitates software-based optimizations that cannot fully exploit the underlying hardware capabilities, resulting in suboptimal performance compared to specialized processing units.

Memory bandwidth limitations represent another critical bottleneck in ARM AR implementations. The unified memory architecture, though beneficial for power consumption, creates contention between CPU and GPU operations when processing large datasets typical in AR applications. This becomes particularly problematic during simultaneous SLAM processing and graphics rendering, where memory access patterns can cause significant performance degradation and increased latency.

Thermal management poses substantial challenges for sustained AR performance on ARM devices. The continuous operation of multiple processing units generates heat that triggers thermal throttling mechanisms, leading to dynamic frequency scaling that compromises real-time performance guarantees. This thermal constraint becomes more severe in mobile form factors where heat dissipation capabilities are limited, directly affecting the stability of tracking algorithms and rendering quality.

Power efficiency requirements create additional performance constraints unique to ARM AR systems. The need to balance computational performance with battery life forces developers to implement aggressive power management strategies that can introduce performance variability. Dynamic voltage and frequency scaling, while essential for thermal management, creates unpredictable execution times that complicate real-time AR pipeline optimization.

Cache hierarchy limitations in current ARM designs present specific challenges for AR workloads characterized by irregular memory access patterns. Computer vision algorithms and 3D graphics operations exhibit poor cache locality, leading to frequent cache misses that significantly impact performance. The relatively smaller cache sizes compared to x86 architectures exacerbate this issue, particularly when processing high-resolution camera feeds and complex 3D models simultaneously.

Instruction set architecture constraints further limit optimization opportunities for AR-specific operations. While ARM processors include NEON SIMD extensions, the instruction width and available operations are insufficient for optimal implementation of certain computer vision kernels and matrix operations critical to AR applications. This limitation necessitates software-based optimizations that cannot fully exploit the underlying hardware capabilities, resulting in suboptimal performance compared to specialized processing units.

Existing ARM Performance Optimization Solutions

01 Instruction set optimization and execution efficiency

Techniques for optimizing ARM instruction set execution to improve performance include enhanced instruction decoding, parallel execution pipelines, and efficient instruction scheduling. These methods focus on reducing instruction latency and increasing throughput by optimizing the way instructions are processed and executed within the ARM architecture.- Instruction set optimization and execution efficiency: Techniques for optimizing ARM instruction set execution to improve performance include enhanced instruction decoding, parallel execution units, and efficient pipeline management. These methods focus on reducing instruction latency and increasing throughput by optimizing the way instructions are fetched, decoded, and executed in ARM processors.

- Memory access and cache optimization: Performance improvements through advanced memory hierarchy designs, cache management strategies, and memory access patterns specific to ARM architecture. These techniques include multi-level cache optimization, prefetching mechanisms, and memory bandwidth enhancement to reduce memory access latency and improve overall system performance.

- Power efficiency and performance scaling: Methods for balancing performance and power consumption in ARM-based systems through dynamic voltage and frequency scaling, power gating, and workload-aware performance optimization. These approaches enable ARM processors to deliver high performance while maintaining energy efficiency across different operating conditions.

- Multi-core and parallel processing optimization: Techniques for enhancing performance in multi-core ARM architectures through efficient thread scheduling, load balancing, inter-core communication optimization, and parallel task execution. These methods maximize the utilization of multiple processing cores to achieve higher computational throughput and system responsiveness.

- Hardware-software co-optimization and virtualization: Performance enhancement through integrated hardware and software optimization strategies, including virtualization support, hardware acceleration for specific workloads, and system-level performance monitoring. These techniques leverage both architectural features and software optimizations to maximize ARM processor performance in various application scenarios.

02 Memory access and cache optimization

Performance improvements through enhanced memory hierarchy management, including cache coherency protocols, prefetching mechanisms, and memory access scheduling. These techniques aim to reduce memory latency and improve data availability by optimizing how the ARM processor interacts with various levels of cache and main memory.Expand Specific Solutions03 Multi-core and parallel processing capabilities

Enhancements to ARM architecture for supporting multiple processing cores and parallel execution of tasks. This includes techniques for workload distribution, inter-core communication, synchronization mechanisms, and resource sharing to maximize overall system performance through concurrent processing.Expand Specific Solutions04 Power management and performance scaling

Dynamic performance optimization techniques that balance processing power with energy efficiency. These include dynamic voltage and frequency scaling, power state transitions, and adaptive performance modes that adjust processor behavior based on workload requirements to optimize both performance and power consumption.Expand Specific Solutions05 Hardware acceleration and specialized processing units

Integration of specialized hardware accelerators and coprocessors within the ARM architecture to enhance performance for specific tasks. This includes dedicated units for graphics processing, signal processing, cryptographic operations, and other computationally intensive functions that can be offloaded from the main processor cores.Expand Specific Solutions

Key Players in ARM AR Ecosystem

The ARM architecture in augmented reality performance tuning market represents an emerging but rapidly evolving competitive landscape. The industry is transitioning from early adoption to mainstream integration, driven by increasing demand for mobile AR experiences and edge computing capabilities. Market growth is accelerated by major technology companies investing heavily in AR hardware and software optimization. Technology maturity varies significantly across players, with established giants like Samsung Electronics, Sony Group, and Google LLC leading in ARM-based processor development and AR platform integration. Meta Platforms Technologies and Snap Inc. drive consumer AR applications, while Chinese companies including Huawei Device, OPPO Mobile, and specialized AR firms like Chengdu Ideal Realm Technology focus on hardware optimization and regional market penetration. The competitive dynamics show a mix of semiconductor manufacturers, device makers, and software platforms converging to address ARM architecture performance challenges in AR applications.

Snap, Inc.

Technical Solution: Snap has developed advanced AR performance optimization techniques specifically for ARM-based mobile devices through their Snapchat platform. Their approach focuses on efficient rendering pipelines that leverage ARM's NEON SIMD instructions for accelerated computer vision processing. The company implements dynamic quality scaling algorithms that adjust AR content complexity based on device thermal states and battery levels. Their Lens Studio platform incorporates ARM-optimized shaders and uses predictive frame scheduling to maintain consistent 60fps performance. Snap's AR engine utilizes ARM's Mali GPU architecture features including tile-based rendering and bandwidth optimization techniques to reduce power consumption while maintaining visual fidelity.

Strengths: Extensive real-world deployment experience with millions of daily users, proven mobile AR optimization expertise. Weaknesses: Limited to consumer-focused applications, less emphasis on enterprise AR solutions.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung leverages its Exynos ARM processors with integrated NPU units to accelerate AR workloads through hardware-software co-optimization. Their AR framework utilizes custom ARM assembly optimizations for critical computer vision algorithms including SLAM and object tracking. The company implements thermal-aware performance scaling that dynamically adjusts CPU and GPU frequencies to prevent throttling during intensive AR sessions. Samsung's approach includes memory bandwidth optimization techniques specific to ARM's cache hierarchy and implements custom GPU drivers that maximize Mali performance for AR rendering pipelines. Their One UI AR features utilize ARM TrustZone for secure AR applications and implement power-efficient background processing.

Strengths: Deep hardware integration capabilities, comprehensive mobile device ecosystem control. Weaknesses: Solutions primarily focused on Samsung devices, limited cross-platform compatibility.

Core ARM Tuning Innovations for AR Workloads

Apparatus and method for optimizing performance of augmented reality

PatentPendingKR1020230125693A

Innovation

- An electronic device with a communication module and processor optimizes AR performance by load balancing AR tasks between the AR device and itself, using dynamic load balancing and personalized performance presets based on device performance, user environment, and AR app characteristics, with support from a server device for data collection and management.

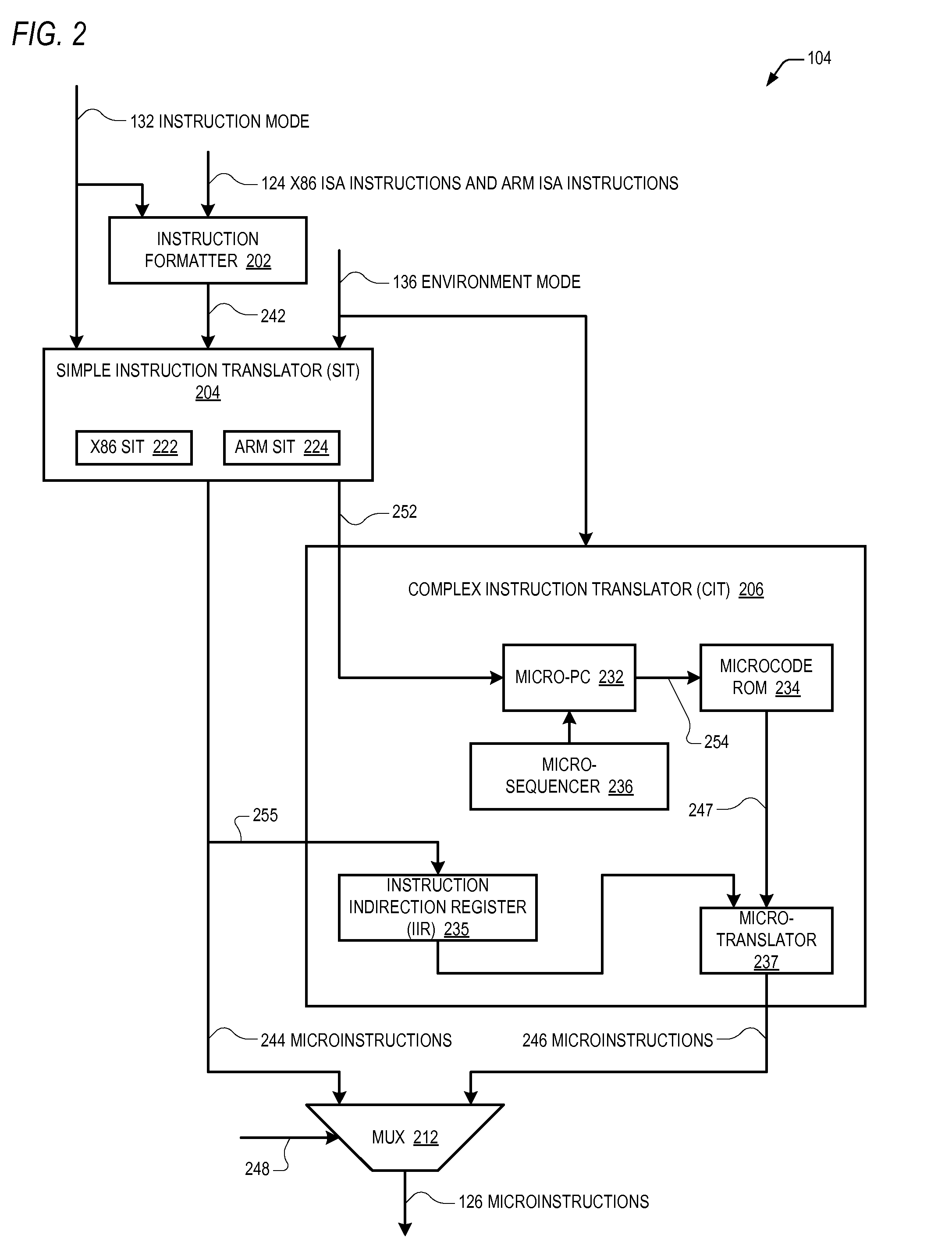

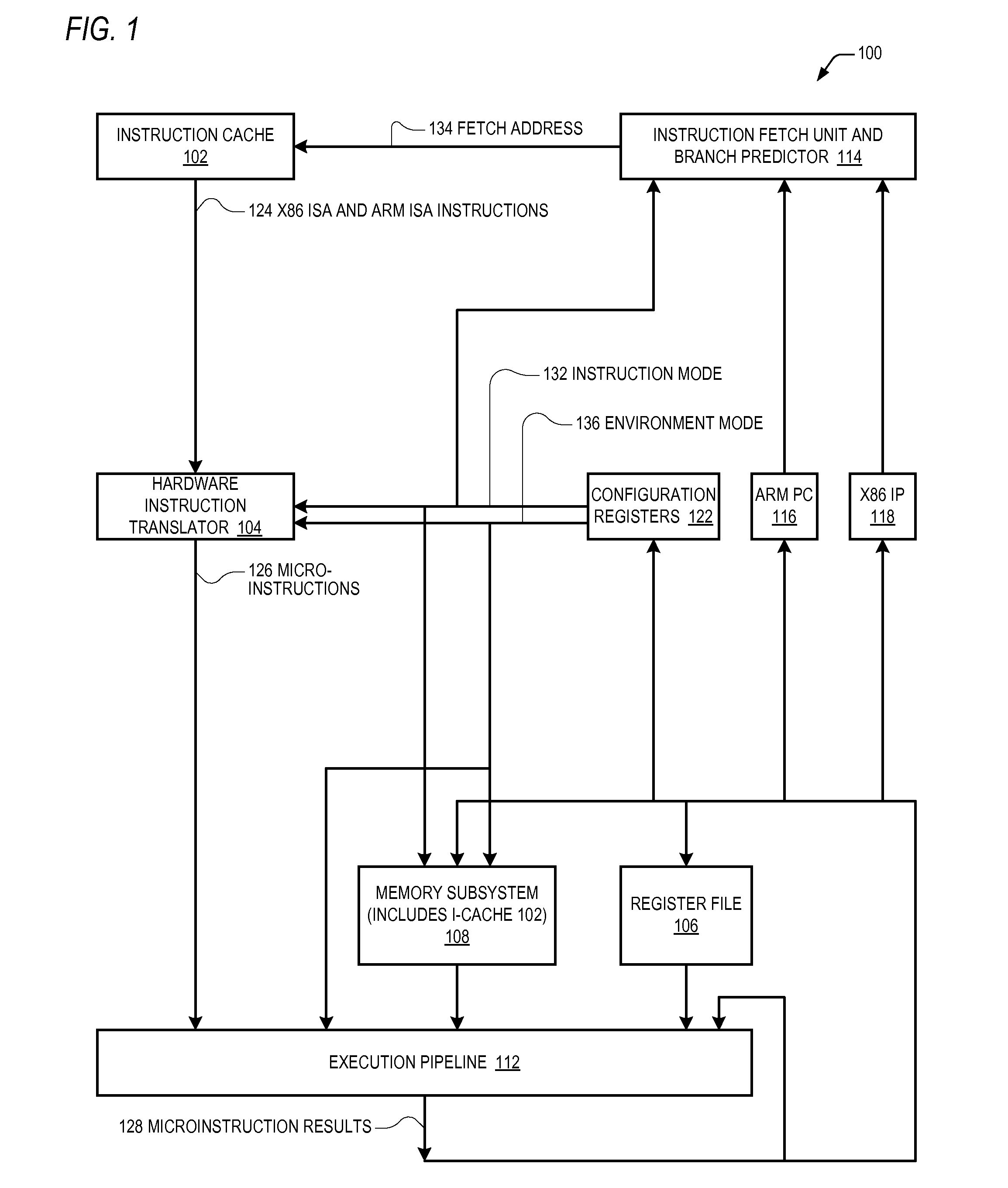

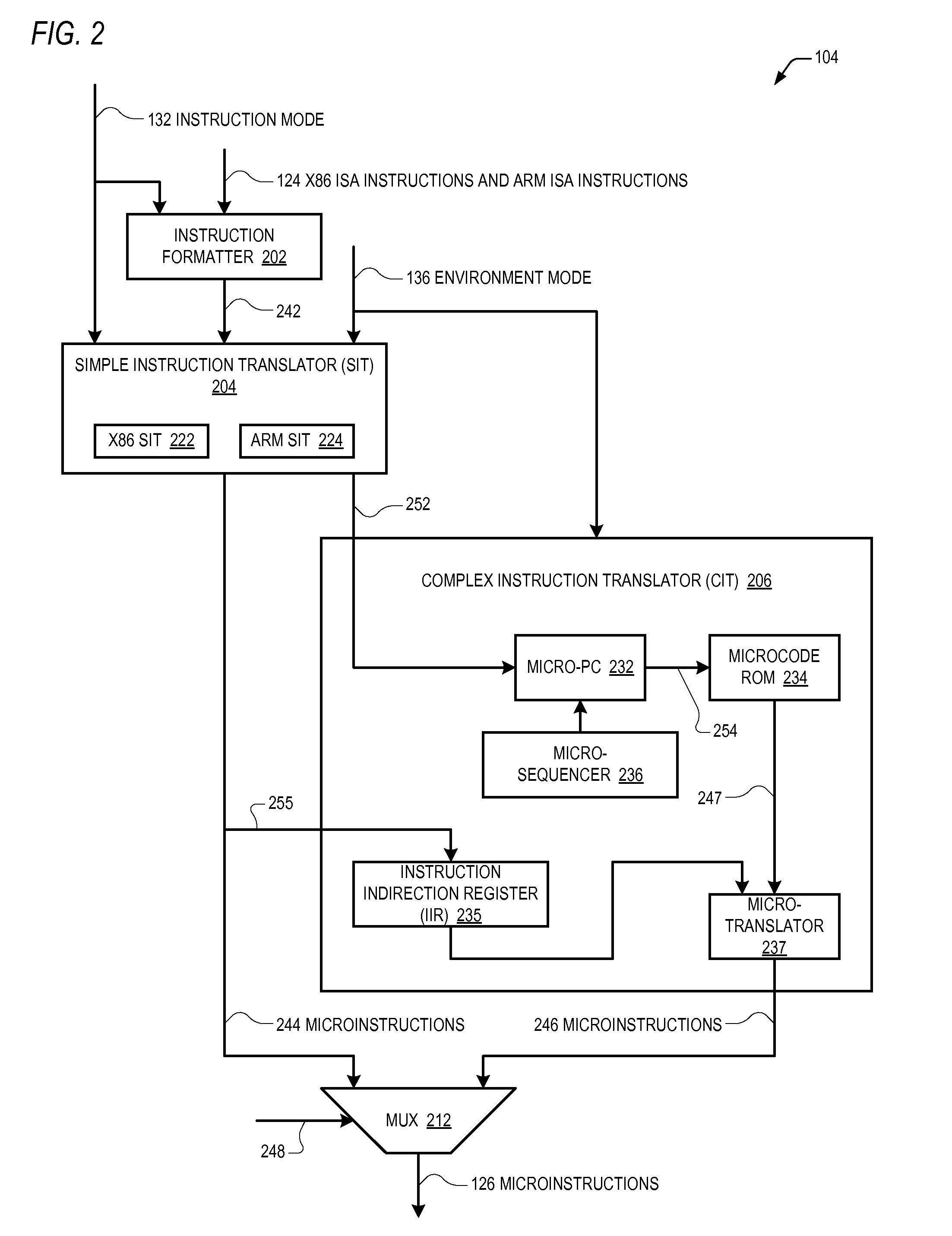

Multi-core microprocessor that performs x86 isa and arm isa machine language program instructions by hardware translation into microinstructions executed by common execution pipeline

PatentActiveUS20120260065A1

Innovation

- A multi-core processor design that includes hardware instruction translators to translate x86 and ARM instruction set architecture (ISA) machine language programs into microinstructions, which are then executed by a common execution pipeline, allowing the processor to run both x86 and ARM ISA programs.

Power Efficiency Considerations in ARM AR Systems

Power efficiency represents a critical design constraint in ARM-based augmented reality systems, where the demanding computational requirements of real-time rendering, computer vision, and sensor fusion must be balanced against the thermal and battery limitations of mobile and wearable devices. ARM processors, with their inherent low-power architecture, provide a foundation for energy-efficient AR implementations, but achieving optimal power performance requires sophisticated tuning strategies across multiple system layers.

The heterogeneous computing capabilities of modern ARM SoCs, featuring big.LITTLE core configurations, enable dynamic workload distribution based on computational intensity and power budgets. AR applications can leverage this architecture by offloading lightweight tracking and sensor processing tasks to energy-efficient LITTLE cores while reserving high-performance big cores for computationally intensive operations such as 3D rendering and complex computer vision algorithms. This approach significantly reduces overall system power consumption while maintaining acceptable performance levels.

Dynamic Voltage and Frequency Scaling (DVFS) mechanisms play a pivotal role in ARM AR power optimization. By continuously monitoring system workload and thermal conditions, DVFS controllers can adjust processor frequencies and voltages in real-time, ensuring that power consumption scales appropriately with computational demands. Advanced implementations incorporate predictive algorithms that anticipate workload changes based on AR application behavior patterns, enabling proactive power management decisions.

GPU power efficiency considerations are equally critical, as graphics rendering typically represents the largest power consumption component in AR systems. ARM Mali GPUs incorporate sophisticated power gating technologies that can selectively disable unused shader cores and processing units during periods of reduced graphical complexity. Adaptive shading techniques, combined with foveated rendering approaches, can dramatically reduce GPU workload by concentrating computational resources on areas of high visual importance while reducing quality in peripheral regions.

Memory subsystem optimization contributes substantially to overall power efficiency in ARM AR implementations. Intelligent memory management strategies, including aggressive texture compression, efficient buffer allocation, and optimized data locality patterns, minimize memory bandwidth requirements and reduce associated power consumption. ARM's cache hierarchy optimizations, particularly L2 and L3 cache configurations, can be tuned to maximize hit rates for AR-specific access patterns.

Thermal management integration becomes essential as sustained AR workloads can quickly approach thermal throttling thresholds. Advanced power management frameworks incorporate thermal feedback loops that proactively reduce system performance before critical temperature limits are reached, ensuring consistent user experience while preventing thermal-induced performance degradation.

The heterogeneous computing capabilities of modern ARM SoCs, featuring big.LITTLE core configurations, enable dynamic workload distribution based on computational intensity and power budgets. AR applications can leverage this architecture by offloading lightweight tracking and sensor processing tasks to energy-efficient LITTLE cores while reserving high-performance big cores for computationally intensive operations such as 3D rendering and complex computer vision algorithms. This approach significantly reduces overall system power consumption while maintaining acceptable performance levels.

Dynamic Voltage and Frequency Scaling (DVFS) mechanisms play a pivotal role in ARM AR power optimization. By continuously monitoring system workload and thermal conditions, DVFS controllers can adjust processor frequencies and voltages in real-time, ensuring that power consumption scales appropriately with computational demands. Advanced implementations incorporate predictive algorithms that anticipate workload changes based on AR application behavior patterns, enabling proactive power management decisions.

GPU power efficiency considerations are equally critical, as graphics rendering typically represents the largest power consumption component in AR systems. ARM Mali GPUs incorporate sophisticated power gating technologies that can selectively disable unused shader cores and processing units during periods of reduced graphical complexity. Adaptive shading techniques, combined with foveated rendering approaches, can dramatically reduce GPU workload by concentrating computational resources on areas of high visual importance while reducing quality in peripheral regions.

Memory subsystem optimization contributes substantially to overall power efficiency in ARM AR implementations. Intelligent memory management strategies, including aggressive texture compression, efficient buffer allocation, and optimized data locality patterns, minimize memory bandwidth requirements and reduce associated power consumption. ARM's cache hierarchy optimizations, particularly L2 and L3 cache configurations, can be tuned to maximize hit rates for AR-specific access patterns.

Thermal management integration becomes essential as sustained AR workloads can quickly approach thermal throttling thresholds. Advanced power management frameworks incorporate thermal feedback loops that proactively reduce system performance before critical temperature limits are reached, ensuring consistent user experience while preventing thermal-induced performance degradation.

Thermal Management Strategies for ARM AR Devices

Thermal management represents one of the most critical challenges in ARM-based augmented reality devices, where sustained high-performance computing generates substantial heat within compact form factors. The inherent power efficiency of ARM architectures provides a foundation for thermal optimization, yet the intensive computational demands of real-time AR processing, including simultaneous computer vision, 3D rendering, and sensor fusion, create significant thermal stress that requires sophisticated management strategies.

Dynamic thermal throttling emerges as the primary defense mechanism, where ARM processors automatically reduce clock frequencies and voltage levels when temperature thresholds are exceeded. Advanced implementations utilize predictive algorithms that anticipate thermal buildup based on workload patterns, enabling proactive frequency scaling before critical temperatures are reached. This approach maintains performance consistency while preventing thermal damage to sensitive components.

Heterogeneous computing architectures in modern ARM systems enable intelligent workload distribution across different processing units to optimize thermal profiles. By strategically allocating computationally intensive AR tasks between CPU clusters, GPU units, and dedicated neural processing units, thermal loads can be distributed more evenly across the silicon die, preventing localized hotspots that could trigger aggressive throttling.

Hardware-level thermal solutions integrate advanced heat dissipation technologies specifically designed for wearable AR devices. Vapor chamber cooling systems, despite their miniaturized form factor, provide efficient heat spreading across larger surface areas. Graphene-based thermal interface materials offer superior thermal conductivity while maintaining the lightweight characteristics essential for head-mounted displays.

Software optimization strategies focus on thermal-aware scheduling algorithms that consider both performance requirements and thermal constraints. Machine learning models predict thermal behavior based on application usage patterns, enabling preemptive adjustments to processing strategies. Frame rate adaptation techniques dynamically adjust rendering complexity and refresh rates based on thermal headroom, maintaining visual quality while respecting thermal limits.

Ambient temperature compensation mechanisms adjust performance profiles based on environmental conditions, recognizing that AR devices operate across diverse thermal environments. These systems incorporate external temperature sensors and user activity detection to optimize thermal management strategies for specific usage scenarios, ensuring consistent performance regardless of external conditions.

Dynamic thermal throttling emerges as the primary defense mechanism, where ARM processors automatically reduce clock frequencies and voltage levels when temperature thresholds are exceeded. Advanced implementations utilize predictive algorithms that anticipate thermal buildup based on workload patterns, enabling proactive frequency scaling before critical temperatures are reached. This approach maintains performance consistency while preventing thermal damage to sensitive components.

Heterogeneous computing architectures in modern ARM systems enable intelligent workload distribution across different processing units to optimize thermal profiles. By strategically allocating computationally intensive AR tasks between CPU clusters, GPU units, and dedicated neural processing units, thermal loads can be distributed more evenly across the silicon die, preventing localized hotspots that could trigger aggressive throttling.

Hardware-level thermal solutions integrate advanced heat dissipation technologies specifically designed for wearable AR devices. Vapor chamber cooling systems, despite their miniaturized form factor, provide efficient heat spreading across larger surface areas. Graphene-based thermal interface materials offer superior thermal conductivity while maintaining the lightweight characteristics essential for head-mounted displays.

Software optimization strategies focus on thermal-aware scheduling algorithms that consider both performance requirements and thermal constraints. Machine learning models predict thermal behavior based on application usage patterns, enabling preemptive adjustments to processing strategies. Frame rate adaptation techniques dynamically adjust rendering complexity and refresh rates based on thermal headroom, maintaining visual quality while respecting thermal limits.

Ambient temperature compensation mechanisms adjust performance profiles based on environmental conditions, recognizing that AR devices operate across diverse thermal environments. These systems incorporate external temperature sensors and user activity detection to optimize thermal management strategies for specific usage scenarios, ensuring consistent performance regardless of external conditions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!