How to Evaluate ARM Efficiency in Distributed Networks

MAR 25, 20269 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

ARM Efficiency in Distributed Networks Background and Goals

ARM-based processors have emerged as a transformative force in distributed computing environments, fundamentally reshaping how organizations approach energy efficiency and computational performance. The proliferation of ARM architectures across data centers, edge computing nodes, and cloud infrastructure has created an urgent need for comprehensive evaluation methodologies that can accurately assess their operational efficiency within complex distributed systems.

The evolution of ARM processors from mobile devices to enterprise-grade server applications represents a significant paradigm shift in the computing landscape. Modern ARM processors, particularly those designed for server workloads, offer compelling advantages in power consumption, thermal management, and cost-effectiveness compared to traditional x86 architectures. This transition has accelerated with the introduction of high-performance ARM cores capable of handling demanding distributed computing tasks while maintaining superior energy efficiency ratios.

Distributed networks present unique challenges for ARM efficiency evaluation due to their inherent complexity and heterogeneous nature. Unlike monolithic systems, distributed environments involve multiple interconnected nodes, varying workload distributions, network latency considerations, and dynamic resource allocation patterns. These factors create a multidimensional evaluation space where traditional single-node performance metrics become insufficient for comprehensive assessment.

The primary objective of ARM efficiency evaluation in distributed networks centers on developing robust methodologies that capture both individual node performance and system-wide optimization potential. This involves establishing standardized benchmarking frameworks that account for network overhead, inter-node communication patterns, load balancing effectiveness, and energy consumption across the entire distributed infrastructure.

Contemporary evaluation approaches must address the growing demand for sustainable computing solutions while maintaining performance standards required for modern applications. Organizations increasingly prioritize total cost of ownership metrics that encompass not only initial hardware investments but also operational expenses related to power consumption, cooling requirements, and maintenance overhead. ARM processors' inherent energy efficiency characteristics position them as attractive alternatives for large-scale distributed deployments.

The strategic importance of accurate ARM efficiency evaluation extends beyond immediate performance considerations to encompass long-term infrastructure planning and technology adoption decisions. As distributed computing continues to expand across edge computing, IoT networks, and hybrid cloud environments, the ability to quantify and predict ARM processor performance becomes critical for informed architectural choices and resource optimization strategies.

The evolution of ARM processors from mobile devices to enterprise-grade server applications represents a significant paradigm shift in the computing landscape. Modern ARM processors, particularly those designed for server workloads, offer compelling advantages in power consumption, thermal management, and cost-effectiveness compared to traditional x86 architectures. This transition has accelerated with the introduction of high-performance ARM cores capable of handling demanding distributed computing tasks while maintaining superior energy efficiency ratios.

Distributed networks present unique challenges for ARM efficiency evaluation due to their inherent complexity and heterogeneous nature. Unlike monolithic systems, distributed environments involve multiple interconnected nodes, varying workload distributions, network latency considerations, and dynamic resource allocation patterns. These factors create a multidimensional evaluation space where traditional single-node performance metrics become insufficient for comprehensive assessment.

The primary objective of ARM efficiency evaluation in distributed networks centers on developing robust methodologies that capture both individual node performance and system-wide optimization potential. This involves establishing standardized benchmarking frameworks that account for network overhead, inter-node communication patterns, load balancing effectiveness, and energy consumption across the entire distributed infrastructure.

Contemporary evaluation approaches must address the growing demand for sustainable computing solutions while maintaining performance standards required for modern applications. Organizations increasingly prioritize total cost of ownership metrics that encompass not only initial hardware investments but also operational expenses related to power consumption, cooling requirements, and maintenance overhead. ARM processors' inherent energy efficiency characteristics position them as attractive alternatives for large-scale distributed deployments.

The strategic importance of accurate ARM efficiency evaluation extends beyond immediate performance considerations to encompass long-term infrastructure planning and technology adoption decisions. As distributed computing continues to expand across edge computing, IoT networks, and hybrid cloud environments, the ability to quantify and predict ARM processor performance becomes critical for informed architectural choices and resource optimization strategies.

Market Demand for ARM-based Distributed Computing Solutions

The global shift toward energy-efficient computing architectures has positioned ARM-based processors as a compelling alternative to traditional x86 systems in distributed computing environments. This transformation is driven by the increasing demand for sustainable data center operations, where power consumption and thermal management have become critical operational concerns. Organizations are actively seeking solutions that can deliver comparable computational performance while significantly reducing energy costs and carbon footprint.

Cloud service providers represent the largest segment driving ARM adoption in distributed networks. Major hyperscale operators are transitioning substantial portions of their infrastructure to ARM-based instances, motivated by the potential for reduced operational expenses and improved performance-per-watt ratios. This trend has accelerated the development of ARM-optimized software stacks and containerized applications, creating a robust ecosystem that supports enterprise migration strategies.

Edge computing applications constitute another rapidly expanding market segment for ARM-based distributed solutions. The proliferation of Internet of Things devices and real-time processing requirements has created demand for lightweight, power-efficient computing nodes that can operate in resource-constrained environments. ARM processors excel in these scenarios due to their inherent energy efficiency and thermal characteristics, making them ideal for deployment in remote locations with limited power infrastructure.

Enterprise workload modernization initiatives are increasingly incorporating ARM-based architectures as organizations seek to optimize their distributed computing investments. The growing maturity of ARM server ecosystems, including comprehensive software support and vendor partnerships, has reduced adoption barriers and increased confidence in ARM-based solutions for mission-critical applications.

The telecommunications sector presents significant opportunities for ARM-based distributed computing, particularly with the deployment of 5G networks and network function virtualization. Service providers require highly efficient processing capabilities at network edges, where ARM processors can deliver the necessary performance while maintaining strict power and space constraints.

Financial services and high-performance computing markets are emerging as notable adopters, driven by the need for cost-effective scaling of computational resources. The ability to deploy larger numbers of ARM-based nodes within existing power budgets enables organizations to achieve greater parallel processing capabilities for data-intensive workloads.

Cloud service providers represent the largest segment driving ARM adoption in distributed networks. Major hyperscale operators are transitioning substantial portions of their infrastructure to ARM-based instances, motivated by the potential for reduced operational expenses and improved performance-per-watt ratios. This trend has accelerated the development of ARM-optimized software stacks and containerized applications, creating a robust ecosystem that supports enterprise migration strategies.

Edge computing applications constitute another rapidly expanding market segment for ARM-based distributed solutions. The proliferation of Internet of Things devices and real-time processing requirements has created demand for lightweight, power-efficient computing nodes that can operate in resource-constrained environments. ARM processors excel in these scenarios due to their inherent energy efficiency and thermal characteristics, making them ideal for deployment in remote locations with limited power infrastructure.

Enterprise workload modernization initiatives are increasingly incorporating ARM-based architectures as organizations seek to optimize their distributed computing investments. The growing maturity of ARM server ecosystems, including comprehensive software support and vendor partnerships, has reduced adoption barriers and increased confidence in ARM-based solutions for mission-critical applications.

The telecommunications sector presents significant opportunities for ARM-based distributed computing, particularly with the deployment of 5G networks and network function virtualization. Service providers require highly efficient processing capabilities at network edges, where ARM processors can deliver the necessary performance while maintaining strict power and space constraints.

Financial services and high-performance computing markets are emerging as notable adopters, driven by the need for cost-effective scaling of computational resources. The ability to deploy larger numbers of ARM-based nodes within existing power budgets enables organizations to achieve greater parallel processing capabilities for data-intensive workloads.

Current State and Challenges of ARM Performance Evaluation

ARM processors have gained significant traction in distributed network environments due to their energy efficiency and cost-effectiveness. Currently, ARM-based systems are widely deployed in edge computing nodes, IoT gateways, and cloud infrastructure, where power consumption and thermal management are critical considerations. Major cloud providers have introduced ARM-based instances, with Amazon's Graviton processors and Ampere's Altra series leading the market adoption.

The evaluation of ARM efficiency in distributed networks faces several fundamental challenges. Traditional performance metrics designed for x86 architectures often fail to capture the unique characteristics of ARM processors, particularly their heterogeneous core configurations and dynamic voltage scaling capabilities. Current benchmarking tools lack standardized methodologies for measuring ARM performance in distributed scenarios, leading to inconsistent evaluation results across different deployment environments.

Network-specific performance evaluation presents additional complexity. ARM processors exhibit varying performance characteristics under different network loads, latency requirements, and concurrent connection scenarios. The interaction between ARM's power management features and network processing workloads creates evaluation challenges that existing tools struggle to address comprehensively. Memory bandwidth limitations and cache coherency protocols in ARM architectures further complicate performance assessment in distributed settings.

Geographical distribution of ARM expertise remains concentrated in specific regions, with advanced research primarily conducted in North America, Europe, and select Asian markets. This concentration creates knowledge gaps in emerging markets where ARM adoption is accelerating. The lack of standardized evaluation frameworks across different regions hampers comparative analysis and best practice sharing.

Current evaluation methodologies suffer from fragmentation across different ARM implementations. Vendor-specific optimization techniques and proprietary performance monitoring tools create silos that prevent holistic efficiency assessment. The rapid evolution of ARM architectures, including the transition to newer instruction sets and core designs, outpaces the development of comprehensive evaluation frameworks.

Integration challenges with existing distributed network infrastructure represent another significant constraint. Legacy monitoring systems often lack ARM-specific instrumentation capabilities, forcing organizations to rely on generic performance metrics that may not accurately reflect ARM efficiency characteristics. The absence of real-time efficiency monitoring tools specifically designed for ARM-based distributed networks limits operational optimization opportunities.

The evaluation of ARM efficiency in distributed networks faces several fundamental challenges. Traditional performance metrics designed for x86 architectures often fail to capture the unique characteristics of ARM processors, particularly their heterogeneous core configurations and dynamic voltage scaling capabilities. Current benchmarking tools lack standardized methodologies for measuring ARM performance in distributed scenarios, leading to inconsistent evaluation results across different deployment environments.

Network-specific performance evaluation presents additional complexity. ARM processors exhibit varying performance characteristics under different network loads, latency requirements, and concurrent connection scenarios. The interaction between ARM's power management features and network processing workloads creates evaluation challenges that existing tools struggle to address comprehensively. Memory bandwidth limitations and cache coherency protocols in ARM architectures further complicate performance assessment in distributed settings.

Geographical distribution of ARM expertise remains concentrated in specific regions, with advanced research primarily conducted in North America, Europe, and select Asian markets. This concentration creates knowledge gaps in emerging markets where ARM adoption is accelerating. The lack of standardized evaluation frameworks across different regions hampers comparative analysis and best practice sharing.

Current evaluation methodologies suffer from fragmentation across different ARM implementations. Vendor-specific optimization techniques and proprietary performance monitoring tools create silos that prevent holistic efficiency assessment. The rapid evolution of ARM architectures, including the transition to newer instruction sets and core designs, outpaces the development of comprehensive evaluation frameworks.

Integration challenges with existing distributed network infrastructure represent another significant constraint. Legacy monitoring systems often lack ARM-specific instrumentation capabilities, forcing organizations to rely on generic performance metrics that may not accurately reflect ARM efficiency characteristics. The absence of real-time efficiency monitoring tools specifically designed for ARM-based distributed networks limits operational optimization opportunities.

Existing ARM Performance Evaluation Methodologies

01 ARM-based processor architecture optimization

Improvements in ARM processor architecture design to enhance computational efficiency through optimized instruction sets, pipeline structures, and execution units. These optimizations focus on reducing power consumption while maintaining or improving processing performance through architectural innovations.- ARM-based processor architecture optimization: Improvements in ARM processor architecture design to enhance computational efficiency through optimized instruction sets, pipeline structures, and execution units. These optimizations focus on reducing power consumption while maintaining or improving processing performance through architectural innovations.

- Power management and energy efficiency control: Technologies for managing power consumption in ARM-based systems through dynamic voltage and frequency scaling, power gating, and intelligent power distribution mechanisms. These methods enable efficient energy utilization by adjusting operational parameters based on workload requirements.

- ARM system thermal management solutions: Thermal control mechanisms designed to maintain optimal operating temperatures in ARM processors and systems. These solutions include heat dissipation structures, cooling systems, and thermal monitoring technologies that prevent overheating while maximizing performance efficiency.

- Multi-core ARM processing optimization: Techniques for improving efficiency in multi-core ARM architectures through load balancing, task scheduling, and inter-core communication optimization. These approaches maximize parallel processing capabilities while minimizing resource conflicts and power overhead.

- ARM-based embedded system efficiency enhancement: Methods for optimizing ARM processor performance in embedded applications through hardware-software co-design, memory hierarchy optimization, and peripheral interface improvements. These techniques focus on reducing latency and improving overall system responsiveness in resource-constrained environments.

02 Power management and energy efficiency techniques

Implementation of dynamic voltage and frequency scaling, power gating, and clock management strategies to reduce energy consumption in ARM-based systems. These techniques enable adaptive power control based on workload requirements, extending battery life and reducing thermal output.Expand Specific Solutions03 Memory access and cache optimization

Enhanced memory hierarchy designs and cache management strategies to improve data access efficiency in ARM systems. These optimizations reduce memory latency and bandwidth bottlenecks through improved cache coherency protocols and prefetching mechanisms.Expand Specific Solutions04 Parallel processing and multi-core coordination

Techniques for efficient task scheduling and workload distribution across multiple ARM cores to maximize throughput. These methods include load balancing algorithms, inter-core communication optimization, and heterogeneous computing strategies that leverage different core types.Expand Specific Solutions05 Hardware acceleration and specialized processing units

Integration of dedicated hardware accelerators and coprocessors with ARM cores to offload specific computational tasks. These specialized units handle operations such as signal processing, cryptography, or graphics rendering more efficiently than general-purpose cores.Expand Specific Solutions

Key Players in ARM and Distributed Computing Industry

The ARM efficiency evaluation in distributed networks represents an emerging technological domain currently in its early-to-mid development stage, with significant market potential driven by the proliferation of edge computing and IoT applications. The market is experiencing rapid growth as organizations seek energy-efficient computing solutions for distributed architectures. Technology maturity varies considerably across market participants, with established telecommunications giants like Huawei, Ericsson, and ZTE leading infrastructure development, while IBM and Siemens contribute enterprise-grade solutions. Chinese companies including Alibaba Group and State Grid Corp demonstrate strong capabilities in large-scale distributed systems implementation. Academic institutions such as Beijing University of Posts & Telecommunications and Xiamen University are advancing theoretical frameworks, while specialized firms like Newracom focus on wireless connectivity optimization. The competitive landscape shows a mix of mature networking solutions and evolving ARM-specific optimization technologies, indicating a transitional phase toward standardized efficiency evaluation methodologies.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed comprehensive ARM-based solutions for distributed networks, including their Kunpeng processors optimized for data center and edge computing scenarios. Their approach focuses on heterogeneous computing architectures that combine ARM cores with specialized accelerators for network processing. The company implements advanced power management techniques and dynamic frequency scaling to optimize energy efficiency across distributed deployments. Their HiSilicon ARM chips are designed with integrated network processing units that can handle packet processing, load balancing, and traffic management with reduced power consumption compared to traditional x86 architectures. Huawei's distributed network management system provides real-time monitoring of ARM processor utilization, thermal characteristics, and power consumption metrics across geographically dispersed network nodes.

Strengths: Strong integration of ARM processors with network-specific accelerators, comprehensive power management capabilities. Weaknesses: Limited ecosystem compatibility compared to x86 solutions, potential supply chain constraints.

International Business Machines Corp.

Technical Solution: IBM has developed sophisticated methodologies for evaluating ARM efficiency in distributed computing environments through their Power Systems and hybrid cloud architectures. Their approach leverages advanced telemetry and analytics platforms that continuously monitor ARM processor performance metrics including instructions per cycle, cache hit ratios, and thermal efficiency across distributed network nodes. IBM's Watson IoT platform integrates ARM-based edge devices with centralized analytics engines to provide comprehensive efficiency assessments. The company utilizes machine learning algorithms to predict optimal workload distribution across ARM clusters, considering factors such as network latency, power consumption, and computational load. Their evaluation framework includes standardized benchmarking tools specifically designed for ARM architectures in distributed scenarios, enabling comparative analysis of different ARM implementations and configurations.

Strengths: Advanced analytics and machine learning capabilities for performance optimization, comprehensive benchmarking frameworks. Weaknesses: Higher complexity in implementation, significant investment required for full deployment.

Core Innovations in ARM Efficiency Measurement Techniques

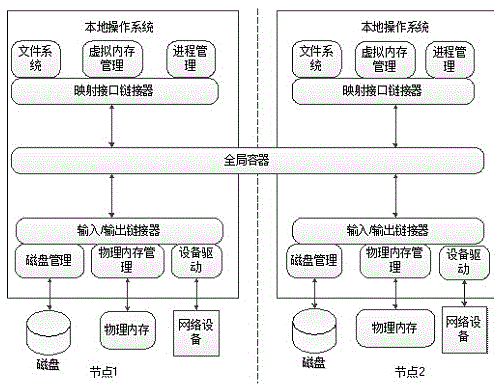

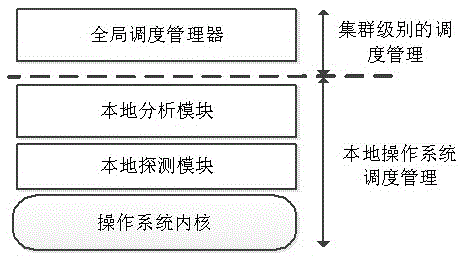

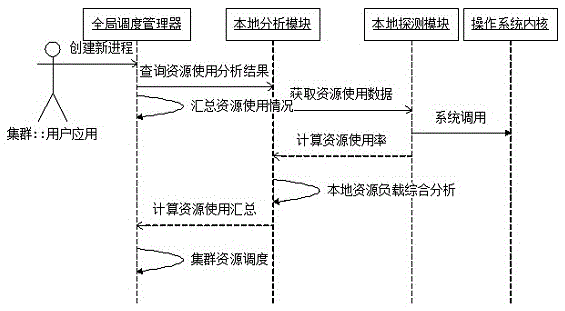

Unified managing and scheduling method of calculation resource in ARM architecture network cluster

PatentActiveCN106302628A

Innovation

- By introducing a global container layer and a configurable global scheduler into the ARM architecture network cluster, system events between the virtual layer and the physical layer are intercepted and redirected to achieve unified management and dynamic scheduling of computing resources and provide global resources. Transparent access and load balancing, supporting operating system optimization of SMP architecture.

Method and device for optimizing power control and modulation coding in wireless communication network

PatentActiveCN105337694A

Innovation

- Adopt an anonymous rating mechanism (ARM) to perform power control and modulation coding in a distributed manner, and use a more refined interference model to achieve adaptive scheduling and power adjustment between links based on the SINR model and limited, discrete MCS and power levels. , to maximize network throughput.

Energy Efficiency Standards for ARM Distributed Systems

Energy efficiency standards for ARM distributed systems have emerged as critical benchmarks for evaluating and optimizing power consumption across networked computing environments. These standards provide systematic frameworks for measuring, comparing, and improving the energy performance of ARM-based processors operating within distributed architectures.

The IEEE 1621 standard serves as a foundational framework for measuring computing equipment energy efficiency, establishing baseline methodologies that have been adapted for ARM distributed systems. This standard defines power measurement protocols, workload characterization techniques, and reporting formats that enable consistent evaluation across different ARM implementations. Additionally, the SPEC Power benchmark suite has evolved to include ARM-specific test scenarios, providing standardized workloads that reflect real-world distributed computing patterns.

Industry consortiums have developed specialized standards tailored to ARM distributed environments. The Green Grid's Power Usage Effectiveness (PUE) metrics have been extended to accommodate ARM cluster configurations, while the Energy Star program has introduced certification criteria specifically addressing low-power ARM server deployments. These standards emphasize holistic system efficiency, considering not only processor power consumption but also memory, storage, and network interface energy usage.

Emerging standards focus on dynamic efficiency measurement, recognizing that ARM distributed systems operate under varying workload conditions. The SPECpower_ssj2008 benchmark has been supplemented with ARM-optimized test suites that evaluate efficiency across different utilization levels, from idle states to peak performance scenarios. These dynamic standards account for ARM's inherent power scaling capabilities and heterogeneous computing architectures.

Regulatory frameworks are increasingly incorporating ARM-specific efficiency requirements. The European Union's Energy Efficiency Directive includes provisions for distributed computing systems, while various national standards bodies have established minimum efficiency thresholds for ARM-based data center equipment. These regulatory standards drive industry adoption of energy-efficient ARM solutions and promote standardized measurement methodologies.

Contemporary standards also address thermal efficiency and cooling requirements specific to ARM distributed systems. The ASHRAE TC 9.9 guidelines have been updated to reflect ARM processors' lower thermal design power characteristics, enabling more efficient cooling strategies and contributing to overall system energy optimization in distributed network deployments.

The IEEE 1621 standard serves as a foundational framework for measuring computing equipment energy efficiency, establishing baseline methodologies that have been adapted for ARM distributed systems. This standard defines power measurement protocols, workload characterization techniques, and reporting formats that enable consistent evaluation across different ARM implementations. Additionally, the SPEC Power benchmark suite has evolved to include ARM-specific test scenarios, providing standardized workloads that reflect real-world distributed computing patterns.

Industry consortiums have developed specialized standards tailored to ARM distributed environments. The Green Grid's Power Usage Effectiveness (PUE) metrics have been extended to accommodate ARM cluster configurations, while the Energy Star program has introduced certification criteria specifically addressing low-power ARM server deployments. These standards emphasize holistic system efficiency, considering not only processor power consumption but also memory, storage, and network interface energy usage.

Emerging standards focus on dynamic efficiency measurement, recognizing that ARM distributed systems operate under varying workload conditions. The SPECpower_ssj2008 benchmark has been supplemented with ARM-optimized test suites that evaluate efficiency across different utilization levels, from idle states to peak performance scenarios. These dynamic standards account for ARM's inherent power scaling capabilities and heterogeneous computing architectures.

Regulatory frameworks are increasingly incorporating ARM-specific efficiency requirements. The European Union's Energy Efficiency Directive includes provisions for distributed computing systems, while various national standards bodies have established minimum efficiency thresholds for ARM-based data center equipment. These regulatory standards drive industry adoption of energy-efficient ARM solutions and promote standardized measurement methodologies.

Contemporary standards also address thermal efficiency and cooling requirements specific to ARM distributed systems. The ASHRAE TC 9.9 guidelines have been updated to reflect ARM processors' lower thermal design power characteristics, enabling more efficient cooling strategies and contributing to overall system energy optimization in distributed network deployments.

Security Implications of ARM Performance Evaluation

The evaluation of ARM processor efficiency in distributed networks introduces several critical security considerations that must be carefully addressed to maintain system integrity and data protection. Performance monitoring activities inherently create potential attack vectors that malicious actors could exploit to compromise network security or extract sensitive information about system operations.

Performance data collection processes represent a primary security concern, as monitoring tools require elevated system privileges to access hardware performance counters, memory utilization metrics, and network traffic patterns. These privileged access requirements create opportunities for privilege escalation attacks if monitoring components are compromised. Additionally, the granular performance data collected during ARM efficiency evaluation can inadvertently expose sensitive information about application behavior, user activity patterns, and system vulnerabilities.

Side-channel attacks pose another significant threat during ARM performance evaluation activities. The detailed timing measurements and power consumption analysis required for efficiency assessment can potentially leak cryptographic keys or other confidential data through observable variations in processor behavior. Attackers monitoring performance evaluation outputs might correlate timing patterns with sensitive operations to extract protected information.

Network-based performance monitoring introduces additional security vulnerabilities through the transmission of performance metrics across distributed infrastructure. Unencrypted performance data streams can be intercepted and analyzed to map network topology, identify critical system components, and understand traffic patterns that could facilitate targeted attacks. The centralized collection of performance data also creates attractive targets for attackers seeking comprehensive system intelligence.

Authentication and authorization mechanisms for performance evaluation tools require robust implementation to prevent unauthorized access to monitoring capabilities. Weak access controls could allow attackers to manipulate performance metrics, inject false data, or use monitoring infrastructure for reconnaissance activities. The distributed nature of ARM-based networks amplifies these risks across multiple nodes and administrative domains.

Data integrity protection becomes crucial when performance evaluation results influence automated scaling decisions or resource allocation policies. Compromised performance metrics could trigger inappropriate system responses, leading to denial-of-service conditions or resource exhaustion attacks. Implementing cryptographic verification and anomaly detection mechanisms helps ensure the authenticity and reliability of performance evaluation data throughout the distributed network infrastructure.

Performance data collection processes represent a primary security concern, as monitoring tools require elevated system privileges to access hardware performance counters, memory utilization metrics, and network traffic patterns. These privileged access requirements create opportunities for privilege escalation attacks if monitoring components are compromised. Additionally, the granular performance data collected during ARM efficiency evaluation can inadvertently expose sensitive information about application behavior, user activity patterns, and system vulnerabilities.

Side-channel attacks pose another significant threat during ARM performance evaluation activities. The detailed timing measurements and power consumption analysis required for efficiency assessment can potentially leak cryptographic keys or other confidential data through observable variations in processor behavior. Attackers monitoring performance evaluation outputs might correlate timing patterns with sensitive operations to extract protected information.

Network-based performance monitoring introduces additional security vulnerabilities through the transmission of performance metrics across distributed infrastructure. Unencrypted performance data streams can be intercepted and analyzed to map network topology, identify critical system components, and understand traffic patterns that could facilitate targeted attacks. The centralized collection of performance data also creates attractive targets for attackers seeking comprehensive system intelligence.

Authentication and authorization mechanisms for performance evaluation tools require robust implementation to prevent unauthorized access to monitoring capabilities. Weak access controls could allow attackers to manipulate performance metrics, inject false data, or use monitoring infrastructure for reconnaissance activities. The distributed nature of ARM-based networks amplifies these risks across multiple nodes and administrative domains.

Data integrity protection becomes crucial when performance evaluation results influence automated scaling decisions or resource allocation policies. Compromised performance metrics could trigger inappropriate system responses, leading to denial-of-service conditions or resource exhaustion attacks. Implementing cryptographic verification and anomaly detection mechanisms helps ensure the authenticity and reliability of performance evaluation data throughout the distributed network infrastructure.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!