How Synchronous Rectifiers Minimize Conduction And Switching Loss Simultaneously?

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Synchronous Rectification Technology Background and Objectives

Synchronous rectification technology emerged in the late 1980s as a significant advancement in power electronics, evolving from traditional diode rectification methods. This technology replaces conventional diodes with actively controlled MOSFETs to convert AC to DC power with substantially higher efficiency. The fundamental principle leverages the significantly lower on-resistance of MOSFETs compared to the forward voltage drop of diodes, which directly translates to reduced conduction losses in power conversion systems.

The evolution of synchronous rectification has been closely tied to the increasing demands for power efficiency in electronic devices. Initially implemented in low-voltage, high-current applications such as computer power supplies, the technology has progressively expanded into broader power management domains including telecommunications, automotive systems, and renewable energy converters.

A critical milestone in this technological progression was the development of integrated driver circuits that could precisely control the timing of MOSFET switching operations. This advancement addressed the challenge of accurately synchronizing the MOSFET gate signals with the power conversion cycle, which is essential for minimizing both conduction and switching losses simultaneously.

The primary objective of modern synchronous rectification technology is to achieve optimal balance between conduction losses during the on-state and switching losses during transitions. This balance represents a fundamental engineering trade-off that varies according to operating frequency, load conditions, and thermal constraints of the application environment.

Current research and development efforts are focused on several key objectives: reducing the RDS(on) of synchronous rectifier MOSFETs to further minimize conduction losses; improving gate driver technologies to optimize switching timing and reduce associated losses; developing advanced control algorithms that can dynamically adjust rectification parameters based on operating conditions; and integrating synchronous rectification with wide bandgap semiconductor technologies such as GaN and SiC.

The technology aims to push power conversion efficiency beyond 98% in many applications, a threshold that has significant implications for energy conservation on a global scale. Additionally, synchronous rectification enables higher power density designs by reducing thermal management requirements, which directly supports the trend toward miniaturization in electronic devices.

Looking forward, the trajectory of synchronous rectification technology is expected to continue toward higher integration, with complete power management solutions incorporating advanced control features, protection mechanisms, and communication capabilities to support the evolving needs of smart power systems and the Internet of Things ecosystem.

The evolution of synchronous rectification has been closely tied to the increasing demands for power efficiency in electronic devices. Initially implemented in low-voltage, high-current applications such as computer power supplies, the technology has progressively expanded into broader power management domains including telecommunications, automotive systems, and renewable energy converters.

A critical milestone in this technological progression was the development of integrated driver circuits that could precisely control the timing of MOSFET switching operations. This advancement addressed the challenge of accurately synchronizing the MOSFET gate signals with the power conversion cycle, which is essential for minimizing both conduction and switching losses simultaneously.

The primary objective of modern synchronous rectification technology is to achieve optimal balance between conduction losses during the on-state and switching losses during transitions. This balance represents a fundamental engineering trade-off that varies according to operating frequency, load conditions, and thermal constraints of the application environment.

Current research and development efforts are focused on several key objectives: reducing the RDS(on) of synchronous rectifier MOSFETs to further minimize conduction losses; improving gate driver technologies to optimize switching timing and reduce associated losses; developing advanced control algorithms that can dynamically adjust rectification parameters based on operating conditions; and integrating synchronous rectification with wide bandgap semiconductor technologies such as GaN and SiC.

The technology aims to push power conversion efficiency beyond 98% in many applications, a threshold that has significant implications for energy conservation on a global scale. Additionally, synchronous rectification enables higher power density designs by reducing thermal management requirements, which directly supports the trend toward miniaturization in electronic devices.

Looking forward, the trajectory of synchronous rectification technology is expected to continue toward higher integration, with complete power management solutions incorporating advanced control features, protection mechanisms, and communication capabilities to support the evolving needs of smart power systems and the Internet of Things ecosystem.

Market Demand for High-Efficiency Power Conversion

The global market for high-efficiency power conversion solutions has experienced substantial growth over the past decade, driven primarily by increasing energy costs, environmental regulations, and the proliferation of electronic devices across all sectors. Power supply efficiency has evolved from a secondary consideration to a critical design parameter, with synchronous rectification technology emerging as a key enabler for meeting stringent efficiency requirements.

Consumer electronics represent the largest market segment demanding high-efficiency power conversion, with an estimated annual growth rate exceeding 7% through 2025. The explosive growth of mobile devices, each requiring multiple charging cycles per day, has created enormous aggregate energy consumption. Even small improvements in conversion efficiency translate to significant energy savings at scale, driving manufacturers to adopt advanced technologies like synchronous rectifiers.

Data centers and telecommunications infrastructure form another crucial market segment, where power conversion efficiency directly impacts operational expenses and cooling requirements. These facilities operate continuously, making even fractional improvements in efficiency economically significant. The total cost of ownership calculations increasingly favor investment in premium power conversion technologies that minimize losses.

Automotive applications, particularly in electric and hybrid vehicles, represent the fastest-growing segment for high-efficiency power conversion. The direct correlation between conversion efficiency and vehicle range has elevated power electronics to a critical competitive differentiator among manufacturers. Synchronous rectification is increasingly deployed in onboard chargers, DC-DC converters, and motor drive systems.

Regulatory frameworks worldwide continue to tighten efficiency standards for electronic equipment. The European Union's ErP Directive, California Energy Commission requirements, and similar regulations in Asia have established minimum efficiency thresholds that effectively mandate advanced power conversion technologies in many applications. These regulations are projected to become more stringent, further expanding market demand.

Industry surveys indicate that design engineers rank efficiency as the second most important parameter in power supply selection, surpassed only by reliability. This represents a significant shift from a decade ago when cost and size typically outranked efficiency considerations. The willingness to pay premium prices for high-efficiency solutions has increased across all market segments.

The economic value proposition for synchronous rectification continues to strengthen as semiconductor manufacturing advances reduce the cost premium while improving performance characteristics. The return on investment period for implementing synchronous rectification has shortened considerably, expanding the addressable market to include more cost-sensitive applications previously dominated by conventional diode rectification.

Consumer electronics represent the largest market segment demanding high-efficiency power conversion, with an estimated annual growth rate exceeding 7% through 2025. The explosive growth of mobile devices, each requiring multiple charging cycles per day, has created enormous aggregate energy consumption. Even small improvements in conversion efficiency translate to significant energy savings at scale, driving manufacturers to adopt advanced technologies like synchronous rectifiers.

Data centers and telecommunications infrastructure form another crucial market segment, where power conversion efficiency directly impacts operational expenses and cooling requirements. These facilities operate continuously, making even fractional improvements in efficiency economically significant. The total cost of ownership calculations increasingly favor investment in premium power conversion technologies that minimize losses.

Automotive applications, particularly in electric and hybrid vehicles, represent the fastest-growing segment for high-efficiency power conversion. The direct correlation between conversion efficiency and vehicle range has elevated power electronics to a critical competitive differentiator among manufacturers. Synchronous rectification is increasingly deployed in onboard chargers, DC-DC converters, and motor drive systems.

Regulatory frameworks worldwide continue to tighten efficiency standards for electronic equipment. The European Union's ErP Directive, California Energy Commission requirements, and similar regulations in Asia have established minimum efficiency thresholds that effectively mandate advanced power conversion technologies in many applications. These regulations are projected to become more stringent, further expanding market demand.

Industry surveys indicate that design engineers rank efficiency as the second most important parameter in power supply selection, surpassed only by reliability. This represents a significant shift from a decade ago when cost and size typically outranked efficiency considerations. The willingness to pay premium prices for high-efficiency solutions has increased across all market segments.

The economic value proposition for synchronous rectification continues to strengthen as semiconductor manufacturing advances reduce the cost premium while improving performance characteristics. The return on investment period for implementing synchronous rectification has shortened considerably, expanding the addressable market to include more cost-sensitive applications previously dominated by conventional diode rectification.

Current Challenges in Synchronous Rectifier Implementation

Despite the significant advancements in synchronous rectifier (SR) technology, several critical challenges persist in their implementation, particularly when attempting to simultaneously minimize both conduction and switching losses. The fundamental trade-off between these two loss mechanisms represents one of the most significant hurdles in SR design. When optimizing for reduced conduction losses by increasing MOSFET die size, designers inevitably face increased gate charge and capacitance, which directly elevates switching losses.

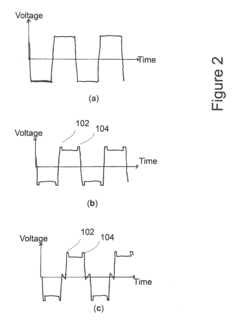

Timing control presents another substantial challenge in SR implementation. Precise gate signal timing is essential to prevent shoot-through current and body diode conduction, both of which can significantly degrade efficiency. This timing becomes increasingly critical at higher switching frequencies, where even nanosecond-level inaccuracies can lead to substantial performance degradation. The challenge intensifies in variable-frequency applications where adaptive timing control systems are required.

Thermal management remains a persistent issue in SR designs. As power density increases in modern power conversion systems, the heat generated by synchronous rectifiers becomes more concentrated and difficult to dissipate. This thermal constraint often limits the practical power handling capability of SR solutions, particularly in compact or thermally constrained environments such as mobile devices or automotive applications.

Driver circuit complexity represents another significant implementation challenge. The gate driver must provide adequate current to rapidly charge and discharge the gate capacitance while maintaining precise timing control. This requires sophisticated driver circuits that add complexity, cost, and potential points of failure to the overall system. Additionally, these drivers themselves consume power, which must be factored into overall efficiency calculations.

Parasitic elements in SR implementations, including package inductance, PCB layout constraints, and device capacitances, create significant design challenges. These parasitics can cause voltage spikes, ringing, and EMI issues that compromise both performance and reliability. As switching frequencies increase, these parasitic effects become increasingly pronounced and difficult to mitigate.

Cost considerations continue to pose challenges for widespread SR adoption in certain applications. While synchronous rectification offers clear efficiency benefits, the additional components, complexity, and design effort required can make it economically unfeasible for cost-sensitive applications. This economic barrier becomes particularly relevant in low-power or consumer-grade products where marginal efficiency improvements may not justify the added expense.

Reliability concerns also persist, particularly regarding the long-term robustness of SR solutions under various operating conditions. The additional active components and control circuitry introduce potential failure modes that must be carefully addressed through comprehensive design validation and testing.

Timing control presents another substantial challenge in SR implementation. Precise gate signal timing is essential to prevent shoot-through current and body diode conduction, both of which can significantly degrade efficiency. This timing becomes increasingly critical at higher switching frequencies, where even nanosecond-level inaccuracies can lead to substantial performance degradation. The challenge intensifies in variable-frequency applications where adaptive timing control systems are required.

Thermal management remains a persistent issue in SR designs. As power density increases in modern power conversion systems, the heat generated by synchronous rectifiers becomes more concentrated and difficult to dissipate. This thermal constraint often limits the practical power handling capability of SR solutions, particularly in compact or thermally constrained environments such as mobile devices or automotive applications.

Driver circuit complexity represents another significant implementation challenge. The gate driver must provide adequate current to rapidly charge and discharge the gate capacitance while maintaining precise timing control. This requires sophisticated driver circuits that add complexity, cost, and potential points of failure to the overall system. Additionally, these drivers themselves consume power, which must be factored into overall efficiency calculations.

Parasitic elements in SR implementations, including package inductance, PCB layout constraints, and device capacitances, create significant design challenges. These parasitics can cause voltage spikes, ringing, and EMI issues that compromise both performance and reliability. As switching frequencies increase, these parasitic effects become increasingly pronounced and difficult to mitigate.

Cost considerations continue to pose challenges for widespread SR adoption in certain applications. While synchronous rectification offers clear efficiency benefits, the additional components, complexity, and design effort required can make it economically unfeasible for cost-sensitive applications. This economic barrier becomes particularly relevant in low-power or consumer-grade products where marginal efficiency improvements may not justify the added expense.

Reliability concerns also persist, particularly regarding the long-term robustness of SR solutions under various operating conditions. The additional active components and control circuitry introduce potential failure modes that must be carefully addressed through comprehensive design validation and testing.

Contemporary SR Solutions for Loss Reduction

01 Synchronous rectifier control techniques for reducing conduction losses

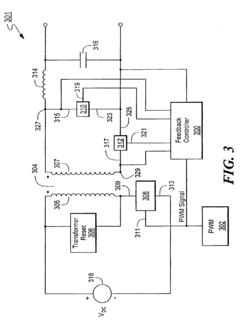

Various control techniques can be implemented to optimize the operation of synchronous rectifiers, specifically targeting the reduction of conduction losses. These techniques include precise timing control of gate signals, adaptive control based on load conditions, and optimized dead-time management. By ensuring that synchronous rectifiers conduct at optimal times and with proper gate drive, the resistance during conduction can be minimized, significantly reducing power losses in the system.- Synchronous rectifier control techniques: Various control techniques are employed to optimize the operation of synchronous rectifiers in power converters. These techniques include timing control for gate signals, adaptive control algorithms, and feedback mechanisms to minimize conduction and switching losses. Advanced control strategies can detect operating conditions and adjust the rectifier behavior accordingly, ensuring efficient power conversion across different load conditions.

- Gate drive optimization for synchronous rectifiers: Gate drive circuits play a crucial role in determining the switching and conduction losses of synchronous rectifiers. Optimized gate drive designs can reduce turn-on and turn-off times, minimize ringing, and ensure proper dead-time management. Advanced gate drivers incorporate features such as adaptive timing control, variable drive strength, and resonant techniques to reduce switching losses while maintaining efficient conduction.

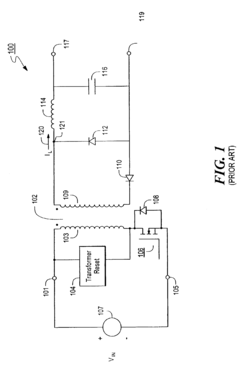

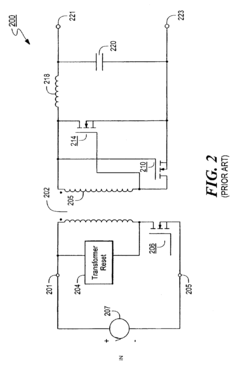

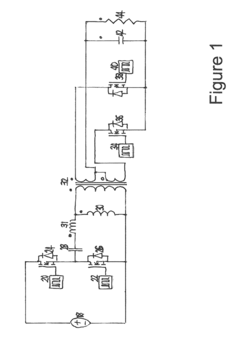

- Topology-specific synchronous rectification solutions: Different power converter topologies require specific synchronous rectification implementations to minimize losses. Various circuit arrangements for flyback, forward, bridge, and resonant converters incorporate synchronous rectifiers with topology-optimized timing and control. These specialized solutions address the unique switching patterns and operating conditions of each topology to achieve maximum efficiency and performance.

- Thermal management and loss reduction techniques: Thermal considerations significantly impact the performance of synchronous rectifiers. Various techniques are employed to manage heat dissipation and reduce overall losses, including optimized PCB layouts, improved packaging, and thermal feedback control. Advanced cooling methods and materials help maintain optimal operating temperatures, which directly affects both conduction and switching losses in synchronous rectifier applications.

- Integrated and advanced synchronous rectifier solutions: Integrated synchronous rectifier solutions combine multiple functions into single packages to optimize performance and reduce losses. These advanced implementations may include built-in drivers, protection features, and intelligent control algorithms. Integration allows for optimized layout, reduced parasitic elements, and better coordination between components, resulting in significant reductions in both conduction and switching losses compared to discrete implementations.

02 Switching loss reduction through gate drive optimization

Gate drive optimization plays a crucial role in reducing switching losses in synchronous rectifiers. This includes techniques such as variable gate drive strength, resonant gate drivers, and optimized gate voltage levels. By controlling the rate at which synchronous rectifiers turn on and off, and by ensuring proper gate voltage levels during transitions, the energy dissipated during switching events can be significantly reduced, improving overall power conversion efficiency.Expand Specific Solutions03 Zero voltage switching techniques for synchronous rectifiers

Zero voltage switching (ZVS) techniques enable synchronous rectifiers to switch when the voltage across them is near or at zero, dramatically reducing switching losses. These techniques include phase-shifted full-bridge topologies, resonant switching circuits, and timing control methods that ensure switching occurs at optimal points in the voltage waveform. By implementing ZVS, the energy normally dissipated during switching transitions is significantly reduced, improving efficiency especially at higher switching frequencies.Expand Specific Solutions04 Thermal management and efficiency optimization for synchronous rectifiers

Effective thermal management is essential for minimizing both conduction and switching losses in synchronous rectifiers. This includes advanced packaging techniques, thermal interface materials, and active cooling solutions. Additionally, efficiency optimization involves adaptive switching frequency control, dynamic dead-time adjustment, and load-dependent operation modes. These approaches help maintain optimal operating temperatures and conditions, reducing losses across varying load conditions and extending the lifetime of the components.Expand Specific Solutions05 Advanced synchronous rectifier topologies and integration techniques

Novel synchronous rectifier topologies and integration techniques offer significant improvements in reducing both conduction and switching losses. These include integrated driver-MOSFET packages, multi-level rectification schemes, and hybrid approaches combining different semiconductor technologies. By optimizing the physical layout, reducing parasitic elements, and integrating control and power components, these advanced designs minimize the resistance and capacitance that contribute to losses, while improving switching characteristics and thermal performance.Expand Specific Solutions

Leading Manufacturers and Competitive Landscape

The synchronous rectifier technology market is in a growth phase, characterized by increasing demand for high-efficiency power conversion solutions across multiple industries. The market size is expanding rapidly due to the proliferation of power-dense applications requiring minimal energy loss. Leading semiconductor manufacturers like Texas Instruments, ON Semiconductor (Semiconductor Components Industries), and STMicroelectronics are driving innovation in this space, with significant contributions also coming from specialized players such as Navitas Semiconductor and Leadtrend Technology. Academic institutions including Southeast University and Zhejiang University are advancing fundamental research. The technology has reached moderate maturity with commercial implementations widely available, but continuous improvements in switching speed, thermal management, and integration capabilities remain active areas of development as companies compete to achieve optimal efficiency in increasingly compact power conversion systems.

Texas Instruments Incorporated

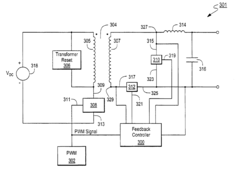

Technical Solution: Texas Instruments has developed advanced synchronous rectifier (SR) controllers that utilize adaptive gate drive technology to minimize both conduction and switching losses. Their UCC24610 SR controller employs precise timing control algorithms that detect the optimal turn-on and turn-off points by monitoring the voltage across the MOSFET, allowing for near-zero voltage switching. TI's implementation includes proprietary "smart drive" technology that adjusts gate drive strength based on load conditions, reducing switching losses during light loads while maintaining low conduction losses during heavy loads. Their SR solutions incorporate temperature compensation circuits that adjust timing parameters as operating temperatures change, maintaining optimal efficiency across varying conditions. TI has also integrated protection features such as shoot-through prevention and under-voltage lockout to enhance reliability while maintaining efficiency. Recent developments include SR controllers with programmable dead-time control that can be dynamically adjusted based on operating conditions to further minimize losses.

Strengths: TI's solutions offer exceptional timing precision with nanosecond-level accuracy, resulting in higher overall efficiency. Their adaptive gate drive technology provides excellent performance across varying load conditions. Weaknesses: Implementation complexity requires more sophisticated control circuitry, potentially increasing system cost. Some of their advanced features require additional external components for optimal performance.

Semiconductor Components Industries LLC

Technical Solution: Semiconductor Components Industries (ON Semiconductor) has developed a comprehensive synchronous rectification solution focused on minimizing both conduction and switching losses through their NCP43xx family of controllers. Their approach centers on ultra-fast detection circuits that precisely monitor the voltage across the SR MOSFET to determine optimal switching points. ON's technology implements adaptive turn-off delay that adjusts based on load conditions, ensuring efficient operation across varying power levels. Their SR controllers feature proprietary minimum on-time control that prevents excessive switching during light load conditions, reducing switching losses while maintaining adequate conduction performance. ON Semiconductor has also integrated temperature compensation features that adjust timing parameters as operating temperatures fluctuate, ensuring consistent efficiency across environmental conditions. Their latest generation controllers incorporate programmable gate drive strength that can be optimized for different MOSFET types and operating conditions, allowing system designers to balance conduction and switching losses based on specific application requirements.

Strengths: ON Semiconductor's solutions offer excellent light-load efficiency through their adaptive timing control, and their controllers provide robust protection features while maintaining high efficiency. Weaknesses: Some of their implementations require careful PCB layout to maintain timing accuracy, and their more advanced controllers may have higher quiescent current consumption compared to simpler solutions.

Key Patents and Innovations in SR Technology

Control circuit for synchronous rectifiers in DC/DC converters to reduce body diode conduction losses

PatentInactiveUS6870747B2

Innovation

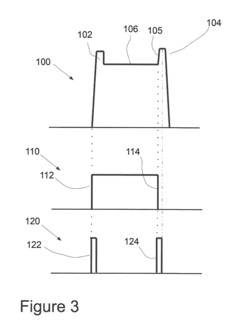

- A control system for switched mode power supplies that minimizes body diode conduction in synchronous rectifiers by adjusting the timing of control signals to prevent forward biasing during switching operations, using predictive algorithms to optimize turn-on and turn-off times based on previous switching cycle data and PWM signals.

Method of control for synchronous rectifiers

PatentActiveUS10014788B2

Innovation

- A method involving a primary side controller that uses an auxiliary winding to measure secondary side conditions, adjusting the timing of the synchronous rectifier's turn-off based on measurements from the auxiliary winding to minimize body diode conduction losses, thereby optimizing the switch-off timing.

Thermal Management Considerations in SR Design

Thermal management is a critical aspect of synchronous rectifier (SR) design that directly impacts both conduction and switching losses. As power density requirements increase in modern power conversion systems, effective thermal management becomes essential for maintaining optimal SR performance and reliability.

The primary thermal challenge in SR design stems from the heat generated during both conduction and switching phases. During conduction, the RDS(on) of MOSFETs increases with temperature, creating a positive feedback loop that can lead to thermal runaway if not properly managed. For every 1°C rise in junction temperature, RDS(on) typically increases by 0.3-0.5%, significantly affecting conduction losses at elevated temperatures.

Advanced packaging technologies play a crucial role in SR thermal management. DirectFET and PQFN packages with exposed pads provide superior thermal paths compared to traditional packages, reducing junction-to-case thermal resistance by up to 50%. These packages enable more efficient heat dissipation to PCB copper planes, which serve as primary heat sinks in many applications.

PCB layout considerations are equally important for effective thermal management. Optimized copper pour designs with multiple thermal vias can reduce thermal resistance by 30-40% compared to standard layouts. Strategic placement of synchronous rectifiers away from other heat-generating components prevents thermal coupling effects that could compromise efficiency.

Active cooling solutions become necessary in high-power density applications. Forced-air cooling can reduce operating temperatures by 15-25°C compared to natural convection, allowing SRs to operate closer to their optimal temperature range. In extreme cases, liquid cooling systems may be implemented, though they add complexity and cost to the overall design.

Thermal modeling and simulation tools have become essential in the design process. Computational fluid dynamics (CFD) simulations enable designers to identify potential hotspots and optimize thermal management strategies before physical prototyping. These tools can predict junction temperatures with accuracy within 5-10% of measured values, significantly reducing design iterations.

Temperature-dependent control algorithms represent an emerging approach to thermal management. By dynamically adjusting gate drive parameters based on real-time temperature measurements, these systems can optimize the trade-off between conduction and switching losses across varying thermal conditions, maintaining peak efficiency even as operating temperatures fluctuate.

The primary thermal challenge in SR design stems from the heat generated during both conduction and switching phases. During conduction, the RDS(on) of MOSFETs increases with temperature, creating a positive feedback loop that can lead to thermal runaway if not properly managed. For every 1°C rise in junction temperature, RDS(on) typically increases by 0.3-0.5%, significantly affecting conduction losses at elevated temperatures.

Advanced packaging technologies play a crucial role in SR thermal management. DirectFET and PQFN packages with exposed pads provide superior thermal paths compared to traditional packages, reducing junction-to-case thermal resistance by up to 50%. These packages enable more efficient heat dissipation to PCB copper planes, which serve as primary heat sinks in many applications.

PCB layout considerations are equally important for effective thermal management. Optimized copper pour designs with multiple thermal vias can reduce thermal resistance by 30-40% compared to standard layouts. Strategic placement of synchronous rectifiers away from other heat-generating components prevents thermal coupling effects that could compromise efficiency.

Active cooling solutions become necessary in high-power density applications. Forced-air cooling can reduce operating temperatures by 15-25°C compared to natural convection, allowing SRs to operate closer to their optimal temperature range. In extreme cases, liquid cooling systems may be implemented, though they add complexity and cost to the overall design.

Thermal modeling and simulation tools have become essential in the design process. Computational fluid dynamics (CFD) simulations enable designers to identify potential hotspots and optimize thermal management strategies before physical prototyping. These tools can predict junction temperatures with accuracy within 5-10% of measured values, significantly reducing design iterations.

Temperature-dependent control algorithms represent an emerging approach to thermal management. By dynamically adjusting gate drive parameters based on real-time temperature measurements, these systems can optimize the trade-off between conduction and switching losses across varying thermal conditions, maintaining peak efficiency even as operating temperatures fluctuate.

Cost-Performance Analysis of SR Implementation

The implementation of Synchronous Rectifiers (SRs) presents a complex cost-performance equation that must be carefully evaluated by power electronics designers. Initial investment in SR technology typically exceeds that of traditional diode rectification by 15-30%, primarily due to the additional semiconductor components, gate drivers, and control circuitry required. However, this cost premium must be weighed against significant performance advantages and long-term operational savings.

From an efficiency standpoint, SR implementation delivers compelling returns. Empirical data shows that replacing Schottky diodes with MOSFETs in synchronous rectification can reduce conduction losses by 50-70% in typical 12V output applications. This efficiency improvement translates directly to reduced thermal management requirements, with SR solutions typically requiring 30-40% less heatsinking area compared to conventional approaches.

The economic analysis becomes particularly favorable in high-current applications. For instance, in server power supplies operating at 100A output, the energy savings from SR implementation can offset the initial cost premium within 8-14 months of continuous operation, depending on electricity costs and duty cycles. This return-on-investment timeline continues to improve as semiconductor manufacturing advances drive down MOSFET costs.

System reliability considerations further enhance the value proposition of SR technology. The reduced thermal stress extends component lifespans, with field data suggesting a 20-30% improvement in mean time between failures (MTBF) for power conversion stages utilizing synchronous rectification. This reliability enhancement translates to reduced maintenance costs and system downtime in critical applications.

Manufacturing complexity represents a countervailing factor in the cost-performance equation. SR implementation requires more sophisticated assembly processes and testing procedures, increasing production costs by approximately 5-10% compared to conventional rectification approaches. Additionally, the control algorithms necessary for optimal SR timing add development costs that must be amortized across production volumes.

Market analysis indicates that the cost-performance balance increasingly favors SR implementation as power density requirements intensify. In applications where space constraints are critical, the superior efficiency of SR solutions enables smaller form factors that command premium pricing, effectively offsetting the higher component costs through enhanced product positioning and competitive differentiation.

From an efficiency standpoint, SR implementation delivers compelling returns. Empirical data shows that replacing Schottky diodes with MOSFETs in synchronous rectification can reduce conduction losses by 50-70% in typical 12V output applications. This efficiency improvement translates directly to reduced thermal management requirements, with SR solutions typically requiring 30-40% less heatsinking area compared to conventional approaches.

The economic analysis becomes particularly favorable in high-current applications. For instance, in server power supplies operating at 100A output, the energy savings from SR implementation can offset the initial cost premium within 8-14 months of continuous operation, depending on electricity costs and duty cycles. This return-on-investment timeline continues to improve as semiconductor manufacturing advances drive down MOSFET costs.

System reliability considerations further enhance the value proposition of SR technology. The reduced thermal stress extends component lifespans, with field data suggesting a 20-30% improvement in mean time between failures (MTBF) for power conversion stages utilizing synchronous rectification. This reliability enhancement translates to reduced maintenance costs and system downtime in critical applications.

Manufacturing complexity represents a countervailing factor in the cost-performance equation. SR implementation requires more sophisticated assembly processes and testing procedures, increasing production costs by approximately 5-10% compared to conventional rectification approaches. Additionally, the control algorithms necessary for optimal SR timing add development costs that must be amortized across production volumes.

Market analysis indicates that the cost-performance balance increasingly favors SR implementation as power density requirements intensify. In applications where space constraints are critical, the superior efficiency of SR solutions enables smaller form factors that command premium pricing, effectively offsetting the higher component costs through enhanced product positioning and competitive differentiation.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!