Cryogenic Memory And Buffering For QEC Control Pipelines

SEP 2, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Cryogenic Memory Evolution and QEC Goals

Cryogenic memory technology has evolved significantly over the past decades, transitioning from conventional room-temperature memory systems to specialized architectures capable of operating at extremely low temperatures. The initial development of cryogenic memory in the 1980s focused primarily on superconducting devices, which demonstrated improved performance characteristics but faced significant manufacturing challenges. By the early 2000s, research shifted toward hybrid approaches that combined semiconductor and superconducting technologies, enabling more practical implementations while maintaining quantum coherence advantages.

The evolution accelerated in the 2010s with the emergence of quantum computing as a viable technology. This period saw the development of specialized memory cells designed specifically for sub-Kelvin environments, including Josephson junction-based memory and cryogenic CMOS technologies. These advancements addressed the fundamental challenge of maintaining data integrity while operating within the strict thermal constraints required by quantum systems.

Recent developments have focused on integrating memory directly into quantum error correction (QEC) control pipelines. This integration represents a critical advancement, as it minimizes latency between error detection and correction operations—a key requirement for maintaining quantum coherence. The proximity of memory elements to quantum processing units reduces signal degradation and thermal noise introduction, which are particularly detrimental to quantum operations.

The primary goal of cryogenic memory in QEC contexts is to enable real-time error syndrome processing with minimal latency. Quantum error correction requires rapid feedback loops that detect and correct errors before they propagate through the quantum system. Traditional approaches involving room-temperature memory introduce unacceptable delays in this process, making local cryogenic buffering essential for practical quantum error correction.

Another critical objective is achieving sufficient memory density while maintaining ultra-low power consumption. Cryogenic systems have extremely limited cooling capacity, typically measured in microwatts at millikelvin temperatures. This constraint necessitates memory architectures that minimize heat generation while providing adequate storage capacity for complex error correction codes.

Looking forward, the field aims to develop fully integrated cryogenic control systems where memory, processing, and quantum elements coexist within a unified thermal environment. This integration would eliminate interface bottlenecks between different temperature stages, potentially enabling more complex QEC protocols that were previously impractical due to latency constraints.

The ultimate technical goal remains the achievement of fault-tolerant quantum computing through efficient error correction, which requires cryogenic memory systems capable of supporting millions of physical qubits with microsecond-scale feedback loops. This represents a scaling challenge several orders of magnitude beyond current capabilities, driving continued innovation in materials science, circuit design, and system architecture.

The evolution accelerated in the 2010s with the emergence of quantum computing as a viable technology. This period saw the development of specialized memory cells designed specifically for sub-Kelvin environments, including Josephson junction-based memory and cryogenic CMOS technologies. These advancements addressed the fundamental challenge of maintaining data integrity while operating within the strict thermal constraints required by quantum systems.

Recent developments have focused on integrating memory directly into quantum error correction (QEC) control pipelines. This integration represents a critical advancement, as it minimizes latency between error detection and correction operations—a key requirement for maintaining quantum coherence. The proximity of memory elements to quantum processing units reduces signal degradation and thermal noise introduction, which are particularly detrimental to quantum operations.

The primary goal of cryogenic memory in QEC contexts is to enable real-time error syndrome processing with minimal latency. Quantum error correction requires rapid feedback loops that detect and correct errors before they propagate through the quantum system. Traditional approaches involving room-temperature memory introduce unacceptable delays in this process, making local cryogenic buffering essential for practical quantum error correction.

Another critical objective is achieving sufficient memory density while maintaining ultra-low power consumption. Cryogenic systems have extremely limited cooling capacity, typically measured in microwatts at millikelvin temperatures. This constraint necessitates memory architectures that minimize heat generation while providing adequate storage capacity for complex error correction codes.

Looking forward, the field aims to develop fully integrated cryogenic control systems where memory, processing, and quantum elements coexist within a unified thermal environment. This integration would eliminate interface bottlenecks between different temperature stages, potentially enabling more complex QEC protocols that were previously impractical due to latency constraints.

The ultimate technical goal remains the achievement of fault-tolerant quantum computing through efficient error correction, which requires cryogenic memory systems capable of supporting millions of physical qubits with microsecond-scale feedback loops. This represents a scaling challenge several orders of magnitude beyond current capabilities, driving continued innovation in materials science, circuit design, and system architecture.

Market Analysis for Quantum Error Correction Systems

The quantum error correction (QEC) systems market is experiencing significant growth as quantum computing transitions from research laboratories to commercial applications. Current market estimates value the global quantum computing market at approximately $500 million, with QEC systems representing a crucial enabling technology segment expected to grow at a compound annual rate of 25-30% through 2030.

Demand for QEC systems is primarily driven by research institutions, national laboratories, and large technology corporations investing in quantum computing infrastructure. Organizations like IBM, Google, Microsoft, and Rigetti are making substantial investments in error correction technologies to achieve quantum advantage in practical applications. Government funding worldwide has also increased dramatically, with the US National Quantum Initiative allocating $1.2 billion and the EU Quantum Flagship program committing €1 billion to quantum technologies including error correction systems.

The market for cryogenic memory and buffering solutions specifically for QEC control pipelines remains nascent but strategically vital. These components address a critical bottleneck in scaling quantum systems by enabling efficient error syndrome extraction and correction at cryogenic temperatures. Industry analysts project this specialized segment could reach $150 million by 2025 as quantum processors scale beyond 100 qubits where error correction becomes essential.

Customer requirements in this market emphasize ultra-low power consumption, nanosecond-scale latency, radiation hardness, and seamless integration with existing quantum control systems. The price sensitivity varies significantly by customer segment, with research institutions being more cost-conscious while commercial entities prioritize performance and reliability over initial acquisition costs.

Regional market distribution shows North America leading with approximately 45% market share, followed by Europe (30%) and Asia-Pacific (20%). China's national quantum initiatives are rapidly accelerating their market position through strategic investments in error correction technologies.

The market exhibits high barriers to entry due to specialized expertise requirements and significant capital investments needed for development. However, venture capital funding for quantum computing startups focusing on error correction has reached record levels, with over $300 million invested in specialized QEC technology companies during 2022 alone.

Long-term market forecasts suggest that as quantum computers approach fault-tolerance thresholds, demand for sophisticated cryogenic memory and buffering solutions will increase exponentially, potentially creating a billion-dollar market segment by 2035 as quantum computing applications expand into pharmaceutical development, materials science, and financial modeling.

Demand for QEC systems is primarily driven by research institutions, national laboratories, and large technology corporations investing in quantum computing infrastructure. Organizations like IBM, Google, Microsoft, and Rigetti are making substantial investments in error correction technologies to achieve quantum advantage in practical applications. Government funding worldwide has also increased dramatically, with the US National Quantum Initiative allocating $1.2 billion and the EU Quantum Flagship program committing €1 billion to quantum technologies including error correction systems.

The market for cryogenic memory and buffering solutions specifically for QEC control pipelines remains nascent but strategically vital. These components address a critical bottleneck in scaling quantum systems by enabling efficient error syndrome extraction and correction at cryogenic temperatures. Industry analysts project this specialized segment could reach $150 million by 2025 as quantum processors scale beyond 100 qubits where error correction becomes essential.

Customer requirements in this market emphasize ultra-low power consumption, nanosecond-scale latency, radiation hardness, and seamless integration with existing quantum control systems. The price sensitivity varies significantly by customer segment, with research institutions being more cost-conscious while commercial entities prioritize performance and reliability over initial acquisition costs.

Regional market distribution shows North America leading with approximately 45% market share, followed by Europe (30%) and Asia-Pacific (20%). China's national quantum initiatives are rapidly accelerating their market position through strategic investments in error correction technologies.

The market exhibits high barriers to entry due to specialized expertise requirements and significant capital investments needed for development. However, venture capital funding for quantum computing startups focusing on error correction has reached record levels, with over $300 million invested in specialized QEC technology companies during 2022 alone.

Long-term market forecasts suggest that as quantum computers approach fault-tolerance thresholds, demand for sophisticated cryogenic memory and buffering solutions will increase exponentially, potentially creating a billion-dollar market segment by 2035 as quantum computing applications expand into pharmaceutical development, materials science, and financial modeling.

Cryogenic Memory Challenges and Technical Limitations

Cryogenic memory systems for quantum error correction (QEC) control pipelines face significant technical challenges that limit their practical implementation. The primary obstacle is maintaining stable memory operations at extremely low temperatures, typically below 4 Kelvin. At these temperatures, conventional semiconductor physics behaves differently, causing increased leakage currents, altered threshold voltages, and unpredictable switching characteristics in transistors. These effects fundamentally change how memory cells retain and access information.

Power dissipation presents another critical limitation. Even minimal heat generation in cryogenic environments can disrupt the delicate quantum states necessary for QEC operations. Current cryogenic memory technologies exhibit power densities that remain orders of magnitude too high for practical integration with quantum processors, creating thermal management challenges that have not been adequately solved.

Material compatibility issues further complicate development efforts. Many standard materials used in conventional memory fabrication exhibit different electrical, mechanical, and thermal properties at cryogenic temperatures. Some materials become brittle or lose conductivity, while others develop microfractures due to thermal contraction during cooling cycles. This necessitates the development of specialized material systems specifically engineered for cryogenic operation.

Integration density represents another significant technical barrier. The physical footprint of cryogenic memory must be minimized to fit within the severely constrained space available in dilution refrigerators. However, as components are miniaturized, quantum effects and thermal management become increasingly problematic, creating a complex engineering trade-off between density, reliability, and performance.

Speed-reliability trade-offs pose additional challenges. While QEC operations require high-speed memory access to process error syndromes within coherence times, increasing operational speeds typically generates more heat and reduces reliability at cryogenic temperatures. Current technologies struggle to achieve the necessary balance between speed and stability required for effective error correction protocols.

Signal integrity degradation occurs as electrical signals must traverse temperature gradients between cryogenic and room-temperature environments. This transition introduces noise, attenuation, and timing variations that can corrupt data integrity. Specialized interconnect technologies and signal conditioning approaches are required but remain underdeveloped.

Finally, testing and validation methodologies for cryogenic memory systems are severely limited. Conventional memory testing equipment cannot operate at quantum-relevant temperatures, and specialized cryogenic test platforms lack the comprehensive capabilities needed to fully characterize memory performance under realistic operating conditions. This creates significant barriers to iterative development and quality assurance processes essential for commercial deployment.

Power dissipation presents another critical limitation. Even minimal heat generation in cryogenic environments can disrupt the delicate quantum states necessary for QEC operations. Current cryogenic memory technologies exhibit power densities that remain orders of magnitude too high for practical integration with quantum processors, creating thermal management challenges that have not been adequately solved.

Material compatibility issues further complicate development efforts. Many standard materials used in conventional memory fabrication exhibit different electrical, mechanical, and thermal properties at cryogenic temperatures. Some materials become brittle or lose conductivity, while others develop microfractures due to thermal contraction during cooling cycles. This necessitates the development of specialized material systems specifically engineered for cryogenic operation.

Integration density represents another significant technical barrier. The physical footprint of cryogenic memory must be minimized to fit within the severely constrained space available in dilution refrigerators. However, as components are miniaturized, quantum effects and thermal management become increasingly problematic, creating a complex engineering trade-off between density, reliability, and performance.

Speed-reliability trade-offs pose additional challenges. While QEC operations require high-speed memory access to process error syndromes within coherence times, increasing operational speeds typically generates more heat and reduces reliability at cryogenic temperatures. Current technologies struggle to achieve the necessary balance between speed and stability required for effective error correction protocols.

Signal integrity degradation occurs as electrical signals must traverse temperature gradients between cryogenic and room-temperature environments. This transition introduces noise, attenuation, and timing variations that can corrupt data integrity. Specialized interconnect technologies and signal conditioning approaches are required but remain underdeveloped.

Finally, testing and validation methodologies for cryogenic memory systems are severely limited. Conventional memory testing equipment cannot operate at quantum-relevant temperatures, and specialized cryogenic test platforms lack the comprehensive capabilities needed to fully characterize memory performance under realistic operating conditions. This creates significant barriers to iterative development and quality assurance processes essential for commercial deployment.

Current Cryogenic Memory Architectures for QEC

01 Cryogenic memory architecture and design

Cryogenic memory systems are designed to operate at extremely low temperatures, offering advantages in quantum computing applications. These memory architectures incorporate specialized materials and circuit designs that maintain functionality in superconducting environments. The designs often include thermal isolation techniques, specialized interconnects, and modified memory cells that can operate efficiently at temperatures near absolute zero while providing necessary buffering capabilities for quantum operations.- Cryogenic memory architecture and design: Cryogenic memory systems are designed to operate at extremely low temperatures, offering advantages in quantum computing applications. These architectures include specialized memory cells that maintain data integrity in superconducting environments. The designs incorporate thermal isolation techniques and materials optimized for low-temperature operation, enabling efficient data storage and retrieval while minimizing heat generation that could disrupt the cryogenic environment.

- Buffer management in cryogenic computing systems: Buffer management techniques specific to cryogenic computing environments focus on optimizing data transfer between room-temperature and cryogenic components. These systems employ specialized buffering mechanisms that minimize thermal load while maintaining high data throughput. The buffer designs include temperature gradient-aware architectures that efficiently handle the transition of signals across thermal boundaries, reducing energy consumption and improving overall system performance.

- Memory access optimization for cryogenic systems: Memory access optimization techniques for cryogenic systems address the unique challenges of data retrieval at extremely low temperatures. These methods include specialized caching algorithms that reduce access frequency to minimize heat generation, and prioritization schemes that optimize the placement of frequently accessed data. The techniques also incorporate timing adjustments to account for the altered electrical characteristics of components operating in cryogenic environments.

- Integration of cryogenic memory with quantum computing: Integration approaches for cryogenic memory with quantum computing systems focus on creating cohesive architectures that support quantum operations. These designs include specialized interfaces between classical cryogenic memory and quantum processing units, allowing for efficient state preparation and measurement results storage. The integration methods address challenges such as maintaining quantum coherence while performing memory operations, and managing the different operational requirements of quantum and classical components within the same cryogenic environment.

- Error correction and reliability in cryogenic memory: Error correction techniques for cryogenic memory systems address the unique failure modes that occur at extremely low temperatures. These methods include specialized error detection and correction codes optimized for cryogenic operation, redundancy schemes that account for temperature-dependent error patterns, and adaptive correction mechanisms that respond to changing error rates as components age. The techniques ensure data integrity despite the challenging operating environment, extending the reliable operational lifetime of cryogenic memory systems.

02 Memory buffering techniques for cryogenic systems

Specialized buffering techniques are implemented in cryogenic memory systems to manage data flow between room-temperature processing units and cryogenically-cooled components. These buffering mechanisms help mitigate thermal challenges while maintaining data integrity across temperature gradients. Advanced buffer designs incorporate superconducting elements, specialized timing circuits, and thermal management features to optimize performance while minimizing heat generation in the cryogenic environment.Expand Specific Solutions03 Integration of cryogenic memory with quantum computing systems

Cryogenic memory systems are specifically designed to interface with quantum computing architectures, providing necessary buffering and storage capabilities. These integrated systems address the unique challenges of quantum data handling, including qubit state preservation, error correction, and the management of classical control signals. The memory subsystems are engineered to minimize decoherence effects while providing rapid access to quantum information during computation processes.Expand Specific Solutions04 Thermal management for cryogenic memory systems

Effective thermal management is critical for cryogenic memory systems to maintain stable operating temperatures while minimizing energy consumption. These systems employ specialized cooling techniques, thermal isolation barriers, and heat dissipation strategies to protect the memory components. Advanced designs incorporate multi-stage cooling systems, radiation shields, and thermally-optimized circuit layouts to ensure reliable operation while maintaining the extreme low temperatures required for cryogenic performance.Expand Specific Solutions05 Performance optimization of cryogenic memory buffers

Optimization techniques for cryogenic memory buffers focus on enhancing speed, reliability, and energy efficiency under extreme temperature conditions. These approaches include specialized circuit designs, novel materials selection, and advanced signal processing methods tailored for cryogenic environments. Memory buffer architectures incorporate superconducting elements, modified addressing schemes, and specialized timing circuits to achieve optimal performance while accommodating the unique constraints of ultra-low temperature operation.Expand Specific Solutions

Leading Organizations in Quantum Control Hardware

The cryogenic memory and buffering for QEC control pipelines market is in an early growth stage, characterized by increasing research investments but limited commercial deployment. The market size is expanding as quantum computing advances, with projections suggesting significant growth as quantum error correction becomes essential for practical quantum computers. Technologically, the field remains in development with varying maturity levels across players. Companies like Google, Intel, and IBM lead in quantum computing infrastructure, while specialized firms such as SeeQC and Rigetti focus on cryogenic control systems. Academic institutions including MIT and Shanghai Tech University contribute fundamental research. Semiconductor manufacturers like Micron, Renesas, and STMicroelectronics bring expertise in memory technologies that could be adapted for cryogenic environments, creating a diverse competitive landscape poised for innovation breakthroughs.

SeeQC, Inc.

Technical Solution: SeeQC has developed a proprietary Digital Quantum Management (DQM) system that integrates classical cryogenic control electronics with quantum processing units. Their approach uses Single Flux Quantum (SFQ) digital logic operating at 4K temperatures to create a multi-chip module architecture where control electronics are physically closer to the quantum processor (operating at 20mK). This proximity significantly reduces latency and increases QEC cycle speeds. SeeQC's cryogenic memory solution incorporates Josephson junction-based memory cells that can operate at quantum-relevant temperatures, enabling fast buffering of error correction data without the thermal and latency penalties of room-temperature memory systems. Their integrated approach allows for scalable error correction by processing quantum measurement data locally within the cryogenic environment.

Strengths: Significantly reduced latency for QEC operations; lower power consumption compared to room-temperature control systems; scalable architecture for larger qubit arrays. Weaknesses: Limited memory density compared to conventional DRAM; requires specialized fabrication processes; integration challenges with different quantum computing platforms.

Rigetti & Co., Inc.

Technical Solution: Rigetti has developed a comprehensive cryogenic control system for quantum error correction that integrates specialized cryogenic memory buffers with their superconducting qubit architecture. Their approach features a multi-layer control stack with cryogenic CMOS circuits operating at 4K that interface between the quantum processor (at millikelvin temperatures) and room-temperature electronics. Rigetti's system implements a hierarchical memory architecture where high-speed, low-capacity cryogenic SRAM buffers store immediate QEC syndrome measurements, while larger cryogenic memory banks handle intermediate data storage. This architecture supports their surface code implementation by enabling rapid syndrome extraction and decoding. The company has demonstrated reduced QEC cycle times by minimizing the latency between measurement and feedback operations through their integrated cryogenic memory system, achieving correction cycles up to 10x faster than conventional room-temperature control approaches.

Strengths: Tightly integrated with their superconducting qubit platform; demonstrated performance improvements in QEC cycle times; scalable architecture designed for future larger-scale processors. Weaknesses: Higher power consumption at cryogenic stages compared to purely superconducting logic approaches; limited memory capacity constrains complex error correction algorithms; requires significant cryogenic cooling resources.

Key Patents in Low-Temperature Quantum Memory

Technologies for resource-efficient quantum error correction

PatentActiveUS20220156630A1

Innovation

- A resource-efficient quantum error correction system utilizing a combination of physical gate qubits and quantum memory, where logical qubits are transferred between physical gate qubits and quantum memory based on error rates, allowing for efficient error correction using codes like surface, GKP, or bosonic mode codes, with error correction performed based on error parameters exceeding a threshold.

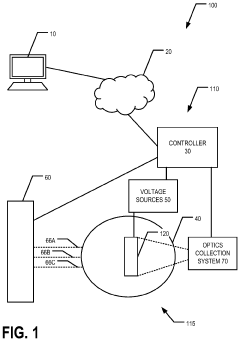

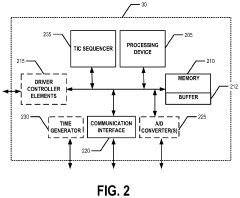

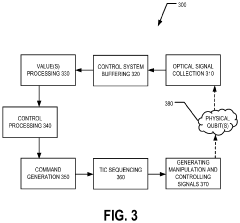

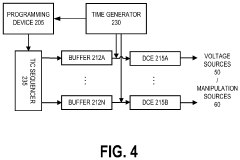

Quantum system controller configured for quantum error correction

PatentActiveUS11934920B2

Innovation

- A quantum system controller configured with a classical or semiconductor-based processing device generates commands to execute quantum error corrections in real-time or near real-time, using time-indexed execution and software-based corrections to modify quantum gates and qubits, ensuring accurate quantum error correction within the coherence time.

Thermal Management Strategies for Quantum Control Systems

Thermal management represents a critical challenge in quantum computing systems, particularly for cryogenic memory and buffering components within Quantum Error Correction (QEC) control pipelines. These systems operate at extremely low temperatures, typically below 100 millikelvin for superconducting qubits, creating unique thermal engineering challenges that conventional cooling approaches cannot address.

The primary thermal management strategies for quantum control systems can be categorized into passive and active cooling methodologies. Passive strategies include thermal isolation techniques such as vacuum-insulated enclosures, radiation shields, and specialized low thermal conductivity materials that minimize heat transfer between temperature stages. These approaches are essential for maintaining the temperature gradient between room temperature control electronics and the quantum processing units.

Active cooling strategies involve sophisticated refrigeration systems, including dilution refrigerators, pulse tube cryocoolers, and adiabatic demagnetization refrigerators. These systems must provide sufficient cooling power to offset the heat generated by control electronics while maintaining stable operating temperatures. Recent innovations in cryogenic recirculating chillers have shown promise for more efficient heat extraction from intermediate temperature stages.

Heat dissipation from cryogenic memory elements presents particular challenges. Traditional CMOS memory generates significant heat during operation, making it unsuitable for direct integration with quantum processors. Emerging solutions include superconducting memory cells based on Single Flux Quantum (SFQ) logic, which operate with minimal power dissipation at cryogenic temperatures. These memory elements can be integrated into the control pipeline while contributing negligible thermal load.

Thermal budgeting has emerged as a critical design methodology for quantum control systems. This approach allocates specific heat dissipation limits to each component based on the available cooling capacity at different temperature stages. For QEC control pipelines, this often means distributing memory and buffering functions across temperature stages, with only the most critical, low-latency components placed at the coldest stages.

Advanced thermal modeling techniques, including finite element analysis and computational fluid dynamics, are increasingly employed to optimize the design of thermal interfaces between components. These models help predict hotspots and thermal gradients that could compromise system performance, allowing engineers to implement targeted cooling solutions before physical prototyping.

The primary thermal management strategies for quantum control systems can be categorized into passive and active cooling methodologies. Passive strategies include thermal isolation techniques such as vacuum-insulated enclosures, radiation shields, and specialized low thermal conductivity materials that minimize heat transfer between temperature stages. These approaches are essential for maintaining the temperature gradient between room temperature control electronics and the quantum processing units.

Active cooling strategies involve sophisticated refrigeration systems, including dilution refrigerators, pulse tube cryocoolers, and adiabatic demagnetization refrigerators. These systems must provide sufficient cooling power to offset the heat generated by control electronics while maintaining stable operating temperatures. Recent innovations in cryogenic recirculating chillers have shown promise for more efficient heat extraction from intermediate temperature stages.

Heat dissipation from cryogenic memory elements presents particular challenges. Traditional CMOS memory generates significant heat during operation, making it unsuitable for direct integration with quantum processors. Emerging solutions include superconducting memory cells based on Single Flux Quantum (SFQ) logic, which operate with minimal power dissipation at cryogenic temperatures. These memory elements can be integrated into the control pipeline while contributing negligible thermal load.

Thermal budgeting has emerged as a critical design methodology for quantum control systems. This approach allocates specific heat dissipation limits to each component based on the available cooling capacity at different temperature stages. For QEC control pipelines, this often means distributing memory and buffering functions across temperature stages, with only the most critical, low-latency components placed at the coldest stages.

Advanced thermal modeling techniques, including finite element analysis and computational fluid dynamics, are increasingly employed to optimize the design of thermal interfaces between components. These models help predict hotspots and thermal gradients that could compromise system performance, allowing engineers to implement targeted cooling solutions before physical prototyping.

Integration Standards for Quantum-Classical Interfaces

The integration of cryogenic memory and buffering systems into quantum error correction (QEC) control pipelines necessitates robust standardization frameworks that bridge quantum and classical computing domains. Current integration standards primarily focus on three critical interface layers: physical connectivity, signal translation protocols, and data exchange formats. At the physical level, standards such as CryoCIMOS (Cryogenic Complementary Metal-Oxide-Semiconductor) and superconducting interconnects define specifications for reliable signal transmission between sub-Kelvin quantum processors and cryogenic memory elements operating at 4K temperatures. These standards address thermal budget constraints, electromagnetic interference shielding, and mechanical stability requirements unique to quantum computing environments.

Signal translation protocols constitute the second standardization layer, with emerging frameworks like Quantum-Classical Interface Protocol (QCIP) and Cryogenic Control Bus (CCB) gaining industry adoption. These protocols define how classical digital signals are converted to analog control pulses for quantum operations and vice versa, with particular emphasis on minimizing latency—a critical factor for real-time error correction. The QCIP standard specifically addresses the timing synchronization between cryogenic memory access operations and quantum gate executions, ensuring deterministic behavior across the quantum-classical boundary.

Data exchange formats represent the third standardization dimension, with the Quantum Intermediate Representation (QIR) and Cryogenic Buffer Exchange Format (CBEF) emerging as leading candidates. These formats define structured representations for quantum error syndrome measurements, correction instructions, and calibration parameters. The CBEF standard specifically addresses the memory layout optimization for cryogenic SRAM and MRAM technologies, enabling efficient buffering of error correction data with minimal power consumption.

Cross-vendor compatibility remains a significant challenge in the standardization landscape. The Quantum-Classical Computing Consortium (QC3) has proposed a certification framework for interface components, though adoption remains fragmented across hardware providers. IBM's OpenQASM and Google's Cirq frameworks have extended their specifications to include cryogenic memory interaction primitives, but these extensions lack full interoperability. The IEEE P1913 working group has recently initiated efforts to develop unified standards specifically addressing cryogenic memory interfaces for quantum systems.

Looking forward, integration standards are evolving toward more comprehensive frameworks that address not only technical specifications but also performance benchmarking methodologies. The Cryogenic Quantum Interface Benchmark Suite (CQIBS) provides standardized tests for measuring key performance indicators such as memory access latency, buffering throughput, and error rates across the quantum-classical boundary. These benchmarks are increasingly important as quantum error correction implementations scale beyond proof-of-concept demonstrations toward fault-tolerant quantum computing systems.

Signal translation protocols constitute the second standardization layer, with emerging frameworks like Quantum-Classical Interface Protocol (QCIP) and Cryogenic Control Bus (CCB) gaining industry adoption. These protocols define how classical digital signals are converted to analog control pulses for quantum operations and vice versa, with particular emphasis on minimizing latency—a critical factor for real-time error correction. The QCIP standard specifically addresses the timing synchronization between cryogenic memory access operations and quantum gate executions, ensuring deterministic behavior across the quantum-classical boundary.

Data exchange formats represent the third standardization dimension, with the Quantum Intermediate Representation (QIR) and Cryogenic Buffer Exchange Format (CBEF) emerging as leading candidates. These formats define structured representations for quantum error syndrome measurements, correction instructions, and calibration parameters. The CBEF standard specifically addresses the memory layout optimization for cryogenic SRAM and MRAM technologies, enabling efficient buffering of error correction data with minimal power consumption.

Cross-vendor compatibility remains a significant challenge in the standardization landscape. The Quantum-Classical Computing Consortium (QC3) has proposed a certification framework for interface components, though adoption remains fragmented across hardware providers. IBM's OpenQASM and Google's Cirq frameworks have extended their specifications to include cryogenic memory interaction primitives, but these extensions lack full interoperability. The IEEE P1913 working group has recently initiated efforts to develop unified standards specifically addressing cryogenic memory interfaces for quantum systems.

Looking forward, integration standards are evolving toward more comprehensive frameworks that address not only technical specifications but also performance benchmarking methodologies. The Cryogenic Quantum Interface Benchmark Suite (CQIBS) provides standardized tests for measuring key performance indicators such as memory access latency, buffering throughput, and error rates across the quantum-classical boundary. These benchmarks are increasingly important as quantum error correction implementations scale beyond proof-of-concept demonstrations toward fault-tolerant quantum computing systems.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!