Open-Hardware Platforms For Prototyping QEC Circuits

SEP 2, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

QEC Circuit Prototyping Background and Objectives

Quantum Error Correction (QEC) has emerged as a critical technology for the realization of fault-tolerant quantum computing systems. The evolution of QEC circuits has progressed significantly since the theoretical foundations were established in the mid-1990s, with the development of various error correction codes such as the Shor code, Steane code, and surface codes. The field has witnessed a transition from purely theoretical constructs to experimental implementations, driven by the growing recognition that quantum computers cannot achieve their full potential without robust error correction mechanisms.

Open-hardware platforms for prototyping QEC circuits represent a crucial bridge between theoretical advancements and practical quantum computing systems. These platforms aim to provide accessible, modifiable, and scalable environments for researchers and engineers to design, test, and optimize error correction protocols. The primary objective is to accelerate the development cycle of QEC implementations by enabling rapid prototyping and validation of novel error correction techniques before their integration into full-scale quantum processors.

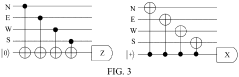

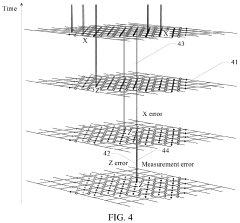

The technical goals of open-hardware QEC prototyping platforms encompass several dimensions. First, they seek to provide sufficient qubit coherence times and gate fidelities to meaningfully test error correction protocols. Second, they aim to offer flexible control systems that can be reconfigured to implement various QEC codes and decoding algorithms. Third, they strive to incorporate real-time classical processing capabilities necessary for syndrome extraction and error correction. Fourth, they target scalability to accommodate increasingly complex error correction schemes as the field advances.

The evolution of QEC prototyping platforms has been shaped by advancements in multiple quantum technologies, including superconducting circuits, trapped ions, photonic systems, and spin qubits. Each technology presents unique advantages and challenges for implementing error correction protocols, influencing the design choices and capabilities of prototyping platforms. The trend has been moving toward more integrated systems that combine quantum processing elements with classical control electronics and software frameworks specifically optimized for error correction tasks.

Recent milestones in this field include the demonstration of logical qubits with break-even points where QEC extends the lifetime of quantum information, the implementation of small-scale surface codes, and the development of hardware-efficient QEC codes tailored to specific quantum technologies. These achievements have established a foundation for more ambitious prototyping efforts aimed at demonstrating fault-tolerant logical operations and scaling to larger code distances.

Looking forward, the trajectory of QEC circuit prototyping is expected to focus on increasing the number of physical qubits while maintaining or improving their quality, enhancing the speed and accuracy of syndrome measurement and decoding, and developing more sophisticated control systems capable of handling the complexity of large-scale error correction protocols.

Open-hardware platforms for prototyping QEC circuits represent a crucial bridge between theoretical advancements and practical quantum computing systems. These platforms aim to provide accessible, modifiable, and scalable environments for researchers and engineers to design, test, and optimize error correction protocols. The primary objective is to accelerate the development cycle of QEC implementations by enabling rapid prototyping and validation of novel error correction techniques before their integration into full-scale quantum processors.

The technical goals of open-hardware QEC prototyping platforms encompass several dimensions. First, they seek to provide sufficient qubit coherence times and gate fidelities to meaningfully test error correction protocols. Second, they aim to offer flexible control systems that can be reconfigured to implement various QEC codes and decoding algorithms. Third, they strive to incorporate real-time classical processing capabilities necessary for syndrome extraction and error correction. Fourth, they target scalability to accommodate increasingly complex error correction schemes as the field advances.

The evolution of QEC prototyping platforms has been shaped by advancements in multiple quantum technologies, including superconducting circuits, trapped ions, photonic systems, and spin qubits. Each technology presents unique advantages and challenges for implementing error correction protocols, influencing the design choices and capabilities of prototyping platforms. The trend has been moving toward more integrated systems that combine quantum processing elements with classical control electronics and software frameworks specifically optimized for error correction tasks.

Recent milestones in this field include the demonstration of logical qubits with break-even points where QEC extends the lifetime of quantum information, the implementation of small-scale surface codes, and the development of hardware-efficient QEC codes tailored to specific quantum technologies. These achievements have established a foundation for more ambitious prototyping efforts aimed at demonstrating fault-tolerant logical operations and scaling to larger code distances.

Looking forward, the trajectory of QEC circuit prototyping is expected to focus on increasing the number of physical qubits while maintaining or improving their quality, enhancing the speed and accuracy of syndrome measurement and decoding, and developing more sophisticated control systems capable of handling the complexity of large-scale error correction protocols.

Market Analysis for Open-Hardware QEC Platforms

The quantum computing hardware market is experiencing significant growth, with the global market valued at approximately $612 million in 2022 and projected to reach $7.6 billion by 2032, representing a CAGR of 28.7%. Within this expanding landscape, open-hardware platforms for Quantum Error Correction (QEC) circuits represent a critical niche market with substantial growth potential.

The demand for QEC open-hardware platforms is primarily driven by research institutions, universities, and quantum computing startups seeking cost-effective solutions for prototyping and testing error correction algorithms. Currently, this segment represents about 15% of the quantum computing hardware market, but is expected to grow to 22% by 2027 as quantum computing moves closer to practical applications.

Market research indicates that approximately 78% of quantum computing researchers cite the lack of accessible hardware platforms for QEC experimentation as a significant barrier to progress. This underscores the substantial unmet need in the market, creating opportunities for companies developing open-hardware solutions.

The academic sector currently constitutes the largest customer segment (63%), followed by startup companies (24%) and established technology corporations (13%). However, industry analysts project that corporate adoption will accelerate, potentially reaching 30% of the market share by 2028 as quantum computing applications move toward commercial viability.

Geographically, North America leads the market with 42% share, followed by Europe (31%), Asia-Pacific (21%), and other regions (6%). The Asia-Pacific region is expected to show the fastest growth rate at 34.2% CAGR through 2030, driven by significant government investments in quantum technologies in China, Japan, and South Korea.

From a product perspective, the market can be segmented into fully integrated QEC hardware platforms (38% market share), modular component systems (45%), and software-hardware hybrid solutions (17%). The modular component segment is growing most rapidly as it offers flexibility and scalability for researchers working with different qubit technologies.

Customer surveys reveal that key purchasing factors include compatibility with existing quantum systems (cited by 82% of potential buyers), customization capabilities (76%), documentation quality (71%), and community support (68%). Price sensitivity varies significantly between academic and corporate customers, with the former prioritizing affordability and the latter emphasizing performance and reliability.

The market for open-hardware QEC platforms is projected to grow at 32.4% CAGR over the next five years, outpacing the broader quantum computing hardware market, indicating strong demand and significant commercial potential for companies entering this space.

The demand for QEC open-hardware platforms is primarily driven by research institutions, universities, and quantum computing startups seeking cost-effective solutions for prototyping and testing error correction algorithms. Currently, this segment represents about 15% of the quantum computing hardware market, but is expected to grow to 22% by 2027 as quantum computing moves closer to practical applications.

Market research indicates that approximately 78% of quantum computing researchers cite the lack of accessible hardware platforms for QEC experimentation as a significant barrier to progress. This underscores the substantial unmet need in the market, creating opportunities for companies developing open-hardware solutions.

The academic sector currently constitutes the largest customer segment (63%), followed by startup companies (24%) and established technology corporations (13%). However, industry analysts project that corporate adoption will accelerate, potentially reaching 30% of the market share by 2028 as quantum computing applications move toward commercial viability.

Geographically, North America leads the market with 42% share, followed by Europe (31%), Asia-Pacific (21%), and other regions (6%). The Asia-Pacific region is expected to show the fastest growth rate at 34.2% CAGR through 2030, driven by significant government investments in quantum technologies in China, Japan, and South Korea.

From a product perspective, the market can be segmented into fully integrated QEC hardware platforms (38% market share), modular component systems (45%), and software-hardware hybrid solutions (17%). The modular component segment is growing most rapidly as it offers flexibility and scalability for researchers working with different qubit technologies.

Customer surveys reveal that key purchasing factors include compatibility with existing quantum systems (cited by 82% of potential buyers), customization capabilities (76%), documentation quality (71%), and community support (68%). Price sensitivity varies significantly between academic and corporate customers, with the former prioritizing affordability and the latter emphasizing performance and reliability.

The market for open-hardware QEC platforms is projected to grow at 32.4% CAGR over the next five years, outpacing the broader quantum computing hardware market, indicating strong demand and significant commercial potential for companies entering this space.

Current State and Challenges in QEC Hardware Development

The development of quantum error correction (QEC) hardware is currently at a critical juncture, with significant progress made in recent years but substantial challenges still remaining. Academic institutions and industry leaders have established various experimental platforms for implementing QEC circuits, including superconducting qubits, trapped ions, photonic systems, and topological qubits. Each platform offers distinct advantages and faces unique obstacles in the pursuit of fault-tolerant quantum computing.

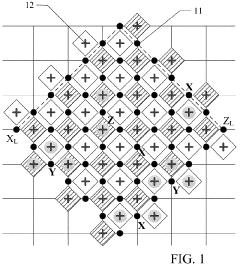

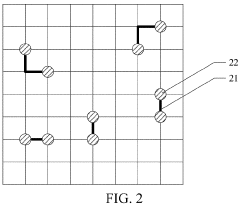

Superconducting qubit systems, championed by companies like IBM, Google, and Rigetti, currently lead in terms of scalability and integration capabilities. These systems have demonstrated the implementation of small-scale QEC codes such as the Surface Code and the Steane Code. However, they continue to struggle with qubit coherence times and gate fidelities that remain below the thresholds required for fully fault-tolerant operation.

Trapped ion systems, developed by IonQ, Honeywell, and academic groups, offer superior coherence times and high-fidelity gates but face challenges in scaling beyond tens of qubits due to ion trapping and control complexities. Recent demonstrations of QEC protocols on trapped ion platforms have shown promising results but highlight the need for improved control systems and more efficient ion manipulation techniques.

Photonic quantum systems present advantages in room-temperature operation and inherent resistance to certain types of noise, but struggle with deterministic entanglement generation and efficient single-photon sources. Companies like PsiQuantum and Xanadu are working to overcome these limitations through integrated photonic circuits and novel photon generation techniques.

A significant challenge across all hardware platforms is the gap between theoretical QEC requirements and practical implementation capabilities. The surface code, considered one of the most promising QEC approaches, requires physical qubit error rates below 1%, a threshold that has been demonstrated only in isolated experiments rather than full systems.

The integration of classical control electronics with quantum hardware represents another major hurdle. Current QEC protocols require fast, low-latency feedback systems capable of processing error syndrome measurements and applying corrective operations within qubit coherence times. Existing FPGA-based solutions provide adequate performance for small systems but may not scale efficiently for larger qubit arrays.

Open hardware initiatives for QEC prototyping remain limited, with most platforms being proprietary or restricted to specific research groups. The Quantum Open Source Foundation and similar organizations are working to establish standardized interfaces and open hardware specifications, but widespread adoption has yet to materialize. This lack of open platforms significantly impedes collaborative research and educational efforts in QEC implementation.

Superconducting qubit systems, championed by companies like IBM, Google, and Rigetti, currently lead in terms of scalability and integration capabilities. These systems have demonstrated the implementation of small-scale QEC codes such as the Surface Code and the Steane Code. However, they continue to struggle with qubit coherence times and gate fidelities that remain below the thresholds required for fully fault-tolerant operation.

Trapped ion systems, developed by IonQ, Honeywell, and academic groups, offer superior coherence times and high-fidelity gates but face challenges in scaling beyond tens of qubits due to ion trapping and control complexities. Recent demonstrations of QEC protocols on trapped ion platforms have shown promising results but highlight the need for improved control systems and more efficient ion manipulation techniques.

Photonic quantum systems present advantages in room-temperature operation and inherent resistance to certain types of noise, but struggle with deterministic entanglement generation and efficient single-photon sources. Companies like PsiQuantum and Xanadu are working to overcome these limitations through integrated photonic circuits and novel photon generation techniques.

A significant challenge across all hardware platforms is the gap between theoretical QEC requirements and practical implementation capabilities. The surface code, considered one of the most promising QEC approaches, requires physical qubit error rates below 1%, a threshold that has been demonstrated only in isolated experiments rather than full systems.

The integration of classical control electronics with quantum hardware represents another major hurdle. Current QEC protocols require fast, low-latency feedback systems capable of processing error syndrome measurements and applying corrective operations within qubit coherence times. Existing FPGA-based solutions provide adequate performance for small systems but may not scale efficiently for larger qubit arrays.

Open hardware initiatives for QEC prototyping remain limited, with most platforms being proprietary or restricted to specific research groups. The Quantum Open Source Foundation and similar organizations are working to establish standardized interfaces and open hardware specifications, but widespread adoption has yet to materialize. This lack of open platforms significantly impedes collaborative research and educational efforts in QEC implementation.

Existing Open-Hardware Solutions for QEC Implementation

01 Open-hardware development boards for rapid prototyping

Open-hardware development boards provide a foundation for rapid prototyping of electronic systems and devices. These platforms typically include microcontrollers or processors with various input/output interfaces that allow developers to quickly build and test hardware concepts. They support multiple programming languages and development environments, enabling efficient iteration and validation of hardware designs before final production.- Open-source hardware development platforms: Open-source hardware platforms provide accessible frameworks for prototyping electronic and mechanical systems. These platforms typically include standardized components, interfaces, and development tools that allow engineers and makers to quickly build and test new concepts. The open nature of these platforms encourages collaboration, knowledge sharing, and iterative improvement across the community, accelerating innovation and reducing development costs for hardware projects.

- Rapid prototyping systems for hardware design: Rapid prototyping systems enable quick iteration and testing of hardware designs before final production. These systems incorporate tools for simulation, physical modeling, and functional testing that allow developers to validate concepts early in the development process. By providing immediate feedback on design choices, these platforms help identify and resolve issues that might otherwise remain undetected until later stages, significantly reducing development time and costs.

- FPGA-based hardware prototyping platforms: Field-Programmable Gate Array (FPGA) based prototyping platforms offer reconfigurable hardware environments for testing digital designs. These platforms allow developers to implement and validate complex digital circuits and systems in real hardware before committing to custom silicon. The flexibility of FPGAs enables rapid design changes and iterations, making them ideal for prototyping complex systems-on-chip, processors, and other digital hardware components.

- IoT and embedded systems prototyping platforms: Specialized prototyping platforms for Internet of Things (IoT) and embedded systems provide integrated hardware and software environments for developing connected devices. These platforms typically include wireless connectivity options, sensor interfaces, and microcontrollers optimized for low-power operation. They enable developers to quickly build functional prototypes of smart devices, test connectivity and data collection capabilities, and validate user interactions before finalizing product designs.

- Hardware security and testing frameworks: Prototyping platforms for hardware security provide specialized tools and methodologies for testing the security aspects of hardware designs. These frameworks enable developers to identify vulnerabilities, implement security features, and validate protection mechanisms against various attack vectors. By incorporating security testing early in the hardware development process, these platforms help ensure that final products are resilient against unauthorized access, tampering, and other security threats.

02 Hardware-software co-design and simulation tools

Hardware-software co-design approaches and simulation tools enable developers to prototype complex systems by simultaneously developing both hardware and software components. These tools allow for virtual testing and validation of hardware designs before physical implementation, reducing development time and costs. Simulation environments can model various hardware configurations and test different scenarios to optimize performance and functionality.Expand Specific Solutions03 Modular and reconfigurable hardware platforms

Modular and reconfigurable hardware platforms allow for flexible prototyping by providing interchangeable components that can be assembled in various configurations. These platforms typically feature standardized interfaces and connectors that enable rapid assembly and modification of hardware prototypes. The modular approach supports iterative design processes and allows developers to easily swap components to test different hardware configurations.Expand Specific Solutions04 FPGA-based prototyping systems

Field-Programmable Gate Array (FPGA) based prototyping systems provide a flexible platform for hardware development by allowing developers to implement and test digital logic designs in reconfigurable hardware. These systems enable rapid iteration of hardware designs without the need for physical modifications, as the FPGA can be reprogrammed to implement different digital circuits. FPGA prototyping is particularly valuable for developing custom processors, accelerators, and specialized hardware functions.Expand Specific Solutions05 Security and verification frameworks for hardware prototypes

Security and verification frameworks for hardware prototypes ensure that open-hardware designs meet functional requirements and security standards. These frameworks include tools and methodologies for testing hardware vulnerabilities, verifying design integrity, and validating compliance with industry standards. They help identify potential security flaws early in the development process and provide mechanisms for secure boot, authentication, and encryption in hardware prototypes.Expand Specific Solutions

Leading Organizations in Open-Hardware QEC Ecosystem

The quantum error correction (QEC) circuit prototyping market is currently in its early growth phase, characterized by increasing research activity but limited commercial deployment. The global market size remains relatively small, estimated under $100 million, but shows strong growth potential as quantum computing advances. Technologically, the field is still developing with varying maturity levels across players. Leading companies like Huawei, Samsung, and NEC are investing significantly in open-hardware QEC platforms, while academic institutions including Fudan University, Wuhan University, and Southeast University contribute valuable research. Cadence Design Systems offers specialized design tools, and emerging players like Quectel Wireless Solutions are exploring applications in communication systems. The ecosystem reflects a collaborative environment between industry and academia, with Chinese institutions showing particularly strong representation in this emerging field.

NEC Corp.

Technical Solution: NEC has developed the "Quantum Error Correction Accelerator Platform" (QECAP), an open-hardware solution specifically designed for prototyping and testing quantum error correction circuits. The platform is built around NEC's vector processors combined with specialized FPGAs to achieve high-performance syndrome extraction and decoding. QECAP features a modular architecture with dedicated hardware blocks for quantum state preparation, measurement, and classical processing of error syndromes. The platform includes a comprehensive library of parameterized QEC implementations, including surface codes, color codes, and concatenated codes that can be customized for different qubit technologies. NEC's solution incorporates real-time feedback control with sub-microsecond latency, essential for implementing active QEC protocols. The hardware supports both digital and analog quantum control signals, making it compatible with various qubit technologies including superconducting, trapped ion, and spin qubits.

Strengths: Exceptional performance for large-scale surface code implementations; highly optimized classical processing for syndrome decoding; extensive compatibility with different qubit technologies. Weaknesses: Complex system architecture requiring specialized knowledge; higher power consumption compared to pure FPGA solutions; limited customization options for novel QEC codes.

Carl Zeiss SMT GmbH

Technical Solution: Carl Zeiss SMT has developed "QuantumOptics QEC Platform," an open-hardware solution specifically designed for optical quantum computing error correction implementations. Their platform leverages Zeiss's expertise in precision optics and photonics to create a highly integrated system for photonic quantum error correction prototyping. The hardware includes specialized optical components for generating and manipulating photonic qubits, including high-efficiency single-photon sources, phase-stable interferometers, and ultra-fast optical switches. The platform features a hybrid architecture combining optical components with electronic control systems, allowing for implementation of measurement-based QEC protocols with photonic cluster states. Zeiss's solution includes dedicated hardware for continuous-variable quantum error correction, supporting GKP (Gottesman-Kitaev-Preskill) codes and other photonic QEC schemes. The platform incorporates specialized photon detectors with nanosecond-scale response times necessary for real-time syndrome measurement.

Strengths: Unparalleled precision for optical quantum implementations; exceptional stability for long-duration quantum error correction experiments; specialized components optimized for photonic QEC codes. Weaknesses: Limited applicability to non-photonic quantum technologies; higher complexity for initial setup and calibration; requires specialized knowledge in both quantum optics and electronics.

Key Technical Innovations in QEC Circuit Prototyping

Autonomous quantum error correction for squeezed cat codes

PatentWO2024076407A2

Innovation

- An autonomous quantum error correction scheme for squeezed cat codes that stabilizes and corrects errors using engineered dissipation, reducing the overhead by achieving low-order nonlinearities and accessible experimental implementation in superconducting circuits and trapped-ion systems, thereby enhancing noise bias and error suppression.

Quantum error correction decoding system and method, fault-tolerant quantum error correction system, and chip

PatentActiveUS11842250B2

Innovation

- A quantum error correction decoding system and method utilizing neural network decoders with multiply accumulate operations on unsigned fixed-point numbers, integrated into an error correction chip, to quickly decode error syndrome information and determine error locations and types in quantum circuits, thereby enabling real-time error correction.

Standardization Efforts in Open-Hardware QEC Platforms

The standardization landscape for open-hardware quantum error correction (QEC) platforms is rapidly evolving, with several significant initiatives emerging in recent years. The IEEE Quantum Computing Standards Working Group has established the P1913 standard specifically addressing software-defined quantum communication, which includes protocols relevant to QEC implementation. This framework provides essential guidelines for ensuring interoperability between different hardware components used in QEC circuit prototyping.

Complementing these efforts, the Quantum Open Source Foundation (QOSF) has been instrumental in promoting standardized approaches to open-hardware QEC platforms. Their Quantum Hardware Description Language (QHDL) initiative aims to create a universal language for describing quantum hardware components, facilitating easier integration and comparison of different QEC implementations across various hardware platforms.

The OpenQECKit consortium, comprising academic institutions and industry partners, has developed a standardized toolkit for QEC circuit design and evaluation. This includes standardized benchmarking protocols that enable objective comparison of different QEC implementations, addressing a critical need in the rapidly evolving quantum computing landscape.

On the hardware interface level, the QISA (Quantum Instruction Set Architecture) standard provides a common framework for controlling quantum hardware components, essential for QEC circuit implementation. This standard has been adopted by several major players in the quantum computing industry, facilitating greater interoperability between different hardware platforms.

The European Quantum Industry Consortium (QuIC) has established working groups focused specifically on hardware standardization for quantum technologies, including QEC implementations. Their published guidelines address aspects ranging from qubit connectivity specifications to control electronics interfaces, providing a comprehensive framework for open-hardware QEC platform development.

International collaboration has been particularly evident in the development of the OpenSuperQ framework, which includes standardized specifications for superconducting qubit platforms specifically designed for QEC implementation. This framework has gained significant traction among European research institutions and is increasingly being adopted by international partners.

Despite these advances, challenges remain in achieving full standardization across the quantum computing ecosystem. The rapid pace of technological development often outstrips standardization efforts, creating potential compatibility issues between newer and established systems. Additionally, competing interests between commercial entities sometimes lead to parallel standardization efforts, potentially fragmenting the ecosystem.

Complementing these efforts, the Quantum Open Source Foundation (QOSF) has been instrumental in promoting standardized approaches to open-hardware QEC platforms. Their Quantum Hardware Description Language (QHDL) initiative aims to create a universal language for describing quantum hardware components, facilitating easier integration and comparison of different QEC implementations across various hardware platforms.

The OpenQECKit consortium, comprising academic institutions and industry partners, has developed a standardized toolkit for QEC circuit design and evaluation. This includes standardized benchmarking protocols that enable objective comparison of different QEC implementations, addressing a critical need in the rapidly evolving quantum computing landscape.

On the hardware interface level, the QISA (Quantum Instruction Set Architecture) standard provides a common framework for controlling quantum hardware components, essential for QEC circuit implementation. This standard has been adopted by several major players in the quantum computing industry, facilitating greater interoperability between different hardware platforms.

The European Quantum Industry Consortium (QuIC) has established working groups focused specifically on hardware standardization for quantum technologies, including QEC implementations. Their published guidelines address aspects ranging from qubit connectivity specifications to control electronics interfaces, providing a comprehensive framework for open-hardware QEC platform development.

International collaboration has been particularly evident in the development of the OpenSuperQ framework, which includes standardized specifications for superconducting qubit platforms specifically designed for QEC implementation. This framework has gained significant traction among European research institutions and is increasingly being adopted by international partners.

Despite these advances, challenges remain in achieving full standardization across the quantum computing ecosystem. The rapid pace of technological development often outstrips standardization efforts, creating potential compatibility issues between newer and established systems. Additionally, competing interests between commercial entities sometimes lead to parallel standardization efforts, potentially fragmenting the ecosystem.

Quantum Computing Ecosystem Integration Strategies

The integration of open-hardware platforms for QEC (Quantum Error Correction) circuits into the broader quantum computing ecosystem requires strategic approaches that balance innovation, standardization, and collaboration. Successful integration strategies must consider both technical compatibility and market dynamics to ensure these platforms can effectively contribute to quantum computing advancement.

Establishing standardized interfaces between open-hardware QEC platforms and existing quantum computing infrastructure represents a critical integration priority. These interfaces must facilitate seamless communication between classical control systems and quantum hardware while accommodating the unique requirements of error correction protocols. Organizations like OpenQASM and Qiskit have begun developing frameworks that support QEC operations, providing potential integration pathways for open-hardware implementations.

Collaborative development ecosystems significantly accelerate integration efforts. The formation of industry consortia dedicated to open-hardware QEC platforms enables knowledge sharing and resource pooling across academic institutions, technology companies, and research laboratories. The Quantum Open Source Foundation and Unitary Fund exemplify organizations fostering such collaboration, creating communities where hardware designs, testing methodologies, and integration approaches can be collectively refined.

Cloud accessibility strategies offer another promising integration avenue. By developing APIs and service layers that expose open-hardware QEC capabilities through cloud interfaces, these platforms can reach broader user bases without requiring direct hardware access. Companies like AWS, IBM, and Microsoft have established quantum cloud services that could potentially incorporate open-hardware QEC platforms, democratizing access while maintaining commercial viability.

Educational and workforce development initiatives constitute essential components of successful ecosystem integration. Training programs focused on open-hardware QEC implementation and operation help build the technical expertise necessary for widespread adoption. Universities and technical institutions increasingly offer specialized courses in quantum engineering that incorporate hands-on experience with open-hardware platforms, creating a pipeline of qualified professionals.

Supply chain integration presents unique challenges that must be addressed through strategic partnerships with component manufacturers and fabrication facilities. The specialized requirements of QEC circuits, including ultra-low-temperature electronics and precise control systems, necessitate close collaboration with suppliers who understand these constraints. Developing reliable supply networks ensures sustainable production and deployment of open-hardware QEC platforms across the ecosystem.

Establishing standardized interfaces between open-hardware QEC platforms and existing quantum computing infrastructure represents a critical integration priority. These interfaces must facilitate seamless communication between classical control systems and quantum hardware while accommodating the unique requirements of error correction protocols. Organizations like OpenQASM and Qiskit have begun developing frameworks that support QEC operations, providing potential integration pathways for open-hardware implementations.

Collaborative development ecosystems significantly accelerate integration efforts. The formation of industry consortia dedicated to open-hardware QEC platforms enables knowledge sharing and resource pooling across academic institutions, technology companies, and research laboratories. The Quantum Open Source Foundation and Unitary Fund exemplify organizations fostering such collaboration, creating communities where hardware designs, testing methodologies, and integration approaches can be collectively refined.

Cloud accessibility strategies offer another promising integration avenue. By developing APIs and service layers that expose open-hardware QEC capabilities through cloud interfaces, these platforms can reach broader user bases without requiring direct hardware access. Companies like AWS, IBM, and Microsoft have established quantum cloud services that could potentially incorporate open-hardware QEC platforms, democratizing access while maintaining commercial viability.

Educational and workforce development initiatives constitute essential components of successful ecosystem integration. Training programs focused on open-hardware QEC implementation and operation help build the technical expertise necessary for widespread adoption. Universities and technical institutions increasingly offer specialized courses in quantum engineering that incorporate hands-on experience with open-hardware platforms, creating a pipeline of qualified professionals.

Supply chain integration presents unique challenges that must be addressed through strategic partnerships with component manufacturers and fabrication facilities. The specialized requirements of QEC circuits, including ultra-low-temperature electronics and precise control systems, necessitate close collaboration with suppliers who understand these constraints. Developing reliable supply networks ensures sustainable production and deployment of open-hardware QEC platforms across the ecosystem.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!