GDDR7 Compliance And Margining: Fixtures, Patterns And Acceptance

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

GDDR7 Technology Evolution and Compliance Goals

GDDR (Graphics Double Data Rate) memory technology has evolved significantly since its inception in the early 2000s. The progression from GDDR to GDDR7 represents a remarkable journey of increasing bandwidth, reduced power consumption, and enhanced performance capabilities. GDDR7, as the latest iteration, builds upon the foundations established by its predecessors while introducing revolutionary improvements in data transfer rates, signal integrity, and power efficiency.

The evolution trajectory shows clear technological milestones: GDDR5 introduced error detection capabilities and operated at 8Gbps, GDDR6 doubled this to 16Gbps with lower operating voltages, and now GDDR7 aims to achieve unprecedented speeds of up to 32Gbps per pin. This exponential growth in performance has been driven by innovations in semiconductor manufacturing processes, signaling techniques, and interface design.

A critical aspect of GDDR7's development is the implementation of new signaling methods, transitioning from traditional NRZ (Non-Return to Zero) to PAM4 (Pulse Amplitude Modulation 4-level) signaling. This fundamental shift enables the transmission of two bits per clock cycle instead of one, effectively doubling the data rate without proportionally increasing the clock frequency.

The compliance goals for GDDR7 technology are multifaceted and demanding. Primary objectives include establishing robust testing methodologies to ensure interoperability between memory devices and graphics processors from different manufacturers. This necessitates standardized compliance fixtures, test patterns, and acceptance criteria that can accurately measure performance across various operating conditions.

Signal integrity represents another crucial compliance goal, particularly as data rates increase and timing margins decrease. GDDR7 systems must maintain clean signal transmission with minimal jitter, crosstalk, and reflections despite operating at frequencies where even minor impedance mismatches can cause significant performance degradation.

Power efficiency targets are equally important in the GDDR7 specification, with goals to deliver more performance per watt than previous generations. This requires sophisticated power management techniques and careful optimization of voltage levels to balance performance and energy consumption.

The industry is also focused on reliability objectives, ensuring that GDDR7 memory can maintain data integrity under extreme workloads and environmental conditions. This includes developing comprehensive margining techniques to verify operational stability across voltage, temperature, and process variations.

As GDDR7 technology matures, compliance testing will play a pivotal role in market adoption, requiring specialized fixtures capable of accurately measuring high-speed signals, sophisticated test patterns that stress worst-case scenarios, and clearly defined acceptance criteria that establish minimum performance thresholds for certification.

The evolution trajectory shows clear technological milestones: GDDR5 introduced error detection capabilities and operated at 8Gbps, GDDR6 doubled this to 16Gbps with lower operating voltages, and now GDDR7 aims to achieve unprecedented speeds of up to 32Gbps per pin. This exponential growth in performance has been driven by innovations in semiconductor manufacturing processes, signaling techniques, and interface design.

A critical aspect of GDDR7's development is the implementation of new signaling methods, transitioning from traditional NRZ (Non-Return to Zero) to PAM4 (Pulse Amplitude Modulation 4-level) signaling. This fundamental shift enables the transmission of two bits per clock cycle instead of one, effectively doubling the data rate without proportionally increasing the clock frequency.

The compliance goals for GDDR7 technology are multifaceted and demanding. Primary objectives include establishing robust testing methodologies to ensure interoperability between memory devices and graphics processors from different manufacturers. This necessitates standardized compliance fixtures, test patterns, and acceptance criteria that can accurately measure performance across various operating conditions.

Signal integrity represents another crucial compliance goal, particularly as data rates increase and timing margins decrease. GDDR7 systems must maintain clean signal transmission with minimal jitter, crosstalk, and reflections despite operating at frequencies where even minor impedance mismatches can cause significant performance degradation.

Power efficiency targets are equally important in the GDDR7 specification, with goals to deliver more performance per watt than previous generations. This requires sophisticated power management techniques and careful optimization of voltage levels to balance performance and energy consumption.

The industry is also focused on reliability objectives, ensuring that GDDR7 memory can maintain data integrity under extreme workloads and environmental conditions. This includes developing comprehensive margining techniques to verify operational stability across voltage, temperature, and process variations.

As GDDR7 technology matures, compliance testing will play a pivotal role in market adoption, requiring specialized fixtures capable of accurately measuring high-speed signals, sophisticated test patterns that stress worst-case scenarios, and clearly defined acceptance criteria that establish minimum performance thresholds for certification.

Market Demand Analysis for High-Performance Memory

The demand for high-performance memory solutions has experienced unprecedented growth in recent years, primarily driven by the rapid advancement of data-intensive applications. The emergence of GDDR7 (Graphics Double Data Rate 7) technology represents a significant leap forward in addressing these escalating requirements, particularly in graphics processing, artificial intelligence, machine learning, and high-performance computing sectors.

Market research indicates that the global high-performance memory market is projected to grow at a compound annual growth rate of 22.3% from 2023 to 2028. This growth trajectory is largely attributed to the increasing adoption of AI and machine learning technologies across various industries, which require substantial memory bandwidth and capacity to process complex algorithms and massive datasets efficiently.

The gaming industry continues to be a major driver for high-performance memory demand. Modern AAA game titles demand increasingly sophisticated graphics rendering capabilities, with 4K and 8K gaming becoming standard expectations. This trend necessitates memory solutions that can handle higher bandwidth requirements while maintaining low latency, precisely what GDDR7 aims to deliver.

Data centers represent another significant market segment for high-performance memory. With the exponential growth in cloud computing services and the proliferation of big data analytics, data centers require memory solutions that can process vast amounts of information quickly and efficiently. GDDR7's improved compliance and margining capabilities directly address these needs by ensuring reliable data transmission at higher speeds.

Automotive applications, particularly advanced driver-assistance systems (ADAS) and autonomous driving technologies, are emerging as substantial consumers of high-performance memory. These systems rely on real-time processing of sensor data, requiring memory solutions with high bandwidth and reliability. The compliance and margining features of GDDR7 are crucial for ensuring the stability and safety of these critical systems.

The cryptocurrency mining sector, despite its volatility, continues to drive demand for high-performance memory solutions. Mining operations require significant computational power and memory bandwidth, making GDDR7 an attractive option for next-generation mining equipment.

Market analysis reveals a growing preference for memory solutions that not only offer superior performance but also demonstrate improved energy efficiency. GDDR7's enhanced power management features align well with this market demand, potentially providing a competitive edge over alternative high-performance memory technologies.

The testing and validation market for high-performance memory is also expanding rapidly, with increasing demand for sophisticated fixtures, testing patterns, and compliance verification tools. This sub-segment represents a significant opportunity for specialized equipment manufacturers and testing service providers focused on GDDR7 technology.

Market research indicates that the global high-performance memory market is projected to grow at a compound annual growth rate of 22.3% from 2023 to 2028. This growth trajectory is largely attributed to the increasing adoption of AI and machine learning technologies across various industries, which require substantial memory bandwidth and capacity to process complex algorithms and massive datasets efficiently.

The gaming industry continues to be a major driver for high-performance memory demand. Modern AAA game titles demand increasingly sophisticated graphics rendering capabilities, with 4K and 8K gaming becoming standard expectations. This trend necessitates memory solutions that can handle higher bandwidth requirements while maintaining low latency, precisely what GDDR7 aims to deliver.

Data centers represent another significant market segment for high-performance memory. With the exponential growth in cloud computing services and the proliferation of big data analytics, data centers require memory solutions that can process vast amounts of information quickly and efficiently. GDDR7's improved compliance and margining capabilities directly address these needs by ensuring reliable data transmission at higher speeds.

Automotive applications, particularly advanced driver-assistance systems (ADAS) and autonomous driving technologies, are emerging as substantial consumers of high-performance memory. These systems rely on real-time processing of sensor data, requiring memory solutions with high bandwidth and reliability. The compliance and margining features of GDDR7 are crucial for ensuring the stability and safety of these critical systems.

The cryptocurrency mining sector, despite its volatility, continues to drive demand for high-performance memory solutions. Mining operations require significant computational power and memory bandwidth, making GDDR7 an attractive option for next-generation mining equipment.

Market analysis reveals a growing preference for memory solutions that not only offer superior performance but also demonstrate improved energy efficiency. GDDR7's enhanced power management features align well with this market demand, potentially providing a competitive edge over alternative high-performance memory technologies.

The testing and validation market for high-performance memory is also expanding rapidly, with increasing demand for sophisticated fixtures, testing patterns, and compliance verification tools. This sub-segment represents a significant opportunity for specialized equipment manufacturers and testing service providers focused on GDDR7 technology.

GDDR7 Technical Challenges and Implementation Barriers

GDDR7 memory technology represents a significant advancement in graphics memory, but implementing it presents substantial technical challenges. The transition from GDDR6 to GDDR7 introduces new compliance testing requirements that demand sophisticated test fixtures capable of handling higher frequencies and more complex signal integrity issues. These fixtures must maintain exceptional signal integrity while supporting data rates exceeding 32 Gbps, requiring advanced materials and precision manufacturing techniques that push the boundaries of current capabilities.

Signal integrity becomes increasingly critical at GDDR7's elevated speeds, with challenges including increased crosstalk, reflections, and electromagnetic interference. The reduced timing margins at these speeds mean that even minor impedance mismatches or via transitions can significantly impact performance, necessitating advanced PCB design techniques and materials with precisely controlled dielectric properties.

Power delivery represents another major hurdle, as GDDR7's higher performance demands increased power consumption while maintaining strict voltage regulation. This creates thermal management challenges that require innovative cooling solutions to prevent performance degradation and ensure long-term reliability.

The testing patterns for GDDR7 compliance must be significantly more comprehensive than previous generations, incorporating complex stress patterns that verify functionality across various operating conditions. These patterns must evaluate both traditional parameters and new features specific to GDDR7, such as PAM3 signaling and adaptive equalization capabilities.

Calibration of test equipment presents additional complexity, requiring precise reference standards and calibration procedures to ensure measurement accuracy at GDDR7's higher frequencies. The test equipment itself must offer bandwidth capabilities well beyond the memory's operating frequency to capture higher-order harmonics and subtle signal anomalies.

Interoperability testing between GDDR7 memory and various controller implementations introduces another layer of complexity, requiring extensive validation across multiple hardware configurations and operating conditions. This necessitates sophisticated validation platforms that can simulate diverse system environments.

The industry also faces a significant knowledge gap, as GDDR7 incorporates novel signaling techniques that require new testing methodologies and expertise. Engineers must develop new skills and understanding to effectively implement and validate GDDR7 designs, creating a temporary barrier to widespread adoption until these competencies become more established in the engineering community.

Signal integrity becomes increasingly critical at GDDR7's elevated speeds, with challenges including increased crosstalk, reflections, and electromagnetic interference. The reduced timing margins at these speeds mean that even minor impedance mismatches or via transitions can significantly impact performance, necessitating advanced PCB design techniques and materials with precisely controlled dielectric properties.

Power delivery represents another major hurdle, as GDDR7's higher performance demands increased power consumption while maintaining strict voltage regulation. This creates thermal management challenges that require innovative cooling solutions to prevent performance degradation and ensure long-term reliability.

The testing patterns for GDDR7 compliance must be significantly more comprehensive than previous generations, incorporating complex stress patterns that verify functionality across various operating conditions. These patterns must evaluate both traditional parameters and new features specific to GDDR7, such as PAM3 signaling and adaptive equalization capabilities.

Calibration of test equipment presents additional complexity, requiring precise reference standards and calibration procedures to ensure measurement accuracy at GDDR7's higher frequencies. The test equipment itself must offer bandwidth capabilities well beyond the memory's operating frequency to capture higher-order harmonics and subtle signal anomalies.

Interoperability testing between GDDR7 memory and various controller implementations introduces another layer of complexity, requiring extensive validation across multiple hardware configurations and operating conditions. This necessitates sophisticated validation platforms that can simulate diverse system environments.

The industry also faces a significant knowledge gap, as GDDR7 incorporates novel signaling techniques that require new testing methodologies and expertise. Engineers must develop new skills and understanding to effectively implement and validate GDDR7 designs, creating a temporary barrier to widespread adoption until these competencies become more established in the engineering community.

Current Test Fixtures and Validation Methodologies

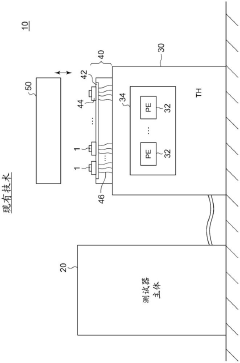

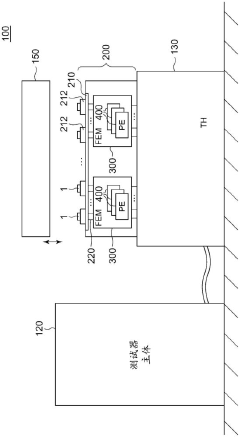

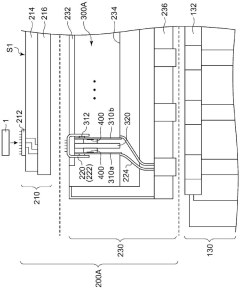

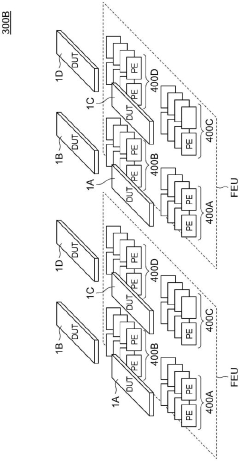

01 Memory testing and compliance verification systems

Systems and methods for testing GDDR7 memory compliance through automated verification processes. These systems can perform margining tests to ensure memory operates within specified parameters, validating signal integrity, timing requirements, and power consumption. Advanced testing frameworks help identify potential issues before deployment in production environments.- Memory testing and compliance verification methods: Various methods and systems for testing GDDR7 memory compliance, including verification of timing parameters, signal integrity, and protocol adherence. These approaches involve automated test equipment that can validate memory performance against specification requirements, ensuring proper functionality across different operating conditions and identifying potential compliance issues before deployment.

- Signal integrity and margining techniques: Techniques for ensuring signal integrity in high-speed memory interfaces like GDDR7, focusing on margining methodologies that test operational boundaries. These include voltage and timing margin analysis, eye diagram measurements, and jitter tolerance testing to determine the robustness of memory interfaces under various stress conditions, helping to establish reliable operating parameters.

- Power management and thermal compliance: Solutions addressing power consumption and thermal management challenges in GDDR7 memory implementations. These include dynamic voltage and frequency scaling techniques, thermal monitoring systems, and power-aware testing methodologies that ensure memory operates within specified power envelopes while maintaining performance requirements, particularly important for high-bandwidth applications.

- Interoperability and compatibility testing: Frameworks and methodologies for validating GDDR7 memory interoperability with various host systems and controllers. These approaches focus on ensuring backward compatibility with previous GDDR standards where applicable, testing across different vendor implementations, and validating proper functionality across various system configurations and operating conditions.

- Automated compliance verification systems: Integrated systems and platforms specifically designed for automated compliance testing of GDDR7 memory. These solutions incorporate hardware and software components that can perform comprehensive compliance verification, including automated test pattern generation, error detection and reporting, and statistical analysis of test results to identify marginal performance issues.

02 Signal integrity and timing margin analysis

Techniques for analyzing signal integrity and timing margins in high-speed memory interfaces like GDDR7. These methods involve measuring voltage and timing margins to ensure reliable data transfer, using eye diagram analysis and jitter measurements to quantify performance. Signal integrity analysis helps optimize memory controller designs and transmission line characteristics.Expand Specific Solutions03 Power management and thermal compliance

Solutions for managing power consumption and thermal characteristics in GDDR7 memory systems. These approaches include dynamic voltage and frequency scaling to maintain operation within power envelopes while ensuring performance requirements are met. Thermal monitoring and management techniques help prevent overheating while maintaining compliance with specifications.Expand Specific Solutions04 Interoperability and compatibility testing

Frameworks for ensuring GDDR7 memory interoperability across different platforms and systems. These methods verify compatibility with various graphics processing units and system architectures through standardized testing protocols. Compatibility testing includes verification of initialization sequences, command protocols, and data exchange mechanisms to ensure seamless integration.Expand Specific Solutions05 Automated compliance certification systems

Automated systems for certifying GDDR7 memory compliance with industry standards and specifications. These platforms provide comprehensive testing suites that validate memory modules against established benchmarks and requirements. Certification processes include documentation of test results, performance metrics, and compliance reports to ensure quality and reliability.Expand Specific Solutions

Key GDDR7 Technology Providers and Ecosystem

The GDDR7 memory compliance and margining landscape is currently in an early development stage, with the market poised for significant growth as next-generation graphics and AI applications demand higher memory bandwidth. The technology is still emerging, with major semiconductor players positioning themselves strategically. Companies like Intel, QUALCOMM, and Huawei are investing heavily in GDDR7 compatibility, while specialized testing equipment providers such as Advantest are developing compliance solutions. Chinese firms including Cambricon and Hygon are accelerating their involvement to reduce dependency on Western technology. Memory manufacturers like Winbond are working on early GDDR7 implementations, though full industry standardization remains in progress as fixture designs and testing patterns continue to evolve.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a comprehensive GDDR7 compliance and margining framework focused on high-performance computing and telecommunications applications. Their solution incorporates custom-designed test fixtures with advanced materials and precision manufacturing techniques to maintain signal integrity at the extreme data rates of GDDR7. Huawei's approach emphasizes multi-lane testing capabilities that can simultaneously evaluate all channels of a GDDR7 interface, significantly reducing test time for complex systems. Their test patterns include specialized sequences designed to evaluate crosstalk between adjacent channels, power supply noise sensitivity, and timing margin under various operating conditions. Huawei has implemented advanced jitter decomposition techniques that can isolate different sources of timing uncertainty, enabling targeted optimization of both device and system design. Their margining methodology incorporates 3D eye diagram analysis across voltage, timing, and temperature variations to create comprehensive maps of operating margins. Huawei's acceptance criteria are tailored to specific application requirements, with more stringent standards applied to telecommunications infrastructure compared to consumer devices.

Strengths: Huawei's extensive experience with high-speed communications gives them deep expertise in signal integrity and jitter analysis. Their vertical integration allows for coordinated optimization of memory interfaces across chips, boards, and systems. Weaknesses: Their solutions may face adoption challenges in some markets due to geopolitical considerations, potentially limiting their global impact despite technical merits.

Intel Corp.

Technical Solution: Intel has developed comprehensive GDDR7 compliance and margining solutions focusing on high-speed memory interfaces for next-generation graphics and AI applications. Their approach includes advanced fixture designs with optimized signal integrity characteristics that minimize insertion loss and return loss at frequencies exceeding 40GHz. Intel's test methodology incorporates specialized test patterns designed to stress-test the GDDR7 interface under various operating conditions, including voltage and timing margin analysis. Their compliance testing framework utilizes high-precision time-domain reflectometry (TDR) and vector network analysis (VNA) to characterize channel performance across the entire operating frequency range. Intel has also implemented automated margining tools that can rapidly identify the operating limits of GDDR7 interfaces, allowing for optimization of both power and performance characteristics. Their acceptance criteria are based on extensive statistical analysis of multiple test vectors across temperature and voltage corners to ensure robust operation in real-world environments.

Strengths: Intel's extensive experience with memory interfaces provides them with deep expertise in signal integrity and compliance testing. Their in-house manufacturing capabilities allow for rapid iteration of test fixtures and validation methodologies. Weaknesses: Their solutions may be optimized primarily for their own products rather than providing vendor-neutral testing approaches, potentially limiting applicability across different implementations.

Critical Test Patterns and Compliance Verification Techniques

Automatic test device and interface device thereof

PatentPendingCN117434309A

Innovation

- An interface device is designed. By arranging a socket board, a first interposer layer and wiring between the test head and the device under test, and using the FPC cable to directly contact the interposer layer, the signal transmission loss is reduced, and the pin electronic IC Modularized into a front-end module, configured near the DUT to shorten the signal transmission distance.

Signal Integrity Considerations for GDDR7 Implementation

Signal integrity represents a critical challenge in GDDR7 implementation due to the memory standard's unprecedented data rates exceeding 40 Gbps. The high-frequency operation introduces significant electromagnetic interference concerns that must be addressed through comprehensive design strategies. Proper impedance matching becomes essential, as even minor mismatches can cause signal reflections leading to data corruption at these elevated speeds.

GDDR7 introduces more stringent requirements for transmission line design compared to previous generations. PCB materials with lower dielectric loss tangent values are necessary to minimize signal attenuation across the interconnect. The selection of appropriate stackup configurations with controlled impedance routing becomes paramount to maintaining signal quality throughout the entire path from memory controller to GDDR7 device.

Crosstalk mitigation strategies must be implemented with greater precision in GDDR7 designs. This includes optimized trace spacing, strategic use of ground planes, and potentially employing differential signaling techniques where applicable. The reduced timing margins at higher data rates make systems increasingly sensitive to noise coupling between adjacent signal lines.

Power delivery network (PDN) design directly impacts signal integrity in GDDR7 implementations. Voltage fluctuations caused by inadequate PDN design can translate to jitter and timing violations. Decoupling capacitor selection and placement must be carefully engineered to provide stable power across the full bandwidth of operation, with particular attention to resonance effects that may occur at GDDR7's operating frequencies.

Advanced equalization techniques become necessary to compensate for channel losses at GDDR7 speeds. Both transmitter-side pre-emphasis and receiver-side equalization must be properly configured to open the data eye sufficiently for reliable sampling. The compliance and margining procedures must verify that these equalization settings provide adequate performance across all process, voltage, and temperature variations.

Time-domain reflectometry (TDR) and vector network analyzer (VNA) measurements are essential tools for characterizing GDDR7 channels. These measurements help identify impedance discontinuities and frequency-dependent losses that could compromise signal integrity. The fixture design for these measurements must carefully account for de-embedding techniques to isolate the performance of the actual channel under test.

Simulation methodologies including 3D electromagnetic field solvers and channel analysis tools play a crucial role in predicting signal integrity issues before physical implementation. These tools must accurately model the complex interactions between signals, power distribution, and physical structures to ensure first-pass design success with GDDR7 interfaces.

GDDR7 introduces more stringent requirements for transmission line design compared to previous generations. PCB materials with lower dielectric loss tangent values are necessary to minimize signal attenuation across the interconnect. The selection of appropriate stackup configurations with controlled impedance routing becomes paramount to maintaining signal quality throughout the entire path from memory controller to GDDR7 device.

Crosstalk mitigation strategies must be implemented with greater precision in GDDR7 designs. This includes optimized trace spacing, strategic use of ground planes, and potentially employing differential signaling techniques where applicable. The reduced timing margins at higher data rates make systems increasingly sensitive to noise coupling between adjacent signal lines.

Power delivery network (PDN) design directly impacts signal integrity in GDDR7 implementations. Voltage fluctuations caused by inadequate PDN design can translate to jitter and timing violations. Decoupling capacitor selection and placement must be carefully engineered to provide stable power across the full bandwidth of operation, with particular attention to resonance effects that may occur at GDDR7's operating frequencies.

Advanced equalization techniques become necessary to compensate for channel losses at GDDR7 speeds. Both transmitter-side pre-emphasis and receiver-side equalization must be properly configured to open the data eye sufficiently for reliable sampling. The compliance and margining procedures must verify that these equalization settings provide adequate performance across all process, voltage, and temperature variations.

Time-domain reflectometry (TDR) and vector network analyzer (VNA) measurements are essential tools for characterizing GDDR7 channels. These measurements help identify impedance discontinuities and frequency-dependent losses that could compromise signal integrity. The fixture design for these measurements must carefully account for de-embedding techniques to isolate the performance of the actual channel under test.

Simulation methodologies including 3D electromagnetic field solvers and channel analysis tools play a crucial role in predicting signal integrity issues before physical implementation. These tools must accurately model the complex interactions between signals, power distribution, and physical structures to ensure first-pass design success with GDDR7 interfaces.

Interoperability Standards and Certification Processes

Interoperability standards for GDDR7 memory interfaces represent a critical framework ensuring seamless integration across diverse hardware ecosystems. The Joint Electron Device Engineering Council (JEDEC) serves as the primary standards body responsible for establishing the compliance specifications that govern GDDR7 implementation. These standards define precise electrical characteristics, timing parameters, and physical interface requirements that all GDDR7-compatible devices must adhere to.

The certification process for GDDR7 compliance follows a multi-tiered approach, beginning with pre-silicon validation through simulation and modeling, followed by silicon-level testing using specialized fixtures and test equipment. Manufacturers must demonstrate that their implementations meet or exceed the established performance thresholds across various operating conditions, including temperature extremes and voltage variations.

Test patterns for GDDR7 certification are specifically designed to stress the memory interface under worst-case scenarios. These include pseudo-random bit sequences (PRBS) that exercise the full frequency spectrum, targeted pattern sets that induce maximum crosstalk, and specialized patterns that verify proper operation of equalization and training algorithms. The certification process requires successful completion of all mandatory test patterns with acceptable margin levels.

Compliance fixtures for GDDR7 represent a significant advancement over previous generations, incorporating precision impedance-controlled channels, calibrated via structures, and integrated measurement points. These fixtures must themselves be certified to ensure measurement accuracy and repeatability across different test environments. The fixture design accounts for the extreme signaling rates of GDDR7, which exceed 30 Gbps per pin.

Acceptance criteria for GDDR7 certification establish clear pass/fail thresholds for key parameters including eye height, eye width, jitter components, and voltage margins. These criteria are typically defined at multiple operating points to ensure robust performance across the entire operating range. Statistical analysis methods are employed to establish confidence levels in the measured results.

Interoperability workshops and plugfests serve as collaborative industry events where manufacturers can verify cross-vendor compatibility of their GDDR7 implementations. These events facilitate early identification of interoperability issues before products reach the market. Participation in these events, while not mandatory, has become a de facto requirement for manufacturers seeking to establish credibility in the GDDR7 ecosystem.

The certification ecosystem includes authorized third-party test laboratories that can independently verify compliance claims. These laboratories maintain calibrated test environments and follow standardized test methodologies to ensure consistent results across different vendors and implementations.

The certification process for GDDR7 compliance follows a multi-tiered approach, beginning with pre-silicon validation through simulation and modeling, followed by silicon-level testing using specialized fixtures and test equipment. Manufacturers must demonstrate that their implementations meet or exceed the established performance thresholds across various operating conditions, including temperature extremes and voltage variations.

Test patterns for GDDR7 certification are specifically designed to stress the memory interface under worst-case scenarios. These include pseudo-random bit sequences (PRBS) that exercise the full frequency spectrum, targeted pattern sets that induce maximum crosstalk, and specialized patterns that verify proper operation of equalization and training algorithms. The certification process requires successful completion of all mandatory test patterns with acceptable margin levels.

Compliance fixtures for GDDR7 represent a significant advancement over previous generations, incorporating precision impedance-controlled channels, calibrated via structures, and integrated measurement points. These fixtures must themselves be certified to ensure measurement accuracy and repeatability across different test environments. The fixture design accounts for the extreme signaling rates of GDDR7, which exceed 30 Gbps per pin.

Acceptance criteria for GDDR7 certification establish clear pass/fail thresholds for key parameters including eye height, eye width, jitter components, and voltage margins. These criteria are typically defined at multiple operating points to ensure robust performance across the entire operating range. Statistical analysis methods are employed to establish confidence levels in the measured results.

Interoperability workshops and plugfests serve as collaborative industry events where manufacturers can verify cross-vendor compatibility of their GDDR7 implementations. These events facilitate early identification of interoperability issues before products reach the market. Participation in these events, while not mandatory, has become a de facto requirement for manufacturers seeking to establish credibility in the GDDR7 ecosystem.

The certification ecosystem includes authorized third-party test laboratories that can independently verify compliance claims. These laboratories maintain calibrated test environments and follow standardized test methodologies to ensure consistent results across different vendors and implementations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!