GDDR7 Power Delivery: VRM Transients, PDN Impedance And Droop Control

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

GDDR7 Power Delivery Background and Objectives

Graphics Double Data Rate (GDDR) memory technology has evolved significantly over the past two decades, with each generation bringing substantial improvements in bandwidth, power efficiency, and overall performance. GDDR7, as the latest iteration in this evolutionary chain, represents a significant leap forward in addressing the ever-increasing demands of high-performance computing applications, particularly in graphics processing, artificial intelligence, and data centers.

The development of GDDR memory has been driven by the relentless pursuit of higher bandwidth and lower latency to support increasingly complex computational tasks. From GDDR3 to GDDR6, we have witnessed a consistent pattern of doubling bandwidth while improving power efficiency. GDDR7 continues this trajectory, promising data rates exceeding 32 Gbps per pin, a substantial improvement over GDDR6's 16-24 Gbps.

However, these performance gains come with significant challenges in power delivery. As data rates increase, so do the power requirements and the complexity of maintaining stable voltage levels across increasingly dense memory arrays. The power delivery network (PDN) for GDDR7 must contend with higher current demands, faster transients, and stricter voltage regulation requirements than previous generations.

Voltage regulator modules (VRMs) for GDDR7 face unprecedented challenges in responding to rapid load transients that occur during memory operations. These transients can cause voltage droops that, if not properly controlled, may lead to data integrity issues or system instability. The impedance characteristics of the PDN become critical at these higher frequencies, necessitating careful design and optimization.

The technical objective of this research is to comprehensively analyze the power delivery challenges specific to GDDR7 implementation, with particular focus on VRM transient response, PDN impedance optimization, and droop control methodologies. We aim to identify the key technical barriers that must be overcome to enable stable, efficient power delivery for GDDR7 memory systems operating at their full potential.

Additionally, this research seeks to explore emerging solutions and best practices for GDDR7 power delivery, including advanced VRM topologies, innovative PDN design techniques, and novel approaches to voltage regulation. By understanding the current state of the art and anticipating future developments, we can provide valuable insights to guide strategic technology investments and product development roadmaps.

The findings from this research will inform design decisions for next-generation graphics processing units, AI accelerators, and high-performance computing systems that will leverage GDDR7 memory to deliver unprecedented computational capabilities while maintaining power efficiency and system reliability.

The development of GDDR memory has been driven by the relentless pursuit of higher bandwidth and lower latency to support increasingly complex computational tasks. From GDDR3 to GDDR6, we have witnessed a consistent pattern of doubling bandwidth while improving power efficiency. GDDR7 continues this trajectory, promising data rates exceeding 32 Gbps per pin, a substantial improvement over GDDR6's 16-24 Gbps.

However, these performance gains come with significant challenges in power delivery. As data rates increase, so do the power requirements and the complexity of maintaining stable voltage levels across increasingly dense memory arrays. The power delivery network (PDN) for GDDR7 must contend with higher current demands, faster transients, and stricter voltage regulation requirements than previous generations.

Voltage regulator modules (VRMs) for GDDR7 face unprecedented challenges in responding to rapid load transients that occur during memory operations. These transients can cause voltage droops that, if not properly controlled, may lead to data integrity issues or system instability. The impedance characteristics of the PDN become critical at these higher frequencies, necessitating careful design and optimization.

The technical objective of this research is to comprehensively analyze the power delivery challenges specific to GDDR7 implementation, with particular focus on VRM transient response, PDN impedance optimization, and droop control methodologies. We aim to identify the key technical barriers that must be overcome to enable stable, efficient power delivery for GDDR7 memory systems operating at their full potential.

Additionally, this research seeks to explore emerging solutions and best practices for GDDR7 power delivery, including advanced VRM topologies, innovative PDN design techniques, and novel approaches to voltage regulation. By understanding the current state of the art and anticipating future developments, we can provide valuable insights to guide strategic technology investments and product development roadmaps.

The findings from this research will inform design decisions for next-generation graphics processing units, AI accelerators, and high-performance computing systems that will leverage GDDR7 memory to deliver unprecedented computational capabilities while maintaining power efficiency and system reliability.

Market Demand Analysis for High-Performance Memory

The high-performance memory market is experiencing unprecedented growth driven by several converging technological trends. Artificial intelligence and machine learning applications have emerged as primary demand drivers, with training large language models and neural networks requiring massive memory bandwidth and capacity. GDDR7, as the next generation of graphics memory, is positioned to address these escalating requirements through improved power delivery systems.

Data centers represent another significant market segment fueling demand for advanced memory solutions. The exponential growth in cloud computing services, big data analytics, and enterprise applications has created substantial need for memory technologies that can deliver higher bandwidth while maintaining power efficiency. Market research indicates that data center memory demand is growing at approximately 25% annually, with power efficiency becoming a critical selection criterion.

Gaming and professional visualization markets continue to push memory performance boundaries. Modern AAA game titles and real-time rendering applications demand increasingly higher frame rates at 4K and 8K resolutions, necessitating memory solutions that can handle massive data throughput. The gaming hardware market alone represents a multi-billion dollar opportunity for high-performance memory technologies.

Automotive applications, particularly advanced driver-assistance systems (ADAS) and autonomous driving platforms, are emerging as significant consumers of high-performance memory. These systems process enormous amounts of sensor data in real-time, requiring memory solutions with exceptional bandwidth and reliability characteristics. Industry forecasts suggest the automotive memory market will grow substantially over the next five years.

The cryptocurrency mining sector, despite its volatility, continues to influence memory demand cycles. During peak mining periods, this sector can absorb significant portions of available high-performance memory production capacity, affecting pricing and availability across other market segments.

From a geographical perspective, North America and Asia-Pacific regions dominate demand for high-performance memory, with China, South Korea, Taiwan, and the United States being key markets. The concentration of AI research, data center operations, and semiconductor manufacturing in these regions drives this regional demand distribution.

Customer requirements are increasingly focused on the total cost of ownership, with power efficiency becoming as important as raw performance metrics. This shift has placed greater emphasis on advanced power delivery solutions like those being developed for GDDR7, including improved VRM transients, optimized PDN impedance, and enhanced droop control mechanisms that can maintain stable operation under dynamic workloads while minimizing energy consumption.

Data centers represent another significant market segment fueling demand for advanced memory solutions. The exponential growth in cloud computing services, big data analytics, and enterprise applications has created substantial need for memory technologies that can deliver higher bandwidth while maintaining power efficiency. Market research indicates that data center memory demand is growing at approximately 25% annually, with power efficiency becoming a critical selection criterion.

Gaming and professional visualization markets continue to push memory performance boundaries. Modern AAA game titles and real-time rendering applications demand increasingly higher frame rates at 4K and 8K resolutions, necessitating memory solutions that can handle massive data throughput. The gaming hardware market alone represents a multi-billion dollar opportunity for high-performance memory technologies.

Automotive applications, particularly advanced driver-assistance systems (ADAS) and autonomous driving platforms, are emerging as significant consumers of high-performance memory. These systems process enormous amounts of sensor data in real-time, requiring memory solutions with exceptional bandwidth and reliability characteristics. Industry forecasts suggest the automotive memory market will grow substantially over the next five years.

The cryptocurrency mining sector, despite its volatility, continues to influence memory demand cycles. During peak mining periods, this sector can absorb significant portions of available high-performance memory production capacity, affecting pricing and availability across other market segments.

From a geographical perspective, North America and Asia-Pacific regions dominate demand for high-performance memory, with China, South Korea, Taiwan, and the United States being key markets. The concentration of AI research, data center operations, and semiconductor manufacturing in these regions drives this regional demand distribution.

Customer requirements are increasingly focused on the total cost of ownership, with power efficiency becoming as important as raw performance metrics. This shift has placed greater emphasis on advanced power delivery solutions like those being developed for GDDR7, including improved VRM transients, optimized PDN impedance, and enhanced droop control mechanisms that can maintain stable operation under dynamic workloads while minimizing energy consumption.

VRM Transient Response Challenges

Voltage Regulator Modules (VRMs) in GDDR7 memory systems face unprecedented transient response challenges due to the extreme power delivery requirements of these high-performance memory interfaces. The rapid load transitions in GDDR7 applications, which can occur within nanoseconds, create significant stress on power delivery networks. These transients manifest as voltage spikes and droops that can exceed acceptable operating margins, potentially causing system instability or even failure.

The primary challenge stems from the fundamental trade-off between response time and stability in VRM design. GDDR7's operating frequencies exceeding 40 Gbps demand ultra-fast response times, yet maintaining stability becomes increasingly difficult as response speeds increase. This creates a complex optimization problem where designers must balance multiple competing requirements.

Load step transients present a particularly difficult challenge. When GDDR7 memory transitions from idle to active states, current demands can increase by orders of magnitude almost instantaneously. Conventional VRM designs struggle to respond quickly enough, resulting in significant voltage droops that can trigger under-voltage protection mechanisms or cause memory errors.

Similarly, load release transients occur when memory transitions from active to idle states, causing voltage overshoots that may exceed maximum ratings and potentially damage sensitive components. These bidirectional transient events require sophisticated control mechanisms that can anticipate and respond to both rising and falling load conditions.

The physical constraints of modern system designs further complicate matters. As form factors continue to shrink, the physical distance between VRMs and GDDR7 memory increases the impedance of power delivery paths, exacerbating transient response issues. This spatial challenge requires innovative approaches to component placement and PCB design.

Advanced semiconductor processes used in GDDR7 memory also contribute to transient response difficulties. Lower operating voltages with tighter tolerances leave minimal margin for error, while simultaneously increasing sensitivity to power supply fluctuations. This creates a scenario where even minor transient events can impact system performance.

Thermal considerations add another dimension to the challenge. Transient events generate heat pulses that can create localized hotspots, potentially triggering thermal throttling mechanisms. Managing these thermal transients requires sophisticated cooling solutions integrated with power delivery systems.

Addressing these challenges requires a multidisciplinary approach combining advanced control theory, innovative circuit design, sophisticated simulation techniques, and precise manufacturing processes. The industry is actively exploring solutions including multi-phase VRMs with advanced phase shedding, adaptive control algorithms, integrated voltage regulators, and distributed power architectures to meet the demanding transient response requirements of GDDR7 memory systems.

The primary challenge stems from the fundamental trade-off between response time and stability in VRM design. GDDR7's operating frequencies exceeding 40 Gbps demand ultra-fast response times, yet maintaining stability becomes increasingly difficult as response speeds increase. This creates a complex optimization problem where designers must balance multiple competing requirements.

Load step transients present a particularly difficult challenge. When GDDR7 memory transitions from idle to active states, current demands can increase by orders of magnitude almost instantaneously. Conventional VRM designs struggle to respond quickly enough, resulting in significant voltage droops that can trigger under-voltage protection mechanisms or cause memory errors.

Similarly, load release transients occur when memory transitions from active to idle states, causing voltage overshoots that may exceed maximum ratings and potentially damage sensitive components. These bidirectional transient events require sophisticated control mechanisms that can anticipate and respond to both rising and falling load conditions.

The physical constraints of modern system designs further complicate matters. As form factors continue to shrink, the physical distance between VRMs and GDDR7 memory increases the impedance of power delivery paths, exacerbating transient response issues. This spatial challenge requires innovative approaches to component placement and PCB design.

Advanced semiconductor processes used in GDDR7 memory also contribute to transient response difficulties. Lower operating voltages with tighter tolerances leave minimal margin for error, while simultaneously increasing sensitivity to power supply fluctuations. This creates a scenario where even minor transient events can impact system performance.

Thermal considerations add another dimension to the challenge. Transient events generate heat pulses that can create localized hotspots, potentially triggering thermal throttling mechanisms. Managing these thermal transients requires sophisticated cooling solutions integrated with power delivery systems.

Addressing these challenges requires a multidisciplinary approach combining advanced control theory, innovative circuit design, sophisticated simulation techniques, and precise manufacturing processes. The industry is actively exploring solutions including multi-phase VRMs with advanced phase shedding, adaptive control algorithms, integrated voltage regulators, and distributed power architectures to meet the demanding transient response requirements of GDDR7 memory systems.

Current PDN Impedance Management Solutions

01 VRM Transient Response Optimization for GDDR7

Voltage Regulator Modules (VRMs) for GDDR7 memory require optimized transient response to handle rapid current changes during memory operations. Advanced control algorithms and circuit designs are implemented to minimize voltage fluctuations during load transients. These designs incorporate fast-responding feedback loops and predictive control mechanisms to maintain stable voltage levels during high-frequency switching operations typical in GDDR7 applications.- VRM Transient Response Optimization for GDDR7: Voltage Regulator Modules (VRMs) for GDDR7 memory require optimized transient response to handle rapid load changes. Advanced control algorithms and circuit designs are implemented to minimize voltage fluctuations during high-speed memory operations. These solutions include adaptive voltage positioning, multi-phase VRM designs, and fast-response feedback loops that can respond to load transients within nanoseconds, ensuring stable power delivery to GDDR7 memory under dynamic workloads.

- Power Distribution Network Impedance Management: Managing PDN impedance is critical for GDDR7 memory systems to maintain signal integrity and power stability. Techniques include strategic placement of decoupling capacitors, controlled impedance power planes, and resonance damping structures. Advanced PDN designs incorporate target impedance profiles across frequency ranges relevant to GDDR7 operation, with special attention to minimizing impedance at the memory controller's switching frequencies to reduce power supply noise and improve system reliability.

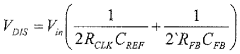

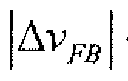

- Adaptive Droop Control Mechanisms: Adaptive droop control mechanisms are implemented in GDDR7 power delivery systems to dynamically adjust voltage levels based on load conditions. These systems monitor current draw and proactively adjust voltage output to compensate for potential droop during high-demand operations. Advanced implementations include machine learning algorithms that predict load patterns and pre-emptively adjust power delivery parameters, reducing latency and improving overall system efficiency while maintaining voltage stability within GDDR7 specifications.

- High-Frequency Decoupling Solutions: GDDR7 memory systems require sophisticated high-frequency decoupling solutions to manage power integrity at elevated operating frequencies. Multi-layer ceramic capacitors with low ESR/ESL characteristics are strategically placed near memory components to filter high-frequency noise. Advanced designs incorporate embedded capacitance within PCB layers and on-die capacitance structures to provide localized charge storage and minimize power delivery path inductance, ensuring clean power delivery during rapid switching events characteristic of GDDR7 operation.

- Thermal-Aware Power Management for GDDR7: Thermal-aware power management systems for GDDR7 integrate temperature monitoring with power delivery control to optimize performance while preventing thermal issues. These systems dynamically adjust voltage and frequency parameters based on thermal feedback, implementing sophisticated algorithms that balance power consumption with thermal constraints. Advanced implementations include predictive thermal modeling that anticipates temperature changes and proactively adjusts power delivery parameters to maintain optimal operating conditions while preventing thermal throttling in high-performance GDDR7 memory subsystems.

02 Power Delivery Network Impedance Management

Managing PDN impedance is critical for GDDR7 memory systems to ensure stable power delivery across a wide frequency range. Techniques include strategic placement of decoupling capacitors, controlled trace impedance, and optimized power plane designs. These approaches minimize impedance resonances and create a low-impedance path across the operational frequency range of GDDR7 memory, reducing noise and improving signal integrity in high-speed memory interfaces.Expand Specific Solutions03 Adaptive Droop Control Mechanisms

Adaptive droop control systems for GDDR7 power delivery dynamically adjust voltage levels based on load conditions. These systems implement load-line calibration and adaptive voltage positioning to intentionally lower voltage during high current demands, reducing peak power consumption while maintaining system stability. Advanced implementations include machine learning algorithms that predict load changes and proactively adjust voltage levels to optimize performance and power efficiency.Expand Specific Solutions04 Multi-phase VRM Designs for High Current Delivery

Multi-phase VRM architectures are employed in GDDR7 power systems to distribute current delivery across multiple phases, reducing thermal stress and improving transient response. These designs feature phase shedding capabilities that dynamically adjust the number of active phases based on load requirements, optimizing efficiency across various operational states. Interleaved switching techniques further reduce output ripple and improve transient response for the high-current demands of GDDR7 memory systems.Expand Specific Solutions05 High-Frequency Decoupling and Noise Suppression

Specialized decoupling networks and noise suppression techniques are implemented in GDDR7 power delivery systems to manage high-frequency noise components. These include multi-layer ceramic capacitors with optimized placement, embedded capacitance in PCB designs, and active noise cancellation circuits. Advanced filtering topologies target specific frequency bands where GDDR7 memory is most sensitive to power noise, ensuring clean power delivery during critical memory operations and reducing bit error rates.Expand Specific Solutions

Key Industry Players in GDDR7 Ecosystem

The GDDR7 power delivery technology landscape is currently in an early growth phase, with a market expected to expand significantly as high-performance computing and AI applications drive demand. The technology is approaching maturity with key players like NVIDIA, AMD, Intel, and Qualcomm leading development efforts. These companies are focusing on solving critical challenges in VRM transients, PDN impedance, and droop control to enable next-generation memory performance. Samsung Electro-Mechanics and Infineon are making notable contributions in power delivery components, while research partnerships with institutions like Columbia University and Georgia Tech are advancing theoretical foundations. The competitive landscape is intensifying as companies race to commercialize solutions that balance power efficiency with the increasing bandwidth demands of modern computing applications.

Intel Corp.

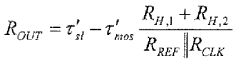

Technical Solution: Intel's GDDR7 power delivery architecture leverages their Fully Integrated Voltage Regulators (FIVR) technology adapted specifically for high-bandwidth memory applications. Their solution integrates high-frequency switching regulators (operating at >5MHz) directly into the package substrate, dramatically reducing power delivery loop inductance to <100pH. Intel employs a hierarchical power delivery approach with multiple regulation stages, including die-integrated low-dropout regulators (LDOs) for final stage regulation that can respond to transients in under 50ns. Their PDN design features embedded silicon capacitors with ultra-low ESR and ESL characteristics, maintaining PDN impedance below 0.5mΩ across the critical 1MHz-500MHz frequency range. Intel has developed proprietary Fast Transient Response (FTR) algorithms that use predictive load modeling to anticipate memory access patterns and pre-emptively adjust voltage levels, reducing effective voltage droop by up to 40% compared to reactive systems. Their solution also incorporates distributed current sensors with sub-microsecond sampling rates to enable real-time power telemetry and dynamic power allocation.

Strengths: Exceptional integration capabilities leveraging advanced packaging technologies; superior transient response characteristics; comprehensive power telemetry for system optimization. Weaknesses: Higher manufacturing complexity; potentially more challenging thermal management due to concentrated power components.

Infineon Technologies Americas Corp.

Technical Solution: Infineon's GDDR7 power delivery solution centers on their TDA21472 DrMOS power stages combined with their XDPE132G5C digital controllers specifically optimized for graphics memory applications. Their architecture features a multi-phase interleaved design (typically 6-8 phases) with phase shedding capabilities that maintain high efficiency across varying load conditions. Infineon employs proprietary VR14-compliant control algorithms with enhanced transient response that can detect load changes in under 200ns and adjust duty cycles within a single switching cycle. Their PDN design incorporates specialized low-inductance packaging technology that reduces power stage inductance to <0.2nH, critical for maintaining clean power delivery at GDDR7's high operating frequencies. Infineon has developed advanced current balancing techniques that ensure even distribution of current across all phases within ±3% tolerance, reducing hotspots and improving overall reliability. Their solution also features integrated di/dt control that limits current slew rates during extreme transients, preventing potential oscillations in the power delivery network while still maintaining voltage within GDDR7 specifications.

Strengths: Industry-leading power conversion efficiency (>93% at typical operating points); extensive experience with graphics card power delivery; comprehensive protection features including over-current, over-voltage, and thermal monitoring. Weaknesses: Requires careful system-level design coordination; potentially higher component count compared to more integrated solutions.

Critical Technologies for Droop Control

Power delivery network analysis

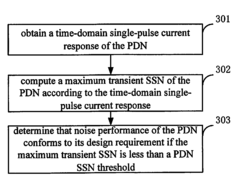

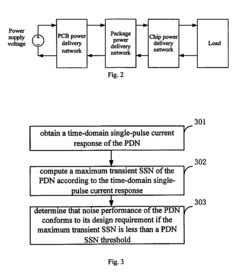

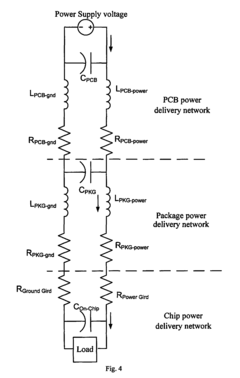

PatentInactiveUS9098671B2

Innovation

- A method and apparatus for PDN analysis that involves obtaining time-domain single-pulse current responses to compute the maximum transient SSN, determining if the noise performance meets design requirements by comparing it to a threshold, without the need for circuit simulation.

Systems and methods for switched-inductor integrated voltage regulators

PatentWO2013032753A2

Innovation

- A power controller with multiple hardware phases and a comparator-based control scheme that generates feedback voltage from inductor current, allowing for dynamic adjustment of duty cycle and output impedance to regulate voltage effectively, using on-chip MOS or deep-trench capacitance to reduce load-line inefficiency and enhance transient response.

Thermal Management Considerations

Thermal management represents a critical aspect of GDDR7 power delivery systems, particularly as memory bandwidth and power requirements continue to escalate. The increased power density of GDDR7 memory modules generates substantial thermal loads that must be effectively managed to maintain system reliability and performance.

Power delivery components, especially Voltage Regulator Modules (VRMs), contribute significantly to the thermal profile of GDDR7 systems. During transient load conditions, VRMs experience current spikes that generate localized heating. This thermal cycling can accelerate component degradation if not properly addressed through strategic thermal design considerations.

The Power Distribution Network (PDN) impedance characteristics directly influence thermal performance. Higher impedance paths create resistance-based heating under load, converting electrical energy to thermal energy. Optimizing PDN layouts to minimize impedance not only improves electrical performance but also reduces thermal hotspots throughout the memory subsystem.

Droop control mechanisms, while primarily designed to maintain voltage stability, play a dual role in thermal management. By smoothing transient responses, these circuits reduce peak currents that would otherwise generate momentary thermal spikes. Advanced droop control implementations must balance electrical performance with thermal considerations to achieve optimal system operation.

Thermal coupling between power delivery components and memory modules presents another design challenge. Heat generated by VRMs can transfer to nearby GDDR7 chips, potentially pushing them beyond their thermal specifications. Thermal isolation techniques and strategic component placement become essential design considerations to mitigate this effect.

Cooling solutions for GDDR7 systems must address both steady-state and transient thermal conditions. Traditional heatsinks and forced air cooling may prove insufficient for managing the thermal profile of high-performance GDDR7 implementations. Advanced cooling technologies, including vapor chambers, heat pipes, and liquid cooling solutions, are increasingly being deployed to maintain acceptable operating temperatures.

Thermal monitoring and dynamic power management represent the final frontier in GDDR7 thermal management. Integrated temperature sensors and intelligent power control algorithms can dynamically adjust system parameters based on thermal conditions, ensuring optimal performance while preventing thermal runaway scenarios.

Power delivery components, especially Voltage Regulator Modules (VRMs), contribute significantly to the thermal profile of GDDR7 systems. During transient load conditions, VRMs experience current spikes that generate localized heating. This thermal cycling can accelerate component degradation if not properly addressed through strategic thermal design considerations.

The Power Distribution Network (PDN) impedance characteristics directly influence thermal performance. Higher impedance paths create resistance-based heating under load, converting electrical energy to thermal energy. Optimizing PDN layouts to minimize impedance not only improves electrical performance but also reduces thermal hotspots throughout the memory subsystem.

Droop control mechanisms, while primarily designed to maintain voltage stability, play a dual role in thermal management. By smoothing transient responses, these circuits reduce peak currents that would otherwise generate momentary thermal spikes. Advanced droop control implementations must balance electrical performance with thermal considerations to achieve optimal system operation.

Thermal coupling between power delivery components and memory modules presents another design challenge. Heat generated by VRMs can transfer to nearby GDDR7 chips, potentially pushing them beyond their thermal specifications. Thermal isolation techniques and strategic component placement become essential design considerations to mitigate this effect.

Cooling solutions for GDDR7 systems must address both steady-state and transient thermal conditions. Traditional heatsinks and forced air cooling may prove insufficient for managing the thermal profile of high-performance GDDR7 implementations. Advanced cooling technologies, including vapor chambers, heat pipes, and liquid cooling solutions, are increasingly being deployed to maintain acceptable operating temperatures.

Thermal monitoring and dynamic power management represent the final frontier in GDDR7 thermal management. Integrated temperature sensors and intelligent power control algorithms can dynamically adjust system parameters based on thermal conditions, ensuring optimal performance while preventing thermal runaway scenarios.

Signal Integrity and EMI Mitigation Strategies

Signal integrity and electromagnetic interference (EMI) are critical concerns in GDDR7 memory systems due to the high-speed data transfer rates exceeding 40 Gbps. The power delivery network (PDN) must be carefully designed to maintain signal integrity while minimizing EMI effects that could compromise system performance.

Advanced signal routing techniques are essential for GDDR7 implementations. Differential pair routing with controlled impedance traces helps maintain signal integrity across the high-speed memory interface. Designers must implement precise length matching between data lanes to ensure synchronous data arrival, with tolerances typically under 5 mils for GDDR7 applications.

Electromagnetic shielding strategies have evolved significantly for GDDR7 systems. Multi-layer PCB designs with dedicated ground planes provide essential isolation between power and signal layers. The strategic placement of these planes helps contain electromagnetic fields and reduces crosstalk between adjacent signal traces. For optimal performance, ground plane continuity must be maintained, with minimal splits or gaps that could create return path discontinuities.

Via optimization represents another critical aspect of signal integrity management. The transition between PCB layers introduces impedance discontinuities that can degrade signal quality. Back-drilling techniques remove unused via stubs that would otherwise act as antennas, generating EMI and causing signal reflections. For GDDR7 applications, via design must account for frequencies exceeding 20 GHz.

Decoupling capacitor placement strategies have become increasingly sophisticated to address the transient response requirements of GDDR7 memory. A multi-tiered approach utilizing various capacitor values (from nF to μF) at strategic locations helps maintain a low-impedance power delivery path across a wide frequency spectrum. This approach effectively dampens resonances in the PDN that could otherwise couple into signal paths.

Advanced termination schemes are necessary to minimize signal reflections in GDDR7 interfaces. Dynamic on-die termination (ODT) techniques adjust termination impedance based on operating conditions, optimizing signal quality while reducing power consumption. These adaptive termination methods are particularly valuable for managing the varying impedance characteristics encountered during different GDDR7 operating modes.

EMI compliance testing for GDDR7 systems requires sophisticated near-field and far-field measurement techniques. Pre-compliance testing during the development phase helps identify potential EMI hotspots before formal certification. Simulation tools that model both conducted and radiated emissions have become essential for predicting EMI performance before hardware implementation.

Advanced signal routing techniques are essential for GDDR7 implementations. Differential pair routing with controlled impedance traces helps maintain signal integrity across the high-speed memory interface. Designers must implement precise length matching between data lanes to ensure synchronous data arrival, with tolerances typically under 5 mils for GDDR7 applications.

Electromagnetic shielding strategies have evolved significantly for GDDR7 systems. Multi-layer PCB designs with dedicated ground planes provide essential isolation between power and signal layers. The strategic placement of these planes helps contain electromagnetic fields and reduces crosstalk between adjacent signal traces. For optimal performance, ground plane continuity must be maintained, with minimal splits or gaps that could create return path discontinuities.

Via optimization represents another critical aspect of signal integrity management. The transition between PCB layers introduces impedance discontinuities that can degrade signal quality. Back-drilling techniques remove unused via stubs that would otherwise act as antennas, generating EMI and causing signal reflections. For GDDR7 applications, via design must account for frequencies exceeding 20 GHz.

Decoupling capacitor placement strategies have become increasingly sophisticated to address the transient response requirements of GDDR7 memory. A multi-tiered approach utilizing various capacitor values (from nF to μF) at strategic locations helps maintain a low-impedance power delivery path across a wide frequency spectrum. This approach effectively dampens resonances in the PDN that could otherwise couple into signal paths.

Advanced termination schemes are necessary to minimize signal reflections in GDDR7 interfaces. Dynamic on-die termination (ODT) techniques adjust termination impedance based on operating conditions, optimizing signal quality while reducing power consumption. These adaptive termination methods are particularly valuable for managing the varying impedance characteristics encountered during different GDDR7 operating modes.

EMI compliance testing for GDDR7 systems requires sophisticated near-field and far-field measurement techniques. Pre-compliance testing during the development phase helps identify potential EMI hotspots before formal certification. Simulation tools that model both conducted and radiated emissions have become essential for predicting EMI performance before hardware implementation.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!