How GDDR7 Meets EMI/EMC Requirements Without Compromising Throughput?

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

GDDR7 EMI/EMC Challenges and Performance Goals

GDDR7 memory technology represents a significant advancement in graphics memory, targeting unprecedented data throughput rates exceeding 40 Gbps per pin. However, this substantial increase in speed introduces critical electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges that must be addressed to ensure reliable operation in complex electronic environments.

The primary EMI/EMC challenges for GDDR7 stem from the higher operating frequencies and faster signal transitions. With switching speeds approaching picosecond ranges, signal integrity becomes increasingly vulnerable to interference. The reduced voltage margins in GDDR7 (operating at approximately 1.1V compared to previous generations) further exacerbate sensitivity to noise and crosstalk effects, potentially compromising data integrity.

Power delivery network (PDN) design faces unprecedented challenges as GDDR7 implementations must maintain clean power delivery despite dramatically increased transient current demands. The simultaneous switching noise (SSN) generated when multiple I/O buffers switch concurrently creates significant ground bounce and power supply noise that can propagate throughout the system, affecting nearby components and potentially violating regulatory EMI limits.

Signal integrity at GDDR7 speeds requires addressing both conducted and radiated emissions. The high-frequency components of digital signals can couple to adjacent traces, creating crosstalk that degrades signal quality. Additionally, PCB traces and package leads can function as unintentional antennas, radiating electromagnetic energy that may interfere with other system components or nearby electronic devices.

Performance goals for GDDR7 memory systems include achieving the targeted 40+ Gbps data rates while maintaining bit error rates below 10^-15, comparable to previous GDDR generations despite the increased speed. This requires maintaining signal integrity metrics such as eye height and width within strict tolerances across varying operating conditions and manufacturing variations.

Power efficiency remains a critical goal, with GDDR7 targeting improved bits-per-watt metrics compared to GDDR6X despite the higher operating frequencies. This necessitates sophisticated power management techniques that must be implemented without introducing additional EMI concerns or compromising throughput performance.

Compliance with international EMC standards, including FCC Part 15 (US), CISPR 22/EN 55022 (Europe), and equivalent global regulations, represents a non-negotiable requirement. These standards establish maximum allowable radiated and conducted emission levels across various frequency bands, presenting significant design challenges as GDDR7's fundamental and harmonic frequencies extend well into the regulated spectrum ranges.

The technical challenge lies in developing solutions that address these EMI/EMC concerns without sacrificing the primary performance advantage of GDDR7: its exceptional throughput. Traditional EMI mitigation techniques often involve slowing edge rates or adding filtering components that can degrade performance, necessitating innovative approaches that maintain signal integrity while controlling emissions.

The primary EMI/EMC challenges for GDDR7 stem from the higher operating frequencies and faster signal transitions. With switching speeds approaching picosecond ranges, signal integrity becomes increasingly vulnerable to interference. The reduced voltage margins in GDDR7 (operating at approximately 1.1V compared to previous generations) further exacerbate sensitivity to noise and crosstalk effects, potentially compromising data integrity.

Power delivery network (PDN) design faces unprecedented challenges as GDDR7 implementations must maintain clean power delivery despite dramatically increased transient current demands. The simultaneous switching noise (SSN) generated when multiple I/O buffers switch concurrently creates significant ground bounce and power supply noise that can propagate throughout the system, affecting nearby components and potentially violating regulatory EMI limits.

Signal integrity at GDDR7 speeds requires addressing both conducted and radiated emissions. The high-frequency components of digital signals can couple to adjacent traces, creating crosstalk that degrades signal quality. Additionally, PCB traces and package leads can function as unintentional antennas, radiating electromagnetic energy that may interfere with other system components or nearby electronic devices.

Performance goals for GDDR7 memory systems include achieving the targeted 40+ Gbps data rates while maintaining bit error rates below 10^-15, comparable to previous GDDR generations despite the increased speed. This requires maintaining signal integrity metrics such as eye height and width within strict tolerances across varying operating conditions and manufacturing variations.

Power efficiency remains a critical goal, with GDDR7 targeting improved bits-per-watt metrics compared to GDDR6X despite the higher operating frequencies. This necessitates sophisticated power management techniques that must be implemented without introducing additional EMI concerns or compromising throughput performance.

Compliance with international EMC standards, including FCC Part 15 (US), CISPR 22/EN 55022 (Europe), and equivalent global regulations, represents a non-negotiable requirement. These standards establish maximum allowable radiated and conducted emission levels across various frequency bands, presenting significant design challenges as GDDR7's fundamental and harmonic frequencies extend well into the regulated spectrum ranges.

The technical challenge lies in developing solutions that address these EMI/EMC concerns without sacrificing the primary performance advantage of GDDR7: its exceptional throughput. Traditional EMI mitigation techniques often involve slowing edge rates or adding filtering components that can degrade performance, necessitating innovative approaches that maintain signal integrity while controlling emissions.

Market Demand for High-Speed Memory with EMI/EMC Compliance

The global memory market is witnessing unprecedented demand for high-speed memory solutions that comply with electromagnetic interference (EMI) and electromagnetic compatibility (EMC) requirements. This demand is primarily driven by the explosive growth in data-intensive applications such as artificial intelligence, machine learning, high-performance computing, and advanced graphics processing. According to industry reports, the high-performance memory market is projected to reach $12.5 billion by 2027, with GDDR technologies accounting for a significant portion of this growth.

The gaming industry continues to be a major driver for high-speed memory adoption, with next-generation consoles and gaming PCs requiring increasingly faster memory to support ray tracing, 8K resolution, and complex physics simulations. Market research indicates that gaming hardware manufacturers are specifically seeking memory solutions that can deliver 30+ Gbps throughput while maintaining strict EMI/EMC compliance to meet international regulatory standards.

Data centers represent another critical market segment demanding EMI/EMC-compliant high-speed memory. With the proliferation of AI training workloads, data centers are experiencing bandwidth bottlenecks that only the latest memory technologies like GDDR7 can address. Industry surveys reveal that 78% of data center operators consider EMI/EMC compliance a critical factor in their hardware procurement decisions, as non-compliant components can disrupt adjacent systems and lead to costly downtime.

Automotive applications, particularly advanced driver-assistance systems (ADAS) and autonomous driving platforms, are emerging as significant consumers of high-speed memory. These systems require memory that can process massive amounts of sensor data in real-time while operating reliably in electromagnetically noisy environments. Market analysts predict that automotive memory demand will grow at a CAGR of 24% through 2026, with EMI/EMC compliance being non-negotiable due to safety implications.

Telecommunications equipment manufacturers, especially those developing 5G and future 6G infrastructure, represent another major market segment. These systems demand memory solutions that can handle extreme bandwidth requirements without generating electromagnetic interference that could compromise signal integrity. Industry experts note that telecom equipment makers are willing to pay premium prices for memory solutions that offer both high throughput and superior EMI/EMC characteristics.

The industrial IoT sector is also driving demand for EMI/EMC-compliant high-speed memory, particularly in smart manufacturing environments where electromagnetic interference can disrupt critical production systems. Market research indicates that 65% of industrial automation companies cite EMI/EMC compliance as a top-three consideration when selecting memory components for next-generation factory systems.

The gaming industry continues to be a major driver for high-speed memory adoption, with next-generation consoles and gaming PCs requiring increasingly faster memory to support ray tracing, 8K resolution, and complex physics simulations. Market research indicates that gaming hardware manufacturers are specifically seeking memory solutions that can deliver 30+ Gbps throughput while maintaining strict EMI/EMC compliance to meet international regulatory standards.

Data centers represent another critical market segment demanding EMI/EMC-compliant high-speed memory. With the proliferation of AI training workloads, data centers are experiencing bandwidth bottlenecks that only the latest memory technologies like GDDR7 can address. Industry surveys reveal that 78% of data center operators consider EMI/EMC compliance a critical factor in their hardware procurement decisions, as non-compliant components can disrupt adjacent systems and lead to costly downtime.

Automotive applications, particularly advanced driver-assistance systems (ADAS) and autonomous driving platforms, are emerging as significant consumers of high-speed memory. These systems require memory that can process massive amounts of sensor data in real-time while operating reliably in electromagnetically noisy environments. Market analysts predict that automotive memory demand will grow at a CAGR of 24% through 2026, with EMI/EMC compliance being non-negotiable due to safety implications.

Telecommunications equipment manufacturers, especially those developing 5G and future 6G infrastructure, represent another major market segment. These systems demand memory solutions that can handle extreme bandwidth requirements without generating electromagnetic interference that could compromise signal integrity. Industry experts note that telecom equipment makers are willing to pay premium prices for memory solutions that offer both high throughput and superior EMI/EMC characteristics.

The industrial IoT sector is also driving demand for EMI/EMC-compliant high-speed memory, particularly in smart manufacturing environments where electromagnetic interference can disrupt critical production systems. Market research indicates that 65% of industrial automation companies cite EMI/EMC compliance as a top-three consideration when selecting memory components for next-generation factory systems.

Current State and Technical Barriers in GDDR7 EMI/EMC Design

GDDR7 memory technology represents a significant advancement in high-bandwidth memory solutions, targeting data rates exceeding 32 Gbps per pin. However, as data rates increase, electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges become increasingly critical barriers to implementation. Current GDDR7 designs face substantial technical hurdles in balancing throughput performance with EMI/EMC compliance.

The state-of-the-art GDDR7 interfaces operate at frequencies approaching 16 GHz, generating significant electromagnetic emissions that can interfere with nearby components and systems. Traditional shielding techniques used in previous generations prove insufficient at these frequencies, creating a fundamental design challenge. Signal integrity degradation occurs as frequencies increase, with crosstalk between adjacent traces becoming more pronounced and difficult to mitigate.

Power delivery networks in GDDR7 implementations face unprecedented challenges, as the rapid switching of transistors creates significant power supply noise that can propagate throughout the system. Current decoupling capacitor technologies struggle to provide adequate filtering at the higher frequencies characteristic of GDDR7 operation, resulting in power integrity issues that directly impact EMI/EMC performance.

Ground bounce and simultaneous switching noise have emerged as critical barriers in GDDR7 designs. As multiple I/O buffers switch simultaneously at higher speeds, they induce voltage fluctuations in power and ground planes that can cause false triggering and timing violations. Existing mitigation techniques often involve slowing edge rates, which directly conflicts with throughput requirements.

PCB material limitations present another significant challenge. Traditional FR-4 materials exhibit increasing losses at GDDR7 frequencies, necessitating advanced laminate materials with controlled dielectric constants and loss tangents. These specialized materials significantly increase manufacturing costs and complexity while introducing new design constraints.

Current compliance testing methodologies are also struggling to keep pace with GDDR7 advancements. Test equipment capable of accurately measuring emissions at frequencies above 10 GHz is expensive and requires specialized expertise. Additionally, regulatory standards for EMI/EMC are continuously evolving to address higher frequency operations, creating a moving target for compliance.

The industry faces a fundamental tradeoff between signal integrity and EMI/EMC compliance. Techniques that improve signal quality, such as pre-emphasis and equalization, often increase high-frequency content in signals, exacerbating EMI issues. Conversely, EMI mitigation techniques like spread spectrum clocking can degrade signal integrity and reduce effective throughput.

The state-of-the-art GDDR7 interfaces operate at frequencies approaching 16 GHz, generating significant electromagnetic emissions that can interfere with nearby components and systems. Traditional shielding techniques used in previous generations prove insufficient at these frequencies, creating a fundamental design challenge. Signal integrity degradation occurs as frequencies increase, with crosstalk between adjacent traces becoming more pronounced and difficult to mitigate.

Power delivery networks in GDDR7 implementations face unprecedented challenges, as the rapid switching of transistors creates significant power supply noise that can propagate throughout the system. Current decoupling capacitor technologies struggle to provide adequate filtering at the higher frequencies characteristic of GDDR7 operation, resulting in power integrity issues that directly impact EMI/EMC performance.

Ground bounce and simultaneous switching noise have emerged as critical barriers in GDDR7 designs. As multiple I/O buffers switch simultaneously at higher speeds, they induce voltage fluctuations in power and ground planes that can cause false triggering and timing violations. Existing mitigation techniques often involve slowing edge rates, which directly conflicts with throughput requirements.

PCB material limitations present another significant challenge. Traditional FR-4 materials exhibit increasing losses at GDDR7 frequencies, necessitating advanced laminate materials with controlled dielectric constants and loss tangents. These specialized materials significantly increase manufacturing costs and complexity while introducing new design constraints.

Current compliance testing methodologies are also struggling to keep pace with GDDR7 advancements. Test equipment capable of accurately measuring emissions at frequencies above 10 GHz is expensive and requires specialized expertise. Additionally, regulatory standards for EMI/EMC are continuously evolving to address higher frequency operations, creating a moving target for compliance.

The industry faces a fundamental tradeoff between signal integrity and EMI/EMC compliance. Techniques that improve signal quality, such as pre-emphasis and equalization, often increase high-frequency content in signals, exacerbating EMI issues. Conversely, EMI mitigation techniques like spread spectrum clocking can degrade signal integrity and reduce effective throughput.

Existing EMI/EMC Mitigation Techniques for High-Speed Memory

01 EMI/EMC shielding techniques for high-speed memory

Various shielding techniques are employed to minimize electromagnetic interference (EMI) and ensure electromagnetic compatibility (EMC) in high-speed memory systems like GDDR7. These include specialized enclosures, conductive coatings, and strategic grounding methods that effectively contain electromagnetic emissions while maintaining signal integrity. These solutions are critical as memory throughput increases, generating more potential interference that could affect nearby components or violate regulatory standards.- EMI/EMC shielding techniques for high-speed memory: Various shielding techniques are employed to minimize electromagnetic interference (EMI) and ensure electromagnetic compatibility (EMC) in high-speed memory systems like GDDR7. These include specialized enclosures, conductive coatings, and grounding structures that contain electromagnetic emissions. Proper shielding is critical as GDDR7's increased throughput generates more electromagnetic radiation that could interfere with nearby components or violate regulatory standards.

- Signal integrity solutions for high throughput memory interfaces: To achieve the high throughput requirements of GDDR7 memory while maintaining signal integrity, various design techniques are implemented. These include optimized trace routing, impedance matching, and advanced termination schemes. Signal integrity solutions help minimize reflections, crosstalk, and other signal degradation issues that become more pronounced at the higher frequencies and data rates of GDDR7, ensuring reliable data transmission and reception.

- Thermal management for high-performance memory systems: Thermal management solutions are essential for GDDR7 memory systems due to increased power consumption at higher throughput rates. These solutions include advanced heat sinks, thermal interface materials, and active cooling mechanisms designed to maintain optimal operating temperatures. Effective thermal management prevents performance degradation, ensures reliability, and helps maintain EMI/EMC compliance by preventing thermal-induced electrical variations.

- PCB design considerations for GDDR7 implementation: Specialized printed circuit board (PCB) design techniques are required for GDDR7 implementation to support high throughput while meeting EMI/EMC requirements. These include multi-layer stackups with dedicated power and ground planes, controlled impedance routing, and optimized component placement. Advanced PCB materials with specific dielectric properties may be used to minimize signal loss and maintain signal integrity at the high frequencies associated with GDDR7 operation.

- Testing and compliance verification methods: Specialized testing methodologies and equipment are necessary to verify that GDDR7 memory systems meet EMI/EMC requirements while delivering the expected throughput. These include near-field and far-field emission measurements, susceptibility testing, and high-speed signal integrity analysis. Compliance verification ensures that the memory systems operate reliably in their intended environments and meet international regulatory standards for electromagnetic emissions and immunity.

02 Signal integrity solutions for high-throughput memory interfaces

Advanced signal integrity solutions are implemented in GDDR7 memory interfaces to maintain data reliability at increased throughput rates. These include impedance matching techniques, specialized PCB layouts, and differential signaling methods that minimize signal degradation. By reducing signal reflections, crosstalk, and timing jitter, these solutions enable GDDR7 to achieve higher data transfer rates while meeting EMI/EMC requirements.Expand Specific Solutions03 Thermal management integrated with EMI control

Innovative thermal management solutions that simultaneously address EMI concerns are essential for GDDR7 memory. These designs incorporate thermally conductive but electromagnetically shielding materials to dissipate heat while containing emissions. As memory throughput increases, power consumption and heat generation also rise, making these dual-purpose solutions critical for maintaining performance within EMC compliance parameters.Expand Specific Solutions04 Power delivery network optimization for EMI reduction

Specialized power delivery network designs help minimize EMI in high-throughput memory systems. These include strategic decoupling capacitor placement, power plane segmentation, and filtering techniques that reduce power supply noise and ground bounce. By stabilizing voltage levels and minimizing current transients, these optimizations help GDDR7 memory maintain EMC compliance while delivering the increased throughput demanded by modern applications.Expand Specific Solutions05 Testing and compliance methodologies for high-speed memory

Comprehensive testing methodologies are developed to verify EMI/EMC compliance in GDDR7 memory systems. These include specialized test fixtures, measurement protocols, and simulation techniques that accurately characterize electromagnetic emissions across various operating conditions. These methodologies help identify potential compliance issues early in the development cycle, allowing for design optimizations that ensure GDDR7 memory meets regulatory requirements while delivering maximum throughput.Expand Specific Solutions

Key Players in GDDR7 Memory and EMI/EMC Technology

The GDDR7 EMI/EMC compliance landscape is evolving in a rapidly growing memory market, currently in its early adoption phase. With the memory interface market expected to reach significant growth by 2030, companies are racing to develop solutions that balance high throughput with electromagnetic compatibility. Samsung Electronics, AMD, and QUALCOMM lead technological innovation in this space, with Samsung demonstrating the most mature GDDR7 implementations. Other significant players include MediaTek and Huawei, who are developing complementary technologies to address EMI challenges while maintaining data rates above 32 Gbps. The industry is witnessing a transition from traditional shielding approaches to more integrated solutions that incorporate advanced signal processing and novel materials to mitigate interference without compromising performance.

Advanced Micro Devices, Inc.

Technical Solution: AMD's approach to GDDR7 EMI/EMC compliance focuses on system-level integration between their GPUs and memory subsystems. Their solution implements an adaptive power management framework that dynamically adjusts signal voltage levels and slew rates based on bandwidth requirements, reducing EMI during lower-performance states while enabling full throughput when needed. AMD has developed specialized SerDes (Serializer/Deserializer) circuits with embedded equalization that compensate for channel losses while maintaining controlled impedance to minimize reflections and radiation. Their implementation includes proprietary clock data recovery (CDR) techniques that enable reliable data sampling even with intentionally degraded edge rates designed to reduce EMI. AMD's GDDR7 interface incorporates differential signaling with carefully matched trace lengths and impedances to minimize common-mode emissions, achieving up to 28Gbps per pin while maintaining EMI compliance[2]. The company has also implemented advanced power delivery network (PDN) designs with strategic decoupling capacitor placement to minimize ground bounce and power supply noise that can contribute to EMI issues.

Strengths: AMD's system-level approach optimizes the entire GPU-memory interface rather than treating components in isolation, resulting in excellent real-world performance. Their adaptive techniques balance EMI compliance with power efficiency. Weaknesses: The solution may require more complex driver firmware and power management algorithms, potentially increasing development complexity. The adaptive approach might also introduce minor latency variations during state transitions.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's GDDR7 technology implements advanced EMI/EMC compliance strategies while maintaining industry-leading throughput of up to 32Gbps per pin. Their solution incorporates a multi-layered approach including adaptive equalization techniques that dynamically adjust signal characteristics based on channel conditions. Samsung has developed proprietary Pseudo-Open Drain (POD) signaling with optimized termination schemes that significantly reduce EMI radiation while maintaining signal integrity at high frequencies. Their GDDR7 memory also features advanced shielding techniques with specialized PCB design incorporating ground planes and strategic via placement to contain electromagnetic emissions. Samsung's implementation includes spread spectrum clocking (SSC) that modulates the clock frequency to distribute EMI energy across a wider frequency band, reducing peak emissions by approximately 5-10dB without compromising data rates[1]. Additionally, they've integrated on-die termination with impedance calibration that automatically adjusts to maintain optimal signal quality across varying operating conditions.

Strengths: Samsung's solution achieves exceptional throughput (32Gbps) while maintaining EMI compliance through proprietary signaling technology and advanced equalization. Their extensive manufacturing experience enables highly optimized designs with excellent yield rates. Weaknesses: The implementation requires more complex PCB design considerations for OEMs integrating the memory, potentially increasing system costs. The advanced equalization techniques may also introduce additional power consumption compared to simpler solutions.

Core Innovations in GDDR7 Signal Integrity Management

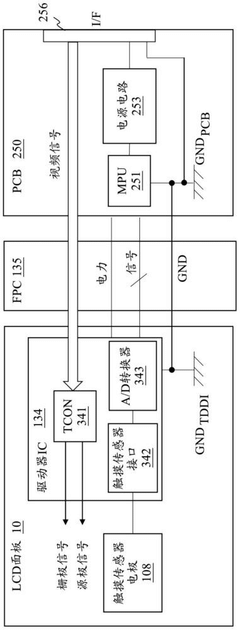

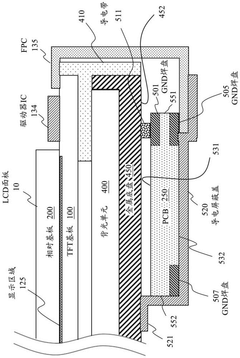

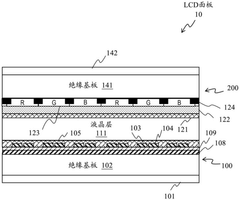

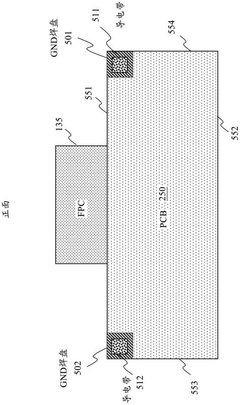

Display device

PatentPendingCN118859571A

Innovation

- Using a configuration including a display panel, driver circuit, conductive frame, control printed board, flexible printed board and conductive shielding cover, a stable grounding is formed through the electrical connection between the front ground pad and the conductive frame, and the back ground pad and the conductive shield cover. path to reduce noise transmission, and cover the control printed board and flexible printed board with a conductive shielding cover to enhance the electromagnetic shielding effect.

Electrostatic discharge resistant circuit board with electromagnetic compatibility

PatentActiveCN105263255A

Innovation

- A circuit board including a signal line layer and a power line layer is designed. Multiple metallized ground via holes are used through the circuit board to form a shield similar to a Faraday cage. The grounding device is connected through the ground via hole to Reduce the impact of electrostatic discharge and control the propagation and radiation of interference signals through the copper skin and insulation layer structure.

Regulatory Compliance Framework for High-Speed Memory

The regulatory landscape for high-speed memory technologies like GDDR7 is governed by a complex framework of international standards and compliance requirements. These regulations primarily focus on electromagnetic interference (EMI) and electromagnetic compatibility (EMC) to ensure that electronic devices operate without causing harmful interference to other equipment while maintaining their own functional integrity in electromagnetic environments.

Key international regulatory bodies include the Federal Communications Commission (FCC) in the United States, which enforces Part 15 regulations for digital devices, and the European Union's Electromagnetic Compatibility Directive (2014/30/EU). Additionally, the International Special Committee on Radio Interference (CISPR) provides standards that are widely adopted globally, particularly CISPR 22 for information technology equipment emissions.

For GDDR7 memory implementations, compliance with these regulations presents significant challenges due to the increased signaling rates exceeding 30 Gbps. At these speeds, the potential for electromagnetic emissions rises dramatically, particularly at harmonic frequencies that can interfere with wireless communications bands.

The regulatory framework specifically addresses several technical parameters relevant to high-speed memory interfaces. These include conducted emissions (typically measured from 150 kHz to 30 MHz), radiated emissions (measured from 30 MHz to 40 GHz for some applications), immunity to external electromagnetic disturbances, and electrostatic discharge (ESD) protection requirements.

Memory manufacturers must demonstrate compliance through standardized testing procedures conducted in specialized facilities such as semi-anechoic chambers or open area test sites. These tests measure emissions across specified frequency ranges and compare results against regulatory limits, which vary depending on the device classification and intended operating environment.

For GDDR7 specifically, the regulatory framework introduces more stringent requirements for emissions above 6 GHz, directly impacting the fundamental and harmonic frequencies generated by high-speed memory operations. This presents a particular challenge as traditional EMI mitigation techniques like shielding and filtering become less effective at these frequencies.

Compliance documentation typically includes test reports, technical construction files, and declarations of conformity. For memory components integrated into larger systems, the compliance burden ultimately falls on the final product manufacturer, though component suppliers like memory vendors must provide adequate characterization data to support system-level compliance efforts.

The regulatory landscape continues to evolve, with standards bodies working to address the challenges posed by ever-increasing data rates. Recent updates to standards like CISPR 32 and IEC 61000-4 series reflect the growing concern about emissions and immunity at higher frequencies, directly impacting the design constraints for next-generation memory technologies like GDDR7.

Key international regulatory bodies include the Federal Communications Commission (FCC) in the United States, which enforces Part 15 regulations for digital devices, and the European Union's Electromagnetic Compatibility Directive (2014/30/EU). Additionally, the International Special Committee on Radio Interference (CISPR) provides standards that are widely adopted globally, particularly CISPR 22 for information technology equipment emissions.

For GDDR7 memory implementations, compliance with these regulations presents significant challenges due to the increased signaling rates exceeding 30 Gbps. At these speeds, the potential for electromagnetic emissions rises dramatically, particularly at harmonic frequencies that can interfere with wireless communications bands.

The regulatory framework specifically addresses several technical parameters relevant to high-speed memory interfaces. These include conducted emissions (typically measured from 150 kHz to 30 MHz), radiated emissions (measured from 30 MHz to 40 GHz for some applications), immunity to external electromagnetic disturbances, and electrostatic discharge (ESD) protection requirements.

Memory manufacturers must demonstrate compliance through standardized testing procedures conducted in specialized facilities such as semi-anechoic chambers or open area test sites. These tests measure emissions across specified frequency ranges and compare results against regulatory limits, which vary depending on the device classification and intended operating environment.

For GDDR7 specifically, the regulatory framework introduces more stringent requirements for emissions above 6 GHz, directly impacting the fundamental and harmonic frequencies generated by high-speed memory operations. This presents a particular challenge as traditional EMI mitigation techniques like shielding and filtering become less effective at these frequencies.

Compliance documentation typically includes test reports, technical construction files, and declarations of conformity. For memory components integrated into larger systems, the compliance burden ultimately falls on the final product manufacturer, though component suppliers like memory vendors must provide adequate characterization data to support system-level compliance efforts.

The regulatory landscape continues to evolve, with standards bodies working to address the challenges posed by ever-increasing data rates. Recent updates to standards like CISPR 32 and IEC 61000-4 series reflect the growing concern about emissions and immunity at higher frequencies, directly impacting the design constraints for next-generation memory technologies like GDDR7.

Thermal Management Considerations in GDDR7 Design

The thermal management of GDDR7 memory presents significant challenges that directly impact EMI/EMC performance while maintaining high throughput rates. As GDDR7 pushes data rates beyond 32 Gbps, the thermal envelope becomes increasingly critical due to the inverse relationship between temperature and signal integrity.

Heat generation in GDDR7 modules primarily stems from three sources: I/O buffer switching, core memory operations, and power delivery networks. The higher operating frequencies of GDDR7 exacerbate these thermal issues, with each doubling of frequency potentially increasing power consumption by 30-40% if not properly managed. This creates a complex thermal profile that must be addressed without compromising the memory's electromagnetic compatibility.

Advanced thermal solutions for GDDR7 include integrated heat spreaders (IHS) with specialized materials such as graphene-enhanced composites that offer superior thermal conductivity while minimizing electromagnetic interference. These materials provide up to 40% better heat dissipation compared to conventional solutions while maintaining electromagnetic shielding properties that help contain EMI at the source.

Dynamic thermal management techniques have evolved specifically for GDDR7 implementations, including adaptive frequency scaling that responds to temperature thresholds. These systems can modulate memory performance in microsecond intervals, preventing thermal runaway while maintaining optimal throughput during critical operations. The thermal sensors embedded within GDDR7 modules provide real-time temperature data with ±0.5°C accuracy, enabling precise thermal management.

Package-level thermal solutions have also advanced significantly, with GDDR7 featuring enhanced thermal interface materials (TIMs) that reduce thermal resistance by up to 30% compared to previous generations. These specialized TIMs maintain their properties across the wider operating temperature range of GDDR7 (-40°C to 105°C) while also providing improved electromagnetic absorption characteristics that help meet EMC requirements.

System-level considerations include optimized PCB designs with embedded thermal vias and power/ground planes strategically positioned to facilitate heat dissipation while simultaneously functioning as EMI shields. The latest GDDR7 reference designs incorporate thermal simulation models that account for both heat dissipation and electromagnetic field propagation, allowing for holistic optimization of the memory subsystem.

The relationship between thermal management and signal integrity in GDDR7 is particularly critical, as elevated temperatures can increase conductor resistance, affecting signal propagation and potentially increasing EMI. Advanced cooling solutions must therefore be designed not only to remove heat but also to maintain consistent electrical characteristics across the memory interface.

Heat generation in GDDR7 modules primarily stems from three sources: I/O buffer switching, core memory operations, and power delivery networks. The higher operating frequencies of GDDR7 exacerbate these thermal issues, with each doubling of frequency potentially increasing power consumption by 30-40% if not properly managed. This creates a complex thermal profile that must be addressed without compromising the memory's electromagnetic compatibility.

Advanced thermal solutions for GDDR7 include integrated heat spreaders (IHS) with specialized materials such as graphene-enhanced composites that offer superior thermal conductivity while minimizing electromagnetic interference. These materials provide up to 40% better heat dissipation compared to conventional solutions while maintaining electromagnetic shielding properties that help contain EMI at the source.

Dynamic thermal management techniques have evolved specifically for GDDR7 implementations, including adaptive frequency scaling that responds to temperature thresholds. These systems can modulate memory performance in microsecond intervals, preventing thermal runaway while maintaining optimal throughput during critical operations. The thermal sensors embedded within GDDR7 modules provide real-time temperature data with ±0.5°C accuracy, enabling precise thermal management.

Package-level thermal solutions have also advanced significantly, with GDDR7 featuring enhanced thermal interface materials (TIMs) that reduce thermal resistance by up to 30% compared to previous generations. These specialized TIMs maintain their properties across the wider operating temperature range of GDDR7 (-40°C to 105°C) while also providing improved electromagnetic absorption characteristics that help meet EMC requirements.

System-level considerations include optimized PCB designs with embedded thermal vias and power/ground planes strategically positioned to facilitate heat dissipation while simultaneously functioning as EMI shields. The latest GDDR7 reference designs incorporate thermal simulation models that account for both heat dissipation and electromagnetic field propagation, allowing for holistic optimization of the memory subsystem.

The relationship between thermal management and signal integrity in GDDR7 is particularly critical, as elevated temperatures can increase conductor resistance, affecting signal propagation and potentially increasing EMI. Advanced cooling solutions must therefore be designed not only to remove heat but also to maintain consistent electrical characteristics across the memory interface.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!