How to Assess DDR5 Compatibility in Quantum Computing Environments

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Integration in Quantum Computing: Background and Objectives

The integration of DDR5 memory technology into quantum computing systems represents a significant frontier in advanced computing architecture. Quantum computing has evolved from theoretical concepts to practical implementations over the past decades, with recent breakthroughs enabling more stable qubits and longer coherence times. Simultaneously, memory technologies have progressed to DDR5, offering unprecedented bandwidth and efficiency improvements over previous generations. The convergence of these technologies presents both opportunities and challenges that require thorough investigation.

The primary objective of this technical exploration is to establish comprehensive assessment methodologies for DDR5 compatibility within quantum computing environments. This includes evaluating the unique electromagnetic interference concerns, thermal management requirements, and timing synchronization challenges that arise when integrating high-speed memory with quantum processing units operating at near-absolute zero temperatures.

Historical context is essential for understanding this integration challenge. Classical computing architectures have traditionally separated memory and processing units, with standardized interfaces facilitating communication. Quantum computing fundamentally disrupts this paradigm through its reliance on quantum states that cannot be transferred using conventional data buses. The evolution of both technologies has been largely independent, with quantum computing focusing on qubit stability and DDR5 development prioritizing bandwidth and power efficiency for classical systems.

Current quantum computing systems typically employ specialized memory solutions designed for cryogenic environments, often sacrificing performance for reliability. The potential introduction of DDR5 technology could dramatically enhance data transfer rates between quantum processors and classical control systems, potentially addressing one of the key bottlenecks in scaling quantum computing capabilities.

Market trends indicate growing investment in quantum-classical hybrid architectures, where high-performance classical components work alongside quantum processing units. This hybrid approach necessitates memory solutions that can efficiently bridge these disparate computing paradigms while maintaining the integrity of quantum operations.

Technical objectives for DDR5 integration include developing interface protocols that minimize decoherence effects, designing signal integrity solutions for the extreme temperature differentials, and creating testing methodologies that can accurately predict compatibility without requiring full system implementation. Additionally, power delivery networks must be optimized to prevent electromagnetic interference with sensitive quantum states.

The long-term vision encompasses creating standardized assessment frameworks that enable quantum computing manufacturers to evaluate and implement DDR5 memory solutions with predictable performance characteristics and reliability metrics, ultimately accelerating the development of practical quantum computing systems with enhanced classical data handling capabilities.

The primary objective of this technical exploration is to establish comprehensive assessment methodologies for DDR5 compatibility within quantum computing environments. This includes evaluating the unique electromagnetic interference concerns, thermal management requirements, and timing synchronization challenges that arise when integrating high-speed memory with quantum processing units operating at near-absolute zero temperatures.

Historical context is essential for understanding this integration challenge. Classical computing architectures have traditionally separated memory and processing units, with standardized interfaces facilitating communication. Quantum computing fundamentally disrupts this paradigm through its reliance on quantum states that cannot be transferred using conventional data buses. The evolution of both technologies has been largely independent, with quantum computing focusing on qubit stability and DDR5 development prioritizing bandwidth and power efficiency for classical systems.

Current quantum computing systems typically employ specialized memory solutions designed for cryogenic environments, often sacrificing performance for reliability. The potential introduction of DDR5 technology could dramatically enhance data transfer rates between quantum processors and classical control systems, potentially addressing one of the key bottlenecks in scaling quantum computing capabilities.

Market trends indicate growing investment in quantum-classical hybrid architectures, where high-performance classical components work alongside quantum processing units. This hybrid approach necessitates memory solutions that can efficiently bridge these disparate computing paradigms while maintaining the integrity of quantum operations.

Technical objectives for DDR5 integration include developing interface protocols that minimize decoherence effects, designing signal integrity solutions for the extreme temperature differentials, and creating testing methodologies that can accurately predict compatibility without requiring full system implementation. Additionally, power delivery networks must be optimized to prevent electromagnetic interference with sensitive quantum states.

The long-term vision encompasses creating standardized assessment frameworks that enable quantum computing manufacturers to evaluate and implement DDR5 memory solutions with predictable performance characteristics and reliability metrics, ultimately accelerating the development of practical quantum computing systems with enhanced classical data handling capabilities.

Market Analysis for Quantum-Compatible Memory Solutions

The quantum computing memory solutions market is experiencing unprecedented growth, driven by the increasing adoption of quantum technologies across various sectors. Current market valuations indicate that quantum computing hardware, including memory components, reached approximately $500 million in 2022, with projections suggesting a compound annual growth rate of 25-30% through 2030. Memory solutions specifically designed for quantum environments represent an emerging segment within this broader market.

Customer demand for quantum-compatible memory solutions stems primarily from research institutions, government agencies, and technology corporations investing heavily in quantum computing infrastructure. These organizations require memory systems that can effectively interface between classical and quantum computing elements while maintaining data integrity under extreme operating conditions. The demand is particularly strong in sectors focusing on cryptography, material science, pharmaceutical research, and financial modeling.

Market research indicates that early adopters of quantum-compatible DDR5 solutions are willing to pay premium prices for memory systems that demonstrate reliable performance in quantum environments. This price elasticity creates significant profit opportunities for first-movers in the space, with potential gross margins exceeding 60% for specialized quantum memory products.

Regional analysis shows North America leading the market with approximately 45% share, followed by Europe at 30% and Asia-Pacific at 20%. China's national quantum initiative is rapidly accelerating demand in the Asia-Pacific region, potentially shifting market dynamics within the next five years.

The competitive landscape remains relatively unconsolidated, with specialized quantum hardware providers competing alongside traditional memory manufacturers entering the quantum space. This fragmentation presents opportunities for strategic partnerships and acquisitions as the market matures. Industry analysts have identified over 25 companies actively developing quantum-compatible memory solutions, though fewer than 10 have commercially viable products.

Customer pain points center around three key areas: thermal management challenges in cryogenic environments, error rates at quantum-classical interfaces, and integration complexity with existing quantum systems. Solutions addressing these specific challenges command significant market premiums and enjoy accelerated adoption rates.

Market forecasts suggest that quantum-compatible memory solutions will reach a critical inflection point around 2025-2026, when quantum advantage demonstrations in specific applications drive increased commercial adoption beyond research environments. This transition will likely expand the addressable market by 3-4 times its current size, creating substantial growth opportunities for well-positioned providers of DDR5 solutions optimized for quantum computing environments.

Customer demand for quantum-compatible memory solutions stems primarily from research institutions, government agencies, and technology corporations investing heavily in quantum computing infrastructure. These organizations require memory systems that can effectively interface between classical and quantum computing elements while maintaining data integrity under extreme operating conditions. The demand is particularly strong in sectors focusing on cryptography, material science, pharmaceutical research, and financial modeling.

Market research indicates that early adopters of quantum-compatible DDR5 solutions are willing to pay premium prices for memory systems that demonstrate reliable performance in quantum environments. This price elasticity creates significant profit opportunities for first-movers in the space, with potential gross margins exceeding 60% for specialized quantum memory products.

Regional analysis shows North America leading the market with approximately 45% share, followed by Europe at 30% and Asia-Pacific at 20%. China's national quantum initiative is rapidly accelerating demand in the Asia-Pacific region, potentially shifting market dynamics within the next five years.

The competitive landscape remains relatively unconsolidated, with specialized quantum hardware providers competing alongside traditional memory manufacturers entering the quantum space. This fragmentation presents opportunities for strategic partnerships and acquisitions as the market matures. Industry analysts have identified over 25 companies actively developing quantum-compatible memory solutions, though fewer than 10 have commercially viable products.

Customer pain points center around three key areas: thermal management challenges in cryogenic environments, error rates at quantum-classical interfaces, and integration complexity with existing quantum systems. Solutions addressing these specific challenges command significant market premiums and enjoy accelerated adoption rates.

Market forecasts suggest that quantum-compatible memory solutions will reach a critical inflection point around 2025-2026, when quantum advantage demonstrations in specific applications drive increased commercial adoption beyond research environments. This transition will likely expand the addressable market by 3-4 times its current size, creating substantial growth opportunities for well-positioned providers of DDR5 solutions optimized for quantum computing environments.

Current Challenges in DDR5-Quantum System Integration

The integration of DDR5 memory with quantum computing systems presents significant technical challenges that require innovative solutions. Current quantum computing architectures operate under extreme conditions, including near-absolute zero temperatures and highly controlled electromagnetic environments, which are fundamentally incompatible with conventional DDR5 memory systems designed for classical computing environments.

One primary challenge is the thermal management discrepancy. Quantum processors typically operate at millikelvin temperatures, while DDR5 memory generates considerable heat during operation. This thermal incompatibility necessitates complex isolation systems and thermal barriers that add significant engineering complexity to quantum computing systems incorporating DDR5 memory components.

Signal integrity issues represent another critical obstacle. Quantum states are extremely fragile and susceptible to decoherence from electromagnetic interference. DDR5's high-frequency operations (up to 6400 MT/s) generate electromagnetic fields that can potentially disrupt quantum coherence, requiring sophisticated shielding solutions and signal isolation techniques that have not been fully developed for quantum-classical interfaces.

The architectural integration challenge stems from fundamental differences in data processing paradigms. Quantum computers process information using qubits that exist in superposition states, while DDR5 memory is designed for deterministic binary data storage. Creating effective translation layers between these disparate computing models remains an unsolved technical problem, particularly at scale where quantum advantage becomes meaningful.

Power delivery networks present additional complications. DDR5 memory requires precise voltage regulation (typically ±3% tolerance), while quantum systems demand extraordinarily stable power supplies with noise levels in the nanovolt range. Current power conditioning technologies struggle to bridge this gap effectively without introducing additional noise sources that could compromise quantum operations.

Latency considerations further complicate integration efforts. Quantum algorithms often require real-time classical processing of measurement results for error correction and algorithm steering. DDR5 memory, despite its improvements over previous generations, still introduces latency that may exceed the coherence time of quantum systems, potentially limiting the practical implementation of error correction protocols.

Standardization remains underdeveloped in this intersection of technologies. While DDR5 specifications are well-established through JEDEC standards, the quantum-classical interface lacks comparable standardization, creating interoperability challenges for system designers attempting to incorporate DDR5 memory into quantum computing architectures.

One primary challenge is the thermal management discrepancy. Quantum processors typically operate at millikelvin temperatures, while DDR5 memory generates considerable heat during operation. This thermal incompatibility necessitates complex isolation systems and thermal barriers that add significant engineering complexity to quantum computing systems incorporating DDR5 memory components.

Signal integrity issues represent another critical obstacle. Quantum states are extremely fragile and susceptible to decoherence from electromagnetic interference. DDR5's high-frequency operations (up to 6400 MT/s) generate electromagnetic fields that can potentially disrupt quantum coherence, requiring sophisticated shielding solutions and signal isolation techniques that have not been fully developed for quantum-classical interfaces.

The architectural integration challenge stems from fundamental differences in data processing paradigms. Quantum computers process information using qubits that exist in superposition states, while DDR5 memory is designed for deterministic binary data storage. Creating effective translation layers between these disparate computing models remains an unsolved technical problem, particularly at scale where quantum advantage becomes meaningful.

Power delivery networks present additional complications. DDR5 memory requires precise voltage regulation (typically ±3% tolerance), while quantum systems demand extraordinarily stable power supplies with noise levels in the nanovolt range. Current power conditioning technologies struggle to bridge this gap effectively without introducing additional noise sources that could compromise quantum operations.

Latency considerations further complicate integration efforts. Quantum algorithms often require real-time classical processing of measurement results for error correction and algorithm steering. DDR5 memory, despite its improvements over previous generations, still introduces latency that may exceed the coherence time of quantum systems, potentially limiting the practical implementation of error correction protocols.

Standardization remains underdeveloped in this intersection of technologies. While DDR5 specifications are well-established through JEDEC standards, the quantum-classical interface lacks comparable standardization, creating interoperability challenges for system designers attempting to incorporate DDR5 memory into quantum computing architectures.

Existing DDR5 Compatibility Assessment Methodologies

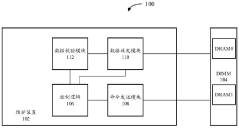

01 DDR5 Memory Controller Compatibility

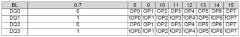

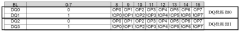

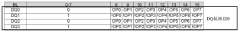

Memory controllers designed specifically for DDR5 technology ensure proper communication between the processor and memory modules. These controllers implement the necessary protocols and timing parameters to support DDR5's higher speeds and different power management features. Advanced memory controllers may include compatibility modes to support both DDR4 and DDR5 memory types, allowing for smoother transition between memory generations in computing systems.- DDR5 memory compatibility with motherboards and processors: DDR5 memory modules require specific motherboard designs and processor generations that support the new memory standard. These patents describe technologies that ensure compatibility between DDR5 memory and various motherboard architectures, including detection mechanisms that identify memory type and adjust system parameters accordingly. The innovations focus on interface designs that accommodate the higher speeds and different power requirements of DDR5 while maintaining backward compatibility options.

- DDR5 signal integrity and power management solutions: These inventions address the signal integrity challenges and power management requirements specific to DDR5 memory. The technologies include advanced voltage regulation modules (VRMs) integrated directly onto DDR5 memory modules, improved power delivery networks, and signal conditioning techniques that maintain data integrity at higher frequencies. Solutions for managing the increased power demands and thermal considerations of DDR5 memory are also covered.

- DDR5 memory controller architecture and optimization: These patents focus on memory controller designs specifically optimized for DDR5 operation. The innovations include new command scheduling algorithms, improved data bus utilization techniques, and memory timing parameter optimization. The controller architectures address the increased complexity of DDR5 memory operations, including support for multiple independent channels, enhanced refresh mechanisms, and new power management states unique to the DDR5 specification.

- DDR5 memory module physical design and interconnection: These inventions relate to the physical design aspects of DDR5 memory modules, including connector layouts, pin assignments, and mechanical form factors. The technologies address challenges in maintaining signal integrity through improved PCB designs, optimized trace routing, and enhanced cooling solutions. Some patents cover innovative socket designs that accommodate the increased pin count and different electrical characteristics of DDR5 modules while ensuring proper mechanical alignment and connection reliability.

- DDR5 compatibility testing and validation methods: These patents describe specialized testing methodologies and validation procedures for ensuring DDR5 memory compatibility across different platforms. The innovations include automated testing systems that verify electrical parameters, timing requirements, and functional operation of DDR5 memory in various system configurations. Some patents cover diagnostic tools that can identify compatibility issues, memory training algorithms that optimize performance, and certification processes that ensure compliance with the DDR5 specification.

02 Motherboard and Socket Design for DDR5 Support

Motherboard designs for DDR5 compatibility incorporate specific physical layouts and electrical characteristics to accommodate the new memory standard. These designs include modified memory slots with different keying to prevent incorrect installation of incompatible memory modules. Power delivery systems on DDR5-compatible motherboards are also redesigned to support the on-module power management features of DDR5 memory, with voltage regulation moved from the motherboard to the memory modules themselves.Expand Specific Solutions03 DDR5 Compatibility with Computing Platforms

System-level compatibility solutions ensure that DDR5 memory can function properly across various computing platforms including servers, desktops, and mobile devices. These solutions address integration challenges between DDR5 memory and different processor architectures, chipsets, and operating systems. Platform compatibility features may include BIOS/UEFI updates, chipset drivers, and hardware abstraction layers that enable DDR5 memory to operate at optimal performance levels while maintaining backward compatibility where possible.Expand Specific Solutions04 DDR5 Signal Integrity and Interface Compatibility

Signal integrity solutions for DDR5 memory address the challenges of maintaining reliable data transmission at higher frequencies. These include improved PCB design techniques, enhanced signal routing, and advanced termination methods to reduce interference and signal degradation. DDR5 interfaces implement decision feedback equalization, improved crosstalk mitigation, and optimized impedance matching to ensure stable operation at speeds exceeding 4800 MT/s while maintaining compatibility with existing system architectures.Expand Specific Solutions05 DDR5 Power Management and Thermal Compatibility

Power management features in DDR5 memory systems include on-module voltage regulation, improved power efficiency, and enhanced thermal management capabilities. These features help maintain compatibility with existing cooling solutions while supporting DDR5's higher operating frequencies and data rates. Advanced thermal solutions include improved heat spreaders, thermal sensors, and dynamic frequency scaling to prevent overheating while maintaining performance. Power delivery network designs accommodate DDR5's different voltage requirements and load profiles to ensure stable operation.Expand Specific Solutions

Leading Organizations in Quantum Memory Development

The quantum computing DDR5 compatibility landscape is evolving rapidly, currently positioned in an early growth phase with market projections reaching $2-3 billion by 2028. Technical maturity varies significantly across key players, with established semiconductor giants like Intel, Micron, and AMD leading conventional memory integration, while quantum-focused companies such as PsiQuantum, D-Wave, and QuEra Computing are pioneering specialized compatibility solutions. Traditional memory manufacturers including ChangXin Memory and Rambus are adapting their DDR5 technologies for quantum environments, while research powerhouses like IBM, Google, and Microsoft are developing proprietary interfaces. The convergence of quantum computing and high-performance memory represents a critical technical challenge requiring cross-industry collaboration to establish standardized compatibility frameworks.

Microsoft Technology Licensing LLC

Technical Solution: Microsoft has pioneered a topological approach to DDR5 compatibility assessment in quantum environments through their Azure Quantum platform. Their methodology focuses on maintaining memory coherence across the quantum-classical boundary by implementing specialized timing protocols that synchronize DDR5 memory operations with quantum gate executions[2]. Microsoft's solution includes a comprehensive software stack that monitors and adjusts for electromagnetic interference patterns specific to quantum computing environments, ensuring DDR5 modules maintain data integrity. Their assessment framework incorporates machine learning algorithms that predict potential compatibility issues based on quantum workload characteristics and memory access patterns. Microsoft has also developed specialized firmware for DDR5 controllers that implements adaptive timing adjustments to accommodate the unique power fluctuations present in quantum computing systems[4]. This approach allows for real-time optimization of memory performance without requiring extensive hardware modifications.

Strengths: Software-defined approach allows for greater flexibility across different quantum hardware platforms; strong integration with existing cloud infrastructure; advanced predictive analytics for compatibility issues. Weaknesses: Heavier reliance on software mitigations rather than hardware solutions; potentially higher computational overhead; less optimized for extreme cryogenic environments.

Micron Technology, Inc.

Technical Solution: Micron has developed specialized DDR5 modules designed specifically for quantum computing interface environments. Their approach focuses on hardware-level solutions that address the unique challenges of quantum-classical memory integration. Micron's quantum-compatible DDR5 modules feature enhanced signal isolation layers that minimize crosstalk between memory channels, which is critical when processing quantum measurement results[5]. The company has implemented advanced thermal management systems within their DDR5 designs to maintain stable operation in proximity to cryogenic quantum computing components. Their assessment methodology includes comprehensive testing for sensitivity to magnetic field fluctuations common in quantum environments, with specialized shielding incorporated into the memory module design. Micron has also developed custom DDR5 timing protocols that accommodate the irregular access patterns typical of quantum error correction procedures, ensuring data integrity during critical quantum operations[6].

Strengths: Purpose-built hardware solutions specifically designed for quantum computing environments; industry-leading expertise in memory manufacturing; advanced materials science approach to electromagnetic interference issues. Weaknesses: Limited flexibility for different quantum architectures; higher production costs compared to standard DDR5 modules; requires specialized integration procedures.

Critical Technologies for Quantum-Classical Memory Interfaces

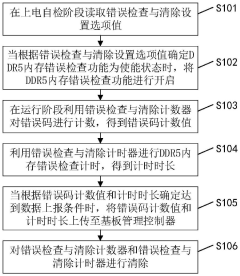

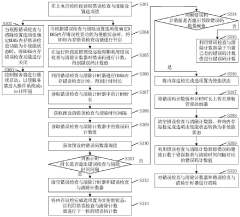

Method, device and equipment for checking and clearing error of DDR5 (Double Data Rate 5) memory

PatentPendingCN118260112A

Innovation

- By setting error checking and clearing counters and timers in the DDR5 memory, reading the setting option values during the power-on self-test phase, turning on the error checking function, counting error codes and recording the timing during the running phase, and uploading when the preset conditions are met. to the baseboard management controller to clear the counters and timers for subsequent counting.

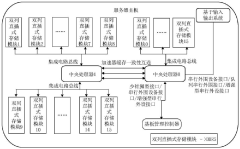

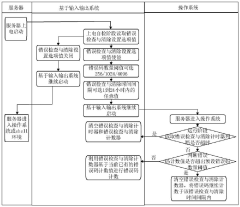

Maintenance device, method, equipment and storage medium for maintaining DDR5 memory subsystem

PatentActiveCN112349342B

Innovation

- By introducing a data verification module into the DDR5 memory subsystem, the mode register read command (MRR) is used to read the DQ data of the DDR5 memory, perform data grouping and XOR operations, and verify the correctness of the DQ data to ensure that it is based on correct data. Maintain the memory subsystem to avoid incorrect operations caused by direct dependence on the DQ signal.

Quantum Error Correction Implications for Memory Systems

Quantum Error Correction (QEC) represents a critical intersection between quantum computing and memory systems, with profound implications for DDR5 compatibility assessment. The fundamental challenge in quantum computing environments stems from quantum decoherence and errors that occur at rates significantly higher than in classical computing. These errors necessitate sophisticated error correction mechanisms that place unique demands on memory systems.

DDR5 memory integration with quantum error correction protocols requires careful consideration of latency constraints. QEC codes such as surface codes and Steane codes demand rapid syndrome measurement and error detection cycles, typically operating in microsecond timeframes. The memory subsystem must therefore support ultra-low latency operations while maintaining data integrity under quantum noise conditions.

Memory bandwidth requirements for QEC implementations scale exponentially with the number of qubits. Current estimates suggest that a practical quantum computer with error correction capabilities may require memory bandwidth exceeding 100 GB/s for real-time error syndrome processing. DDR5's theoretical bandwidth improvements (up to 51.2 GB/s) represent a significant advancement, but may still require parallel channel configurations for advanced quantum systems.

Error rate tolerance presents another critical consideration. While classical computing typically operates with bit error rates of 10^-15 or better, quantum error correction must function effectively with physical qubit error rates of 10^-3 to 10^-2. This disparity necessitates memory systems with enhanced error detection and correction capabilities beyond standard ECC implementations found in conventional DDR5 modules.

The thermal characteristics of DDR5 memory also impact quantum computing environments. Quantum systems operate at extremely low temperatures (often below 100 mK), while memory systems generate heat during operation. Specialized interface architectures must be developed to thermally isolate memory components while maintaining high-speed data pathways to the quantum processing units.

Power consumption profiles of memory systems take on new significance in quantum computing contexts. The cryogenic cooling budget is extremely limited, with each watt of power dissipation requiring approximately 1000 watts of cooling capacity. DDR5's improved power efficiency metrics must be carefully evaluated against the stringent power constraints of quantum computing environments.

DDR5 memory integration with quantum error correction protocols requires careful consideration of latency constraints. QEC codes such as surface codes and Steane codes demand rapid syndrome measurement and error detection cycles, typically operating in microsecond timeframes. The memory subsystem must therefore support ultra-low latency operations while maintaining data integrity under quantum noise conditions.

Memory bandwidth requirements for QEC implementations scale exponentially with the number of qubits. Current estimates suggest that a practical quantum computer with error correction capabilities may require memory bandwidth exceeding 100 GB/s for real-time error syndrome processing. DDR5's theoretical bandwidth improvements (up to 51.2 GB/s) represent a significant advancement, but may still require parallel channel configurations for advanced quantum systems.

Error rate tolerance presents another critical consideration. While classical computing typically operates with bit error rates of 10^-15 or better, quantum error correction must function effectively with physical qubit error rates of 10^-3 to 10^-2. This disparity necessitates memory systems with enhanced error detection and correction capabilities beyond standard ECC implementations found in conventional DDR5 modules.

The thermal characteristics of DDR5 memory also impact quantum computing environments. Quantum systems operate at extremely low temperatures (often below 100 mK), while memory systems generate heat during operation. Specialized interface architectures must be developed to thermally isolate memory components while maintaining high-speed data pathways to the quantum processing units.

Power consumption profiles of memory systems take on new significance in quantum computing contexts. The cryogenic cooling budget is extremely limited, with each watt of power dissipation requiring approximately 1000 watts of cooling capacity. DDR5's improved power efficiency metrics must be carefully evaluated against the stringent power constraints of quantum computing environments.

Cryogenic Performance Standards for DDR5 Components

The establishment of cryogenic performance standards for DDR5 components represents a critical challenge in quantum computing environments. Current DDR5 memory modules are designed to operate within conventional temperature ranges (typically 0-85°C for commercial grade), while quantum computing systems often require components to function at extremely low temperatures approaching absolute zero (-273.15°C or 0K).

Standard testing methodologies for DDR5 memory must be adapted for cryogenic conditions. These standards should include thermal cycling tests between room temperature and cryogenic levels to evaluate thermal stress resistance and potential material fatigue. Signal integrity measurements at cryogenic temperatures are essential, as electrical characteristics of semiconductors change dramatically at these extreme conditions.

Power consumption metrics require recalibration for cryogenic environments, as traditional power models become invalid. New standards must account for superconductivity thresholds and altered leakage current behaviors. Timing parameters also need redefinition, as electron mobility increases significantly at ultra-low temperatures, potentially enabling higher clock speeds but introducing new timing challenges.

Material compatibility standards must address thermal expansion coefficients at cryogenic temperatures. Conventional solder joints and PCB materials may experience stress fractures or delamination when cooled to quantum computing operational temperatures. Standards should specify acceptable materials and construction techniques that maintain structural integrity across the entire temperature range.

Reliability testing frameworks need extension to include mean time between failures (MTBF) metrics specific to cryogenic operation. Accelerated life testing methodologies must be developed to predict long-term performance without requiring decades of actual testing time. These standards should establish minimum operational lifetimes at various temperature points along the cooling curve.

Interoperability standards between DDR5 components and quantum control systems are necessary to ensure seamless integration. This includes defining interface protocols that remain stable across extreme temperature gradients and specifying shielding requirements to prevent quantum decoherence caused by electromagnetic interference from memory operations.

Certification procedures for "quantum-compatible DDR5" should be established, providing manufacturers with clear guidelines for product development and giving quantum computing system integrators confidence in component selection. These standards will accelerate adoption by reducing qualification time and enabling more reliable quantum computing architectures.

Standard testing methodologies for DDR5 memory must be adapted for cryogenic conditions. These standards should include thermal cycling tests between room temperature and cryogenic levels to evaluate thermal stress resistance and potential material fatigue. Signal integrity measurements at cryogenic temperatures are essential, as electrical characteristics of semiconductors change dramatically at these extreme conditions.

Power consumption metrics require recalibration for cryogenic environments, as traditional power models become invalid. New standards must account for superconductivity thresholds and altered leakage current behaviors. Timing parameters also need redefinition, as electron mobility increases significantly at ultra-low temperatures, potentially enabling higher clock speeds but introducing new timing challenges.

Material compatibility standards must address thermal expansion coefficients at cryogenic temperatures. Conventional solder joints and PCB materials may experience stress fractures or delamination when cooled to quantum computing operational temperatures. Standards should specify acceptable materials and construction techniques that maintain structural integrity across the entire temperature range.

Reliability testing frameworks need extension to include mean time between failures (MTBF) metrics specific to cryogenic operation. Accelerated life testing methodologies must be developed to predict long-term performance without requiring decades of actual testing time. These standards should establish minimum operational lifetimes at various temperature points along the cooling curve.

Interoperability standards between DDR5 components and quantum control systems are necessary to ensure seamless integration. This includes defining interface protocols that remain stable across extreme temperature gradients and specifying shielding requirements to prevent quantum decoherence caused by electromagnetic interference from memory operations.

Certification procedures for "quantum-compatible DDR5" should be established, providing manufacturers with clear guidelines for product development and giving quantum computing system integrators confidence in component selection. These standards will accelerate adoption by reducing qualification time and enabling more reliable quantum computing architectures.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!