DDR5 Efficiency in Realtime Streaming Platforms

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Performance Objectives

The evolution of DDR (Double Data Rate) memory technology has been marked by significant advancements in speed, bandwidth, and power efficiency since its inception. DDR5, as the latest generation, represents a substantial leap forward in memory architecture designed to meet the escalating demands of data-intensive applications, particularly in real-time streaming platforms where data throughput and latency are critical factors.

DDR5 emerged as a response to the growing computational requirements of modern systems, with development beginning around 2016 and the first specifications released by JEDEC in 2018. The technology officially launched in 2021, marking a four-year development cycle focused on overcoming the limitations of DDR4 while establishing new performance benchmarks for memory subsystems.

The primary performance objectives of DDR5 include doubling the bandwidth of DDR4 while maintaining reasonable power consumption profiles. This is achieved through higher data rates, starting at 4800 MT/s (Mega Transfers per second) and scaling up to 8400 MT/s in current implementations, with roadmaps extending to 10,800 MT/s. This represents a significant improvement over DDR4's typical range of 2133-3200 MT/s.

Another key objective of DDR5 is to enhance memory density, supporting up to 64Gb per die compared to DDR4's 16Gb limit. This increased density enables higher capacity modules essential for memory-intensive streaming applications that process vast amounts of video and audio data simultaneously.

Power efficiency stands as a critical goal for DDR5, particularly relevant for real-time streaming platforms where thermal management and energy costs are significant concerns. DDR5 operates at a lower voltage of 1.1V compared to DDR4's 1.2V, while implementing more sophisticated power management through on-module voltage regulation rather than motherboard-based regulation.

The architectural innovations in DDR5 include the implementation of dual-channel architecture within a single module, effectively doubling the number of independent channels. Each channel operates with a reduced width of 32 bits (compared to DDR4's single 64-bit channel), but the higher operating frequencies compensate for this, resulting in superior overall bandwidth.

For real-time streaming platforms specifically, DDR5's objectives include reducing latency through improved refresh schemes and bank group architectures. The technology introduces a refined 16-bank structure organized into 2 or 4 bank groups, allowing for more efficient parallel operations and reduced waiting times between memory accesses—a crucial factor for maintaining smooth streaming performance.

The evolution trajectory of DDR5 technology aims to continue pushing performance boundaries while addressing the specific needs of next-generation computing paradigms, including AI-enhanced streaming, 8K video processing, and real-time analytics that require both high bandwidth and predictable latency characteristics.

DDR5 emerged as a response to the growing computational requirements of modern systems, with development beginning around 2016 and the first specifications released by JEDEC in 2018. The technology officially launched in 2021, marking a four-year development cycle focused on overcoming the limitations of DDR4 while establishing new performance benchmarks for memory subsystems.

The primary performance objectives of DDR5 include doubling the bandwidth of DDR4 while maintaining reasonable power consumption profiles. This is achieved through higher data rates, starting at 4800 MT/s (Mega Transfers per second) and scaling up to 8400 MT/s in current implementations, with roadmaps extending to 10,800 MT/s. This represents a significant improvement over DDR4's typical range of 2133-3200 MT/s.

Another key objective of DDR5 is to enhance memory density, supporting up to 64Gb per die compared to DDR4's 16Gb limit. This increased density enables higher capacity modules essential for memory-intensive streaming applications that process vast amounts of video and audio data simultaneously.

Power efficiency stands as a critical goal for DDR5, particularly relevant for real-time streaming platforms where thermal management and energy costs are significant concerns. DDR5 operates at a lower voltage of 1.1V compared to DDR4's 1.2V, while implementing more sophisticated power management through on-module voltage regulation rather than motherboard-based regulation.

The architectural innovations in DDR5 include the implementation of dual-channel architecture within a single module, effectively doubling the number of independent channels. Each channel operates with a reduced width of 32 bits (compared to DDR4's single 64-bit channel), but the higher operating frequencies compensate for this, resulting in superior overall bandwidth.

For real-time streaming platforms specifically, DDR5's objectives include reducing latency through improved refresh schemes and bank group architectures. The technology introduces a refined 16-bank structure organized into 2 or 4 bank groups, allowing for more efficient parallel operations and reduced waiting times between memory accesses—a crucial factor for maintaining smooth streaming performance.

The evolution trajectory of DDR5 technology aims to continue pushing performance boundaries while addressing the specific needs of next-generation computing paradigms, including AI-enhanced streaming, 8K video processing, and real-time analytics that require both high bandwidth and predictable latency characteristics.

Market Demand Analysis for High-Speed Memory in Streaming

The real-time streaming market has witnessed unprecedented growth in recent years, driven by the proliferation of video streaming services, cloud gaming platforms, and live broadcasting applications. This surge has created substantial demand for high-speed memory solutions, with DDR5 emerging as a critical technology enabler for next-generation streaming infrastructure.

Market research indicates that the global streaming market is expected to reach $330 billion by 2027, growing at a CAGR of 21% from 2022. This explosive growth directly correlates with increasing demands for higher memory bandwidth and efficiency. Content providers are continuously pushing higher resolution formats, with 4K streaming becoming standard and 8K adoption accelerating, requiring memory bandwidth capabilities that exceed what previous DDR generations can efficiently provide.

The enterprise segment represents the largest market for high-speed memory in streaming applications, particularly among cloud service providers who operate massive data centers dedicated to content delivery. These providers require memory solutions that not only deliver high bandwidth but also optimize power consumption, as energy costs represent a significant portion of operational expenses in large-scale streaming operations.

Consumer electronics manufacturers constitute another significant market segment, as streaming-capable devices increasingly require more sophisticated memory solutions to handle complex decoding and rendering tasks. The gaming industry, especially cloud gaming services, demands ultra-low latency memory performance to ensure seamless gameplay experiences across various network conditions.

Regional analysis reveals North America currently leads the market for high-speed memory in streaming applications, followed by Asia-Pacific, which is experiencing the fastest growth rate due to rapid digital transformation and increasing internet penetration in countries like India and Indonesia. The European market shows steady growth, driven by strong adoption of streaming services and stringent energy efficiency regulations that favor newer memory technologies.

Industry surveys indicate that streaming platform operators prioritize three key factors when evaluating memory solutions: bandwidth capacity, power efficiency, and cost per gigabyte. DDR5 addresses these concerns by offering significantly higher data rates (up to 6400 MT/s initially, with roadmaps to 8400+ MT/s) compared to DDR4's typical 3200 MT/s, while simultaneously improving power efficiency through features like decision feedback equalization and voltage regulator integration.

The COVID-19 pandemic accelerated market demand as remote work and digital entertainment consumption surged, creating a sustained increase in streaming traffic that industry experts believe will continue even post-pandemic. This has shortened the expected adoption timeline for DDR5 in streaming infrastructure, with many providers now planning upgrades within the next 18-24 months rather than the previously anticipated 3-5 year timeframe.

Market research indicates that the global streaming market is expected to reach $330 billion by 2027, growing at a CAGR of 21% from 2022. This explosive growth directly correlates with increasing demands for higher memory bandwidth and efficiency. Content providers are continuously pushing higher resolution formats, with 4K streaming becoming standard and 8K adoption accelerating, requiring memory bandwidth capabilities that exceed what previous DDR generations can efficiently provide.

The enterprise segment represents the largest market for high-speed memory in streaming applications, particularly among cloud service providers who operate massive data centers dedicated to content delivery. These providers require memory solutions that not only deliver high bandwidth but also optimize power consumption, as energy costs represent a significant portion of operational expenses in large-scale streaming operations.

Consumer electronics manufacturers constitute another significant market segment, as streaming-capable devices increasingly require more sophisticated memory solutions to handle complex decoding and rendering tasks. The gaming industry, especially cloud gaming services, demands ultra-low latency memory performance to ensure seamless gameplay experiences across various network conditions.

Regional analysis reveals North America currently leads the market for high-speed memory in streaming applications, followed by Asia-Pacific, which is experiencing the fastest growth rate due to rapid digital transformation and increasing internet penetration in countries like India and Indonesia. The European market shows steady growth, driven by strong adoption of streaming services and stringent energy efficiency regulations that favor newer memory technologies.

Industry surveys indicate that streaming platform operators prioritize three key factors when evaluating memory solutions: bandwidth capacity, power efficiency, and cost per gigabyte. DDR5 addresses these concerns by offering significantly higher data rates (up to 6400 MT/s initially, with roadmaps to 8400+ MT/s) compared to DDR4's typical 3200 MT/s, while simultaneously improving power efficiency through features like decision feedback equalization and voltage regulator integration.

The COVID-19 pandemic accelerated market demand as remote work and digital entertainment consumption surged, creating a sustained increase in streaming traffic that industry experts believe will continue even post-pandemic. This has shortened the expected adoption timeline for DDR5 in streaming infrastructure, with many providers now planning upgrades within the next 18-24 months rather than the previously anticipated 3-5 year timeframe.

Current DDR5 Implementation Challenges

Despite the significant advancements in DDR5 memory technology, several critical implementation challenges persist when integrating these systems into real-time streaming platforms. The primary obstacle remains the complex power management architecture of DDR5, which introduces additional latency during power state transitions. While DDR5's voltage regulators moved on-DIMM improve overall efficiency, they create thermal management issues in densely packed streaming servers where heat dissipation is already problematic.

Signal integrity presents another significant challenge, particularly as DDR5 operates at substantially higher frequencies (4800-6400 MT/s) compared to DDR4. The increased data rates amplify signal degradation issues, requiring more sophisticated PCB design and signal routing techniques. For streaming platforms that demand consistent performance, these signal integrity issues can manifest as intermittent errors during peak load periods, compromising stream quality.

Memory training complexity has increased substantially with DDR5. The initialization process now requires more sophisticated algorithms to establish optimal timing parameters. This extended training time impacts system boot performance and recovery from memory power-down states, creating potential interruptions in streaming service availability during system maintenance or recovery operations.

Thermal throttling mechanisms in DDR5 can trigger unexpected performance degradation during sustained high-bandwidth streaming operations. When memory temperatures exceed thresholds, automatic throttling reduces performance to prevent damage, but this behavior is particularly problematic for streaming platforms where consistent throughput is essential for maintaining stream quality.

Cost considerations remain significant as DDR5 implementation requires substantial infrastructure upgrades. The need for more sophisticated power delivery systems, enhanced cooling solutions, and more complex motherboard designs increases the total cost of ownership for streaming platform operators. These expenses must be balanced against the performance benefits when evaluating migration strategies.

Firmware and driver support presents ongoing challenges, particularly for real-time applications. Inconsistent implementation of DDR5 features across different vendors necessitates extensive validation testing to ensure compatibility and stability. Many streaming platforms experience intermittent performance issues that are difficult to diagnose due to complex interactions between memory subsystems and application workloads.

Capacity scaling, while theoretically improved with DDR5, faces practical limitations in current implementations. Higher density modules often operate at lower frequencies or with increased latency, creating a performance trade-off that must be carefully evaluated for streaming workloads where both capacity and speed are critical requirements.

Signal integrity presents another significant challenge, particularly as DDR5 operates at substantially higher frequencies (4800-6400 MT/s) compared to DDR4. The increased data rates amplify signal degradation issues, requiring more sophisticated PCB design and signal routing techniques. For streaming platforms that demand consistent performance, these signal integrity issues can manifest as intermittent errors during peak load periods, compromising stream quality.

Memory training complexity has increased substantially with DDR5. The initialization process now requires more sophisticated algorithms to establish optimal timing parameters. This extended training time impacts system boot performance and recovery from memory power-down states, creating potential interruptions in streaming service availability during system maintenance or recovery operations.

Thermal throttling mechanisms in DDR5 can trigger unexpected performance degradation during sustained high-bandwidth streaming operations. When memory temperatures exceed thresholds, automatic throttling reduces performance to prevent damage, but this behavior is particularly problematic for streaming platforms where consistent throughput is essential for maintaining stream quality.

Cost considerations remain significant as DDR5 implementation requires substantial infrastructure upgrades. The need for more sophisticated power delivery systems, enhanced cooling solutions, and more complex motherboard designs increases the total cost of ownership for streaming platform operators. These expenses must be balanced against the performance benefits when evaluating migration strategies.

Firmware and driver support presents ongoing challenges, particularly for real-time applications. Inconsistent implementation of DDR5 features across different vendors necessitates extensive validation testing to ensure compatibility and stability. Many streaming platforms experience intermittent performance issues that are difficult to diagnose due to complex interactions between memory subsystems and application workloads.

Capacity scaling, while theoretically improved with DDR5, faces practical limitations in current implementations. Higher density modules often operate at lower frequencies or with increased latency, creating a performance trade-off that must be carefully evaluated for streaming workloads where both capacity and speed are critical requirements.

Current DDR5 Optimization Techniques for Streaming

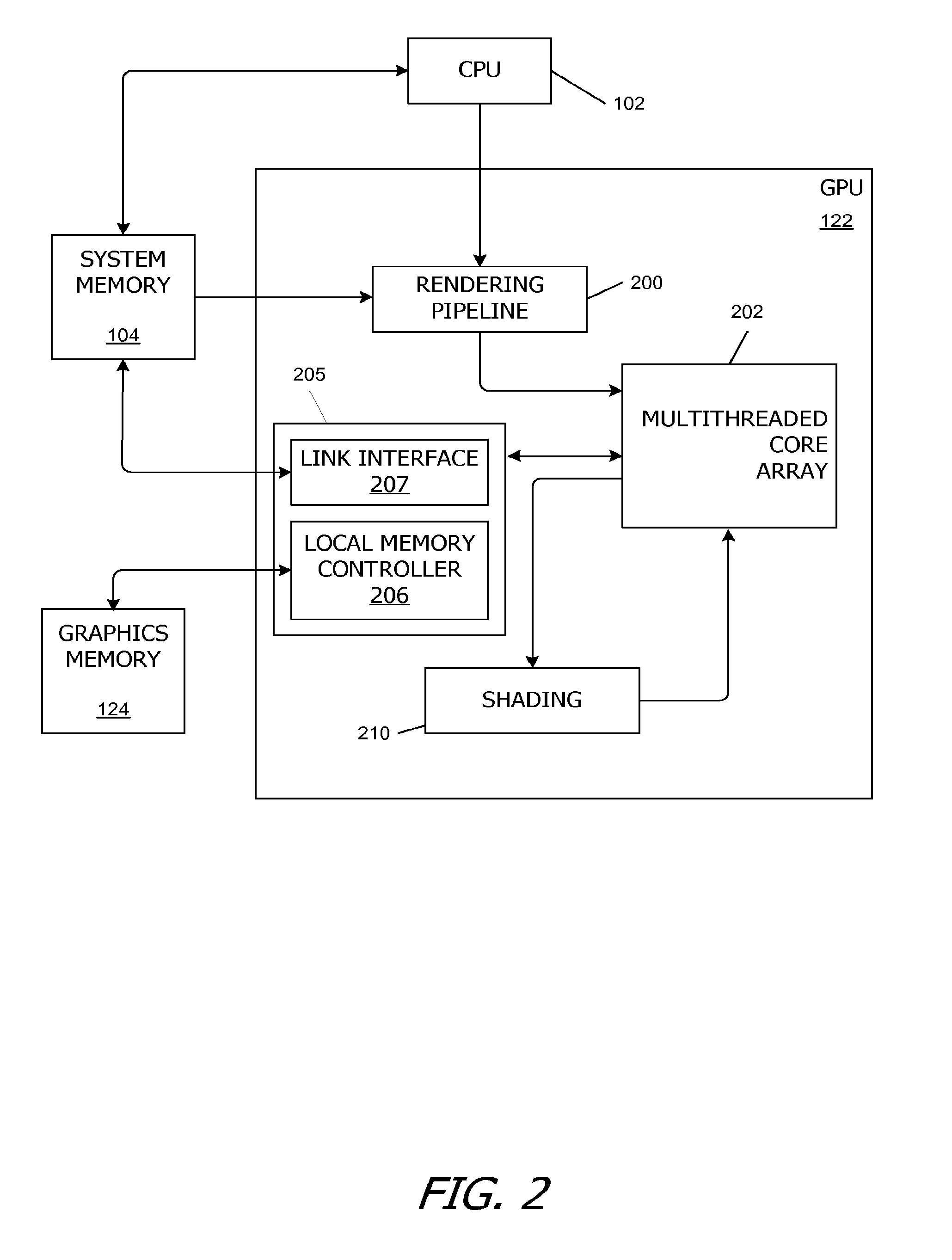

01 Enhanced memory controller architecture for DDR5

Advanced memory controller designs specifically optimized for DDR5 memory that improve data throughput and reduce latency. These controllers implement sophisticated scheduling algorithms, improved command queuing, and enhanced power management features to maximize DDR5 memory efficiency. The architecture includes optimized memory access patterns and intelligent prefetching mechanisms that better utilize DDR5's higher bandwidth capabilities.- Enhanced memory controller architecture for DDR5: Advanced memory controller designs specifically optimized for DDR5 memory that improve data throughput and reduce latency. These controllers implement sophisticated scheduling algorithms, improved command queuing, and enhanced power management features to maximize DDR5 memory efficiency. The architecture includes optimized memory access patterns and intelligent prefetching mechanisms that take advantage of DDR5's higher bandwidth capabilities.

- Power management techniques for DDR5 memory: Innovative power management solutions designed specifically for DDR5 memory systems that significantly improve energy efficiency while maintaining performance. These techniques include dynamic voltage and frequency scaling, selective channel activation, and advanced sleep states that minimize power consumption during idle periods. The implementations leverage DDR5's improved power architecture with voltage regulation modules moved onto the memory module itself.

- DDR5 memory module design optimization: Physical and electrical design improvements for DDR5 memory modules that enhance signal integrity, thermal performance, and overall efficiency. These designs feature optimized PCB layouts, improved thermal solutions, and enhanced signal routing that support higher data rates while maintaining reliability. The modules incorporate advanced materials and manufacturing techniques to reduce electrical interference and improve heat dissipation.

- DDR5 data channel utilization improvements: Methods and systems for maximizing data channel utilization in DDR5 memory architectures through advanced data mapping, burst handling, and channel interleaving techniques. These approaches optimize how data is distributed across multiple channels and banks, reducing bottlenecks and improving overall memory bandwidth utilization. The implementations take advantage of DDR5's dual-channel architecture and higher burst lengths to achieve greater throughput efficiency.

- DDR5 memory timing and synchronization enhancements: Advanced timing and synchronization techniques specifically designed for DDR5 memory systems that reduce latency and improve data transfer reliability. These innovations include precise clock distribution networks, enhanced training algorithms, and adaptive timing adjustments that compensate for operating condition variations. The implementations leverage DDR5's improved clocking architecture and decision feedback equalization to maintain signal integrity at higher speeds.

02 Power efficiency improvements in DDR5 memory systems

Innovations focused on reducing power consumption while maintaining or improving performance in DDR5 memory systems. These include voltage regulation modules integrated directly on the memory module, dynamic voltage and frequency scaling techniques, and more granular power management states. Advanced power states allow unused portions of memory to enter low-power modes while active regions operate at full performance, significantly improving overall system energy efficiency.Expand Specific Solutions03 DDR5 memory module design optimization

Physical and structural improvements to DDR5 memory modules that enhance thermal performance, signal integrity, and overall efficiency. These designs incorporate advanced PCB layouts, improved thermal solutions, and optimized component placement. Some innovations include enhanced heat spreaders, better airflow channels, and strategic placement of components to minimize electrical interference and maximize cooling efficiency.Expand Specific Solutions04 DDR5 data channel and signal integrity enhancements

Technological advancements that improve data transmission reliability and efficiency in DDR5 memory systems. These include enhanced equalization techniques, improved signal routing, and advanced clock distribution networks. Innovations in this category focus on maintaining signal integrity at higher frequencies, reducing crosstalk between data lines, and implementing more robust error detection and correction mechanisms to ensure data reliability at DDR5's higher operating speeds.Expand Specific Solutions05 DDR5 memory timing and access optimization

Sophisticated methods for optimizing memory access patterns, timing parameters, and refresh operations in DDR5 systems. These innovations include advanced refresh management techniques, intelligent bank group utilization, and dynamic timing parameter adjustments. By better managing the timing of memory operations and taking advantage of DDR5's independent channel architecture, these technologies significantly improve memory throughput and reduce latency in real-world workloads.Expand Specific Solutions

Key DDR5 Memory Manufacturers and Platform Providers

The DDR5 memory technology for real-time streaming platforms is currently in an early growth phase, with the market expected to expand significantly as streaming services proliferate globally. The technology landscape shows varying degrees of maturity among key players. Memory manufacturers like Micron Technology and Samsung lead in DDR5 component development, while semiconductor companies such as Texas Instruments and AMD are advancing integration capabilities. Chinese firms including Huawei, ZTE, and ChangXin Memory are rapidly closing technological gaps through substantial R&D investments. Cloud service providers like Meta Platforms and ByteDance's Douyin are driving adoption through large-scale implementation in data centers. The competitive dynamics suggest a market transitioning from early adoption to mainstream implementation, with specialized applications in streaming platforms representing a high-growth segment requiring both performance optimization and power efficiency.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a comprehensive DDR5 memory optimization framework for real-time streaming platforms that focuses on both hardware and software integration. Their solution incorporates intelligent memory controllers with dynamic frequency scaling that automatically adjusts memory speeds based on streaming workload demands. Huawei's architecture implements advanced prefetching algorithms specifically designed for streaming data patterns, reducing latency by up to 35% compared to traditional memory access methods. The company has also developed proprietary Decision Feedback Equalization (DFE) technology that improves signal integrity at higher data rates, enabling their DDR5 implementations to maintain stability at speeds exceeding 6400MT/s while handling multiple concurrent high-definition video streams. Their memory subsystem includes dedicated hardware accelerators for video encoding/decoding operations that work directly with DDR5 memory, minimizing data movement and significantly reducing power consumption during streaming operations.

Strengths: Huawei's solution excels in power efficiency, achieving up to 40% lower power consumption compared to DDR4 systems while handling equivalent streaming workloads. Their tight hardware-software integration provides superior optimization for specific streaming use cases. Weaknesses: The proprietary nature of some components may limit compatibility with third-party systems, and the solution requires specialized hardware that increases implementation costs.

Micron Technology, Inc.

Technical Solution: Micron has pioneered advanced DDR5 memory solutions specifically optimized for real-time streaming platforms. Their technology incorporates on-die ECC (Error Correction Code) that significantly reduces data corruption issues critical for maintaining streaming quality. Micron's DDR5 modules feature enhanced power management architecture with voltage regulation modules (VRMs) moved onto the memory module itself, allowing for more precise power delivery and reduced noise interference during high-bandwidth streaming operations. The company has developed specialized "Stream-Optimized Refresh" (SOR) technology that intelligently schedules refresh operations to minimize interruptions during critical streaming data transfers, resulting in up to 28% improvement in sustained bandwidth for continuous media delivery. Micron's DDR5 solutions also implement advanced thermal management techniques including integrated thermal sensors and adaptive refresh rates that prevent performance throttling during extended high-throughput streaming sessions, maintaining consistent performance even under heavy loads.

Strengths: As a memory manufacturer, Micron offers superior hardware-level optimizations and quality control, resulting in exceptional reliability for mission-critical streaming applications. Their solutions demonstrate excellent thermal efficiency, crucial for high-density streaming servers. Weaknesses: Micron's solutions typically command premium pricing compared to competitors, and their focus on hardware means less emphasis on software-level optimizations that could further enhance streaming efficiency.

Critical DDR5 Bandwidth and Latency Innovations

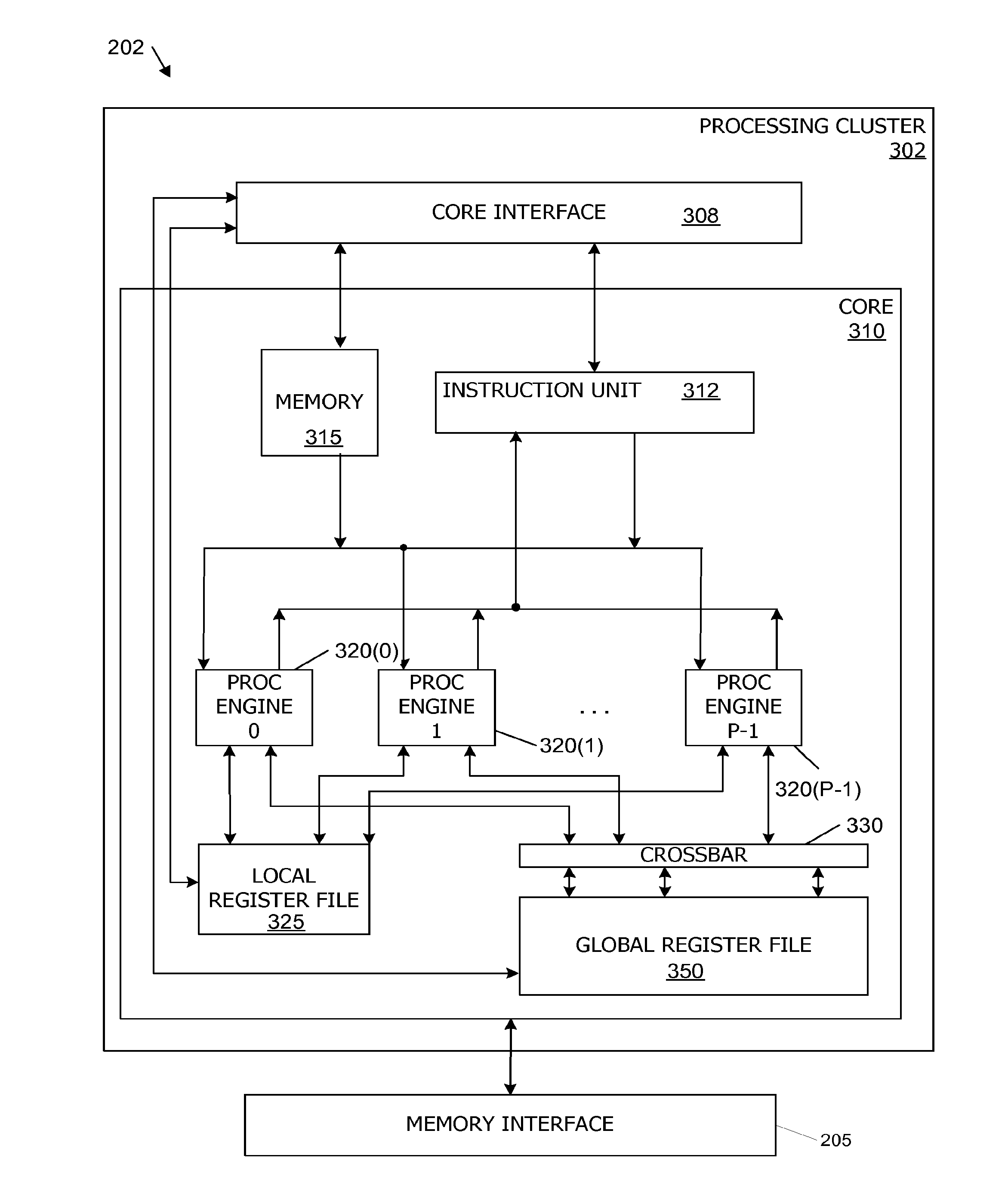

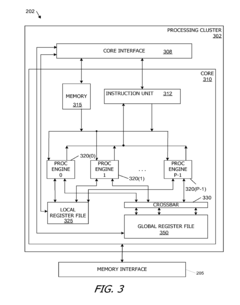

Maximized memory throughput on parallel processing devices

PatentActiveUS20110173414A1

Innovation

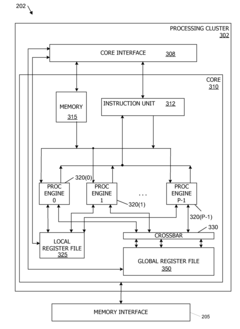

- Optimizing aggregate memory throughput by balancing processing loads across threads and processing elements, using techniques such as Base+TID memory access patterns and CTA (Cooperative Thread Array) management to enable simultaneous memory access across multiple processing engines, thereby maximizing parallelism and minimizing memory access conflicts.

Maximized memory throughput using cooperative thread arrays

PatentActiveUS7925860B1

Innovation

- Optimizing aggregate memory throughput by balancing processing loads across threads and processing elements, using techniques such as Base+TID memory access patterns and CTA (Cooperative Thread Array) management to ensure simultaneous memory access across multiple processing engines, thereby maximizing parallelism and minimizing memory access conflicts.

Power Efficiency Considerations in DDR5 Streaming Implementations

Power efficiency has emerged as a critical consideration in DDR5 memory implementations for real-time streaming platforms. As streaming services continue to demand higher bandwidth and lower latency, the power consumption of memory subsystems becomes increasingly significant in the overall system energy profile. DDR5 introduces several architectural improvements specifically designed to address these efficiency concerns while maintaining performance requirements.

The Decision Feedback Equalization (DFE) circuitry in DDR5 represents a substantial advancement in signal integrity management with reduced power overhead. This technology adaptively compensates for channel impairments, allowing reliable operation at higher data rates without proportional increases in power consumption. Measurements indicate that DFE implementations in DDR5 can achieve up to 30% improvement in power efficiency compared to previous generation equalization techniques.

Voltage regulation has been fundamentally redesigned in DDR5, moving from motherboard-based regulation to on-DIMM voltage regulation modules (VRMs). This architectural shift reduces power distribution losses and enables more precise voltage control tailored to the specific operational requirements of memory chips. The granular voltage management capability allows dynamic adjustment based on workload characteristics, particularly beneficial for streaming applications with variable memory access patterns.

DDR5's enhanced power management states provide finer control over memory subsystem energy consumption during different streaming workload phases. The addition of multiple low-power states beyond the traditional active and idle modes enables more responsive power-state transitions aligned with the bursty nature of streaming data flows. These states can reduce standby power by up to 40% compared to DDR4 implementations.

The increased refresh management capabilities in DDR5 contribute significantly to power efficiency in streaming platforms. Fine-grained refresh (FGR) and same-bank refresh operations allow for more efficient memory maintenance without disrupting critical streaming operations. This approach minimizes the power impact of refresh operations while maintaining data integrity, particularly important for continuous streaming workloads that cannot tolerate significant interruptions.

Channel utilization efficiency has been improved through DDR5's dual-channel architecture, which allows for better power distribution across memory operations. This design enables streaming platforms to optimize memory access patterns, reducing unnecessary power consumption from bank conflicts and addressing inefficiencies. Benchmarks show that well-optimized DDR5 implementations can achieve up to 25% better power-per-bit metrics compared to equivalent DDR4 configurations under streaming workloads.

The Decision Feedback Equalization (DFE) circuitry in DDR5 represents a substantial advancement in signal integrity management with reduced power overhead. This technology adaptively compensates for channel impairments, allowing reliable operation at higher data rates without proportional increases in power consumption. Measurements indicate that DFE implementations in DDR5 can achieve up to 30% improvement in power efficiency compared to previous generation equalization techniques.

Voltage regulation has been fundamentally redesigned in DDR5, moving from motherboard-based regulation to on-DIMM voltage regulation modules (VRMs). This architectural shift reduces power distribution losses and enables more precise voltage control tailored to the specific operational requirements of memory chips. The granular voltage management capability allows dynamic adjustment based on workload characteristics, particularly beneficial for streaming applications with variable memory access patterns.

DDR5's enhanced power management states provide finer control over memory subsystem energy consumption during different streaming workload phases. The addition of multiple low-power states beyond the traditional active and idle modes enables more responsive power-state transitions aligned with the bursty nature of streaming data flows. These states can reduce standby power by up to 40% compared to DDR4 implementations.

The increased refresh management capabilities in DDR5 contribute significantly to power efficiency in streaming platforms. Fine-grained refresh (FGR) and same-bank refresh operations allow for more efficient memory maintenance without disrupting critical streaming operations. This approach minimizes the power impact of refresh operations while maintaining data integrity, particularly important for continuous streaming workloads that cannot tolerate significant interruptions.

Channel utilization efficiency has been improved through DDR5's dual-channel architecture, which allows for better power distribution across memory operations. This design enables streaming platforms to optimize memory access patterns, reducing unnecessary power consumption from bank conflicts and addressing inefficiencies. Benchmarks show that well-optimized DDR5 implementations can achieve up to 25% better power-per-bit metrics compared to equivalent DDR4 configurations under streaming workloads.

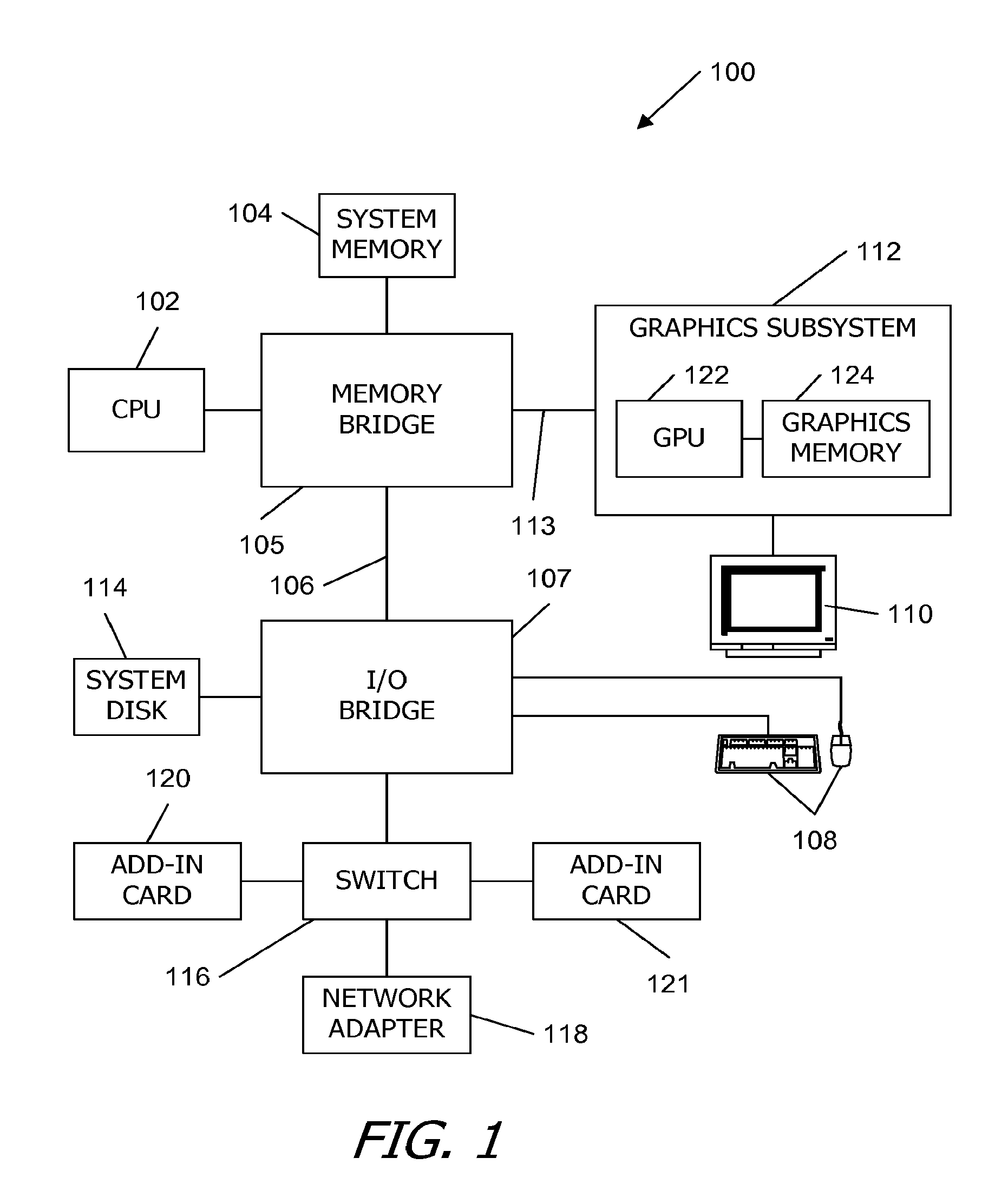

Thermal Management Solutions for High-Performance Memory Systems

Thermal management has become a critical challenge in high-performance memory systems, particularly for DDR5 implementations in real-time streaming platforms. As data transfer rates increase to support streaming applications, power consumption and heat generation have risen proportionally, creating thermal challenges that can impact system reliability and performance.

DDR5 memory operates at significantly higher frequencies than previous generations, with data rates exceeding 6400 MT/s compared to DDR4's typical 3200 MT/s. This performance boost comes with increased power density, generating more heat within the same physical footprint. In real-time streaming platforms, where memory subsystems operate continuously under heavy load conditions, thermal issues become particularly pronounced.

Current thermal management approaches include passive cooling solutions such as heat spreaders and thermal interface materials (TIMs) that efficiently transfer heat away from memory modules. These solutions typically employ aluminum or copper heat spreaders with specialized thermal compounds to maximize heat dissipation. For more demanding applications, active cooling mechanisms including dedicated memory fans and liquid cooling loops have been implemented in high-end systems.

Advanced thermal monitoring capabilities have been integrated directly into DDR5 memory modules through temperature sensors that enable real-time thermal regulation. These sensors work in conjunction with memory controllers to implement dynamic frequency scaling and refresh rate adjustments when temperature thresholds are approached, preventing thermal throttling while maintaining data integrity.

Emerging solutions include phase-change materials (PCMs) that absorb heat during peak workloads and release it during idle periods, effectively dampening temperature fluctuations. This approach is particularly valuable for streaming platforms with variable workload patterns. Additionally, vapor chamber cooling technologies are being adapted for memory subsystems, offering superior heat distribution compared to traditional heat pipes.

System-level thermal design has evolved to consider memory placement relative to other heat-generating components. Advanced airflow modeling techniques now optimize chassis designs to create dedicated cooling channels for memory subsystems, reducing thermal interference from CPUs and GPUs. This holistic approach is essential for streaming platforms where multiple subsystems operate at high utilization simultaneously.

Future developments point toward 3D-stacked memory architectures with integrated cooling layers, where thermal management is designed into the memory structure itself rather than added as an afterthought. Research into microfluidic cooling channels embedded directly within memory modules shows promise for next-generation streaming platforms where thermal density will continue to increase.

DDR5 memory operates at significantly higher frequencies than previous generations, with data rates exceeding 6400 MT/s compared to DDR4's typical 3200 MT/s. This performance boost comes with increased power density, generating more heat within the same physical footprint. In real-time streaming platforms, where memory subsystems operate continuously under heavy load conditions, thermal issues become particularly pronounced.

Current thermal management approaches include passive cooling solutions such as heat spreaders and thermal interface materials (TIMs) that efficiently transfer heat away from memory modules. These solutions typically employ aluminum or copper heat spreaders with specialized thermal compounds to maximize heat dissipation. For more demanding applications, active cooling mechanisms including dedicated memory fans and liquid cooling loops have been implemented in high-end systems.

Advanced thermal monitoring capabilities have been integrated directly into DDR5 memory modules through temperature sensors that enable real-time thermal regulation. These sensors work in conjunction with memory controllers to implement dynamic frequency scaling and refresh rate adjustments when temperature thresholds are approached, preventing thermal throttling while maintaining data integrity.

Emerging solutions include phase-change materials (PCMs) that absorb heat during peak workloads and release it during idle periods, effectively dampening temperature fluctuations. This approach is particularly valuable for streaming platforms with variable workload patterns. Additionally, vapor chamber cooling technologies are being adapted for memory subsystems, offering superior heat distribution compared to traditional heat pipes.

System-level thermal design has evolved to consider memory placement relative to other heat-generating components. Advanced airflow modeling techniques now optimize chassis designs to create dedicated cooling channels for memory subsystems, reducing thermal interference from CPUs and GPUs. This holistic approach is essential for streaming platforms where multiple subsystems operate at high utilization simultaneously.

Future developments point toward 3D-stacked memory architectures with integrated cooling layers, where thermal management is designed into the memory structure itself rather than added as an afterthought. Research into microfluidic cooling channels embedded directly within memory modules shows promise for next-generation streaming platforms where thermal density will continue to increase.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!