DDR5 Speed Optimization Techniques for Real-Time Data

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Performance Objectives

DDR5 memory technology represents a significant evolution in the DRAM landscape, building upon the foundations established by its predecessors while introducing revolutionary advancements in speed, capacity, and power efficiency. The development of DDR5 began in 2016, with JEDEC finalizing the standard in 2020, marking a critical milestone in memory technology progression. This fifth generation of Double Data Rate Synchronous Dynamic Random-Access Memory aims to address the exponentially growing data processing demands of modern computing environments, particularly in data centers, AI applications, and high-performance computing systems.

The historical trajectory of DRAM technology shows consistent improvements in data transfer rates, from DDR4's maximum of 3200 MT/s to DDR5's initial speeds of 4800 MT/s, with a roadmap extending to 8400 MT/s and beyond. This represents more than a doubling of bandwidth capability, crucial for real-time data processing applications where memory speed often constitutes a significant bottleneck.

Performance objectives for DDR5 optimization in real-time data contexts center around several key parameters. Latency reduction remains paramount, with techniques focusing on minimizing CAS, RAS, and command delays. Bandwidth enhancement strategies include higher frequency operation, improved channel architecture, and advanced signaling methods. Power efficiency has gained prominence, with DDR5 introducing voltage reduction from 1.2V to 1.1V and implementing sophisticated power management features.

The technical evolution path includes architectural innovations such as the transition from a single 72-bit bus to two independent 40-bit channels, effectively doubling the accessible banks while maintaining the same pin count. Decision Feedback Equalization (DFE) and improved on-die termination represent significant signal integrity enhancements critical for maintaining reliable operation at higher frequencies.

Real-time data applications place unique demands on memory subsystems, requiring not just raw bandwidth but consistent, predictable performance under varying workloads. DDR5 optimization techniques must therefore balance peak performance capabilities with reliability metrics such as error rates and thermal stability. The introduction of on-die ECC in DDR5 addresses this concern directly, providing enhanced data integrity without imposing additional burden on the memory controller.

Looking forward, the DDR5 roadmap indicates continued evolution toward higher densities (up to 64Gb per die) and faster speeds, with industry projections suggesting practical implementations reaching 10,000 MT/s within the technology's lifecycle. These advancements will be essential to support next-generation real-time applications in fields such as autonomous vehicles, industrial automation, and edge computing, where data processing latency directly impacts system responsiveness and safety.

The historical trajectory of DRAM technology shows consistent improvements in data transfer rates, from DDR4's maximum of 3200 MT/s to DDR5's initial speeds of 4800 MT/s, with a roadmap extending to 8400 MT/s and beyond. This represents more than a doubling of bandwidth capability, crucial for real-time data processing applications where memory speed often constitutes a significant bottleneck.

Performance objectives for DDR5 optimization in real-time data contexts center around several key parameters. Latency reduction remains paramount, with techniques focusing on minimizing CAS, RAS, and command delays. Bandwidth enhancement strategies include higher frequency operation, improved channel architecture, and advanced signaling methods. Power efficiency has gained prominence, with DDR5 introducing voltage reduction from 1.2V to 1.1V and implementing sophisticated power management features.

The technical evolution path includes architectural innovations such as the transition from a single 72-bit bus to two independent 40-bit channels, effectively doubling the accessible banks while maintaining the same pin count. Decision Feedback Equalization (DFE) and improved on-die termination represent significant signal integrity enhancements critical for maintaining reliable operation at higher frequencies.

Real-time data applications place unique demands on memory subsystems, requiring not just raw bandwidth but consistent, predictable performance under varying workloads. DDR5 optimization techniques must therefore balance peak performance capabilities with reliability metrics such as error rates and thermal stability. The introduction of on-die ECC in DDR5 addresses this concern directly, providing enhanced data integrity without imposing additional burden on the memory controller.

Looking forward, the DDR5 roadmap indicates continued evolution toward higher densities (up to 64Gb per die) and faster speeds, with industry projections suggesting practical implementations reaching 10,000 MT/s within the technology's lifecycle. These advancements will be essential to support next-generation real-time applications in fields such as autonomous vehicles, industrial automation, and edge computing, where data processing latency directly impacts system responsiveness and safety.

Real-Time Data Market Requirements Analysis

The real-time data processing market has experienced exponential growth over the past decade, driven primarily by the increasing digitization across industries and the proliferation of IoT devices. Current market analysis indicates that industries including financial services, telecommunications, healthcare, and manufacturing are the primary consumers of real-time data processing technologies, with financial trading platforms and telecommunications networks demonstrating the most stringent requirements for data processing speed and reliability.

Market research reveals that latency requirements have become increasingly demanding, with financial trading systems now requiring sub-microsecond response times to maintain competitive advantage. Similarly, telecommunications networks supporting 5G infrastructure demand processing capabilities that can handle millions of concurrent connections with minimal delay. These market segments are particularly sensitive to memory performance bottlenecks, making DDR5 optimization techniques critically important.

Consumer expectations for real-time experiences have also evolved significantly. Modern applications in gaming, video streaming, and augmented reality require seamless, instantaneous data processing to deliver acceptable user experiences. Market surveys indicate that users abandon applications that demonstrate even slight latency issues, with a 100-millisecond delay increasing bounce rates by approximately 32% across digital platforms.

The enterprise sector demonstrates growing demand for real-time analytics capabilities, with organizations increasingly basing operational decisions on immediate data insights. This trend has created substantial market pressure for memory solutions that can support high-throughput, low-latency data processing at scale. Market forecasts project the real-time analytics segment to grow at a compound annual rate of 30% through 2027, significantly outpacing general IT infrastructure growth.

From a technical requirements perspective, the market increasingly demands memory solutions capable of handling diverse workloads simultaneously. Modern data centers must efficiently process traditional structured database operations alongside machine learning inference tasks and streaming analytics. This diversity of workloads creates complex memory access patterns that conventional DDR implementations struggle to optimize for concurrently.

Energy efficiency has emerged as another critical market requirement, particularly in data center environments where power consumption directly impacts operational costs. Market analysis shows that organizations are prioritizing memory solutions that deliver performance improvements without proportional increases in power consumption, creating demand for DDR5 implementations that optimize both speed and energy efficiency simultaneously.

Security requirements for real-time data processing have also intensified, with regulatory frameworks like GDPR and industry-specific compliance standards mandating robust data protection even during high-speed processing. This has created market demand for memory technologies that incorporate security features without compromising performance characteristics.

Market research reveals that latency requirements have become increasingly demanding, with financial trading systems now requiring sub-microsecond response times to maintain competitive advantage. Similarly, telecommunications networks supporting 5G infrastructure demand processing capabilities that can handle millions of concurrent connections with minimal delay. These market segments are particularly sensitive to memory performance bottlenecks, making DDR5 optimization techniques critically important.

Consumer expectations for real-time experiences have also evolved significantly. Modern applications in gaming, video streaming, and augmented reality require seamless, instantaneous data processing to deliver acceptable user experiences. Market surveys indicate that users abandon applications that demonstrate even slight latency issues, with a 100-millisecond delay increasing bounce rates by approximately 32% across digital platforms.

The enterprise sector demonstrates growing demand for real-time analytics capabilities, with organizations increasingly basing operational decisions on immediate data insights. This trend has created substantial market pressure for memory solutions that can support high-throughput, low-latency data processing at scale. Market forecasts project the real-time analytics segment to grow at a compound annual rate of 30% through 2027, significantly outpacing general IT infrastructure growth.

From a technical requirements perspective, the market increasingly demands memory solutions capable of handling diverse workloads simultaneously. Modern data centers must efficiently process traditional structured database operations alongside machine learning inference tasks and streaming analytics. This diversity of workloads creates complex memory access patterns that conventional DDR implementations struggle to optimize for concurrently.

Energy efficiency has emerged as another critical market requirement, particularly in data center environments where power consumption directly impacts operational costs. Market analysis shows that organizations are prioritizing memory solutions that deliver performance improvements without proportional increases in power consumption, creating demand for DDR5 implementations that optimize both speed and energy efficiency simultaneously.

Security requirements for real-time data processing have also intensified, with regulatory frameworks like GDPR and industry-specific compliance standards mandating robust data protection even during high-speed processing. This has created market demand for memory technologies that incorporate security features without compromising performance characteristics.

DDR5 Technical Limitations and Bottlenecks

Despite the significant advancements in DDR5 memory technology, several technical limitations and bottlenecks continue to challenge its optimization for real-time data applications. The primary constraint remains the inherent latency characteristics of DDR5 memory. While DDR5 offers substantially higher bandwidth compared to its predecessors, its CAS latency (CL) values have increased, resulting in higher absolute access times. For real-time data applications requiring immediate response, these increased latencies present a significant challenge, particularly in time-sensitive environments such as financial trading systems or autonomous vehicle control.

Power consumption represents another critical bottleneck in DDR5 implementation. Although DDR5 incorporates improved power management features like on-die voltage regulation, the higher operating frequencies and data rates inevitably lead to increased power consumption and thermal output. This creates design challenges for systems with strict power budgets or those operating in thermally constrained environments, potentially limiting the maximum achievable performance in practical deployments.

Signal integrity issues become more pronounced at DDR5's higher operating frequencies. As data rates exceed 4800 MT/s and approach 8400 MT/s, maintaining clean signal paths becomes exponentially more difficult. Factors such as crosstalk, reflection, and electromagnetic interference significantly impact reliable data transmission, requiring more sophisticated PCB designs and signal routing techniques. These challenges are particularly acute in dense server environments where multiple memory channels operate in close proximity.

Memory controller limitations also present substantial bottlenecks. Current controller architectures struggle to fully utilize DDR5's theoretical bandwidth while maintaining low latency. The complexity of managing multiple sub-channels, different refresh groups, and sophisticated power management features increases controller overhead, potentially reducing effective throughput in real-world applications.

Thermal management presents another significant challenge. DDR5 modules operating at high speeds generate considerable heat, which can lead to thermal throttling if not adequately addressed. This is particularly problematic in compact systems with limited airflow or in data centers where cooling efficiency directly impacts operational costs. The thermal constraints often force systems to operate memory at lower than optimal speeds to maintain stability.

Finally, software optimization lags behind hardware capabilities. Many existing applications and operating systems are not fully optimized to leverage DDR5's architectural advantages, such as its dual-channel architecture and improved command scheduling. This software-hardware mismatch creates inefficiencies that prevent systems from achieving theoretical performance levels, particularly in real-time data processing scenarios where memory access patterns are critical to overall system responsiveness.

Power consumption represents another critical bottleneck in DDR5 implementation. Although DDR5 incorporates improved power management features like on-die voltage regulation, the higher operating frequencies and data rates inevitably lead to increased power consumption and thermal output. This creates design challenges for systems with strict power budgets or those operating in thermally constrained environments, potentially limiting the maximum achievable performance in practical deployments.

Signal integrity issues become more pronounced at DDR5's higher operating frequencies. As data rates exceed 4800 MT/s and approach 8400 MT/s, maintaining clean signal paths becomes exponentially more difficult. Factors such as crosstalk, reflection, and electromagnetic interference significantly impact reliable data transmission, requiring more sophisticated PCB designs and signal routing techniques. These challenges are particularly acute in dense server environments where multiple memory channels operate in close proximity.

Memory controller limitations also present substantial bottlenecks. Current controller architectures struggle to fully utilize DDR5's theoretical bandwidth while maintaining low latency. The complexity of managing multiple sub-channels, different refresh groups, and sophisticated power management features increases controller overhead, potentially reducing effective throughput in real-world applications.

Thermal management presents another significant challenge. DDR5 modules operating at high speeds generate considerable heat, which can lead to thermal throttling if not adequately addressed. This is particularly problematic in compact systems with limited airflow or in data centers where cooling efficiency directly impacts operational costs. The thermal constraints often force systems to operate memory at lower than optimal speeds to maintain stability.

Finally, software optimization lags behind hardware capabilities. Many existing applications and operating systems are not fully optimized to leverage DDR5's architectural advantages, such as its dual-channel architecture and improved command scheduling. This software-hardware mismatch creates inefficiencies that prevent systems from achieving theoretical performance levels, particularly in real-time data processing scenarios where memory access patterns are critical to overall system responsiveness.

Current DDR5 Speed Optimization Solutions

01 Memory timing and clock optimization

Optimizing DDR5 memory speed involves precise timing control and clock synchronization techniques. These methods include adjusting memory clock frequencies, implementing advanced timing parameters, and enhancing signal integrity for high-speed data transfer. By fine-tuning these timing parameters, memory controllers can achieve higher data rates while maintaining system stability, which is crucial for DDR5's increased bandwidth capabilities.- Memory timing and clock optimization: Optimizing DDR5 memory speed involves precise timing adjustments and clock synchronization techniques. This includes implementing advanced clock distribution networks, reducing clock skew, and fine-tuning memory timing parameters. These optimizations help maintain signal integrity at higher frequencies and ensure stable data transfer rates, which is crucial for maximizing DDR5 performance while maintaining system stability.

- Memory controller architecture enhancements: Advanced memory controller designs specifically tailored for DDR5 can significantly improve memory speed. These controllers implement sophisticated request scheduling algorithms, enhanced buffer management, and optimized command sequencing. By reducing latency and improving throughput between the processor and memory modules, these architectural enhancements allow DDR5 memory to operate closer to its theoretical maximum bandwidth.

- Power management and thermal optimization: Effective power delivery and thermal management are essential for DDR5 speed optimization. This includes implementing advanced voltage regulation modules, dynamic power states, and thermal monitoring systems. By maintaining optimal operating temperatures and ensuring stable power delivery, these techniques prevent thermal throttling and voltage fluctuations that could otherwise limit memory performance at high speeds.

- Signal integrity and interface optimization: Maintaining signal integrity is critical for DDR5 memory operating at high speeds. This involves implementing advanced equalization techniques, optimized PCB routing, and improved I/O buffer designs. These methods help mitigate signal degradation, reduce electromagnetic interference, and minimize crosstalk between data lines, allowing for reliable data transmission at the increased speeds that DDR5 memory is capable of achieving.

- Memory training and calibration techniques: Sophisticated training and calibration algorithms are essential for optimizing DDR5 memory speed. These techniques include advanced read/write leveling, data eye training, and dynamic impedance calibration. By precisely adjusting timing parameters and signal characteristics during system initialization and operation, these methods ensure optimal data sampling points and signal margins, enabling reliable operation at maximum supported frequencies.

02 Memory controller architecture improvements

Advanced memory controller designs specifically tailored for DDR5 can significantly improve memory speed. These controllers implement sophisticated command scheduling, enhanced buffer management, and optimized data path architectures. By reducing latency and improving throughput in the controller itself, these architectural improvements allow DDR5 memory to operate closer to its theoretical maximum speed while handling the increased complexity of DDR5 protocols.Expand Specific Solutions03 Power management and thermal optimization

DDR5 memory speed optimization requires effective power management and thermal solutions. Techniques include dynamic voltage scaling, intelligent power state transitions, and thermal monitoring systems that prevent performance throttling. By maintaining optimal operating temperatures and efficiently managing power consumption, these methods ensure sustained high-speed operation without compromising reliability or exceeding thermal constraints, which becomes increasingly important at DDR5's higher operating frequencies.Expand Specific Solutions04 Signal integrity and interface optimization

Enhancing signal integrity is critical for DDR5 memory speed optimization. This involves advanced equalization techniques, improved PCB routing methodologies, and optimized I/O buffer designs. These approaches minimize signal distortion, reduce electromagnetic interference, and compensate for channel losses at high frequencies. By maintaining clean signal transmission between the memory controller and DDR5 modules, these techniques enable reliable operation at increased data rates without increasing error rates.Expand Specific Solutions05 Training and calibration algorithms

Sophisticated training and calibration algorithms are essential for maximizing DDR5 memory speed. These include advanced read/write leveling, data eye training, and adaptive equalization techniques that optimize timing parameters during system initialization and operation. By dynamically adjusting to system characteristics and environmental conditions, these algorithms ensure optimal timing margins and signal quality, allowing DDR5 memory to operate reliably at higher speeds across varying conditions and system configurations.Expand Specific Solutions

Leading DDR5 Manufacturers and Ecosystem

The DDR5 memory optimization market is currently in a growth phase, with increasing demand for real-time data processing solutions driving innovation. The market is projected to expand significantly as data-intensive applications proliferate across industries. Key players in this competitive landscape include established semiconductor giants like Intel, Micron Technology, and Samsung Electronics, who leverage their extensive R&D capabilities to develop advanced DDR5 technologies. Chinese companies such as Huawei, ChangXin Memory, and Inspur are rapidly gaining market share through aggressive investment in memory optimization solutions. Qualcomm and ZTE are focusing on mobile and telecommunications applications of DDR5, while research institutions like Xidian University contribute to technological advancement. The technology is approaching maturity in standard applications but continues to evolve for specialized high-performance computing and AI workloads.

Intel Corp.

Technical Solution: Intel has developed comprehensive DDR5 speed optimization techniques focusing on memory controller architecture and signal integrity. Their 13th Gen Core processors feature an advanced DDR5 memory controller that supports speeds up to 5600 MT/s with optimized timing parameters and reduced latency. Intel's Memory Latency Checker (MLC) tool enables real-time memory performance analysis and optimization. Their approach includes adaptive refresh management that intelligently schedules refresh operations to minimize impact on real-time data access. Intel has also implemented Decision Feedback Equalization (DFE) in their memory controllers to compensate for signal degradation at high speeds, allowing for more reliable data transmission at DDR5's higher frequencies. Their platform design guidelines incorporate specific PCB routing recommendations and power delivery optimizations to maintain signal integrity at maximum DDR5 speeds.

Strengths: Comprehensive ecosystem approach combining hardware, firmware, and software optimizations; strong integration with their CPU architectures; extensive testing and validation tools. Weaknesses: Solutions are often optimized primarily for their own platforms; premium implementations may have higher power requirements compared to some competitors.

ChangXin Memory Technologies, Inc.

Technical Solution: ChangXin Memory Technologies (CXMT) has developed several DDR5 speed optimization techniques focused on real-time data applications. Their approach includes an advanced prefetch architecture that doubles the prefetch from DDR4's 8n to DDR5's 16n, significantly improving burst data transfer rates for real-time applications. CXMT has implemented a multi-channel architecture with independent channel operation, allowing simultaneous read and write operations across different channels to reduce latency for time-sensitive data. Their DDR5 modules feature on-die ECC with real-time error detection and correction capabilities, maintaining data integrity at high speeds without compromising performance. CXMT has also developed proprietary signal integrity enhancement techniques including equalization circuits that compensate for channel loss at high frequencies, enabling stable operation at speeds up to 6400 MT/s. Their memory controller design incorporates adaptive training algorithms that optimize timing parameters based on specific operating conditions and workload characteristics.

Strengths: Strong focus on cost-effective solutions while maintaining competitive performance; growing domestic ecosystem support in China; good balance of performance and power efficiency. Weaknesses: More limited global market presence compared to larger competitors; fewer established partnerships with major platform providers outside domestic market.

Key Patents in DDR5 Latency Reduction

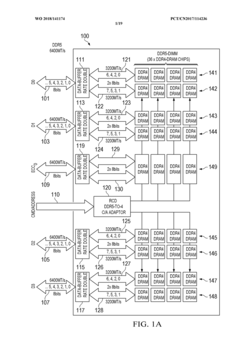

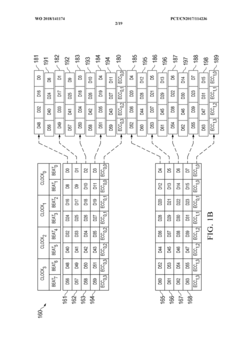

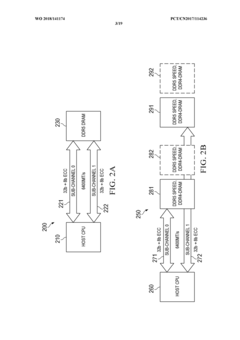

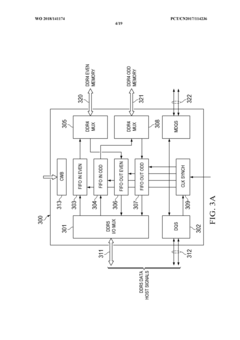

Systems and methods for utilizing DDR4-dram chips in hybrid DDR5-dimms and for cascading DDR5-dimms

PatentWO2018141174A1

Innovation

- Systems for utilizing DDR4-DRAM chips in hybrid DDR5-DIMMs to leverage existing DDR4 technology while transitioning to DDR5 standards.

- Methods for cascading DDR5-DIMMs to overcome the 1DPC limitation at high speeds (>4400MT/s) while maintaining memory capacity.

- Hybrid memory architecture that enables higher memory capacity at faster speeds compared to traditional DDR4 implementations limited to 1DPC at 3200MT/s.

Data processing circuit, data processing method, transmission circuit, and semiconductor memory

PatentPendingCN117176180A

Innovation

- A data processing circuit is designed, including a preprocessing module and a driving module. It converts the parallel initial data signal into a serial data signal to be processed and an auxiliary data signal, and adjusts the initial calibration code according to the preset scenario to obtain the target calibration. code, and then adjust the driving resistance and driving capability to generate a target signal that adapts to the preset scene.

Thermal Management in High-Speed DDR5 Systems

Thermal management has become a critical challenge in high-speed DDR5 systems as operating frequencies continue to increase beyond 6400MT/s. The elevated speeds generate significantly more heat, with thermal output increasing exponentially rather than linearly with frequency scaling. Modern DDR5 modules operating at peak performance can generate thermal loads exceeding 10W per module, creating potential reliability issues and performance degradation if not properly managed.

The primary thermal concerns in DDR5 systems stem from three sources: increased voltage requirements for high-speed operation, tighter signal integrity constraints necessitating more complex PCB designs, and higher refresh rates generating additional heat during memory operations. These factors combine to create thermal hotspots particularly around memory controllers and DRAM chips themselves, which can lead to timing violations and data corruption if temperatures exceed specified operating ranges.

Industry-standard thermal solutions for DDR5 include passive heat spreaders with enhanced surface area, typically constructed from aluminum or copper alloys with specialized thermal interface materials. More advanced implementations incorporate active cooling solutions such as miniaturized fans or liquid cooling pathways integrated directly into memory subsystems. These cooling technologies must balance thermal efficiency with space constraints, as DDR5 modules in server environments are often densely packed.

Thermal throttling mechanisms have been implemented at both hardware and firmware levels to prevent catastrophic failures. Modern DDR5 controllers incorporate on-die temperature sensors that continuously monitor thermal conditions and can dynamically adjust refresh rates, operating voltages, and even clock frequencies to maintain safe operating temperatures. These adaptive mechanisms help preserve data integrity while maximizing performance within thermal constraints.

Recent innovations in thermal management include phase-change materials embedded within DIMM heat spreaders, which absorb thermal energy during peak workloads and release it gradually during idle periods. Additionally, advanced thermal modeling techniques using computational fluid dynamics have enabled more precise placement of memory components and cooling structures, optimizing airflow patterns across memory subsystems.

For real-time data applications requiring maximum DDR5 performance, thermal considerations must be integrated into the earliest stages of system design rather than addressed as an afterthought. This includes proper chassis ventilation planning, strategic placement of memory modules relative to other heat-generating components, and implementation of thermal monitoring systems that can predict and prevent thermal throttling events before they impact application performance.

The primary thermal concerns in DDR5 systems stem from three sources: increased voltage requirements for high-speed operation, tighter signal integrity constraints necessitating more complex PCB designs, and higher refresh rates generating additional heat during memory operations. These factors combine to create thermal hotspots particularly around memory controllers and DRAM chips themselves, which can lead to timing violations and data corruption if temperatures exceed specified operating ranges.

Industry-standard thermal solutions for DDR5 include passive heat spreaders with enhanced surface area, typically constructed from aluminum or copper alloys with specialized thermal interface materials. More advanced implementations incorporate active cooling solutions such as miniaturized fans or liquid cooling pathways integrated directly into memory subsystems. These cooling technologies must balance thermal efficiency with space constraints, as DDR5 modules in server environments are often densely packed.

Thermal throttling mechanisms have been implemented at both hardware and firmware levels to prevent catastrophic failures. Modern DDR5 controllers incorporate on-die temperature sensors that continuously monitor thermal conditions and can dynamically adjust refresh rates, operating voltages, and even clock frequencies to maintain safe operating temperatures. These adaptive mechanisms help preserve data integrity while maximizing performance within thermal constraints.

Recent innovations in thermal management include phase-change materials embedded within DIMM heat spreaders, which absorb thermal energy during peak workloads and release it gradually during idle periods. Additionally, advanced thermal modeling techniques using computational fluid dynamics have enabled more precise placement of memory components and cooling structures, optimizing airflow patterns across memory subsystems.

For real-time data applications requiring maximum DDR5 performance, thermal considerations must be integrated into the earliest stages of system design rather than addressed as an afterthought. This includes proper chassis ventilation planning, strategic placement of memory modules relative to other heat-generating components, and implementation of thermal monitoring systems that can predict and prevent thermal throttling events before they impact application performance.

Power Efficiency vs Speed Trade-offs in DDR5

The optimization of DDR5 memory for real-time data applications presents a fundamental challenge in balancing power consumption against performance requirements. DDR5 technology inherently consumes more power than its predecessors due to higher operating frequencies and voltage requirements. This creates a critical trade-off scenario where system designers must carefully evaluate their priorities between maximizing data throughput and minimizing energy consumption.

At the architectural level, DDR5 implements several power-saving features that can be selectively engaged based on workload requirements. The introduction of multiple independent channels within a single DIMM allows for more granular power management, where unused channels can be placed in low-power states while active channels maintain full performance. This represents a significant advancement over DDR4's all-or-nothing approach to channel power states.

Voltage regulation has moved on-die with DDR5, replacing the traditional motherboard-based voltage regulation. This architectural shift enables more precise and responsive power delivery, allowing memory modules to rapidly transition between power states based on real-time data processing needs. The trade-off emerges in the form of increased thermal management requirements at the module level, necessitating more sophisticated cooling solutions.

Dynamic frequency scaling presents another critical trade-off mechanism. DDR5 systems can dynamically adjust operating frequencies based on workload demands, scaling down during periods of lower activity to conserve power. However, this introduces latency penalties during frequency transitions that can impact real-time data processing. System designers must carefully tune these transitions to avoid disrupting time-sensitive operations.

The implementation of advanced power management states in DDR5 provides additional granularity in the speed-power equation. These states include various self-refresh modes that preserve data while minimizing power consumption during idle periods. The challenge lies in determining the optimal threshold for entering these states, as premature power-down can result in performance penalties when data access resumes.

For real-time data applications specifically, the trade-off calculation must account for both average and worst-case latency scenarios. While aggressive power management may benefit overall system efficiency, it can introduce unpredictable latency spikes that compromise real-time processing guarantees. This necessitates application-specific optimization strategies that balance power efficiency against consistent performance requirements.

At the architectural level, DDR5 implements several power-saving features that can be selectively engaged based on workload requirements. The introduction of multiple independent channels within a single DIMM allows for more granular power management, where unused channels can be placed in low-power states while active channels maintain full performance. This represents a significant advancement over DDR4's all-or-nothing approach to channel power states.

Voltage regulation has moved on-die with DDR5, replacing the traditional motherboard-based voltage regulation. This architectural shift enables more precise and responsive power delivery, allowing memory modules to rapidly transition between power states based on real-time data processing needs. The trade-off emerges in the form of increased thermal management requirements at the module level, necessitating more sophisticated cooling solutions.

Dynamic frequency scaling presents another critical trade-off mechanism. DDR5 systems can dynamically adjust operating frequencies based on workload demands, scaling down during periods of lower activity to conserve power. However, this introduces latency penalties during frequency transitions that can impact real-time data processing. System designers must carefully tune these transitions to avoid disrupting time-sensitive operations.

The implementation of advanced power management states in DDR5 provides additional granularity in the speed-power equation. These states include various self-refresh modes that preserve data while minimizing power consumption during idle periods. The challenge lies in determining the optimal threshold for entering these states, as premature power-down can result in performance penalties when data access resumes.

For real-time data applications specifically, the trade-off calculation must account for both average and worst-case latency scenarios. While aggressive power management may benefit overall system efficiency, it can introduce unpredictable latency spikes that compromise real-time processing guarantees. This necessitates application-specific optimization strategies that balance power efficiency against consistent performance requirements.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!