DDR5 Use in Autonomous Vehicle Data Processing

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Automotive Implementation Goals

The evolution of DDR5 memory technology represents a significant advancement in the field of high-performance computing, with particular relevance to autonomous vehicle systems. DDR5 (Double Data Rate 5) emerged as the successor to DDR4, offering substantial improvements in bandwidth, capacity, and power efficiency that are critical for processing the massive data volumes generated by autonomous driving systems.

The development trajectory of DDR5 began around 2016, with JEDEC (Joint Electron Device Engineering Council) initiating the standardization process. By 2018, preliminary specifications were established, and the official standard was released in 2020. This evolution was driven by increasing demands for higher memory performance across multiple industries, with automotive applications emerging as a key driver due to the computational requirements of advanced driver assistance systems (ADAS) and autonomous driving platforms.

In the context of autonomous vehicles, DDR5 addresses several critical technical challenges. These vehicles generate approximately 4TB of data per day from various sensors including LiDAR, radar, cameras, and ultrasonic sensors. This data requires real-time processing for navigation, object detection, and decision-making functions. The previous DDR4 standard was approaching its limitations in handling such workloads, creating a technological bottleneck.

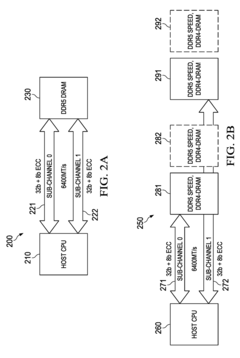

The primary technical goals for DDR5 implementation in autonomous vehicles include achieving data transfer rates exceeding 6400 MT/s (compared to DDR4's typical 3200 MT/s), reducing latency for real-time processing requirements, and improving power efficiency to address the energy constraints of vehicle electrical systems. Additionally, DDR5 aims to enhance reliability through features like on-die ECC (Error Correction Code), which is particularly crucial for automotive applications where memory errors could have safety implications.

Another significant objective is to support the increasing memory density requirements of autonomous driving systems. Modern autonomous platforms utilize complex neural networks and AI algorithms that demand substantial memory resources. DDR5's higher capacity modules (up to 128GB per DIMM compared to DDR4's 64GB) directly address this need, enabling more sophisticated on-board processing capabilities.

The automotive implementation of DDR5 also focuses on meeting stringent industry-specific requirements, including extended temperature ranges (-40°C to 125°C), enhanced durability for vibration resistance, and compliance with automotive functional safety standards such as ISO 26262. These specialized requirements necessitate modifications to standard DDR5 designs, creating a distinct automotive-grade variant of the technology.

Looking forward, the DDR5 roadmap for autonomous vehicles aims to achieve transfer rates of 8400 MT/s and beyond by 2025, with corresponding increases in channel efficiency and reductions in power consumption per bit transferred. These advancements will be essential to support the progression toward Level 4 and Level 5 autonomous driving capabilities, where computational demands will continue to escalate dramatically.

The development trajectory of DDR5 began around 2016, with JEDEC (Joint Electron Device Engineering Council) initiating the standardization process. By 2018, preliminary specifications were established, and the official standard was released in 2020. This evolution was driven by increasing demands for higher memory performance across multiple industries, with automotive applications emerging as a key driver due to the computational requirements of advanced driver assistance systems (ADAS) and autonomous driving platforms.

In the context of autonomous vehicles, DDR5 addresses several critical technical challenges. These vehicles generate approximately 4TB of data per day from various sensors including LiDAR, radar, cameras, and ultrasonic sensors. This data requires real-time processing for navigation, object detection, and decision-making functions. The previous DDR4 standard was approaching its limitations in handling such workloads, creating a technological bottleneck.

The primary technical goals for DDR5 implementation in autonomous vehicles include achieving data transfer rates exceeding 6400 MT/s (compared to DDR4's typical 3200 MT/s), reducing latency for real-time processing requirements, and improving power efficiency to address the energy constraints of vehicle electrical systems. Additionally, DDR5 aims to enhance reliability through features like on-die ECC (Error Correction Code), which is particularly crucial for automotive applications where memory errors could have safety implications.

Another significant objective is to support the increasing memory density requirements of autonomous driving systems. Modern autonomous platforms utilize complex neural networks and AI algorithms that demand substantial memory resources. DDR5's higher capacity modules (up to 128GB per DIMM compared to DDR4's 64GB) directly address this need, enabling more sophisticated on-board processing capabilities.

The automotive implementation of DDR5 also focuses on meeting stringent industry-specific requirements, including extended temperature ranges (-40°C to 125°C), enhanced durability for vibration resistance, and compliance with automotive functional safety standards such as ISO 26262. These specialized requirements necessitate modifications to standard DDR5 designs, creating a distinct automotive-grade variant of the technology.

Looking forward, the DDR5 roadmap for autonomous vehicles aims to achieve transfer rates of 8400 MT/s and beyond by 2025, with corresponding increases in channel efficiency and reductions in power consumption per bit transferred. These advancements will be essential to support the progression toward Level 4 and Level 5 autonomous driving capabilities, where computational demands will continue to escalate dramatically.

Market Demand for High-Speed Memory in Autonomous Vehicles

The autonomous vehicle market is experiencing unprecedented growth, with projections indicating a compound annual growth rate of 40% through 2030. This rapid expansion is driving an equally significant demand for high-performance memory solutions, particularly DDR5, which represents a critical component in the data processing architecture of self-driving vehicles.

Autonomous vehicles generate massive volumes of data—approximately 4TB per hour of operation—from multiple sensor arrays including LiDAR, radar, cameras, and ultrasonic sensors. This data requires immediate processing for real-time decision making, creating an urgent need for memory systems that can handle extreme bandwidth requirements while maintaining low latency performance.

Market research indicates that the automotive memory segment is expected to reach $15 billion by 2025, with high-speed memory for autonomous driving applications accounting for approximately 30% of this value. This represents a substantial opportunity for memory manufacturers who can deliver solutions optimized for the unique demands of autonomous vehicle computing platforms.

The transition from ADAS (Advanced Driver Assistance Systems) to fully autonomous vehicles is accelerating memory bandwidth requirements exponentially. While Level 2 autonomous systems typically require 8-16GB of DRAM, Level 4 and 5 autonomous vehicles demand 64-128GB of high-speed memory to support their sophisticated AI algorithms and sensor fusion operations.

Vehicle manufacturers and tier-one suppliers are increasingly prioritizing memory performance in their system architectures, recognizing it as a potential bottleneck in processing capabilities. Industry surveys reveal that 78% of automotive system designers consider memory bandwidth a critical factor in next-generation autonomous platforms, with 65% specifically evaluating DDR5 implementation for upcoming vehicle designs.

The market is also witnessing growing demand for memory solutions that address automotive-specific requirements beyond pure performance metrics. These include extended temperature ranges (-40°C to 125°C), enhanced reliability with 15+ year operational lifespans, functional safety compliance with ISO 26262 standards, and power efficiency to minimize thermal management challenges in vehicle environments.

Regional analysis shows that North America and Asia-Pacific currently lead in autonomous vehicle development and consequently in high-performance memory demand, with Europe following closely. China represents the fastest-growing market segment, with domestic memory manufacturers rapidly expanding production capacity to meet anticipated demand from the country's ambitious autonomous vehicle initiatives.

Autonomous vehicles generate massive volumes of data—approximately 4TB per hour of operation—from multiple sensor arrays including LiDAR, radar, cameras, and ultrasonic sensors. This data requires immediate processing for real-time decision making, creating an urgent need for memory systems that can handle extreme bandwidth requirements while maintaining low latency performance.

Market research indicates that the automotive memory segment is expected to reach $15 billion by 2025, with high-speed memory for autonomous driving applications accounting for approximately 30% of this value. This represents a substantial opportunity for memory manufacturers who can deliver solutions optimized for the unique demands of autonomous vehicle computing platforms.

The transition from ADAS (Advanced Driver Assistance Systems) to fully autonomous vehicles is accelerating memory bandwidth requirements exponentially. While Level 2 autonomous systems typically require 8-16GB of DRAM, Level 4 and 5 autonomous vehicles demand 64-128GB of high-speed memory to support their sophisticated AI algorithms and sensor fusion operations.

Vehicle manufacturers and tier-one suppliers are increasingly prioritizing memory performance in their system architectures, recognizing it as a potential bottleneck in processing capabilities. Industry surveys reveal that 78% of automotive system designers consider memory bandwidth a critical factor in next-generation autonomous platforms, with 65% specifically evaluating DDR5 implementation for upcoming vehicle designs.

The market is also witnessing growing demand for memory solutions that address automotive-specific requirements beyond pure performance metrics. These include extended temperature ranges (-40°C to 125°C), enhanced reliability with 15+ year operational lifespans, functional safety compliance with ISO 26262 standards, and power efficiency to minimize thermal management challenges in vehicle environments.

Regional analysis shows that North America and Asia-Pacific currently lead in autonomous vehicle development and consequently in high-performance memory demand, with Europe following closely. China represents the fastest-growing market segment, with domestic memory manufacturers rapidly expanding production capacity to meet anticipated demand from the country's ambitious autonomous vehicle initiatives.

DDR5 Technical Challenges in Automotive Environments

DDR5 memory technology faces significant challenges when deployed in autonomous vehicle environments due to the extreme operating conditions and reliability requirements unique to automotive applications. The automotive environment presents temperature extremes ranging from -40°C to 125°C, far exceeding typical consumer electronics specifications. These temperature variations can affect DDR5's timing parameters, signal integrity, and overall reliability, requiring specialized design considerations for thermal management systems.

Vibration and shock resistance represent another major challenge, as autonomous vehicles operate in dynamic environments with constant mechanical stresses. Standard DDR5 modules designed for stationary computing environments may experience connection failures, solder joint fractures, or physical damage when subjected to continuous vibration. This necessitates enhanced mechanical designs, reinforced solder joints, and specialized mounting solutions to ensure memory integrity during vehicle operation.

Electromagnetic interference (EMI) presents a particularly complex challenge in automotive environments. The dense electronic systems in autonomous vehicles generate significant electromagnetic noise that can compromise DDR5 signal integrity. Simultaneously, the high-speed operation of DDR5 (up to 6400 MT/s and beyond) creates its own EMI concerns that must be mitigated to prevent interference with critical vehicle systems like ADAS sensors, radar, and communication modules.

Power management challenges are amplified in automotive applications where energy efficiency directly impacts vehicle range and battery life. While DDR5 offers improved power efficiency compared to DDR4 through features like voltage regulation on DIMM, the automotive environment demands additional power optimization. The memory subsystem must maintain performance during voltage fluctuations common in vehicle electrical systems while implementing sophisticated power-saving modes that don't compromise rapid data access for critical driving functions.

Reliability and longevity requirements for automotive-grade DDR5 far exceed those of consumer applications. Autonomous vehicle components must maintain functionality for 10-15 years and 150,000+ miles under harsh conditions, compared to the 3-5 year expectation for consumer electronics. This necessitates enhanced error correction capabilities, on-die error detection, and specialized testing methodologies to ensure memory integrity throughout the vehicle's operational lifetime.

Security considerations add another layer of complexity, as autonomous vehicle memory systems must protect against both physical tampering and remote cyber attacks. DDR5 implementations must incorporate secure boot processes, memory encryption, and hardware-level security features to prevent unauthorized access to sensitive driving algorithms and sensor data, while maintaining the performance necessary for real-time processing.

Vibration and shock resistance represent another major challenge, as autonomous vehicles operate in dynamic environments with constant mechanical stresses. Standard DDR5 modules designed for stationary computing environments may experience connection failures, solder joint fractures, or physical damage when subjected to continuous vibration. This necessitates enhanced mechanical designs, reinforced solder joints, and specialized mounting solutions to ensure memory integrity during vehicle operation.

Electromagnetic interference (EMI) presents a particularly complex challenge in automotive environments. The dense electronic systems in autonomous vehicles generate significant electromagnetic noise that can compromise DDR5 signal integrity. Simultaneously, the high-speed operation of DDR5 (up to 6400 MT/s and beyond) creates its own EMI concerns that must be mitigated to prevent interference with critical vehicle systems like ADAS sensors, radar, and communication modules.

Power management challenges are amplified in automotive applications where energy efficiency directly impacts vehicle range and battery life. While DDR5 offers improved power efficiency compared to DDR4 through features like voltage regulation on DIMM, the automotive environment demands additional power optimization. The memory subsystem must maintain performance during voltage fluctuations common in vehicle electrical systems while implementing sophisticated power-saving modes that don't compromise rapid data access for critical driving functions.

Reliability and longevity requirements for automotive-grade DDR5 far exceed those of consumer applications. Autonomous vehicle components must maintain functionality for 10-15 years and 150,000+ miles under harsh conditions, compared to the 3-5 year expectation for consumer electronics. This necessitates enhanced error correction capabilities, on-die error detection, and specialized testing methodologies to ensure memory integrity throughout the vehicle's operational lifetime.

Security considerations add another layer of complexity, as autonomous vehicle memory systems must protect against both physical tampering and remote cyber attacks. DDR5 implementations must incorporate secure boot processes, memory encryption, and hardware-level security features to prevent unauthorized access to sensitive driving algorithms and sensor data, while maintaining the performance necessary for real-time processing.

Current DDR5 Integration Solutions for Vehicle Data Processing

01 DDR5 Memory Architecture and Design

DDR5 memory introduces advanced architectural designs that improve data processing capabilities. These innovations include enhanced memory controllers, optimized circuit layouts, and improved signal integrity for higher bandwidth operations. The architecture supports higher data rates while maintaining power efficiency through voltage regulation and thermal management techniques.- DDR5 memory architecture and data processing improvements: DDR5 memory introduces architectural improvements for enhanced data processing capabilities, including higher bandwidth, improved power efficiency, and advanced error correction. These innovations enable faster data transfer rates and more reliable memory operations in computing systems. The architecture supports more efficient data handling mechanisms and optimized memory controller designs that reduce latency and improve overall system performance.

- DDR5 memory controller design for data processing: Specialized memory controllers are designed to manage DDR5 memory operations efficiently. These controllers implement advanced data processing algorithms, command scheduling, and timing control mechanisms to maximize memory throughput. The controllers feature improved buffer management, enhanced power state transitions, and optimized refresh operations that collectively contribute to better data processing performance in high-demand computing environments.

- DDR5 data buffering and signal integrity solutions: Data buffering techniques and signal integrity solutions are implemented in DDR5 memory systems to ensure reliable data processing. These include advanced buffer designs, improved signal routing methodologies, and noise reduction techniques. The solutions address challenges related to high-speed data transfer, maintaining signal quality across memory channels, and ensuring data integrity during processing operations.

- DDR5 memory power management for data processing efficiency: Power management techniques specific to DDR5 memory improve data processing efficiency while reducing energy consumption. These include voltage regulation modules, dynamic power states, and intelligent power distribution systems. The implementations allow for optimized performance-per-watt metrics, enabling more sustainable data processing operations in various computing applications from mobile devices to data centers.

- DDR5 memory testing and validation methodologies: Specialized testing and validation methodologies are developed for DDR5 memory to ensure reliable data processing under various operating conditions. These include comprehensive test patterns, stress testing procedures, and performance validation frameworks. The methodologies help identify potential issues in memory operations, data integrity, and processing reliability, ensuring that DDR5 memory systems meet the demanding requirements of modern computing applications.

02 Data Processing Optimization for DDR5

Specific data processing techniques have been developed for DDR5 memory to enhance performance. These include advanced data buffering mechanisms, improved error correction algorithms, and optimized data path designs. These optimizations enable faster data transfer rates, reduced latency, and more efficient handling of large data volumes in computing systems.Expand Specific Solutions03 DDR5 Memory Controller Implementations

Memory controllers specifically designed for DDR5 implement sophisticated data processing capabilities. These controllers feature advanced command scheduling, improved refresh management, and intelligent power state transitions. The implementations include specialized interfaces that can dynamically adjust timing parameters to optimize data throughput based on workload characteristics.Expand Specific Solutions04 DDR5 Integration with Computing Systems

Integration methods for DDR5 memory in various computing platforms focus on maximizing data processing efficiency. These approaches include optimized motherboard designs, specialized interconnect technologies, and system-level power management. The integration techniques enable seamless communication between processors and DDR5 memory modules while supporting advanced features like on-die ECC and decision feedback equalization.Expand Specific Solutions05 DDR5 Testing and Validation Methodologies

Specialized testing and validation methodologies have been developed for DDR5 memory data processing. These include advanced signal integrity analysis, performance benchmarking under various workloads, and reliability testing procedures. The methodologies ensure that DDR5 memory modules meet specifications for data integrity, transfer rates, and long-term stability across different operating conditions.Expand Specific Solutions

Key DDR5 Manufacturers and Automotive Partners

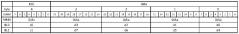

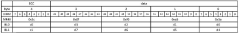

The autonomous vehicle data processing market utilizing DDR5 memory is in an early growth phase, characterized by rapid technological advancement and increasing market demand. The global market size is expanding significantly as autonomous driving capabilities evolve from Level 2 to Level 4/5, requiring more sophisticated data processing solutions. In terms of technical maturity, companies like Micron Technology and Samsung Electronics lead in DDR5 memory production, while Intel, AMD, and Baidu are advancing integration into autonomous vehicle systems. Huawei and ChangXin Memory Technologies are emerging as strong competitors in this space, particularly in the Asian market. Automotive specialists like DENSO and FAW are collaborating with semiconductor companies to optimize DDR5 implementation for vehicle-specific requirements, creating a complex ecosystem of partnerships across traditionally separate industries.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed an advanced DDR5-based computing architecture specifically for autonomous vehicle data processing applications, centered around their Kunpeng automotive-grade processors and specialized memory controllers. Their solution supports DDR5 data rates up to 6400MT/s while implementing sophisticated power management features that reduce system power consumption by approximately 28% compared to previous generation memory technologies[9]. Huawei's implementation includes specialized memory access optimizations for autonomous driving workloads, particularly for neural network inference operations and sensor data processing. Their DDR5 memory subsystem incorporates enhanced reliability features including on-die ECC, command/address parity checking, and write CRC capabilities that ensure data integrity in challenging automotive environments. Huawei has also developed proprietary algorithms that dynamically adjust DDR5 timing parameters based on workload characteristics, thermal conditions, and system power state[10]. Their solution includes comprehensive functional safety features designed to meet automotive requirements, with particular emphasis on memory subsystem monitoring, error detection and containment, and fault tolerance capabilities that support ASIL requirements for autonomous driving systems.

Strengths: Exceptional energy efficiency benefits electric vehicle platforms with limited power budgets; sophisticated memory management algorithms optimize performance for AI workloads; comprehensive safety features facilitate integration into safety-critical autonomous systems. Weaknesses: Geopolitical concerns may limit adoption in certain markets; more limited automotive ecosystem compared to established competitors; requires specialized expertise for optimal system integration.

Micron Technology, Inc.

Technical Solution: Micron has developed specialized DDR5 memory solutions specifically optimized for autonomous vehicle data processing requirements. Their automotive-grade DDR5 modules deliver up to 6400MT/s data rates with significantly improved power efficiency compared to DDR4, achieving up to 36% reduction in power consumption per bit transferred[1]. Micron's implementation includes enhanced reliability features critical for automotive applications, such as on-die ECC (Error Correction Code) that can detect and correct single-bit errors without CPU intervention. Their DDR5 solutions incorporate temperature sensors and thermal management capabilities designed to operate reliably in extreme automotive environments (-40°C to 125°C). Micron has also implemented advanced signal integrity features including equalization and decision feedback equalization (DFE) to maintain data integrity at high speeds in electrically noisy automotive environments[3]. Their automotive DDR5 modules are qualified to meet AEC-Q100 standards and include additional safety mechanisms to support ASIL (Automotive Safety Integrity Level) requirements for autonomous driving systems.

Strengths: Industry-leading reliability features specifically designed for automotive environments; AEC-Q100 qualification ensures durability in extreme conditions; advanced power management capabilities reduce thermal concerns in confined vehicle spaces. Weaknesses: Premium pricing compared to consumer-grade memory; requires sophisticated thermal management systems in vehicle designs; higher implementation complexity for automotive system integrators.

Critical Patents and Innovations in Automotive-Grade DDR5

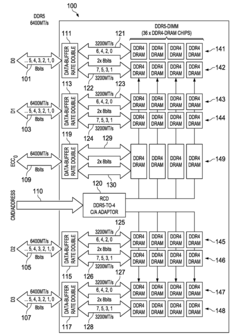

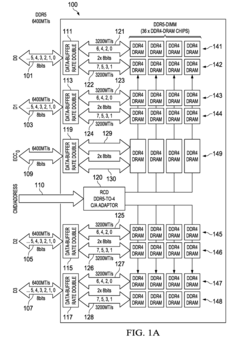

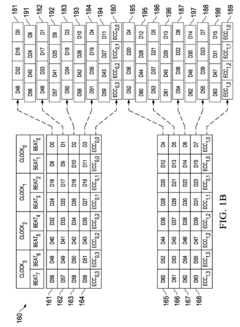

Systems and methods for utilizing DDR4-dram chips in hybrid DDR5-dimms and for cascading DDR5-dimms

PatentActiveUS20180225235A1

Innovation

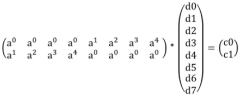

- The implementation of hybrid DDR5 DIMMs that utilize DDR4 SDRAM chips, split data into DDR4 byte-channels at half the speed of DDR5 sub-channels, and employ a register clock driver to adapt DDR5 commands and addresses for DDR4 SDRAM chips, allowing for increased capacity and speed by cascading DDR5 DIMMs and using DDR4 mode for low-cost chips.

Memory system and data processing method

PatentPendingCN118245272A

Innovation

- By introducing a write mode command generation circuit and a mode register in the memory controller, it can determine whether the write data is in the preset mode and generate a write mode command, thereby reducing data transmission power consumption and expanding the application scope of the write mode function.

Thermal Management Strategies for DDR5 in Vehicles

The thermal management of DDR5 memory in autonomous vehicles presents unique challenges due to the harsh operating environments and high-performance requirements. As vehicle data processing demands increase exponentially with advanced driver assistance systems (ADAS) and full autonomy, DDR5 modules generate significantly more heat than previous generations, operating at higher frequencies and voltages.

Effective thermal solutions must address both passive and active cooling strategies. Passive approaches include advanced thermal interface materials (TIMs) with higher thermal conductivity, optimized PCB designs with embedded heat spreaders, and strategic component placement to enhance natural convection. These passive methods provide the first line of defense against thermal buildup without consuming additional power.

Active cooling technologies complement these passive approaches through intelligent fan control systems that respond dynamically to memory temperature fluctuations. Liquid cooling solutions, once exclusive to high-performance computing, are now being adapted for automotive applications with sealed, maintenance-free designs that meet automotive reliability standards.

Temperature-aware memory management algorithms represent a software-based approach to thermal challenges. These systems can redistribute computational loads across memory modules, implement dynamic frequency scaling during peak thermal conditions, and even temporarily reduce memory bandwidth when thermal thresholds are approached, ensuring system stability without compromising critical functions.

Vehicle-specific considerations further complicate thermal management. The wide ambient temperature range (-40°C to +85°C) that automotive electronics must withstand requires adaptive cooling strategies. Limited space within vehicle computing enclosures necessitates compact cooling solutions, while power constraints in electric vehicles demand energy-efficient thermal management approaches.

Emerging technologies show promise for next-generation thermal management. Phase-change materials embedded in memory modules can absorb heat during intensive operations, while graphene-based thermal solutions offer superior heat dissipation in compact form factors. Advanced 3D packaging techniques with integrated cooling channels are also being developed specifically for automotive memory applications.

Standardization efforts across the industry are working to establish thermal design guidelines for automotive-grade DDR5 implementations, ensuring interoperability and reliability across different vehicle platforms and computing architectures. These collaborative approaches will be crucial as autonomous vehicle capabilities continue to advance, driving ever-increasing demands on memory subsystems.

Effective thermal solutions must address both passive and active cooling strategies. Passive approaches include advanced thermal interface materials (TIMs) with higher thermal conductivity, optimized PCB designs with embedded heat spreaders, and strategic component placement to enhance natural convection. These passive methods provide the first line of defense against thermal buildup without consuming additional power.

Active cooling technologies complement these passive approaches through intelligent fan control systems that respond dynamically to memory temperature fluctuations. Liquid cooling solutions, once exclusive to high-performance computing, are now being adapted for automotive applications with sealed, maintenance-free designs that meet automotive reliability standards.

Temperature-aware memory management algorithms represent a software-based approach to thermal challenges. These systems can redistribute computational loads across memory modules, implement dynamic frequency scaling during peak thermal conditions, and even temporarily reduce memory bandwidth when thermal thresholds are approached, ensuring system stability without compromising critical functions.

Vehicle-specific considerations further complicate thermal management. The wide ambient temperature range (-40°C to +85°C) that automotive electronics must withstand requires adaptive cooling strategies. Limited space within vehicle computing enclosures necessitates compact cooling solutions, while power constraints in electric vehicles demand energy-efficient thermal management approaches.

Emerging technologies show promise for next-generation thermal management. Phase-change materials embedded in memory modules can absorb heat during intensive operations, while graphene-based thermal solutions offer superior heat dissipation in compact form factors. Advanced 3D packaging techniques with integrated cooling channels are also being developed specifically for automotive memory applications.

Standardization efforts across the industry are working to establish thermal design guidelines for automotive-grade DDR5 implementations, ensuring interoperability and reliability across different vehicle platforms and computing architectures. These collaborative approaches will be crucial as autonomous vehicle capabilities continue to advance, driving ever-increasing demands on memory subsystems.

Functional Safety Compliance for Memory Systems

Functional safety compliance represents a critical consideration for memory systems deployed in autonomous vehicles, particularly with the integration of DDR5 technology. The ISO 26262 standard establishes comprehensive requirements for automotive electrical and electronic systems, mandating specific safety measures for memory components that process critical driving data.

DDR5 memory systems in autonomous vehicles must adhere to Automotive Safety Integrity Levels (ASIL), with most critical functions requiring ASIL D compliance—the highest safety classification. This necessitates implementation of robust error detection and correction capabilities beyond standard ECC, including in-line and background memory scrubbing, address/command parity checking, and cyclic redundancy checks (CRC) for data paths.

Memory controllers interfacing with DDR5 must incorporate safety mechanisms such as redundant execution paths, lockstep processing, and built-in self-test (BIST) capabilities. These features enable continuous monitoring of memory integrity during vehicle operation, with the ability to detect and mitigate potential failures before they impact critical driving functions.

Thermal management represents another crucial safety consideration, as DDR5 operates at higher frequencies and power densities compared to previous generations. Autonomous vehicle memory systems must implement advanced thermal monitoring and throttling mechanisms to prevent overheating scenarios that could compromise system reliability or trigger unexpected shutdowns during critical driving operations.

Supply chain considerations also factor into functional safety compliance, requiring memory manufacturers to maintain ISO 26262-certified development processes. This includes comprehensive documentation of design specifications, verification procedures, and failure mode analyses. Memory components must undergo rigorous qualification testing including temperature cycling, vibration resistance, and accelerated aging to validate their reliability under automotive conditions.

System-level redundancy strategies further enhance functional safety, with many autonomous vehicle architectures implementing dual or triple memory channels with voting mechanisms. This approach allows the system to continue operating safely even if individual memory components experience failures, providing essential fault tolerance for safety-critical applications.

The certification process for DDR5 memory systems in autonomous vehicles involves extensive documentation and testing, requiring manufacturers to demonstrate compliance through safety cases that address potential failure modes and their mitigation strategies. This process typically involves collaboration between memory suppliers, automotive OEMs, and third-party certification bodies to validate that all safety requirements are satisfied.

DDR5 memory systems in autonomous vehicles must adhere to Automotive Safety Integrity Levels (ASIL), with most critical functions requiring ASIL D compliance—the highest safety classification. This necessitates implementation of robust error detection and correction capabilities beyond standard ECC, including in-line and background memory scrubbing, address/command parity checking, and cyclic redundancy checks (CRC) for data paths.

Memory controllers interfacing with DDR5 must incorporate safety mechanisms such as redundant execution paths, lockstep processing, and built-in self-test (BIST) capabilities. These features enable continuous monitoring of memory integrity during vehicle operation, with the ability to detect and mitigate potential failures before they impact critical driving functions.

Thermal management represents another crucial safety consideration, as DDR5 operates at higher frequencies and power densities compared to previous generations. Autonomous vehicle memory systems must implement advanced thermal monitoring and throttling mechanisms to prevent overheating scenarios that could compromise system reliability or trigger unexpected shutdowns during critical driving operations.

Supply chain considerations also factor into functional safety compliance, requiring memory manufacturers to maintain ISO 26262-certified development processes. This includes comprehensive documentation of design specifications, verification procedures, and failure mode analyses. Memory components must undergo rigorous qualification testing including temperature cycling, vibration resistance, and accelerated aging to validate their reliability under automotive conditions.

System-level redundancy strategies further enhance functional safety, with many autonomous vehicle architectures implementing dual or triple memory channels with voting mechanisms. This approach allows the system to continue operating safely even if individual memory components experience failures, providing essential fault tolerance for safety-critical applications.

The certification process for DDR5 memory systems in autonomous vehicles involves extensive documentation and testing, requiring manufacturers to demonstrate compliance through safety cases that address potential failure modes and their mitigation strategies. This process typically involves collaboration between memory suppliers, automotive OEMs, and third-party certification bodies to validate that all safety requirements are satisfied.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!