Optimize DDR5 Performance in Energy-Conserving Algorithms

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Technology Evolution and Performance Goals

DDR5 memory technology represents a significant leap forward in the evolution of DRAM technology, building upon the foundations established by its predecessors. Since its introduction in 2020, DDR5 has marked a pivotal shift in memory architecture, offering substantial improvements in bandwidth, capacity, and power efficiency compared to DDR4. The technology evolution trajectory shows a consistent pattern of doubling performance approximately every three years, with DDR5 continuing this trend by delivering up to twice the performance of DDR4.

The core architectural advancements in DDR5 include an increased base frequency starting at 4800 MT/s (compared to DDR4's 3200 MT/s), with a roadmap extending to 8400 MT/s and beyond. This frequency enhancement directly translates to higher bandwidth capabilities, addressing the growing demands of data-intensive applications. Additionally, DDR5 introduces a dual-channel architecture within a single module, effectively doubling the accessible bandwidth without requiring additional memory channels on the processor side.

Power management represents another significant evolutionary step in DDR5, with the integration of Power Management Integrated Circuits (PMICs) directly onto the memory modules. This shift from motherboard-based power regulation to on-DIMM regulation enables more precise voltage control, reducing from DDR4's 1.2V to DDR5's 1.1V standard operating voltage, with further reductions anticipated in future iterations.

The primary performance goals for DDR5 in energy-conserving algorithms center around maximizing computational throughput while minimizing energy consumption. This balance is particularly crucial for applications in high-performance computing, artificial intelligence, and large-scale data processing, where memory operations can account for up to 40% of system power consumption. Specific targets include achieving energy efficiency improvements of 30-40% per bit transferred compared to DDR4 systems.

Another key performance objective involves optimizing the newly introduced Decision Feedback Equalization (DFE) and adaptive equalization features in DDR5, which compensate for signal integrity issues at higher frequencies. Properly leveraging these capabilities can significantly reduce error rates and retransmissions, directly contributing to energy conservation by minimizing redundant operations.

The technology roadmap also emphasizes enhancing DDR5's reliability features, including on-die ECC (Error Correction Code) capabilities. While primarily designed to improve data integrity, these features also present opportunities for energy optimization by reducing the computational overhead associated with error detection and correction at the system level, particularly in scenarios where algorithmic precision can be traded for energy efficiency.

The core architectural advancements in DDR5 include an increased base frequency starting at 4800 MT/s (compared to DDR4's 3200 MT/s), with a roadmap extending to 8400 MT/s and beyond. This frequency enhancement directly translates to higher bandwidth capabilities, addressing the growing demands of data-intensive applications. Additionally, DDR5 introduces a dual-channel architecture within a single module, effectively doubling the accessible bandwidth without requiring additional memory channels on the processor side.

Power management represents another significant evolutionary step in DDR5, with the integration of Power Management Integrated Circuits (PMICs) directly onto the memory modules. This shift from motherboard-based power regulation to on-DIMM regulation enables more precise voltage control, reducing from DDR4's 1.2V to DDR5's 1.1V standard operating voltage, with further reductions anticipated in future iterations.

The primary performance goals for DDR5 in energy-conserving algorithms center around maximizing computational throughput while minimizing energy consumption. This balance is particularly crucial for applications in high-performance computing, artificial intelligence, and large-scale data processing, where memory operations can account for up to 40% of system power consumption. Specific targets include achieving energy efficiency improvements of 30-40% per bit transferred compared to DDR4 systems.

Another key performance objective involves optimizing the newly introduced Decision Feedback Equalization (DFE) and adaptive equalization features in DDR5, which compensate for signal integrity issues at higher frequencies. Properly leveraging these capabilities can significantly reduce error rates and retransmissions, directly contributing to energy conservation by minimizing redundant operations.

The technology roadmap also emphasizes enhancing DDR5's reliability features, including on-die ECC (Error Correction Code) capabilities. While primarily designed to improve data integrity, these features also present opportunities for energy optimization by reducing the computational overhead associated with error detection and correction at the system level, particularly in scenarios where algorithmic precision can be traded for energy efficiency.

Market Demand for Energy-Efficient Memory Solutions

The global market for energy-efficient memory solutions has witnessed substantial growth in recent years, driven primarily by the increasing power consumption concerns in data centers and cloud computing environments. As computational demands continue to escalate, organizations are facing mounting pressure to optimize their energy footprint while maintaining or improving performance metrics. This dichotomy has created a robust demand for memory technologies that can deliver enhanced performance with reduced power requirements.

DDR5 memory represents a significant advancement in addressing these market needs, offering substantial improvements in data rates, capacity, and power efficiency compared to its predecessors. Market research indicates that the data center segment alone is projected to consume over 60% of all DDR5 memory shipments by 2025, highlighting the critical importance of energy efficiency in this sector.

The enterprise computing market has emerged as a particularly strong driver for energy-efficient memory solutions. With the total cost of ownership (TCO) becoming an increasingly important metric for IT decision-makers, the operational expenditure associated with power consumption has gained prominence in procurement considerations. Studies demonstrate that memory subsystems can account for up to 40% of server power consumption in certain workloads, making memory optimization a high-priority target for energy conservation efforts.

Mobile computing and edge devices represent another significant market segment demanding energy-efficient memory solutions. As computational capabilities expand at the network edge, the constraints of limited power availability and thermal management challenges have intensified the need for memory technologies that can deliver performance within strict power envelopes. This trend is particularly evident in IoT deployments, where device longevity and operational autonomy are directly tied to energy efficiency.

The financial services sector has emerged as an early adopter of energy-efficient memory technologies, driven by the dual requirements of high-performance computing for algorithmic trading and regulatory pressures to reduce carbon footprints. Similarly, the healthcare and scientific computing sectors are increasingly investing in memory solutions that can support complex simulations and data analysis while minimizing energy consumption.

Geographically, North America and Asia-Pacific regions dominate the market demand for energy-efficient memory solutions, with Europe showing accelerated adoption rates due to stringent environmental regulations and sustainability initiatives. The market is expected to maintain a compound annual growth rate exceeding 15% through 2027, reflecting the sustained demand for technologies that can optimize the performance-per-watt equation in modern computing environments.

DDR5 memory represents a significant advancement in addressing these market needs, offering substantial improvements in data rates, capacity, and power efficiency compared to its predecessors. Market research indicates that the data center segment alone is projected to consume over 60% of all DDR5 memory shipments by 2025, highlighting the critical importance of energy efficiency in this sector.

The enterprise computing market has emerged as a particularly strong driver for energy-efficient memory solutions. With the total cost of ownership (TCO) becoming an increasingly important metric for IT decision-makers, the operational expenditure associated with power consumption has gained prominence in procurement considerations. Studies demonstrate that memory subsystems can account for up to 40% of server power consumption in certain workloads, making memory optimization a high-priority target for energy conservation efforts.

Mobile computing and edge devices represent another significant market segment demanding energy-efficient memory solutions. As computational capabilities expand at the network edge, the constraints of limited power availability and thermal management challenges have intensified the need for memory technologies that can deliver performance within strict power envelopes. This trend is particularly evident in IoT deployments, where device longevity and operational autonomy are directly tied to energy efficiency.

The financial services sector has emerged as an early adopter of energy-efficient memory technologies, driven by the dual requirements of high-performance computing for algorithmic trading and regulatory pressures to reduce carbon footprints. Similarly, the healthcare and scientific computing sectors are increasingly investing in memory solutions that can support complex simulations and data analysis while minimizing energy consumption.

Geographically, North America and Asia-Pacific regions dominate the market demand for energy-efficient memory solutions, with Europe showing accelerated adoption rates due to stringent environmental regulations and sustainability initiatives. The market is expected to maintain a compound annual growth rate exceeding 15% through 2027, reflecting the sustained demand for technologies that can optimize the performance-per-watt equation in modern computing environments.

DDR5 Technical Challenges and Power Constraints

DDR5 memory technology represents a significant advancement over previous generations, offering higher bandwidth, increased capacity, and improved power efficiency. However, optimizing DDR5 performance while maintaining energy efficiency presents several technical challenges that must be addressed for effective implementation in energy-conserving algorithms.

The primary power constraint in DDR5 systems stems from the increased operating frequency, which can reach up to 6400 MT/s compared to DDR4's typical 3200 MT/s. This higher frequency inherently increases power consumption, creating a fundamental tension between performance and energy efficiency. The voltage reduction from DDR4's 1.2V to DDR5's 1.1V partially mitigates this issue but introduces stability challenges at higher speeds.

DDR5's architectural changes introduce additional power management complexities. The transition to dual-channel architecture with independent 32-bit channels increases parallelism but requires more sophisticated power distribution. The on-die ECC (Error Correction Code) functionality, while improving data integrity, adds computational overhead that consumes additional power during memory operations.

Another significant challenge lies in the thermal management of DDR5 modules. Higher operating frequencies generate more heat, which can lead to thermal throttling and reduced performance if not properly managed. This is particularly problematic in dense computing environments where cooling solutions may be limited by space or noise constraints.

The decision-making logic in memory controllers must be optimized to balance performance and power consumption. Traditional memory access patterns may not be optimal for DDR5's architecture, requiring new algorithms that can effectively utilize the increased parallelism while minimizing unnecessary power expenditure. The increased complexity of DDR5's command structure also demands more sophisticated controller logic.

Power-saving features in DDR5, such as the improved refresh mechanisms and fine-grained power management, offer potential solutions but require careful implementation. The new refresh management system reduces refresh operations by 16 times compared to DDR4, but leveraging this feature effectively requires changes to memory access patterns and timing parameters.

Voltage regulation presents another challenge, as DDR5 moves the voltage regulator module (VRM) onto the DIMM itself. While this improves signal integrity and power delivery, it also increases the complexity of power management on the memory module and can lead to increased heat generation in close proximity to memory cells.

The interaction between DDR5 memory and energy-conserving algorithms introduces additional layers of complexity. Algorithms must be redesigned to take advantage of DDR5's architectural benefits while avoiding patterns that trigger high power states unnecessarily. This requires deep understanding of both the memory technology and the specific algorithmic requirements.

The primary power constraint in DDR5 systems stems from the increased operating frequency, which can reach up to 6400 MT/s compared to DDR4's typical 3200 MT/s. This higher frequency inherently increases power consumption, creating a fundamental tension between performance and energy efficiency. The voltage reduction from DDR4's 1.2V to DDR5's 1.1V partially mitigates this issue but introduces stability challenges at higher speeds.

DDR5's architectural changes introduce additional power management complexities. The transition to dual-channel architecture with independent 32-bit channels increases parallelism but requires more sophisticated power distribution. The on-die ECC (Error Correction Code) functionality, while improving data integrity, adds computational overhead that consumes additional power during memory operations.

Another significant challenge lies in the thermal management of DDR5 modules. Higher operating frequencies generate more heat, which can lead to thermal throttling and reduced performance if not properly managed. This is particularly problematic in dense computing environments where cooling solutions may be limited by space or noise constraints.

The decision-making logic in memory controllers must be optimized to balance performance and power consumption. Traditional memory access patterns may not be optimal for DDR5's architecture, requiring new algorithms that can effectively utilize the increased parallelism while minimizing unnecessary power expenditure. The increased complexity of DDR5's command structure also demands more sophisticated controller logic.

Power-saving features in DDR5, such as the improved refresh mechanisms and fine-grained power management, offer potential solutions but require careful implementation. The new refresh management system reduces refresh operations by 16 times compared to DDR4, but leveraging this feature effectively requires changes to memory access patterns and timing parameters.

Voltage regulation presents another challenge, as DDR5 moves the voltage regulator module (VRM) onto the DIMM itself. While this improves signal integrity and power delivery, it also increases the complexity of power management on the memory module and can lead to increased heat generation in close proximity to memory cells.

The interaction between DDR5 memory and energy-conserving algorithms introduces additional layers of complexity. Algorithms must be redesigned to take advantage of DDR5's architectural benefits while avoiding patterns that trigger high power states unnecessarily. This requires deep understanding of both the memory technology and the specific algorithmic requirements.

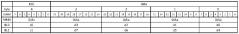

Current Energy-Conserving Algorithms for DDR5

01 DDR5 Memory Architecture Enhancements

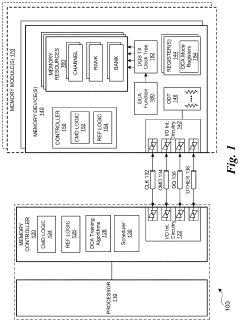

DDR5 memory introduces architectural improvements over previous generations, including higher bandwidth capabilities, improved channel efficiency, and enhanced memory density. These architectural enhancements enable better overall system performance through features like independent channel operation and optimized internal bank structures, allowing for more efficient data handling and reduced latency in high-performance computing environments.- DDR5 Memory Architecture and Speed Improvements: DDR5 memory introduces architectural improvements that significantly enhance performance compared to previous generations. These improvements include higher data transfer rates, increased bandwidth, and more efficient channel utilization. The architecture supports higher frequencies and improved signal integrity, allowing for faster data processing and reduced latency in computing systems.

- Power Management and Efficiency in DDR5: DDR5 memory implements advanced power management features that optimize energy consumption while maintaining high performance. These innovations include on-die voltage regulation, improved power delivery networks, and more granular power states. The enhanced power efficiency allows DDR5 modules to operate at higher speeds while consuming less energy per bit transferred, making them suitable for both high-performance computing and energy-sensitive applications.

- DDR5 Memory Controller Optimizations: Memory controllers designed specifically for DDR5 incorporate various optimizations to fully leverage the capabilities of the new memory standard. These controllers feature improved command scheduling, enhanced prefetching algorithms, and more sophisticated error correction mechanisms. The optimized controllers can better manage the increased number of banks and bank groups in DDR5, resulting in more efficient memory access patterns and higher overall system performance.

- DDR5 Integration with Advanced Computing Systems: DDR5 memory is designed to integrate seamlessly with advanced computing architectures, including multi-core processors, AI accelerators, and high-performance servers. The integration involves specialized interface designs, optimized memory subsystems, and enhanced compatibility with various computing platforms. This integration enables DDR5 to deliver superior performance in data-intensive applications such as artificial intelligence, machine learning, and high-performance computing.

- Reliability and Error Handling in DDR5 Memory: DDR5 memory incorporates advanced error detection and correction mechanisms to ensure data integrity at higher operating speeds. These features include on-die ECC (Error Correction Code), improved refresh schemes, and more robust signal integrity solutions. The enhanced reliability features allow DDR5 memory to maintain stable performance even under demanding workloads and help prevent data corruption in critical applications.

02 Power Management and Efficiency in DDR5

DDR5 memory implements advanced power management features that significantly improve energy efficiency while maintaining high performance. These innovations include on-die voltage regulation, improved power delivery networks, and more granular power states. The enhanced power management capabilities allow systems to dynamically adjust power consumption based on workload demands, resulting in better performance-per-watt metrics for data centers and mobile applications.Expand Specific Solutions03 DDR5 Memory Controller Optimizations

Memory controllers specifically designed for DDR5 incorporate sophisticated algorithms and hardware features to maximize performance. These controllers implement advanced scheduling techniques, improved prefetching mechanisms, and optimized command sequencing to reduce latency and increase throughput. The controllers also feature enhanced error detection and correction capabilities, ensuring data integrity while maintaining high performance under various workload conditions.Expand Specific Solutions04 DDR5 Integration with Computing Systems

The integration of DDR5 memory with modern computing architectures requires specialized interface designs and system-level optimizations. These include improved signal integrity solutions, enhanced thermal management techniques, and optimized motherboard layouts. The integration approaches focus on maximizing the benefits of DDR5's higher data rates while addressing challenges related to signal integrity at higher frequencies, resulting in more reliable and higher-performing computing systems.Expand Specific Solutions05 DDR5 Performance Testing and Validation

Specialized methodologies and tools have been developed for testing and validating DDR5 memory performance. These include advanced benchmarking techniques, stress testing procedures, and performance analysis frameworks that can accurately measure and characterize DDR5 memory behavior under various workloads. The testing approaches help identify performance bottlenecks and validate that DDR5 memory systems meet their specified performance targets across different operating conditions.Expand Specific Solutions

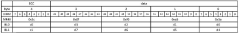

Key DDR5 Manufacturers and Industry Ecosystem

The DDR5 performance optimization in energy-conserving algorithms market is currently in its growth phase, with increasing adoption across computing platforms. The market is projected to expand significantly as data centers and mobile devices prioritize energy efficiency alongside performance. Leading players like Micron Technology, Samsung, and SK Hynix dominate the core memory manufacturing, while Qualcomm, AMD, and Intel are advancing application-specific optimizations. Companies including Rambus and Etron Technology are developing specialized buffer solutions, while research institutions like Zhejiang University contribute to algorithmic innovations. The competitive landscape features established semiconductor giants investing heavily in R&D alongside emerging specialized firms focusing on energy-efficient memory controllers and software optimization techniques, creating a dynamic ecosystem balancing performance gains with power conservation requirements.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed mobile-focused DDR5 optimization technologies emphasizing energy efficiency in battery-powered devices. Their Adaptive Memory Subsystem dynamically scales memory bandwidth and power based on application requirements, reducing memory power consumption by up to 40% during typical smartphone usage patterns. Qualcomm's Memory Traffic Shaping algorithms intelligently schedule memory accesses to maximize burst efficiency and minimize power-hungry transitions between power states. Their DDR5 controllers implement specialized Quality of Service mechanisms that prioritize latency-sensitive tasks while allowing background tasks to operate in more energy-efficient modes. Qualcomm has also developed advanced prefetching algorithms that leverage AI-based prediction to reduce overall memory accesses while maintaining performance. Their System Power Collapse technology enables ultra-fast transitions between full-power and near-zero power states, allowing aggressive power management even in interactive applications.

Strengths: Unmatched expertise in mobile power constraints leads to highly optimized solutions for battery-powered devices; tight integration with SoC design enables system-level optimizations. Weaknesses: Solutions are primarily optimized for mobile workloads and may not scale optimally to server environments; some techniques trade peak performance for energy efficiency.

Micron Technology, Inc.

Technical Solution: Micron has pioneered several DDR5 energy conservation technologies focused on both hardware and algorithmic optimizations. Their Extended Temperature Range (ETR) DDR5 modules incorporate adaptive refresh algorithms that dynamically adjust refresh rates based on operating temperature, reducing refresh power by up to 45% in typical server environments. Micron's Smart Refresh Management technology implements intelligent refresh scheduling that tracks actual data retention needs rather than using worst-case timing parameters. Their Targeted Row Refresh mechanism minimizes the power impact of row hammering protection by selectively refreshing only vulnerable rows. Micron has also developed specialized DDR5 modules with integrated power management controllers that implement fine-grained voltage regulation directly on the DIMM, reducing power delivery losses by approximately 20%. Their latest DDR5 modules feature on-die ECC and advanced signal integrity features that allow reliable operation at lower voltages, contributing to overall system energy efficiency.

Strengths: Direct control over memory die design enables optimizations at the most fundamental level; extensive testing capabilities ensure reliability while pushing energy efficiency boundaries. Weaknesses: Some advanced features require specific motherboard support; optimization techniques sometimes prioritize server workloads over client computing patterns.

Critical Patents in DDR5 Power Optimization

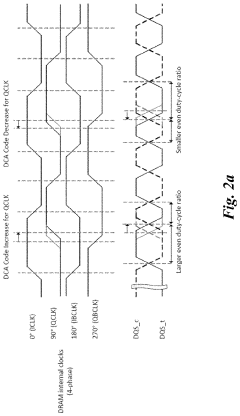

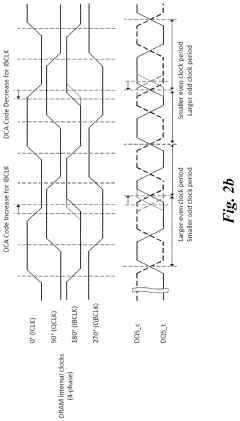

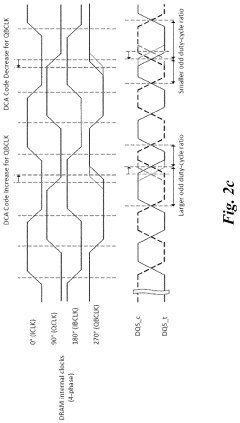

Duty cycle adjuster optimization training algorithm to minimize the jitter associated with DDR5 dram transmitter

PatentActiveUS20210390991A1

Innovation

- The implementation of Duty Cycle Adjuster (DCA) training algorithms, including Basic and Advanced DCA training algorithms, to optimize the DQS transmitter clock trees by adjusting DCA mode registers, reducing duty cycle errors and phase mismatches, thereby minimizing jitter in DDR5 DRAM transmitters.

Memory system and data processing method

PatentPendingCN118245272A

Innovation

- By introducing a write mode command generation circuit and a mode register in the memory controller, it can determine whether the write data is in the preset mode and generate a write mode command, thereby reducing data transmission power consumption and expanding the application scope of the write mode function.

Thermal Management Strategies for DDR5 Systems

Thermal management has become a critical factor in optimizing DDR5 performance, particularly when implementing energy-conserving algorithms. As DDR5 modules operate at higher frequencies and voltages compared to previous generations, they generate significantly more heat during operation. This thermal challenge is further complicated by the increased density of memory components and the integration of on-die ECC (Error Correction Code) and power management ICs directly onto the memory modules.

The primary thermal management approaches for DDR5 systems can be categorized into passive and active cooling strategies. Passive cooling solutions include heat spreaders and thermal pads that efficiently dissipate heat from memory modules to the surrounding environment. These solutions are particularly effective in systems where airflow is already optimized and additional active cooling components would increase power consumption, contradicting energy conservation goals.

Active cooling strategies involve dedicated fans, liquid cooling systems, or phase-change materials specifically designed for memory modules. While these solutions provide superior thermal performance, they must be carefully balanced against their energy consumption to maintain the overall efficiency of energy-conserving algorithms. Advanced implementations utilize dynamic thermal throttling that adjusts memory performance based on real-time temperature monitoring.

Thermal simulation and modeling have become essential tools in DDR5 system design. Computational fluid dynamics (CFD) simulations allow engineers to predict hotspots and optimize airflow patterns before physical prototyping. These simulations are particularly valuable when designing systems that must balance performance with energy efficiency, as they can identify potential thermal bottlenecks that might otherwise compromise algorithm efficiency.

Recent innovations in DDR5 thermal management include temperature-aware memory controllers that dynamically adjust refresh rates and access patterns based on thermal conditions. These controllers can prioritize cooler memory ranks or channels, distributing workloads to minimize thermal peaks while maintaining overall system performance. This approach is particularly beneficial for energy-conserving algorithms that can tolerate variable memory access latencies.

Material science advancements have also contributed significantly to DDR5 thermal management. New composite materials with higher thermal conductivity are being employed in heat spreaders, while phase-change materials embedded in memory modules provide thermal buffering during peak workloads. These materials help maintain stable operating temperatures without requiring additional energy for active cooling.

For data centers implementing energy-conserving algorithms at scale, rack-level thermal management strategies have evolved to specifically address DDR5 requirements. These include precision-directed airflow systems and intelligent workload distribution that considers memory thermal characteristics alongside traditional CPU utilization metrics when scheduling tasks.

The primary thermal management approaches for DDR5 systems can be categorized into passive and active cooling strategies. Passive cooling solutions include heat spreaders and thermal pads that efficiently dissipate heat from memory modules to the surrounding environment. These solutions are particularly effective in systems where airflow is already optimized and additional active cooling components would increase power consumption, contradicting energy conservation goals.

Active cooling strategies involve dedicated fans, liquid cooling systems, or phase-change materials specifically designed for memory modules. While these solutions provide superior thermal performance, they must be carefully balanced against their energy consumption to maintain the overall efficiency of energy-conserving algorithms. Advanced implementations utilize dynamic thermal throttling that adjusts memory performance based on real-time temperature monitoring.

Thermal simulation and modeling have become essential tools in DDR5 system design. Computational fluid dynamics (CFD) simulations allow engineers to predict hotspots and optimize airflow patterns before physical prototyping. These simulations are particularly valuable when designing systems that must balance performance with energy efficiency, as they can identify potential thermal bottlenecks that might otherwise compromise algorithm efficiency.

Recent innovations in DDR5 thermal management include temperature-aware memory controllers that dynamically adjust refresh rates and access patterns based on thermal conditions. These controllers can prioritize cooler memory ranks or channels, distributing workloads to minimize thermal peaks while maintaining overall system performance. This approach is particularly beneficial for energy-conserving algorithms that can tolerate variable memory access latencies.

Material science advancements have also contributed significantly to DDR5 thermal management. New composite materials with higher thermal conductivity are being employed in heat spreaders, while phase-change materials embedded in memory modules provide thermal buffering during peak workloads. These materials help maintain stable operating temperatures without requiring additional energy for active cooling.

For data centers implementing energy-conserving algorithms at scale, rack-level thermal management strategies have evolved to specifically address DDR5 requirements. These include precision-directed airflow systems and intelligent workload distribution that considers memory thermal characteristics alongside traditional CPU utilization metrics when scheduling tasks.

Benchmarking Methodologies for DDR5 Performance

Benchmarking methodologies for DDR5 performance evaluation require systematic approaches to accurately measure and compare memory subsystem capabilities within energy-conserving algorithms. Traditional benchmarking tools like STREAM, RAMspeed, and SPEC CPU have been adapted to accommodate DDR5's unique features, including higher bandwidth, improved power efficiency, and enhanced channel architecture.

Memory latency testing has evolved significantly for DDR5 systems, with specialized tools now measuring not only raw access times but also the effectiveness of on-die ECC and decision feedback equalization circuits. These measurements must be conducted across various power states to understand performance characteristics under energy conservation constraints.

Bandwidth assessment methodologies have been refined to account for DDR5's dual-channel architecture and improved burst capabilities. Modern benchmarking approaches now incorporate varied access patterns that simulate real-world algorithm behaviors, particularly those optimized for energy efficiency. Sequential, random, and mixed access patterns provide comprehensive insights into how memory performance affects algorithm execution under power constraints.

Power efficiency metrics have become central to DDR5 benchmarking, with methodologies now incorporating performance-per-watt measurements across different workloads. This approach allows for direct comparison between performance optimization and energy conservation objectives, revealing optimal operational parameters for specific algorithmic requirements.

Workload-specific benchmarking has emerged as a critical methodology, with custom test suites designed to simulate particular algorithm classes. For energy-conserving algorithms, benchmarks now incorporate dynamic frequency scaling scenarios, power state transitions, and thermal throttling conditions to provide realistic performance expectations.

Comparative analysis frameworks have been standardized to enable meaningful cross-platform evaluation. These frameworks normalize results across different system configurations, allowing organizations to make informed decisions about memory subsystem design based on their specific energy and performance requirements.

Reliability testing under varied voltage conditions has become an essential component of DDR5 benchmarking methodologies, particularly for systems implementing aggressive power management. These tests evaluate memory stability during frequent transitions between power states, identifying potential performance degradation points in energy-conserving implementations.

Memory latency testing has evolved significantly for DDR5 systems, with specialized tools now measuring not only raw access times but also the effectiveness of on-die ECC and decision feedback equalization circuits. These measurements must be conducted across various power states to understand performance characteristics under energy conservation constraints.

Bandwidth assessment methodologies have been refined to account for DDR5's dual-channel architecture and improved burst capabilities. Modern benchmarking approaches now incorporate varied access patterns that simulate real-world algorithm behaviors, particularly those optimized for energy efficiency. Sequential, random, and mixed access patterns provide comprehensive insights into how memory performance affects algorithm execution under power constraints.

Power efficiency metrics have become central to DDR5 benchmarking, with methodologies now incorporating performance-per-watt measurements across different workloads. This approach allows for direct comparison between performance optimization and energy conservation objectives, revealing optimal operational parameters for specific algorithmic requirements.

Workload-specific benchmarking has emerged as a critical methodology, with custom test suites designed to simulate particular algorithm classes. For energy-conserving algorithms, benchmarks now incorporate dynamic frequency scaling scenarios, power state transitions, and thermal throttling conditions to provide realistic performance expectations.

Comparative analysis frameworks have been standardized to enable meaningful cross-platform evaluation. These frameworks normalize results across different system configurations, allowing organizations to make informed decisions about memory subsystem design based on their specific energy and performance requirements.

Reliability testing under varied voltage conditions has become an essential component of DDR5 benchmarking methodologies, particularly for systems implementing aggressive power management. These tests evaluate memory stability during frequent transitions between power states, identifying potential performance degradation points in energy-conserving implementations.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!