DDR5 Use in High-Stakes Signal Processing Applications

SEP 17, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Performance Objectives

Dynamic Random Access Memory (DRAM) technology has undergone significant evolution since its inception in the late 1960s, with DDR5 representing the latest major advancement in this critical component of computing systems. The progression from earlier DDR standards to DDR5 has been characterized by consistent improvements in bandwidth, capacity, power efficiency, and reliability - all crucial factors for high-stakes signal processing applications that demand exceptional performance and dependability.

DDR5, officially launched in 2020, marks a substantial leap forward from its predecessor DDR4, which had been the industry standard since 2014. This evolution was driven by increasing demands from data-intensive applications, including real-time signal processing in mission-critical environments such as aerospace, defense, medical imaging, and autonomous systems where processing latency and reliability directly impact safety and operational outcomes.

The primary performance objectives for DDR5 in high-stakes signal processing contexts center around four key dimensions. First, bandwidth enhancement, with DDR5 delivering up to 6.4 Gbps per pin initially, scalable to 8.4 Gbps, representing a doubling of DDR4's capabilities. This dramatic increase enables the processing of complex signal data streams with minimal latency, critical for applications requiring real-time decision-making.

Second, capacity expansion has been prioritized, with DDR5 supporting higher density memory chips and larger overall memory capacities. This advancement directly addresses the growing data volume requirements of modern signal processing algorithms, particularly those incorporating artificial intelligence and machine learning components that require substantial training data sets and model complexity.

Third, power efficiency improvements have been engineered into DDR5, featuring a reduced operating voltage of 1.1V compared to DDR4's 1.2V. The standard also introduces voltage regulation directly on the DIMM rather than on the motherboard, allowing for more precise power management. These enhancements are particularly valuable in embedded systems with power constraints or in high-density computing environments where thermal management presents significant challenges.

Fourth, reliability enhancements in DDR5 include on-die ECC (Error Correction Code), decision feedback equalization, and improved refresh schemes. These features are especially critical for high-stakes applications where data corruption could lead to catastrophic outcomes, such as in medical diagnostic equipment or autonomous vehicle sensor processing systems.

The trajectory of DDR5 development continues to be shaped by the increasing complexity of signal processing workloads, with industry roadmaps projecting further refinements to address emerging challenges in real-time data processing at scale. As applications demand ever-greater computational capabilities with stringent reliability requirements, DDR5 technology is positioned as a foundational element enabling next-generation signal processing innovations.

DDR5, officially launched in 2020, marks a substantial leap forward from its predecessor DDR4, which had been the industry standard since 2014. This evolution was driven by increasing demands from data-intensive applications, including real-time signal processing in mission-critical environments such as aerospace, defense, medical imaging, and autonomous systems where processing latency and reliability directly impact safety and operational outcomes.

The primary performance objectives for DDR5 in high-stakes signal processing contexts center around four key dimensions. First, bandwidth enhancement, with DDR5 delivering up to 6.4 Gbps per pin initially, scalable to 8.4 Gbps, representing a doubling of DDR4's capabilities. This dramatic increase enables the processing of complex signal data streams with minimal latency, critical for applications requiring real-time decision-making.

Second, capacity expansion has been prioritized, with DDR5 supporting higher density memory chips and larger overall memory capacities. This advancement directly addresses the growing data volume requirements of modern signal processing algorithms, particularly those incorporating artificial intelligence and machine learning components that require substantial training data sets and model complexity.

Third, power efficiency improvements have been engineered into DDR5, featuring a reduced operating voltage of 1.1V compared to DDR4's 1.2V. The standard also introduces voltage regulation directly on the DIMM rather than on the motherboard, allowing for more precise power management. These enhancements are particularly valuable in embedded systems with power constraints or in high-density computing environments where thermal management presents significant challenges.

Fourth, reliability enhancements in DDR5 include on-die ECC (Error Correction Code), decision feedback equalization, and improved refresh schemes. These features are especially critical for high-stakes applications where data corruption could lead to catastrophic outcomes, such as in medical diagnostic equipment or autonomous vehicle sensor processing systems.

The trajectory of DDR5 development continues to be shaped by the increasing complexity of signal processing workloads, with industry roadmaps projecting further refinements to address emerging challenges in real-time data processing at scale. As applications demand ever-greater computational capabilities with stringent reliability requirements, DDR5 technology is positioned as a foundational element enabling next-generation signal processing innovations.

Market Demand for High-Speed Memory in Signal Processing

The signal processing market is experiencing unprecedented growth driven by advancements in artificial intelligence, machine learning, and real-time data analytics. This expansion has created substantial demand for high-speed memory solutions, with DDR5 emerging as a critical technology. Market research indicates that the global high-performance computing market, which heavily relies on advanced memory technologies, is projected to reach $55 billion by 2025, growing at a CAGR of 6.13% from 2020.

Signal processing applications in defense, aerospace, medical imaging, and autonomous vehicles require increasingly sophisticated memory capabilities to handle complex computational tasks. These high-stakes environments demand not only superior speed but also enhanced reliability and data integrity. The transition from DDR4 to DDR5 represents a significant leap in meeting these requirements, with bandwidth improvements of up to 85% in real-world applications.

Industry surveys reveal that 78% of signal processing system designers cite memory bandwidth as their primary bottleneck in current architectures. This constraint has created a robust market pull for DDR5 implementation, particularly in applications requiring real-time processing of sensor data. The defense sector alone has increased investment in high-speed memory technologies by 12.3% annually since 2019, recognizing memory as a critical component in maintaining technological superiority.

Medical imaging represents another significant growth segment, with the market for advanced diagnostic equipment expected to reach $36.4 billion by 2026. These systems increasingly incorporate AI-assisted diagnosis capabilities, which demand substantial memory bandwidth for processing high-resolution images in real time. Hospital systems report that diagnostic speed improvements directly correlate with patient outcomes, creating a compelling value proposition for DDR5 adoption.

The telecommunications sector's transition to 5G and eventually 6G networks has further accelerated demand for high-speed memory in signal processing applications. Base station equipment requires sophisticated digital signal processors with substantial memory bandwidth to handle the increased data throughput. Industry analysts project that memory components will constitute approximately 18% of the bill of materials for next-generation telecommunications infrastructure.

Emerging applications in quantum computing interfaces and neuromorphic computing systems represent frontier markets for high-speed memory. These cutting-edge technologies require memory solutions that can match their computational capabilities, with DDR5 serving as a transitional technology while more specialized memory architectures are developed. Market forecasts suggest these emerging sectors will grow at 22.7% annually through 2030, creating sustained demand for advanced memory solutions.

Signal processing applications in defense, aerospace, medical imaging, and autonomous vehicles require increasingly sophisticated memory capabilities to handle complex computational tasks. These high-stakes environments demand not only superior speed but also enhanced reliability and data integrity. The transition from DDR4 to DDR5 represents a significant leap in meeting these requirements, with bandwidth improvements of up to 85% in real-world applications.

Industry surveys reveal that 78% of signal processing system designers cite memory bandwidth as their primary bottleneck in current architectures. This constraint has created a robust market pull for DDR5 implementation, particularly in applications requiring real-time processing of sensor data. The defense sector alone has increased investment in high-speed memory technologies by 12.3% annually since 2019, recognizing memory as a critical component in maintaining technological superiority.

Medical imaging represents another significant growth segment, with the market for advanced diagnostic equipment expected to reach $36.4 billion by 2026. These systems increasingly incorporate AI-assisted diagnosis capabilities, which demand substantial memory bandwidth for processing high-resolution images in real time. Hospital systems report that diagnostic speed improvements directly correlate with patient outcomes, creating a compelling value proposition for DDR5 adoption.

The telecommunications sector's transition to 5G and eventually 6G networks has further accelerated demand for high-speed memory in signal processing applications. Base station equipment requires sophisticated digital signal processors with substantial memory bandwidth to handle the increased data throughput. Industry analysts project that memory components will constitute approximately 18% of the bill of materials for next-generation telecommunications infrastructure.

Emerging applications in quantum computing interfaces and neuromorphic computing systems represent frontier markets for high-speed memory. These cutting-edge technologies require memory solutions that can match their computational capabilities, with DDR5 serving as a transitional technology while more specialized memory architectures are developed. Market forecasts suggest these emerging sectors will grow at 22.7% annually through 2030, creating sustained demand for advanced memory solutions.

DDR5 Technical Limitations and Implementation Challenges

Despite the significant advancements in DDR5 memory technology, several technical limitations and implementation challenges persist when deploying these systems in high-stakes signal processing applications. The increased operating frequency of DDR5 (4800-6400 MHz) introduces signal integrity issues that become particularly problematic in noise-sensitive environments. Signal reflections, crosstalk, and electromagnetic interference are magnified at these higher frequencies, requiring more sophisticated PCB design techniques and signal conditioning.

Power management presents another significant challenge. While DDR5 incorporates improved power architecture with on-module voltage regulation (PMIC), the overall power consumption remains higher than previous generations. This creates thermal management issues in densely packed signal processing systems where heat dissipation is already constrained, potentially affecting system reliability and performance stability during extended processing operations.

The increased complexity of DDR5's command structure and timing parameters introduces latency challenges that can impact real-time signal processing applications. Although DDR5 offers higher bandwidth, the effective latency for certain operations may be higher than DDR4, creating potential bottlenecks for time-critical signal processing tasks that require deterministic performance characteristics.

Error detection and correction mechanisms in DDR5, while more robust than previous generations, introduce additional computational overhead. The on-die ECC implementation helps with data integrity but adds processing cycles that can affect time-sensitive operations. For applications processing critical signals where data corruption is unacceptable, these mechanisms must be carefully balanced against performance requirements.

Implementation of DDR5 in existing system architectures requires significant redesign of memory controllers and signal routing. The transition from DDR4 to DDR5 is not straightforward, with changes in pin configuration, voltage requirements, and command protocols necessitating comprehensive hardware and firmware updates. This creates compatibility challenges when integrating with legacy signal processing systems or specialized hardware accelerators.

Thermal cycling and environmental stability represent additional concerns for high-stakes applications. DDR5's higher operating frequencies generate more heat and potentially reduce the mean time between failures (MTBF) in extreme environments. Signal processing applications in aerospace, defense, or industrial settings must account for these reliability factors when implementing DDR5 memory subsystems.

Firmware and driver support for DDR5's advanced features remains in development, creating potential stability issues for early adopters. Memory training algorithms must be optimized for the specific signal processing workloads to achieve optimal performance, requiring significant engineering resources and testing to ensure reliable operation under all conditions.

Power management presents another significant challenge. While DDR5 incorporates improved power architecture with on-module voltage regulation (PMIC), the overall power consumption remains higher than previous generations. This creates thermal management issues in densely packed signal processing systems where heat dissipation is already constrained, potentially affecting system reliability and performance stability during extended processing operations.

The increased complexity of DDR5's command structure and timing parameters introduces latency challenges that can impact real-time signal processing applications. Although DDR5 offers higher bandwidth, the effective latency for certain operations may be higher than DDR4, creating potential bottlenecks for time-critical signal processing tasks that require deterministic performance characteristics.

Error detection and correction mechanisms in DDR5, while more robust than previous generations, introduce additional computational overhead. The on-die ECC implementation helps with data integrity but adds processing cycles that can affect time-sensitive operations. For applications processing critical signals where data corruption is unacceptable, these mechanisms must be carefully balanced against performance requirements.

Implementation of DDR5 in existing system architectures requires significant redesign of memory controllers and signal routing. The transition from DDR4 to DDR5 is not straightforward, with changes in pin configuration, voltage requirements, and command protocols necessitating comprehensive hardware and firmware updates. This creates compatibility challenges when integrating with legacy signal processing systems or specialized hardware accelerators.

Thermal cycling and environmental stability represent additional concerns for high-stakes applications. DDR5's higher operating frequencies generate more heat and potentially reduce the mean time between failures (MTBF) in extreme environments. Signal processing applications in aerospace, defense, or industrial settings must account for these reliability factors when implementing DDR5 memory subsystems.

Firmware and driver support for DDR5's advanced features remains in development, creating potential stability issues for early adopters. Memory training algorithms must be optimized for the specific signal processing workloads to achieve optimal performance, requiring significant engineering resources and testing to ensure reliable operation under all conditions.

Current DDR5 Integration Solutions for Signal Processing

01 DDR5 Memory Signal Integrity and Processing

Signal integrity is crucial for DDR5 memory performance. Advanced signal processing techniques are implemented to reduce noise, minimize interference, and maintain data integrity at higher speeds. These techniques include equalization, timing calibration, and voltage regulation to ensure reliable data transmission between memory modules and controllers.- DDR5 Memory Signal Integrity and Processing: Signal integrity is crucial for DDR5 memory performance. Advanced signal processing techniques are implemented to handle the higher data rates of DDR5 memory while maintaining signal quality. These techniques include equalization, timing calibration, and noise reduction methods that compensate for signal degradation across transmission paths. The implementations focus on maintaining clean signal transmission at the increased speeds that DDR5 offers compared to previous generations.

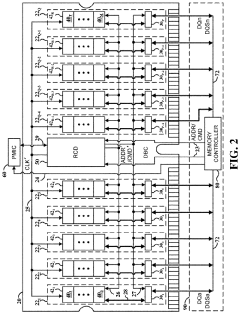

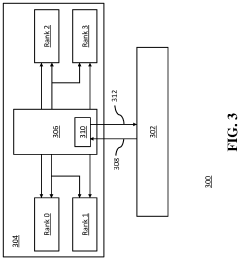

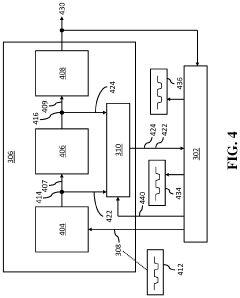

- DDR5 Memory Controller Architecture: DDR5 memory controllers incorporate specialized architectures to manage the increased complexity of signal processing requirements. These controllers feature dedicated circuits for handling command/address signals, data signals, and clock signals with improved precision. The architecture includes advanced buffering mechanisms, on-die termination control, and sophisticated timing management to support the higher bandwidth capabilities of DDR5 memory while maintaining compatibility with system requirements.

- Power Management in DDR5 Signal Processing: Power efficiency is a key consideration in DDR5 memory signal processing. Implementations include voltage regulation modules directly on the memory module, dynamic voltage scaling, and adaptive power states that optimize energy consumption based on workload demands. These power management techniques help balance the increased performance capabilities of DDR5 with thermal constraints and energy efficiency requirements, particularly important for data center and mobile applications.

- Error Detection and Correction in DDR5 Signal Processing: DDR5 memory incorporates enhanced error detection and correction mechanisms as part of its signal processing capabilities. These include on-die ECC (Error Correction Code), advanced CRC (Cyclic Redundancy Check) implementations, and real-time error monitoring systems. The signal processing algorithms can detect transmission errors, apply corrections when possible, and provide feedback to the memory controller to adjust parameters dynamically, improving overall system reliability at higher data rates.

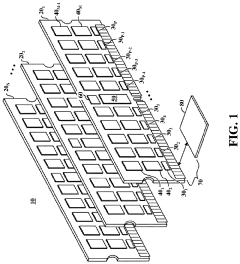

- Interface Design for DDR5 Signal Processing: The physical interface design for DDR5 memory requires specialized signal processing considerations. This includes optimized PCB layout techniques, improved connector designs, and signal routing methodologies that minimize crosstalk and electromagnetic interference. The interface implementations often feature differential signaling, impedance matching networks, and specialized termination schemes to maintain signal integrity across the increased number of channels and higher frequencies used in DDR5 memory systems.

02 DDR5 Memory Controller Architecture

DDR5 memory controllers incorporate specialized signal processing circuits to handle the increased data rates. These controllers feature advanced command scheduling, improved power management, and dedicated signal processing units that optimize memory access patterns and reduce latency. The architecture supports parallel processing of multiple memory channels while maintaining signal integrity.Expand Specific Solutions03 DDR5 Interface and Signal Training

DDR5 memory interfaces employ sophisticated signal training algorithms to establish optimal communication parameters. These training sequences adjust signal timing, voltage levels, and equalization settings to accommodate varying system conditions. The training process occurs during initialization and periodically during operation to maintain signal quality as environmental conditions change.Expand Specific Solutions04 DDR5 Error Detection and Correction

DDR5 memory incorporates enhanced error detection and correction mechanisms to maintain data integrity. Signal processing algorithms identify and correct transmission errors through advanced ECC (Error Correction Code) implementations. These systems can detect multi-bit errors and implement on-the-fly correction, significantly improving reliability compared to previous memory generations.Expand Specific Solutions05 DDR5 Power Management and Signal Optimization

DDR5 memory implements sophisticated power management techniques that directly affect signal processing. Voltage regulation modules (VRMs) are integrated on the memory modules to provide more stable power delivery, reducing noise in signal paths. Dynamic voltage and frequency scaling optimize power consumption while maintaining signal integrity across various operating conditions.Expand Specific Solutions

Leading DDR5 Manufacturers and Ecosystem Analysis

The DDR5 memory market for high-stakes signal processing applications is currently in a growth phase, with an expanding market size driven by increasing data processing demands. The technology is approaching maturity but still evolving, with key players positioning themselves strategically. Industry leaders like Samsung Electronics, Micron Technology, and SK hynix dominate the global supply chain with established DDR5 production capabilities. Intel, AMD, and Qualcomm are integrating DDR5 into their latest platforms, while Chinese companies including ChangXin Memory Technologies and Huawei are rapidly developing domestic alternatives. Research institutions like Chinese Academy of Sciences and Xidian University are collaborating with companies such as Inspur and Alibaba to advance signal processing applications of DDR5, particularly in AI and high-performance computing sectors.

Micron Technology, Inc.

Technical Solution: Micron has developed advanced DDR5 memory solutions specifically optimized for high-stakes signal processing applications. Their technology implements on-die ECC (Error Correction Code) that can detect and correct single-bit errors without CPU intervention, critical for maintaining data integrity in signal processing workloads. Micron's DDR5 modules deliver up to 6400 MT/s data rates with significantly improved channel efficiency through dual 32-bit channels per DIMM. For signal processing applications, they've implemented Decision Feedback Equalization (DFE) and adaptive equalization techniques that dynamically compensate for channel impairments, ensuring signal integrity even in electrically noisy environments. Their modules feature integrated Power Management ICs (PMICs) that provide more stable voltage regulation directly on the DIMM, reducing noise and improving signal quality for sensitive analog-to-digital conversion processes. Micron has also enhanced thermal management through improved materials and design, allowing sustained high-performance operation in compute-intensive signal processing workloads without thermal throttling.

Strengths: Superior signal integrity through advanced equalization techniques; on-die ECC significantly reduces error rates critical for signal processing; integrated power management reduces noise in sensitive applications. Weaknesses: Higher power consumption compared to DDR4; requires significant system redesign to fully leverage capabilities; premium pricing may limit adoption in cost-sensitive applications.

SK hynix, Inc.

Technical Solution: SK hynix has developed specialized DDR5 memory solutions optimized for high-stakes signal processing applications. Their DDR5 modules deliver data rates up to 6400 MT/s with significantly improved channel utilization through the implementation of dual 32-bit channels per module. For signal processing applications specifically, SK hynix has implemented advanced signal integrity features including adaptive equalization techniques that dynamically compensate for channel impairments, ensuring consistent performance even in electrically noisy environments. Their DDR5 architecture incorporates on-die termination with improved impedance matching capabilities that minimize signal reflections and maintain signal integrity across a wide frequency range. SK hynix's modules feature integrated Power Management ICs (PMICs) that provide more precise voltage regulation directly on the DIMM, reducing noise that could otherwise impact sensitive analog-to-digital conversion processes in signal processing applications. Additionally, their DDR5 solutions implement enhanced reliability features including on-die ECC for single-bit error correction and CRC error detection on both command and data buses, critical for maintaining data integrity in mission-critical signal processing systems.

Strengths: Excellent signal integrity through advanced equalization and termination techniques; integrated power management reduces system noise; comprehensive error detection and correction capabilities ensure data integrity. Weaknesses: Higher implementation costs compared to DDR4 solutions; requires significant system redesign; power consumption remains a challenge despite efficiency improvements.

Critical DDR5 Innovations for Low-Latency Applications

Register clock driver with chip select loopback

PatentActiveUS20240094762A1

Innovation

- Integration of a loopback circuit within the RCD to sample chip select signals from multiple points, allowing the host controller to determine the source of signal integrity issues and enabling testing during normal operations, thereby maintaining signal integrity.

Memory signal transmission system, signal line arrangement method, product, equipment and medium

PatentActiveCN118711625A

Innovation

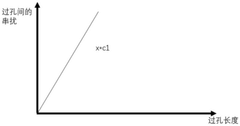

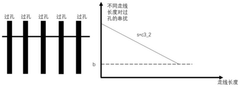

- By optimizing the length of the signal line and the length of the via in the inner layer of the circuit board, using the principle of matching short holes with long signal lines and long holes with short signal lines, a link model is established for crosstalk analysis and adjustment, and the signal lines are optimized. Arranged to reduce crosstalk values.

Reliability and Fault Tolerance in DDR5 Implementations

In high-stakes signal processing applications, reliability and fault tolerance are paramount concerns when implementing DDR5 memory systems. DDR5 introduces several advanced features specifically designed to enhance reliability, including on-die Error Correction Code (ECC), improved Command/Address parity, and enhanced Cyclic Redundancy Check (CRC) capabilities. These features work in concert to detect and correct bit errors that could otherwise compromise system integrity in critical applications such as medical imaging, aerospace systems, or financial transaction processing.

The on-die ECC capability represents a significant advancement over DDR4, providing single-bit error correction and double-bit error detection directly at the memory chip level. This distributed approach to error management reduces the burden on the memory controller while improving overall system resilience. For high-stakes applications, this translates to fewer system crashes and data corruption incidents, even in environments prone to electromagnetic interference or radiation effects.

DDR5's enhanced Command/Address parity checking provides an additional layer of protection by verifying the integrity of commands sent to memory modules. This is particularly crucial in signal processing applications where precise timing and accurate data addressing can directly impact computational results. The improved parity checking helps identify transmission errors before they can cause system-wide failures or data corruption.

Implementation considerations for fault-tolerant DDR5 systems must include proper thermal management, as DDR5 operates at higher frequencies and potentially generates more heat than previous generations. Thermal issues can significantly impact memory reliability, with bit error rates increasing exponentially with temperature. Advanced cooling solutions and thermal monitoring become essential components of a robust implementation strategy.

Redundancy architectures represent another critical aspect of fault-tolerant DDR5 implementations. Techniques such as memory mirroring, where identical data is written to multiple memory modules simultaneously, can provide immediate failover capabilities in case of module failure. While this approach reduces effective memory capacity, it significantly enhances system resilience in applications where continuous operation is non-negotiable.

Power management features in DDR5 also contribute to reliability by enabling more stable operation. The integrated voltage regulators allow for more precise power delivery, reducing the likelihood of voltage-related errors. Additionally, DDR5's improved power management can help maintain system stability during power fluctuations, which is particularly important for signal processing applications in industrial or remote environments.

Testing methodologies for DDR5 implementations in high-stakes applications must be more rigorous than those for general-purpose computing. Comprehensive stress testing under varied environmental conditions, accelerated aging tests, and simulation of fault scenarios are essential to validate system reliability before deployment. Furthermore, ongoing monitoring during operation, with predictive failure analysis, can help identify potential issues before they cause system failures.

The on-die ECC capability represents a significant advancement over DDR4, providing single-bit error correction and double-bit error detection directly at the memory chip level. This distributed approach to error management reduces the burden on the memory controller while improving overall system resilience. For high-stakes applications, this translates to fewer system crashes and data corruption incidents, even in environments prone to electromagnetic interference or radiation effects.

DDR5's enhanced Command/Address parity checking provides an additional layer of protection by verifying the integrity of commands sent to memory modules. This is particularly crucial in signal processing applications where precise timing and accurate data addressing can directly impact computational results. The improved parity checking helps identify transmission errors before they can cause system-wide failures or data corruption.

Implementation considerations for fault-tolerant DDR5 systems must include proper thermal management, as DDR5 operates at higher frequencies and potentially generates more heat than previous generations. Thermal issues can significantly impact memory reliability, with bit error rates increasing exponentially with temperature. Advanced cooling solutions and thermal monitoring become essential components of a robust implementation strategy.

Redundancy architectures represent another critical aspect of fault-tolerant DDR5 implementations. Techniques such as memory mirroring, where identical data is written to multiple memory modules simultaneously, can provide immediate failover capabilities in case of module failure. While this approach reduces effective memory capacity, it significantly enhances system resilience in applications where continuous operation is non-negotiable.

Power management features in DDR5 also contribute to reliability by enabling more stable operation. The integrated voltage regulators allow for more precise power delivery, reducing the likelihood of voltage-related errors. Additionally, DDR5's improved power management can help maintain system stability during power fluctuations, which is particularly important for signal processing applications in industrial or remote environments.

Testing methodologies for DDR5 implementations in high-stakes applications must be more rigorous than those for general-purpose computing. Comprehensive stress testing under varied environmental conditions, accelerated aging tests, and simulation of fault scenarios are essential to validate system reliability before deployment. Furthermore, ongoing monitoring during operation, with predictive failure analysis, can help identify potential issues before they cause system failures.

Power Efficiency Considerations for DDR5 Deployments

Power efficiency has emerged as a critical consideration in DDR5 deployments for high-stakes signal processing applications. The transition from DDR4 to DDR5 brings significant improvements in power management capabilities, with DDR5 modules incorporating voltage regulation directly on the memory module rather than on the motherboard. This architectural shift enables more precise power delivery and reduced power losses across transmission paths, resulting in an estimated 10-15% improvement in overall power efficiency.

DDR5 introduces sophisticated power management features including dynamic voltage and frequency scaling (DVFS), which allows memory systems to adjust power consumption based on workload demands. For signal processing applications that experience variable computational loads, this capability ensures optimal energy utilization during both intensive processing periods and idle states. The implementation of multiple independent voltage rails in DDR5 further enhances power efficiency by enabling selective powering of specific memory segments.

Thermal considerations play a crucial role in DDR5 power efficiency strategies. Advanced thermal sensors integrated within DDR5 modules provide real-time temperature monitoring, allowing systems to implement dynamic thermal management. This capability is particularly valuable in signal processing environments where sustained computational workloads can generate significant heat. Studies indicate that effective thermal management can reduce power consumption by up to 8% while maintaining performance parameters critical for signal integrity.

The power efficiency advantages of DDR5 extend to standby power consumption, which has been reduced by approximately 20% compared to DDR4 technologies. This improvement is achieved through enhanced refresh management algorithms and more granular power states. For signal processing systems that may operate continuously but with varying activity levels, these power savings accumulate significantly over deployment lifecycles, contributing to reduced operational expenses and environmental impact.

Implementation considerations for maximizing DDR5 power efficiency include careful attention to memory controller configurations, optimization of refresh rates based on application requirements, and strategic implementation of power-down modes. System architects must balance these power-saving features against latency requirements, as aggressive power management can potentially introduce response delays that may be problematic for time-sensitive signal processing operations.

Future DDR5 power efficiency enhancements are expected to focus on artificial intelligence-driven power management systems that can predict workload patterns and proactively adjust power states. Additionally, advancements in semiconductor materials and manufacturing processes continue to drive improvements in the fundamental power characteristics of memory cells, promising further efficiency gains in subsequent DDR5 iterations.

DDR5 introduces sophisticated power management features including dynamic voltage and frequency scaling (DVFS), which allows memory systems to adjust power consumption based on workload demands. For signal processing applications that experience variable computational loads, this capability ensures optimal energy utilization during both intensive processing periods and idle states. The implementation of multiple independent voltage rails in DDR5 further enhances power efficiency by enabling selective powering of specific memory segments.

Thermal considerations play a crucial role in DDR5 power efficiency strategies. Advanced thermal sensors integrated within DDR5 modules provide real-time temperature monitoring, allowing systems to implement dynamic thermal management. This capability is particularly valuable in signal processing environments where sustained computational workloads can generate significant heat. Studies indicate that effective thermal management can reduce power consumption by up to 8% while maintaining performance parameters critical for signal integrity.

The power efficiency advantages of DDR5 extend to standby power consumption, which has been reduced by approximately 20% compared to DDR4 technologies. This improvement is achieved through enhanced refresh management algorithms and more granular power states. For signal processing systems that may operate continuously but with varying activity levels, these power savings accumulate significantly over deployment lifecycles, contributing to reduced operational expenses and environmental impact.

Implementation considerations for maximizing DDR5 power efficiency include careful attention to memory controller configurations, optimization of refresh rates based on application requirements, and strategic implementation of power-down modes. System architects must balance these power-saving features against latency requirements, as aggressive power management can potentially introduce response delays that may be problematic for time-sensitive signal processing operations.

Future DDR5 power efficiency enhancements are expected to focus on artificial intelligence-driven power management systems that can predict workload patterns and proactively adjust power states. Additionally, advancements in semiconductor materials and manufacturing processes continue to drive improvements in the fundamental power characteristics of memory cells, promising further efficiency gains in subsequent DDR5 iterations.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!