DDR5 Testing Strategies in Advanced Avionics Systems

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Testing Objectives

DDR5 memory technology represents a significant advancement in the evolution of dynamic random-access memory, offering substantial improvements in bandwidth, capacity, and power efficiency compared to its predecessors. The development of DDR5 began in 2016, with JEDEC finalizing the standard in 2020, marking a pivotal moment in memory technology progression. This fifth generation of DDR technology has been designed to address the increasing demands of data-intensive applications, with particular relevance to advanced avionics systems where reliability and performance under extreme conditions are paramount.

The historical trajectory of memory technology in avionics has evolved from simple static RAM implementations to sophisticated DDR solutions capable of supporting complex computational tasks required in modern aircraft systems. This evolution has been driven by the growing complexity of avionics applications, including flight control systems, navigation, communication, and real-time data processing for situational awareness.

In the context of avionics systems, DDR5 offers theoretical bandwidth capabilities exceeding 6400 MT/s (million transfers per second), representing more than double the performance of mature DDR4 implementations. This substantial increase in data throughput capacity enables more sophisticated real-time processing of sensor data, enhanced graphical displays, and more complex computational models for flight systems.

The primary technical objectives for DDR5 testing in avionics environments focus on ensuring memory integrity under extreme conditions, including temperature variations from -55°C to +125°C, vibration resistance, radiation tolerance, and electromagnetic compatibility. These testing objectives are aligned with the stringent requirements of aerospace standards such as DO-254 and MIL-STD-810, which govern the development and certification of electronic hardware for airborne systems.

Additionally, testing strategies must address the unique architectural features of DDR5, including the transition to dual-channel architecture with independent 40-bit channels, on-die ECC (Error Correction Code) capabilities, and the implementation of Decision Feedback Equalization (DFE) for signal integrity at higher frequencies. These features present both opportunities for enhanced reliability and challenges for comprehensive validation.

The evolution of DDR5 testing methodologies must also account for the increased complexity of power management in DDR5, with the transition from a controller-based to PMIC (Power Management Integrated Circuit) approach. This shift necessitates new testing protocols to verify proper voltage regulation and power sequencing under the dynamic load conditions typical in avionics operations.

Looking forward, the testing objectives for DDR5 in avionics must anticipate future developments, including potential speed grades exceeding 8400 MT/s and the integration with emerging technologies such as artificial intelligence accelerators and advanced sensor fusion systems that will define next-generation aircraft capabilities.

The historical trajectory of memory technology in avionics has evolved from simple static RAM implementations to sophisticated DDR solutions capable of supporting complex computational tasks required in modern aircraft systems. This evolution has been driven by the growing complexity of avionics applications, including flight control systems, navigation, communication, and real-time data processing for situational awareness.

In the context of avionics systems, DDR5 offers theoretical bandwidth capabilities exceeding 6400 MT/s (million transfers per second), representing more than double the performance of mature DDR4 implementations. This substantial increase in data throughput capacity enables more sophisticated real-time processing of sensor data, enhanced graphical displays, and more complex computational models for flight systems.

The primary technical objectives for DDR5 testing in avionics environments focus on ensuring memory integrity under extreme conditions, including temperature variations from -55°C to +125°C, vibration resistance, radiation tolerance, and electromagnetic compatibility. These testing objectives are aligned with the stringent requirements of aerospace standards such as DO-254 and MIL-STD-810, which govern the development and certification of electronic hardware for airborne systems.

Additionally, testing strategies must address the unique architectural features of DDR5, including the transition to dual-channel architecture with independent 40-bit channels, on-die ECC (Error Correction Code) capabilities, and the implementation of Decision Feedback Equalization (DFE) for signal integrity at higher frequencies. These features present both opportunities for enhanced reliability and challenges for comprehensive validation.

The evolution of DDR5 testing methodologies must also account for the increased complexity of power management in DDR5, with the transition from a controller-based to PMIC (Power Management Integrated Circuit) approach. This shift necessitates new testing protocols to verify proper voltage regulation and power sequencing under the dynamic load conditions typical in avionics operations.

Looking forward, the testing objectives for DDR5 in avionics must anticipate future developments, including potential speed grades exceeding 8400 MT/s and the integration with emerging technologies such as artificial intelligence accelerators and advanced sensor fusion systems that will define next-generation aircraft capabilities.

Avionics Market Requirements for High-Speed Memory

The avionics market demands for high-speed memory systems have evolved dramatically in recent years, driven by the increasing complexity of flight systems and the exponential growth in data processing requirements. Modern aircraft now function as sophisticated data centers in the sky, processing vast amounts of information from numerous sensors, navigation systems, and communication equipment simultaneously. This shift has created an urgent need for memory solutions that can handle higher bandwidths while maintaining the stringent reliability standards essential for aviation safety.

DDR5 memory has emerged as a critical technology to address these demands, offering significant improvements over previous generations with data rates exceeding 4800 MT/s compared to DDR4's typical 3200 MT/s. For avionics applications, this translates to faster processing of flight-critical data, enhanced real-time decision-making capabilities, and support for advanced functions such as synthetic vision systems and predictive maintenance algorithms.

Reliability requirements in avionics far exceed those of consumer or even enterprise markets. Memory systems must maintain perfect operation under extreme conditions including temperature ranges from -55°C to +125°C, radiation exposure at high altitudes, and vibration profiles that would destroy conventional components. The industry standard for avionics memory failure rates is measured in parts per billion, compared to parts per million in consumer electronics, reflecting the zero-tolerance approach to system failures in flight-critical applications.

Power efficiency represents another crucial requirement, particularly as modern aircraft designs increasingly incorporate more electric systems. DDR5's improved power management features, including voltage regulation moved on-die, align well with these needs, potentially reducing power consumption by 20% compared to equivalent DDR4 implementations while delivering higher performance. This efficiency is vital for managing thermal loads in densely packed avionics bays with limited cooling capacity.

Security considerations have also become paramount as aircraft systems become more interconnected. Memory subsystems must now incorporate advanced encryption and authentication mechanisms to prevent unauthorized access or tampering. The aviation industry requires memory solutions that can implement these security features without compromising performance or adding significant latency to operations.

Certification requirements add another layer of complexity to avionics memory specifications. Components must meet DO-254 hardware certification standards and integrate seamlessly with software systems developed under DO-178C guidelines. This necessitates extensive documentation, traceability of design decisions, and comprehensive testing regimes that far exceed typical commercial validation processes.

DDR5 memory has emerged as a critical technology to address these demands, offering significant improvements over previous generations with data rates exceeding 4800 MT/s compared to DDR4's typical 3200 MT/s. For avionics applications, this translates to faster processing of flight-critical data, enhanced real-time decision-making capabilities, and support for advanced functions such as synthetic vision systems and predictive maintenance algorithms.

Reliability requirements in avionics far exceed those of consumer or even enterprise markets. Memory systems must maintain perfect operation under extreme conditions including temperature ranges from -55°C to +125°C, radiation exposure at high altitudes, and vibration profiles that would destroy conventional components. The industry standard for avionics memory failure rates is measured in parts per billion, compared to parts per million in consumer electronics, reflecting the zero-tolerance approach to system failures in flight-critical applications.

Power efficiency represents another crucial requirement, particularly as modern aircraft designs increasingly incorporate more electric systems. DDR5's improved power management features, including voltage regulation moved on-die, align well with these needs, potentially reducing power consumption by 20% compared to equivalent DDR4 implementations while delivering higher performance. This efficiency is vital for managing thermal loads in densely packed avionics bays with limited cooling capacity.

Security considerations have also become paramount as aircraft systems become more interconnected. Memory subsystems must now incorporate advanced encryption and authentication mechanisms to prevent unauthorized access or tampering. The aviation industry requires memory solutions that can implement these security features without compromising performance or adding significant latency to operations.

Certification requirements add another layer of complexity to avionics memory specifications. Components must meet DO-254 hardware certification standards and integrate seamlessly with software systems developed under DO-178C guidelines. This necessitates extensive documentation, traceability of design decisions, and comprehensive testing regimes that far exceed typical commercial validation processes.

DDR5 Implementation Challenges in Aerospace Applications

The implementation of DDR5 memory in aerospace applications presents unique challenges that extend beyond those encountered in conventional computing environments. The harsh operating conditions of avionics systems, including extreme temperatures, radiation exposure, and high-altitude electromagnetic interference, create significant hurdles for DDR5 integration. These environmental factors can compromise signal integrity, accelerate component degradation, and increase the likelihood of data corruption.

Power management represents another critical challenge for DDR5 implementation in aerospace systems. While DDR5 offers improved power efficiency compared to previous generations, the voltage regulation architecture has shifted from motherboard-based to DIMM-based regulation. This architectural change requires additional components on memory modules, increasing complexity and potential points of failure in systems where reliability is paramount. The power management integrated circuits (PMICs) on DDR5 modules must be qualified for aerospace-grade reliability, which often necessitates custom solutions.

Thermal management poses substantial difficulties in the confined spaces of avionics equipment. DDR5 operates at higher frequencies than its predecessors, generating more heat that must be dissipated effectively to prevent performance degradation and premature component failure. Traditional cooling solutions may be insufficient or impractical in aerospace applications due to weight constraints and the absence of forced-air cooling in many avionics enclosures.

Qualification and certification processes present perhaps the most significant implementation barrier. Aerospace components must undergo rigorous testing to meet standards such as DO-254 for hardware and DO-160 for environmental conditions. The relatively recent emergence of DDR5 technology means that aerospace-qualified components are limited, and the certification process for new memory subsystems is both time-consuming and costly.

Supply chain considerations further complicate DDR5 implementation. Aerospace systems typically have lifecycles measured in decades, requiring long-term component availability. However, commercial memory technologies evolve rapidly, creating potential obsolescence issues. Manufacturers must secure extended supply commitments or develop strategies for managing component obsolescence throughout the system lifecycle.

Backward compatibility with existing systems presents another challenge. Many aerospace platforms undergo incremental upgrades rather than complete redesigns. Integrating DDR5 memory into legacy systems may require substantial architectural changes to accommodate different signaling, power requirements, and physical interfaces. These modifications can cascade into additional qualification and certification requirements.

The balance between leveraging commercial off-the-shelf (COTS) components and developing specialized aerospace-grade solutions represents a strategic decision point for manufacturers. While COTS DDR5 components offer cost advantages and technological currency, they may lack the robustness required for mission-critical aerospace applications.

Power management represents another critical challenge for DDR5 implementation in aerospace systems. While DDR5 offers improved power efficiency compared to previous generations, the voltage regulation architecture has shifted from motherboard-based to DIMM-based regulation. This architectural change requires additional components on memory modules, increasing complexity and potential points of failure in systems where reliability is paramount. The power management integrated circuits (PMICs) on DDR5 modules must be qualified for aerospace-grade reliability, which often necessitates custom solutions.

Thermal management poses substantial difficulties in the confined spaces of avionics equipment. DDR5 operates at higher frequencies than its predecessors, generating more heat that must be dissipated effectively to prevent performance degradation and premature component failure. Traditional cooling solutions may be insufficient or impractical in aerospace applications due to weight constraints and the absence of forced-air cooling in many avionics enclosures.

Qualification and certification processes present perhaps the most significant implementation barrier. Aerospace components must undergo rigorous testing to meet standards such as DO-254 for hardware and DO-160 for environmental conditions. The relatively recent emergence of DDR5 technology means that aerospace-qualified components are limited, and the certification process for new memory subsystems is both time-consuming and costly.

Supply chain considerations further complicate DDR5 implementation. Aerospace systems typically have lifecycles measured in decades, requiring long-term component availability. However, commercial memory technologies evolve rapidly, creating potential obsolescence issues. Manufacturers must secure extended supply commitments or develop strategies for managing component obsolescence throughout the system lifecycle.

Backward compatibility with existing systems presents another challenge. Many aerospace platforms undergo incremental upgrades rather than complete redesigns. Integrating DDR5 memory into legacy systems may require substantial architectural changes to accommodate different signaling, power requirements, and physical interfaces. These modifications can cascade into additional qualification and certification requirements.

The balance between leveraging commercial off-the-shelf (COTS) components and developing specialized aerospace-grade solutions represents a strategic decision point for manufacturers. While COTS DDR5 components offer cost advantages and technological currency, they may lack the robustness required for mission-critical aerospace applications.

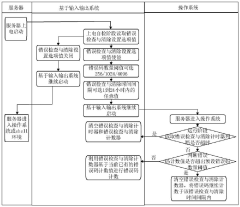

Current DDR5 Testing Methodologies for Mission-Critical Systems

01 DDR5 Memory Testing Methodologies

Various methodologies for testing DDR5 memory modules have been developed to ensure reliability and performance. These methodologies include functional testing, stress testing, and error detection techniques specifically designed for the high-speed operation of DDR5 memory. Testing approaches often involve specialized test patterns that target specific failure modes common in DDR5 architecture, along with automated test equipment capable of operating at the higher frequencies required for DDR5 validation.- High-speed memory testing methodologies: Testing methodologies specifically designed for high-speed memory like DDR5 involve specialized techniques to verify timing parameters, signal integrity, and data transfer rates. These approaches include at-speed testing, margin testing, and jitter analysis to ensure reliable operation at the increased frequencies of DDR5. Advanced test equipment and protocols are employed to validate memory performance under various operating conditions and to detect timing violations that could lead to data corruption.

- Error detection and correction mechanisms: DDR5 memory testing incorporates sophisticated error detection and correction mechanisms to identify and resolve memory faults. These include built-in self-test (BIST) capabilities, cyclic redundancy checks (CRC), and error-correcting code (ECC) implementations. Testing strategies focus on validating these mechanisms by intentionally introducing errors and verifying proper detection and correction, ensuring data integrity even at higher speeds and densities characteristic of DDR5 memory.

- Power and thermal management testing: Testing strategies for DDR5 memory include comprehensive evaluation of power consumption patterns and thermal characteristics. This involves measuring voltage fluctuations during different operational modes, testing power-saving features, and monitoring thermal profiles under various workloads. The testing ensures that the memory operates efficiently within specified power envelopes and temperature ranges, validating the effectiveness of DDR5's enhanced power management capabilities.

- System-level integration and compatibility testing: System-level testing strategies for DDR5 memory focus on integration with various platforms and compatibility with different components. These tests validate memory controller interactions, BIOS/firmware compatibility, and overall system stability. Testing procedures include boot testing, long-duration stress tests, and performance benchmarking across multiple system configurations to ensure seamless operation in diverse computing environments.

- Advanced signal integrity and timing analysis: DDR5 memory testing employs sophisticated signal integrity and timing analysis techniques to validate high-frequency operation. These include eye diagram analysis, clock jitter measurements, and impedance testing to ensure reliable data transmission. Testing strategies focus on evaluating signal margins, crosstalk effects, and timing parameters across different operating conditions, addressing the challenges posed by DDR5's increased data rates and stricter timing requirements.

02 Error Detection and Correction Mechanisms

Advanced error detection and correction mechanisms are essential for DDR5 memory testing. These include built-in self-test (BIST) capabilities, cyclic redundancy checks (CRC), and parity checking systems designed to identify and address errors that may occur during high-speed data transfer. DDR5 memory incorporates more sophisticated error correction code (ECC) capabilities compared to previous generations, requiring specialized testing strategies to verify these features function correctly under various operating conditions.Expand Specific Solutions03 Performance and Timing Verification

Testing strategies for DDR5 memory must verify performance parameters and timing specifications that are significantly more demanding than previous memory generations. This includes validating higher data transfer rates, stricter timing requirements, and power management features. Testing approaches focus on measuring signal integrity at higher frequencies, verifying timing margins, and ensuring compliance with DDR5 specifications across various operating conditions including temperature variations and voltage fluctuations.Expand Specific Solutions04 System-Level Integration Testing

System-level testing strategies for DDR5 memory focus on integration with processors, controllers, and other system components. These approaches verify compatibility, stability, and performance in real-world application scenarios. Testing methodologies include boot testing, application-level stress testing, and long-term reliability assessment. System-level tests also evaluate power management features, thermal characteristics, and the interaction between memory subsystems and other components under various workloads.Expand Specific Solutions05 Security and Vulnerability Testing

With increased complexity and connectivity in modern computing systems, DDR5 memory testing strategies now incorporate security and vulnerability assessments. These testing approaches identify potential security weaknesses, side-channel vulnerabilities, and protection against unauthorized access or manipulation of memory contents. Testing methodologies include penetration testing, fault injection analysis, and verification of security features implemented in DDR5 memory architecture to protect against emerging threats.Expand Specific Solutions

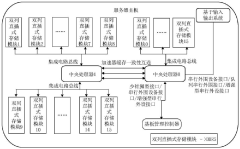

Leading Manufacturers and Aerospace Memory Solution Providers

The DDR5 testing landscape in avionics systems is currently in an early growth phase, with market size expanding as aerospace manufacturers adopt next-generation memory technologies. The technical maturity varies significantly among key players, with established semiconductor companies like Micron Technology, SK hynix, and Intel leading development of specialized DDR5 solutions for high-reliability environments. Aerospace giants Airbus and Saab are integrating these technologies into advanced avionics platforms, while Huawei and Futurewei are making significant R&D investments in this space. Defense-oriented institutions like National University of Defense Technology are collaborating with memory manufacturers to develop testing protocols that address the unique reliability requirements of avionics applications, creating a competitive ecosystem balancing commercial innovation with stringent aerospace certification standards.

Airbus Operations SAS

Technical Solution: Airbus has developed comprehensive DDR5 testing strategies specifically tailored for avionics systems that operate in extreme environments. Their approach includes multi-layered validation protocols that test memory modules under various altitude, temperature, and vibration conditions to ensure reliability in flight operations. Airbus implements Hardware-in-the-Loop (HIL) simulation environments that replicate real-world avionics scenarios while monitoring DDR5 performance metrics including data transfer rates, error correction capabilities, and power consumption profiles. Their testing framework incorporates automated fault injection techniques to verify error detection and correction mechanisms essential for flight-critical systems. Airbus has also pioneered radiation-hardened testing methodologies that evaluate DDR5 components' resilience against cosmic radiation effects at cruising altitudes, ensuring memory integrity during long-duration flights.

Strengths: Comprehensive environmental testing capabilities that accurately simulate aviation conditions; deep integration with actual flight systems providing realistic operational data. Weaknesses: Proprietary testing methodologies may limit industry-wide standardization; high implementation costs compared to commercial testing approaches.

Micron Technology, Inc.

Technical Solution: Micron has developed specialized DDR5 testing solutions for avionics applications that focus on reliability and performance under extreme conditions. Their testing strategy incorporates automated test equipment (ATE) platforms specifically calibrated for high-reliability aerospace requirements. Micron's approach includes accelerated life testing that simulates years of operation in compressed timeframes, with particular emphasis on temperature cycling (-55°C to +125°C) to meet military and aerospace standards. Their DDR5 validation process includes bit error rate testing under various electromagnetic interference conditions common in avionics environments. Micron has also implemented specialized signal integrity testing that accounts for the longer trace lengths and complex routing often found in avionics systems. Their testing methodology incorporates power integrity analysis to ensure DDR5 modules maintain stable operation during voltage fluctuations that may occur in aircraft power systems.

Strengths: Industry-leading expertise in memory manufacturing provides deep technical insights into failure modes; extensive reliability data from diverse applications. Weaknesses: Testing may emphasize general high-reliability applications rather than avionics-specific use cases; commercial focus may sometimes prioritize time-to-market over exhaustive qualification.

Critical Patents and Standards for Avionics Memory Testing

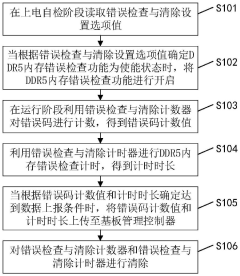

Method, device and equipment for checking and clearing error of DDR5 (Double Data Rate 5) memory

PatentPendingCN118260112A

Innovation

- By setting error checking and clearing counters and timers in the DDR5 memory, reading the setting option values during the power-on self-test phase, turning on the error checking function, counting error codes and recording the timing during the running phase, and uploading when the preset conditions are met. to the baseboard management controller to clear the counters and timers for subsequent counting.

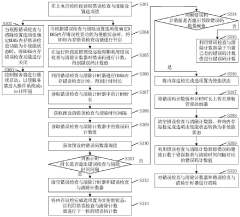

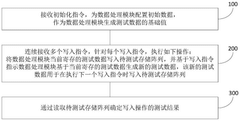

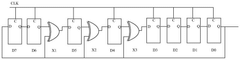

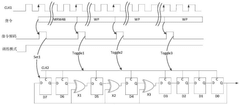

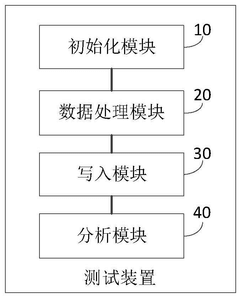

Test method and device and electronic equipment

PatentPendingCN118866068A

Innovation

- Configure initial data for the data processing module by receiving initialization instructions, and when continuously receiving write instructions, write the currently registered test data to the storage array, and generate new test data based on the write instructions for the next write. Reduce the number of initialization instructions and improve test data generation efficiency.

Certification Requirements for Avionics Memory Components

The certification of memory components in avionics systems follows stringent regulatory frameworks established by aviation authorities worldwide. For DDR5 memory integration in advanced avionics systems, manufacturers must adhere to DO-254 (Design Assurance Guidance for Airborne Electronic Hardware) requirements, which categorize components based on their criticality levels from A to E. DDR5 memory components typically fall under Level A or B due to their critical role in flight systems.

FAA and EASA regulations mandate extensive environmental testing for avionics memory, including temperature cycling (-55°C to +125°C), vibration resistance, electromagnetic interference (EMI) compliance, and radiation hardening. DDR5 components must demonstrate resilience against single event upsets (SEUs) and total ionizing dose (TID) effects, particularly for high-altitude operations.

Memory qualification for avionics must follow the MIL-STD-883 testing methodology, with specific attention to Method 1005 (Steady State Life) and Method 1010 (Temperature Cycling). The introduction of DDR5's higher operating frequencies necessitates enhanced EMI/EMC testing protocols under DO-160 standards, with particular focus on sections 16-22 covering various electromagnetic effects.

Reliability demonstration requirements have become more stringent for DDR5 implementations, requiring mean time between failure (MTBF) calculations exceeding 100,000 flight hours. Manufacturers must provide comprehensive failure mode and effects analysis (FMEA) documentation, with particular attention to DDR5's on-die ECC capabilities and their impact on system reliability metrics.

Software certification interfaces with hardware through DO-178C compliance, which becomes particularly complex with DDR5's advanced power management features and decision request (DQS) timing parameters. Memory testing must verify proper operation across all software-controlled power states while maintaining deterministic timing behavior required for safety-critical systems.

Certification documentation for DDR5 components must include traceability matrices linking requirements to test results, detailed manufacturing process controls, and component obsolescence management plans. The higher integration density of DDR5 necessitates enhanced particle impact noise detection (PIND) testing to ensure physical integrity of the memory packages under extreme aviation conditions.

FAA and EASA regulations mandate extensive environmental testing for avionics memory, including temperature cycling (-55°C to +125°C), vibration resistance, electromagnetic interference (EMI) compliance, and radiation hardening. DDR5 components must demonstrate resilience against single event upsets (SEUs) and total ionizing dose (TID) effects, particularly for high-altitude operations.

Memory qualification for avionics must follow the MIL-STD-883 testing methodology, with specific attention to Method 1005 (Steady State Life) and Method 1010 (Temperature Cycling). The introduction of DDR5's higher operating frequencies necessitates enhanced EMI/EMC testing protocols under DO-160 standards, with particular focus on sections 16-22 covering various electromagnetic effects.

Reliability demonstration requirements have become more stringent for DDR5 implementations, requiring mean time between failure (MTBF) calculations exceeding 100,000 flight hours. Manufacturers must provide comprehensive failure mode and effects analysis (FMEA) documentation, with particular attention to DDR5's on-die ECC capabilities and their impact on system reliability metrics.

Software certification interfaces with hardware through DO-178C compliance, which becomes particularly complex with DDR5's advanced power management features and decision request (DQS) timing parameters. Memory testing must verify proper operation across all software-controlled power states while maintaining deterministic timing behavior required for safety-critical systems.

Certification documentation for DDR5 components must include traceability matrices linking requirements to test results, detailed manufacturing process controls, and component obsolescence management plans. The higher integration density of DDR5 necessitates enhanced particle impact noise detection (PIND) testing to ensure physical integrity of the memory packages under extreme aviation conditions.

Radiation Hardening Techniques for DDR5 in Aerospace

Radiation hardening is a critical consideration for DDR5 memory implementation in aerospace applications, where exposure to cosmic rays, solar flares, and other radiation sources can cause significant operational disruptions. The aerospace environment presents unique challenges for memory systems, with radiation effects potentially causing single event upsets (SEUs), single event latchups (SELs), and total ionizing dose (TID) damage that can compromise system integrity and reliability.

Current radiation hardening techniques for DDR5 in aerospace applications focus on both physical and logical protection mechanisms. Physical hardening involves specialized manufacturing processes using silicon-on-insulator (SOI) technology, which provides inherent resistance to radiation-induced charge collection. Depleted substrate transistors (DSTs) are increasingly being incorporated into DDR5 designs specifically for aerospace applications, offering improved immunity to radiation effects while maintaining high-speed performance characteristics.

Error detection and correction (EDAC) mechanisms have evolved significantly for DDR5 implementations. Advanced error correction codes (ECCs) now provide multi-bit error detection and correction capabilities, essential for maintaining data integrity in radiation-prone environments. These systems can detect and correct multiple bit flips within a single data word, significantly enhancing reliability compared to previous DDR generations.

Redundancy approaches have become more sophisticated in DDR5 aerospace applications. Triple modular redundancy (TMR) is being implemented at both the circuit and system levels, with voting mechanisms that can identify and override radiation-induced errors. Some cutting-edge designs incorporate selective TMR, applying redundancy only to critical memory sections to optimize the balance between radiation hardness and resource utilization.

Scrubbing techniques have been enhanced for DDR5, with background error checking and correction processes that continuously scan memory for radiation-induced errors. These processes operate during system idle times without impacting performance, allowing for proactive error correction before corrupted data is accessed by the system.

Testing protocols for radiation-hardened DDR5 include accelerated radiation exposure in specialized facilities that simulate years of space radiation in compressed timeframes. These tests evaluate both immediate effects (SEUs) and cumulative damage (TID), providing critical data for reliability predictions in actual aerospace deployments. Manufacturers are increasingly adopting standardized radiation testing protocols specifically designed for high-speed memory systems in aerospace applications.

Current radiation hardening techniques for DDR5 in aerospace applications focus on both physical and logical protection mechanisms. Physical hardening involves specialized manufacturing processes using silicon-on-insulator (SOI) technology, which provides inherent resistance to radiation-induced charge collection. Depleted substrate transistors (DSTs) are increasingly being incorporated into DDR5 designs specifically for aerospace applications, offering improved immunity to radiation effects while maintaining high-speed performance characteristics.

Error detection and correction (EDAC) mechanisms have evolved significantly for DDR5 implementations. Advanced error correction codes (ECCs) now provide multi-bit error detection and correction capabilities, essential for maintaining data integrity in radiation-prone environments. These systems can detect and correct multiple bit flips within a single data word, significantly enhancing reliability compared to previous DDR generations.

Redundancy approaches have become more sophisticated in DDR5 aerospace applications. Triple modular redundancy (TMR) is being implemented at both the circuit and system levels, with voting mechanisms that can identify and override radiation-induced errors. Some cutting-edge designs incorporate selective TMR, applying redundancy only to critical memory sections to optimize the balance between radiation hardness and resource utilization.

Scrubbing techniques have been enhanced for DDR5, with background error checking and correction processes that continuously scan memory for radiation-induced errors. These processes operate during system idle times without impacting performance, allowing for proactive error correction before corrupted data is accessed by the system.

Testing protocols for radiation-hardened DDR5 include accelerated radiation exposure in specialized facilities that simulate years of space radiation in compressed timeframes. These tests evaluate both immediate effects (SEUs) and cumulative damage (TID), providing critical data for reliability predictions in actual aerospace deployments. Manufacturers are increasingly adopting standardized radiation testing protocols specifically designed for high-speed memory systems in aerospace applications.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!