DDR5 Heat Management in Compact IoT Architectures

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Thermal Evolution and Cooling Objectives

The evolution of DDR5 memory technology represents a significant advancement in computing architecture, with thermal management becoming increasingly critical as data rates and power densities escalate. DDR5 memory, introduced in 2021, marked a substantial leap from DDR4 with operating frequencies starting at 4800 MT/s compared to DDR4's typical 3200 MT/s. This performance improvement comes with heightened thermal challenges, particularly in space-constrained IoT devices where cooling solutions are limited by form factor restrictions.

Historically, DDR memory thermal management has evolved from passive cooling in early generations to more sophisticated approaches necessitated by increasing power densities. DDR3 typically operated at 1.5V, while DDR4 reduced this to 1.2V. DDR5 further decreases operating voltage to 1.1V, yet the higher frequencies result in comparable or even increased heat generation despite the voltage reduction.

The thermal profile of DDR5 presents unique challenges in IoT architectures. While server environments can implement elaborate cooling systems, IoT devices must balance thermal efficiency with size, weight, and power constraints. The trend toward edge computing further exacerbates these challenges as more data processing occurs locally within IoT devices rather than in centralized data centers.

Current thermal objectives for DDR5 in IoT applications focus on maintaining memory module temperatures below 85°C under full load conditions, with optimal performance typically achieved below 70°C. Exceeding these thresholds can trigger thermal throttling, reducing performance and potentially shortening component lifespan. The challenge is particularly acute in fanless designs common in IoT deployments.

Industry projections indicate DDR5 adoption in IoT will accelerate as edge computing demands increase, necessitating innovative cooling approaches. The technology roadmap suggests memory speeds will continue to increase, with DDR5-6400 and beyond becoming standard in coming years, further intensifying thermal management requirements.

The technical objectives for DDR5 thermal management in IoT architectures therefore include: developing low-profile thermal solutions compatible with compact form factors; implementing intelligent thermal monitoring and management systems; exploring phase-change materials for passive cooling enhancement; and optimizing power delivery networks to reduce localized hotspots.

Additionally, system-level thermal design considerations must account for the interaction between DDR5 modules and adjacent components, as thermal coupling effects can significantly impact overall system reliability in densely packed IoT devices. This holistic approach to thermal management represents a paradigm shift from component-level to system-level thermal design thinking.

Historically, DDR memory thermal management has evolved from passive cooling in early generations to more sophisticated approaches necessitated by increasing power densities. DDR3 typically operated at 1.5V, while DDR4 reduced this to 1.2V. DDR5 further decreases operating voltage to 1.1V, yet the higher frequencies result in comparable or even increased heat generation despite the voltage reduction.

The thermal profile of DDR5 presents unique challenges in IoT architectures. While server environments can implement elaborate cooling systems, IoT devices must balance thermal efficiency with size, weight, and power constraints. The trend toward edge computing further exacerbates these challenges as more data processing occurs locally within IoT devices rather than in centralized data centers.

Current thermal objectives for DDR5 in IoT applications focus on maintaining memory module temperatures below 85°C under full load conditions, with optimal performance typically achieved below 70°C. Exceeding these thresholds can trigger thermal throttling, reducing performance and potentially shortening component lifespan. The challenge is particularly acute in fanless designs common in IoT deployments.

Industry projections indicate DDR5 adoption in IoT will accelerate as edge computing demands increase, necessitating innovative cooling approaches. The technology roadmap suggests memory speeds will continue to increase, with DDR5-6400 and beyond becoming standard in coming years, further intensifying thermal management requirements.

The technical objectives for DDR5 thermal management in IoT architectures therefore include: developing low-profile thermal solutions compatible with compact form factors; implementing intelligent thermal monitoring and management systems; exploring phase-change materials for passive cooling enhancement; and optimizing power delivery networks to reduce localized hotspots.

Additionally, system-level thermal design considerations must account for the interaction between DDR5 modules and adjacent components, as thermal coupling effects can significantly impact overall system reliability in densely packed IoT devices. This holistic approach to thermal management represents a paradigm shift from component-level to system-level thermal design thinking.

IoT Market Requirements for DDR5 Memory Solutions

The IoT market is experiencing a significant transformation with the integration of DDR5 memory solutions, driven by the increasing complexity of edge computing applications. Current market analysis indicates that IoT devices are processing larger datasets locally, requiring higher memory bandwidth and capacity while maintaining strict power and thermal constraints. This evolution necessitates memory solutions that can deliver enhanced performance without compromising the compact form factors characteristic of IoT deployments.

Market research reveals that IoT device manufacturers are prioritizing memory solutions that offer improved data rates (up to 6400 MT/s) while maintaining or reducing power consumption compared to DDR4 implementations. The demand for real-time data processing capabilities in industrial IoT, smart city infrastructure, and advanced consumer devices is creating pressure for memory systems that can handle complex AI algorithms and data analytics at the edge.

Thermal management has emerged as a critical requirement, with surveys indicating that over 80% of IoT solution architects consider heat dissipation a primary design constraint. The compact nature of IoT devices, often deployed in environmentally challenging locations, exacerbates thermal concerns. Market feedback shows strong preference for DDR5 solutions that incorporate advanced thermal management features without requiring extensive additional cooling infrastructure.

Energy efficiency remains paramount in the IoT sector, with battery-powered and energy-harvesting devices representing a growing segment. DDR5's improved power management features, including voltage regulation on the DIMM rather than the motherboard, align well with these requirements. However, market adoption hinges on solutions that can demonstrate tangible power savings in real-world IoT deployment scenarios.

Reliability under varying environmental conditions represents another key market requirement. IoT deployments in industrial settings, outdoor environments, and remote locations demand memory solutions that maintain performance integrity across wide temperature ranges and potentially harsh operating conditions. DDR5 implementations must address these concerns to gain traction in mission-critical IoT applications.

Scalability and future-proofing are increasingly important as IoT ecosystems evolve. The market shows preference for memory architectures that can accommodate growing computational demands without hardware replacement. DDR5's higher density capabilities and improved channel architecture position it favorably in this regard, but implementation must be optimized for the specific constraints of IoT form factors.

Cost sensitivity varies significantly across IoT market segments, with industrial and enterprise applications demonstrating greater willingness to invest in premium memory solutions compared to consumer-oriented products. However, all segments require clear ROI justification, particularly regarding the thermal management advantages that DDR5 can provide in compact deployments.

Market research reveals that IoT device manufacturers are prioritizing memory solutions that offer improved data rates (up to 6400 MT/s) while maintaining or reducing power consumption compared to DDR4 implementations. The demand for real-time data processing capabilities in industrial IoT, smart city infrastructure, and advanced consumer devices is creating pressure for memory systems that can handle complex AI algorithms and data analytics at the edge.

Thermal management has emerged as a critical requirement, with surveys indicating that over 80% of IoT solution architects consider heat dissipation a primary design constraint. The compact nature of IoT devices, often deployed in environmentally challenging locations, exacerbates thermal concerns. Market feedback shows strong preference for DDR5 solutions that incorporate advanced thermal management features without requiring extensive additional cooling infrastructure.

Energy efficiency remains paramount in the IoT sector, with battery-powered and energy-harvesting devices representing a growing segment. DDR5's improved power management features, including voltage regulation on the DIMM rather than the motherboard, align well with these requirements. However, market adoption hinges on solutions that can demonstrate tangible power savings in real-world IoT deployment scenarios.

Reliability under varying environmental conditions represents another key market requirement. IoT deployments in industrial settings, outdoor environments, and remote locations demand memory solutions that maintain performance integrity across wide temperature ranges and potentially harsh operating conditions. DDR5 implementations must address these concerns to gain traction in mission-critical IoT applications.

Scalability and future-proofing are increasingly important as IoT ecosystems evolve. The market shows preference for memory architectures that can accommodate growing computational demands without hardware replacement. DDR5's higher density capabilities and improved channel architecture position it favorably in this regard, but implementation must be optimized for the specific constraints of IoT form factors.

Cost sensitivity varies significantly across IoT market segments, with industrial and enterprise applications demonstrating greater willingness to invest in premium memory solutions compared to consumer-oriented products. However, all segments require clear ROI justification, particularly regarding the thermal management advantages that DDR5 can provide in compact deployments.

Current Thermal Challenges in Compact DDR5 Implementations

The integration of DDR5 memory in compact IoT architectures presents significant thermal management challenges that require innovative solutions. As these devices continue to shrink in size while demanding higher performance, heat dissipation has become a critical bottleneck in system design. Current DDR5 modules operate at higher frequencies (4800-6400 MHz) and voltages compared to previous generations, resulting in thermal outputs that can exceed 5-7W per module under heavy workloads—a substantial increase from DDR4's typical 3-4W.

In compact IoT implementations, the thermal density problem is exacerbated by the limited physical space available for traditional cooling solutions. The proximity of components creates hotspots where temperatures can exceed 85°C, approaching the operational limits of DDR5 memory (typically 0-95°C). This thermal congestion is particularly problematic in edge computing devices that require continuous operation in variable environmental conditions, often without active cooling systems.

Current thermal solutions face significant constraints in these compact architectures. Traditional heat sinks and spreaders, effective in larger systems, become impractical when device thickness is limited to under 10mm, as is common in modern IoT endpoints. Thermal interface materials (TIMs) with improved conductivity (5-8 W/mK) are being employed but still struggle to efficiently transfer heat in tightly packed designs where airflow is minimal or non-existent.

The power management integrated circuits (PMICs) relocated onto the DDR5 modules themselves create additional thermal complexity. While this on-die power management improves voltage regulation efficiency, it concentrates heat generation directly on the memory module rather than distributing it across the motherboard as in previous generations. This concentration effect can create temperature gradients of 15-20°C across a single module in poorly ventilated designs.

Another significant challenge is the increased refresh rates required at higher temperatures. DDR5 memory requires 2x refresh rates when operating above 85°C, creating a negative feedback loop where higher temperatures lead to more frequent refresh operations, which in turn generate additional heat while reducing performance and increasing power consumption by up to 20%.

Passive cooling techniques like phase-change materials and graphene-based heat spreaders show promise but currently offer limited thermal conductivity (typically 10-25 W/mK) compared to what these compact DDR5 implementations require. The industry is actively seeking solutions that can provide effective cooling without increasing device dimensions or power requirements, as the thermal challenges threaten to become the primary limiting factor in the adoption of DDR5 memory in next-generation IoT architectures.

In compact IoT implementations, the thermal density problem is exacerbated by the limited physical space available for traditional cooling solutions. The proximity of components creates hotspots where temperatures can exceed 85°C, approaching the operational limits of DDR5 memory (typically 0-95°C). This thermal congestion is particularly problematic in edge computing devices that require continuous operation in variable environmental conditions, often without active cooling systems.

Current thermal solutions face significant constraints in these compact architectures. Traditional heat sinks and spreaders, effective in larger systems, become impractical when device thickness is limited to under 10mm, as is common in modern IoT endpoints. Thermal interface materials (TIMs) with improved conductivity (5-8 W/mK) are being employed but still struggle to efficiently transfer heat in tightly packed designs where airflow is minimal or non-existent.

The power management integrated circuits (PMICs) relocated onto the DDR5 modules themselves create additional thermal complexity. While this on-die power management improves voltage regulation efficiency, it concentrates heat generation directly on the memory module rather than distributing it across the motherboard as in previous generations. This concentration effect can create temperature gradients of 15-20°C across a single module in poorly ventilated designs.

Another significant challenge is the increased refresh rates required at higher temperatures. DDR5 memory requires 2x refresh rates when operating above 85°C, creating a negative feedback loop where higher temperatures lead to more frequent refresh operations, which in turn generate additional heat while reducing performance and increasing power consumption by up to 20%.

Passive cooling techniques like phase-change materials and graphene-based heat spreaders show promise but currently offer limited thermal conductivity (typically 10-25 W/mK) compared to what these compact DDR5 implementations require. The industry is actively seeking solutions that can provide effective cooling without increasing device dimensions or power requirements, as the thermal challenges threaten to become the primary limiting factor in the adoption of DDR5 memory in next-generation IoT architectures.

Contemporary DDR5 Heat Dissipation Approaches

01 Thermal management solutions for DDR5 memory modules

Various thermal management solutions are implemented for DDR5 memory modules to address heat dissipation challenges. These include specialized heat sinks, thermal interface materials, and cooling structures designed specifically for high-performance DDR5 memory. These solutions help maintain optimal operating temperatures, prevent thermal throttling, and extend the lifespan of memory components operating at higher frequencies and voltages.- Thermal management solutions for DDR5 memory modules: Various thermal management solutions are implemented for DDR5 memory modules to dissipate heat effectively. These include heat spreaders, thermal interface materials, and specialized cooling structures designed to maintain optimal operating temperatures. Advanced thermal designs help prevent performance degradation and ensure reliability during high-speed operations characteristic of DDR5 memory.

- Dynamic thermal throttling mechanisms: DDR5 memory implements dynamic thermal throttling mechanisms that monitor temperature and adjust performance parameters to prevent overheating. These systems can reduce clock speeds, adjust refresh rates, or modify power states when temperature thresholds are exceeded. This adaptive approach balances performance needs with thermal constraints to maintain system stability.

- Power management techniques for heat reduction: Advanced power management techniques are employed in DDR5 memory to reduce heat generation. These include voltage regulation modules integrated directly on memory modules, dynamic voltage scaling, and intelligent power state transitions. By optimizing power consumption based on workload demands, these techniques minimize thermal output while maintaining performance requirements.

- Memory controller optimizations for thermal efficiency: Memory controllers for DDR5 implement specialized algorithms and scheduling techniques to optimize thermal efficiency. These controllers can distribute memory access patterns to prevent hotspots, implement temperature-aware refresh schemes, and coordinate with system thermal management. Advanced controllers may also implement predictive thermal models to anticipate and prevent thermal issues before they occur.

- Physical design and layout considerations for heat dissipation: DDR5 memory modules incorporate specific physical design and layout considerations to enhance heat dissipation. These include optimized PCB designs with improved thermal conductivity, strategic component placement to facilitate airflow, and integration with system-level cooling solutions. Some designs feature increased spacing between memory chips or specialized materials to improve thermal performance in high-density configurations.

02 Dynamic thermal management techniques

Dynamic thermal management techniques are employed to regulate DDR5 memory temperatures during operation. These include adaptive frequency scaling, intelligent power management, and thermal monitoring systems that can adjust memory performance parameters based on temperature readings. By dynamically managing thermal conditions, these techniques help balance performance requirements with thermal constraints to prevent overheating while maintaining system responsiveness.Expand Specific Solutions03 Memory controller optimizations for thermal efficiency

Memory controllers are optimized to improve thermal efficiency in DDR5 systems. These optimizations include intelligent scheduling algorithms, workload distribution techniques, and power-aware memory access patterns. By controlling how and when memory is accessed, these controller optimizations help reduce hotspots, balance thermal loads across memory modules, and minimize unnecessary power consumption that contributes to heat generation.Expand Specific Solutions04 Physical design and layout considerations for heat dissipation

Physical design and layout considerations play a crucial role in DDR5 memory heat management. These include optimized PCB designs with improved thermal conductivity, strategic component placement to enhance airflow, and specialized memory module form factors that facilitate better heat dissipation. The physical arrangement of memory components and supporting structures is engineered to maximize thermal efficiency and minimize heat concentration in critical areas.Expand Specific Solutions05 System-level thermal solutions for DDR5 integration

System-level thermal solutions address DDR5 memory heat management within the context of the entire computing system. These include chassis airflow optimization, integrated cooling systems that address both CPU and memory thermal requirements, and thermal zone management techniques. By taking a holistic approach to thermal management, these solutions ensure that DDR5 memory operates within safe temperature ranges even under demanding workloads and in compact system designs.Expand Specific Solutions

Leading DDR5 Memory and Cooling Solution Providers

The DDR5 heat management market in compact IoT architectures is in its growth phase, with increasing demand driven by IoT device proliferation. The market is expanding rapidly as thermal challenges become critical in space-constrained designs. Leading semiconductor manufacturers like Samsung, Intel, and Micron are at the forefront of technological innovation, developing advanced thermal solutions for DDR5 memory in compact form factors. Companies such as Qualcomm and Huawei are integrating these technologies into their IoT platforms, while IBM and Dell are focusing on enterprise-level implementations. Chinese players including Zhaoxin and Hygon are emerging as significant competitors, particularly in regional markets. The technology is approaching maturity in standard applications but remains in development for ultra-compact IoT implementations requiring specialized thermal management approaches.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed an innovative thermal management solution for DDR5 memory in compact IoT architectures called "Low-Profile Heat Spreader Technology." This approach utilizes ultra-thin graphene-based heat spreaders with thickness under 0.5mm specifically designed for space-constrained IoT devices. The technology incorporates a multi-layered thermal interface material (TIM) that maximizes contact between memory modules and cooling elements while minimizing z-height requirements. Samsung's solution also features integrated temperature sensors that enable dynamic thermal management, allowing the memory to adjust refresh rates and operating parameters based on real-time temperature data. Their implementation includes specialized low-profile heat sinks with optimized fin designs that increase surface area while maintaining compact dimensions suitable for IoT form factors. Samsung has reported that this solution reduces DDR5 operating temperatures by up to 15°C compared to conventional cooling methods in similar space constraints.

Strengths: Exceptional thermal efficiency in ultra-compact form factors; seamless integration with existing manufacturing processes; dynamic thermal management capabilities. Weaknesses: Higher production costs compared to traditional cooling solutions; requires specialized manufacturing equipment; potential compatibility issues with some third-party IoT platforms.

Intel Corp.

Technical Solution: Intel has developed a comprehensive "Adaptive Thermal Distribution System" for DDR5 memory in IoT devices. This solution combines hardware and firmware innovations to address the unique thermal challenges of compact IoT architectures. At the hardware level, Intel employs a proprietary micro-vapor chamber design that's only 1.2mm thick, allowing for efficient heat dissipation without compromising the small form factor requirements of IoT devices. The system incorporates phase-change materials (PCMs) strategically placed between memory modules that absorb heat during peak operations and release it during idle periods, effectively smoothing temperature fluctuations. Intel's approach also includes an intelligent power management controller that dynamically adjusts memory voltage and timing parameters based on workload and temperature conditions, reducing heat generation during intensive operations. The firmware component includes thermal profiling algorithms that learn device usage patterns over time and preemptively adjust cooling parameters before thermal throttling occurs.

Strengths: Holistic approach combining hardware and firmware solutions; adaptive learning capabilities that improve thermal management over time; excellent compatibility with various IoT platforms. Weaknesses: Higher initial implementation cost; requires periodic firmware updates to maintain optimal performance; slightly increased power consumption for the thermal management subsystem.

Critical Patents in Compact Memory Cooling Technologies

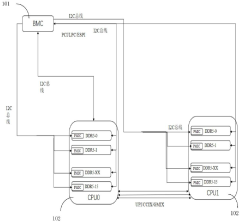

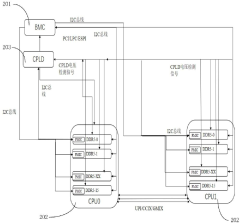

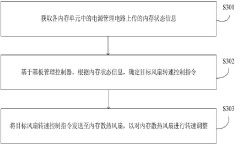

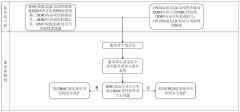

Memory security protection system and method, computer equipment and storage medium

PatentActiveCN118244865A

Innovation

- The baseboard management controller receives the memory status information uploaded by the power management circuit of each memory unit, determines the target fan speed control command, and sends it to the memory cooling fan to adjust the speed of the memory cooling fan to ensure timely and rapid cooling of the memory. and security.

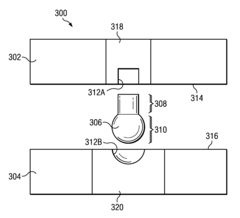

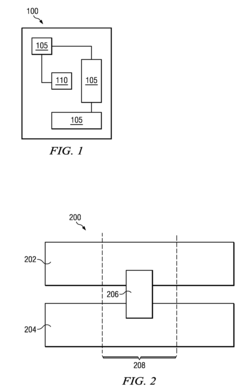

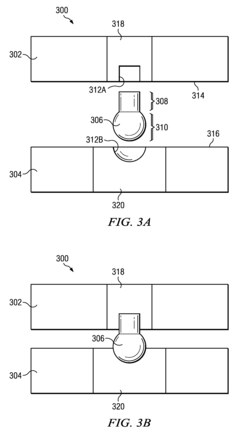

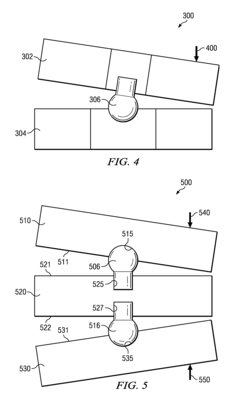

System for relieving stress and improving heat management in a 3D chip stack having an array of inter-stack connections

PatentActiveUS8564137B2

Innovation

- A stress relief apparatus that adjusts chip positioning in response to pressure and an elastic thermal material system with heat sink walls to manage heat, allowing for flexible interconnection and efficient heat transfer without sacrificing performance.

Power Efficiency Considerations for IoT DDR5 Applications

Power efficiency represents a critical consideration in the implementation of DDR5 memory within IoT architectures. As IoT devices continue to evolve toward more sophisticated computing capabilities while maintaining strict power constraints, the energy consumption profile of DDR5 becomes increasingly significant. The higher operating frequencies of DDR5 memory (4800-6400 MT/s) compared to DDR4 (3200 MT/s) create inherent power efficiency challenges that must be addressed through innovative approaches.

DDR5 introduces several power management features specifically designed to improve efficiency. The transition from a single 12V power management IC (PMIC) to on-DIMM voltage regulation allows for more precise power delivery and reduced voltage conversion losses. This architectural change enables finer-grained power states and improved energy proportionality, where power consumption scales more effectively with actual memory utilization patterns typical in IoT workloads.

Decision Feedback Equalization (DFE) and adaptive power management algorithms in DDR5 controllers can dynamically adjust power states based on workload characteristics. For IoT applications with intermittent processing requirements, these features can reduce idle power consumption by up to 30% compared to DDR4 implementations. The dual-channel architecture of DDR5 further enhances efficiency by allowing independent channel operation, enabling partial powering down of memory resources when full capacity is not required.

Thermal considerations directly impact power efficiency in compact IoT form factors. Higher operating temperatures increase leakage current, which can account for 15-20% of total memory power consumption in thermally constrained environments. Implementing effective thermal management solutions not only prevents performance throttling but also improves overall power efficiency by maintaining optimal operating temperatures.

Software-level optimizations play an equally important role in DDR5 power efficiency. Memory-aware scheduling algorithms that consolidate access patterns to minimize active-precharge cycles can reduce dynamic power consumption by 10-15%. Similarly, intelligent refresh management techniques that adapt refresh rates based on data retention characteristics and environmental conditions can significantly reduce background power consumption in IoT deployments.

When evaluating DDR5 for IoT applications, designers must consider the power-performance tradeoff carefully. While DDR5 offers substantially higher bandwidth, many IoT applications may not require the full performance potential, making power-optimized configurations more appropriate. Techniques such as frequency scaling, rank-based power gating, and workload-specific optimization of timing parameters can help achieve the optimal balance between performance capabilities and power constraints.

DDR5 introduces several power management features specifically designed to improve efficiency. The transition from a single 12V power management IC (PMIC) to on-DIMM voltage regulation allows for more precise power delivery and reduced voltage conversion losses. This architectural change enables finer-grained power states and improved energy proportionality, where power consumption scales more effectively with actual memory utilization patterns typical in IoT workloads.

Decision Feedback Equalization (DFE) and adaptive power management algorithms in DDR5 controllers can dynamically adjust power states based on workload characteristics. For IoT applications with intermittent processing requirements, these features can reduce idle power consumption by up to 30% compared to DDR4 implementations. The dual-channel architecture of DDR5 further enhances efficiency by allowing independent channel operation, enabling partial powering down of memory resources when full capacity is not required.

Thermal considerations directly impact power efficiency in compact IoT form factors. Higher operating temperatures increase leakage current, which can account for 15-20% of total memory power consumption in thermally constrained environments. Implementing effective thermal management solutions not only prevents performance throttling but also improves overall power efficiency by maintaining optimal operating temperatures.

Software-level optimizations play an equally important role in DDR5 power efficiency. Memory-aware scheduling algorithms that consolidate access patterns to minimize active-precharge cycles can reduce dynamic power consumption by 10-15%. Similarly, intelligent refresh management techniques that adapt refresh rates based on data retention characteristics and environmental conditions can significantly reduce background power consumption in IoT deployments.

When evaluating DDR5 for IoT applications, designers must consider the power-performance tradeoff carefully. While DDR5 offers substantially higher bandwidth, many IoT applications may not require the full performance potential, making power-optimized configurations more appropriate. Techniques such as frequency scaling, rank-based power gating, and workload-specific optimization of timing parameters can help achieve the optimal balance between performance capabilities and power constraints.

Reliability Testing Standards for Thermally-Constrained Environments

Reliability testing standards for thermally-constrained environments represent a critical framework for evaluating DDR5 memory performance in compact IoT architectures. These standards must account for the unique thermal challenges presented by miniaturized form factors where traditional cooling solutions are impractical or insufficient. Industry standards such as JEDEC's JEP122H and JESD22-A104E provide baseline methodologies, but require significant adaptation for IoT-specific thermal constraints.

The testing protocols must evaluate DDR5 modules under sustained high-temperature conditions, typically ranging from 85°C to 105°C, which represent the upper operational limits in compact IoT deployments. Thermal cycling tests should simulate the rapid temperature fluctuations common in edge computing environments, with transition rates of 10-15°C per minute between temperature extremes to assess thermal expansion stress on memory components and interconnects.

Accelerated life testing methodologies have been modified specifically for DDR5 in IoT applications, incorporating higher operating temperatures while maintaining realistic workloads. The Highly Accelerated Temperature and Humidity Stress Test (HAST) has emerged as particularly valuable, subjecting memory modules to 130°C at 85% relative humidity to evaluate moisture-related degradation mechanisms that are exacerbated in thermally-constrained environments.

Power cycling reliability tests have gained prominence in DDR5 evaluation frameworks, as IoT devices frequently transition between active and low-power states. These tests typically require 10,000+ power cycles while maintaining thermal monitoring to identify potential failure points in thermal management systems. The Mean Time Between Failure (MTBF) calculations have been adjusted to incorporate thermal acceleration factors specific to compact form factors.

On-die thermal sensors and integrated temperature monitoring have become mandatory components of reliability testing, with standards now requiring continuous temperature data collection at microsecond intervals during all test phases. This granular thermal profiling enables the identification of transient hotspots that might otherwise escape detection in traditional testing regimes.

Compliance with these specialized reliability standards requires sophisticated thermal chambers capable of maintaining temperature stability within ±0.5°C while simulating the airflow restrictions typical in IoT enclosures. Test duration requirements have increased significantly, with qualification testing now extending to 2,000 hours under maximum thermal load to account for the extended deployment lifespans expected of IoT infrastructure.

The testing protocols must evaluate DDR5 modules under sustained high-temperature conditions, typically ranging from 85°C to 105°C, which represent the upper operational limits in compact IoT deployments. Thermal cycling tests should simulate the rapid temperature fluctuations common in edge computing environments, with transition rates of 10-15°C per minute between temperature extremes to assess thermal expansion stress on memory components and interconnects.

Accelerated life testing methodologies have been modified specifically for DDR5 in IoT applications, incorporating higher operating temperatures while maintaining realistic workloads. The Highly Accelerated Temperature and Humidity Stress Test (HAST) has emerged as particularly valuable, subjecting memory modules to 130°C at 85% relative humidity to evaluate moisture-related degradation mechanisms that are exacerbated in thermally-constrained environments.

Power cycling reliability tests have gained prominence in DDR5 evaluation frameworks, as IoT devices frequently transition between active and low-power states. These tests typically require 10,000+ power cycles while maintaining thermal monitoring to identify potential failure points in thermal management systems. The Mean Time Between Failure (MTBF) calculations have been adjusted to incorporate thermal acceleration factors specific to compact form factors.

On-die thermal sensors and integrated temperature monitoring have become mandatory components of reliability testing, with standards now requiring continuous temperature data collection at microsecond intervals during all test phases. This granular thermal profiling enables the identification of transient hotspots that might otherwise escape detection in traditional testing regimes.

Compliance with these specialized reliability standards requires sophisticated thermal chambers capable of maintaining temperature stability within ±0.5°C while simulating the airflow restrictions typical in IoT enclosures. Test duration requirements have increased significantly, with qualification testing now extending to 2,000 hours under maximum thermal load to account for the extended deployment lifespans expected of IoT infrastructure.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!