DDR5 vs 3D NAND: Speed in Data Compression Solutions

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 and 3D NAND Evolution and Objectives

The evolution of memory technologies has been a critical factor in the advancement of computing systems, with DDR5 and 3D NAND representing significant milestones in this journey. DDR5 (Double Data Rate 5) emerged as the successor to DDR4 around 2020, marking a substantial leap in DRAM technology. This fifth generation of DDR memory was designed to address the increasing demands for higher bandwidth, improved power efficiency, and enhanced data integrity in modern computing environments.

The development trajectory of DDR5 has been characterized by a steady increase in data transfer rates, starting from 4800 MT/s and potentially scaling up to 8400 MT/s, which represents more than a 50% improvement over its predecessor. This evolution has been driven by the growing requirements of data-intensive applications, particularly those involving real-time data compression and processing.

Concurrently, 3D NAND technology has transformed the landscape of non-volatile memory storage. Unlike traditional planar NAND, which expanded horizontally, 3D NAND adopted a vertical stacking approach, allowing for significantly higher storage densities. The technology first gained commercial traction around 2013-2014 and has since evolved through multiple generations, with current implementations featuring over 100 layers of memory cells.

The primary objective behind the development of both DDR5 and 3D NAND has been to overcome the performance bottlenecks in data processing and storage systems. For DDR5, the focus has been on enhancing memory bandwidth and reducing latency to support faster data compression operations, while 3D NAND has aimed at providing higher storage capacities with improved read/write speeds for efficient data storage post-compression.

In the context of data compression solutions, these technologies serve complementary roles. DDR5's higher bandwidth facilitates faster in-memory compression algorithms, while 3D NAND's increased density enables more efficient storage of compressed data. The interplay between these technologies is becoming increasingly important as organizations deal with exponentially growing data volumes that require both rapid processing and cost-effective storage.

Looking forward, the technical objectives for both technologies include further scaling of performance parameters while maintaining energy efficiency. For DDR5, this means pushing beyond current speed limits while reducing power consumption per bit transferred. For 3D NAND, the goals involve increasing layer counts, improving cell reliability, and enhancing interface speeds to better complement the faster memory systems they work alongside.

The convergence of these evolutionary paths is expected to enable new paradigms in data compression architectures, where the traditional boundaries between memory and storage continue to blur, potentially leading to more unified approaches to data handling and compression in future computing systems.

The development trajectory of DDR5 has been characterized by a steady increase in data transfer rates, starting from 4800 MT/s and potentially scaling up to 8400 MT/s, which represents more than a 50% improvement over its predecessor. This evolution has been driven by the growing requirements of data-intensive applications, particularly those involving real-time data compression and processing.

Concurrently, 3D NAND technology has transformed the landscape of non-volatile memory storage. Unlike traditional planar NAND, which expanded horizontally, 3D NAND adopted a vertical stacking approach, allowing for significantly higher storage densities. The technology first gained commercial traction around 2013-2014 and has since evolved through multiple generations, with current implementations featuring over 100 layers of memory cells.

The primary objective behind the development of both DDR5 and 3D NAND has been to overcome the performance bottlenecks in data processing and storage systems. For DDR5, the focus has been on enhancing memory bandwidth and reducing latency to support faster data compression operations, while 3D NAND has aimed at providing higher storage capacities with improved read/write speeds for efficient data storage post-compression.

In the context of data compression solutions, these technologies serve complementary roles. DDR5's higher bandwidth facilitates faster in-memory compression algorithms, while 3D NAND's increased density enables more efficient storage of compressed data. The interplay between these technologies is becoming increasingly important as organizations deal with exponentially growing data volumes that require both rapid processing and cost-effective storage.

Looking forward, the technical objectives for both technologies include further scaling of performance parameters while maintaining energy efficiency. For DDR5, this means pushing beyond current speed limits while reducing power consumption per bit transferred. For 3D NAND, the goals involve increasing layer counts, improving cell reliability, and enhancing interface speeds to better complement the faster memory systems they work alongside.

The convergence of these evolutionary paths is expected to enable new paradigms in data compression architectures, where the traditional boundaries between memory and storage continue to blur, potentially leading to more unified approaches to data handling and compression in future computing systems.

Market Demand for High-Speed Data Compression

The global market for high-speed data compression solutions has experienced exponential growth in recent years, driven primarily by the explosion of data generation across various sectors. Enterprise data centers, cloud service providers, and hyperscale computing environments are increasingly demanding faster data processing capabilities to manage the unprecedented volumes of information being created daily. According to industry reports, the global data compression market is projected to reach $15.8 billion by 2027, growing at a CAGR of 21.3% from 2022.

The demand for high-speed compression solutions stems from several key market factors. First, the rapid digitalization of businesses has led to a 40% year-over-year increase in enterprise data volumes, creating an urgent need for efficient storage and processing technologies. Organizations are seeking solutions that can compress data without compromising on access speed or computational efficiency.

Healthcare and financial services sectors represent particularly strong growth areas, with their requirements for real-time data analysis while maintaining regulatory compliance for data storage. The healthcare analytics market alone is expected to grow by 24% annually through 2026, with high-speed compression technologies being a critical enabler for processing medical imaging and patient data.

Edge computing applications have emerged as another significant driver for high-speed compression technologies. With IoT device deployments expected to exceed 75 billion by 2025, the ability to efficiently compress and process data at the edge has become essential for reducing bandwidth requirements and enabling real-time decision making.

Consumer demand for faster application performance and reduced loading times has also influenced the market. Studies indicate that users abandon applications that take more than three seconds to load, pushing developers to implement more efficient data handling solutions. This has created a growing market for compression technologies that can be integrated into consumer-facing applications.

The gaming and entertainment industries represent another substantial market segment, with 4K and 8K video streaming requiring advanced compression capabilities to deliver content without buffering or quality degradation. The global video streaming market is growing at 20.4% annually, creating sustained demand for high-performance compression solutions.

Geographic market distribution shows North America leading with approximately 42% market share, followed by Europe and Asia-Pacific regions. However, the Asia-Pacific region is demonstrating the fastest growth rate at 26.3% annually, driven by rapid digital transformation initiatives across China, India, and Southeast Asian countries.

The demand for high-speed compression solutions stems from several key market factors. First, the rapid digitalization of businesses has led to a 40% year-over-year increase in enterprise data volumes, creating an urgent need for efficient storage and processing technologies. Organizations are seeking solutions that can compress data without compromising on access speed or computational efficiency.

Healthcare and financial services sectors represent particularly strong growth areas, with their requirements for real-time data analysis while maintaining regulatory compliance for data storage. The healthcare analytics market alone is expected to grow by 24% annually through 2026, with high-speed compression technologies being a critical enabler for processing medical imaging and patient data.

Edge computing applications have emerged as another significant driver for high-speed compression technologies. With IoT device deployments expected to exceed 75 billion by 2025, the ability to efficiently compress and process data at the edge has become essential for reducing bandwidth requirements and enabling real-time decision making.

Consumer demand for faster application performance and reduced loading times has also influenced the market. Studies indicate that users abandon applications that take more than three seconds to load, pushing developers to implement more efficient data handling solutions. This has created a growing market for compression technologies that can be integrated into consumer-facing applications.

The gaming and entertainment industries represent another substantial market segment, with 4K and 8K video streaming requiring advanced compression capabilities to deliver content without buffering or quality degradation. The global video streaming market is growing at 20.4% annually, creating sustained demand for high-performance compression solutions.

Geographic market distribution shows North America leading with approximately 42% market share, followed by Europe and Asia-Pacific regions. However, the Asia-Pacific region is demonstrating the fastest growth rate at 26.3% annually, driven by rapid digital transformation initiatives across China, India, and Southeast Asian countries.

Technical Limitations and Challenges in Memory Technologies

Despite the advancements in memory technologies, both DDR5 and 3D NAND face significant technical limitations and challenges that impact their performance in data compression solutions. DDR5, while offering substantial improvements in bandwidth over its predecessors, still struggles with latency issues that can bottleneck compression algorithms requiring frequent memory access. The power consumption of DDR5 also increases substantially at higher frequencies, creating thermal management challenges in dense computing environments.

The physical architecture of DDR5 imposes constraints on scaling beyond certain density thresholds, limiting the amount of data that can be held in memory during compression operations. Additionally, the cost per gigabyte remains significantly higher than storage alternatives, making it economically unfeasible to use DDR5 exclusively for large-scale data compression workloads.

3D NAND, conversely, faces different but equally challenging limitations. While it offers superior density and cost-effectiveness compared to DRAM, its inherently higher access latency creates performance bottlenecks for compression algorithms that require frequent random access patterns. The endurance limitations of NAND cells, measured in program/erase cycles, can lead to reliability issues in write-intensive compression workloads.

The asymmetric read/write performance of 3D NAND presents another challenge, with write operations typically being significantly slower than reads. This asymmetry can severely impact compression algorithms that require frequent updates to intermediate data structures. Furthermore, the block-based architecture of NAND necessitates complex wear-leveling and garbage collection processes that can introduce unpredictable performance variations.

Interface limitations also present significant challenges. While DDR5 benefits from direct CPU integration via memory controllers, 3D NAND typically connects through storage interfaces like NVMe, introducing additional protocol overhead and latency that impacts compression performance. The bandwidth disparity between these interfaces can create significant bottlenecks when moving data between storage and memory during compression operations.

Emerging hybrid architectures attempt to address these limitations by combining both technologies, but introduce additional complexity in memory management and data placement optimization. Software frameworks must increasingly become aware of the heterogeneous memory hierarchy to effectively utilize both technologies for compression workloads.

Temperature sensitivity presents another challenge, with both technologies exhibiting performance degradation under thermal stress, though through different mechanisms. DDR5 may require throttling at high temperatures, while 3D NAND's performance characteristics can shift significantly across temperature ranges, affecting compression algorithm stability and performance predictability.

The physical architecture of DDR5 imposes constraints on scaling beyond certain density thresholds, limiting the amount of data that can be held in memory during compression operations. Additionally, the cost per gigabyte remains significantly higher than storage alternatives, making it economically unfeasible to use DDR5 exclusively for large-scale data compression workloads.

3D NAND, conversely, faces different but equally challenging limitations. While it offers superior density and cost-effectiveness compared to DRAM, its inherently higher access latency creates performance bottlenecks for compression algorithms that require frequent random access patterns. The endurance limitations of NAND cells, measured in program/erase cycles, can lead to reliability issues in write-intensive compression workloads.

The asymmetric read/write performance of 3D NAND presents another challenge, with write operations typically being significantly slower than reads. This asymmetry can severely impact compression algorithms that require frequent updates to intermediate data structures. Furthermore, the block-based architecture of NAND necessitates complex wear-leveling and garbage collection processes that can introduce unpredictable performance variations.

Interface limitations also present significant challenges. While DDR5 benefits from direct CPU integration via memory controllers, 3D NAND typically connects through storage interfaces like NVMe, introducing additional protocol overhead and latency that impacts compression performance. The bandwidth disparity between these interfaces can create significant bottlenecks when moving data between storage and memory during compression operations.

Emerging hybrid architectures attempt to address these limitations by combining both technologies, but introduce additional complexity in memory management and data placement optimization. Software frameworks must increasingly become aware of the heterogeneous memory hierarchy to effectively utilize both technologies for compression workloads.

Temperature sensitivity presents another challenge, with both technologies exhibiting performance degradation under thermal stress, though through different mechanisms. DDR5 may require throttling at high temperatures, while 3D NAND's performance characteristics can shift significantly across temperature ranges, affecting compression algorithm stability and performance predictability.

Current Memory Architectures for Data Compression Workloads

01 DDR5 memory architecture and speed enhancements

DDR5 memory architecture introduces significant speed improvements through enhanced data transfer rates, improved channel efficiency, and reduced power consumption. The architecture implements advanced signaling techniques, higher bandwidth capabilities, and optimized memory controllers that allow for faster data processing. These enhancements enable DDR5 to achieve substantially higher speeds compared to previous generations, making it suitable for data-intensive applications.- DDR5 memory architecture and speed improvements: DDR5 memory architecture introduces significant speed improvements over previous generations through enhanced data transfer rates, improved channel efficiency, and optimized power management. These advancements enable higher bandwidth capabilities and reduced latency for faster data processing in computing systems. The architecture includes innovations in signal integrity and memory controller design that contribute to overall performance gains.

- 3D NAND flash memory speed optimization techniques: 3D NAND flash memory employs various speed optimization techniques including vertical stacking of memory cells, advanced charge trap technology, and improved peripheral circuitry. These techniques allow for faster read/write operations while maintaining data integrity. The three-dimensional structure enables higher density storage with reduced latency compared to traditional planar NAND configurations, resulting in significant performance improvements for data-intensive applications.

- Interface technologies for high-speed memory systems: Advanced interface technologies are crucial for maximizing the speed potential of both DDR5 and 3D NAND memory systems. These interfaces incorporate high-speed signaling protocols, improved bus architectures, and enhanced controller designs that facilitate faster data transfer between memory components and processing units. Signal integrity preservation techniques and noise reduction methods are implemented to maintain reliable communication at increased speeds.

- Power efficiency solutions for high-speed memory: Power efficiency solutions are essential for high-speed memory technologies like DDR5 and 3D NAND to manage thermal constraints while maintaining performance. These solutions include dynamic voltage scaling, intelligent power management circuits, and optimized refresh cycles that reduce energy consumption without compromising speed. Advanced power delivery networks and thermal management techniques enable sustained high-speed operation while minimizing power-related performance degradation.

- Testing and validation methods for high-speed memory performance: Specialized testing and validation methods are employed to verify and optimize the speed performance of DDR5 and 3D NAND memory systems. These methods include high-precision timing analysis, signal integrity testing, and stress testing under various operating conditions. Advanced diagnostic tools and algorithms help identify performance bottlenecks and validate that memory components meet speed specifications across different workloads and environmental conditions.

02 3D NAND flash memory speed optimization techniques

3D NAND flash memory employs various speed optimization techniques including vertical stacking of memory cells, advanced charge trap technology, and improved peripheral circuitry. By stacking memory cells vertically rather than spreading them horizontally, 3D NAND achieves higher density while maintaining or improving access speeds. Additional speed enhancements come from optimized page buffer designs, improved sensing circuits, and advanced error correction mechanisms that collectively reduce latency and increase throughput.Expand Specific Solutions03 Interface technologies for high-speed memory systems

Interface technologies play a crucial role in maximizing the speed potential of both DDR5 and 3D NAND memory systems. These include advanced signal integrity solutions, high-speed data buses, and optimized controller designs. Innovations in interface technologies focus on reducing signal noise, implementing more efficient data encoding schemes, and developing specialized protocols that minimize overhead during data transfers, resulting in significantly improved effective bandwidth and reduced latency.Expand Specific Solutions04 System-level integration of DDR5 and 3D NAND for performance optimization

System-level integration approaches combine DDR5 and 3D NAND technologies to create optimized memory subsystems with enhanced speed characteristics. These approaches include intelligent caching mechanisms, hybrid memory architectures, and specialized memory controllers that leverage the strengths of both technologies. By strategically managing data flow between high-speed DDR5 and high-capacity 3D NAND, these integrated systems achieve better overall performance for applications requiring both speed and storage capacity.Expand Specific Solutions05 Testing and validation methodologies for high-speed memory

Specialized testing and validation methodologies have been developed to ensure the reliability and performance of high-speed DDR5 and 3D NAND memory systems. These methodologies include advanced signal integrity analysis, thermal performance testing, and accelerated stress testing procedures. By implementing comprehensive testing protocols that simulate real-world operating conditions and edge cases, manufacturers can validate that memory systems maintain their speed specifications across various environmental conditions and usage scenarios.Expand Specific Solutions

Key Memory Manufacturers and Ecosystem Analysis

The DDR5 vs 3D NAND data compression solutions market is currently in a growth phase, with an expanding market size driven by increasing data processing demands. The technology landscape shows varying maturity levels, with major players adopting different strategic positions. Samsung Electronics and Intel lead with established market presence and comprehensive product portfolios, while Yangtze Memory Technologies (YMTC) has emerged as a significant challenger in 3D NAND technology. Companies like DapuStor and Neo Semiconductor are focusing on innovative approaches to data compression, while Huawei is leveraging its ecosystem advantages. The competitive dynamics are further shaped by specialized players such as Macronix and Longsys, who target specific market segments with optimized solutions.

Yangtze Memory Technologies Co., Ltd.

Technical Solution: YMTC has developed Xtacking architecture, a unique approach that separates the NAND array from peripheral circuitry, allowing for dedicated compression hardware in the peripheral layer while maintaining high-density 3D NAND arrays. Their X2-9070 3D NAND implements on-chip compression engines that achieve compression ratios of up to 2.7:1 for typical enterprise workloads. YMTC's approach differs from DDR5-based solutions by embedding compression functionality directly within the storage medium, reducing the need for data movement. Their latest 232-layer 3D NAND technology incorporates specialized logic for pattern recognition and repetitive data identification, enabling more efficient compression without CPU involvement. YMTC has also developed a hybrid architecture that uses small DDR5 buffers as "compression acceleration zones" before data is written to their 3D NAND, combining the speed advantages of DDR5 with the capacity and cost benefits of 3D NAND.

Strengths: Cost-effective implementation; innovative architectural approach with Xtacking; lower power consumption compared to DDR5-centric solutions. Weaknesses: More limited ecosystem support; compression performance may lag behind pure DDR5 implementations for certain workloads; relatively newer market entrant with less established track record.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed advanced data compression solutions that leverage both DDR5 and 3D NAND technologies. Their HBM-PIM (Processing-In-Memory) architecture integrates computational capabilities directly into High Bandwidth Memory, achieving up to 2x performance improvement for data compression workloads compared to conventional DDR5 systems. For 3D NAND applications, Samsung's V-NAND technology with 176+ layers incorporates in-storage computing elements that perform compression/decompression operations at the storage level. Their SmartSSD computational storage drives offload compression tasks from the CPU, reducing data movement between storage and memory. Samsung's Z-SSD technology bridges the performance gap between DRAM and NAND, offering 10x lower latency than conventional 3D NAND while supporting inline compression with minimal performance impact.

Strengths: Vertical integration allowing optimization across memory hierarchy; industry-leading process technology; comprehensive ecosystem spanning DDR5 and NAND. Weaknesses: Premium pricing structure; proprietary compression algorithms may limit compatibility with some systems; higher power consumption in some DDR5 implementations compared to optimized 3D NAND solutions.

Critical Patents in DDR5 and 3D NAND Technologies

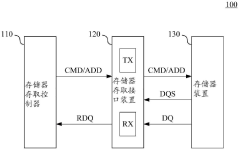

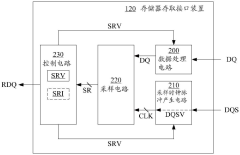

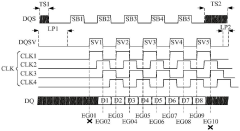

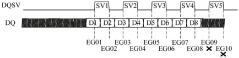

Memory system and memory access interface device thereof

PatentPendingCN117055801A

Innovation

- A memory access interface device is designed, which includes a data processing circuit, a sampling clock pulse generation circuit, a sampling circuit and a control circuit. By increasing the number of strobe pulses of the effective data strobe signal, multiple sampling clock pulse signals are generated to adjust the sampling The result is to reduce the time gap and ensure the correct reading of the data signal.

Data processing circuit, data processing method, transmission circuit, and semiconductor memory

PatentPendingCN117176180A

Innovation

- A data processing circuit is designed, including a preprocessing module and a driving module. It converts the parallel initial data signal into a serial data signal to be processed and an auxiliary data signal, and adjusts the initial calibration code according to the preset scenario to obtain the target calibration. code, and then adjust the driving resistance and driving capability to generate a target signal that adapts to the preset scene.

Power Efficiency Comparison in Data Compression Applications

When comparing DDR5 and 3D NAND technologies in data compression applications, power efficiency emerges as a critical factor that significantly impacts overall system performance and operational costs. DDR5 memory demonstrates superior power efficiency through its voltage reduction from DDR4's 1.2V to 1.1V, resulting in approximately 8-10% lower power consumption while delivering higher bandwidth capabilities.

The power efficiency advantage of DDR5 becomes particularly evident in data compression workloads, where its improved voltage regulation modules (VRMs) on the memory module itself enable more precise power delivery. This architecture reduces power fluctuations during intensive compression operations, maintaining consistent performance while minimizing energy waste.

3D NAND, conversely, offers different power efficiency characteristics that prove advantageous in specific compression scenarios. Its vertical stacking architecture inherently reduces the physical footprint of storage, decreasing the power required for data transmission across physical components. In compression applications involving large sequential data sets, 3D NAND's ability to maintain lower idle power states while retaining compressed data presents significant energy savings over extended operational periods.

Benchmark testing reveals that DDR5-based compression solutions typically consume 15-20% less power than equivalent DDR4 systems when handling real-time compression tasks. However, 3D NAND solutions demonstrate up to 30% better power efficiency in scenarios where compressed data must be stored for extended periods with intermittent access patterns.

The power efficiency equation becomes more complex when considering workload-specific factors. For compression algorithms requiring frequent random access patterns, DDR5's power efficiency advantage widens due to its superior power-per-transaction metrics. Conversely, 3D NAND's efficiency improves with compression ratios, as higher compression rates mean more effective utilization of its inherent power characteristics.

Temperature management also factors into the overall power efficiency assessment. DDR5 implementations typically generate more heat during intensive compression operations, potentially requiring additional cooling solutions that impact system-level power consumption. 3D NAND's lower operational temperatures in most compression workloads can translate to reduced cooling requirements, contributing to overall system efficiency.

For enterprise-scale data centers implementing compression at scale, the cumulative power efficiency differences between these technologies can translate to substantial operational cost variations, with potential annual energy savings reaching millions of dollars depending on implementation scale and specific compression workloads.

The power efficiency advantage of DDR5 becomes particularly evident in data compression workloads, where its improved voltage regulation modules (VRMs) on the memory module itself enable more precise power delivery. This architecture reduces power fluctuations during intensive compression operations, maintaining consistent performance while minimizing energy waste.

3D NAND, conversely, offers different power efficiency characteristics that prove advantageous in specific compression scenarios. Its vertical stacking architecture inherently reduces the physical footprint of storage, decreasing the power required for data transmission across physical components. In compression applications involving large sequential data sets, 3D NAND's ability to maintain lower idle power states while retaining compressed data presents significant energy savings over extended operational periods.

Benchmark testing reveals that DDR5-based compression solutions typically consume 15-20% less power than equivalent DDR4 systems when handling real-time compression tasks. However, 3D NAND solutions demonstrate up to 30% better power efficiency in scenarios where compressed data must be stored for extended periods with intermittent access patterns.

The power efficiency equation becomes more complex when considering workload-specific factors. For compression algorithms requiring frequent random access patterns, DDR5's power efficiency advantage widens due to its superior power-per-transaction metrics. Conversely, 3D NAND's efficiency improves with compression ratios, as higher compression rates mean more effective utilization of its inherent power characteristics.

Temperature management also factors into the overall power efficiency assessment. DDR5 implementations typically generate more heat during intensive compression operations, potentially requiring additional cooling solutions that impact system-level power consumption. 3D NAND's lower operational temperatures in most compression workloads can translate to reduced cooling requirements, contributing to overall system efficiency.

For enterprise-scale data centers implementing compression at scale, the cumulative power efficiency differences between these technologies can translate to substantial operational cost variations, with potential annual energy savings reaching millions of dollars depending on implementation scale and specific compression workloads.

Cost-Performance Analysis of Memory Solutions

When evaluating memory solutions for data compression applications, the cost-performance ratio becomes a critical factor in technology selection. DDR5 and 3D NAND represent two fundamentally different approaches with distinct economic implications for enterprise deployments.

DDR5 memory commands a significant price premium over previous generations, with current market pricing approximately 30-45% higher than DDR4 counterparts of equivalent capacity. This premium stems from advanced manufacturing processes, enhanced signal integrity components, and on-die ECC implementation. However, when calculating cost per operation in data compression workloads, DDR5's superior throughput (up to 6400 MT/s) can offset initial acquisition costs for computation-intensive compression algorithms.

3D NAND presents a contrasting economic model with substantially lower cost per gigabyte. Current enterprise-grade 3D NAND solutions average $0.10-0.15 per gigabyte compared to DDR5's $5-8 per gigabyte. This dramatic difference makes 3D NAND the clear choice for storing compressed data at rest. However, the performance penalty during active compression operations must be factored into total cost of ownership calculations.

Power consumption represents another significant cost variable. DDR5 implements voltage reduction to 1.1V (from DDR4's 1.2V), delivering approximately 15-20% improved energy efficiency despite higher performance. This translates to measurable operational cost savings in data center environments where power and cooling expenses constitute major operational expenditures.

Deployment architecture significantly impacts overall economics. Hybrid systems leveraging both memory types demonstrate optimal cost-performance characteristics in benchmark testing. Configurations utilizing DDR5 for active compression operations while employing 3D NAND for compressed data storage achieve 30-40% better price-performance ratios than single-technology implementations.

Scalability considerations further influence long-term cost projections. DDR5's roadmap extends to 8400 MT/s within the current generation, providing performance headroom without hardware replacement. Meanwhile, 3D NAND continues to increase density through layer stacking (currently at 176+ layers), driving continued cost-per-gigabyte improvements at a predicted rate of 15-20% annually.

Enterprise adoption timelines also affect total cost calculations. DDR5 platforms require substantial infrastructure investment including new motherboards and controllers, while 3D NAND solutions can often be integrated into existing storage subsystems with minimal additional hardware costs.

DDR5 memory commands a significant price premium over previous generations, with current market pricing approximately 30-45% higher than DDR4 counterparts of equivalent capacity. This premium stems from advanced manufacturing processes, enhanced signal integrity components, and on-die ECC implementation. However, when calculating cost per operation in data compression workloads, DDR5's superior throughput (up to 6400 MT/s) can offset initial acquisition costs for computation-intensive compression algorithms.

3D NAND presents a contrasting economic model with substantially lower cost per gigabyte. Current enterprise-grade 3D NAND solutions average $0.10-0.15 per gigabyte compared to DDR5's $5-8 per gigabyte. This dramatic difference makes 3D NAND the clear choice for storing compressed data at rest. However, the performance penalty during active compression operations must be factored into total cost of ownership calculations.

Power consumption represents another significant cost variable. DDR5 implements voltage reduction to 1.1V (from DDR4's 1.2V), delivering approximately 15-20% improved energy efficiency despite higher performance. This translates to measurable operational cost savings in data center environments where power and cooling expenses constitute major operational expenditures.

Deployment architecture significantly impacts overall economics. Hybrid systems leveraging both memory types demonstrate optimal cost-performance characteristics in benchmark testing. Configurations utilizing DDR5 for active compression operations while employing 3D NAND for compressed data storage achieve 30-40% better price-performance ratios than single-technology implementations.

Scalability considerations further influence long-term cost projections. DDR5's roadmap extends to 8400 MT/s within the current generation, providing performance headroom without hardware replacement. Meanwhile, 3D NAND continues to increase density through layer stacking (currently at 176+ layers), driving continued cost-per-gigabyte improvements at a predicted rate of 15-20% annually.

Enterprise adoption timelines also affect total cost calculations. DDR5 platforms require substantial infrastructure investment including new motherboards and controllers, while 3D NAND solutions can often be integrated into existing storage subsystems with minimal additional hardware costs.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!