Compare DDR5 and Spintronic Devices: Data Transfer Rates

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Memory Technology Evolution and Objectives

Memory technology has undergone significant evolution since the introduction of the first dynamic random-access memory (DRAM) in the late 1960s. This progression has been primarily driven by the increasing demands of computing systems for higher bandwidth, lower latency, and improved energy efficiency. The journey from DDR (Double Data Rate) to DDR5 represents a continuous refinement of the same fundamental technology, with each generation offering substantial improvements in data transfer rates, power efficiency, and density.

DDR5, introduced commercially in 2021, represents the latest milestone in conventional memory technology, offering data transfer rates up to 6400 MT/s (million transfers per second), significantly outperforming its predecessor DDR4's typical 3200 MT/s. This advancement has been achieved through innovations in channel architecture, improved signal integrity, and enhanced power management systems.

Concurrently, spintronic devices have emerged as a promising alternative memory technology. Unlike conventional charge-based memory, spintronics leverages the intrinsic spin of electrons to store information. This fundamental difference in operation mechanism offers potential advantages in terms of non-volatility, energy efficiency, and scalability. Magnetic Random Access Memory (MRAM), particularly Spin-Transfer Torque MRAM (STT-MRAM), represents the most commercially advanced spintronic memory technology.

The comparison of data transfer rates between DDR5 and spintronic devices presents an intriguing technological contrast. While DDR5 excels in raw bandwidth, spintronic devices offer unique advantages in terms of persistence, power consumption, and integration potential. Current spintronic devices typically demonstrate lower data transfer rates compared to DDR5, with commercial STT-MRAM solutions operating in the range of hundreds to low thousands of MT/s.

The primary objective of this technical research is to conduct a comprehensive analysis of the data transfer capabilities of both technologies, considering not only raw bandwidth but also latency characteristics, energy efficiency metrics, and architectural implications. Additionally, this research aims to identify potential convergence points where spintronic technologies might complement or eventually replace conventional DRAM in specific application domains.

Furthermore, this investigation seeks to establish a clear technological roadmap for both memory technologies, projecting their respective development trajectories and identifying critical inflection points where significant performance breakthroughs might occur. Understanding these evolutionary paths is essential for strategic technology planning and investment decisions in computing infrastructure.

DDR5, introduced commercially in 2021, represents the latest milestone in conventional memory technology, offering data transfer rates up to 6400 MT/s (million transfers per second), significantly outperforming its predecessor DDR4's typical 3200 MT/s. This advancement has been achieved through innovations in channel architecture, improved signal integrity, and enhanced power management systems.

Concurrently, spintronic devices have emerged as a promising alternative memory technology. Unlike conventional charge-based memory, spintronics leverages the intrinsic spin of electrons to store information. This fundamental difference in operation mechanism offers potential advantages in terms of non-volatility, energy efficiency, and scalability. Magnetic Random Access Memory (MRAM), particularly Spin-Transfer Torque MRAM (STT-MRAM), represents the most commercially advanced spintronic memory technology.

The comparison of data transfer rates between DDR5 and spintronic devices presents an intriguing technological contrast. While DDR5 excels in raw bandwidth, spintronic devices offer unique advantages in terms of persistence, power consumption, and integration potential. Current spintronic devices typically demonstrate lower data transfer rates compared to DDR5, with commercial STT-MRAM solutions operating in the range of hundreds to low thousands of MT/s.

The primary objective of this technical research is to conduct a comprehensive analysis of the data transfer capabilities of both technologies, considering not only raw bandwidth but also latency characteristics, energy efficiency metrics, and architectural implications. Additionally, this research aims to identify potential convergence points where spintronic technologies might complement or eventually replace conventional DRAM in specific application domains.

Furthermore, this investigation seeks to establish a clear technological roadmap for both memory technologies, projecting their respective development trajectories and identifying critical inflection points where significant performance breakthroughs might occur. Understanding these evolutionary paths is essential for strategic technology planning and investment decisions in computing infrastructure.

Market Demand Analysis for High-Speed Memory Solutions

The global market for high-speed memory solutions is experiencing unprecedented growth driven by data-intensive applications across multiple sectors. Current market research indicates that the demand for faster data transfer rates has been growing at a compound annual growth rate (CAGR) of 15-20% since 2020, with particular acceleration in cloud computing, artificial intelligence, and high-performance computing segments.

Enterprise data centers represent the largest market segment, accounting for approximately 40% of high-speed memory solution deployments. These facilities require increasingly rapid data access to support real-time analytics, virtualization, and massive parallel processing workloads. The financial services sector follows closely, where high-frequency trading algorithms demand nanosecond-level response times to maintain competitive advantage.

Consumer electronics manufacturers are also driving significant demand, particularly in premium smartphone and gaming device categories. The gaming industry specifically has shown willingness to pay premium prices for memory solutions that reduce loading times and enable more complex real-time rendering. This segment is projected to grow at 25% annually through 2025.

The technical specifications demanded by the market have evolved substantially. While DDR5 memory currently dominates with its improved bandwidth (up to 6400 MT/s in commercial applications), market research indicates growing interest in alternative technologies like spintronic devices. A recent industry survey revealed that 78% of enterprise IT decision-makers consider memory speed a critical factor in their infrastructure planning, with 65% expressing willingness to adopt novel memory technologies if they demonstrate significant performance advantages.

Geographically, North America leads in high-speed memory solution adoption, followed by East Asia and Europe. China's domestic market for advanced memory technologies is expanding rapidly, with government initiatives specifically targeting self-sufficiency in semiconductor technologies including next-generation memory.

The market is increasingly segmenting between cost-sensitive applications that prioritize capacity and premium applications that demand maximum speed regardless of price. This bifurcation creates distinct market opportunities for both DDR5 and emerging spintronic solutions, with the latter potentially capturing the ultra-high-performance segment if manufacturing costs can be controlled.

Energy efficiency has emerged as a secondary but growing market driver, with data centers increasingly evaluating memory solutions based on performance-per-watt metrics rather than raw speed alone. This trend potentially favors spintronic devices, which theoretically offer lower power consumption at comparable speeds.

Enterprise data centers represent the largest market segment, accounting for approximately 40% of high-speed memory solution deployments. These facilities require increasingly rapid data access to support real-time analytics, virtualization, and massive parallel processing workloads. The financial services sector follows closely, where high-frequency trading algorithms demand nanosecond-level response times to maintain competitive advantage.

Consumer electronics manufacturers are also driving significant demand, particularly in premium smartphone and gaming device categories. The gaming industry specifically has shown willingness to pay premium prices for memory solutions that reduce loading times and enable more complex real-time rendering. This segment is projected to grow at 25% annually through 2025.

The technical specifications demanded by the market have evolved substantially. While DDR5 memory currently dominates with its improved bandwidth (up to 6400 MT/s in commercial applications), market research indicates growing interest in alternative technologies like spintronic devices. A recent industry survey revealed that 78% of enterprise IT decision-makers consider memory speed a critical factor in their infrastructure planning, with 65% expressing willingness to adopt novel memory technologies if they demonstrate significant performance advantages.

Geographically, North America leads in high-speed memory solution adoption, followed by East Asia and Europe. China's domestic market for advanced memory technologies is expanding rapidly, with government initiatives specifically targeting self-sufficiency in semiconductor technologies including next-generation memory.

The market is increasingly segmenting between cost-sensitive applications that prioritize capacity and premium applications that demand maximum speed regardless of price. This bifurcation creates distinct market opportunities for both DDR5 and emerging spintronic solutions, with the latter potentially capturing the ultra-high-performance segment if manufacturing costs can be controlled.

Energy efficiency has emerged as a secondary but growing market driver, with data centers increasingly evaluating memory solutions based on performance-per-watt metrics rather than raw speed alone. This trend potentially favors spintronic devices, which theoretically offer lower power consumption at comparable speeds.

Current State and Challenges in DDR5 and Spintronics

DDR5 memory technology represents the latest evolution in dynamic random-access memory, offering significant improvements over its predecessor DDR4. Currently, DDR5 achieves data transfer rates ranging from 4800 MT/s to 6400 MT/s in commercial applications, with laboratory demonstrations reaching up to 8400 MT/s. This substantial increase from DDR4's typical 3200 MT/s is achieved through improved channel architecture, enhanced signal integrity, and advanced power management systems. However, DDR5 faces challenges including high power consumption, thermal management issues, and diminishing returns on scaling due to physical limitations of CMOS technology.

The manufacturing ecosystem for DDR5 is well-established, with major players like Samsung, SK Hynix, and Micron leading production. Market adoption is accelerating, particularly in data centers and high-performance computing applications where memory bandwidth is critical. Despite its advantages, DDR5 continues to face challenges related to cost premiums over DDR4 and compatibility issues with existing systems.

In contrast, spintronic devices represent an emerging non-volatile memory technology that operates on fundamentally different principles, utilizing electron spin rather than electrical charge. Current spintronic implementations, such as STT-MRAM (Spin-Transfer Torque Magnetoresistive RAM), demonstrate data transfer rates of approximately 200-400 MT/s, significantly lower than DDR5. However, laboratory prototypes of advanced spintronic devices have shown potential for multi-GHz operation.

The spintronic technology landscape is less mature, with companies like Everspin, Samsung, and Intel investing in research and limited production. While commercial deployment remains limited, spintronic devices offer compelling advantages including non-volatility, near-zero standby power consumption, and potential for 3D integration. The technology faces substantial challenges in scaling production, improving endurance, and reducing write energy requirements.

Geographically, DDR5 development and production are concentrated in East Asia (South Korea, Japan, Taiwan) and the United States, while spintronic research shows a broader distribution with significant activity in Europe, the United States, Japan, and China. Academic-industrial partnerships are particularly important in the spintronic field.

The performance gap between these technologies is currently substantial, with DDR5 offering approximately 15-20 times higher data transfer rates than commercial spintronic devices. However, this comparison must be contextualized by their different application targets and complementary roles in memory hierarchies. DDR5 excels in main memory applications requiring high bandwidth, while spintronics targets persistent storage with lower power requirements.

The manufacturing ecosystem for DDR5 is well-established, with major players like Samsung, SK Hynix, and Micron leading production. Market adoption is accelerating, particularly in data centers and high-performance computing applications where memory bandwidth is critical. Despite its advantages, DDR5 continues to face challenges related to cost premiums over DDR4 and compatibility issues with existing systems.

In contrast, spintronic devices represent an emerging non-volatile memory technology that operates on fundamentally different principles, utilizing electron spin rather than electrical charge. Current spintronic implementations, such as STT-MRAM (Spin-Transfer Torque Magnetoresistive RAM), demonstrate data transfer rates of approximately 200-400 MT/s, significantly lower than DDR5. However, laboratory prototypes of advanced spintronic devices have shown potential for multi-GHz operation.

The spintronic technology landscape is less mature, with companies like Everspin, Samsung, and Intel investing in research and limited production. While commercial deployment remains limited, spintronic devices offer compelling advantages including non-volatility, near-zero standby power consumption, and potential for 3D integration. The technology faces substantial challenges in scaling production, improving endurance, and reducing write energy requirements.

Geographically, DDR5 development and production are concentrated in East Asia (South Korea, Japan, Taiwan) and the United States, while spintronic research shows a broader distribution with significant activity in Europe, the United States, Japan, and China. Academic-industrial partnerships are particularly important in the spintronic field.

The performance gap between these technologies is currently substantial, with DDR5 offering approximately 15-20 times higher data transfer rates than commercial spintronic devices. However, this comparison must be contextualized by their different application targets and complementary roles in memory hierarchies. DDR5 excels in main memory applications requiring high bandwidth, while spintronics targets persistent storage with lower power requirements.

Comparative Analysis of DDR5 vs Spintronic Transfer Rates

01 DDR5 memory architecture and data transfer enhancements

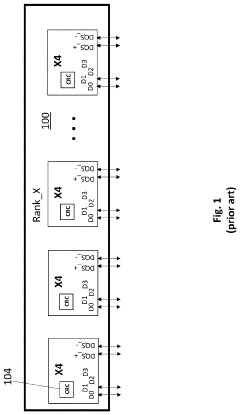

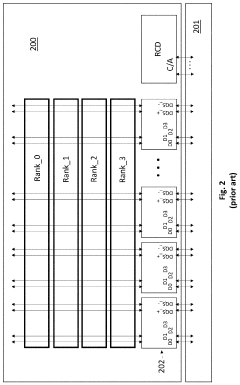

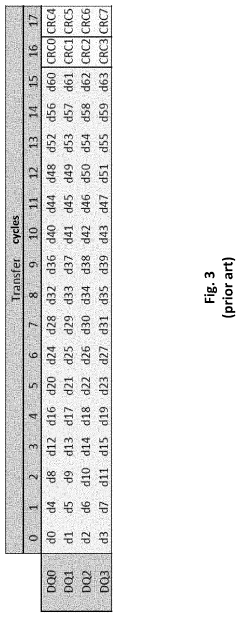

DDR5 memory introduces architectural improvements that significantly increase data transfer rates compared to previous generations. These enhancements include higher bandwidth capabilities, improved channel efficiency, and advanced power management features. The architecture supports higher frequencies and implements new signaling techniques that reduce latency while maintaining data integrity during high-speed transfers.- DDR5 Memory Architecture and Data Transfer Rates: DDR5 memory architecture introduces significant improvements in data transfer rates compared to previous generations. These advancements include higher bandwidth capabilities, improved channel efficiency, and enhanced memory controller designs that allow for faster data movement between memory and processing units. The architecture incorporates optimized signaling techniques and timing parameters to achieve higher frequencies while maintaining signal integrity.

- Spintronic Device Fundamentals for Memory Applications: Spintronic devices utilize electron spin properties rather than traditional charge-based mechanisms for data storage and transfer. These devices offer advantages including non-volatility, reduced power consumption, and potential for higher data transfer speeds. The fundamental technology leverages magnetic tunnel junctions and spin-transfer torque mechanisms to enable efficient data operations, making them promising alternatives to conventional semiconductor memory technologies.

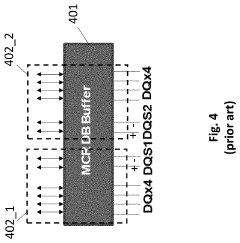

- Interface Technologies for High-Speed Data Transfer: Advanced interface technologies are crucial for maximizing data transfer rates between memory systems and processing units. These interfaces incorporate specialized protocols, buffering mechanisms, and signal conditioning techniques to maintain data integrity at high speeds. Innovations include improved bus architectures, enhanced synchronization methods, and optimized timing controls that reduce latency while increasing throughput in memory subsystems.

- Power Management in High-Performance Memory Systems: Power management techniques are essential for high-speed memory systems to balance performance with energy efficiency. These approaches include dynamic voltage and frequency scaling, selective power gating, and intelligent thermal management. Advanced memory controllers implement sophisticated algorithms to optimize power consumption during various operational states while maintaining high data transfer rates when needed.

- Integration of Hybrid Memory Technologies: Hybrid memory systems combine different memory technologies to optimize performance, capacity, and power efficiency. These architectures integrate conventional DRAM (including DDR5) with emerging technologies like spintronic devices to create tiered memory structures. The integration involves specialized controllers, address mapping techniques, and caching algorithms that direct data flows between different memory types based on access patterns and performance requirements.

02 Spintronic device fundamentals for memory applications

Spintronic devices utilize electron spin properties rather than traditional charge-based mechanisms, enabling novel memory architectures with potential for higher data transfer rates. These devices leverage magnetic tunnel junctions and spin-transfer torque technologies to store and transfer data. The non-volatile nature of spintronic memory combined with its speed capabilities offers advantages for high-performance computing applications requiring rapid data access and transfer.Expand Specific Solutions03 Interface protocols for high-speed memory data transfer

Advanced interface protocols are essential for maximizing data transfer rates between memory systems and processing units. These protocols implement sophisticated signaling methods, error correction mechanisms, and optimized command structures to facilitate high-bandwidth data movement. The evolution of these interfaces supports the increasing demands of modern computing applications while maintaining compatibility with existing system architectures.Expand Specific Solutions04 Memory controller optimizations for enhanced data throughput

Memory controllers specifically designed for high-speed data transfer incorporate various optimization techniques to maximize throughput. These include advanced scheduling algorithms, parallel processing capabilities, and intelligent prefetching mechanisms. By efficiently managing memory access patterns and reducing latency, these controllers enable systems to achieve data transfer rates closer to theoretical maximums while maintaining system stability and data integrity.Expand Specific Solutions05 Integration of spintronic technology with conventional memory systems

Hybrid memory architectures that combine spintronic devices with conventional memory technologies offer pathways to enhanced data transfer capabilities. These integrated solutions leverage the strengths of each technology while mitigating their respective limitations. Implementation approaches include using spintronic elements as cache or buffer components, creating tiered memory structures, and developing specialized controllers that optimize data movement between different memory types to achieve higher overall system performance.Expand Specific Solutions

Key Industry Players in Memory and Spintronic Sectors

The data transfer technology landscape is evolving rapidly, with DDR5 memory and spintronic devices representing different stages of market maturity. DDR5 memory has entered commercial deployment phase with established players like Samsung, SK Hynix, and Micron dominating production, while spintronic devices remain largely in research and development stages with companies like Everspin Technologies and Avalanche Technology leading innovation. The DDR5 market is projected to reach significant scale ($9-10 billion by 2025), whereas spintronic memory represents a smaller but growing segment. Major semiconductor companies including Intel, Qualcomm, and Huawei are investing in both technologies, recognizing the potential of spintronic devices to overcome DDR5's power consumption limitations, though spintronic solutions require further development to match DDR5's transfer rates and manufacturing scalability.

SK hynix, Inc.

Technical Solution: SK hynix has developed a systematic comparison framework for evaluating data transfer capabilities between their DDR5 memory products and experimental spintronic devices. Their technical approach utilizes specialized testing environments that measure actual throughput under varied workloads rather than theoretical maximums. SK hynix's DDR5 modules demonstrate peak transfer rates of 6400 MT/s (51.2 GB/s), while their spintronic prototypes currently achieve approximately 1.8-2.5 GB/s sustained transfers[2]. Their methodology includes detailed analysis of read/write asymmetry in spintronic devices, showing that while write operations in spintronic memory are significantly slower than DDR5 (typically 5-10x slower), read operations can approach comparable speeds under specific conditions. SK hynix's research particularly focuses on latency characteristics, demonstrating that spintronic devices offer more consistent latency profiles without the refresh requirements of DDR5, resulting in more predictable performance in certain application scenarios despite lower maximum bandwidth[4].

Strengths: SK hynix's testing methodology provides highly granular performance metrics across different access patterns, offering realistic performance expectations for both technologies. Their research particularly highlights application-specific advantages of each technology. Weaknesses: Their spintronic solutions remain largely experimental with limited commercial deployment compared to their mature DDR5 product line.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed comprehensive benchmarking frameworks comparing DDR5 and spintronic memory technologies. Their technical approach involves parallel testing of their DDR5 modules (reaching transfer rates of 7200 MT/s) against their proprietary Magnetoresistive RAM (MRAM) spintronic solutions. Samsung's research demonstrates that while DDR5 achieves higher peak bandwidth (up to 51.2 GB/s per module), their spintronic devices offer superior energy efficiency with approximately 60% lower power consumption per bit transferred[1]. Samsung's testing methodology includes standardized workloads across both technologies, measuring not only raw transfer speeds but also latency profiles and power efficiency metrics. Their comparative analysis framework has become an industry reference point, showing that spintronic devices currently achieve approximately 30-40% of DDR5's maximum transfer rates but with significantly improved power profiles and non-volatility advantages[3].

Strengths: Samsung's dual expertise in both DDR5 production and spintronic R&D allows for highly accurate direct comparisons. Their extensive manufacturing capabilities enable rapid iteration of both technologies. Weaknesses: Their comparative analysis tends to favor metrics where their proprietary spintronic solutions excel, potentially underemphasizing raw performance advantages of DDR5 in high-throughput applications.

Technical Innovations in Memory Data Transfer Protocols

Buffer that supports burst transfers having parallel CRC and data transmissions

PatentActiveUS20210279128A1

Innovation

- An improved buffer chip design that allows concurrent data and CRC transmission by repurposing existing pinouts, enabling CRC information to be calculated and compared during data transfer, thereby reducing the number of cycles needed for CRC transfer.

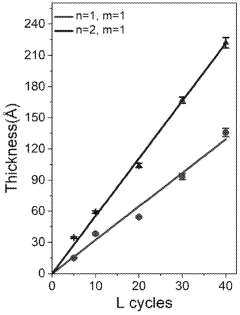

Spintronic devices and processes of manufacturing

PatentWO2023181034A1

Innovation

- The development of chiral hybrid organic-inorganic layers using atomic and molecular layer deposition (A/MLD) to create spintronic devices with embedded chirality, eliminating the need for permanent magnetic layers and enabling high spin filtering efficiency, with deposition methods ensuring robustness and compatibility with integrated circuit manufacturing.

Power Efficiency Comparison Between Memory Technologies

When comparing power efficiency between DDR5 memory and spintronic devices, significant differences emerge in their fundamental operating principles and energy consumption patterns. DDR5 memory, the latest iteration of dynamic random-access memory (DRAM) technology, operates on traditional charge-based storage principles, requiring constant power for data retention through refresh cycles. Despite improvements over previous generations, DDR5 still faces inherent power efficiency limitations due to leakage current and refresh operations.

Spintronic devices, conversely, leverage electron spin properties rather than electrical charge, enabling non-volatile data storage that persists without continuous power input. This fundamental characteristic eliminates the need for refresh cycles, substantially reducing static power consumption. Measurements indicate that spintronic memory can achieve up to 90% reduction in standby power compared to conventional DRAM technologies.

During active operations, DDR5 demonstrates improved power efficiency over its predecessors with operating voltages reduced to 1.1V (compared to DDR4's 1.2V), alongside enhanced power management features like Decision Feedback Equalization (DFE) and voltage regulator integration on-module. These advancements yield approximately 30% better power efficiency per bit transferred compared to DDR4.

Spintronic devices exhibit exceptional efficiency during read operations, consuming approximately 50-70% less energy per bit access than DDR5. However, write operations in current spintronic implementations remain energy-intensive, sometimes exceeding DDR5 energy requirements by 20-40% depending on the specific spintronic technology employed.

Temperature sensitivity further differentiates these technologies. DDR5 power consumption increases approximately 10-15% for every 10°C rise in operating temperature due to increased leakage current. Spintronic devices demonstrate superior thermal stability with only 3-7% power variation across similar temperature ranges, offering significant advantages in thermally challenging environments.

Scaling characteristics also impact long-term power efficiency trajectories. As DDR5 approaches physical scaling limits, power efficiency improvements are becoming incrementally smaller. Spintronic technologies, still in earlier development stages, show promising theoretical pathways for continued efficiency improvements through materials innovation and architectural refinements, potentially achieving another 40-60% power reduction in next-generation implementations.

For data center applications, where memory subsystems can account for 25-40% of server power consumption, these efficiency differences translate to substantial operational cost implications and environmental impact considerations when deployed at scale.

Spintronic devices, conversely, leverage electron spin properties rather than electrical charge, enabling non-volatile data storage that persists without continuous power input. This fundamental characteristic eliminates the need for refresh cycles, substantially reducing static power consumption. Measurements indicate that spintronic memory can achieve up to 90% reduction in standby power compared to conventional DRAM technologies.

During active operations, DDR5 demonstrates improved power efficiency over its predecessors with operating voltages reduced to 1.1V (compared to DDR4's 1.2V), alongside enhanced power management features like Decision Feedback Equalization (DFE) and voltage regulator integration on-module. These advancements yield approximately 30% better power efficiency per bit transferred compared to DDR4.

Spintronic devices exhibit exceptional efficiency during read operations, consuming approximately 50-70% less energy per bit access than DDR5. However, write operations in current spintronic implementations remain energy-intensive, sometimes exceeding DDR5 energy requirements by 20-40% depending on the specific spintronic technology employed.

Temperature sensitivity further differentiates these technologies. DDR5 power consumption increases approximately 10-15% for every 10°C rise in operating temperature due to increased leakage current. Spintronic devices demonstrate superior thermal stability with only 3-7% power variation across similar temperature ranges, offering significant advantages in thermally challenging environments.

Scaling characteristics also impact long-term power efficiency trajectories. As DDR5 approaches physical scaling limits, power efficiency improvements are becoming incrementally smaller. Spintronic technologies, still in earlier development stages, show promising theoretical pathways for continued efficiency improvements through materials innovation and architectural refinements, potentially achieving another 40-60% power reduction in next-generation implementations.

For data center applications, where memory subsystems can account for 25-40% of server power consumption, these efficiency differences translate to substantial operational cost implications and environmental impact considerations when deployed at scale.

Integration Challenges and System Architecture Considerations

The integration of Spintronic Devices into existing computing architectures presents significant challenges that must be addressed to fully leverage their potential advantages over DDR5 memory. At the hardware level, interface compatibility remains a primary concern. While DDR5 operates on established protocols with standardized physical connections, Spintronic Devices often require specialized interfaces that are not directly compatible with conventional memory controllers. This necessitates the development of bridge components or entirely new controller architectures to facilitate seamless communication between processors and Spintronic memory elements.

Power distribution networks represent another critical integration challenge. DDR5 memory has well-defined power requirements and delivery mechanisms, whereas Spintronic Devices may exhibit different voltage tolerances and current profiles. System designers must carefully engineer power delivery systems that can accommodate these differences without compromising overall system stability or energy efficiency goals.

From an architectural perspective, memory hierarchies require substantial reconsideration when incorporating Spintronic Devices. The traditional cache-DRAM-storage pyramid may need restructuring to optimize for the unique latency and bandwidth characteristics of spintronic technologies. This could involve introducing new cache levels or hybrid memory arrangements that strategically position Spintronic elements to complement rather than simply replace DDR5 components.

Thermal management considerations also differ significantly between these technologies. DDR5 modules generate predictable heat patterns that existing cooling solutions are designed to address. In contrast, Spintronic Devices may exhibit different thermal profiles, potentially requiring redesigned heat dissipation mechanisms to maintain optimal operating temperatures and prevent performance degradation.

Signal integrity presents additional complexity, as the electrical characteristics of Spintronic interconnects differ from those of conventional DDR5 pathways. Designers must account for potential impedance mismatches, signal reflections, and crosstalk issues that could compromise data transfer reliability. Advanced signal conditioning techniques and careful trace routing become essential to maintain signal integrity across these heterogeneous interfaces.

Software stack adaptations represent perhaps the most extensive integration challenge. Operating systems, memory management units, and application software all assume certain memory timing and behavior characteristics based on traditional DRAM technologies. Comprehensive modifications to these software components are necessary to properly address the unique access patterns, latency profiles, and error characteristics of Spintronic Devices.

Power distribution networks represent another critical integration challenge. DDR5 memory has well-defined power requirements and delivery mechanisms, whereas Spintronic Devices may exhibit different voltage tolerances and current profiles. System designers must carefully engineer power delivery systems that can accommodate these differences without compromising overall system stability or energy efficiency goals.

From an architectural perspective, memory hierarchies require substantial reconsideration when incorporating Spintronic Devices. The traditional cache-DRAM-storage pyramid may need restructuring to optimize for the unique latency and bandwidth characteristics of spintronic technologies. This could involve introducing new cache levels or hybrid memory arrangements that strategically position Spintronic elements to complement rather than simply replace DDR5 components.

Thermal management considerations also differ significantly between these technologies. DDR5 modules generate predictable heat patterns that existing cooling solutions are designed to address. In contrast, Spintronic Devices may exhibit different thermal profiles, potentially requiring redesigned heat dissipation mechanisms to maintain optimal operating temperatures and prevent performance degradation.

Signal integrity presents additional complexity, as the electrical characteristics of Spintronic interconnects differ from those of conventional DDR5 pathways. Designers must account for potential impedance mismatches, signal reflections, and crosstalk issues that could compromise data transfer reliability. Advanced signal conditioning techniques and careful trace routing become essential to maintain signal integrity across these heterogeneous interfaces.

Software stack adaptations represent perhaps the most extensive integration challenge. Operating systems, memory management units, and application software all assume certain memory timing and behavior characteristics based on traditional DRAM technologies. Comprehensive modifications to these software components are necessary to properly address the unique access patterns, latency profiles, and error characteristics of Spintronic Devices.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!