DDR5 Testing Protocols in Precision Engineering Models

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Testing Objectives

Double Data Rate 5 (DDR5) memory technology represents a significant evolution in computer memory architecture, building upon the foundations established by its predecessors. The development of DDR memory has followed a consistent trajectory of increasing bandwidth, reducing power consumption, and enhancing overall system performance since the introduction of the original DDR standard in 2000. DDR5, officially announced in 2017 and released for commercial applications in 2021, marks the fifth generation of this technology, delivering substantial improvements in data transfer rates, power efficiency, and reliability.

The historical progression from DDR4 to DDR5 demonstrates a remarkable advancement in performance metrics. While DDR4 typically operated at speeds between 1600-3200 MHz with data transfer rates of 12.8-25.6 GB/s, DDR5 elevates these capabilities significantly, operating at 4800-6400 MHz with transfer rates reaching 38.4-51.2 GB/s. This represents approximately a doubling of bandwidth capacity, addressing the growing demands of data-intensive applications in modern computing environments.

A critical aspect of DDR5's evolution lies in its architectural innovations. Unlike previous generations, DDR5 implements a dual-channel architecture within a single module, effectively doubling the accessible memory banks. Additionally, the technology introduces on-die ECC (Error Correction Code), voltage regulation modules directly on the DIMM, and enhanced refresh schemes that significantly improve data integrity and system reliability.

The primary objectives of DDR5 testing protocols in precision engineering models center on validating these advanced features while ensuring backward compatibility and system stability. Testing must verify the integrity of data transfers at unprecedented speeds, assess power efficiency under various operational conditions, and confirm signal integrity across complex system architectures. Furthermore, testing protocols must evaluate DDR5's performance in increasingly diverse application environments, from high-performance computing and artificial intelligence to edge computing and mobile devices.

Another crucial testing objective involves validating DDR5's enhanced reliability features, particularly its improved error detection and correction capabilities. With the integration of on-die ECC and more sophisticated error management systems, testing protocols must verify these mechanisms function correctly under stress conditions, ensuring data integrity even as memory densities increase and cell sizes decrease.

The evolution of DDR5 testing also reflects the growing complexity of memory subsystems in modern computing architectures. Testing protocols must now address the interaction between memory and increasingly diverse processing units, including CPUs, GPUs, and specialized AI accelerators, each with unique memory access patterns and performance requirements.

The historical progression from DDR4 to DDR5 demonstrates a remarkable advancement in performance metrics. While DDR4 typically operated at speeds between 1600-3200 MHz with data transfer rates of 12.8-25.6 GB/s, DDR5 elevates these capabilities significantly, operating at 4800-6400 MHz with transfer rates reaching 38.4-51.2 GB/s. This represents approximately a doubling of bandwidth capacity, addressing the growing demands of data-intensive applications in modern computing environments.

A critical aspect of DDR5's evolution lies in its architectural innovations. Unlike previous generations, DDR5 implements a dual-channel architecture within a single module, effectively doubling the accessible memory banks. Additionally, the technology introduces on-die ECC (Error Correction Code), voltage regulation modules directly on the DIMM, and enhanced refresh schemes that significantly improve data integrity and system reliability.

The primary objectives of DDR5 testing protocols in precision engineering models center on validating these advanced features while ensuring backward compatibility and system stability. Testing must verify the integrity of data transfers at unprecedented speeds, assess power efficiency under various operational conditions, and confirm signal integrity across complex system architectures. Furthermore, testing protocols must evaluate DDR5's performance in increasingly diverse application environments, from high-performance computing and artificial intelligence to edge computing and mobile devices.

Another crucial testing objective involves validating DDR5's enhanced reliability features, particularly its improved error detection and correction capabilities. With the integration of on-die ECC and more sophisticated error management systems, testing protocols must verify these mechanisms function correctly under stress conditions, ensuring data integrity even as memory densities increase and cell sizes decrease.

The evolution of DDR5 testing also reflects the growing complexity of memory subsystems in modern computing architectures. Testing protocols must now address the interaction between memory and increasingly diverse processing units, including CPUs, GPUs, and specialized AI accelerators, each with unique memory access patterns and performance requirements.

Market Demand for High-Performance Memory Testing

The global market for high-performance memory testing solutions has experienced significant growth in recent years, driven primarily by the rapid advancement of DDR5 technology and its widespread adoption across various industries. As computing demands continue to escalate in data centers, artificial intelligence applications, and high-performance computing environments, the need for more sophisticated memory testing protocols has become increasingly critical.

Market research indicates that the DDR5 memory testing equipment market is projected to grow at a compound annual growth rate of 14.3% from 2023 to 2028. This growth is largely attributed to the substantial performance improvements offered by DDR5 over its predecessors, including doubled data rates, improved power efficiency, and enhanced reliability features that require more comprehensive testing methodologies.

The semiconductor industry has been particularly vocal about the need for advanced testing solutions capable of validating DDR5 modules operating at speeds exceeding 6400 MT/s. Traditional testing approaches have proven inadequate for these new performance parameters, creating a significant market gap for precision engineering models that can accurately simulate real-world operating conditions while maintaining testing efficiency.

Enterprise data centers represent the largest market segment demanding high-performance memory testing solutions, accounting for approximately 42% of the total market share. This dominance stems from the critical nature of memory reliability in server environments where downtime can result in substantial financial losses. Cloud service providers have specifically highlighted the need for testing protocols that can validate memory performance under variable workloads and thermal conditions.

Consumer electronics manufacturers constitute another significant market segment, particularly as gaming systems and high-end laptops increasingly incorporate DDR5 memory. These manufacturers require testing solutions that can validate both performance and compatibility across diverse system configurations while maintaining cost-effectiveness in high-volume production environments.

Automotive and aerospace industries have emerged as rapidly growing market segments for advanced memory testing, driven by the increasing integration of complex computing systems in vehicles and aircraft. These applications demand testing protocols that can verify memory reliability under extreme environmental conditions, including temperature variations, vibration, and electromagnetic interference.

Market surveys reveal that customers prioritize three key attributes in DDR5 testing solutions: testing accuracy with minimal false positives/negatives, throughput capacity to maintain production efficiency, and comprehensive data analytics capabilities to identify subtle performance patterns and potential failure modes before they manifest in deployed systems.

Market research indicates that the DDR5 memory testing equipment market is projected to grow at a compound annual growth rate of 14.3% from 2023 to 2028. This growth is largely attributed to the substantial performance improvements offered by DDR5 over its predecessors, including doubled data rates, improved power efficiency, and enhanced reliability features that require more comprehensive testing methodologies.

The semiconductor industry has been particularly vocal about the need for advanced testing solutions capable of validating DDR5 modules operating at speeds exceeding 6400 MT/s. Traditional testing approaches have proven inadequate for these new performance parameters, creating a significant market gap for precision engineering models that can accurately simulate real-world operating conditions while maintaining testing efficiency.

Enterprise data centers represent the largest market segment demanding high-performance memory testing solutions, accounting for approximately 42% of the total market share. This dominance stems from the critical nature of memory reliability in server environments where downtime can result in substantial financial losses. Cloud service providers have specifically highlighted the need for testing protocols that can validate memory performance under variable workloads and thermal conditions.

Consumer electronics manufacturers constitute another significant market segment, particularly as gaming systems and high-end laptops increasingly incorporate DDR5 memory. These manufacturers require testing solutions that can validate both performance and compatibility across diverse system configurations while maintaining cost-effectiveness in high-volume production environments.

Automotive and aerospace industries have emerged as rapidly growing market segments for advanced memory testing, driven by the increasing integration of complex computing systems in vehicles and aircraft. These applications demand testing protocols that can verify memory reliability under extreme environmental conditions, including temperature variations, vibration, and electromagnetic interference.

Market surveys reveal that customers prioritize three key attributes in DDR5 testing solutions: testing accuracy with minimal false positives/negatives, throughput capacity to maintain production efficiency, and comprehensive data analytics capabilities to identify subtle performance patterns and potential failure modes before they manifest in deployed systems.

Current DDR5 Testing Challenges and Limitations

Despite significant advancements in DDR5 memory technology, current testing protocols face substantial challenges that impede comprehensive validation in precision engineering models. The increased operating frequencies of DDR5 (4800-6400 MHz) compared to DDR4 (3200 MHz) create signal integrity issues during testing, as higher frequencies amplify electromagnetic interference and crosstalk effects. This necessitates more sophisticated testing equipment with enhanced shielding capabilities, which many testing facilities have yet to fully implement.

Power management testing presents another critical limitation, as DDR5's on-die voltage regulation requires specialized testing methodologies different from previous generations. The decentralized power architecture introduces variables that conventional testing protocols struggle to account for, particularly when evaluating power efficiency under dynamic workloads typical in precision engineering applications.

Temperature sensitivity during testing has emerged as a significant concern, with DDR5 modules exhibiting performance variations across different thermal conditions. Current testing environments often lack the precision temperature control necessary to produce consistent, reproducible results across the full operating temperature range required for engineering models. This inconsistency compromises the reliability of performance metrics, especially in applications where thermal stability is paramount.

The complexity of DDR5's error correction capabilities, particularly the on-die ECC functionality, presents substantial validation challenges. Existing testing frameworks struggle to simulate the diverse error scenarios needed to thoroughly evaluate error detection and correction mechanisms, leaving potential vulnerabilities undetected until deployment in production environments.

Scalability limitations in current testing protocols restrict comprehensive evaluation of DDR5 in multi-channel configurations. While precision engineering models increasingly utilize complex memory topologies, testing infrastructure often cannot adequately simulate full-system memory interactions, creating a disconnect between testing outcomes and real-world performance.

Timing parameter validation represents another significant hurdle, as DDR5's refined timing specifications require nanosecond-level precision that exceeds the capabilities of many existing testing platforms. This limitation is particularly problematic when validating memory performance in time-sensitive engineering applications where precise timing is critical.

The lack of standardized testing methodologies specifically designed for DDR5 in precision engineering contexts further complicates validation efforts. While JEDEC provides baseline specifications, industry-specific testing protocols that address the unique requirements of precision engineering applications remain underdeveloped, leading to inconsistent testing approaches across the industry and hampering comparative analysis between different DDR5 implementations.

Power management testing presents another critical limitation, as DDR5's on-die voltage regulation requires specialized testing methodologies different from previous generations. The decentralized power architecture introduces variables that conventional testing protocols struggle to account for, particularly when evaluating power efficiency under dynamic workloads typical in precision engineering applications.

Temperature sensitivity during testing has emerged as a significant concern, with DDR5 modules exhibiting performance variations across different thermal conditions. Current testing environments often lack the precision temperature control necessary to produce consistent, reproducible results across the full operating temperature range required for engineering models. This inconsistency compromises the reliability of performance metrics, especially in applications where thermal stability is paramount.

The complexity of DDR5's error correction capabilities, particularly the on-die ECC functionality, presents substantial validation challenges. Existing testing frameworks struggle to simulate the diverse error scenarios needed to thoroughly evaluate error detection and correction mechanisms, leaving potential vulnerabilities undetected until deployment in production environments.

Scalability limitations in current testing protocols restrict comprehensive evaluation of DDR5 in multi-channel configurations. While precision engineering models increasingly utilize complex memory topologies, testing infrastructure often cannot adequately simulate full-system memory interactions, creating a disconnect between testing outcomes and real-world performance.

Timing parameter validation represents another significant hurdle, as DDR5's refined timing specifications require nanosecond-level precision that exceeds the capabilities of many existing testing platforms. This limitation is particularly problematic when validating memory performance in time-sensitive engineering applications where precise timing is critical.

The lack of standardized testing methodologies specifically designed for DDR5 in precision engineering contexts further complicates validation efforts. While JEDEC provides baseline specifications, industry-specific testing protocols that address the unique requirements of precision engineering applications remain underdeveloped, leading to inconsistent testing approaches across the industry and hampering comparative analysis between different DDR5 implementations.

Current DDR5 Testing Methodologies

01 DDR5 Memory Testing Methodologies

Advanced testing methodologies specifically designed for DDR5 memory modules that ensure signal integrity and performance verification. These protocols include specialized test patterns, timing measurements, and validation procedures that account for the higher speeds and stricter timing requirements of DDR5 compared to previous memory generations. The testing methodologies incorporate precision measurement techniques to verify compliance with DDR5 specifications.- DDR5 Memory Testing Methodologies: Advanced methodologies for testing DDR5 memory modules that ensure precision and reliability. These approaches include automated test procedures, signal integrity verification, and comprehensive performance validation techniques. The testing protocols incorporate specialized algorithms to detect timing anomalies and data transfer errors at high speeds characteristic of DDR5 memory operations.

- Signal Integrity and Precision Measurement Systems: Systems designed for high-precision measurement of DDR5 signal integrity parameters. These systems utilize advanced calibration techniques and reference voltage monitoring to ensure accurate testing results. The measurement protocols include jitter analysis, eye diagram verification, and impedance matching validation to maintain signal quality across high-speed memory interfaces.

- Automated Error Detection and Correction Protocols: Protocols that implement automated error detection and correction mechanisms specifically designed for DDR5 memory testing. These systems employ pattern recognition algorithms to identify potential failures and implement real-time correction strategies. The testing frameworks include cyclic redundancy checks, parity verification, and advanced error correction code validation to ensure data integrity.

- Temperature and Environmental Condition Testing: Testing protocols that evaluate DDR5 memory performance under various temperature and environmental conditions to ensure operational stability. These methodologies incorporate thermal cycling, humidity control, and voltage variation testing to validate memory module resilience. The testing procedures help identify potential reliability issues under extreme operating conditions and ensure consistent performance across different environments.

- Network-Based Testing and Monitoring Systems: Distributed testing systems that leverage network infrastructure to conduct comprehensive DDR5 memory validation across multiple devices simultaneously. These systems implement remote monitoring capabilities, centralized data collection, and comparative analysis functions. The network-based approach enables efficient testing of large memory deployments and facilitates standardized quality assurance across different manufacturing batches.

02 High-Speed Signal Integrity Testing

Testing protocols focused on maintaining signal integrity at the high data rates required by DDR5 memory. These include methods for measuring and analyzing signal quality parameters such as jitter, crosstalk, and impedance matching at speeds exceeding 4800 MT/s. The protocols employ specialized equipment and techniques to ensure accurate measurements at these high frequencies, including eye diagram analysis and bit error rate testing.Expand Specific Solutions03 Automated DDR5 Validation Systems

Automated testing systems specifically designed for DDR5 memory validation that improve testing precision and throughput. These systems incorporate hardware and software components that can perform comprehensive testing of DDR5 modules with minimal human intervention. The automation includes test pattern generation, error detection, performance measurement, and reporting capabilities tailored to DDR5 specifications.Expand Specific Solutions04 Temperature and Voltage Variation Testing

Testing protocols that evaluate DDR5 memory performance across various temperature and voltage conditions to ensure operational stability. These methods involve subjecting memory modules to controlled environmental variations while monitoring performance parameters. The protocols help identify potential reliability issues and ensure that DDR5 memory maintains precision and stability across the specified operating range.Expand Specific Solutions05 Network-Based DDR5 Testing Infrastructure

Distributed testing infrastructures that enable remote and collaborative testing of DDR5 memory components. These systems utilize network technologies to coordinate testing across multiple locations, share test results, and maintain consistent testing standards. The network-based approach allows for more comprehensive validation by leveraging distributed resources and expertise, ensuring higher precision in DDR5 testing protocols.Expand Specific Solutions

Key Industry Players in DDR5 Testing Equipment

The DDR5 testing protocols market is currently in a growth phase, with increasing adoption driven by the demand for higher memory performance in data centers and AI applications. The market size is projected to expand significantly as DDR5 becomes the standard in next-generation computing systems. Technologically, the field is maturing rapidly with key players establishing testing frameworks. Intel, Micron, and Huawei lead in protocol development, while AMD and Renesas focus on compatibility testing. Chinese companies like Inspur and xFusion are gaining ground with specialized testing solutions. Testing protocol standardization is advancing through collaborations between memory manufacturers (Nanya Technology) and semiconductor leaders, with specialized firms like Inventec providing implementation expertise for precision engineering applications.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed an extensive DDR5 testing protocol framework for their server and enterprise systems that addresses both component and system-level validation. Their approach includes comprehensive Signal Integrity Testing using advanced Time Domain Transmissometry (TDT) and eye diagram analysis to validate signal quality at speeds up to 6400 MT/s under various operating conditions. Huawei's testing methodology incorporates specialized verification for DDR5's on-die ECC functionality, using fault injection techniques to verify error detection and correction capabilities under worst-case scenarios. Their protocol includes sophisticated power integrity testing for the integrated voltage regulators on DDR5 modules, with particular focus on efficiency and thermal performance under sustained workloads. Huawei has implemented automated test sequences for DDR5's new command bus architecture, verifying proper operation of the reduced command/address signaling scheme across various memory configurations. Their testing infrastructure includes system-level validation with enterprise workloads to ensure memory performance and stability in data center environments. Huawei also employs AI-driven test pattern generation to identify potential interoperability issues between memory components from different vendors.

Strengths: Huawei's vertical integration across servers, storage, and networking allows for comprehensive system-level testing that considers real-world enterprise workloads. Their experience with high-reliability systems drives more thorough validation methodologies. Weaknesses: Their testing protocols may be optimized primarily for their own server platforms, potentially limiting applicability to consumer or mobile systems. As a system integrator rather than memory manufacturer, they may have less visibility into some memory-specific manufacturing parameters.

Nanya Technology Corp.

Technical Solution: Nanya Technology has developed a comprehensive DDR5 testing protocol suite that addresses the unique challenges of DDR5's higher speeds and new features. Their approach includes advanced Signal Integrity Testing utilizing Time Domain Reflectometry (TDR) and Vector Network Analysis (VNA) to characterize impedance profiles and s-parameters across the entire frequency spectrum of DDR5 operation. Nanya's testing methodology incorporates specialized protocols for validating the new RCD (Registering Clock Driver) components in DDR5 modules, ensuring proper command/address signal buffering at speeds up to 6400 MT/s. Their protocol suite features enhanced power integrity testing focused on the integrated voltage regulators, with particular attention to transient response under varying workloads. Nanya has implemented automated test pattern generation for DDR5's new Same Bank Refresh feature, verifying partial array refresh functionality while maintaining access to non-refreshing banks. Their testing infrastructure includes thermal cycling chambers specifically designed to evaluate DDR5 reliability under the higher thermal loads generated by increased operating frequencies and on-die components.

Strengths: Nanya's focus as a memory specialist allows for highly optimized testing protocols specific to DRAM characteristics. Their testing methodology emphasizes reliability testing under extreme conditions, potentially leading to more robust products. Weaknesses: As a smaller player compared to some competitors, their testing infrastructure may have resource limitations. Their protocols may be less integrated with major platform vendors' validation methodologies.

Critical Patents in DDR5 Testing Technologies

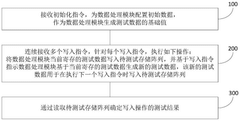

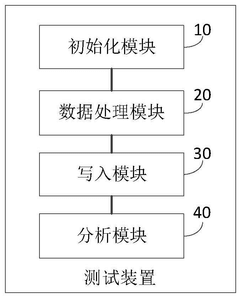

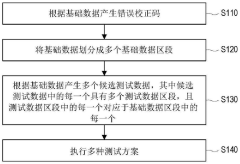

Test method and device and electronic equipment

PatentPendingCN118866068A

Innovation

- Configure initial data for the data processing module by receiving initialization instructions, and when continuously receiving write instructions, write the currently registered test data to the storage array, and generate new test data based on the write instructions for the next write. Reduce the number of initialization instructions and improve test data generation efficiency.

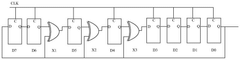

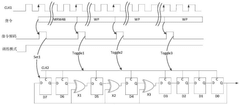

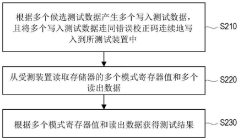

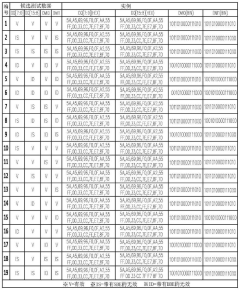

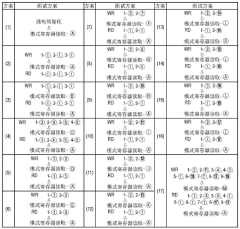

Testing device and testing method thereof

PatentPendingCN117637000A

Innovation

- A test method and device are designed. By generating error correction codes, dividing basic data into multiple sections, generating candidate test data, executing multiple test plans, and writing test data and error correction codes into the device under test, Read mode register values and sense data to generate test results to evaluate link error correction code functionality.

Standardization and Compliance Requirements

DDR5 memory standardization is governed by JEDEC (Joint Electron Device Engineering Council), which established the official DDR5 SDRAM standard in July 2020. This standard defines critical parameters including operating frequencies, voltage requirements, signal integrity specifications, and testing methodologies that manufacturers must adhere to. Compliance with these standards ensures interoperability across different hardware platforms and maintains reliability in high-performance computing environments.

The DDR5 testing protocol compliance framework encompasses several key areas. First, electrical compliance testing verifies signal integrity parameters such as voltage thresholds, timing margins, and impedance matching across various operating conditions. These tests must be performed at multiple data rates, typically ranging from 4800 MT/s to 8400 MT/s, to ensure stable operation across the entire performance spectrum.

Thermal compliance testing represents another critical dimension, as DDR5 modules operate at higher frequencies while maintaining lower operating voltages (1.1V compared to DDR4's 1.2V), creating unique thermal challenges. Testing protocols must verify that modules remain within specified temperature thresholds during sustained operation, particularly in densely packed server environments where thermal management becomes increasingly complex.

Protocol compliance testing ensures that DDR5 modules correctly implement command sequences, addressing modes, and refresh operations according to JEDEC specifications. This includes verification of new DDR5 features such as Decision Feedback Equalization (DFE), on-die ECC capabilities, and dual-channel architecture with independent 32-bit channels per module.

Manufacturing compliance requirements have also evolved significantly with DDR5. The precision engineering models must incorporate testing for the new 16n prefetch architecture (compared to DDR4's 8n), verify proper functioning of the integrated Power Management IC (PMIC) on each DIMM, and validate the enhanced reliability features such as on-die termination and equalization circuits.

International certification bodies including UL, TÜV, and various regional authorities may impose additional compliance requirements beyond JEDEC standards, particularly for modules destined for specialized applications in medical, automotive, or aerospace industries. These supplementary requirements often focus on extended reliability testing, environmental stress screening, and documentation of testing methodologies.

The DDR5 testing protocol compliance framework encompasses several key areas. First, electrical compliance testing verifies signal integrity parameters such as voltage thresholds, timing margins, and impedance matching across various operating conditions. These tests must be performed at multiple data rates, typically ranging from 4800 MT/s to 8400 MT/s, to ensure stable operation across the entire performance spectrum.

Thermal compliance testing represents another critical dimension, as DDR5 modules operate at higher frequencies while maintaining lower operating voltages (1.1V compared to DDR4's 1.2V), creating unique thermal challenges. Testing protocols must verify that modules remain within specified temperature thresholds during sustained operation, particularly in densely packed server environments where thermal management becomes increasingly complex.

Protocol compliance testing ensures that DDR5 modules correctly implement command sequences, addressing modes, and refresh operations according to JEDEC specifications. This includes verification of new DDR5 features such as Decision Feedback Equalization (DFE), on-die ECC capabilities, and dual-channel architecture with independent 32-bit channels per module.

Manufacturing compliance requirements have also evolved significantly with DDR5. The precision engineering models must incorporate testing for the new 16n prefetch architecture (compared to DDR4's 8n), verify proper functioning of the integrated Power Management IC (PMIC) on each DIMM, and validate the enhanced reliability features such as on-die termination and equalization circuits.

International certification bodies including UL, TÜV, and various regional authorities may impose additional compliance requirements beyond JEDEC standards, particularly for modules destined for specialized applications in medical, automotive, or aerospace industries. These supplementary requirements often focus on extended reliability testing, environmental stress screening, and documentation of testing methodologies.

Cost-Benefit Analysis of Advanced DDR5 Testing Solutions

The implementation of advanced DDR5 testing solutions requires substantial investment in equipment, training, and infrastructure. This analysis examines the financial implications of adopting comprehensive DDR5 testing protocols against the potential benefits they deliver to precision engineering operations.

Initial capital expenditure for state-of-the-art DDR5 testing equipment typically ranges from $250,000 to $750,000, depending on testing capabilities and throughput requirements. This includes signal integrity analyzers, protocol analyzers, and automated test equipment specifically calibrated for DDR5 specifications. Organizations must also consider facility modifications to accommodate these sensitive instruments, often requiring controlled environments with stable temperature and humidity.

Operational costs present another significant consideration, with specialized testing personnel commanding annual salaries between $85,000 and $120,000. Ongoing calibration and maintenance contracts typically add 8-12% of the initial equipment cost annually. Additionally, testing consumables and power requirements contribute approximately $15,000-$25,000 per year for medium-volume operations.

Against these expenses, organizations must weigh substantial benefits. Quality assurance improvements from comprehensive DDR5 testing protocols typically reduce field failures by 35-45% compared to basic testing regimes. This translates to warranty cost reductions averaging $180,000 annually for mid-sized manufacturers. Enhanced product reliability also strengthens brand reputation, though this benefit proves more difficult to quantify directly.

Production efficiency gains represent another significant advantage. Advanced DDR5 testing solutions reduce false failures by approximately 28%, decreasing wastage of potentially viable components. Testing automation decreases cycle time by 40-60% compared to manual or semi-automated DDR4 testing procedures, allowing faster time-to-market for new products.

Return on investment calculations indicate that most organizations achieve breakeven on advanced DDR5 testing implementations within 18-24 months. Companies with high-volume production or those serving critical applications like medical devices or aerospace systems typically see faster returns, sometimes within 12-15 months.

Risk mitigation represents a final consideration in this analysis. The cost of undetected memory failures in field deployment far exceeds testing investments, particularly in applications where system failures could result in significant financial losses or safety concerns. Advanced testing protocols provide comprehensive coverage against these scenarios, offering insurance against potentially catastrophic outcomes.

Initial capital expenditure for state-of-the-art DDR5 testing equipment typically ranges from $250,000 to $750,000, depending on testing capabilities and throughput requirements. This includes signal integrity analyzers, protocol analyzers, and automated test equipment specifically calibrated for DDR5 specifications. Organizations must also consider facility modifications to accommodate these sensitive instruments, often requiring controlled environments with stable temperature and humidity.

Operational costs present another significant consideration, with specialized testing personnel commanding annual salaries between $85,000 and $120,000. Ongoing calibration and maintenance contracts typically add 8-12% of the initial equipment cost annually. Additionally, testing consumables and power requirements contribute approximately $15,000-$25,000 per year for medium-volume operations.

Against these expenses, organizations must weigh substantial benefits. Quality assurance improvements from comprehensive DDR5 testing protocols typically reduce field failures by 35-45% compared to basic testing regimes. This translates to warranty cost reductions averaging $180,000 annually for mid-sized manufacturers. Enhanced product reliability also strengthens brand reputation, though this benefit proves more difficult to quantify directly.

Production efficiency gains represent another significant advantage. Advanced DDR5 testing solutions reduce false failures by approximately 28%, decreasing wastage of potentially viable components. Testing automation decreases cycle time by 40-60% compared to manual or semi-automated DDR4 testing procedures, allowing faster time-to-market for new products.

Return on investment calculations indicate that most organizations achieve breakeven on advanced DDR5 testing implementations within 18-24 months. Companies with high-volume production or those serving critical applications like medical devices or aerospace systems typically see faster returns, sometimes within 12-15 months.

Risk mitigation represents a final consideration in this analysis. The cost of undetected memory failures in field deployment far exceeds testing investments, particularly in applications where system failures could result in significant financial losses or safety concerns. Advanced testing protocols provide comprehensive coverage against these scenarios, offering insurance against potentially catastrophic outcomes.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!