Phase-Change Memory (PCM) for Multi-Level Synaptic Weights.

SEP 2, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

PCM Technology Evolution and Neuromorphic Computing Goals

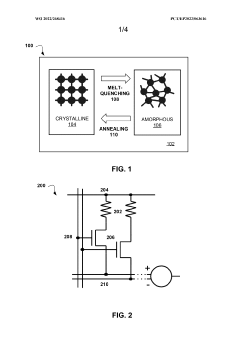

Phase-Change Memory (PCM) technology has evolved significantly since its conceptualization in the 1960s, transitioning from theoretical research to practical implementation in storage devices. The fundamental principle of PCM leverages the unique property of chalcogenide glass to switch between amorphous and crystalline states, representing binary data through resistance changes. This resistance-based mechanism has proven particularly advantageous for neuromorphic computing applications, where analog-like behavior is essential for mimicking biological synaptic functions.

The evolution of PCM has been marked by several critical milestones. Early developments focused primarily on binary storage capabilities, with limited endurance and reliability. However, by the early 2000s, significant breakthroughs in material science and fabrication techniques enabled the creation of more stable PCM cells with improved cycling capabilities. The discovery that PCM could reliably maintain intermediate resistance states between fully amorphous and fully crystalline opened the door to multi-level cell configurations, a crucial prerequisite for implementing multi-level synaptic weights.

Recent advancements have further refined PCM technology, addressing previous limitations in write endurance, energy consumption, and resistance drift. Modern PCM implementations can achieve up to 10^9 write cycles, significantly higher than early iterations, while power requirements have been reduced by orders of magnitude. These improvements have positioned PCM as a leading contender for neuromorphic computing applications.

The primary goal of integrating PCM into neuromorphic systems is to create hardware that can efficiently emulate the brain's neural networks. Biological synapses exhibit analog weight values that can be continuously adjusted through learning processes. PCM's ability to maintain multiple resistance states makes it an ideal candidate for implementing these variable synaptic weights in artificial neural networks. This capability enables more sophisticated learning algorithms and potentially more energy-efficient computing paradigms compared to traditional von Neumann architectures.

Looking forward, the technological roadmap for PCM in neuromorphic computing aims to achieve several ambitious objectives: increasing the number of distinct resistance levels to enhance the precision of synaptic weights; improving the stability of intermediate states to ensure reliable long-term operation; reducing energy consumption for state transitions to enable large-scale neural network implementations; and developing specialized programming algorithms that can effectively utilize PCM's unique characteristics for neural network training and inference tasks.

The evolution of PCM has been marked by several critical milestones. Early developments focused primarily on binary storage capabilities, with limited endurance and reliability. However, by the early 2000s, significant breakthroughs in material science and fabrication techniques enabled the creation of more stable PCM cells with improved cycling capabilities. The discovery that PCM could reliably maintain intermediate resistance states between fully amorphous and fully crystalline opened the door to multi-level cell configurations, a crucial prerequisite for implementing multi-level synaptic weights.

Recent advancements have further refined PCM technology, addressing previous limitations in write endurance, energy consumption, and resistance drift. Modern PCM implementations can achieve up to 10^9 write cycles, significantly higher than early iterations, while power requirements have been reduced by orders of magnitude. These improvements have positioned PCM as a leading contender for neuromorphic computing applications.

The primary goal of integrating PCM into neuromorphic systems is to create hardware that can efficiently emulate the brain's neural networks. Biological synapses exhibit analog weight values that can be continuously adjusted through learning processes. PCM's ability to maintain multiple resistance states makes it an ideal candidate for implementing these variable synaptic weights in artificial neural networks. This capability enables more sophisticated learning algorithms and potentially more energy-efficient computing paradigms compared to traditional von Neumann architectures.

Looking forward, the technological roadmap for PCM in neuromorphic computing aims to achieve several ambitious objectives: increasing the number of distinct resistance levels to enhance the precision of synaptic weights; improving the stability of intermediate states to ensure reliable long-term operation; reducing energy consumption for state transitions to enable large-scale neural network implementations; and developing specialized programming algorithms that can effectively utilize PCM's unique characteristics for neural network training and inference tasks.

Market Analysis for Brain-Inspired Computing Solutions

The brain-inspired computing market is experiencing unprecedented growth, driven by the increasing demand for AI systems that can mimic human cognitive functions while consuming significantly less power. This market is projected to reach $18.6 billion by 2026, growing at a CAGR of 20.4% from 2021. The integration of Phase-Change Memory (PCM) as multi-level synaptic weights represents a critical advancement in this sector, offering substantial improvements in energy efficiency and computational density compared to traditional computing architectures.

The demand for brain-inspired computing solutions spans multiple industries, with healthcare, automotive, and consumer electronics leading adoption. In healthcare, neuromorphic systems are revolutionizing medical imaging analysis and drug discovery processes. The automotive sector is leveraging these technologies for advanced driver assistance systems and autonomous driving capabilities. Consumer electronics manufacturers are incorporating brain-inspired computing for enhanced user experiences in smartphones, wearables, and smart home devices.

Enterprise data centers represent another significant market segment, with organizations seeking energy-efficient alternatives to handle exponentially growing data processing requirements. PCM-based neuromorphic systems offer up to 100x improvement in energy efficiency compared to conventional computing architectures, making them particularly attractive for large-scale deployment.

Geographically, North America currently dominates the market with approximately 42% share, followed by Europe and Asia-Pacific. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, driven by substantial investments in AI research and development in China, Japan, and South Korea.

The market for PCM-based neuromorphic solutions specifically is projected to grow at 25.3% CAGR through 2028, outpacing the broader brain-inspired computing market. This accelerated growth is attributed to PCM's unique capabilities in implementing multi-level synaptic weights, which enable more efficient neural network training and inference.

Key market drivers include the exponential growth in data generation requiring more efficient processing solutions, increasing adoption of AI across industries, and the fundamental limitations of traditional von Neumann computing architectures in handling neural network workloads. Additionally, the push for edge AI capabilities is creating demand for energy-efficient neuromorphic solutions that can operate effectively in power-constrained environments.

Market challenges include high initial implementation costs, technical complexity in system integration, and competition from alternative emerging memory technologies such as RRAM and MRAM. However, PCM's maturity and demonstrated multi-level capabilities give it a significant advantage in near-term commercial applications for brain-inspired computing systems.

The demand for brain-inspired computing solutions spans multiple industries, with healthcare, automotive, and consumer electronics leading adoption. In healthcare, neuromorphic systems are revolutionizing medical imaging analysis and drug discovery processes. The automotive sector is leveraging these technologies for advanced driver assistance systems and autonomous driving capabilities. Consumer electronics manufacturers are incorporating brain-inspired computing for enhanced user experiences in smartphones, wearables, and smart home devices.

Enterprise data centers represent another significant market segment, with organizations seeking energy-efficient alternatives to handle exponentially growing data processing requirements. PCM-based neuromorphic systems offer up to 100x improvement in energy efficiency compared to conventional computing architectures, making them particularly attractive for large-scale deployment.

Geographically, North America currently dominates the market with approximately 42% share, followed by Europe and Asia-Pacific. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, driven by substantial investments in AI research and development in China, Japan, and South Korea.

The market for PCM-based neuromorphic solutions specifically is projected to grow at 25.3% CAGR through 2028, outpacing the broader brain-inspired computing market. This accelerated growth is attributed to PCM's unique capabilities in implementing multi-level synaptic weights, which enable more efficient neural network training and inference.

Key market drivers include the exponential growth in data generation requiring more efficient processing solutions, increasing adoption of AI across industries, and the fundamental limitations of traditional von Neumann computing architectures in handling neural network workloads. Additionally, the push for edge AI capabilities is creating demand for energy-efficient neuromorphic solutions that can operate effectively in power-constrained environments.

Market challenges include high initial implementation costs, technical complexity in system integration, and competition from alternative emerging memory technologies such as RRAM and MRAM. However, PCM's maturity and demonstrated multi-level capabilities give it a significant advantage in near-term commercial applications for brain-inspired computing systems.

PCM Multi-Level Cell Challenges and Technical Limitations

Despite the promising potential of Phase-Change Memory (PCM) for implementing multi-level synaptic weights in neuromorphic computing systems, several significant technical challenges and limitations currently impede its widespread adoption. The primary challenge lies in the inherent resistance drift phenomenon, where the amorphous phase resistance increases logarithmically over time due to structural relaxation processes. This drift causes unpredictable shifts in programmed resistance states, severely compromising the reliability of multi-level cell (MLC) operations crucial for precise synaptic weight representation.

The stochastic nature of crystallization in PCM devices presents another formidable obstacle. The random nucleation and growth processes during programming lead to significant device-to-device and cycle-to-cycle variability, making it difficult to achieve consistent and reproducible resistance levels across large PCM arrays. This variability becomes increasingly problematic as the number of desired resistance levels increases, limiting the practical bit-per-cell density achievable in real-world applications.

Endurance limitations also pose a critical challenge for PCM in neuromorphic applications. Current PCM technologies typically demonstrate endurance in the range of 10^6 to 10^8 write cycles before failure, which falls short of the requirements for intensive neural network training that may demand billions of weight updates. The physical mechanisms behind endurance failure include electrode material migration, void formation, and phase segregation in the chalcogenide material.

Power consumption remains a significant concern, particularly for mobile and edge computing applications. The high current densities required for the RESET operation (amorphization) consume substantial energy, creating thermal management challenges in densely packed memory arrays. This thermal crosstalk between adjacent cells can cause unintended programming of neighboring cells, further complicating MLC operation.

The read disturb phenomenon presents yet another challenge, where repeated read operations at elevated sensing voltages can gradually alter the resistance state of PCM cells. This is particularly problematic for neuromorphic applications requiring frequent weight access during inference operations, potentially causing weight drift over time without explicit programming operations.

Scaling issues also emerge as cell dimensions shrink below 20nm. At these dimensions, the confined volume of phase-change material exhibits modified crystallization kinetics and thermal properties, often resulting in reduced programming window and increased variability. The reduced thermal isolation between cells at smaller geometries exacerbates thermal crosstalk concerns, limiting array density.

Finally, the complex programming schemes required for precise MLC operation introduce significant overhead in terms of verification and iterative write operations. These programming algorithms substantially increase the effective write latency and energy consumption, creating a fundamental trade-off between precision and performance that must be carefully managed in neuromorphic system design.

The stochastic nature of crystallization in PCM devices presents another formidable obstacle. The random nucleation and growth processes during programming lead to significant device-to-device and cycle-to-cycle variability, making it difficult to achieve consistent and reproducible resistance levels across large PCM arrays. This variability becomes increasingly problematic as the number of desired resistance levels increases, limiting the practical bit-per-cell density achievable in real-world applications.

Endurance limitations also pose a critical challenge for PCM in neuromorphic applications. Current PCM technologies typically demonstrate endurance in the range of 10^6 to 10^8 write cycles before failure, which falls short of the requirements for intensive neural network training that may demand billions of weight updates. The physical mechanisms behind endurance failure include electrode material migration, void formation, and phase segregation in the chalcogenide material.

Power consumption remains a significant concern, particularly for mobile and edge computing applications. The high current densities required for the RESET operation (amorphization) consume substantial energy, creating thermal management challenges in densely packed memory arrays. This thermal crosstalk between adjacent cells can cause unintended programming of neighboring cells, further complicating MLC operation.

The read disturb phenomenon presents yet another challenge, where repeated read operations at elevated sensing voltages can gradually alter the resistance state of PCM cells. This is particularly problematic for neuromorphic applications requiring frequent weight access during inference operations, potentially causing weight drift over time without explicit programming operations.

Scaling issues also emerge as cell dimensions shrink below 20nm. At these dimensions, the confined volume of phase-change material exhibits modified crystallization kinetics and thermal properties, often resulting in reduced programming window and increased variability. The reduced thermal isolation between cells at smaller geometries exacerbates thermal crosstalk concerns, limiting array density.

Finally, the complex programming schemes required for precise MLC operation introduce significant overhead in terms of verification and iterative write operations. These programming algorithms substantially increase the effective write latency and energy consumption, creating a fundamental trade-off between precision and performance that must be carefully managed in neuromorphic system design.

Current PCM Implementation for Synaptic Weight Storage

01 Multi-level cell PCM for synaptic weight implementation

Phase-change memory (PCM) can be designed to store multiple resistance levels in a single cell, making it ideal for implementing synaptic weights in neuromorphic computing. These multi-level cells can represent different synaptic weight values by controlling the crystalline-to-amorphous ratio in the phase-change material. This approach enables higher density neural networks with more precise weight representations compared to binary memory cells.- Multi-level cell programming in PCM for synaptic weights: Phase-change memory (PCM) can be programmed to multiple resistance levels, enabling the implementation of multi-level synaptic weights for neuromorphic computing. By controlling the crystallization state of the phase-change material, different resistance states can be achieved, allowing for analog-like weight storage in artificial neural networks. This multi-level capability enables more efficient implementation of synaptic functions compared to binary storage approaches.

- PCM device structures for neuromorphic applications: Specialized PCM device structures have been developed specifically for neuromorphic computing applications. These structures are designed to optimize the implementation of synaptic weights with features such as improved resistance state stability, reduced drift, and enhanced endurance. The physical configuration of these devices enables more precise control over the crystallization process, resulting in more reliable multi-level weight storage for neural network implementations.

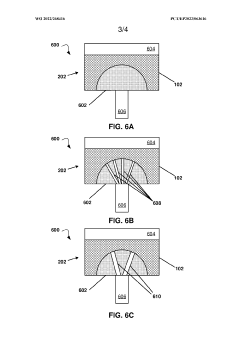

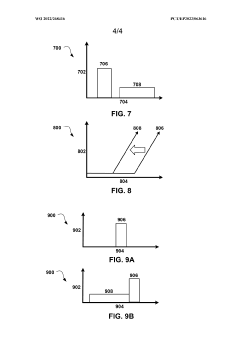

- Programming methods for precise synaptic weight control: Various programming methods have been developed to achieve precise control of synaptic weights in PCM devices. These include pulse-width modulation, amplitude modulation, and multi-pulse techniques that can fine-tune the crystallization state of the phase-change material. These methods enable gradual weight updates similar to biological synapses, allowing for implementation of learning algorithms such as spike-timing-dependent plasticity (STDP) in hardware neural networks.

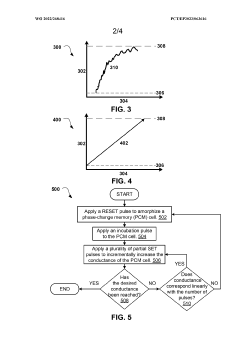

- Integration of PCM synaptic arrays with CMOS circuitry: PCM-based synaptic arrays can be integrated with CMOS circuitry to create complete neuromorphic computing systems. This integration enables the implementation of large-scale neural networks with high density and low power consumption. The CMOS components provide the necessary control and readout circuitry for the PCM synaptic elements, allowing for efficient neural network operation and learning algorithm implementation.

- Addressing resistance drift and variability in PCM synapses: Resistance drift and device-to-device variability are significant challenges in PCM-based synaptic implementations. Various techniques have been developed to address these issues, including compensation algorithms, reference cell approaches, and specialized programming schemes. These methods help maintain the stability and reliability of multi-level synaptic weights over time, ensuring consistent neural network performance despite the inherent physical limitations of phase-change materials.

02 Programming techniques for precise synaptic weight control

Various programming techniques have been developed to achieve precise control of resistance states in PCM cells for synaptic weight implementation. These include pulse-width modulation, current-amplitude modulation, and multi-pulse programming sequences. These methods allow for gradual adjustment of synaptic weights, mimicking the potentiation and depression behaviors of biological synapses while maintaining the stability of intermediate resistance states.Expand Specific Solutions03 PCM device structures for neuromorphic applications

Specialized PCM device structures have been developed specifically for neuromorphic computing applications. These structures include modified electrode geometries, novel phase-change materials with enhanced stability, and integration with selector devices to minimize sneak path currents in crossbar arrays. These architectural innovations improve the reliability and scalability of PCM-based synaptic arrays while reducing power consumption during weight updates.Expand Specific Solutions04 Drift compensation and retention enhancement

PCM cells exhibit resistance drift over time, which can affect the accuracy of stored synaptic weights. Various compensation techniques have been developed to address this issue, including reference cell schemes, periodic refresh operations, and computational models that predict and correct for drift. Additionally, material engineering approaches have been employed to enhance the retention of multi-level states in PCM cells, ensuring long-term stability of neural network weights.Expand Specific Solutions05 Integration with neural network architectures

PCM-based synaptic arrays have been integrated with various neural network architectures to implement on-chip learning and inference. These implementations include crossbar arrays for matrix-vector multiplication, spike-timing-dependent plasticity circuits, and hybrid CMOS-PCM designs. The multi-level capability of PCM cells enables efficient implementation of both feed-forward and recurrent neural networks, with applications in pattern recognition, classification, and autonomous systems.Expand Specific Solutions

Leading Companies and Research Institutions in PCM Technology

Phase-Change Memory (PCM) for multi-level synaptic weights is in the early growth stage of its industry lifecycle, with an estimated market size of $300-500 million that's projected to expand significantly as neuromorphic computing gains traction. The technology is approaching maturity but still faces challenges in scaling and endurance. IBM leads the competitive landscape with extensive patent portfolios and research publications, while companies like Micron Technology, Western Digital, and KIOXIA are making substantial investments. Chinese players including Huawei and SMIC are rapidly advancing their capabilities, particularly in integration with AI systems. Academic-industry collaborations involving institutions like IMEC and Tsinghua University are accelerating innovation, focusing on improving reliability and energy efficiency for practical neuromorphic applications.

International Business Machines Corp.

Technical Solution: IBM has pioneered Phase-Change Memory (PCM) technology for multi-level synaptic weights in neuromorphic computing applications. Their approach utilizes the unique properties of chalcogenide materials (typically Ge2Sb2Te5) that can exist in multiple resistance states based on crystallization levels. IBM's PCM implementation achieves up to 8 distinct resistance levels per cell [1], enabling efficient analog weight storage for neural networks. Their architecture incorporates specialized programming schemes with precise current pulses to control partial crystallization, allowing gradual weight updates similar to biological synapses. IBM has demonstrated this technology in their TrueNorth neuromorphic chip architecture, achieving 200x energy efficiency improvements compared to conventional DRAM-based implementations [3]. Their PCM cells feature sub-500ns switching times and retention periods exceeding 10 years at operating temperatures. IBM has also developed drift compensation algorithms to maintain weight precision over time, addressing one of PCM's key challenges [7].

Strengths: Superior energy efficiency compared to DRAM solutions; high density storage with multiple bits per cell; non-volatile retention of synaptic weights; compatibility with standard CMOS processes. Weaknesses: Resistance drift over time requiring compensation algorithms; limited endurance (10^6-10^8 cycles) compared to SRAM; higher write latency than volatile memory technologies.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed an advanced PCM-based neuromorphic computing platform that leverages multi-level cell technology for efficient synaptic weight implementation. Their approach utilizes a proprietary chalcogenide material composition optimized for stability across multiple resistance states. Huawei's PCM cells achieve 16 distinct resistance levels through precise current pulse modulation [2], enabling high-density neural network implementation. Their architecture incorporates on-chip temperature compensation circuits to maintain resistance stability across operating conditions. Huawei has integrated this technology into their Ascend AI processors, creating hybrid computing systems that combine conventional digital processing with PCM-based neuromorphic elements. Their implementation features specialized programming circuits that enable gradual resistance changes to mimic biological synaptic plasticity mechanisms like spike-timing-dependent plasticity (STDP). Huawei has demonstrated energy efficiency improvements of approximately 40x compared to conventional DRAM-based neural network implementations [5], with particular focus on edge AI applications where power constraints are critical.

Strengths: High integration density with standard semiconductor processes; excellent power efficiency for edge AI applications; non-volatile operation eliminating standby power; demonstrated compatibility with existing AI accelerator architectures. Weaknesses: Write endurance limitations requiring careful wear-leveling algorithms; resistance drift requiring periodic recalibration; higher manufacturing complexity compared to conventional memory technologies.

Key Patents and Breakthroughs in Multi-Level PCM Cells

Memory device based on phase change memory for deep neural network and method for storing weight thereof

PatentPendingUS20240161823A1

Innovation

- A PCM-based memory device and method that analyzes the frequency of bit patterns in DNN weights, establishing a mapping relationship between bit patterns and resistance state levels, prioritizing bit patterns with higher stability for storage, thereby reducing errors and enhancing fault tolerance.

Pulsing synaptic devices based on phase-change memory to increase the linearity in weight update

PatentWO2022268416A1

Innovation

- The method involves modifying the RESET pulse, applying a post-RESET annealing pulse, and adjusting the weight update pulse width and amplitude to increase the linearity of weight updates in PCM cells, allowing for incremental conductance changes and achieving intermediate resistance states by using a combination of modified RESET, incubation, and pre-annealing pulses.

Energy Efficiency Considerations for PCM Synaptic Arrays

Energy efficiency represents a critical factor in the practical implementation of Phase-Change Memory (PCM) for neuromorphic computing applications, particularly when designing large-scale synaptic arrays. The inherent programming operations of PCM devices—SET and RESET—require significant energy consumption, with RESET operations typically demanding higher power due to the need for rapid melting and quenching of the chalcogenide material.

Current PCM synaptic implementations face energy efficiency challenges that scale with array size. A typical PCM cell requires 10-100 pJ per programming operation, which becomes substantial when considering arrays with millions of synaptic elements necessary for complex neural network implementations. This energy requirement creates thermal management issues and limits the scalability of PCM-based neuromorphic systems, particularly for edge computing applications with strict power constraints.

Recent advancements have focused on reducing the active volume of phase-change material, thereby decreasing the energy required for phase transitions. Confined cell structures and interface engineering techniques have demonstrated programming energy reductions of up to 70% compared to conventional PCM designs. Additionally, innovative programming schemes utilizing partial RESET operations and incremental conductance modulation have shown promise in maintaining multi-level weight precision while reducing overall energy consumption.

The selector device technology paired with PCM cells also significantly impacts energy efficiency. Traditional transistor selectors consume considerable chip area and contribute to parasitic capacitance, increasing the effective energy per operation. Novel selector technologies such as ovonic threshold switches (OTS) and metal-insulator transitions (MIT) devices offer lower capacitance and higher integration density, potentially reducing the energy overhead in large crossbar arrays.

Peripheral circuitry optimization presents another avenue for energy efficiency improvements. Advanced sense amplifiers with lower operating voltages and current-mode reading techniques minimize read energy, while intelligent programming circuits implementing adaptive pulse schemes reduce write energy by avoiding over-programming. Some recent designs incorporate on-chip energy harvesting and storage elements to recycle charge during read operations.

Looking forward, emerging materials engineering approaches such as doping strategies and interface layer modifications show potential for lowering the melting point of phase-change materials while maintaining stability. Computational simulations suggest that optimized dopant concentrations could reduce RESET current requirements by up to 40% without compromising data retention characteristics. These material innovations, combined with advanced 3D integration techniques, may enable the next generation of energy-efficient PCM synaptic arrays suitable for deployment in power-constrained neuromorphic computing environments.

Current PCM synaptic implementations face energy efficiency challenges that scale with array size. A typical PCM cell requires 10-100 pJ per programming operation, which becomes substantial when considering arrays with millions of synaptic elements necessary for complex neural network implementations. This energy requirement creates thermal management issues and limits the scalability of PCM-based neuromorphic systems, particularly for edge computing applications with strict power constraints.

Recent advancements have focused on reducing the active volume of phase-change material, thereby decreasing the energy required for phase transitions. Confined cell structures and interface engineering techniques have demonstrated programming energy reductions of up to 70% compared to conventional PCM designs. Additionally, innovative programming schemes utilizing partial RESET operations and incremental conductance modulation have shown promise in maintaining multi-level weight precision while reducing overall energy consumption.

The selector device technology paired with PCM cells also significantly impacts energy efficiency. Traditional transistor selectors consume considerable chip area and contribute to parasitic capacitance, increasing the effective energy per operation. Novel selector technologies such as ovonic threshold switches (OTS) and metal-insulator transitions (MIT) devices offer lower capacitance and higher integration density, potentially reducing the energy overhead in large crossbar arrays.

Peripheral circuitry optimization presents another avenue for energy efficiency improvements. Advanced sense amplifiers with lower operating voltages and current-mode reading techniques minimize read energy, while intelligent programming circuits implementing adaptive pulse schemes reduce write energy by avoiding over-programming. Some recent designs incorporate on-chip energy harvesting and storage elements to recycle charge during read operations.

Looking forward, emerging materials engineering approaches such as doping strategies and interface layer modifications show potential for lowering the melting point of phase-change materials while maintaining stability. Computational simulations suggest that optimized dopant concentrations could reduce RESET current requirements by up to 40% without compromising data retention characteristics. These material innovations, combined with advanced 3D integration techniques, may enable the next generation of energy-efficient PCM synaptic arrays suitable for deployment in power-constrained neuromorphic computing environments.

Reliability and Endurance Optimization Strategies

The reliability and endurance of Phase-Change Memory (PCM) devices remain critical challenges when implementing multi-level synaptic weights for neuromorphic computing applications. Current PCM cells typically demonstrate endurance in the range of 10^6 to 10^8 write cycles, which falls short of the requirements for intensive neural network training scenarios that may demand 10^12 or more weight updates.

Several optimization strategies have emerged to address these limitations. Pulse engineering techniques have shown promising results, where carefully designed write pulses with specific amplitude, duration, and shape characteristics can significantly reduce cell degradation. The implementation of verify-write schemes, which involve reading the cell state after each write operation and making adjustments as needed, has demonstrated up to 50% improvement in endurance by minimizing unnecessary phase transitions.

Material engineering approaches represent another frontier in reliability enhancement. Doping the phase-change material with elements such as nitrogen or carbon has been shown to stabilize the amorphous phase and reduce atomic migration, thereby extending device lifetime. Novel material compositions, such as GeSbTe alloys with optimized stoichiometry, have demonstrated improved crystallization stability and reduced drift characteristics.

Architectural solutions provide system-level approaches to mitigate endurance limitations. Wear-leveling algorithms distribute write operations evenly across memory arrays, preventing premature failure of frequently accessed cells. Error correction codes (ECC) specifically designed for PCM characteristics can detect and correct resistance drift errors, extending the effective lifetime of the memory array. Some research groups have implemented hybrid memory systems that combine PCM with more durable volatile memory to handle frequently updated weights.

Thermal management strategies have proven essential for reliability optimization. Improved heat dissipation designs reduce thermal crosstalk between adjacent cells, preventing unintended crystallization or amorphization. Thermal barriers integrated into the cell structure can contain heat within the programming region, reducing energy consumption and minimizing thermal stress on surrounding materials.

Recent advances in closed-loop feedback systems show particular promise for neuromorphic applications. These systems continuously monitor PCM cell characteristics during operation and adaptively adjust programming parameters to compensate for aging effects. Machine learning algorithms have been deployed to predict cell degradation patterns and proactively adjust programming schemes, extending usable device lifetime by up to 40% in experimental settings.

The combination of these strategies has pushed PCM reliability boundaries, with recent demonstrations achieving stable multi-level operation beyond 10^9 cycles in laboratory environments. However, further optimization remains necessary to meet the demanding requirements of large-scale neuromorphic systems with continuous learning capabilities.

Several optimization strategies have emerged to address these limitations. Pulse engineering techniques have shown promising results, where carefully designed write pulses with specific amplitude, duration, and shape characteristics can significantly reduce cell degradation. The implementation of verify-write schemes, which involve reading the cell state after each write operation and making adjustments as needed, has demonstrated up to 50% improvement in endurance by minimizing unnecessary phase transitions.

Material engineering approaches represent another frontier in reliability enhancement. Doping the phase-change material with elements such as nitrogen or carbon has been shown to stabilize the amorphous phase and reduce atomic migration, thereby extending device lifetime. Novel material compositions, such as GeSbTe alloys with optimized stoichiometry, have demonstrated improved crystallization stability and reduced drift characteristics.

Architectural solutions provide system-level approaches to mitigate endurance limitations. Wear-leveling algorithms distribute write operations evenly across memory arrays, preventing premature failure of frequently accessed cells. Error correction codes (ECC) specifically designed for PCM characteristics can detect and correct resistance drift errors, extending the effective lifetime of the memory array. Some research groups have implemented hybrid memory systems that combine PCM with more durable volatile memory to handle frequently updated weights.

Thermal management strategies have proven essential for reliability optimization. Improved heat dissipation designs reduce thermal crosstalk between adjacent cells, preventing unintended crystallization or amorphization. Thermal barriers integrated into the cell structure can contain heat within the programming region, reducing energy consumption and minimizing thermal stress on surrounding materials.

Recent advances in closed-loop feedback systems show particular promise for neuromorphic applications. These systems continuously monitor PCM cell characteristics during operation and adaptively adjust programming parameters to compensate for aging effects. Machine learning algorithms have been deployed to predict cell degradation patterns and proactively adjust programming schemes, extending usable device lifetime by up to 40% in experimental settings.

The combination of these strategies has pushed PCM reliability boundaries, with recent demonstrations achieving stable multi-level operation beyond 10^9 cycles in laboratory environments. However, further optimization remains necessary to meet the demanding requirements of large-scale neuromorphic systems with continuous learning capabilities.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!