SiC Gate Driver Isolation: Digital Vs Magnetic Vs Capacitive—Latency And Robustness

SEP 22, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

SiC Gate Driver Isolation Technology Background and Objectives

Silicon Carbide (SiC) power devices have emerged as revolutionary components in power electronics over the past two decades, offering superior performance characteristics compared to traditional silicon-based semiconductors. The evolution of SiC technology has been marked by significant improvements in efficiency, power density, and switching speeds, enabling more compact and efficient power conversion systems across various applications.

Gate driver isolation technology represents a critical interface between control circuitry and SiC power devices, ensuring safe and reliable operation while maintaining optimal switching performance. Historically, isolation techniques have evolved from optocoupler-based solutions to more advanced digital, magnetic, and capacitive isolation technologies to meet the increasing demands of high-frequency switching applications.

The technical trajectory of SiC gate driver isolation has been driven by the inherent characteristics of SiC devices, which can switch at frequencies exceeding 100 kHz and withstand blocking voltages above 10 kV. These capabilities have necessitated isolation solutions with minimal propagation delay, high common-mode transient immunity (CMTI), and extended reliability under extreme operating conditions.

Current market trends indicate a growing adoption of SiC technology in electric vehicles, renewable energy systems, industrial drives, and grid infrastructure, creating an urgent need for isolation solutions that can maintain signal integrity while withstanding the harsh electrical environments associated with high-voltage, high-frequency switching.

The primary technical objectives for SiC gate driver isolation development include: reducing propagation delay to sub-50ns levels to fully leverage SiC's high-speed switching capability; enhancing CMTI performance beyond 100 kV/μs to withstand extreme dv/dt conditions; ensuring long-term reliability under high-temperature operation (175°C and above); and maintaining isolation integrity throughout the device lifetime despite thermal cycling and electrical stress.

Additionally, there is a growing emphasis on achieving these performance metrics while simultaneously reducing power consumption, physical footprint, and system cost to facilitate broader market adoption of SiC technology across various applications.

The comparative analysis of digital, magnetic, and capacitive isolation technologies represents a critical evaluation framework for determining optimal solutions for specific SiC applications, with particular focus on latency performance and robustness under extreme operating conditions. Each isolation technology offers distinct advantages and limitations that must be carefully considered in the context of application requirements.

As SiC devices continue to advance toward higher voltage ratings, faster switching speeds, and more compact form factors, the development of compatible isolation technologies remains a key enabler for unlocking the full potential of wide-bandgap semiconductor technology in next-generation power electronics systems.

Gate driver isolation technology represents a critical interface between control circuitry and SiC power devices, ensuring safe and reliable operation while maintaining optimal switching performance. Historically, isolation techniques have evolved from optocoupler-based solutions to more advanced digital, magnetic, and capacitive isolation technologies to meet the increasing demands of high-frequency switching applications.

The technical trajectory of SiC gate driver isolation has been driven by the inherent characteristics of SiC devices, which can switch at frequencies exceeding 100 kHz and withstand blocking voltages above 10 kV. These capabilities have necessitated isolation solutions with minimal propagation delay, high common-mode transient immunity (CMTI), and extended reliability under extreme operating conditions.

Current market trends indicate a growing adoption of SiC technology in electric vehicles, renewable energy systems, industrial drives, and grid infrastructure, creating an urgent need for isolation solutions that can maintain signal integrity while withstanding the harsh electrical environments associated with high-voltage, high-frequency switching.

The primary technical objectives for SiC gate driver isolation development include: reducing propagation delay to sub-50ns levels to fully leverage SiC's high-speed switching capability; enhancing CMTI performance beyond 100 kV/μs to withstand extreme dv/dt conditions; ensuring long-term reliability under high-temperature operation (175°C and above); and maintaining isolation integrity throughout the device lifetime despite thermal cycling and electrical stress.

Additionally, there is a growing emphasis on achieving these performance metrics while simultaneously reducing power consumption, physical footprint, and system cost to facilitate broader market adoption of SiC technology across various applications.

The comparative analysis of digital, magnetic, and capacitive isolation technologies represents a critical evaluation framework for determining optimal solutions for specific SiC applications, with particular focus on latency performance and robustness under extreme operating conditions. Each isolation technology offers distinct advantages and limitations that must be carefully considered in the context of application requirements.

As SiC devices continue to advance toward higher voltage ratings, faster switching speeds, and more compact form factors, the development of compatible isolation technologies remains a key enabler for unlocking the full potential of wide-bandgap semiconductor technology in next-generation power electronics systems.

Market Demand Analysis for SiC Power Electronics

The Silicon Carbide (SiC) power electronics market is experiencing unprecedented growth driven by the global shift towards energy efficiency and electrification. Current market analysis indicates that the SiC power device market is expanding at a CAGR of 30% and is projected to reach $3 billion by 2025, with significant acceleration expected beyond this timeframe.

This robust market growth is primarily fueled by the automotive sector, particularly electric vehicles (EVs), where SiC-based power modules offer substantial advantages in efficiency, power density, and thermal performance. The EV market alone is expected to consume over 60% of all SiC power devices produced by 2026, as manufacturers seek to extend vehicle range, reduce charging times, and decrease overall system costs.

Industrial applications represent the second-largest demand segment, with factory automation, renewable energy systems, and grid infrastructure collectively accounting for approximately 25% of the market. The superior switching characteristics of SiC devices enable more compact and efficient power conversion systems, which are increasingly essential for industrial modernization and energy transition initiatives.

The aerospace and defense sectors are emerging as high-value niche markets for SiC power electronics, where the material's radiation hardness and high-temperature operation capabilities provide critical advantages in harsh operating environments. Though smaller in volume, these applications command premium pricing and drive innovation in reliability engineering.

Gate driver isolation technology, a critical component in SiC power systems, is experiencing intensified demand for solutions that can match the high-speed switching capabilities of SiC devices while maintaining robust isolation. Market research indicates that approximately 40% of system designers cite gate driver performance as a primary bottleneck in fully leveraging SiC benefits.

The comparative performance of digital, magnetic, and capacitive isolation technologies has become a decisive factor in design selection. Industry surveys reveal that 45% of power electronics engineers consider isolation latency as the most critical parameter for high-frequency SiC applications, while 35% prioritize noise immunity and robustness in harsh industrial environments.

Regional analysis shows that Asia-Pacific dominates SiC device production, but North America and Europe lead in high-performance gate driver technology development. This geographical distribution is creating new supply chain dynamics and strategic partnerships between semiconductor manufacturers and isolation technology providers.

The market is increasingly segmenting based on application-specific requirements, with automotive designs favoring solutions that optimize efficiency, industrial applications prioritizing robustness, and consumer electronics focusing on size reduction and cost optimization.

This robust market growth is primarily fueled by the automotive sector, particularly electric vehicles (EVs), where SiC-based power modules offer substantial advantages in efficiency, power density, and thermal performance. The EV market alone is expected to consume over 60% of all SiC power devices produced by 2026, as manufacturers seek to extend vehicle range, reduce charging times, and decrease overall system costs.

Industrial applications represent the second-largest demand segment, with factory automation, renewable energy systems, and grid infrastructure collectively accounting for approximately 25% of the market. The superior switching characteristics of SiC devices enable more compact and efficient power conversion systems, which are increasingly essential for industrial modernization and energy transition initiatives.

The aerospace and defense sectors are emerging as high-value niche markets for SiC power electronics, where the material's radiation hardness and high-temperature operation capabilities provide critical advantages in harsh operating environments. Though smaller in volume, these applications command premium pricing and drive innovation in reliability engineering.

Gate driver isolation technology, a critical component in SiC power systems, is experiencing intensified demand for solutions that can match the high-speed switching capabilities of SiC devices while maintaining robust isolation. Market research indicates that approximately 40% of system designers cite gate driver performance as a primary bottleneck in fully leveraging SiC benefits.

The comparative performance of digital, magnetic, and capacitive isolation technologies has become a decisive factor in design selection. Industry surveys reveal that 45% of power electronics engineers consider isolation latency as the most critical parameter for high-frequency SiC applications, while 35% prioritize noise immunity and robustness in harsh industrial environments.

Regional analysis shows that Asia-Pacific dominates SiC device production, but North America and Europe lead in high-performance gate driver technology development. This geographical distribution is creating new supply chain dynamics and strategic partnerships between semiconductor manufacturers and isolation technology providers.

The market is increasingly segmenting based on application-specific requirements, with automotive designs favoring solutions that optimize efficiency, industrial applications prioritizing robustness, and consumer electronics focusing on size reduction and cost optimization.

Current Isolation Technologies and Technical Challenges

Silicon Carbide (SiC) power devices have revolutionized power electronics with their superior performance characteristics, including higher switching frequencies, temperature tolerance, and efficiency. However, these advantages come with challenges, particularly in gate driver isolation technologies. Currently, three primary isolation technologies dominate the SiC gate driver landscape: digital, magnetic, and capacitive isolation.

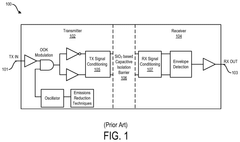

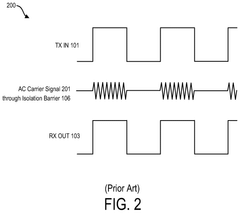

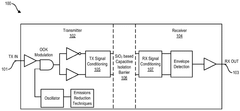

Digital isolators utilize CMOS-based architectures with integrated RF modulators and demodulators to transmit signals across an isolation barrier. These devices offer excellent common-mode transient immunity (CMTI) typically ranging from 50 to 100 kV/μs, making them suitable for high-switching-frequency SiC applications. However, they face challenges with propagation delay (typically 10-50ns) and potential susceptibility to electromagnetic interference in harsh industrial environments.

Magnetic isolation technology employs transformer-based coupling to transmit signals across the isolation barrier. This approach offers inherently high isolation voltage capabilities (up to 10kV) and exceptional CMTI performance (>200 kV/μs). The primary technical challenge for magnetic isolators remains their relatively higher propagation delay (typically 20-60ns) compared to newer technologies, which can limit switching performance in ultra-high-frequency applications.

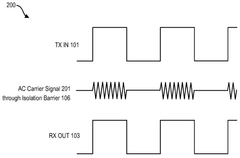

Capacitive isolation utilizes high-voltage capacitors to transmit signals across the isolation barrier. These isolators excel in speed with propagation delays as low as 5-10ns, making them particularly attractive for high-frequency SiC applications. However, they typically demonstrate lower CMTI ratings (30-75 kV/μs) compared to magnetic isolators and may experience reliability issues in environments with significant temperature variations.

A critical technical challenge across all isolation technologies is maintaining signal integrity during the extreme dv/dt conditions characteristic of SiC switching. The rapid voltage transitions (often exceeding 50 kV/μs) can induce common-mode currents through parasitic capacitances, potentially causing false triggering or isolation barrier breakdown.

Power supply requirements present another significant challenge. SiC gate drivers require higher gate voltages (typically +20V/-5V compared to +15V/-5V for silicon) and must deliver higher peak currents to achieve optimal switching performance. This places additional stress on the isolated power supply architecture, requiring careful design considerations.

Thermal management remains problematic across all isolation technologies. SiC devices operate at higher temperatures, and isolation components must maintain performance integrity across wider temperature ranges (often -40°C to +125°C or higher). This thermal stress can accelerate aging mechanisms in isolation materials, potentially compromising long-term reliability.

Standardization and qualification testing represent ongoing challenges, as existing standards developed for silicon-based systems may not adequately address the unique operational characteristics of SiC power systems, particularly regarding isolation performance under extreme dv/dt conditions and elevated temperatures.

Digital isolators utilize CMOS-based architectures with integrated RF modulators and demodulators to transmit signals across an isolation barrier. These devices offer excellent common-mode transient immunity (CMTI) typically ranging from 50 to 100 kV/μs, making them suitable for high-switching-frequency SiC applications. However, they face challenges with propagation delay (typically 10-50ns) and potential susceptibility to electromagnetic interference in harsh industrial environments.

Magnetic isolation technology employs transformer-based coupling to transmit signals across the isolation barrier. This approach offers inherently high isolation voltage capabilities (up to 10kV) and exceptional CMTI performance (>200 kV/μs). The primary technical challenge for magnetic isolators remains their relatively higher propagation delay (typically 20-60ns) compared to newer technologies, which can limit switching performance in ultra-high-frequency applications.

Capacitive isolation utilizes high-voltage capacitors to transmit signals across the isolation barrier. These isolators excel in speed with propagation delays as low as 5-10ns, making them particularly attractive for high-frequency SiC applications. However, they typically demonstrate lower CMTI ratings (30-75 kV/μs) compared to magnetic isolators and may experience reliability issues in environments with significant temperature variations.

A critical technical challenge across all isolation technologies is maintaining signal integrity during the extreme dv/dt conditions characteristic of SiC switching. The rapid voltage transitions (often exceeding 50 kV/μs) can induce common-mode currents through parasitic capacitances, potentially causing false triggering or isolation barrier breakdown.

Power supply requirements present another significant challenge. SiC gate drivers require higher gate voltages (typically +20V/-5V compared to +15V/-5V for silicon) and must deliver higher peak currents to achieve optimal switching performance. This places additional stress on the isolated power supply architecture, requiring careful design considerations.

Thermal management remains problematic across all isolation technologies. SiC devices operate at higher temperatures, and isolation components must maintain performance integrity across wider temperature ranges (often -40°C to +125°C or higher). This thermal stress can accelerate aging mechanisms in isolation materials, potentially compromising long-term reliability.

Standardization and qualification testing represent ongoing challenges, as existing standards developed for silicon-based systems may not adequately address the unique operational characteristics of SiC power systems, particularly regarding isolation performance under extreme dv/dt conditions and elevated temperatures.

Comparative Analysis of Digital, Magnetic and Capacitive Isolation

01 Isolation techniques for SiC gate drivers

Various isolation technologies are employed in SiC gate drivers to ensure electrical separation between control and power circuits while maintaining signal integrity. These include galvanic isolation, optical isolation, and magnetic isolation methods that protect control circuitry from high voltages while minimizing propagation delays. Advanced isolation barriers are designed to withstand high dv/dt and di/dt transients common in SiC applications, providing robust protection against noise and interference.- Isolation techniques for SiC gate drivers: Various isolation techniques are employed in SiC gate drivers to ensure electrical separation between control and power circuits while maintaining signal integrity. These techniques include galvanic isolation, optical isolation, and magnetic isolation methods that protect the control circuitry from high voltages and transients in the power stage. Proper isolation is critical for the robustness of SiC-based power systems, especially in high-voltage applications where isolation barriers must withstand substantial voltage differences while minimizing propagation delays.

- Latency reduction in SiC gate driver circuits: Minimizing signal propagation delay (latency) in SiC gate driver circuits is essential for high-frequency operation and switching performance. Advanced circuit designs incorporate specialized components and topologies to reduce the time delay between control signal generation and gate switching. These designs focus on optimizing signal paths, using high-speed components, and implementing parallel processing techniques to achieve faster response times while maintaining isolation integrity, which is particularly important for SiC MOSFETs operating at high switching frequencies.

- Robustness enhancement for SiC gate drivers: Enhancing the robustness of SiC gate drivers involves implementing protection mechanisms against various operational stresses and environmental factors. These include overvoltage protection, overcurrent protection, temperature compensation, and EMI immunity features. Advanced designs incorporate fault detection and handling capabilities, along with redundant systems to ensure continued operation under adverse conditions. These robustness features are critical for maintaining reliable operation in harsh industrial environments and preventing catastrophic failures in high-power applications.

- Integrated solutions for SiC power modules: Integrated gate driver solutions for SiC power modules combine multiple functions into compact packages to optimize performance and reliability. These integrated designs incorporate isolation barriers, protection circuits, power management, and control logic within a single module or chip. By reducing interconnection complexity and parasitic elements, these solutions improve switching performance, thermal management, and overall system reliability. The integration approach also enables standardized interfaces and simplified system design for various SiC-based power conversion applications.

- Advanced control algorithms for SiC gate drivers: Advanced control algorithms implemented in SiC gate drivers optimize switching behavior and system performance. These algorithms include adaptive gate drive techniques, dead-time optimization, and active gate control methods that dynamically adjust driving parameters based on operating conditions. By precisely controlling gate voltage profiles and timing, these algorithms reduce switching losses, minimize electromagnetic interference, and extend device lifetime. The implementation often involves digital signal processors or specialized integrated circuits that balance switching speed with robustness requirements.

02 Latency reduction in SiC gate driver circuits

Minimizing signal propagation delay is critical for high-frequency SiC MOSFET switching. Specialized circuit designs incorporate high-speed components and optimized signal paths to reduce turn-on and turn-off delays. Advanced gate driver architectures employ parallel processing paths, pre-emphasis techniques, and adaptive timing control to compensate for temperature and load variations. These approaches enable faster switching transitions while maintaining safe operating margins, ultimately improving power conversion efficiency.Expand Specific Solutions03 Robustness enhancement for harsh operating environments

SiC gate drivers must maintain reliable operation under extreme conditions including high temperatures, voltage spikes, and electromagnetic interference. Robust designs incorporate temperature compensation circuits, overvoltage protection mechanisms, and EMI filtering. Advanced packaging techniques and materials improve thermal management and physical durability. Fault detection and protection features prevent catastrophic failures by rapidly responding to abnormal operating conditions, ensuring system reliability in demanding industrial and automotive applications.Expand Specific Solutions04 Integrated protection features for SiC gate drivers

Modern SiC gate drivers incorporate multiple protection mechanisms to safeguard expensive SiC power devices. These include desaturation detection, overcurrent protection, short-circuit protection, and under-voltage lockout. Advanced designs feature programmable fault response times and soft shutdown capabilities to minimize stress during fault conditions. Some implementations use active Miller clamp circuits to prevent parasitic turn-on and provide controlled switching during transients, significantly improving system reliability and robustness.Expand Specific Solutions05 Novel architectures for optimized SiC switching performance

Innovative gate driver architectures specifically designed for SiC devices address the unique challenges of high-speed switching. These include multi-level driving schemes, resonant gate drivers, and active gate control techniques that dynamically adjust gate resistance and voltage profiles during switching transitions. Some designs incorporate feedback mechanisms to monitor and adjust switching parameters in real-time, optimizing the trade-off between switching speed and electromagnetic emissions. These advanced architectures enable SiC devices to achieve their full performance potential while maintaining system stability.Expand Specific Solutions

Key Industry Players in SiC Gate Driver Market

The SiC Gate Driver Isolation technology market is in a growth phase, with increasing adoption in power electronics applications requiring high efficiency and reliability. The market is expanding rapidly, driven by electric vehicle adoption and renewable energy integration, with projections exceeding $500 million by 2026. Regarding technology maturity, digital isolation solutions from Microchip Technology and Infineon Technologies lead in integration capabilities, while magnetic isolation approaches by ROHM and Wolfspeed offer superior noise immunity. Capacitive isolation technologies developed by companies like Hitachi Energy and Delta Electronics provide balanced performance with lower latency. Emerging players like Fast SiC Semiconductor are advancing novel isolation techniques to address the critical trade-offs between switching speed, robustness against common-mode transients, and reliability in harsh environments.

Microchip Technology, Inc.

Technical Solution: Microchip has developed a comprehensive SiC gate driver isolation portfolio centered around their digital isolation technology. Their approach utilizes high-speed CMOS-based isolators with propagation delays as low as 50ns while achieving common-mode transient immunity ratings of 200V/ns[6]. Microchip's SiC gate driver solutions incorporate advanced power management features on the isolated side, including regulated gate drive voltages that can be dynamically adjusted based on operating conditions to optimize switching performance and reliability. Their isolation architecture implements redundant isolation channels with continuous monitoring for critical signals, enhancing system safety in industrial and automotive applications. Microchip's latest generation includes programmable dead-time control and adaptive gate drive strength adjustment, allowing optimization for different SiC device characteristics and switching frequencies. Their digital isolation approach enables additional features like isolated fault reporting and status monitoring with minimal additional components, simplifying system design while enhancing diagnostic capabilities[7].

Strengths: Excellent CMTI performance (200V/ns) provides superior noise immunity; programmable features allow optimization for different SiC devices and operating conditions; comprehensive diagnostic capabilities enhance system reliability. Weaknesses: Digital isolation typically consumes more power than magnetic or capacitive alternatives; implementation complexity increases with advanced features; slightly higher propagation delay compared to some capacitive solutions.

ROHM Co., Ltd.

Technical Solution: ROHM has pioneered a hybrid isolation approach for SiC gate drivers that combines the advantages of different isolation technologies. Their BM2SCQ12xT-LBZ series utilizes capacitive isolation for control signals, achieving industry-leading propagation delays of approximately 35ns[4], while implementing magnetic isolation for power transfer across the barrier. This dual-technology approach optimizes both speed and power delivery. ROHM's isolation design incorporates advanced common-mode noise cancellation techniques, with differential signaling paths and specialized filtering that maintains signal integrity even in environments with dv/dt rates exceeding 100V/ns. Their gate drivers feature integrated temperature compensation circuits that adjust drive strength based on SiC device characteristics across operating conditions, maintaining optimal switching performance. ROHM's latest generation includes advanced short-circuit protection with response times under 200ns, significantly faster than conventional approaches, enabling the use of smaller, more efficient SiC dies while maintaining system reliability[5].

Strengths: Ultra-low latency capacitive signal isolation (35ns) enables highest switching frequencies; hybrid isolation approach optimizes both speed and power delivery; integrated protection features specifically designed for SiC switching characteristics. Weaknesses: More complex implementation compared to single-technology solutions; capacitive isolation may be more susceptible to external electric field interference in certain applications.

Critical Patents and Technical Literature on Isolation Technologies

Silicon Carbide Driver Using High Voltage Capacitors for Isolation and Signal Transmission

PatentPendingUS20250183890A1

Innovation

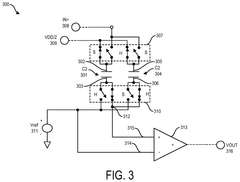

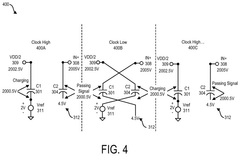

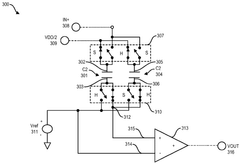

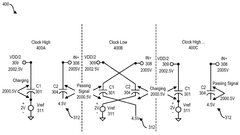

- A gate driver circuit is designed with a first and second capacitor, each with terminals that are selectively coupled to an input drive signal and a power supply voltage using high voltage domain switches, and to a reference voltage and high impedance node using low voltage domain switches. A comparator compares the reference voltage with the voltage at the high impedance node to generate an output drive signal, effectively transferring the high voltage input drive signal to a low voltage output drive signal.

Silicon carbide driver using high voltage capacitors for isolation and signal transmission

PatentWO2025117986A1

Innovation

- A gate driver circuit utilizing high voltage capacitors for isolation and signal transmission, where capacitors are selectively coupled to input drive signals and power supply voltages using switches controlled by a clock signal, allowing for efficient voltage transfer and comparison to generate output drive signals.

Reliability and Robustness Testing Methodologies

Reliability and robustness testing methodologies for SiC gate driver isolation technologies must be comprehensive and rigorous to ensure performance under extreme conditions. These methodologies typically begin with baseline characterization tests that establish performance metrics for digital, magnetic, and capacitive isolation technologies under normal operating conditions.

Environmental stress testing forms a critical component of the evaluation process. This includes temperature cycling (-55°C to +150°C), humidity testing (85% relative humidity at 85°C), and thermal shock tests. SiC devices operate at significantly higher temperatures than traditional silicon, making thermal performance particularly important for isolation barriers.

Electrical stress testing evaluates isolation performance under extreme voltage conditions. Common methodologies include partial discharge testing, surge immunity testing (per IEC 61000-4-5), and high-voltage breakdown testing. For SiC applications, the isolation barrier must withstand common mode transients exceeding 100 kV/μs, requiring specialized test equipment to accurately simulate these conditions.

EMI/EMC testing is particularly relevant for comparing isolation technologies. Digital isolators must be tested for susceptibility to electromagnetic interference, while magnetic isolators require evaluation of core saturation under high magnetic fields. Capacitive isolators need assessment for immunity to electric field disturbances. Standard methodologies include radiated and conducted emissions testing per CISPR 25 and IEC 61967.

Accelerated lifetime testing provides critical data on long-term reliability. This includes high-temperature operating life (HTOL) testing, typically at 125°C for 1000+ hours, and highly accelerated life testing (HALT) that combines temperature cycling with vibration stress. Time-dependent dielectric breakdown (TDDB) testing specifically evaluates the isolation barrier's long-term integrity.

Statistical analysis methodologies are employed to process test data, including Weibull analysis for failure distribution and mean time between failures (MTBF) calculations. For automotive and industrial applications, testing must conform to AEC-Q100 and IEC 60747 standards respectively.

Comparative analysis methodologies enable direct comparison between isolation technologies. This includes side-by-side testing under identical conditions and standardized metrics for latency, common-mode transient immunity (CMTI), and isolation lifetime. These methodologies reveal that while digital isolators typically offer superior latency characteristics, magnetic isolators often demonstrate better robustness under extreme EMI conditions, and capacitive isolators provide a balance of performance attributes.

Environmental stress testing forms a critical component of the evaluation process. This includes temperature cycling (-55°C to +150°C), humidity testing (85% relative humidity at 85°C), and thermal shock tests. SiC devices operate at significantly higher temperatures than traditional silicon, making thermal performance particularly important for isolation barriers.

Electrical stress testing evaluates isolation performance under extreme voltage conditions. Common methodologies include partial discharge testing, surge immunity testing (per IEC 61000-4-5), and high-voltage breakdown testing. For SiC applications, the isolation barrier must withstand common mode transients exceeding 100 kV/μs, requiring specialized test equipment to accurately simulate these conditions.

EMI/EMC testing is particularly relevant for comparing isolation technologies. Digital isolators must be tested for susceptibility to electromagnetic interference, while magnetic isolators require evaluation of core saturation under high magnetic fields. Capacitive isolators need assessment for immunity to electric field disturbances. Standard methodologies include radiated and conducted emissions testing per CISPR 25 and IEC 61967.

Accelerated lifetime testing provides critical data on long-term reliability. This includes high-temperature operating life (HTOL) testing, typically at 125°C for 1000+ hours, and highly accelerated life testing (HALT) that combines temperature cycling with vibration stress. Time-dependent dielectric breakdown (TDDB) testing specifically evaluates the isolation barrier's long-term integrity.

Statistical analysis methodologies are employed to process test data, including Weibull analysis for failure distribution and mean time between failures (MTBF) calculations. For automotive and industrial applications, testing must conform to AEC-Q100 and IEC 60747 standards respectively.

Comparative analysis methodologies enable direct comparison between isolation technologies. This includes side-by-side testing under identical conditions and standardized metrics for latency, common-mode transient immunity (CMTI), and isolation lifetime. These methodologies reveal that while digital isolators typically offer superior latency characteristics, magnetic isolators often demonstrate better robustness under extreme EMI conditions, and capacitive isolators provide a balance of performance attributes.

EMI/EMC Considerations in SiC Gate Driver Design

Silicon Carbide (SiC) power devices operate at significantly higher switching frequencies and voltage slew rates compared to traditional silicon devices, creating unique electromagnetic interference (EMI) and electromagnetic compatibility (EMC) challenges in gate driver design. These challenges are particularly pronounced in the isolation interfaces, where digital, magnetic, and capacitive isolation technologies each present distinct EMI/EMC profiles.

Digital isolators, while offering excellent common-mode transient immunity (CMTI) typically exceeding 100 kV/μs, can become sources of high-frequency noise due to their internal oscillators operating in the range of 100-500 MHz. This noise may couple into sensitive control circuits, potentially causing false triggering or signal corruption in high-power density applications.

Magnetic isolators demonstrate superior performance in high dv/dt environments typical of SiC applications. Their transformer-based isolation barrier provides natural immunity to common-mode noise, but requires careful PCB layout to prevent magnetic flux leakage that could induce currents in adjacent signal traces. Proper shielding and strategic component placement are essential to maintain signal integrity.

Capacitive isolation, while offering the lowest latency among the three technologies, presents unique susceptibility to electric field interference. The very mechanism that enables its operation—capacitive coupling—makes it vulnerable to external electric fields generated during high-speed switching events. Implementing guard rings and ground planes becomes critical to shield these isolators from switching noise.

Board-level design considerations significantly impact EMI/EMC performance regardless of isolation technology. Minimizing loop areas in gate drive circuits, implementing separate ground planes for high-voltage and low-voltage sections, and strategic placement of decoupling capacitors are fundamental practices. The physical separation between power and signal traces must be carefully managed, with recommended minimum distances scaling with voltage levels.

Filter design represents another crucial aspect of EMI mitigation. Common-mode chokes and differential filters must be carefully selected based on the specific noise spectrum generated by the chosen isolation technology. Digital isolators typically require filtering in higher frequency bands compared to magnetic isolators.

Compliance testing reveals that SiC gate drivers with properly designed isolation interfaces can meet stringent standards such as CISPR 32 for conducted and radiated emissions. However, achieving this compliance often requires additional filtering and shielding compared to traditional silicon-based systems, increasing both cost and complexity.

Recent advancements in isolation technologies have introduced hybrid approaches that combine the strengths of multiple isolation methods, offering improved EMI/EMC performance while maintaining the low latency required for efficient SiC operation.

Digital isolators, while offering excellent common-mode transient immunity (CMTI) typically exceeding 100 kV/μs, can become sources of high-frequency noise due to their internal oscillators operating in the range of 100-500 MHz. This noise may couple into sensitive control circuits, potentially causing false triggering or signal corruption in high-power density applications.

Magnetic isolators demonstrate superior performance in high dv/dt environments typical of SiC applications. Their transformer-based isolation barrier provides natural immunity to common-mode noise, but requires careful PCB layout to prevent magnetic flux leakage that could induce currents in adjacent signal traces. Proper shielding and strategic component placement are essential to maintain signal integrity.

Capacitive isolation, while offering the lowest latency among the three technologies, presents unique susceptibility to electric field interference. The very mechanism that enables its operation—capacitive coupling—makes it vulnerable to external electric fields generated during high-speed switching events. Implementing guard rings and ground planes becomes critical to shield these isolators from switching noise.

Board-level design considerations significantly impact EMI/EMC performance regardless of isolation technology. Minimizing loop areas in gate drive circuits, implementing separate ground planes for high-voltage and low-voltage sections, and strategic placement of decoupling capacitors are fundamental practices. The physical separation between power and signal traces must be carefully managed, with recommended minimum distances scaling with voltage levels.

Filter design represents another crucial aspect of EMI mitigation. Common-mode chokes and differential filters must be carefully selected based on the specific noise spectrum generated by the chosen isolation technology. Digital isolators typically require filtering in higher frequency bands compared to magnetic isolators.

Compliance testing reveals that SiC gate drivers with properly designed isolation interfaces can meet stringent standards such as CISPR 32 for conducted and radiated emissions. However, achieving this compliance often requires additional filtering and shielding compared to traditional silicon-based systems, increasing both cost and complexity.

Recent advancements in isolation technologies have introduced hybrid approaches that combine the strengths of multiple isolation methods, offering improved EMI/EMC performance while maintaining the low latency required for efficient SiC operation.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!