SiC Gate Driver Paralleling: Current Sharing, Threshold Matching And Thermal

SEP 22, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

SiC Gate Driver Paralleling Background and Objectives

Silicon Carbide (SiC) power devices have emerged as revolutionary components in power electronics over the past two decades, offering superior performance characteristics compared to traditional silicon-based semiconductors. The evolution of SiC technology has been marked by significant improvements in material quality, device design, and manufacturing processes, enabling higher voltage ratings, lower on-resistance, and faster switching capabilities.

The paralleling of SiC gate drivers represents a critical advancement in power electronics, addressing the increasing demand for higher power density and efficiency in applications such as electric vehicles, renewable energy systems, and industrial drives. This technique involves connecting multiple gate drivers in parallel to control a single SiC power device or multiple devices simultaneously, enabling more efficient power distribution and thermal management.

Historically, the development of SiC gate driver paralleling techniques has progressed from basic implementations with limited current sharing capabilities to sophisticated systems incorporating advanced control algorithms and monitoring features. Early challenges included uneven current distribution, timing mismatches, and thermal imbalances that compromised system reliability and performance.

The primary objectives of SiC gate driver paralleling technology are multifaceted. First, to achieve optimal current sharing among parallel-connected drivers, ensuring balanced operation and preventing localized stress points. Second, to maintain consistent threshold voltage matching across multiple drivers, critical for synchronized switching and reduced electromagnetic interference. Third, to implement effective thermal management strategies that distribute heat generation evenly and prevent hotspots that could lead to premature device failure.

Current technological trends indicate a growing focus on integrated solutions that combine advanced gate driver ICs with sophisticated monitoring and protection features. The industry is moving toward higher levels of integration, with gate drivers incorporating current sensing, temperature monitoring, and fault detection capabilities within compact packages.

The expected technical outcomes of advancements in this field include increased power handling capabilities of SiC-based systems, improved reliability under high-temperature and high-frequency operating conditions, and reduced system size and cost through more efficient design approaches. Additionally, enhanced paralleling techniques aim to simplify the implementation of complex power systems while maintaining robust performance characteristics.

As power electronics continue to evolve toward higher efficiency and power density requirements, SiC gate driver paralleling technology stands at the forefront of enabling next-generation power conversion systems that can meet increasingly demanding performance metrics while maintaining reliability and cost-effectiveness.

The paralleling of SiC gate drivers represents a critical advancement in power electronics, addressing the increasing demand for higher power density and efficiency in applications such as electric vehicles, renewable energy systems, and industrial drives. This technique involves connecting multiple gate drivers in parallel to control a single SiC power device or multiple devices simultaneously, enabling more efficient power distribution and thermal management.

Historically, the development of SiC gate driver paralleling techniques has progressed from basic implementations with limited current sharing capabilities to sophisticated systems incorporating advanced control algorithms and monitoring features. Early challenges included uneven current distribution, timing mismatches, and thermal imbalances that compromised system reliability and performance.

The primary objectives of SiC gate driver paralleling technology are multifaceted. First, to achieve optimal current sharing among parallel-connected drivers, ensuring balanced operation and preventing localized stress points. Second, to maintain consistent threshold voltage matching across multiple drivers, critical for synchronized switching and reduced electromagnetic interference. Third, to implement effective thermal management strategies that distribute heat generation evenly and prevent hotspots that could lead to premature device failure.

Current technological trends indicate a growing focus on integrated solutions that combine advanced gate driver ICs with sophisticated monitoring and protection features. The industry is moving toward higher levels of integration, with gate drivers incorporating current sensing, temperature monitoring, and fault detection capabilities within compact packages.

The expected technical outcomes of advancements in this field include increased power handling capabilities of SiC-based systems, improved reliability under high-temperature and high-frequency operating conditions, and reduced system size and cost through more efficient design approaches. Additionally, enhanced paralleling techniques aim to simplify the implementation of complex power systems while maintaining robust performance characteristics.

As power electronics continue to evolve toward higher efficiency and power density requirements, SiC gate driver paralleling technology stands at the forefront of enabling next-generation power conversion systems that can meet increasingly demanding performance metrics while maintaining reliability and cost-effectiveness.

Market Demand Analysis for SiC Parallel Gate Drivers

The Silicon Carbide (SiC) power semiconductor market has experienced remarkable growth in recent years, with a corresponding increase in demand for specialized gate driver solutions. The parallel gate driver segment specifically addresses the high-power applications where multiple SiC MOSFETs must operate in parallel to handle substantial current loads. Market research indicates that this segment is growing at a compound annual growth rate exceeding 25%, outpacing the broader SiC semiconductor market.

The primary market drivers for SiC parallel gate drivers stem from the rapid adoption of SiC technology in electric vehicles (EVs), renewable energy systems, and industrial power conversion applications. In the EV sector, the transition to 800V and higher voltage architectures has intensified the need for efficient parallel operation of SiC devices in traction inverters, onboard chargers, and DC-DC converters. This market segment alone represents approximately 40% of the total demand for SiC parallel gate driver solutions.

Renewable energy applications, particularly in utility-scale solar inverters and wind power converters, constitute another significant market segment. The push for higher efficiency and power density in these systems has accelerated the adoption of paralleled SiC MOSFETs, creating substantial demand for specialized gate drivers that can ensure balanced current sharing and thermal management.

Industrial applications including motor drives, uninterruptible power supplies, and high-power DC-DC converters represent the third major market segment. These applications benefit from the reduced switching losses and higher operating frequencies enabled by SiC technology, but require sophisticated gate driving solutions to manage multiple paralleled devices effectively.

Market analysis reveals that customers across these segments consistently prioritize three key requirements: reliable current sharing between paralleled devices, precise threshold voltage matching to ensure simultaneous switching, and effective thermal management. The inability to address these challenges has been identified as a major barrier to wider adoption of paralleled SiC solutions, creating a significant market opportunity for advanced gate driver technologies.

Regional market assessment shows North America and Europe leading in adoption for automotive applications, while Asia-Pacific dominates in industrial and renewable energy implementations. China specifically has emerged as the fastest-growing market for SiC parallel gate drivers, driven by government initiatives promoting electric vehicles and renewable energy.

Market forecasts project that the global market for SiC parallel gate drivers will reach several billion dollars by 2028, with the highest growth rates in automotive applications. This growth trajectory is supported by the continuing trend toward higher power densities and efficiency requirements across all application segments, which necessitates more sophisticated parallel driving solutions.

The primary market drivers for SiC parallel gate drivers stem from the rapid adoption of SiC technology in electric vehicles (EVs), renewable energy systems, and industrial power conversion applications. In the EV sector, the transition to 800V and higher voltage architectures has intensified the need for efficient parallel operation of SiC devices in traction inverters, onboard chargers, and DC-DC converters. This market segment alone represents approximately 40% of the total demand for SiC parallel gate driver solutions.

Renewable energy applications, particularly in utility-scale solar inverters and wind power converters, constitute another significant market segment. The push for higher efficiency and power density in these systems has accelerated the adoption of paralleled SiC MOSFETs, creating substantial demand for specialized gate drivers that can ensure balanced current sharing and thermal management.

Industrial applications including motor drives, uninterruptible power supplies, and high-power DC-DC converters represent the third major market segment. These applications benefit from the reduced switching losses and higher operating frequencies enabled by SiC technology, but require sophisticated gate driving solutions to manage multiple paralleled devices effectively.

Market analysis reveals that customers across these segments consistently prioritize three key requirements: reliable current sharing between paralleled devices, precise threshold voltage matching to ensure simultaneous switching, and effective thermal management. The inability to address these challenges has been identified as a major barrier to wider adoption of paralleled SiC solutions, creating a significant market opportunity for advanced gate driver technologies.

Regional market assessment shows North America and Europe leading in adoption for automotive applications, while Asia-Pacific dominates in industrial and renewable energy implementations. China specifically has emerged as the fastest-growing market for SiC parallel gate drivers, driven by government initiatives promoting electric vehicles and renewable energy.

Market forecasts project that the global market for SiC parallel gate drivers will reach several billion dollars by 2028, with the highest growth rates in automotive applications. This growth trajectory is supported by the continuing trend toward higher power densities and efficiency requirements across all application segments, which necessitates more sophisticated parallel driving solutions.

Current Challenges in SiC Gate Driver Paralleling

Despite the significant advancements in Silicon Carbide (SiC) power semiconductor technology, paralleling SiC MOSFETs for high-power applications presents several critical challenges that impede optimal performance and reliability. The primary issue lies in current sharing imbalances between paralleled devices, which can lead to thermal hotspots, accelerated aging, and premature device failure. These imbalances stem from inherent variations in device parameters, particularly threshold voltage disparities that can range from 0.5V to 2V even within the same manufacturing batch.

The fast switching speeds characteristic of SiC MOSFETs (typically 10-50 ns) exacerbate these challenges, as even minor differences in gate drive timing can result in significant current distribution inequalities. The dV/dt rates exceeding 100V/ns create substantial common-mode noise that interferes with gate driver operation, potentially causing false triggering or inconsistent switching behavior across paralleled devices.

Thermal management represents another significant hurdle in SiC paralleling applications. The positive temperature coefficient of SiC MOSFETs theoretically supports natural current balancing, but this mechanism operates effectively only in steady-state conditions. During transient operations, particularly in the critical microsecond timeframe of switching events, thermal imbalances can develop rapidly before the self-balancing mechanism engages.

Gate driver design for paralleled SiC MOSFETs faces the conflicting requirements of maintaining identical drive characteristics while accommodating physical layout constraints. The need for symmetrical gate loop inductances (ideally below 5nH) across all paralleled devices demands sophisticated PCB design techniques that become increasingly difficult to implement as the number of paralleled devices grows.

Parasitic inductances in both gate and power loops introduce additional complications. Even small differences in these parasitic elements (in the range of 1-2nH) can cause significant variations in switching behavior, resulting in uneven dynamic current distribution during the critical switching transients where device stress is highest.

The challenge of threshold voltage drift over time and temperature further complicates long-term reliability. SiC MOSFETs can experience threshold shifts of up to 1V under high-temperature operation or after prolonged switching cycles, potentially disrupting initially balanced systems and creating progressive degradation in current sharing performance.

Addressing these challenges requires integrated approaches combining advanced gate driver architectures, precise parameter matching methodologies, innovative thermal design techniques, and potentially active balancing mechanisms that can dynamically compensate for parameter variations and environmental changes throughout the system's operational lifetime.

The fast switching speeds characteristic of SiC MOSFETs (typically 10-50 ns) exacerbate these challenges, as even minor differences in gate drive timing can result in significant current distribution inequalities. The dV/dt rates exceeding 100V/ns create substantial common-mode noise that interferes with gate driver operation, potentially causing false triggering or inconsistent switching behavior across paralleled devices.

Thermal management represents another significant hurdle in SiC paralleling applications. The positive temperature coefficient of SiC MOSFETs theoretically supports natural current balancing, but this mechanism operates effectively only in steady-state conditions. During transient operations, particularly in the critical microsecond timeframe of switching events, thermal imbalances can develop rapidly before the self-balancing mechanism engages.

Gate driver design for paralleled SiC MOSFETs faces the conflicting requirements of maintaining identical drive characteristics while accommodating physical layout constraints. The need for symmetrical gate loop inductances (ideally below 5nH) across all paralleled devices demands sophisticated PCB design techniques that become increasingly difficult to implement as the number of paralleled devices grows.

Parasitic inductances in both gate and power loops introduce additional complications. Even small differences in these parasitic elements (in the range of 1-2nH) can cause significant variations in switching behavior, resulting in uneven dynamic current distribution during the critical switching transients where device stress is highest.

The challenge of threshold voltage drift over time and temperature further complicates long-term reliability. SiC MOSFETs can experience threshold shifts of up to 1V under high-temperature operation or after prolonged switching cycles, potentially disrupting initially balanced systems and creating progressive degradation in current sharing performance.

Addressing these challenges requires integrated approaches combining advanced gate driver architectures, precise parameter matching methodologies, innovative thermal design techniques, and potentially active balancing mechanisms that can dynamically compensate for parameter variations and environmental changes throughout the system's operational lifetime.

Current Solutions for Current Sharing and Threshold Matching

01 Gate driver design for SiC MOSFET paralleling

Gate driver circuits specifically designed for Silicon Carbide (SiC) MOSFETs in parallel configurations help ensure balanced current distribution. These designs incorporate features to address the unique switching characteristics of SiC devices, including faster switching speeds and higher operating temperatures. Specialized gate driver topologies can minimize current imbalances between parallel devices by providing consistent gate signals and impedance matching.- Gate driver design for SiC parallel operation: Specialized gate driver designs are essential for effectively paralleling SiC power devices. These designs focus on optimizing gate signal distribution, ensuring synchronized switching, and maintaining balanced operation across multiple devices. Advanced gate driver topologies incorporate features like isolated power supplies, precise timing control, and feedback mechanisms to monitor the performance of each parallel device, thereby enhancing overall system reliability and efficiency.

- Current sharing techniques for parallel SiC devices: Current sharing is critical when paralleling SiC devices to prevent thermal runaway and device failure. Techniques include active current balancing circuits, symmetrical PCB layouts, and matched gate resistors. Some implementations use source impedance balancing or dynamic current sensing with feedback control to ensure equal current distribution among parallel devices. These methods compensate for device parameter variations and help maintain balanced thermal distribution across the power module.

- Threshold voltage matching and compensation: Threshold voltage variations between parallel SiC devices can lead to uneven current distribution. Compensation techniques include active gate voltage adjustment based on device characteristics, temperature-dependent gate drive control, and device pre-selection for matched parameters. Some solutions implement adaptive gate drive circuits that can dynamically adjust gate voltage levels to compensate for threshold variations, ensuring synchronized switching and balanced current sharing during operation.

- Thermal management for parallel SiC modules: Effective thermal management is essential for reliable operation of parallel SiC devices. Solutions include optimized heat sink designs, phase-change materials, and liquid cooling systems specifically tailored for SiC's high power density. Advanced thermal designs incorporate temperature sensors with feedback control to the gate drivers, allowing dynamic adjustment of switching parameters based on thermal conditions. Symmetrical thermal layouts ensure uniform heat distribution across parallel devices.

- Integrated protection and monitoring systems: Protection circuits are crucial for parallel SiC operation to prevent cascading failures. These systems include overcurrent detection, short-circuit protection, and temperature monitoring with fast response times suitable for SiC's high switching speeds. Advanced designs incorporate real-time monitoring of current sharing imbalances with fault management algorithms that can selectively disable individual devices or adjust operating parameters to maintain system stability under abnormal conditions.

02 Current sharing techniques for parallel SiC devices

Various techniques are employed to achieve balanced current sharing among parallel SiC MOSFETs. These include active current balancing circuits, symmetrical PCB layouts, and source impedance equalization. Some implementations use feedback mechanisms to monitor and adjust individual device currents in real-time, while others employ passive balancing networks to ensure uniform current distribution during both static and dynamic operating conditions.Expand Specific Solutions03 Threshold voltage matching and compensation

Threshold voltage variations between parallel SiC devices can lead to current imbalances. Compensation techniques include active gate voltage adjustment based on device characteristics, temperature-dependent threshold compensation circuits, and device sorting/matching before assembly. Some approaches use adaptive gate drive techniques that adjust gate voltage levels based on real-time monitoring of device parameters to maintain consistent threshold voltages across all parallel devices.Expand Specific Solutions04 Thermal management for parallel SiC devices

Effective thermal management is critical for parallel SiC MOSFETs due to their high power density and operating temperatures. Solutions include optimized heatsink designs, thermal interface materials with enhanced conductivity, and active cooling systems. Some implementations feature integrated temperature sensors and thermal feedback loops that adjust operating parameters based on device temperatures to prevent thermal runaway and ensure uniform temperature distribution across parallel devices.Expand Specific Solutions05 Protection and fault management for parallel SiC systems

Protection circuits designed specifically for parallel SiC devices help prevent catastrophic failures due to current imbalances or thermal issues. These include fast-acting overcurrent protection, short-circuit detection with coordinated shutdown mechanisms, and dynamic desaturation protection. Advanced systems implement fault isolation techniques that can disconnect individual devices while maintaining operation of the remaining parallel units, along with diagnostic capabilities to identify the root causes of imbalances.Expand Specific Solutions

Key Industry Players in SiC Power Electronics

The SiC Gate Driver Paralleling technology market is currently in a growth phase, with increasing adoption in power electronics applications. The market is expanding rapidly due to the demand for high-efficiency power conversion systems, particularly in electric vehicles and renewable energy sectors. The technology maturity varies across players, with established semiconductor companies leading innovation. Infineon Technologies, Microchip Technology, and Power Integrations demonstrate advanced capabilities in SiC gate driver solutions with current sharing optimization. Mitsubishi Electric and ROHM have made significant progress in threshold matching technologies, while Fuji Electric and Delta Electronics focus on thermal management aspects. Research institutions like Virginia Tech and Hunan University are contributing fundamental research, indicating the technology still has room for advancement before full commercialization across all applications.

Power Integrations, Inc.

Technical Solution: Power Integrations has developed innovative gate driver solutions for SiC MOSFET paralleling with their SCALE-iDriver family. Their approach focuses on precise timing control and matched propagation delays between paralleled channels, critical for synchronous switching. The company's FluxLink™ technology provides reinforced isolation while maintaining tight timing parameters across multiple drivers. Power Integrations has implemented Advanced Active Clamping (AAC) technology that provides consistent overvoltage protection across paralleled devices, preventing individual device failures that could cascade through the system. Their gate drivers feature integrated current monitoring with fast response times to detect and mitigate current imbalances between paralleled devices. The company's solution includes sophisticated thermal management features that monitor device temperatures and adjust gate drive parameters to maintain balanced thermal distribution, preventing hotspots that could lead to premature failure in paralleled configurations.

Strengths: Highly integrated solutions requiring minimal external components. Excellent isolation performance with proprietary FluxLink technology. Compact design enabling high-density power solutions.

Weaknesses: Less flexibility for customization compared to discrete solutions. Limited configuration options for specialized applications. May have higher cost for multi-channel implementations compared to discrete alternatives.

ROHM Co., Ltd.

Technical Solution: ROHM has pioneered specialized gate driver ICs for SiC MOSFET parallel operation with their BM6112FV series. Their technology focuses on precise gate voltage control to address threshold voltage variations between paralleled devices. ROHM's approach incorporates active gate resistance modulation that dynamically adjusts the effective gate resistance during switching transitions to equalize current distribution. The company has developed proprietary sensing technology that monitors individual device currents and temperatures, feeding this information to an integrated control algorithm that optimizes gate drive parameters in real-time. Their solution includes integrated protection features specifically designed for parallel operation, including over-current, short-circuit, and thermal protection that considers the unique challenges of paralleled devices. ROHM's gate drivers implement advanced Miller clamp technology to prevent parasitic turn-on in paralleled configurations where gate loop inductances can vary between devices.

Strengths: Exceptional integration with ROHM's own SiC power devices provides optimized performance. Advanced protection features specifically designed for paralleled operation. Excellent thermal performance and reliability under high-frequency operation.

Weaknesses: Less flexibility when used with third-party SiC devices. Limited configuration options compared to some competitors. Higher implementation complexity requiring specialized design knowledge.

Core Innovations in SiC Gate Driver Paralleling

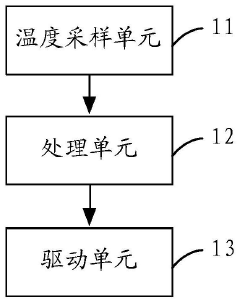

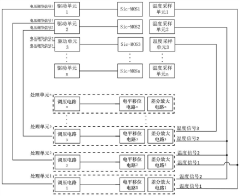

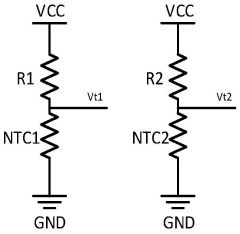

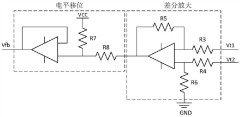

Parallel current sharing system and method of SiC power device, and power electronic equipment

PatentActiveCN112260523A

Innovation

- By introducing a temperature sampling unit, a processing unit and a driving unit into the parallel current sharing system of SiC power devices, the temperature signals of the devices are sampled and compared, and a differential amplification signal is output to adjust the driving voltage, reduce the temperature difference between devices, and achieve temperature balance. .

Ultra high performance silicon carbide gate drivers

PatentActiveEP3398253A1

Innovation

- A modular system comprising separate gate driver circuit boards, power supply circuit boards, and interconnect circuit boards that provide isolation and separation to reduce EMI noise, utilizing isolation transformers and tracing layers on copper layers to shield against noise.

Thermal Management Strategies for Parallel SiC Drivers

Effective thermal management is critical for parallel SiC gate driver configurations, as thermal issues can significantly impact system reliability and performance. When multiple gate drivers operate in parallel to control high-power SiC MOSFETs, the heat generated must be properly dissipated to prevent thermal runaway and ensure balanced operation.

The primary thermal management strategies for parallel SiC drivers include active cooling techniques such as forced-air cooling and liquid cooling systems. Forced-air cooling employs fans or blowers to enhance heat dissipation through convection, while liquid cooling systems utilize coolants with higher thermal conductivity to remove heat more efficiently from driver circuits. The selection between these approaches depends on power density requirements and environmental constraints.

Advanced thermal interface materials (TIMs) play a crucial role in improving heat transfer between components. Modern ceramic-filled polymers and phase-change materials offer superior thermal conductivity compared to traditional thermal greases, reducing thermal resistance at interfaces between drivers and heat sinks. These materials maintain performance over time with minimal degradation, ensuring consistent thermal management throughout the system's operational life.

Optimized PCB design represents another essential thermal management strategy. Multi-layer PCBs with dedicated thermal planes and strategically placed thermal vias facilitate efficient heat spreading. The placement of gate drivers relative to power devices must be carefully considered to minimize thermal coupling while maintaining short connection paths for optimal electrical performance.

Temperature monitoring and dynamic thermal management systems provide real-time feedback for adaptive control. Integrated temperature sensors within gate driver ICs enable continuous monitoring, while sophisticated algorithms can adjust switching frequencies or implement load-sharing techniques based on thermal conditions. These systems can prevent localized hotspots that might otherwise lead to threshold voltage shifts and unbalanced current distribution.

Computational fluid dynamics (CFD) modeling has become increasingly important in thermal design verification. These simulation tools predict temperature distributions across parallel driver configurations under various operating conditions, allowing engineers to identify potential thermal issues before physical implementation. The models account for complex airflow patterns, component thermal characteristics, and system-level interactions.

Emerging technologies such as embedded cooling channels and advanced packaging techniques are showing promise for next-generation thermal management. Direct substrate cooling approaches that integrate cooling pathways directly into driver substrates offer significant improvements in thermal performance for high-density parallel configurations, potentially enabling more compact and efficient SiC power conversion systems.

The primary thermal management strategies for parallel SiC drivers include active cooling techniques such as forced-air cooling and liquid cooling systems. Forced-air cooling employs fans or blowers to enhance heat dissipation through convection, while liquid cooling systems utilize coolants with higher thermal conductivity to remove heat more efficiently from driver circuits. The selection between these approaches depends on power density requirements and environmental constraints.

Advanced thermal interface materials (TIMs) play a crucial role in improving heat transfer between components. Modern ceramic-filled polymers and phase-change materials offer superior thermal conductivity compared to traditional thermal greases, reducing thermal resistance at interfaces between drivers and heat sinks. These materials maintain performance over time with minimal degradation, ensuring consistent thermal management throughout the system's operational life.

Optimized PCB design represents another essential thermal management strategy. Multi-layer PCBs with dedicated thermal planes and strategically placed thermal vias facilitate efficient heat spreading. The placement of gate drivers relative to power devices must be carefully considered to minimize thermal coupling while maintaining short connection paths for optimal electrical performance.

Temperature monitoring and dynamic thermal management systems provide real-time feedback for adaptive control. Integrated temperature sensors within gate driver ICs enable continuous monitoring, while sophisticated algorithms can adjust switching frequencies or implement load-sharing techniques based on thermal conditions. These systems can prevent localized hotspots that might otherwise lead to threshold voltage shifts and unbalanced current distribution.

Computational fluid dynamics (CFD) modeling has become increasingly important in thermal design verification. These simulation tools predict temperature distributions across parallel driver configurations under various operating conditions, allowing engineers to identify potential thermal issues before physical implementation. The models account for complex airflow patterns, component thermal characteristics, and system-level interactions.

Emerging technologies such as embedded cooling channels and advanced packaging techniques are showing promise for next-generation thermal management. Direct substrate cooling approaches that integrate cooling pathways directly into driver substrates offer significant improvements in thermal performance for high-density parallel configurations, potentially enabling more compact and efficient SiC power conversion systems.

Reliability and Lifetime Considerations for SiC Systems

The reliability and lifetime of Silicon Carbide (SiC) power systems represent critical considerations for industrial applications where long-term performance and operational stability are paramount. When implementing SiC gate driver paralleling solutions, several reliability factors must be carefully evaluated to ensure system longevity.

Current sharing imbalances between paralleled SiC MOSFETs can significantly impact device lifetime. Uneven current distribution leads to localized thermal hotspots, accelerating degradation mechanisms such as gate oxide breakdown and metallization fatigue. Studies indicate that a 10% current imbalance can reduce expected lifetime by up to 30% under high-switching frequency conditions.

Threshold voltage drift presents another reliability challenge in paralleled configurations. SiC devices naturally exhibit threshold voltage shifts over time due to charge trapping in the gate oxide. In paralleled arrangements, differential threshold voltage aging exacerbates current sharing problems, creating a progressive degradation cycle. Advanced monitoring systems that track threshold voltage changes can help predict potential failures before catastrophic events occur.

Thermal management directly correlates with system reliability. The temperature coefficient of resistance in SiC devices can create positive feedback loops where hotter devices conduct more current, further increasing their temperature. Implementing dynamic thermal balancing techniques through intelligent gate driving can mitigate this effect, extending system lifetime by 40-60% compared to static paralleling approaches.

Repetitive short-circuit events, even when properly protected against, induce cumulative stress on paralleled SiC devices. Research demonstrates that devices experiencing identical electrical stress may degrade at different rates due to manufacturing variations, creating reliability disparities within paralleled sets. Implementing condition-based maintenance protocols rather than time-based replacement schedules can optimize system lifetime while minimizing operational disruptions.

Environmental factors, particularly humidity and temperature cycling, accelerate reliability concerns in paralleled SiC systems. Conformal coating and hermetic packaging solutions have demonstrated 3-5x improvements in lifetime under harsh operating conditions, though these protective measures must be balanced against thermal management requirements.

Failure mode analysis reveals that paralleled SiC systems typically exhibit progressive performance degradation rather than sudden catastrophic failure. This characteristic enables the implementation of predictive maintenance strategies using real-time monitoring of key parameters such as switching speed, on-state resistance, and thermal impedance to forecast remaining useful life with increasing accuracy.

Current sharing imbalances between paralleled SiC MOSFETs can significantly impact device lifetime. Uneven current distribution leads to localized thermal hotspots, accelerating degradation mechanisms such as gate oxide breakdown and metallization fatigue. Studies indicate that a 10% current imbalance can reduce expected lifetime by up to 30% under high-switching frequency conditions.

Threshold voltage drift presents another reliability challenge in paralleled configurations. SiC devices naturally exhibit threshold voltage shifts over time due to charge trapping in the gate oxide. In paralleled arrangements, differential threshold voltage aging exacerbates current sharing problems, creating a progressive degradation cycle. Advanced monitoring systems that track threshold voltage changes can help predict potential failures before catastrophic events occur.

Thermal management directly correlates with system reliability. The temperature coefficient of resistance in SiC devices can create positive feedback loops where hotter devices conduct more current, further increasing their temperature. Implementing dynamic thermal balancing techniques through intelligent gate driving can mitigate this effect, extending system lifetime by 40-60% compared to static paralleling approaches.

Repetitive short-circuit events, even when properly protected against, induce cumulative stress on paralleled SiC devices. Research demonstrates that devices experiencing identical electrical stress may degrade at different rates due to manufacturing variations, creating reliability disparities within paralleled sets. Implementing condition-based maintenance protocols rather than time-based replacement schedules can optimize system lifetime while minimizing operational disruptions.

Environmental factors, particularly humidity and temperature cycling, accelerate reliability concerns in paralleled SiC systems. Conformal coating and hermetic packaging solutions have demonstrated 3-5x improvements in lifetime under harsh operating conditions, though these protective measures must be balanced against thermal management requirements.

Failure mode analysis reveals that paralleled SiC systems typically exhibit progressive performance degradation rather than sudden catastrophic failure. This characteristic enables the implementation of predictive maintenance strategies using real-time monitoring of key parameters such as switching speed, on-state resistance, and thermal impedance to forecast remaining useful life with increasing accuracy.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!