Patents

Literature

310results about "Power consumption reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor integrated circuit

InactiveUS8547771B2Reduce power consumptionReduce delaysTransistorPower consumption reductionElectricityHemt circuits

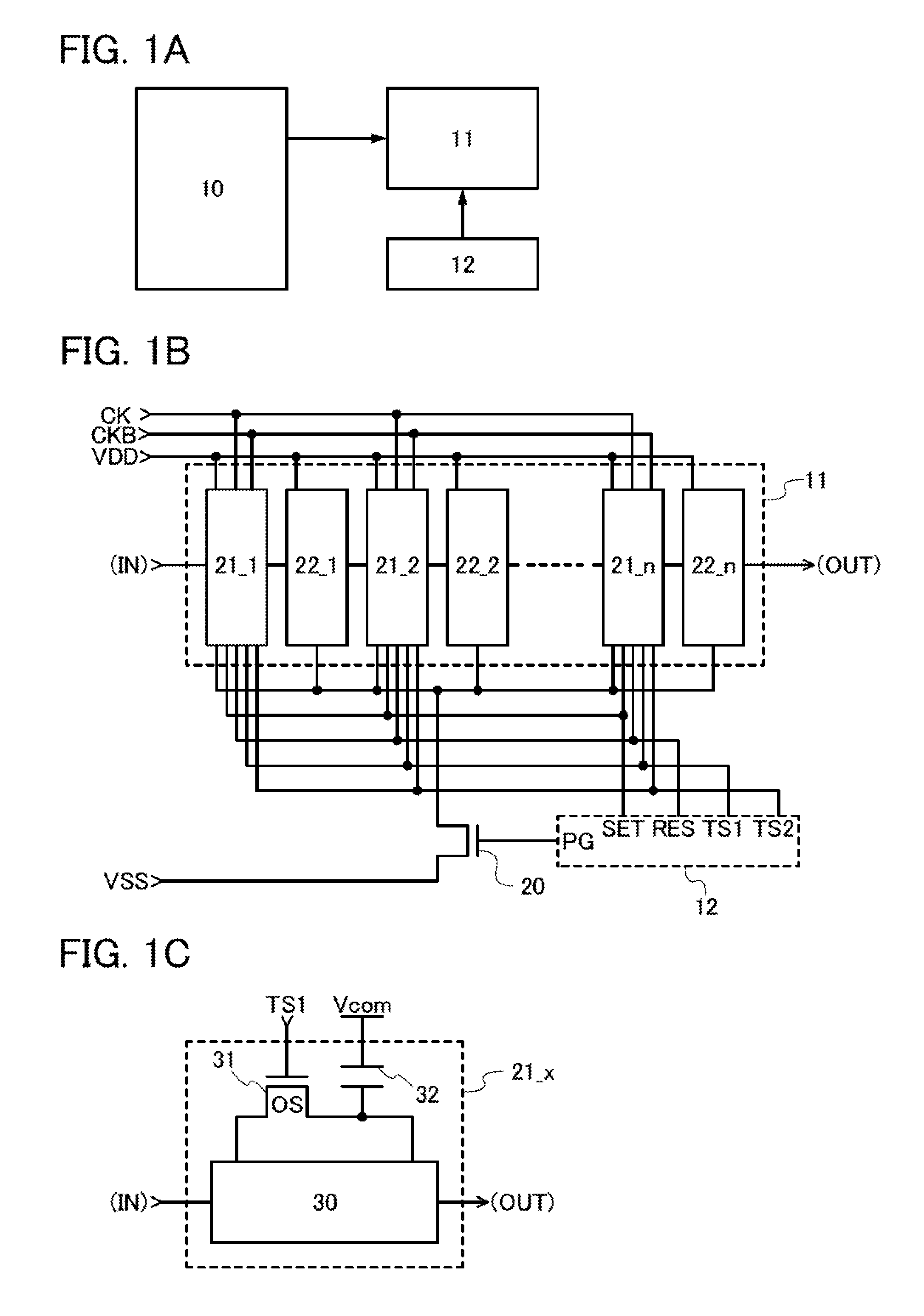

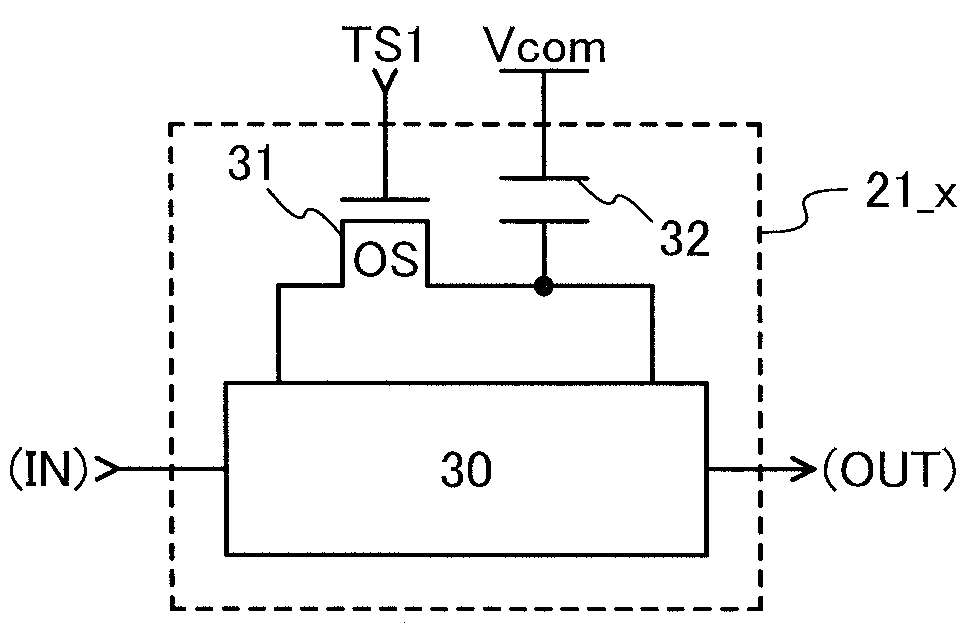

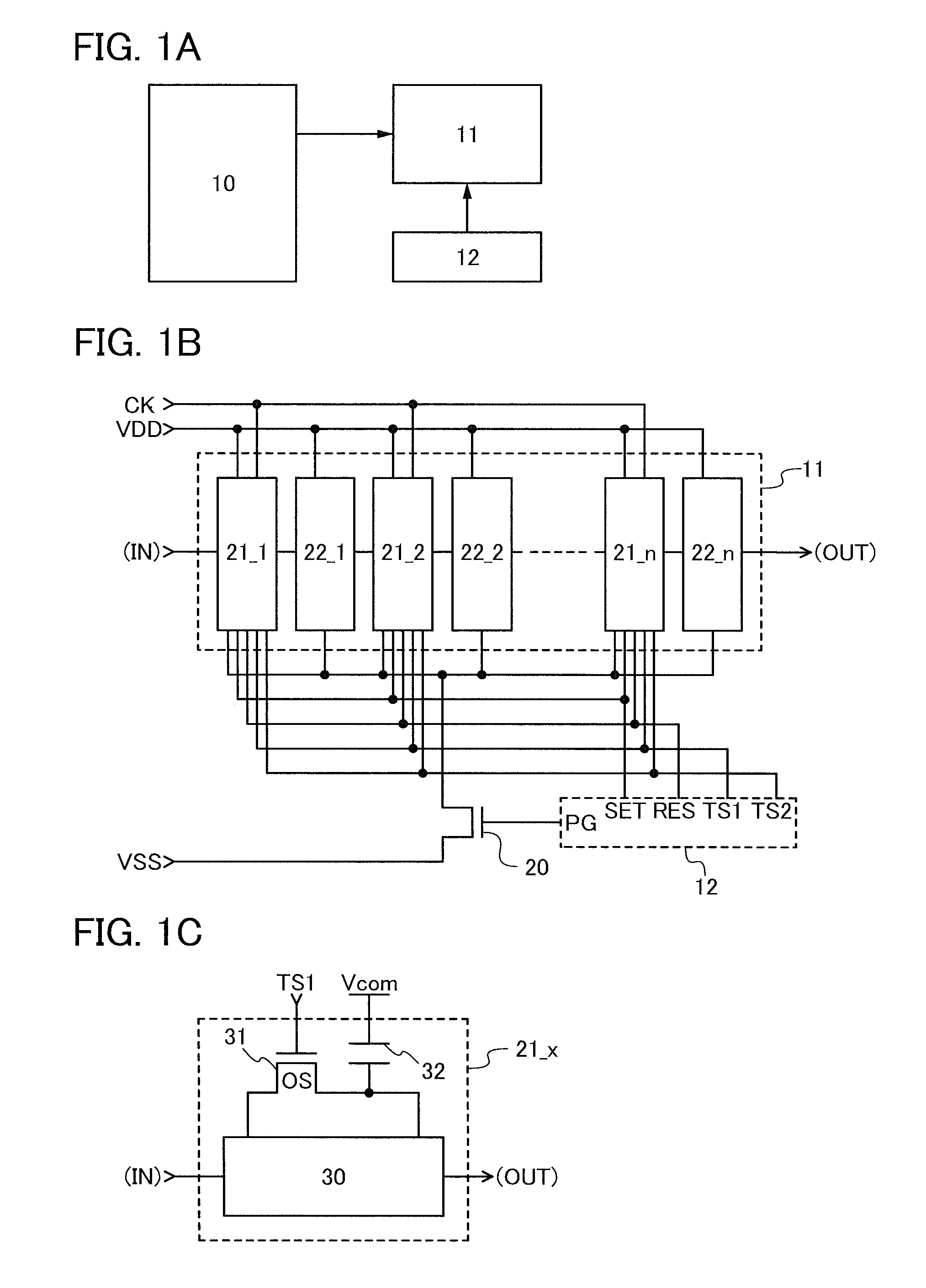

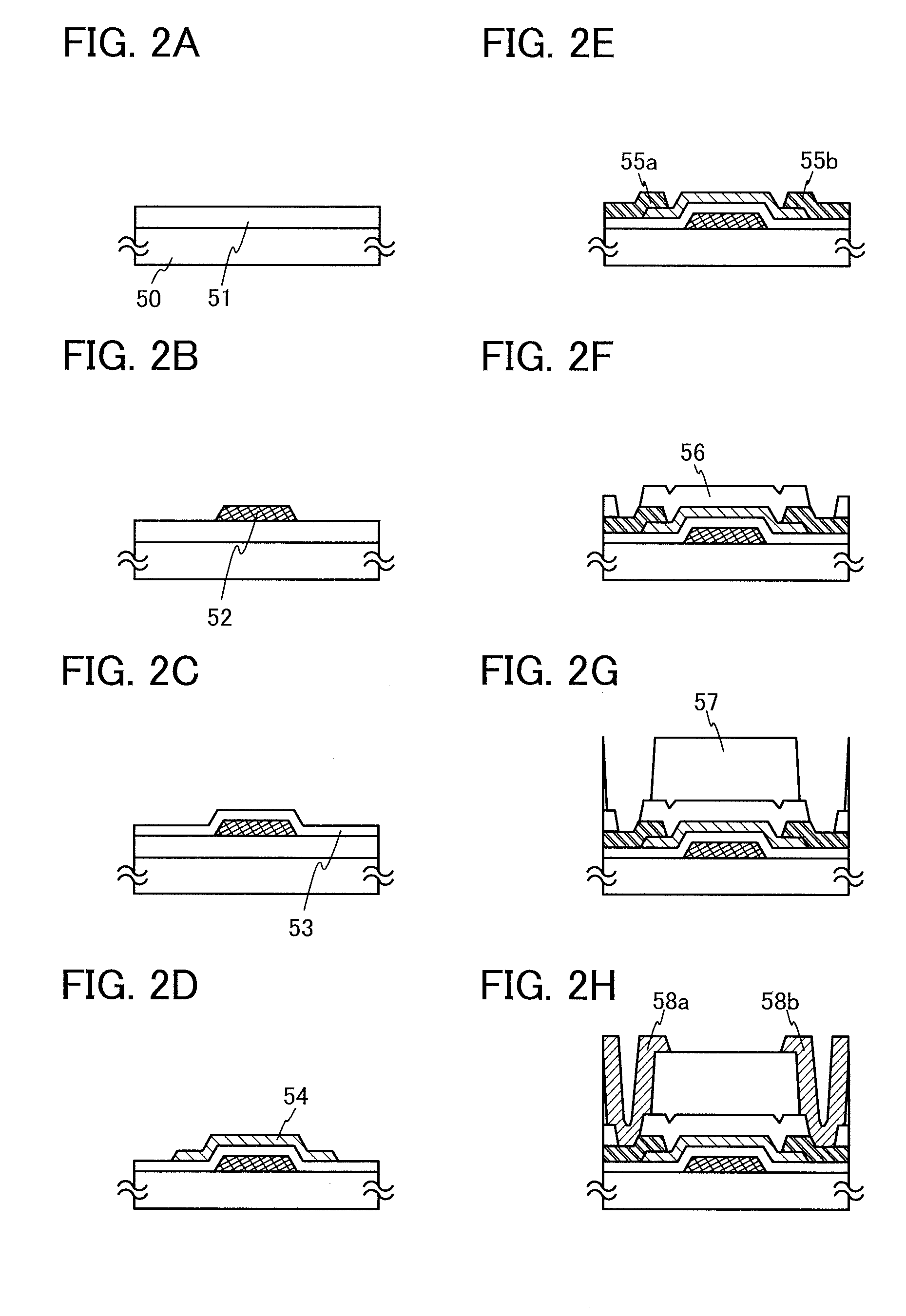

To reduce power consumption of a semiconductor integrated circuit and to reduce delay of the operation in the semiconductor integrated circuit, a plurality of sequential circuits included in a storage circuit each include a transistor whose channel formation region is formed with an oxide semiconductor, and a capacitor whose one electrode is electrically connected to a node that is brought into a floating state when the transistor is turned off. By using an oxide semiconductor for the channel formation region of the transistor, the transistor with an extremely low off-state current (leakage current) can be realized. Thus, by turning off the transistor in a period during which power supply voltage is not supplied to the storage circuit, the potential in that period of the node to which one electrode of the capacitor is electrically connected can be kept constant or almost constant. Consequently, the above objects can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor integrated device

InactiveUS20120032730A1Reduce power consumptionReduce operational latencyTransistorPower consumption reductionNODALElectricity

To reduce power consumption of a semiconductor integrated circuit and to reduce delay of the operation in the semiconductor integrated circuit, a plurality of sequential circuits included in a storage circuit each include a transistor whose channel formation region is formed with an oxide semiconductor, and a capacitor whose one electrode is electrically connected to a node that is brought into a floating state when the transistor is turned off. By using an oxide semiconductor for the channel formation region of the transistor, the transistor with an extremely low off-state current (leakage current) can be realized. Thus, by turning off the transistor in a period during which power supply voltage is not supplied to the storage circuit, the potential in that period of the node to which one electrode of the capacitor is electrically connected can be kept constant or almost constant. Consequently, the above objects can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

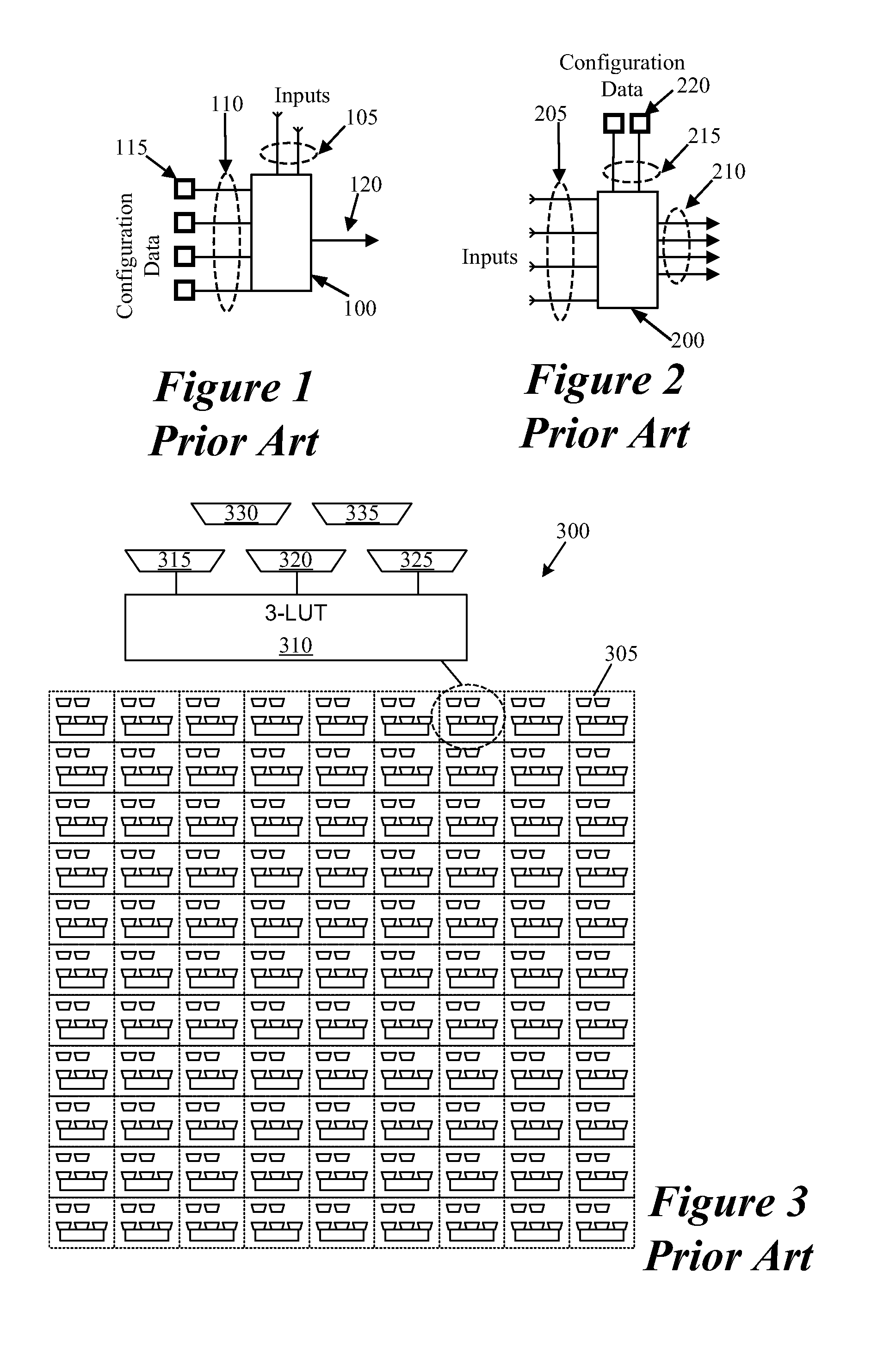

Multiple-valued logic circuit architecture; supplementary symmetrical logic circuit structure (SUS-LOC)

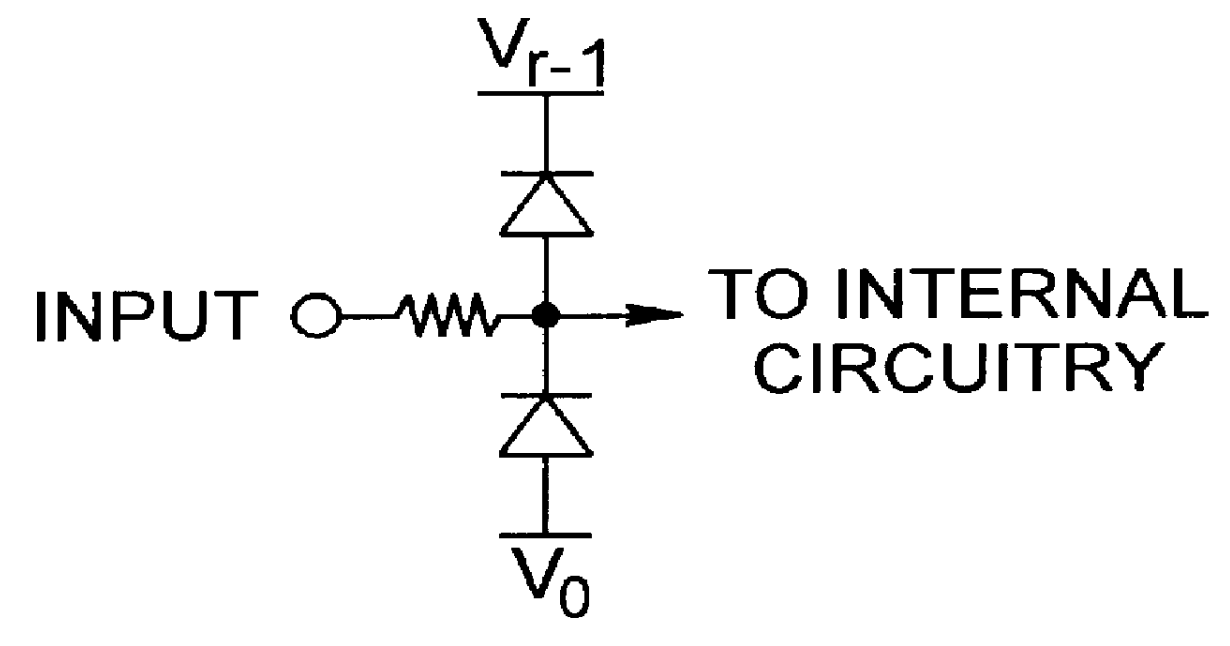

InactiveUS6133754AEasy to copyEasy transferPower consumption reductionLogic circuits characterised by logic functionMany-valued logicLogic synthesis

Circuit structure and resulting circuitry for multiple-valued logic. The circuit structure allows the design and fabrication of any r-valued logic function of n-places where r is an integer greater than 1 and n is an integer greater than 0. This structure is called SUpplementary Symmetrical LOgic Circuit structure (SUS-LOC). In circuits incorporating SUS-LOC, circuit branches are realized that uniquely deliver circuit response and output. For some circuits, and due to the operating characteristics of the switch elements, additional circuit elements, or stages, must be incorporated to prevent "back biasing." SUS-LOC is fully active. Only active elements perform logic synthesis and those components not directly related to logic synthesis, such as resistors and / or other passive loads, are relegated the task of circuit protection. The fabrication of r-valued, multi-valued, or multiple-valued logic circuits, designed using the definitions of the SUS-LOC structure can be accomplished with known techniques, materials, and equipment.

Owner:OMNIBASE LOGIC

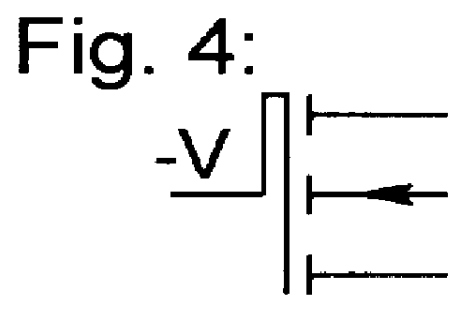

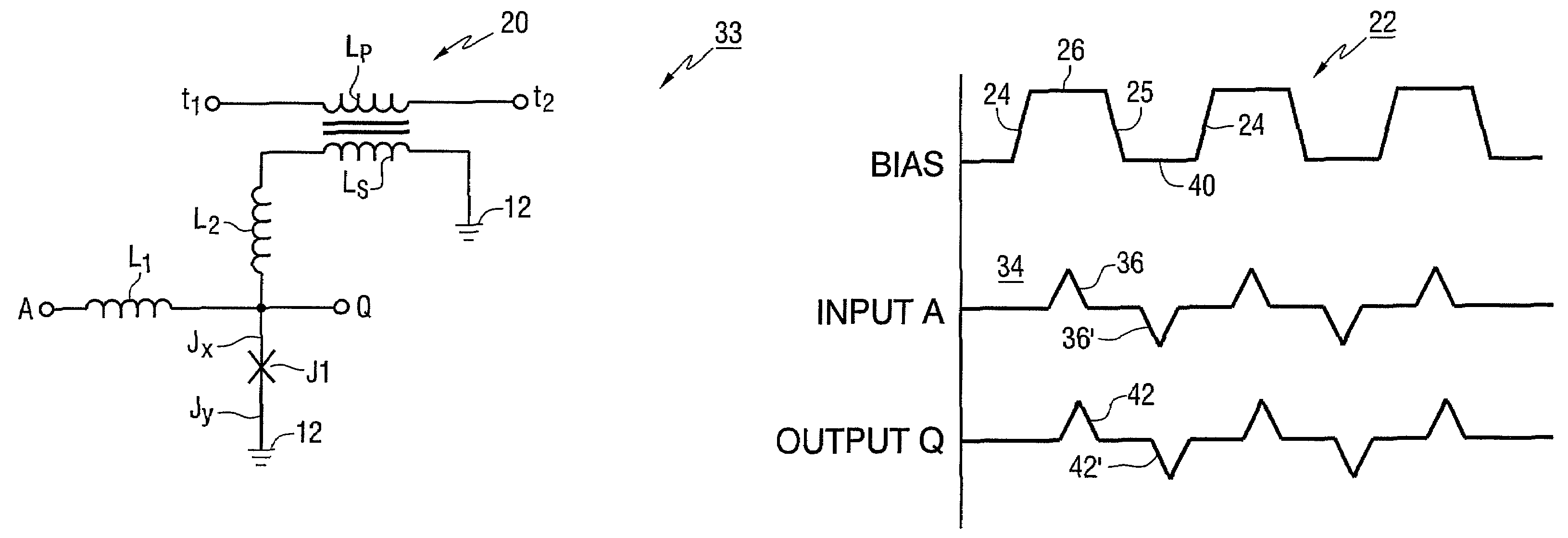

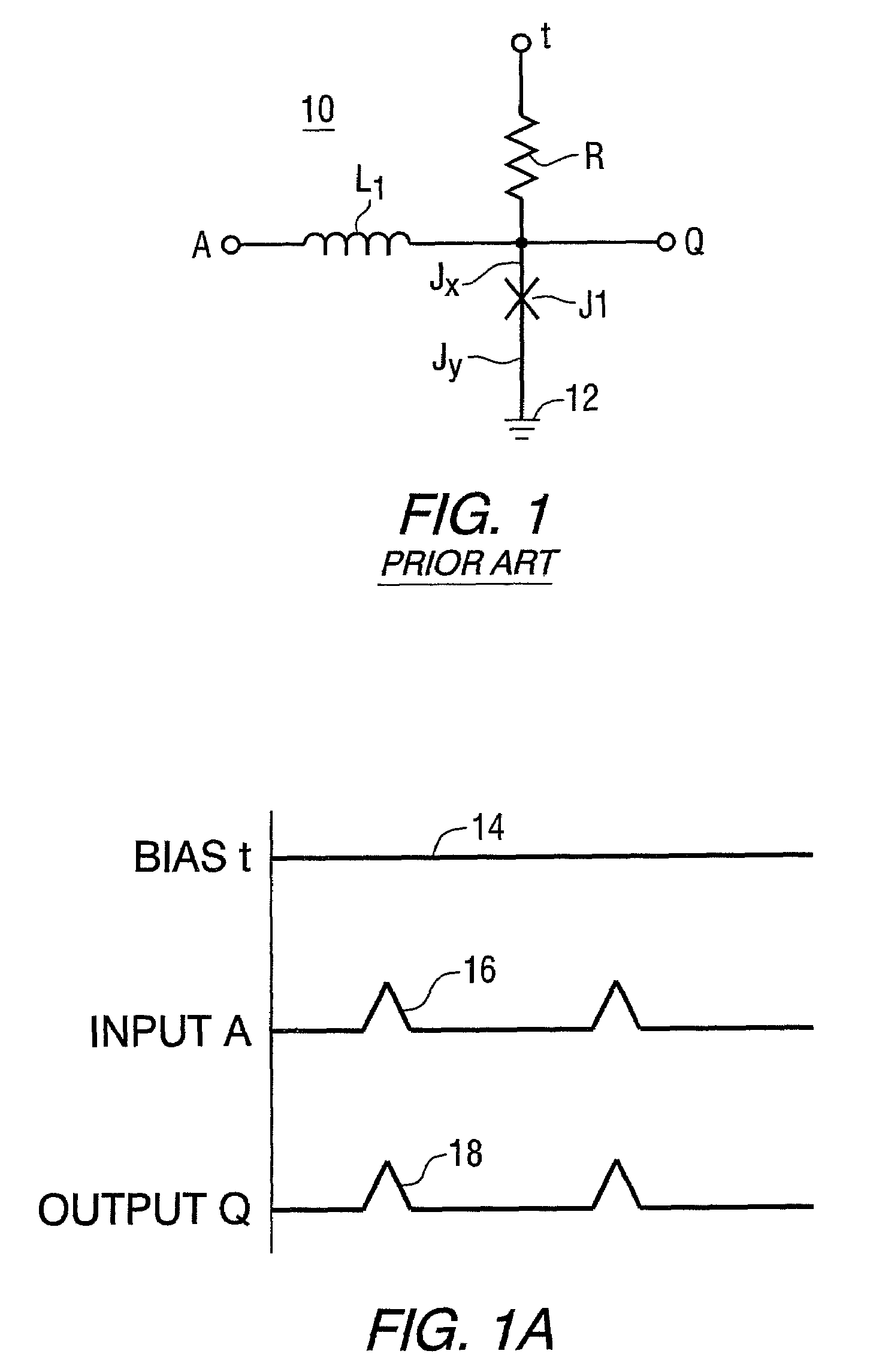

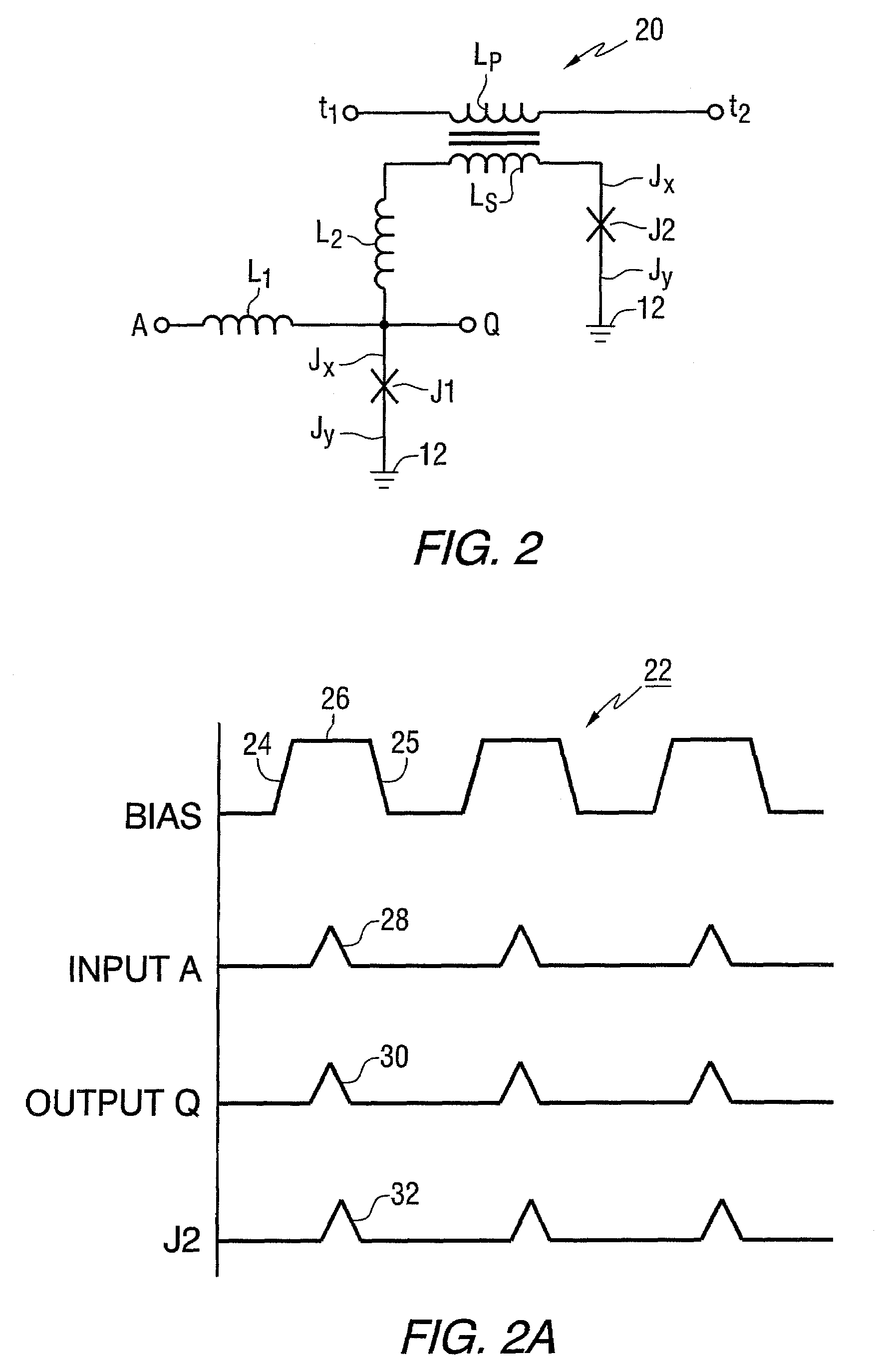

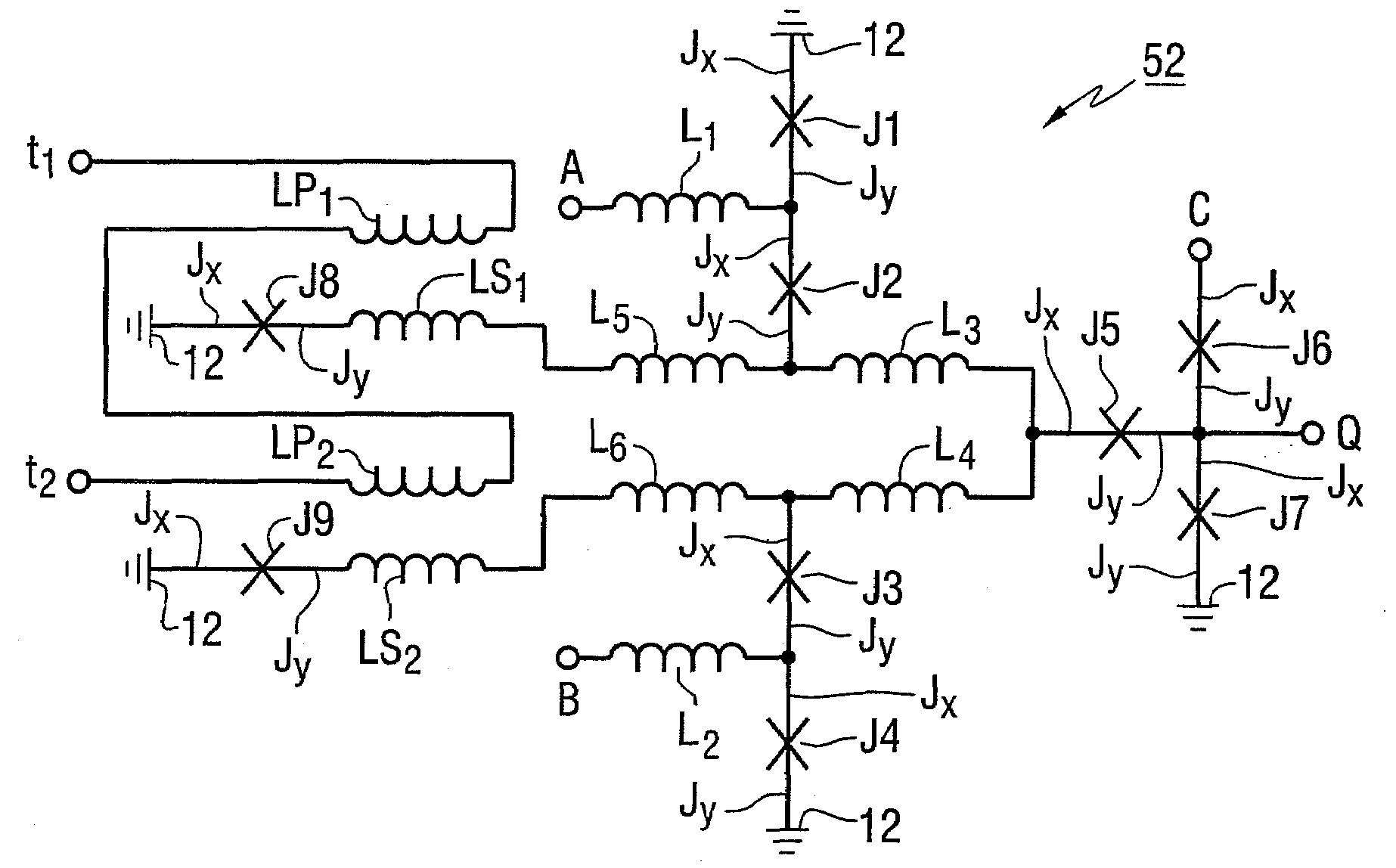

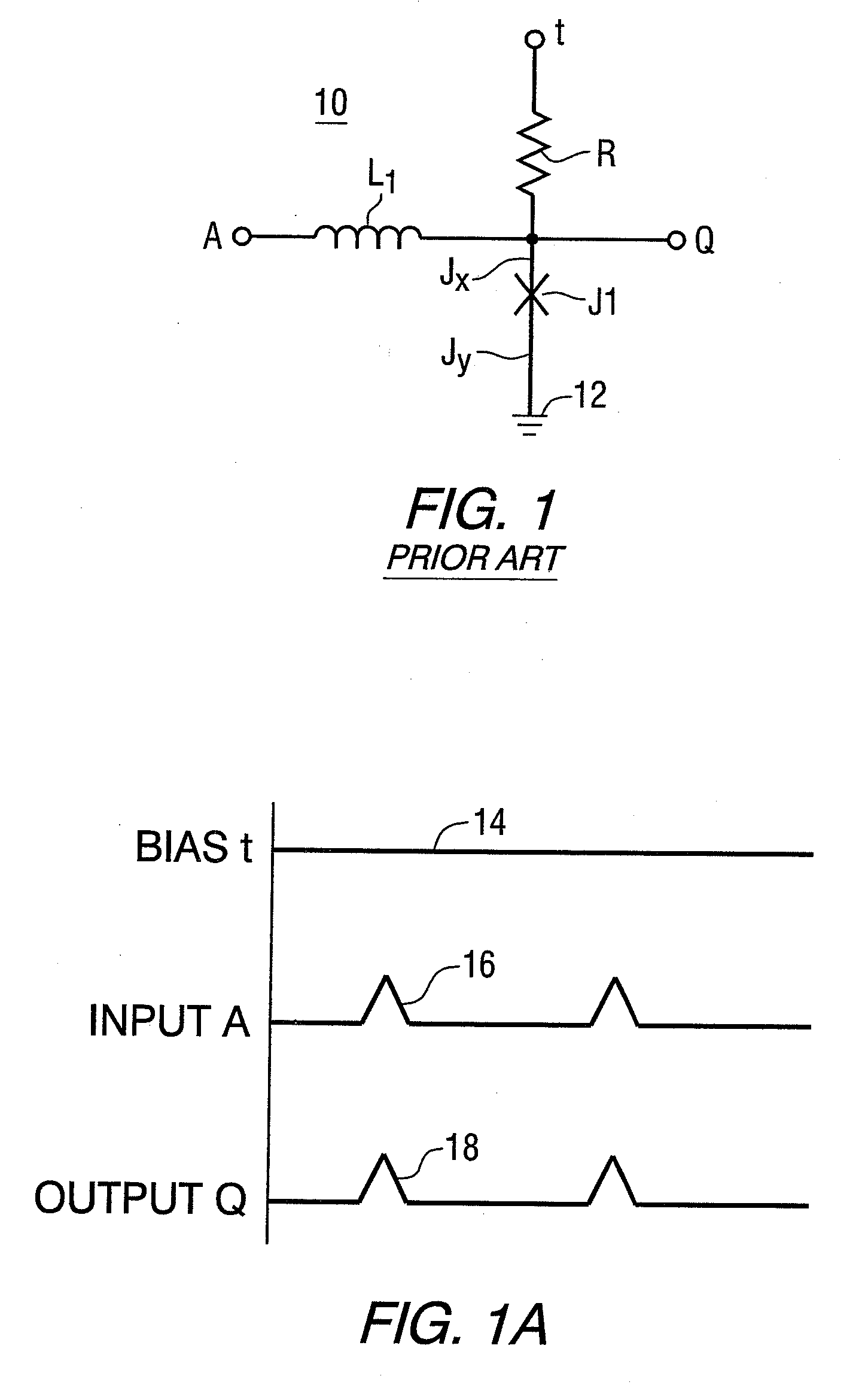

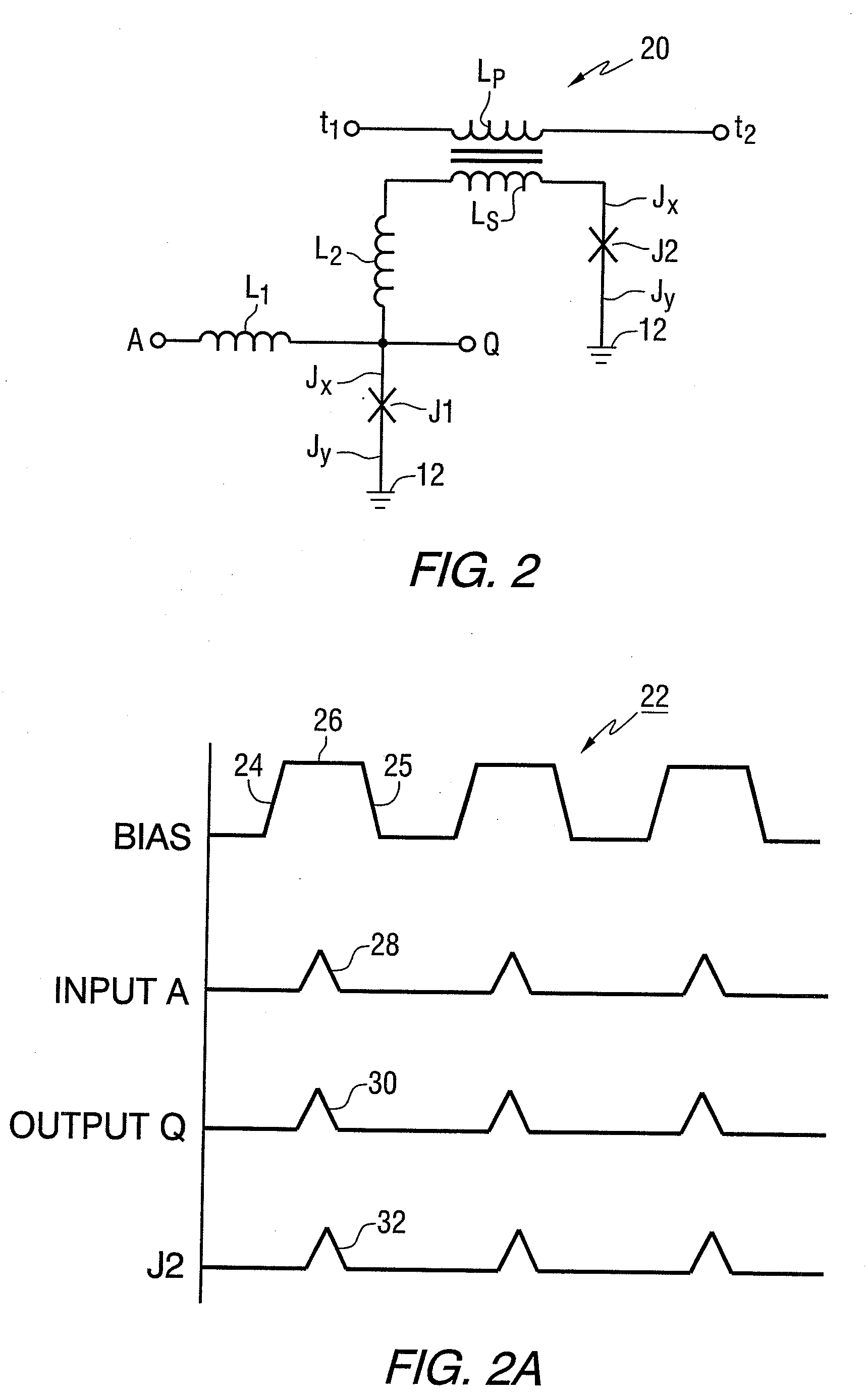

Single flux quantum circuits

ActiveUS7724020B2Reduce and eliminate unnecessary power dissipationQuantum computersPower consumption reductionQuantum circuitTransformer

Superconducting single flux quantum circuits are disclosed herein, each having at least one Josephson junction which will flip when the current through it exceeds a critical current. Bias current for the Josephson junction is provided by a biasing transformer instead of a resistor. The lack of any bias resistors ensures that unwanted power dissipation is eliminated.

Owner:NORTHROP GRUMMAN SYST CORP

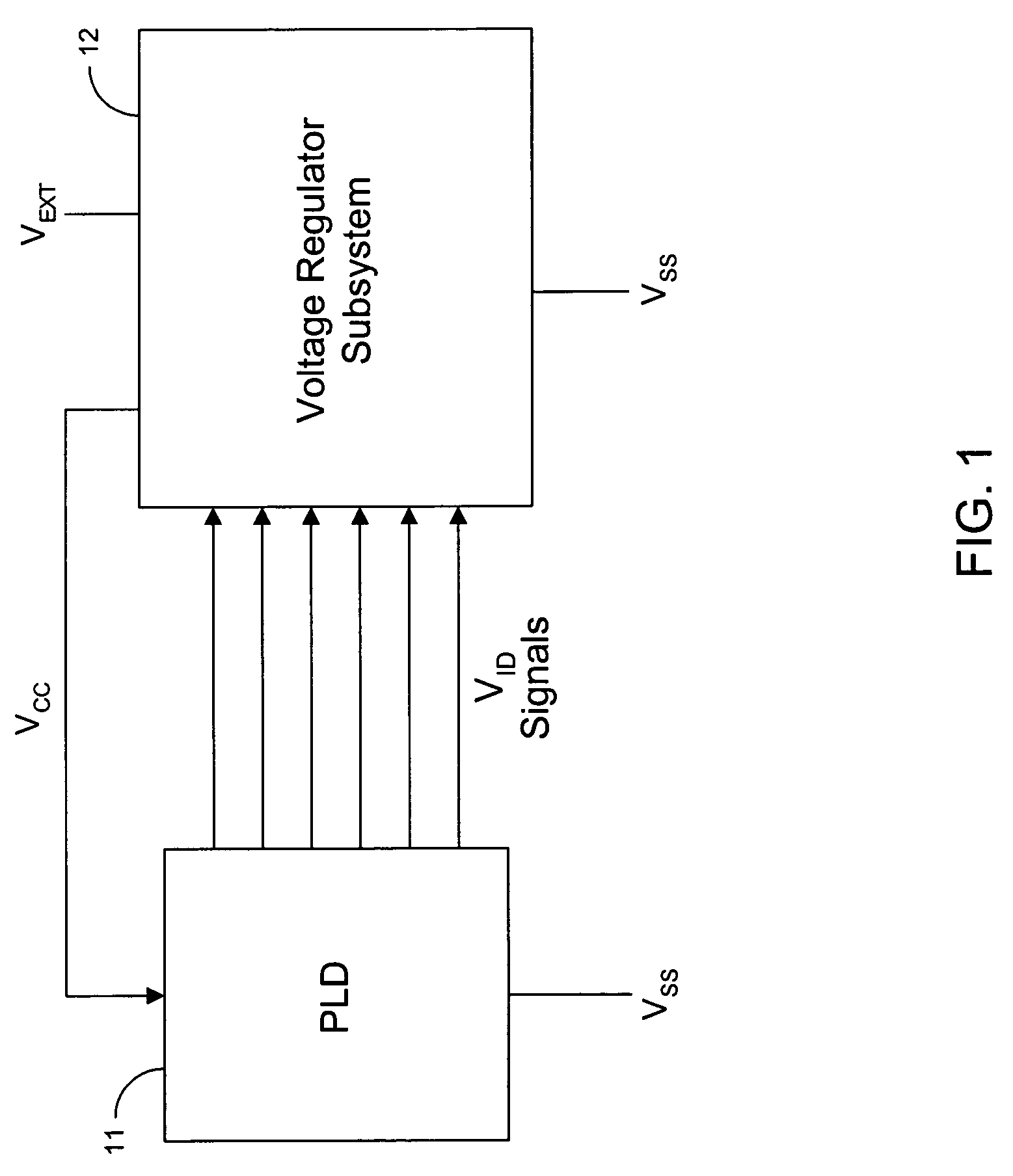

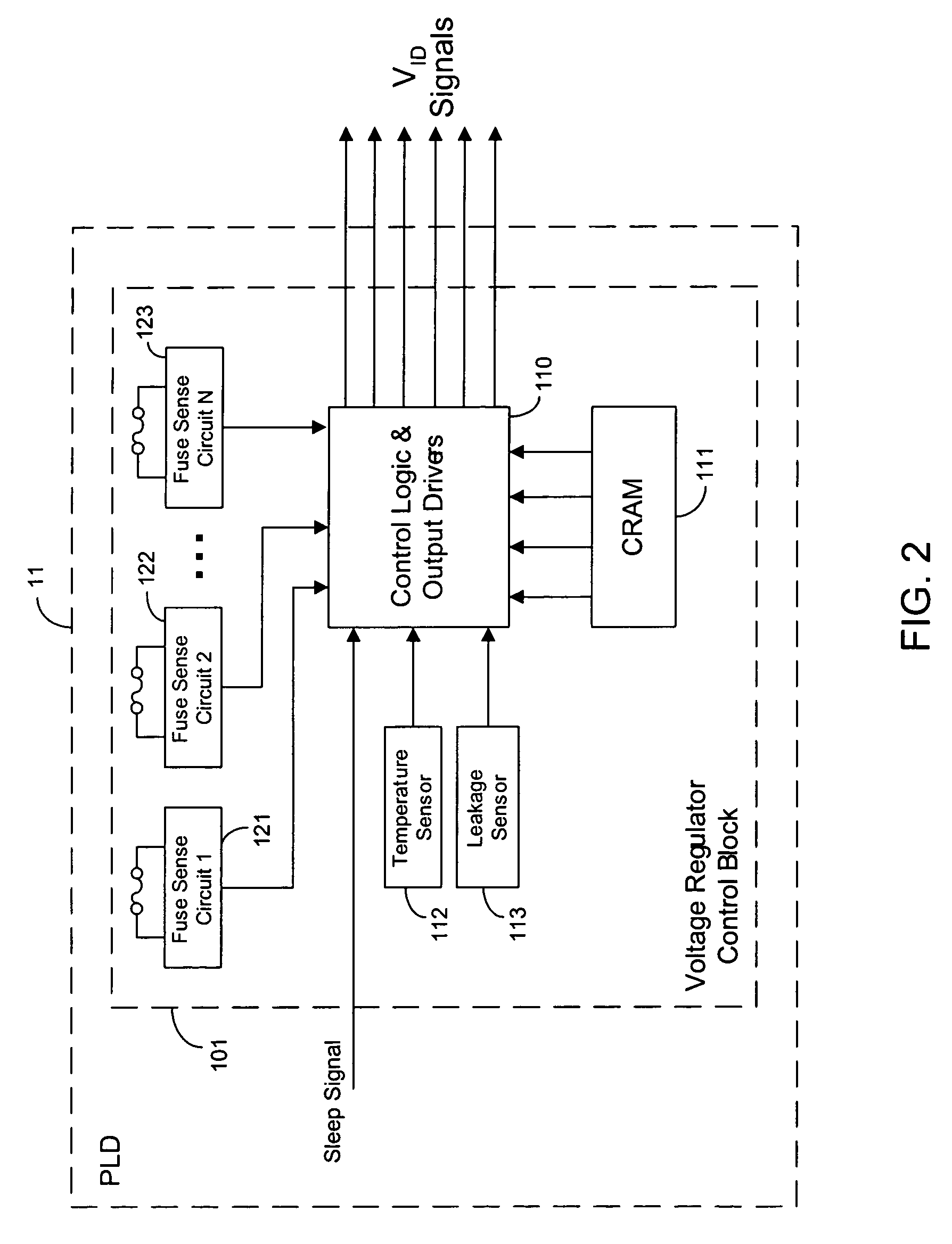

Adaptive power supply voltage regulation for programmable logic

ActiveUS7142009B1Reduce power consumptionPower consumption reductionVolume/mass flow measurementVoltage regulator moduleProgrammable logic device

Adaptive regulated power supply voltages are applied to programmable logic integrated circuits. Control circuitry in a programmable logic IC generates control signals that are transmitted to an external voltage regulator. The voltage regulator generates one or more power supply voltages in response to the control signals. The values of control signals determine the target values of the supply voltages. The control circuitry can adapt the power supply voltages to compensate for temperature and process variations on the IC. The power supply voltages can be programmed by a manufacturer or by a user to achieve desired target values. The control circuitry can also put a programmable logic IC into a sleep mode by dropping the high supply voltage to a low value to reduce power consumption during periods of low usage.

Owner:TAHOE RES LTD

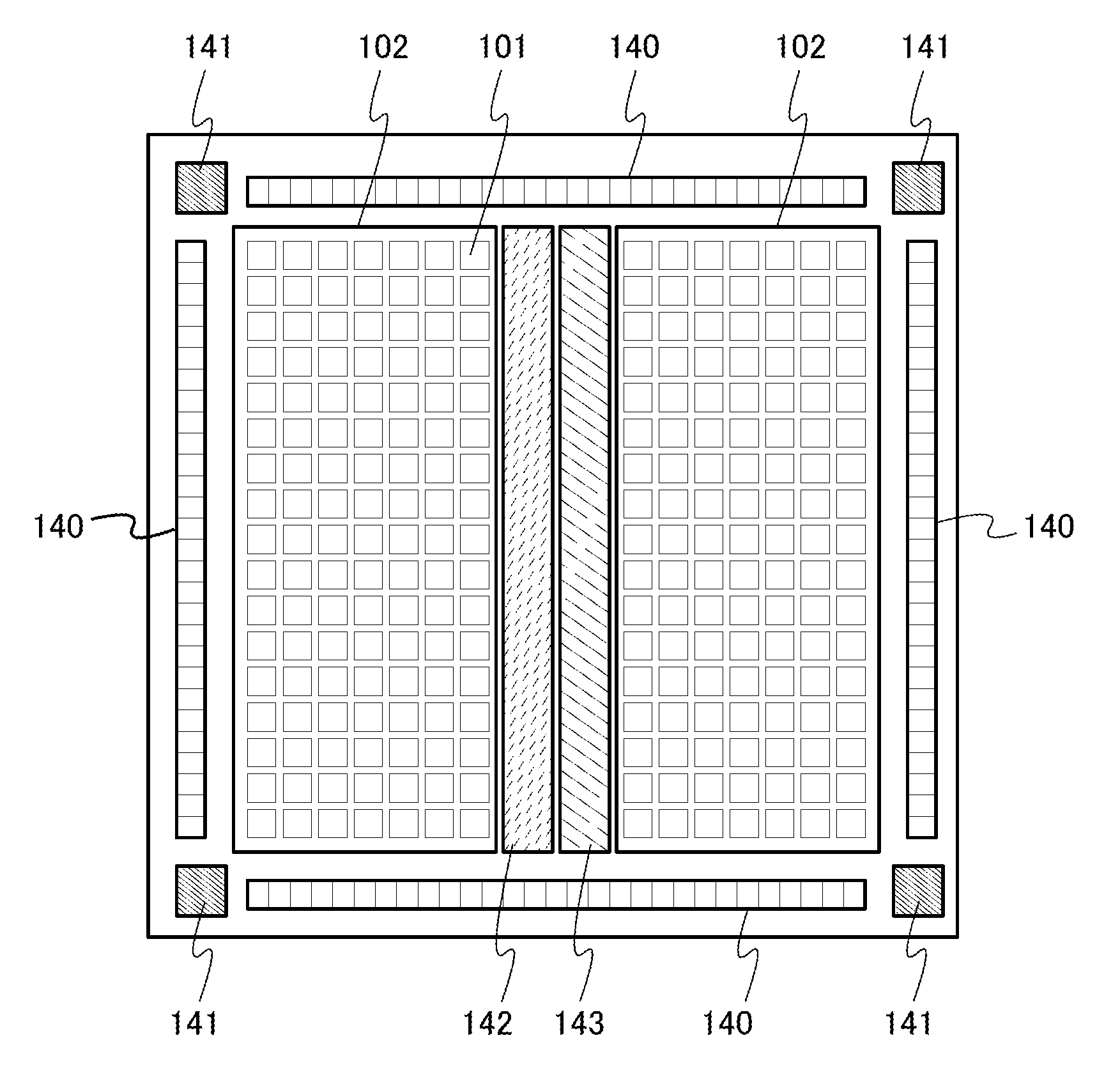

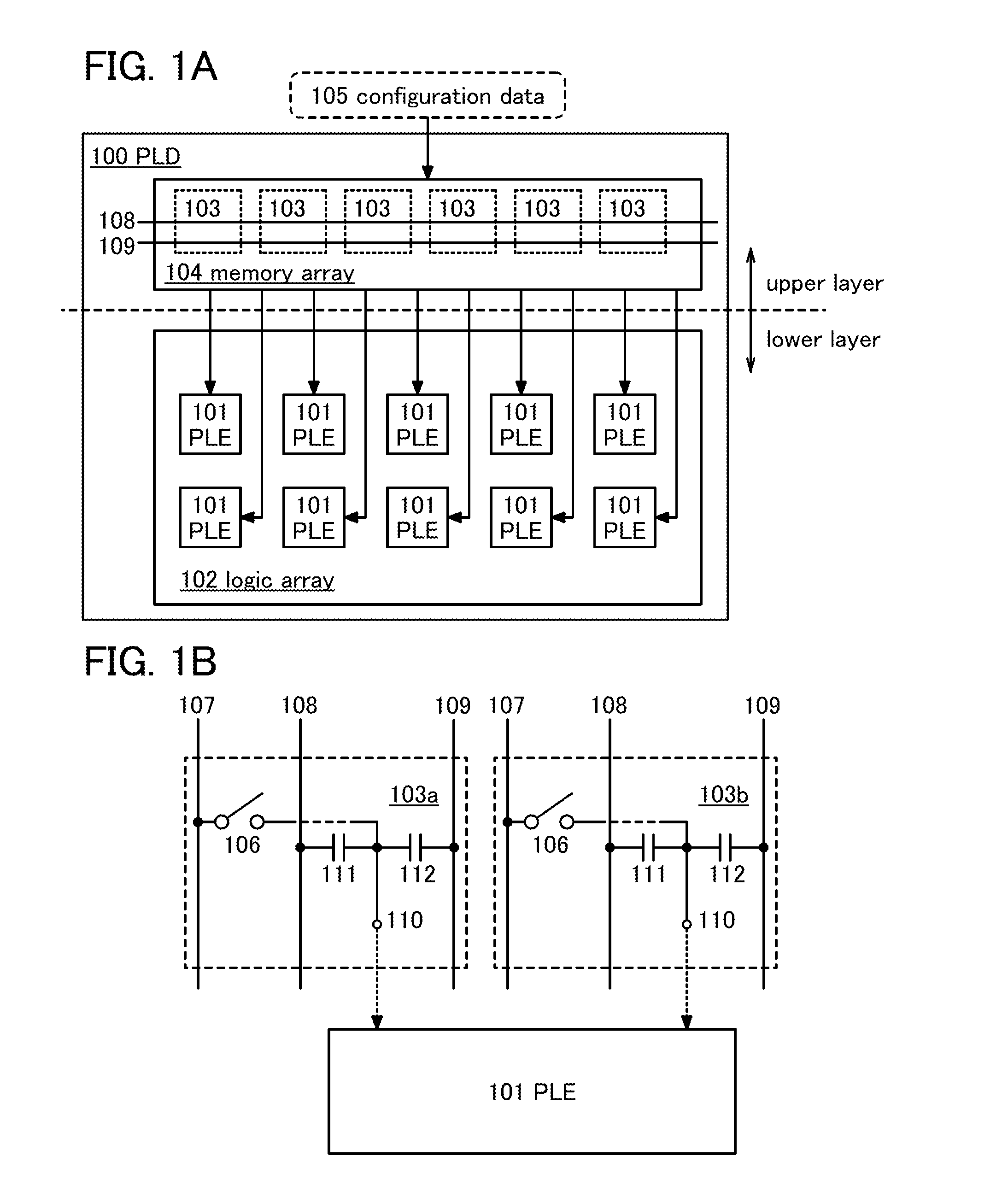

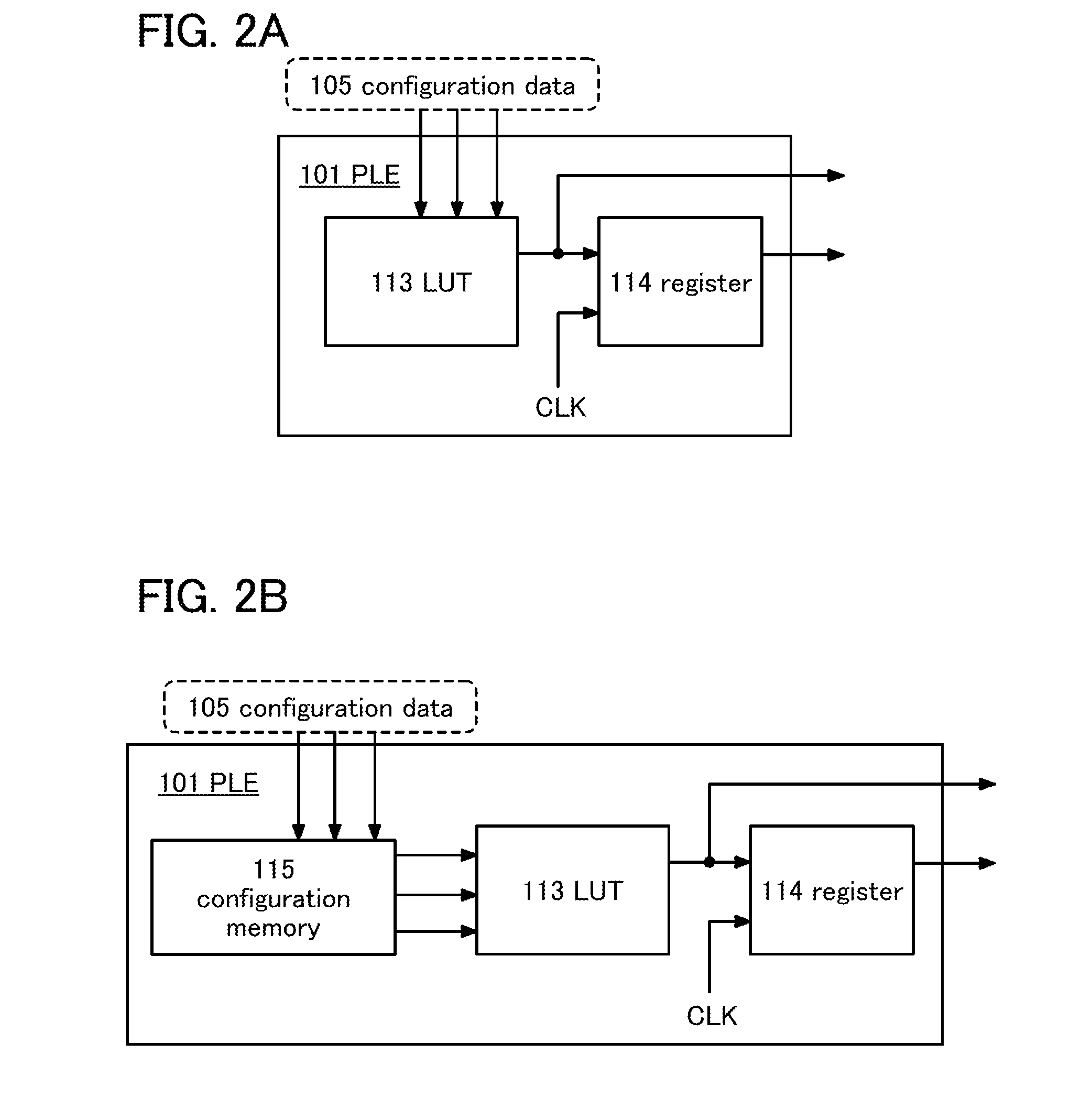

Programmable logic device and method for manufacturing semiconductor device

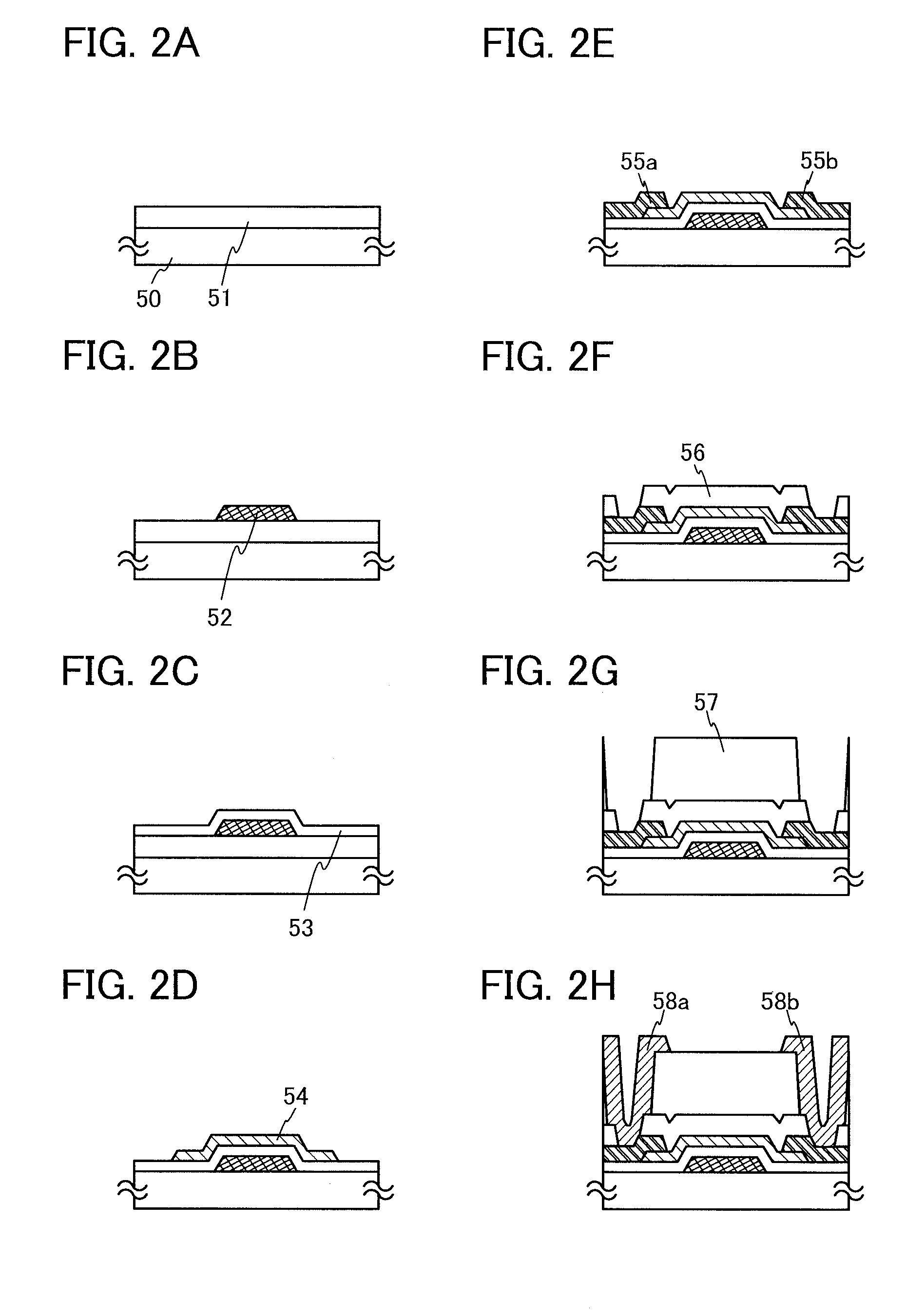

ActiveUS20130207170A1Reduce in quantityAccurate estimateTransistorPower consumption reductionCapacitanceProgrammable logic device

To provide a programmable logic device in which the number of elements per bit in a memory array can be reduced and with which power consumption or operation frequency can be estimated accurately at a testing stage. Provided is a programmable logic device including a plurality of programmable logic elements and a memory array which stores configuration data that determines logic operation executed in the plurality of programmable logic elements. The memory array includes a plurality of memory elements. The memory element includes a node which establishes electrical connection between the programmable logic element and the memory array, a switch for supplying charge whose amount is determined by the configuration data to the node, holding the charge in the node, or releasing the charge from the node, and a plurality of wirings. Capacitance is formed between the node and the wiring.

Owner:SEMICON ENERGY LAB CO LTD

Single flux quantum circuits

ActiveUS20090153180A1Reduce and eliminate unnecessary power dissipationQuantum computersPower consumption reductionQuantum circuitTransformer

Superconducting single flux quantum circuits are disclosed herein, each having at least one Josephson junction which will flip when the current through it exceeds a critical current. Bias current for the Josephson junction is provided by a biasing transformer instead of a resistor. The lack of any bias resistors ensures that unwanted power dissipation is eliminated.

Owner:NORTHROP GRUMMAN SYST CORP

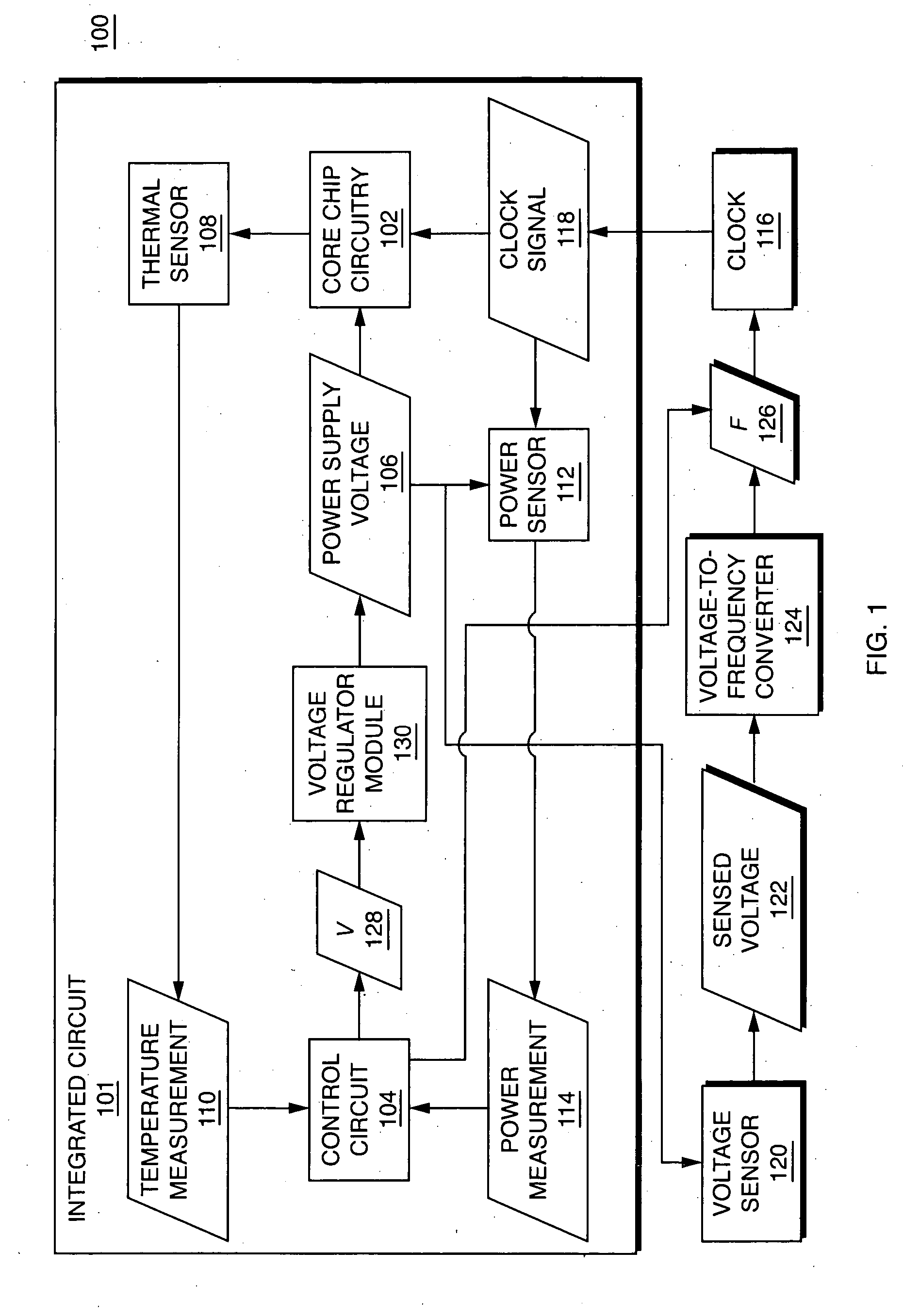

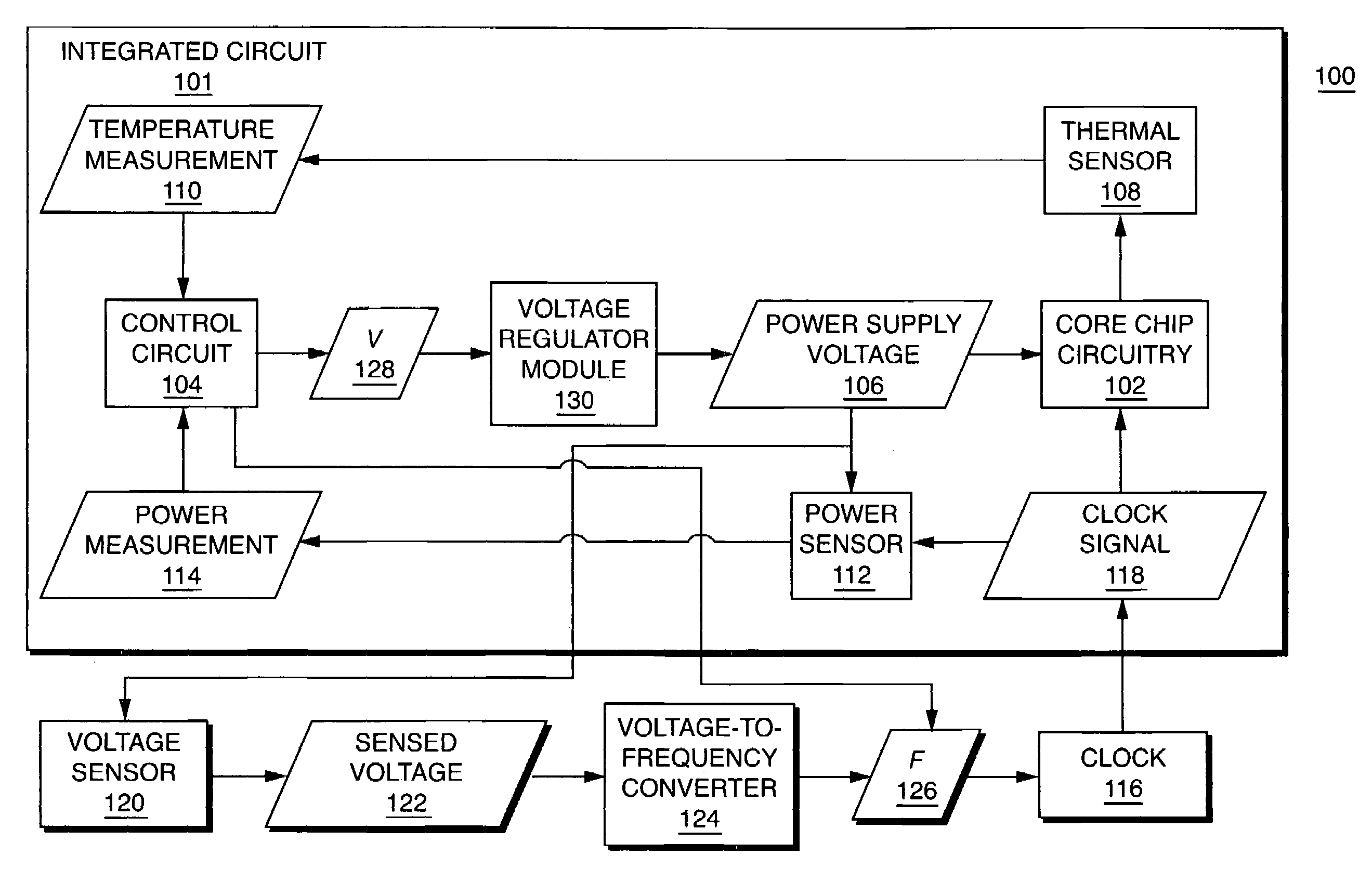

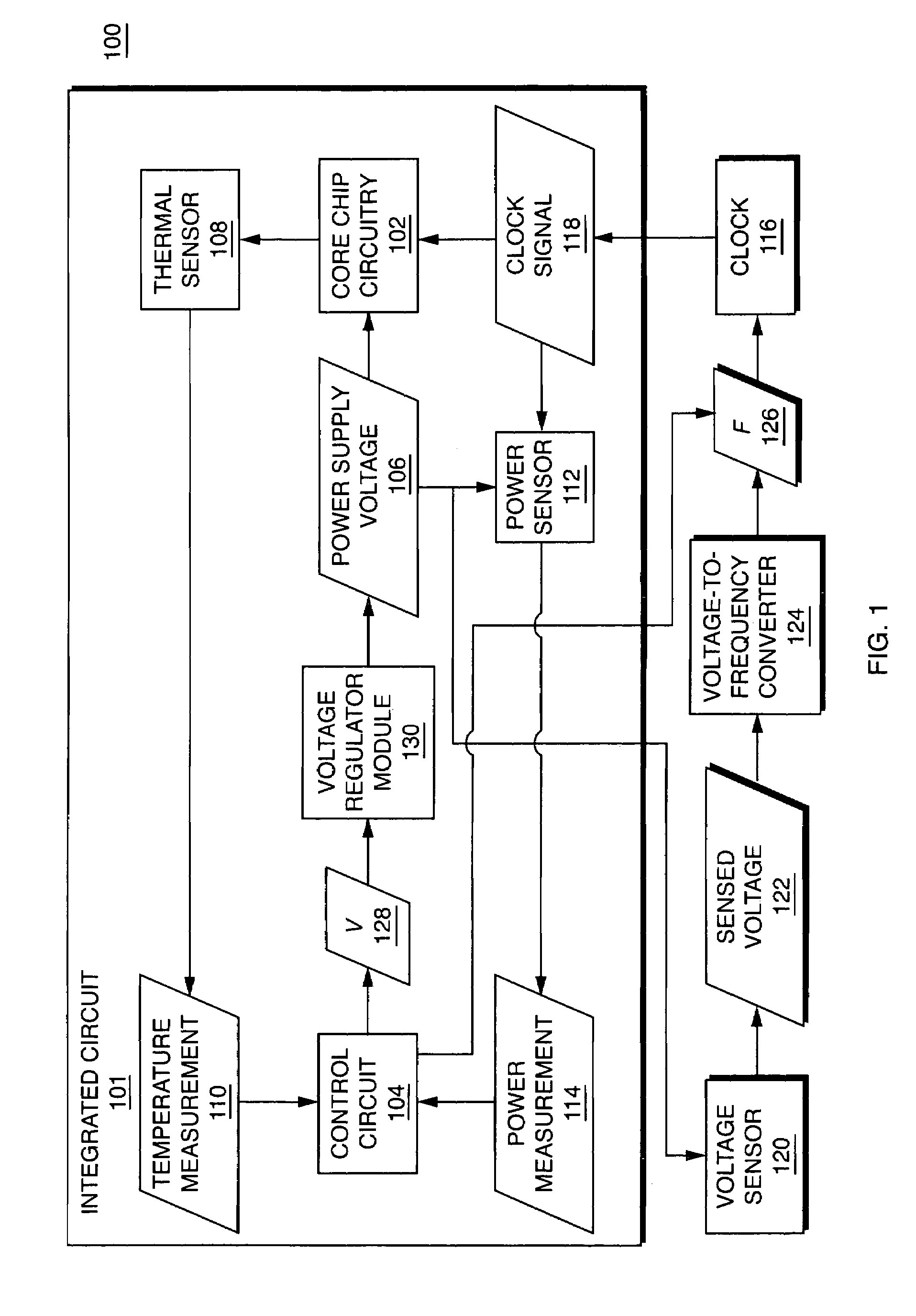

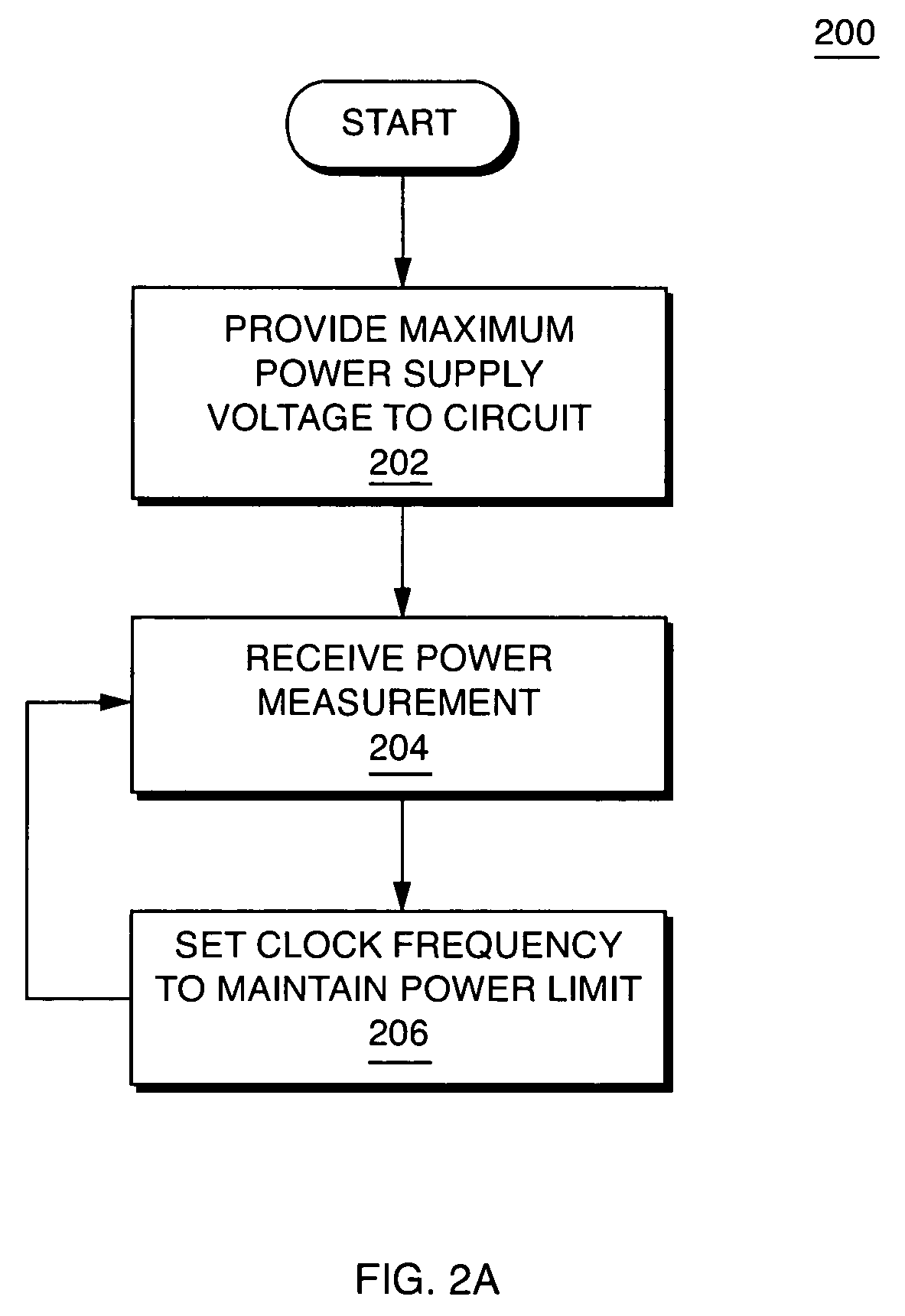

Voltage modulation for increased reliability in an integrated circuit

Techniques are disclosed for increasing reliability of an integrated circuit. In one embodiment, an integrated circuit includes core chip circuitry. The integrated circuit includes means for increasing a power supply voltage V provided to the core chip circuitry, such as by increasing the voltage V to a maximum value. The integrated circuit also includes means for identifying a clock frequency F for which F<Pmax / (CV2), where C is a switching capacitance and where Pmax is a predetermined maximum power consumption of the core chip circuitry. The integrated circuit also includes means for providing a clock signal having frequency F to the circuit.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

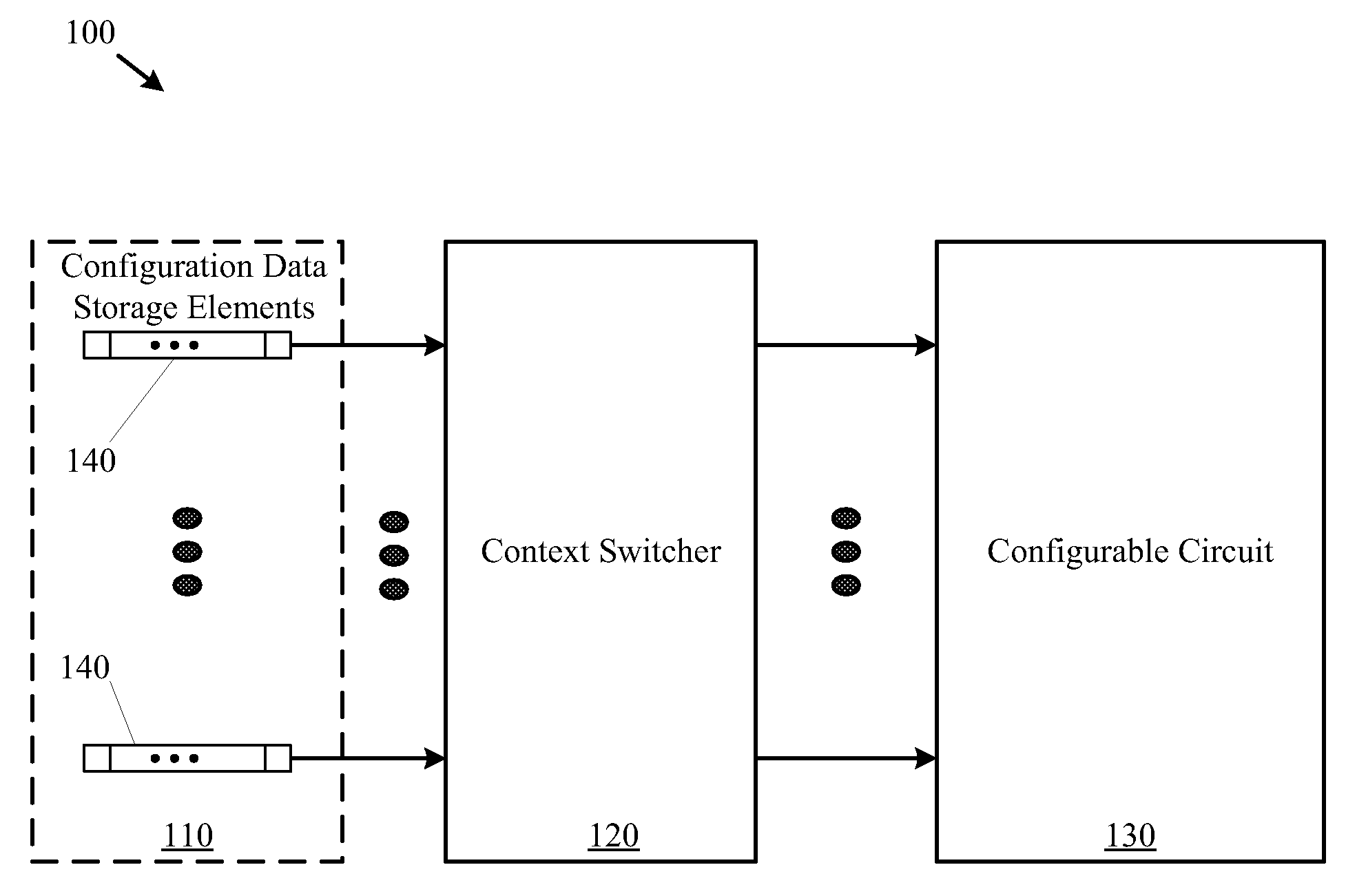

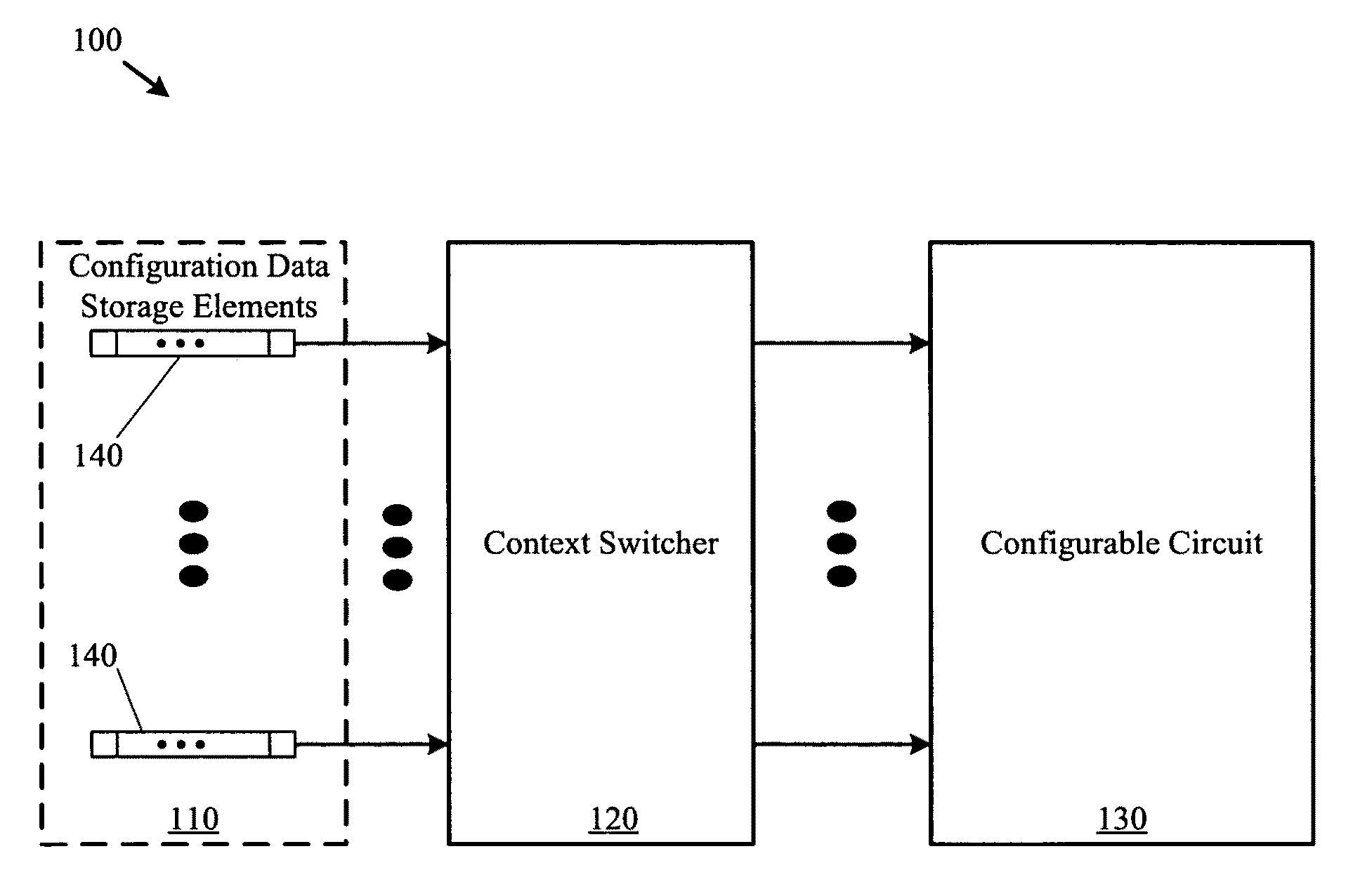

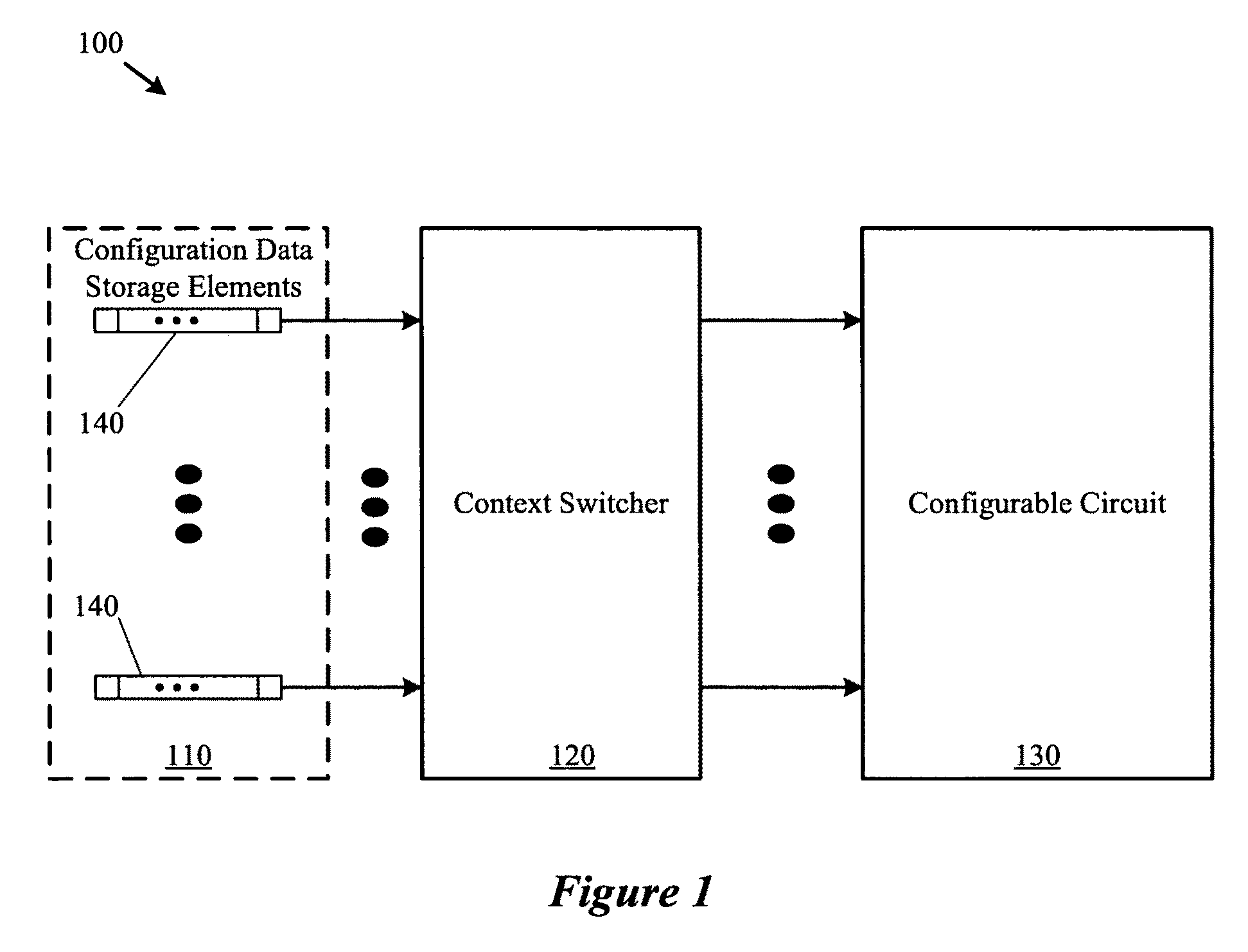

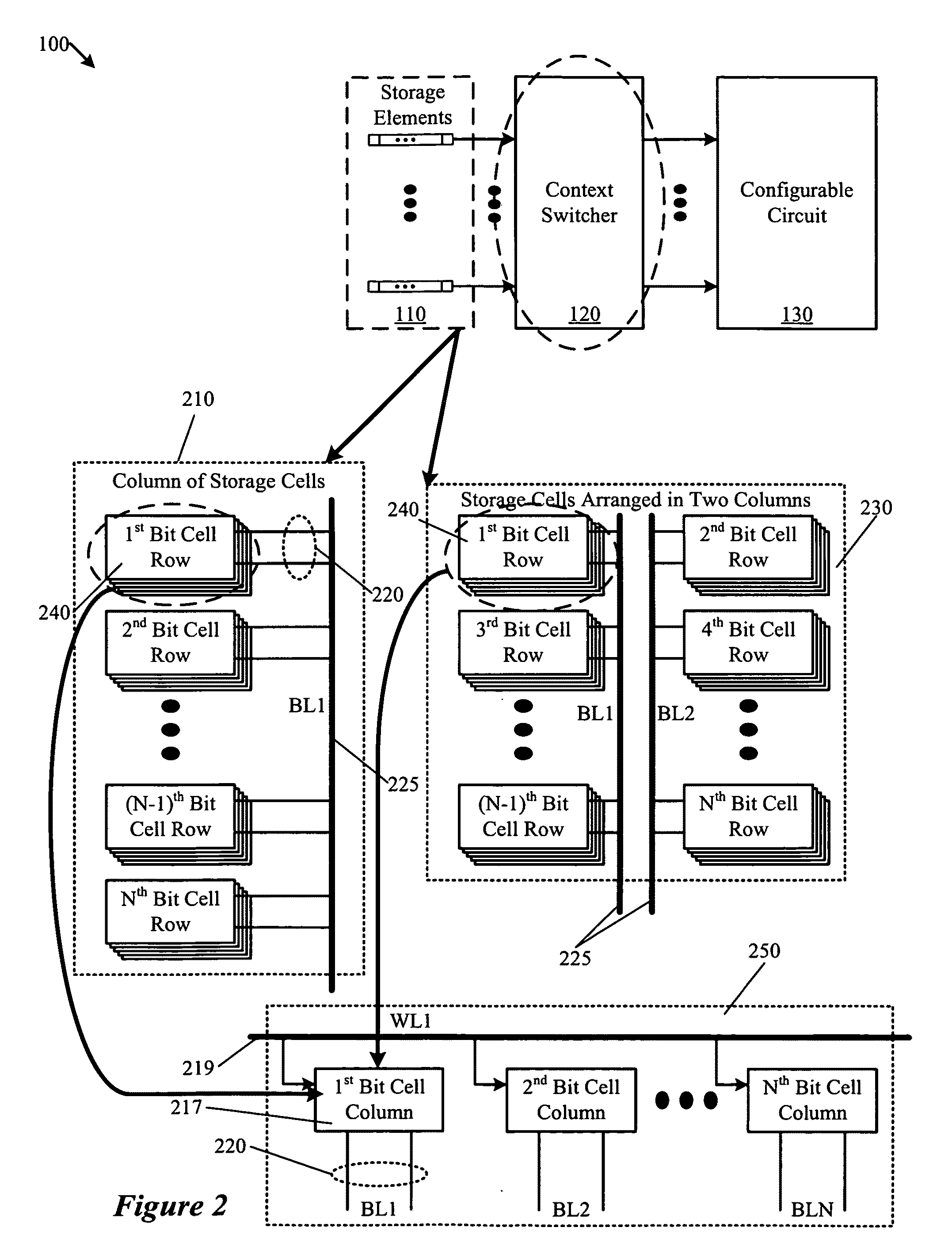

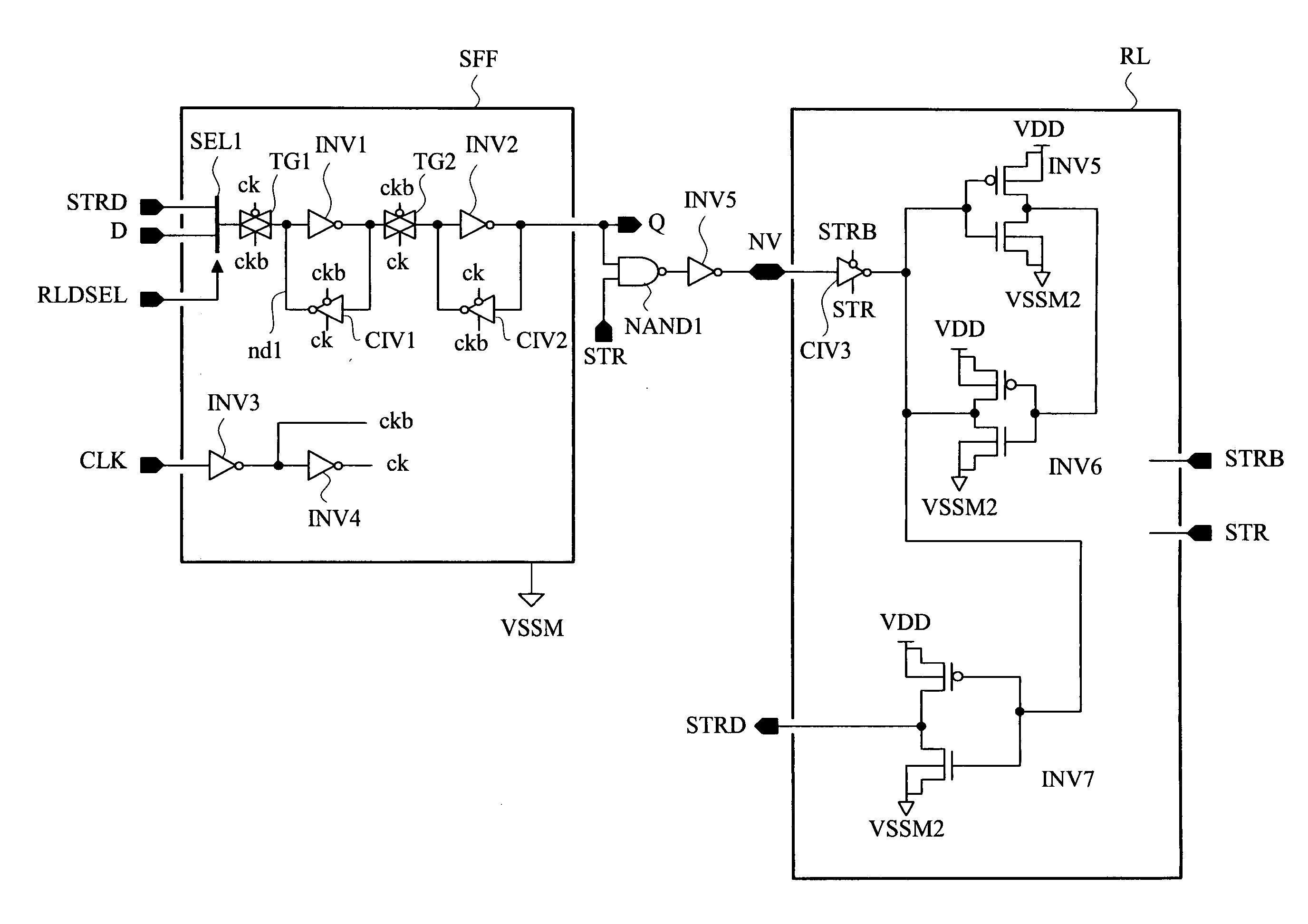

Configuration Context Switcher with a Latch

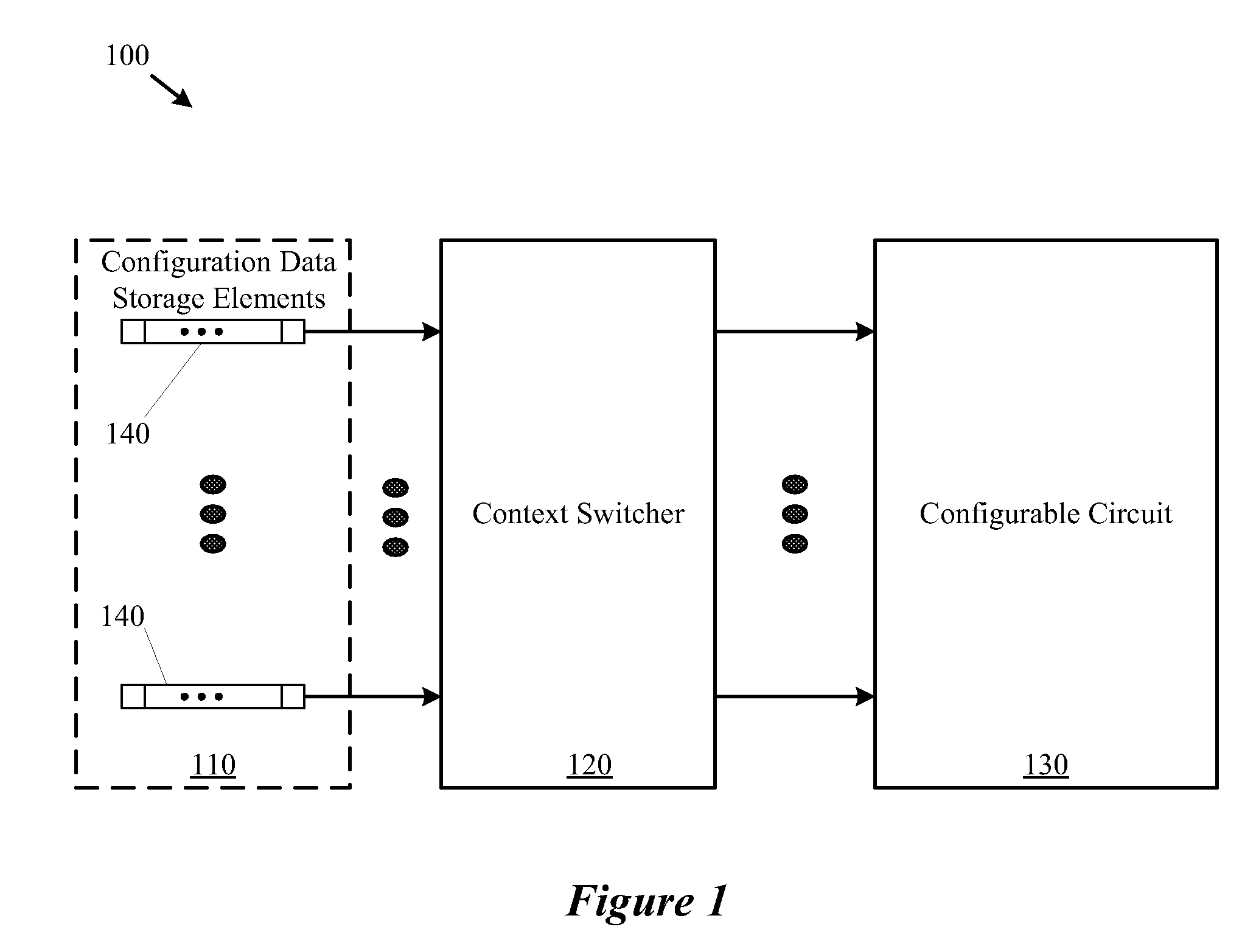

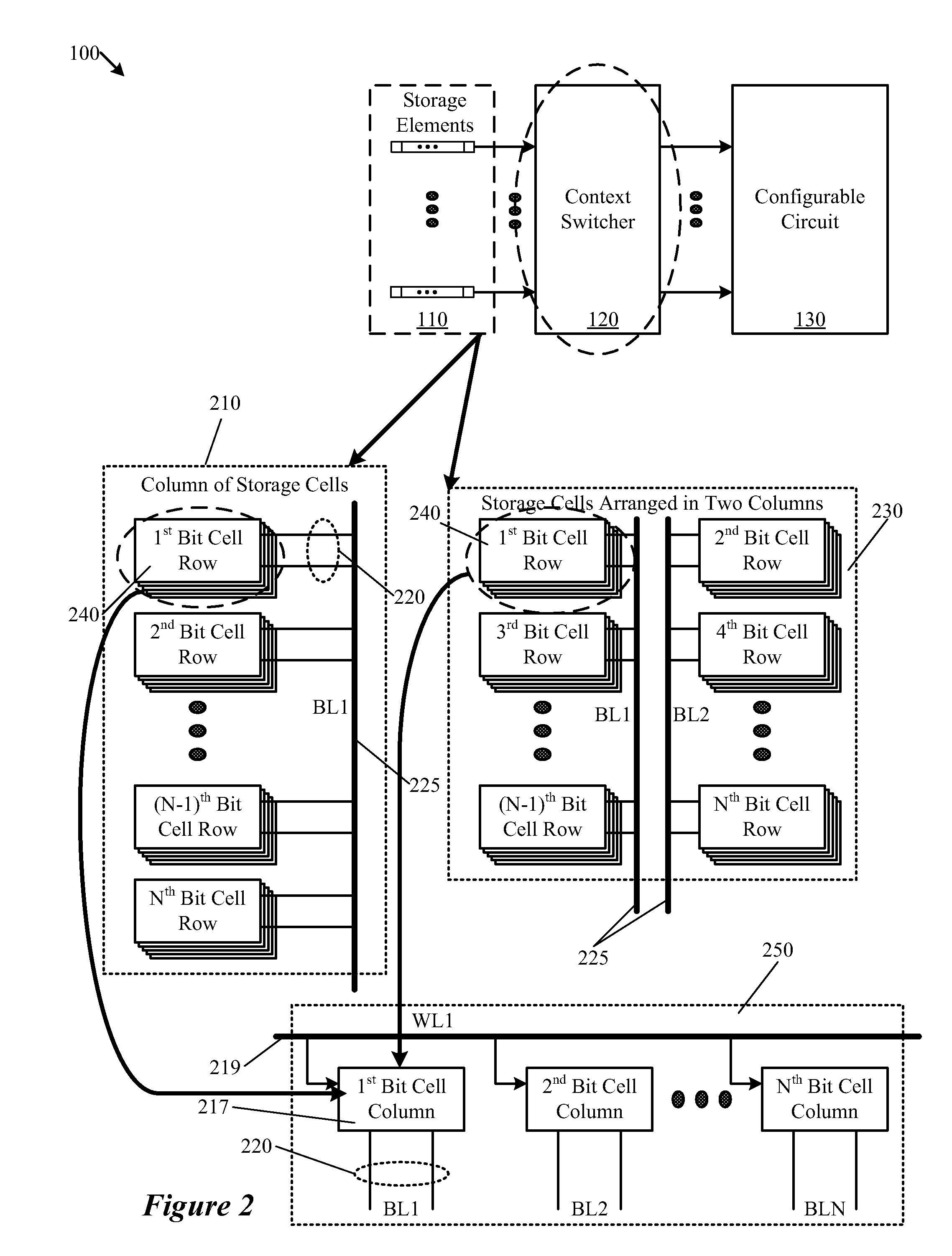

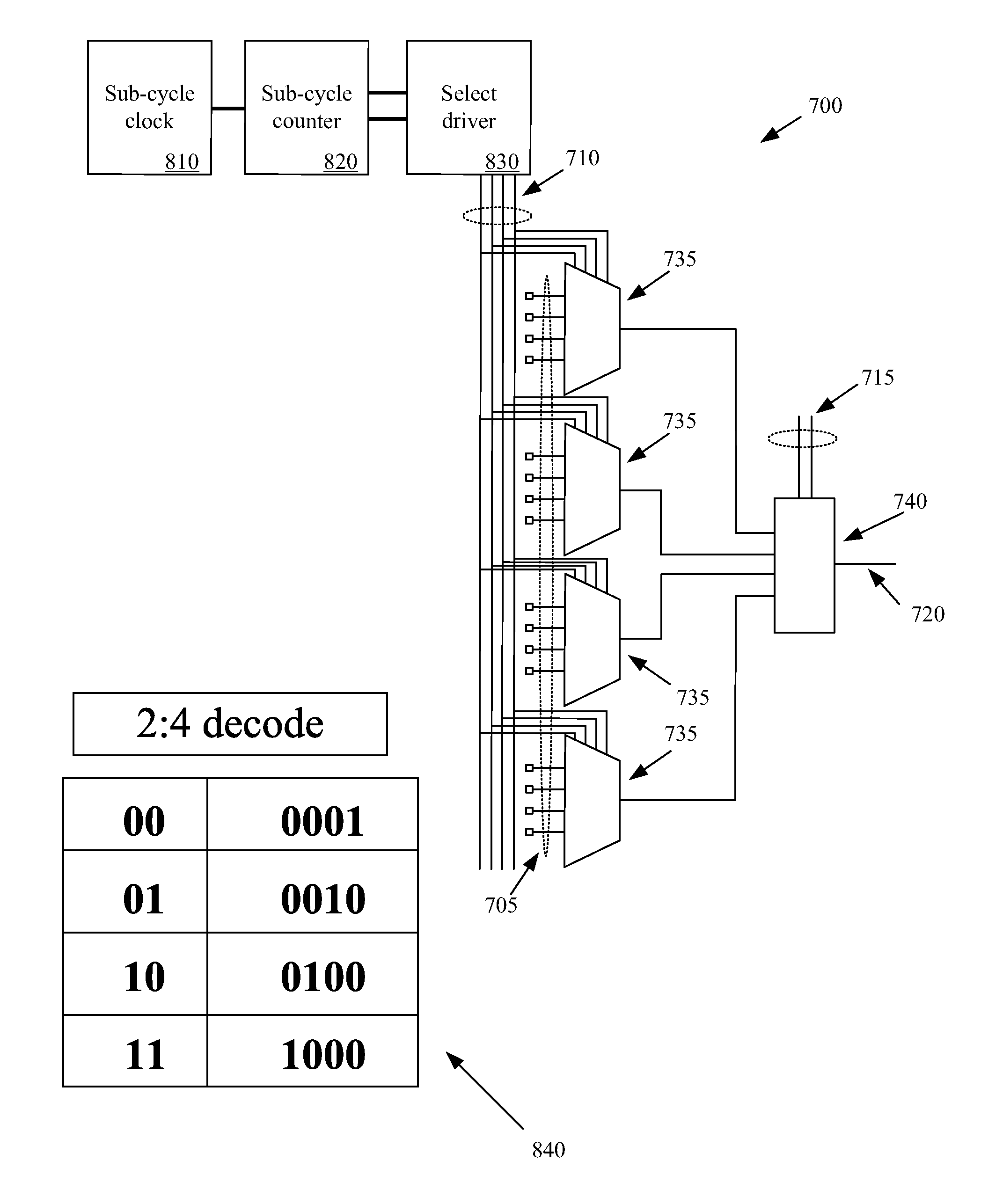

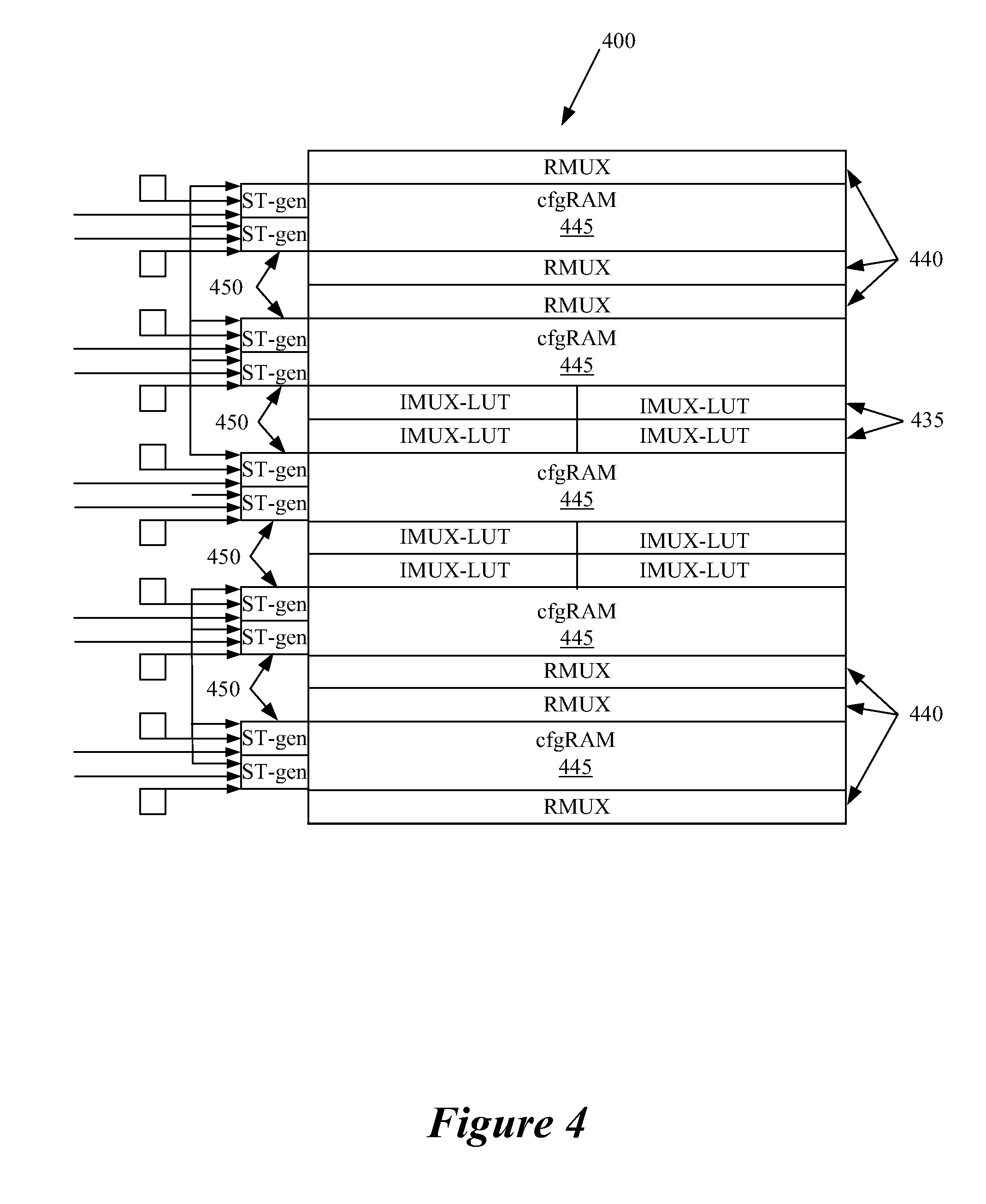

ActiveUS20090146686A1Reduce in quantityPower consumption reductionSolid-state devicesData setComputer architecture

Some embodiments provide an IC with configuration context switchers. The IC includes several configurable circuits, each of which configurably performs one of several operations at any given time, based on the configuration data set that it receives at that time. The IC includes several storage circuits for storing several configuration data sets for each of the configurable circuits. The IC also includes a context switching interconnect circuit for switchably connecting the configurable circuit to different sets of storage circuits to receive different sets of configuration data sets. The context switcher includes one or more stages for re-timing the data coming from the configuration storage elements. The stages can include interconnect circuitry or storage circuitry. Some embodiments build one of the stages in the configuration data storage elements. Some embodiments encode the configuration data bits and hence utilize a decoder in the context switcher to decode the encoded configuration data.

Owner:ALTERA CORP

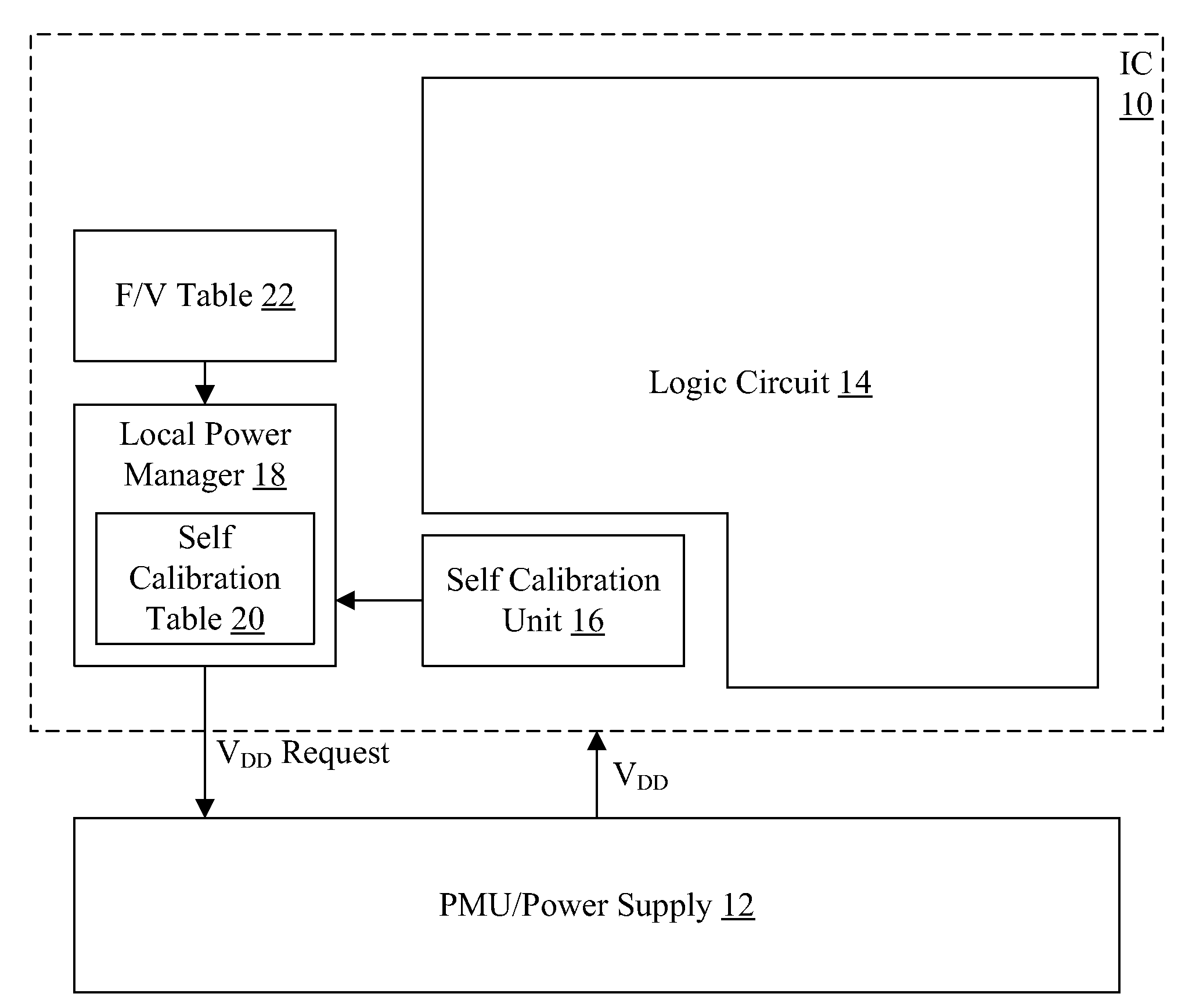

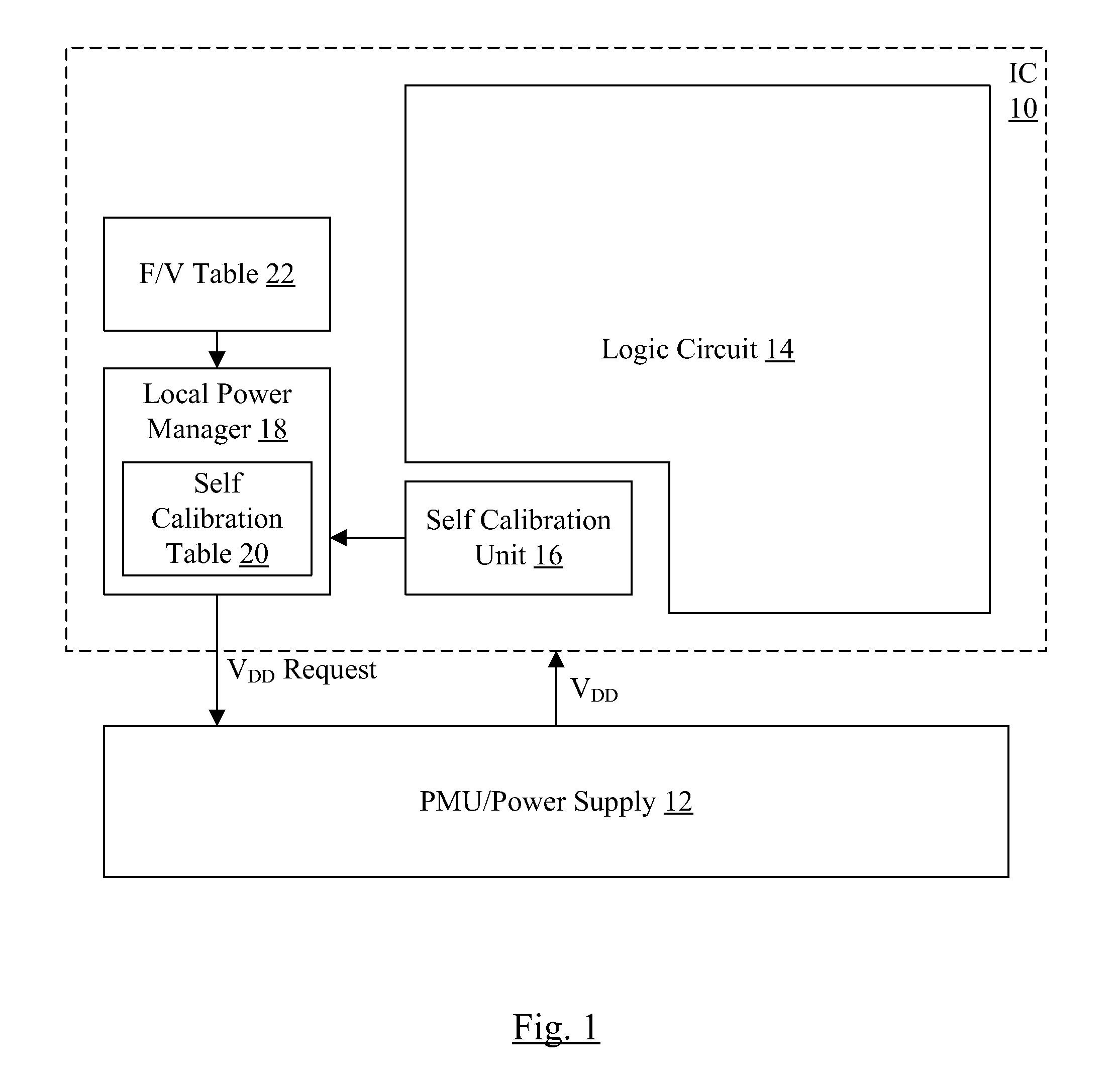

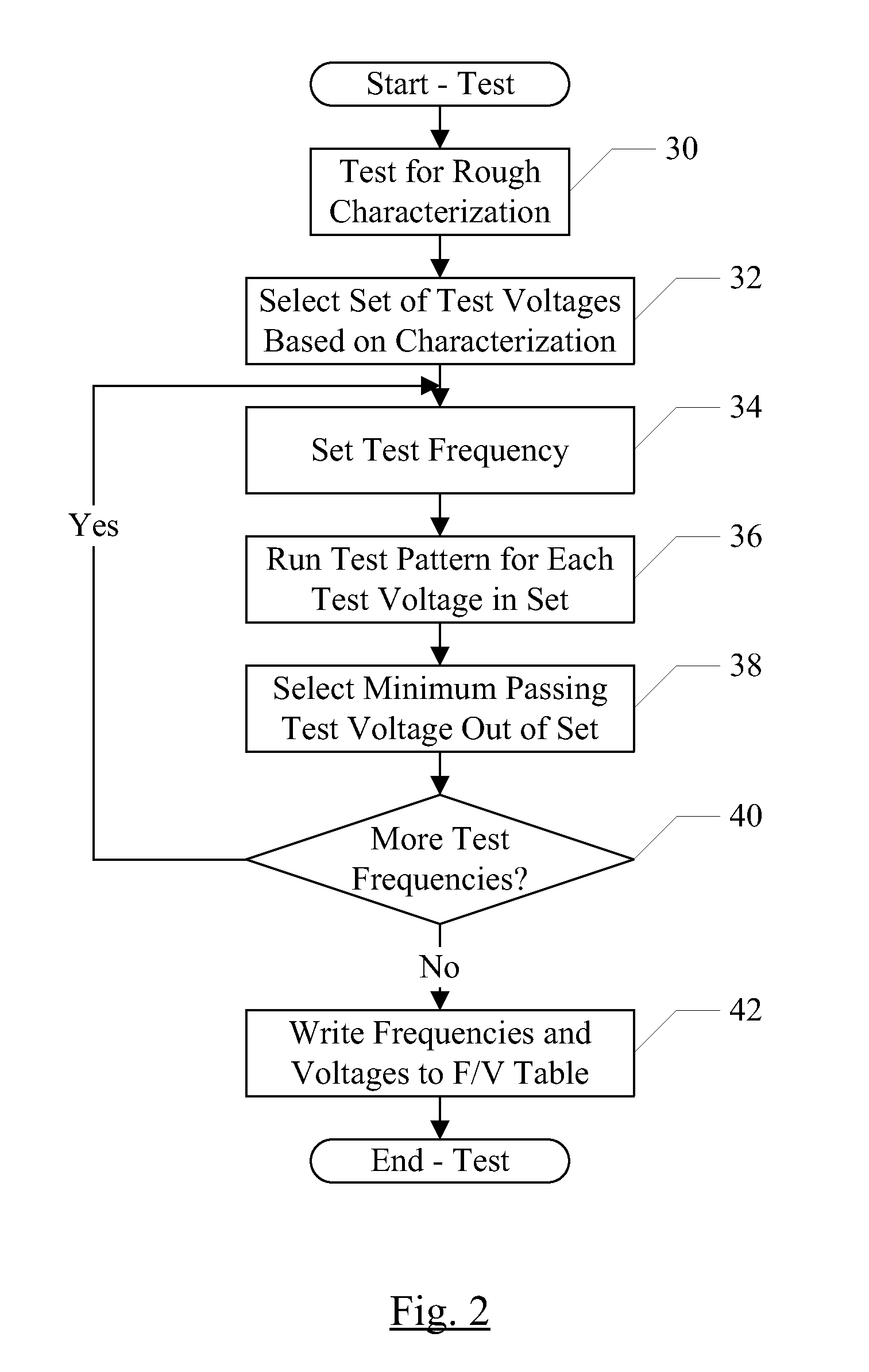

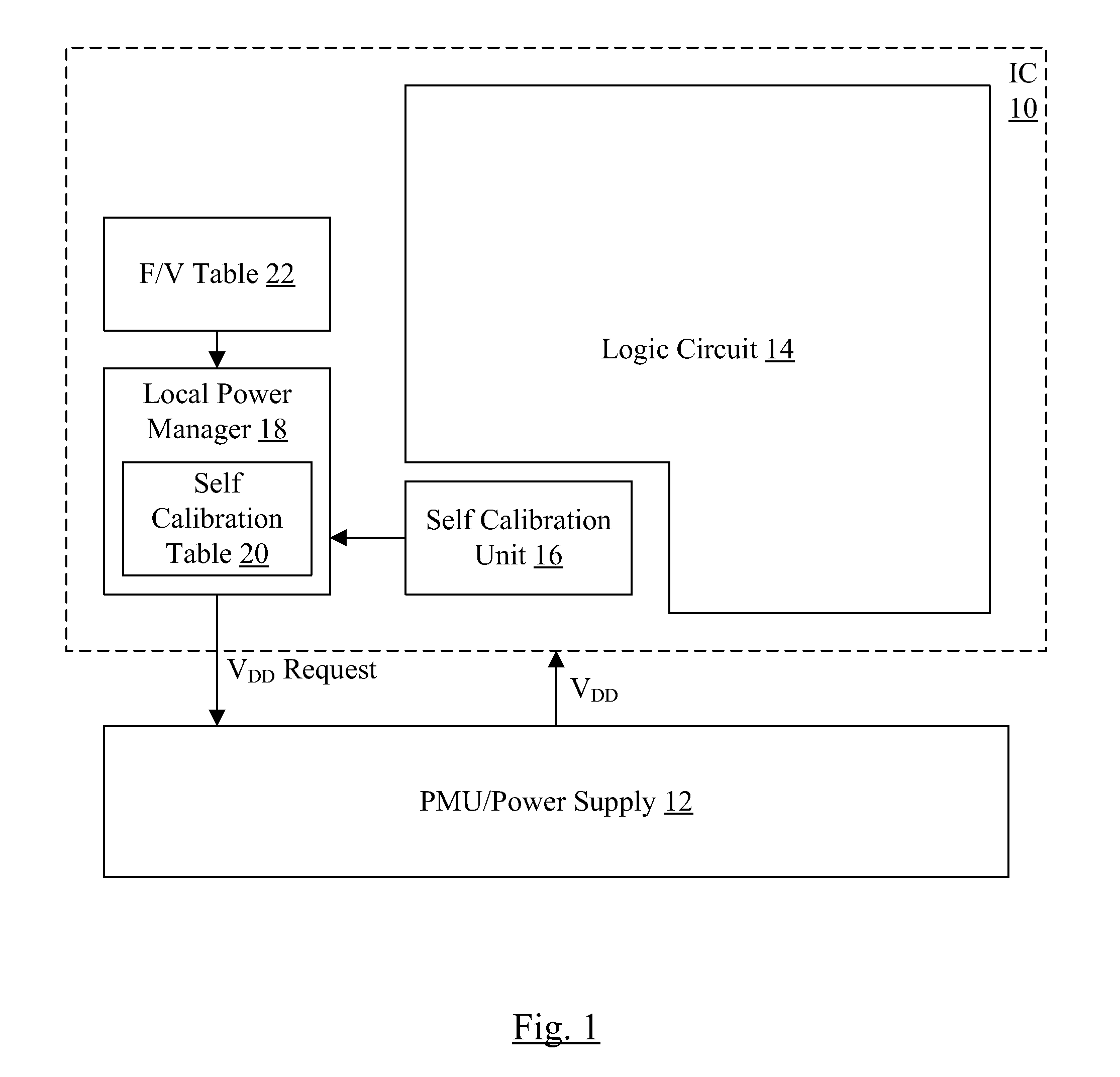

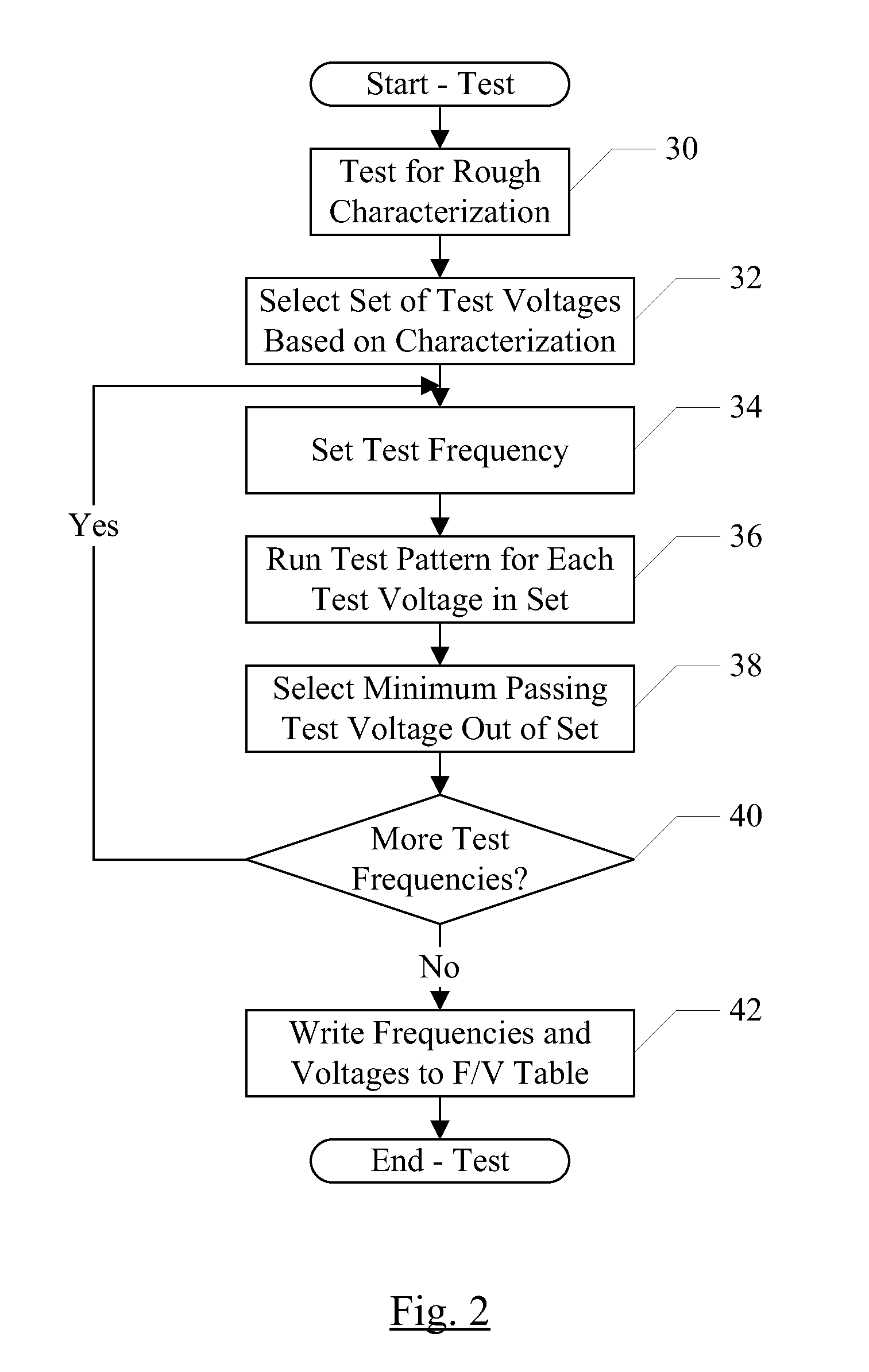

Dynamic Voltage and Frequency Management

In one embodiment, an integrated circuit includes a self calibration unit configured to iterate a test on a logic circuit in the integrated circuit at respectively lower supply voltage magnitudes until the test fails. A lowest supply voltage magnitude at which the test passes is used to generate a requested supply voltage magnitude for the integrated circuit. In an embodiment, an integrated circuit includes a series connection of logic gates physically distributed over an area of the integrated circuit, and a measurement unit configured to launch a logical transition into the series and detect a corresponding transition at the output of the series. The amount of time between the launch and the detection is used to request a supply voltage magnitude for the integrated circuit.

Owner:APPLE INC

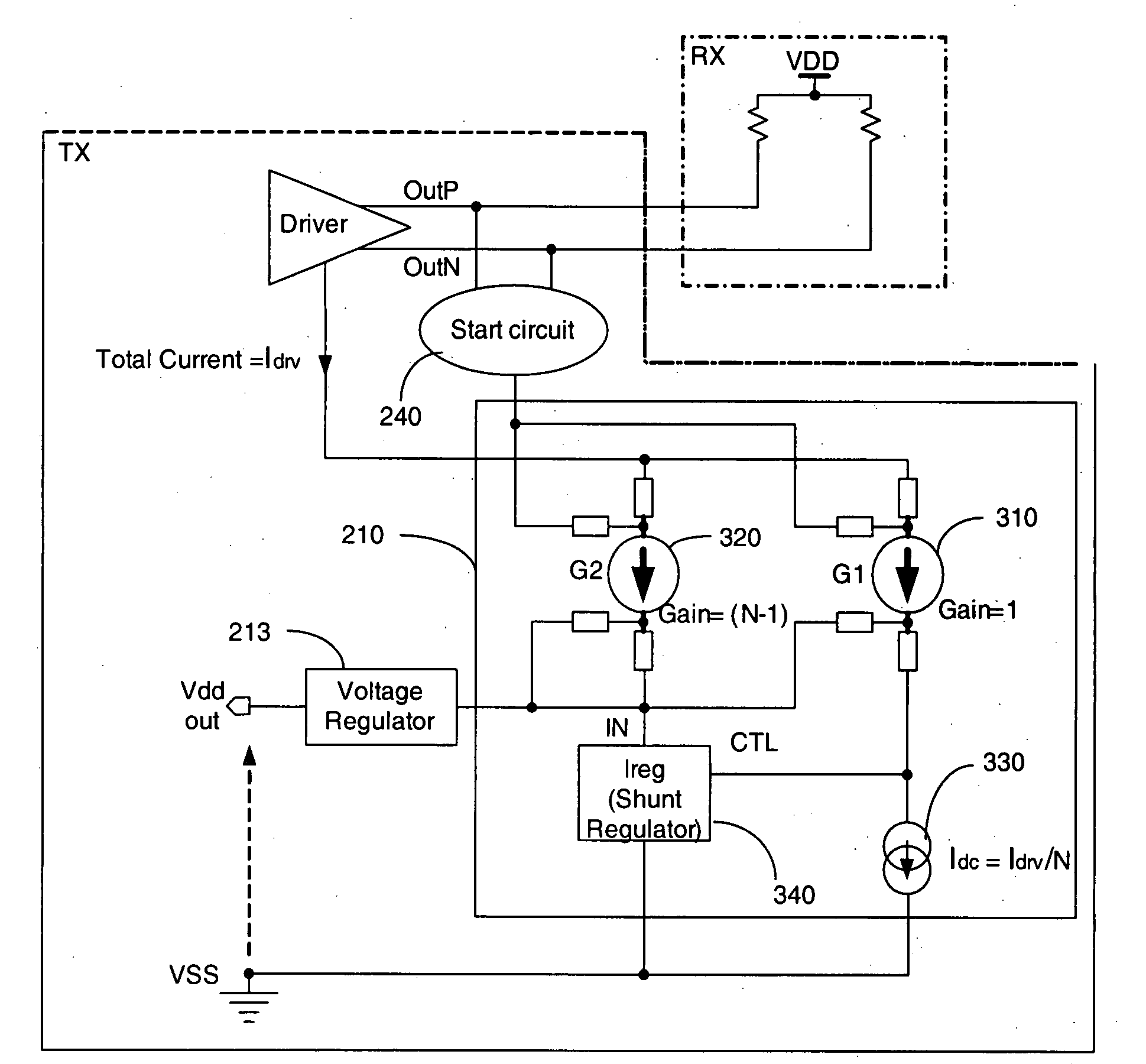

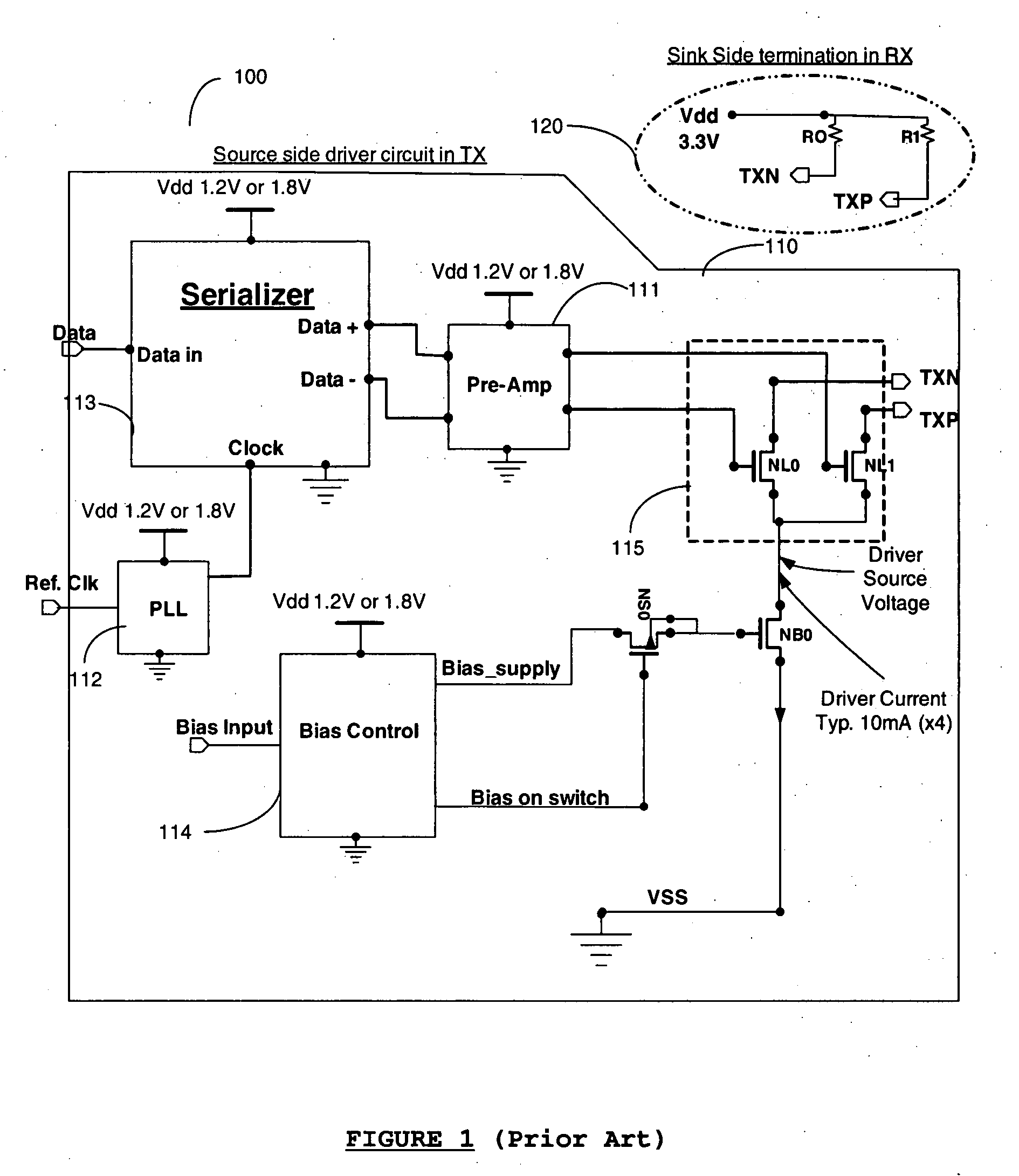

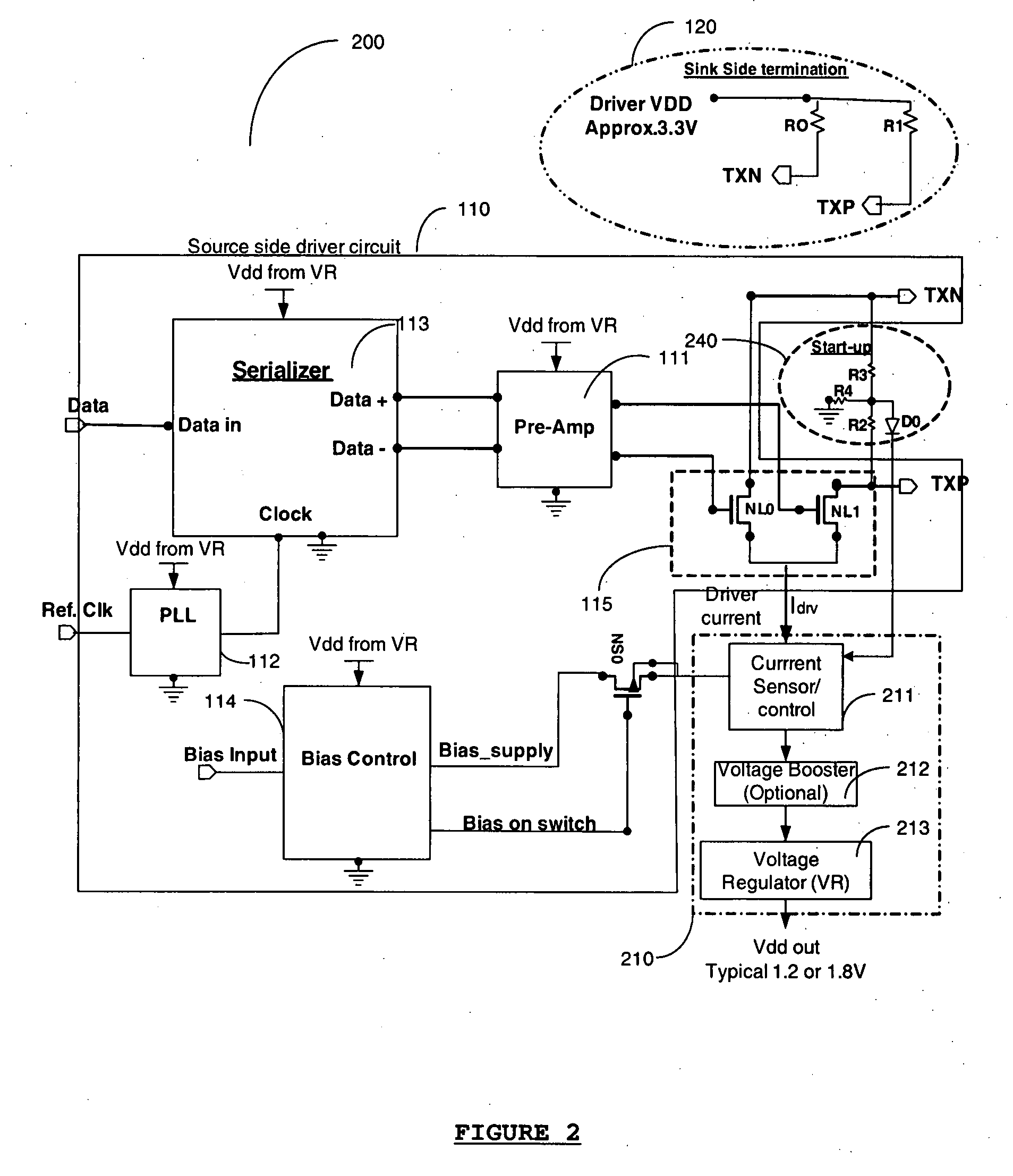

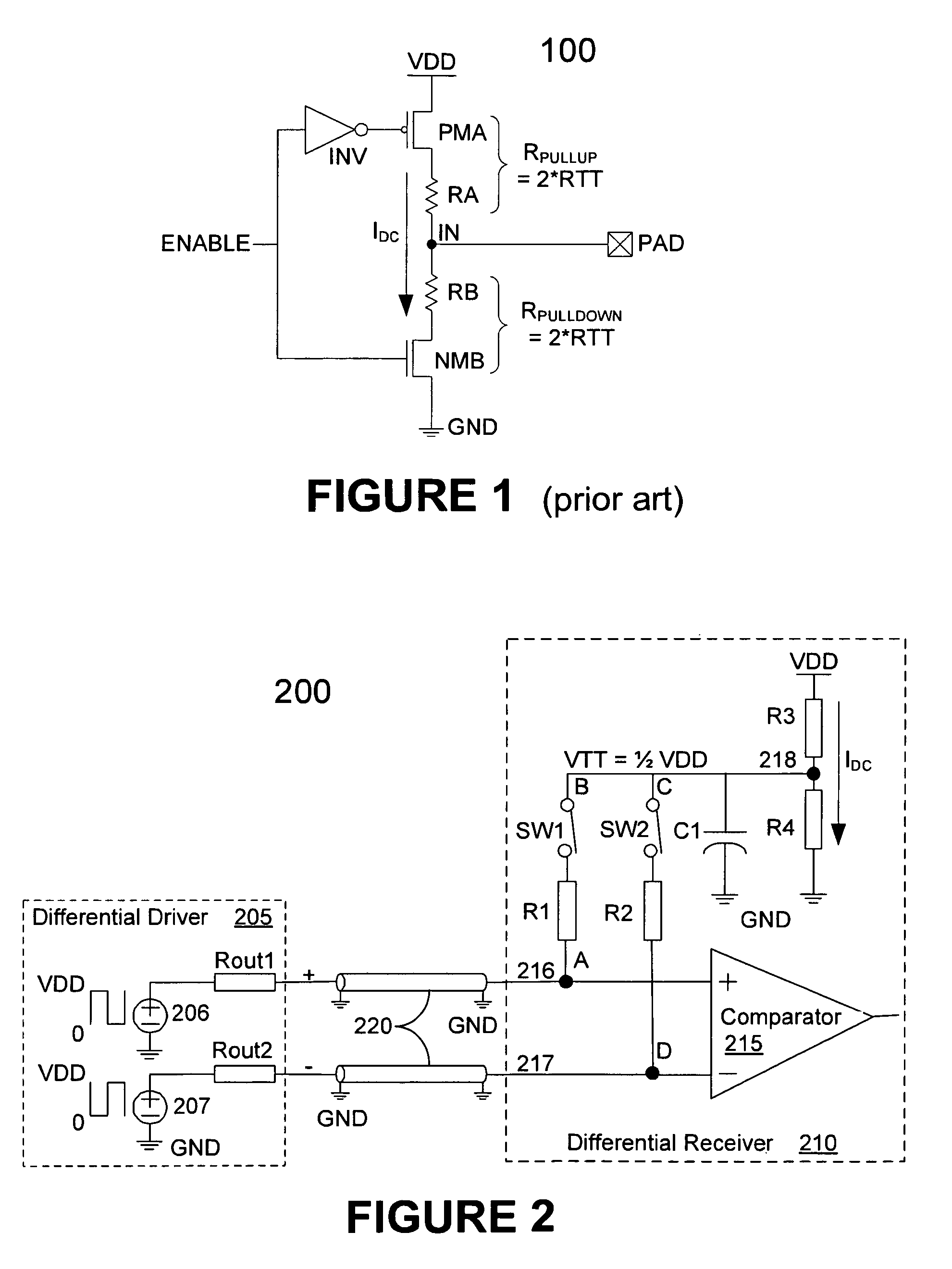

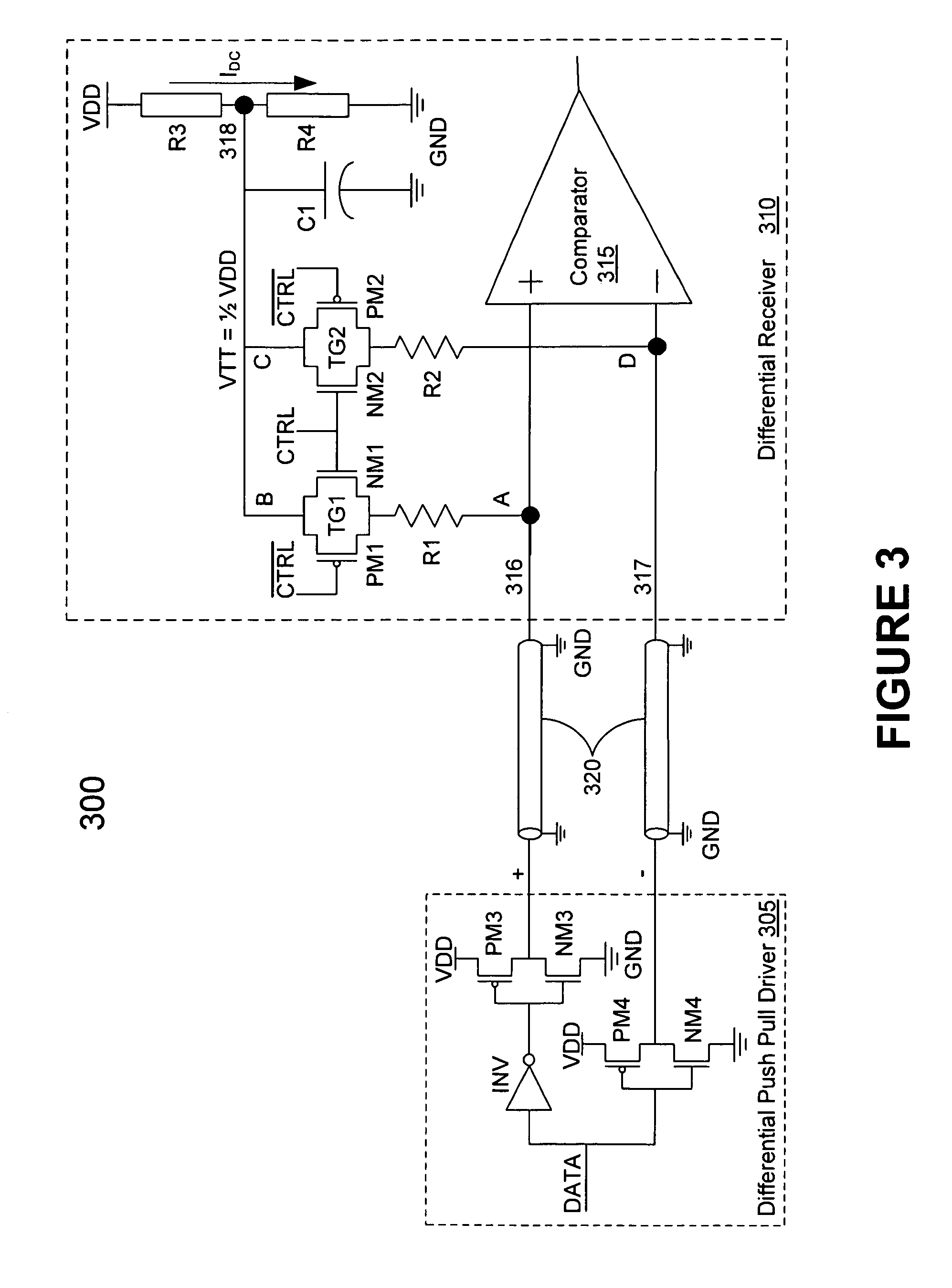

Apparatus and method for termination powered differential interface periphery

ActiveUS20080278122A1Resonant long antennasPower consumption reductionDifferential lineElectrical resistance and conductance

An apparatus and method for supplying power to the peripheral circuits of a transmitter circuit, especially an HDMI transmitter circuit, is disclosed. In an HDMI transmitter the termination resistors of the output driver are part of the receiver. DC power for the driver is supplied through these termination resistors. In prior art implementations of circuits this power, supplied by the receiver circuit, is wasted in the DC set-up circuit of the differential line driver. It is suggested to use this wasted power from the remote termination to power selected peripheral circuits of the transmitter. The use of this wasted power in the line driver for powering the peripheral circuits reduces the total system power.

Owner:ANALOGIX SEMICON

System and method for reducing reconfiguration power usage

ActiveUS20130021058A1Low costIncrease costPower consumption reductionCAD circuit designComputer hardwarePower usage

A system and method for reducing power consumption in a reconfigurable integrated circuit. Some embodiments provide placement and routing programs that reduce the number of bits to be reconfigured. Some embodiments provide placement and routing programs that increase the number of groups of circuits that do not need reconfiguration at some times. Some embodiments include circuits that selectively block reconfiguration.

Owner:ALTERA CORP

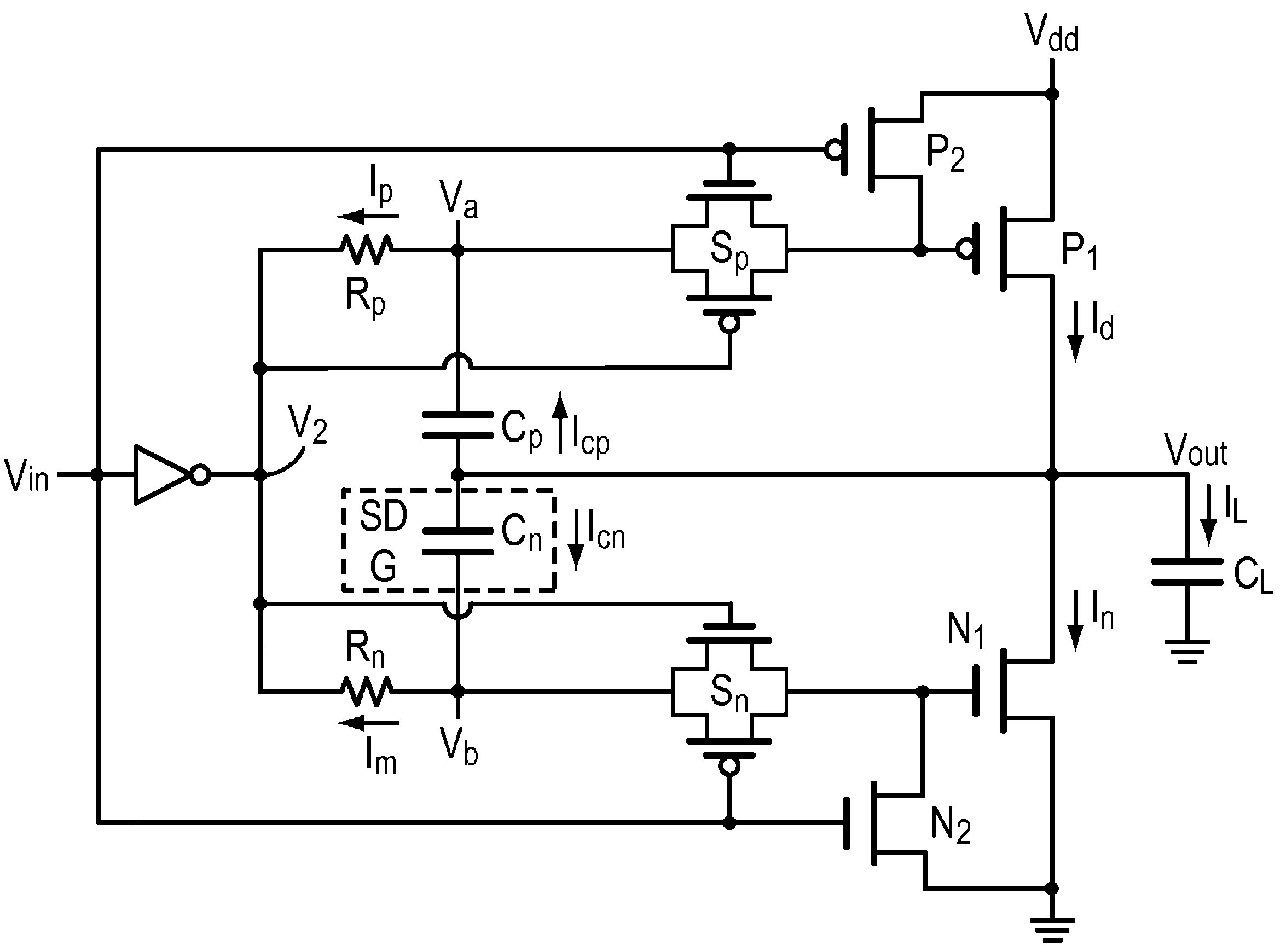

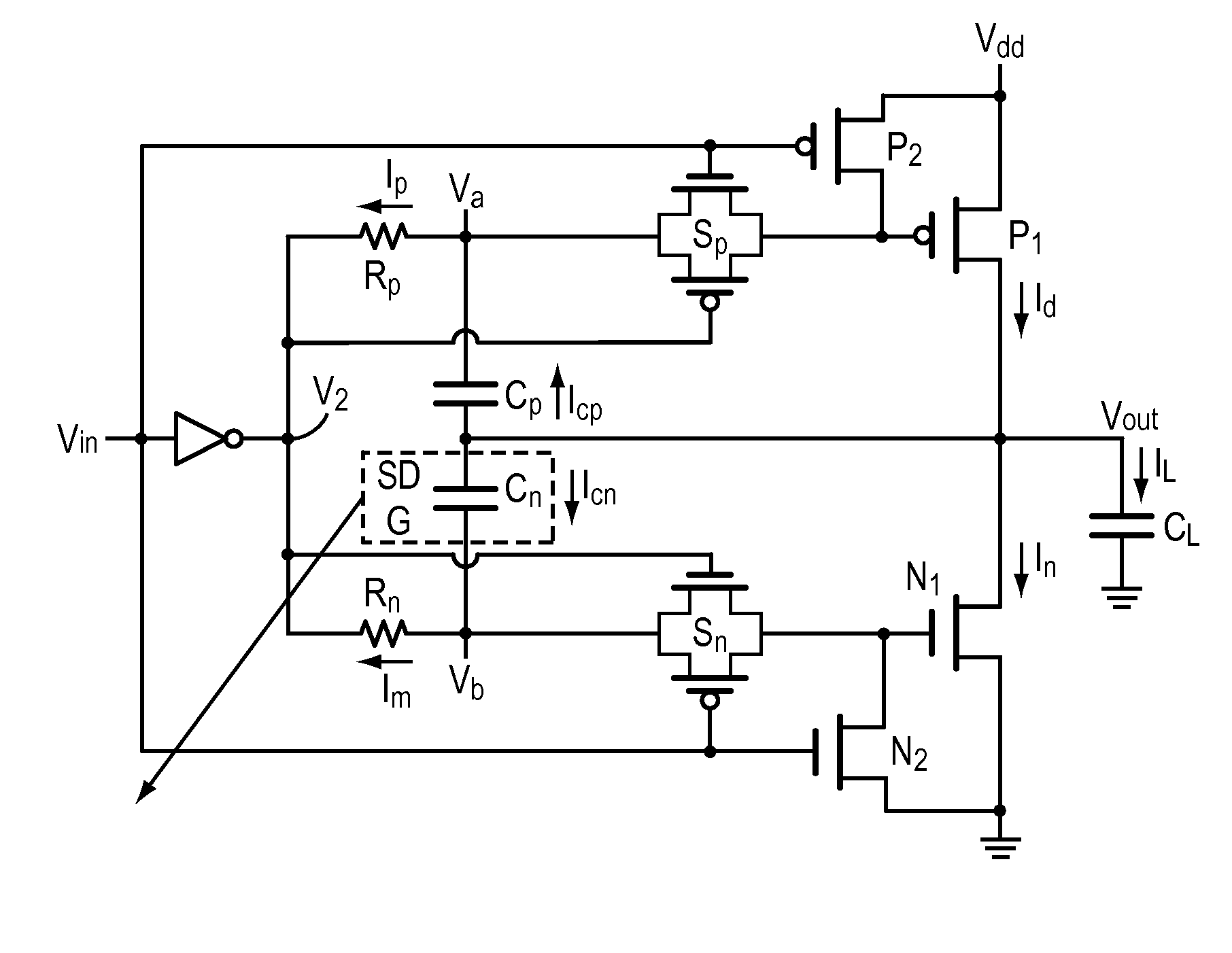

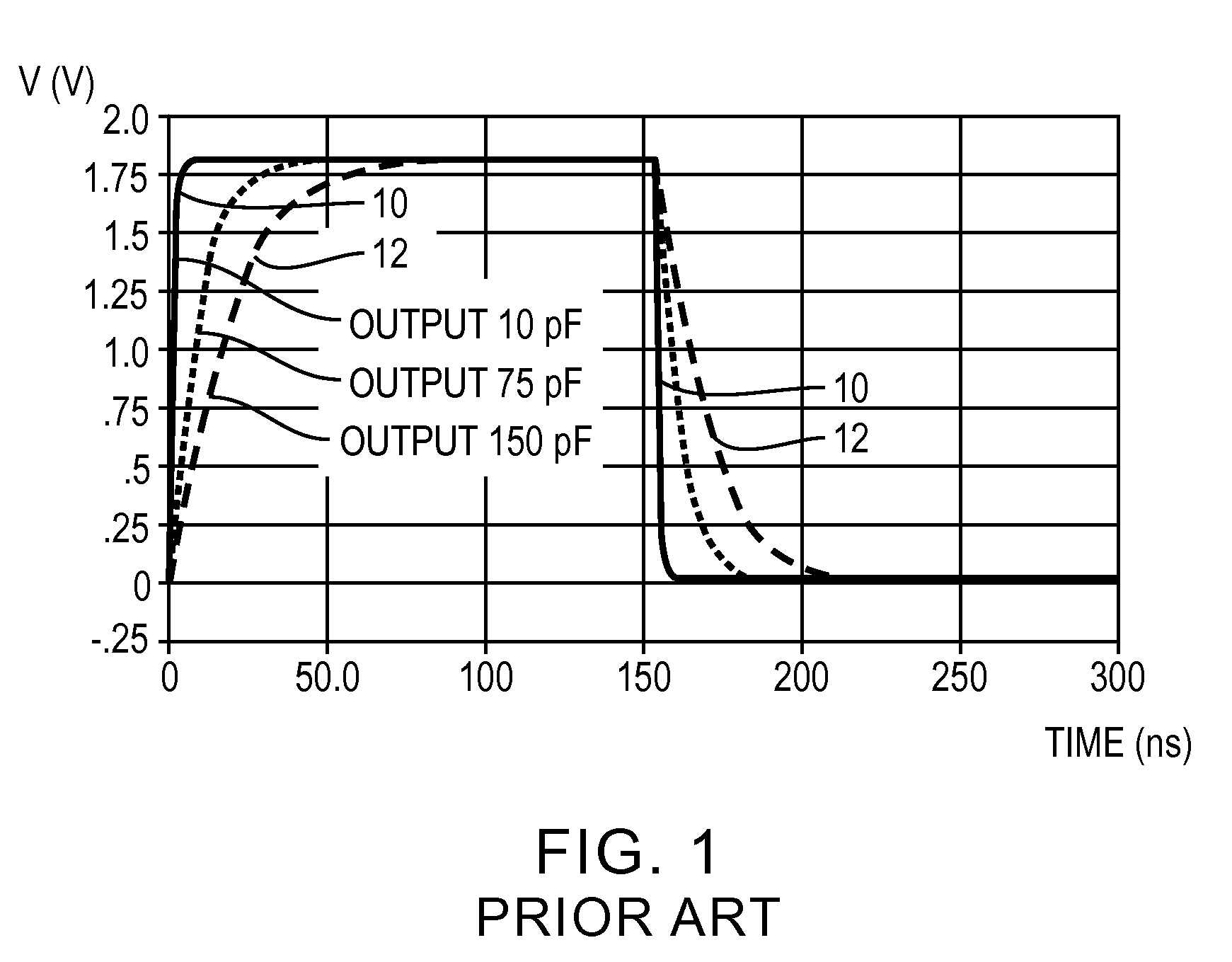

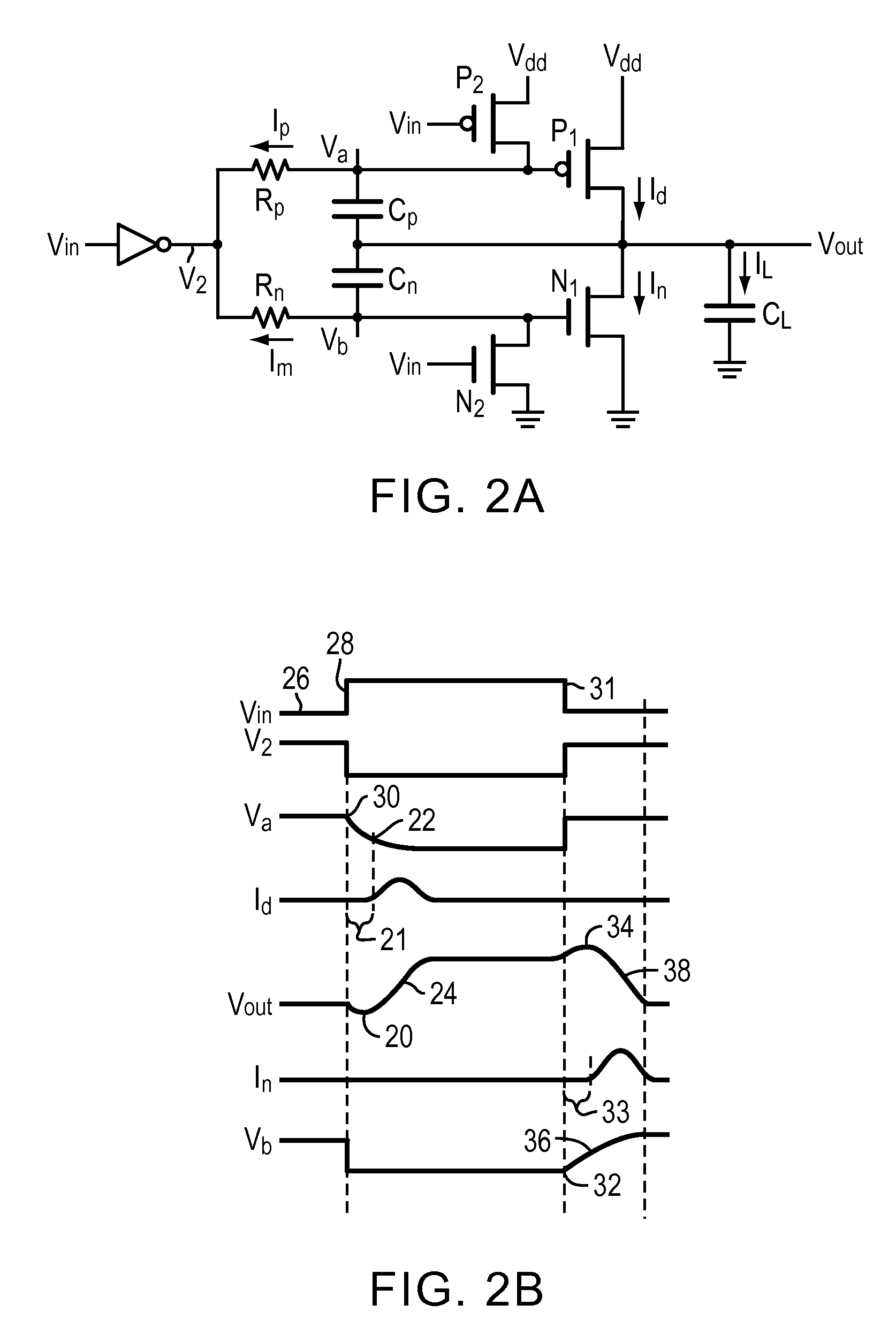

Low speed, load independent, slew rate controlled output buffer with no DC power consumption

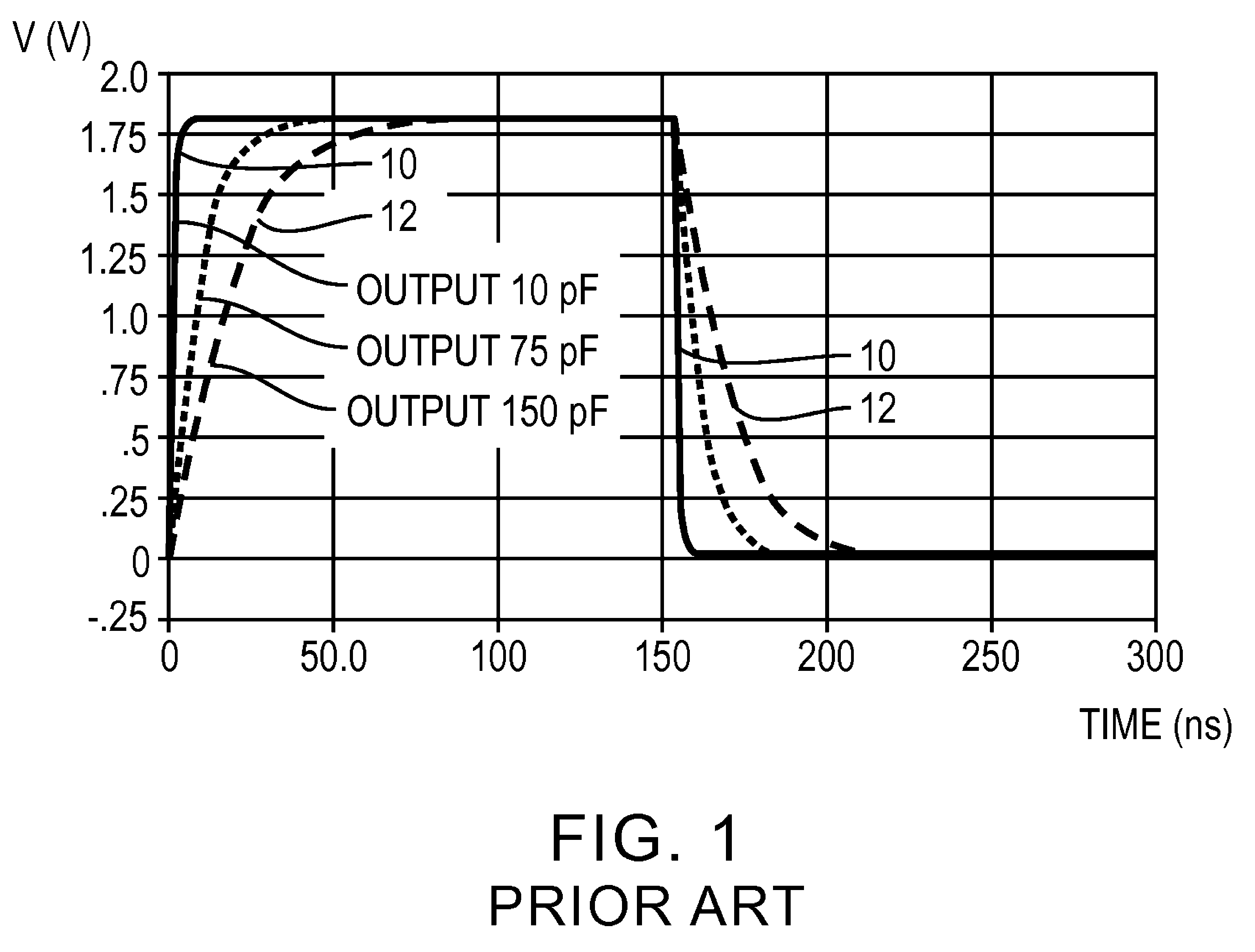

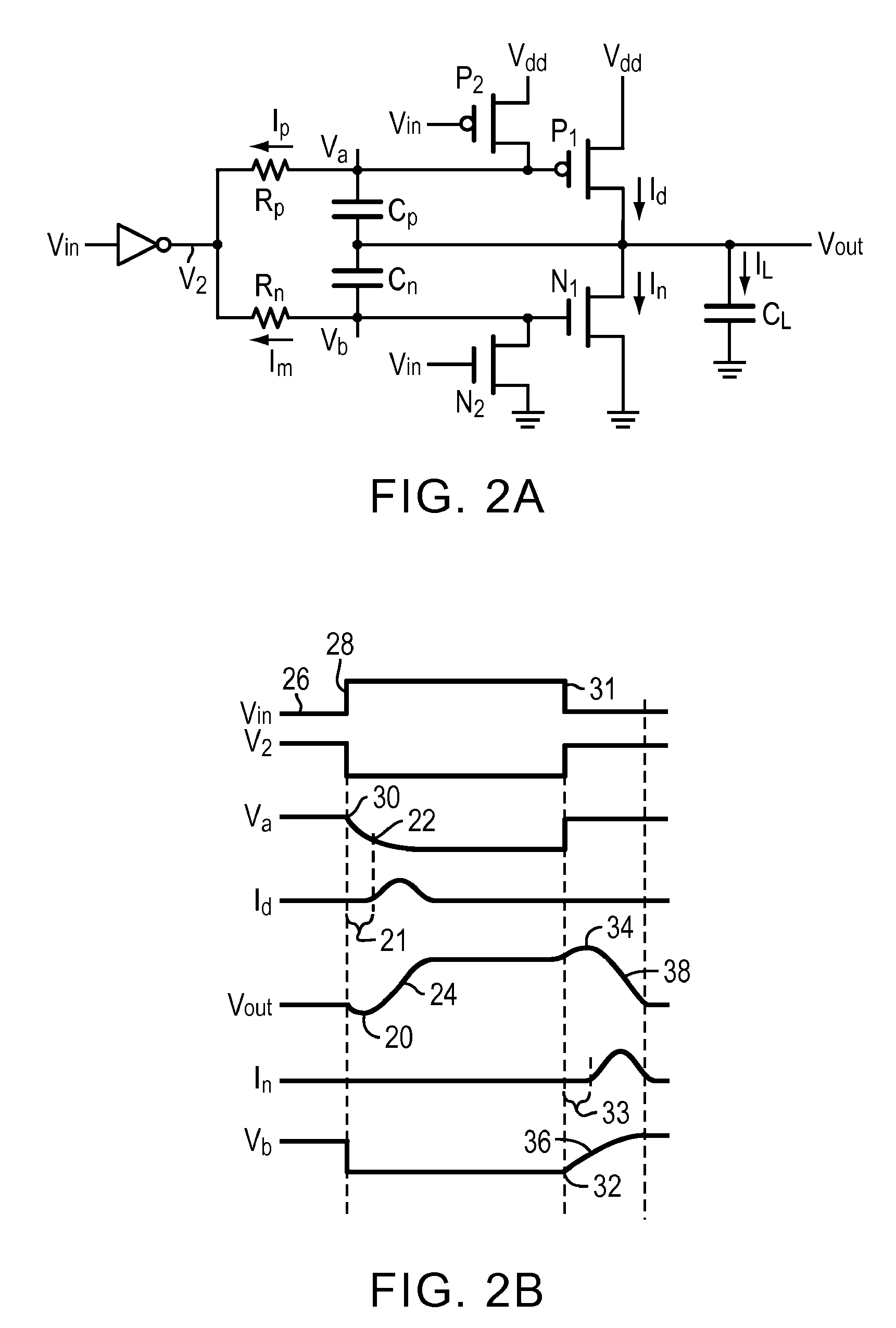

InactiveUS7924066B2Improve degradation rateShorten the timePower consumption reductionElectric pulse generatorCapacitanceLow speed

An output buffer utilizes capacitive feedback to control the output slew rate largely independent of load capacitance. The invention slows the rising and falling slew rates and via a capacitance feedback reduces the effect of load capacitance on slew rate, and uses no DC current. Transistor switches are employed to isolate and reduce noise and interaction among the circuit components and functions.

Owner:SEMICON COMPONENTS IND LLC

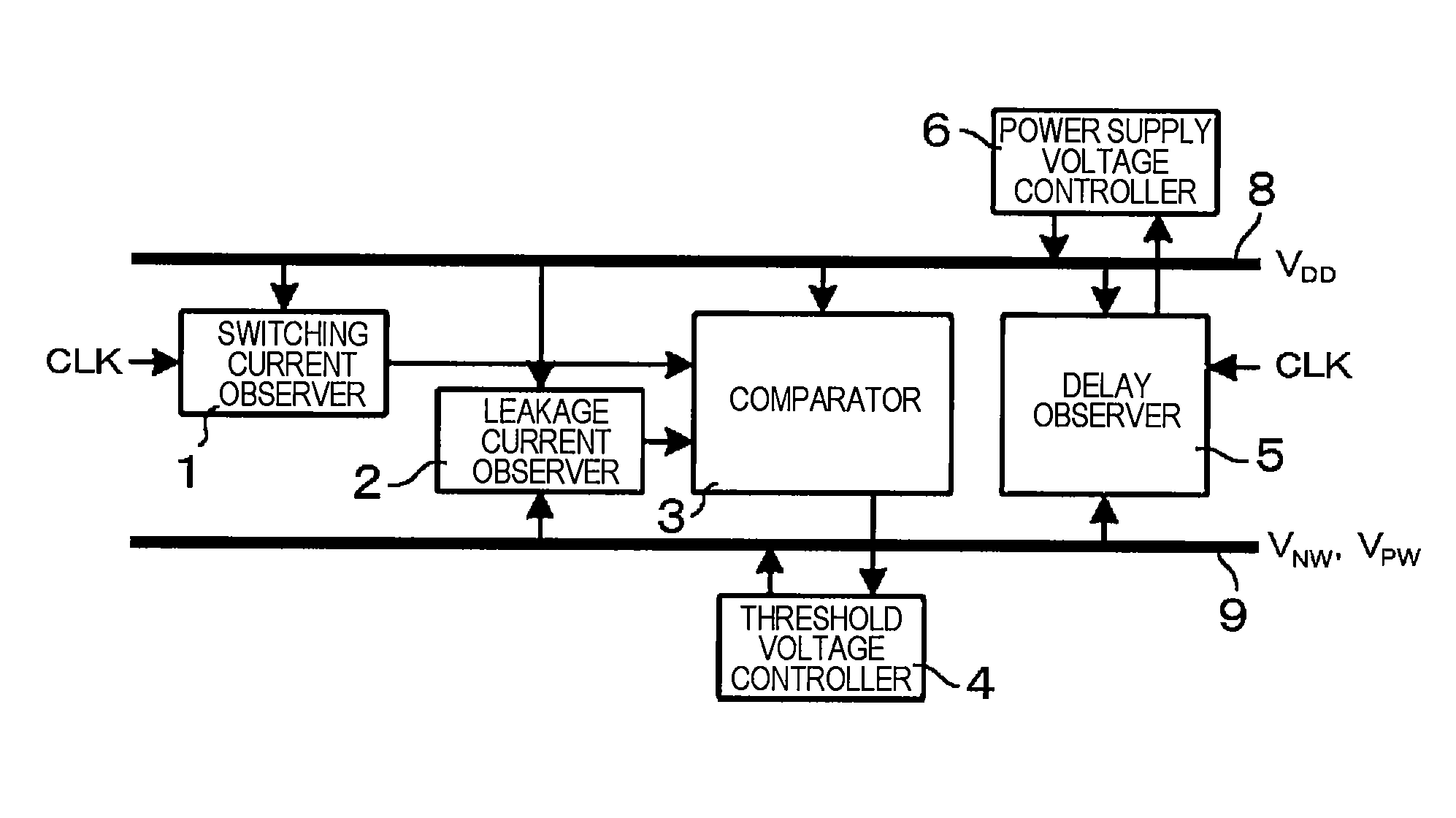

Semiconductor Integrated Circuit Device

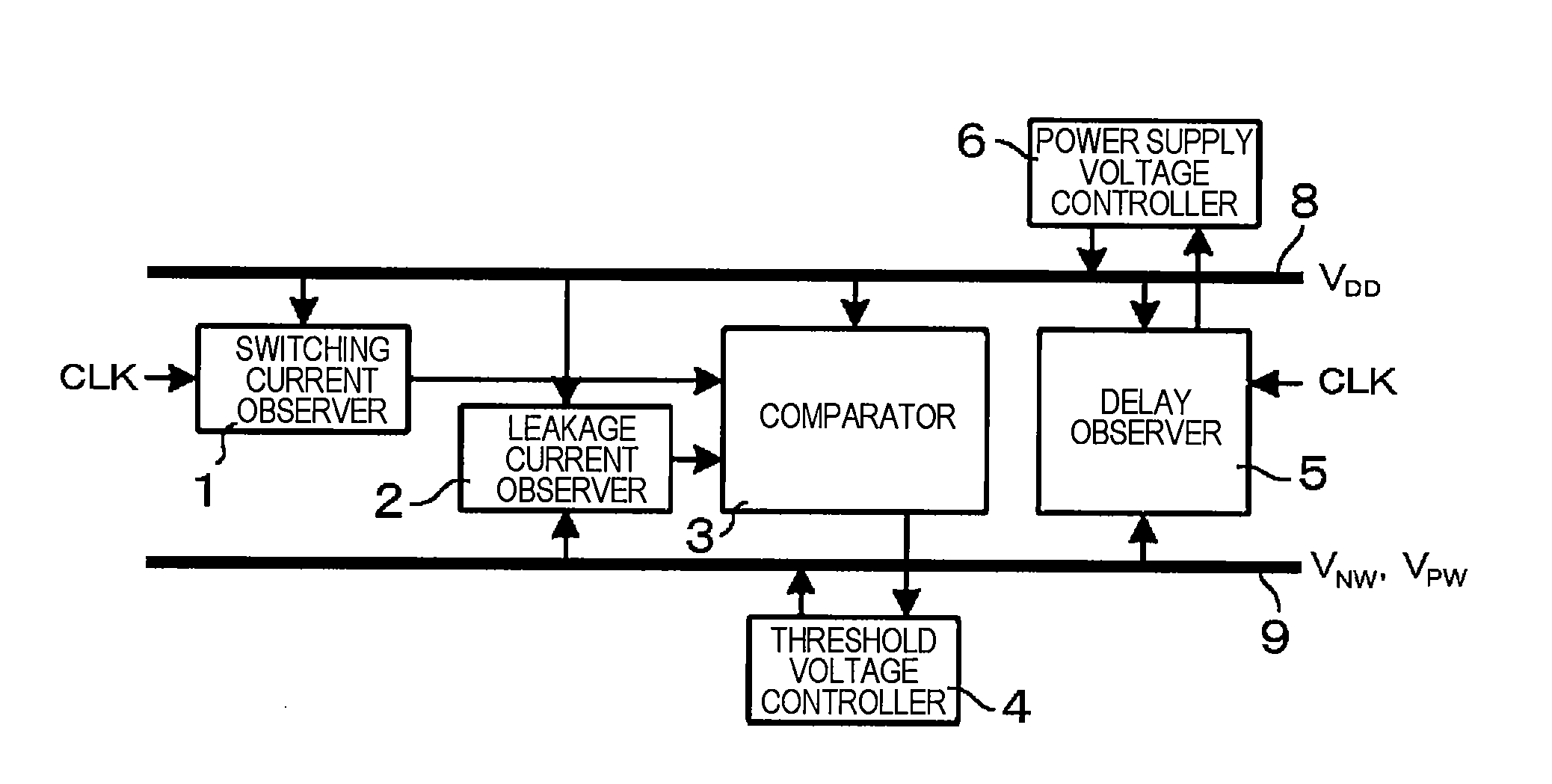

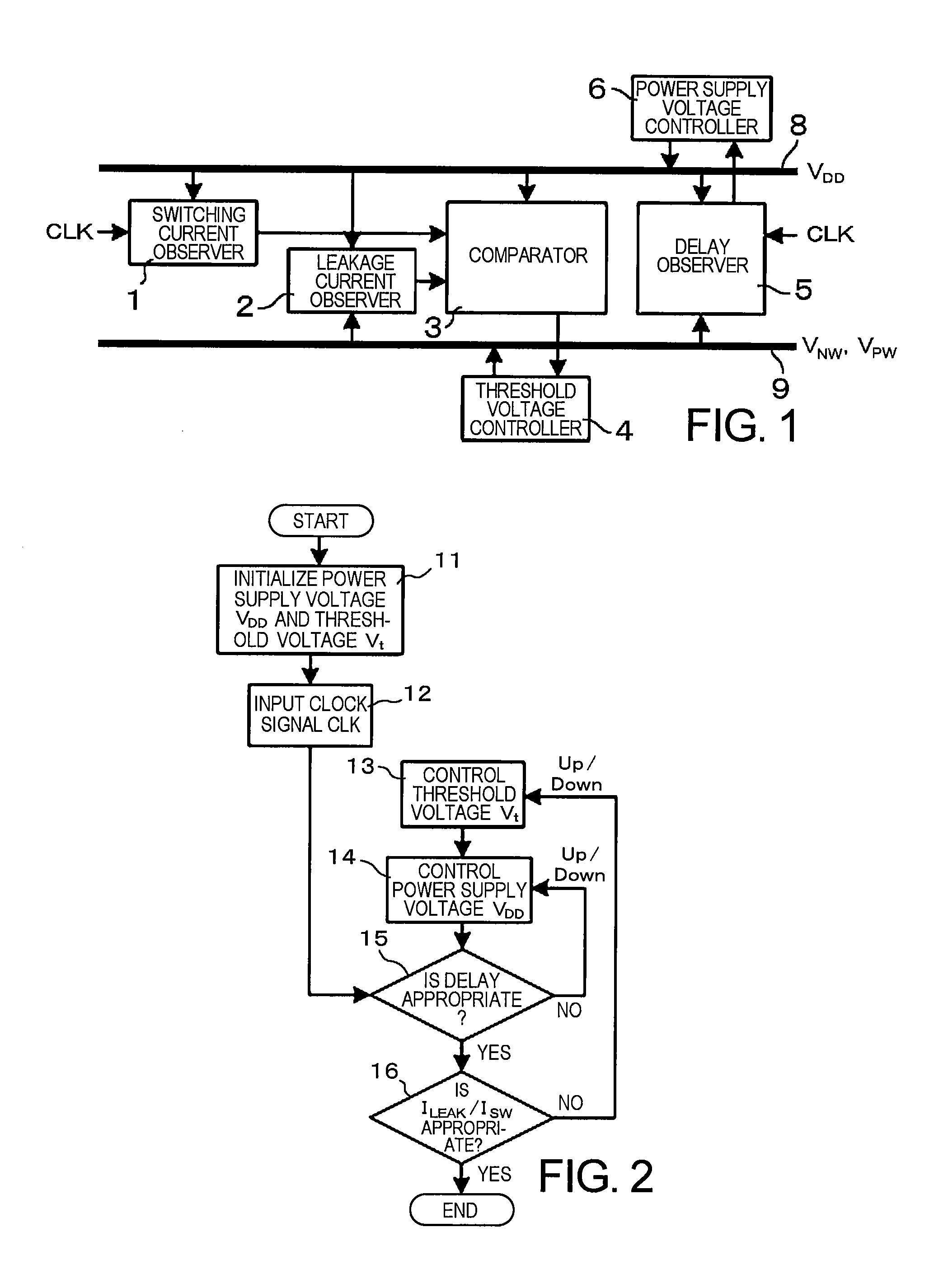

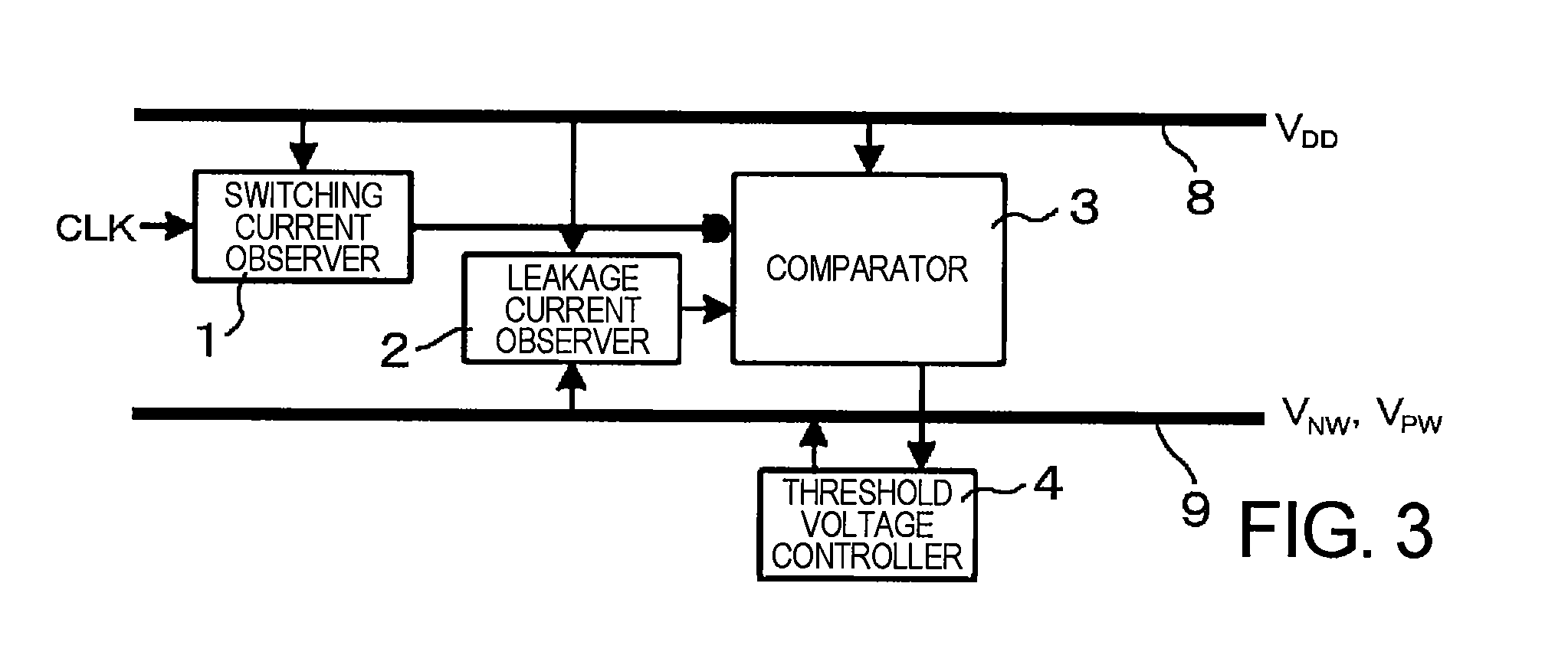

ActiveUS20080191791A1Minimizing operational powerReduce adverse effectsPower consumption reductionElectric pulse generator detailsSwitched currentDrain current

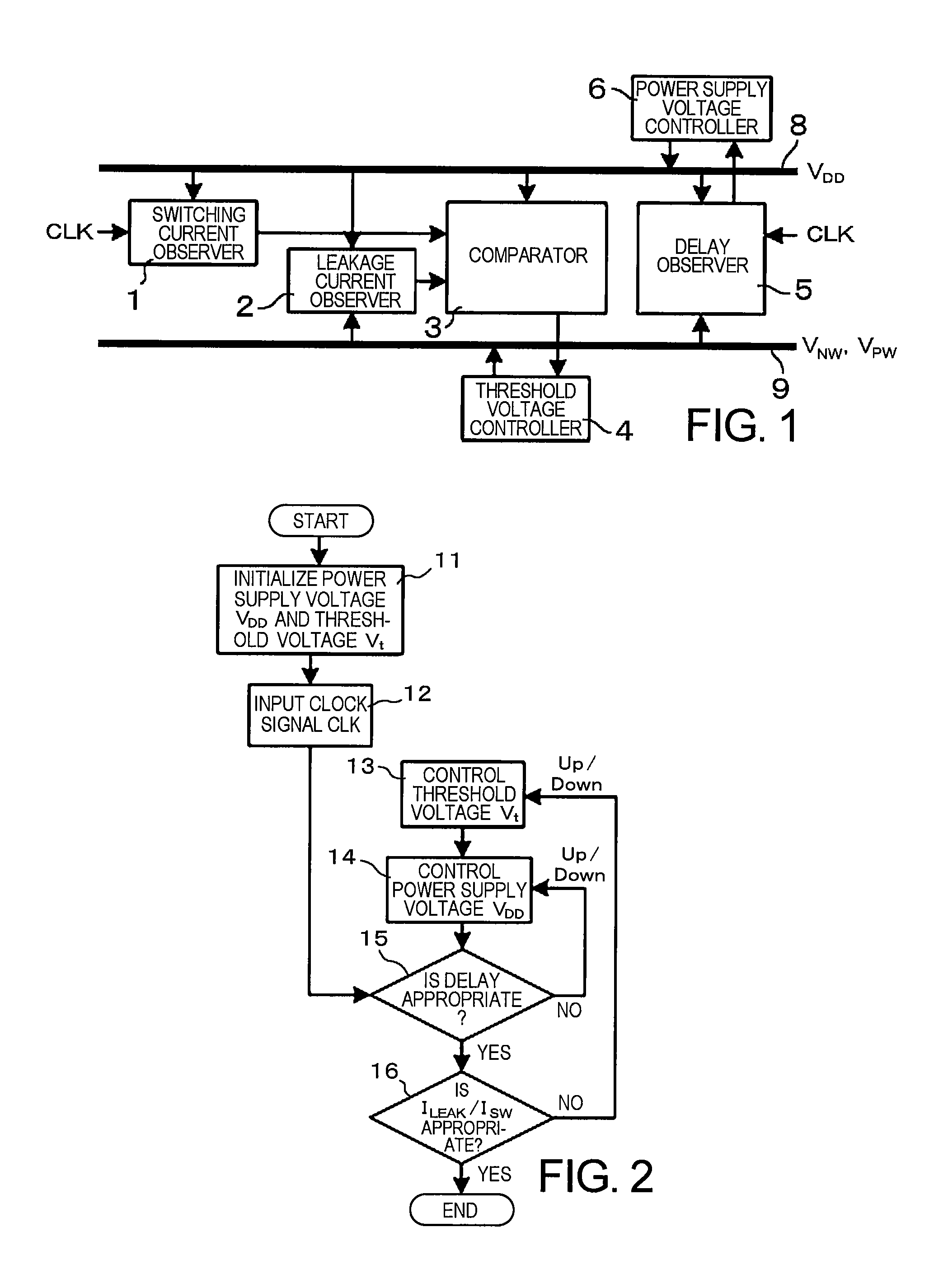

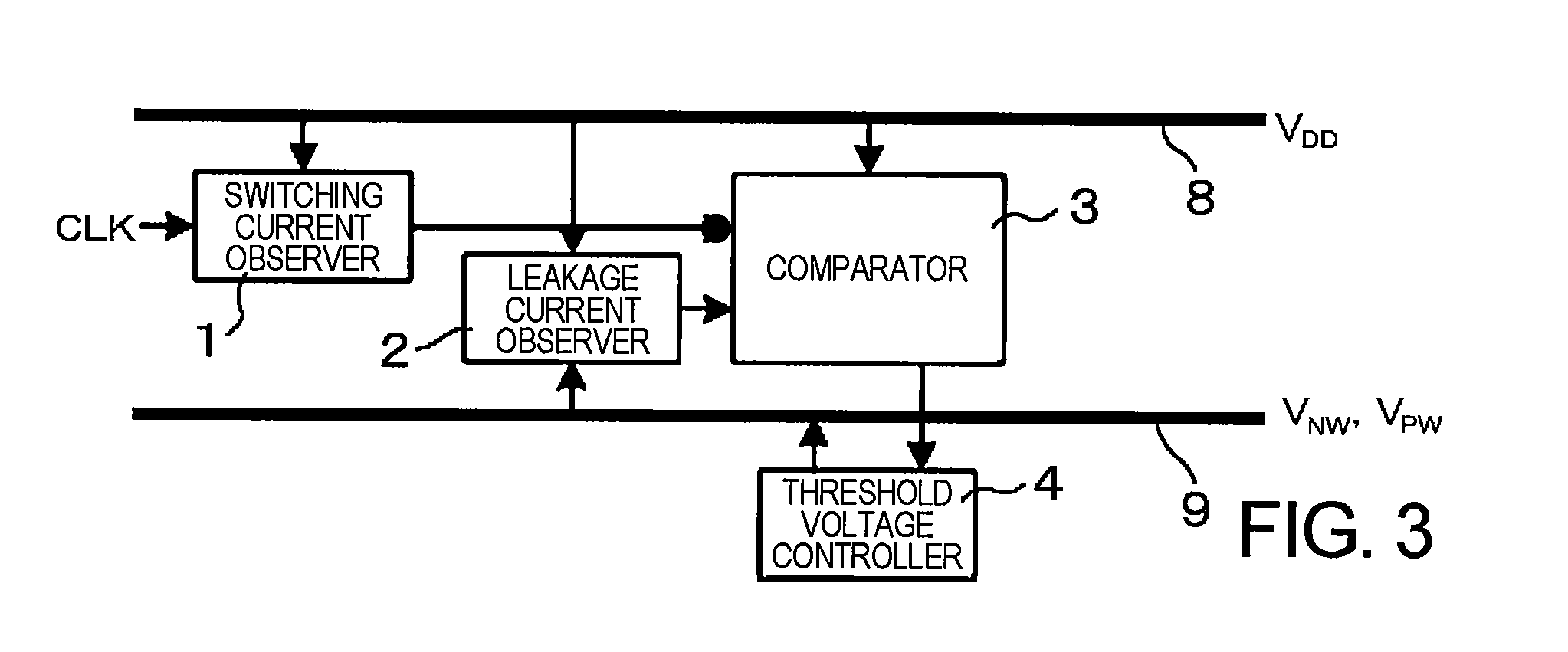

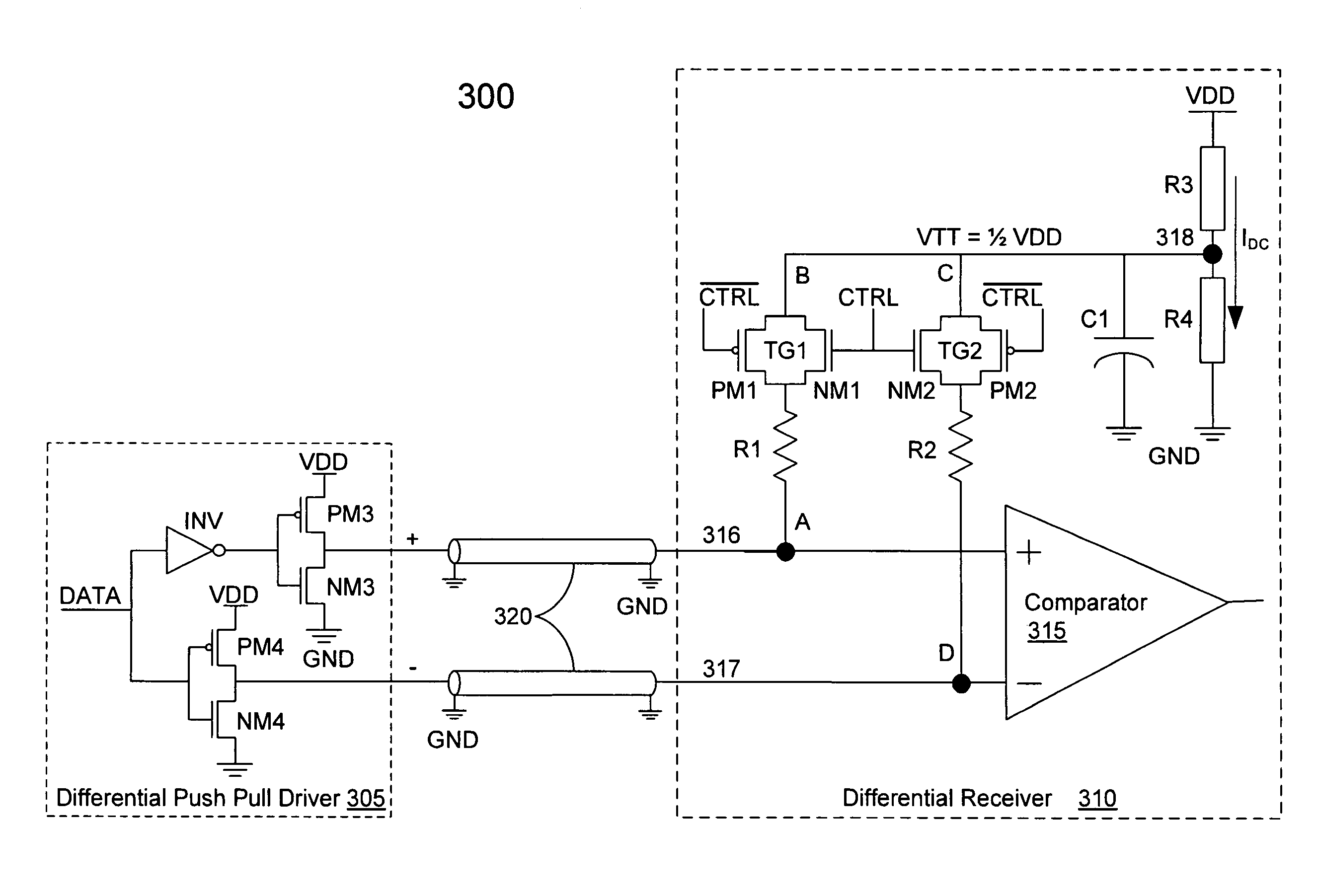

A semiconductor integrated circuit device includes: a switching current observer for observing a switching current; a leakage current observer for observing a leakage current; a comparator which compares the switching current and the leakage current with each other; a threshold voltage controller for controlling a substrate bias voltage in order to make a ratio of the switching current and the leakage current constant; a delay observer for observing a delay amount; and a power supply voltage controller for controlling a power supply voltage in order to keep the delay amount in a predetermined range. In the semiconductor integrated circuit device, a process which enables the minimization of an operation power is carried out by controlling the threshold voltage to make the ratio of the switching current and the leakage current constant at a given clock frequency and controlling the power supply voltage to guarantee the operating speed.

Owner:NEC CORP

Low speed, load independent, slew rate controlled output buffer with no DC power consumption

InactiveUS20100244907A1Reduce slew rate variationImprove degradation ratePower consumption reductionElectric pulse generatorCapacitanceLow speed

An output buffer utilizes capacitive feedback to control the output slew rate largely independent of load capacitance. The invention slows the rising and falling slew rates and via a capacitance feedback reduces the effect of load capacitance on slew rate, and uses no DC current. Transistor switches are employed to isolate and reduce noise and interaction among the circuit components and functions.

Owner:SEMICON COMPONENTS IND LLC

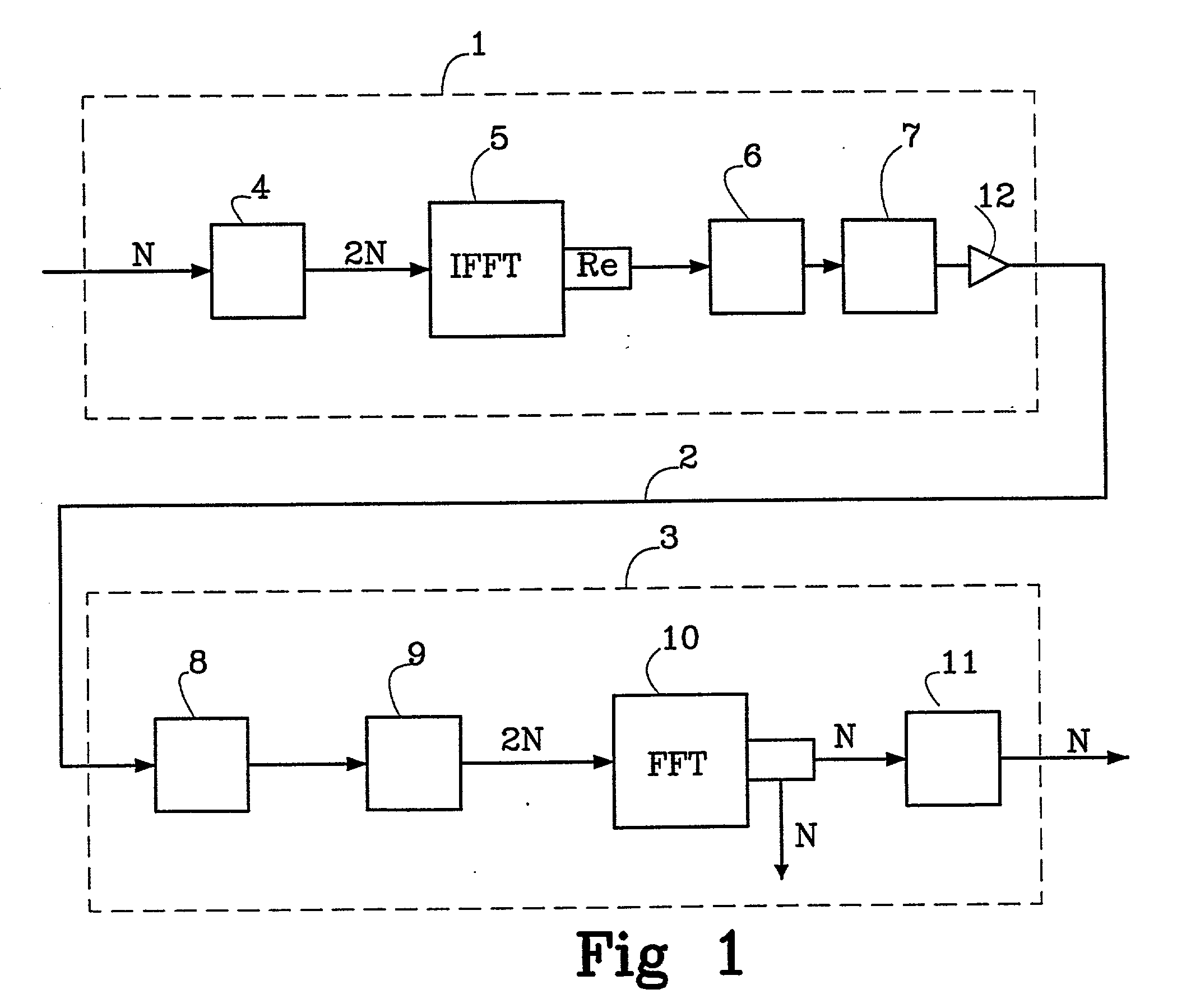

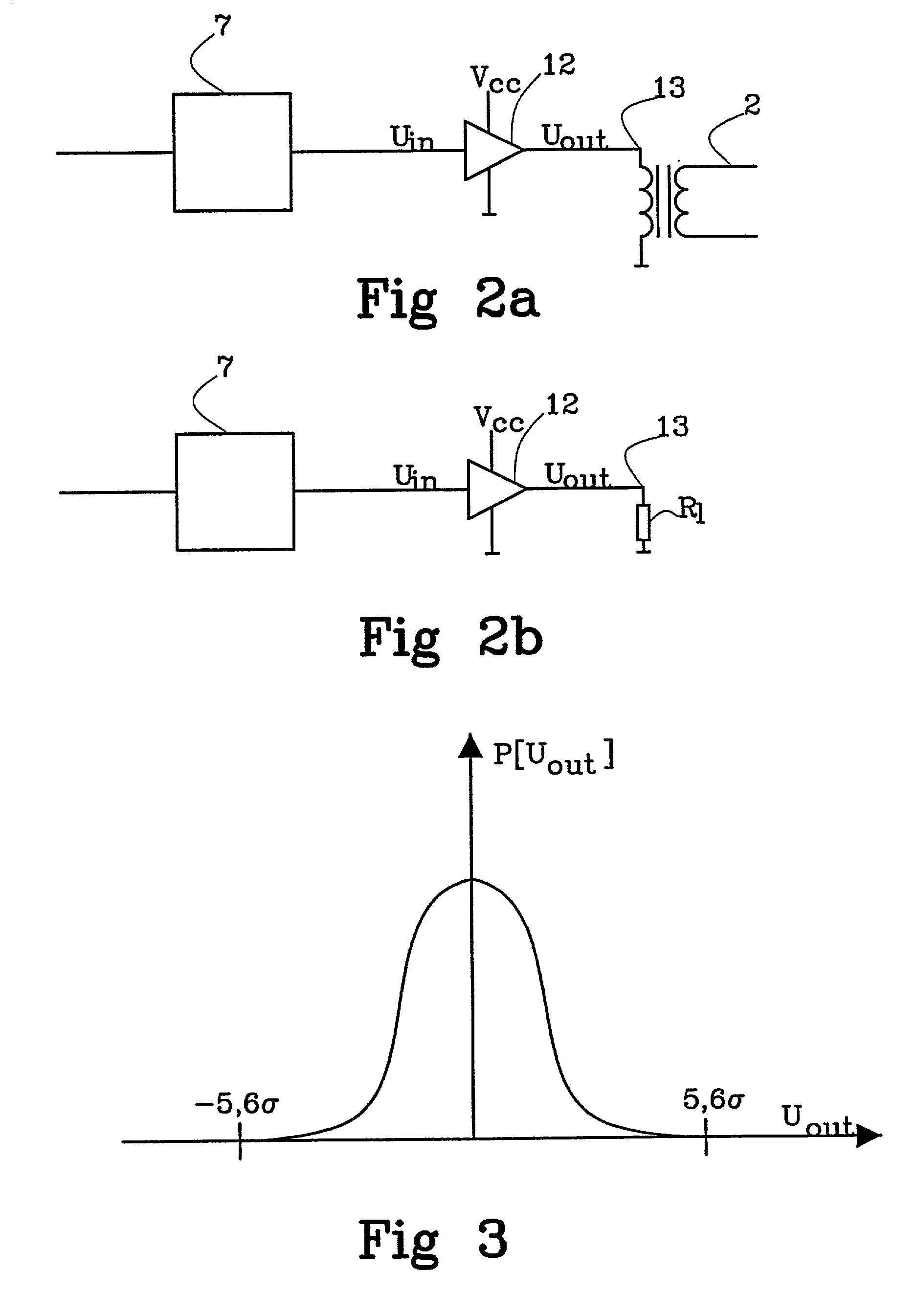

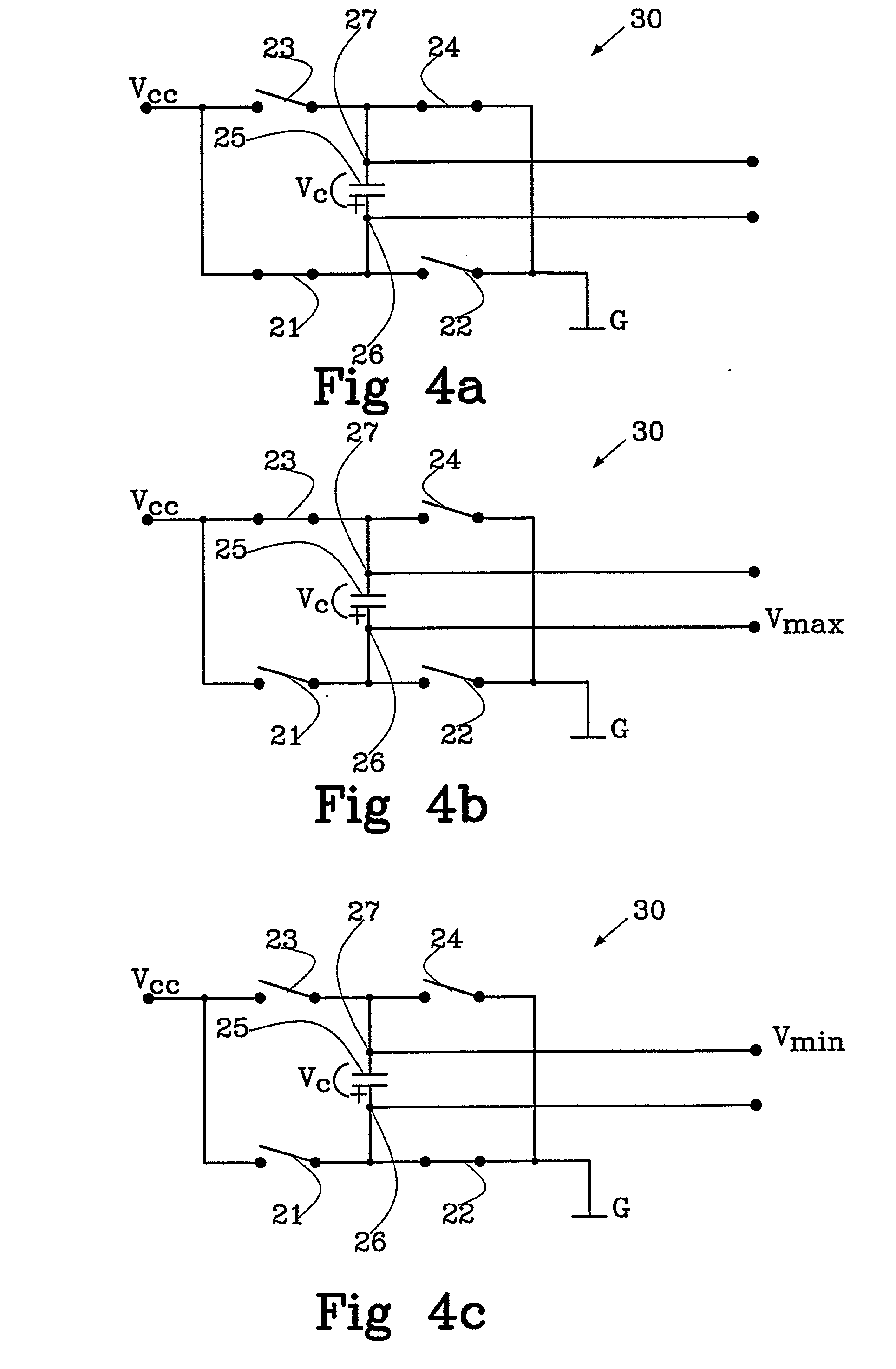

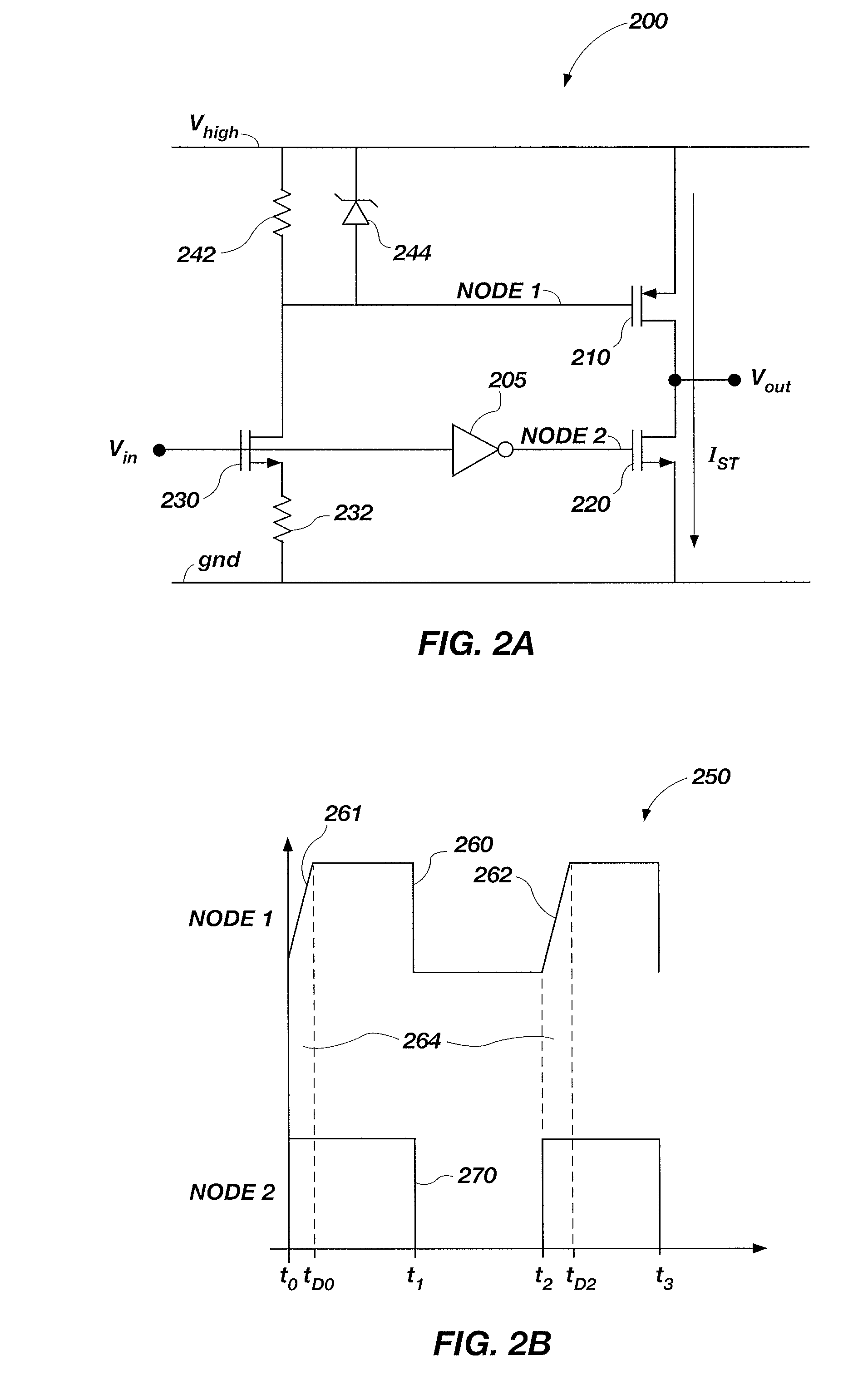

Line driver

InactiveUS20010028271A1Reduce power consumptionStable voltageSwitching accelaration modificationsPower consumption reductionCapacitor voltageEngineering

The invention relates to a line driver supplied with a power supply voltage from a power supply and an amplifying method. According to the invention the following steps are performed: using whole or part of the power supply voltage to generate the output voltage if the input voltage is within the predefined range; loading at least one capacitor with at least one capacitor voltage; and using whole or part of the capacitor voltage in addition to whole or part of the power supply voltage to generate the output voltage if the input voltage is outside the predefined range.

Owner:TELEFON AB LM ERICSSON (PUBL)

Semiconductor integrated circuit device

ActiveUS7659772B2Reduce power consumptionManufacturing process is complexPower consumption reductionElectric pulse generator detailsSwitched currentEngineering

A semiconductor integrated circuit device includes: a switching current observer for observing a switching current; a leakage current observer for observing a leakage current; a comparator which compares the switching current and the leakage current with each other; a threshold voltage controller for controlling a substrate bias voltage in order to make a ratio of the switching current and the leakage current constant; a delay observer for observing a delay amount; and a power supply voltage controller for controlling a power supply voltage in order to keep the delay amount in a predetermined range. In the semiconductor integrated circuit device, a process which enables the minimization of an operation power is carried out by controlling the threshold voltage to make the ratio of the switching current and the leakage current constant at a given clock frequency and controlling the power supply voltage to guarantee the operating speed.

Owner:NEC CORP

Reduced power differential type termination circuit

ActiveUS7750666B2Reduce power consumptionImprove integrityInput/output impedence modificationLogic circuit coupling arrangementsVoltage generatorTransmission gate

A reduced power differential type termination circuit for use in SSTL, HSTL and other transmission line systems reduces power consumption. A differential type termination circuit may comprise first and second nodes for coupling, respectively, to first and second transmission lines; a first impedance coupled between the first transmission line and a third node; a second impedance coupled between the second transmission line and the third node; and a low direct current reference voltage generator for generating a reference voltage applied to the third node. The first and second transmission lines may transmit complimentary signals. The first and second impedances may be symmetric or asymmetric. The first impedance may match the second impedance. The first and second impedances may, respectively, match the impedances of the first and second transmission lines. The first and / or second impedances may include a bidirectional switch, such as a transmission gate, to enable and disable the termination circuit.

Owner:INTEGRATED DEVICE TECH INC

Dynamic voltage and frequency management

ActiveUS7915910B2Reliability increasing modificationsEnergy efficient ICTLogic gateFrequency management

In one embodiment, an integrated circuit includes a self calibration unit configured to iterate a test on a logic circuit in the integrated circuit at respectively lower supply voltage magnitudes until the test fails. A lowest supply voltage magnitude at which the test passes is used to generate a requested supply voltage magnitude for the integrated circuit. In an embodiment, an integrated circuit includes a series connection of logic gates physically distributed over an area of the integrated circuit, and a measurement unit configured to launch a logical transition into the series and detect a corresponding transition at the output of the series. The amount of time between the launch and the detection is used to request a supply voltage magnitude for the integrated circuit.

Owner:APPLE INC

Circuitry and method for timing speculation via toggling functional critical paths

InactiveUS9564883B1Power consumption reductionSingle output arrangementsTransition densityExclusive or

Toggling functional critical path timing sensors measure delays in toggling functional critical paths that are replicas of actual critical paths or representations of worst-case delay paths. A Toggle flip-flop or Linear-Feedback-Shift Register (LFSR) drives high-transition-density test patterns to the toggling functional critical paths. When a toggling functional critical path's delay fails to meet set-up timing requirement to a next register, the toggling functional critical path timing sensors signal a controller to increase VDD. When no failures occur over a period of time, the controller decreases VDD. A margin delay buffer adds a delay to the toggling functional critical path before being clocked into an early capture flip-flop. A reference register receives the test pattern without the delay of the toggling functional critical path, and an exclusive-OR (XOR) gate compares outputs of reference and early capture flip-flops to generate timing failure signals to the controller.

Owner:QUALCOMM INC

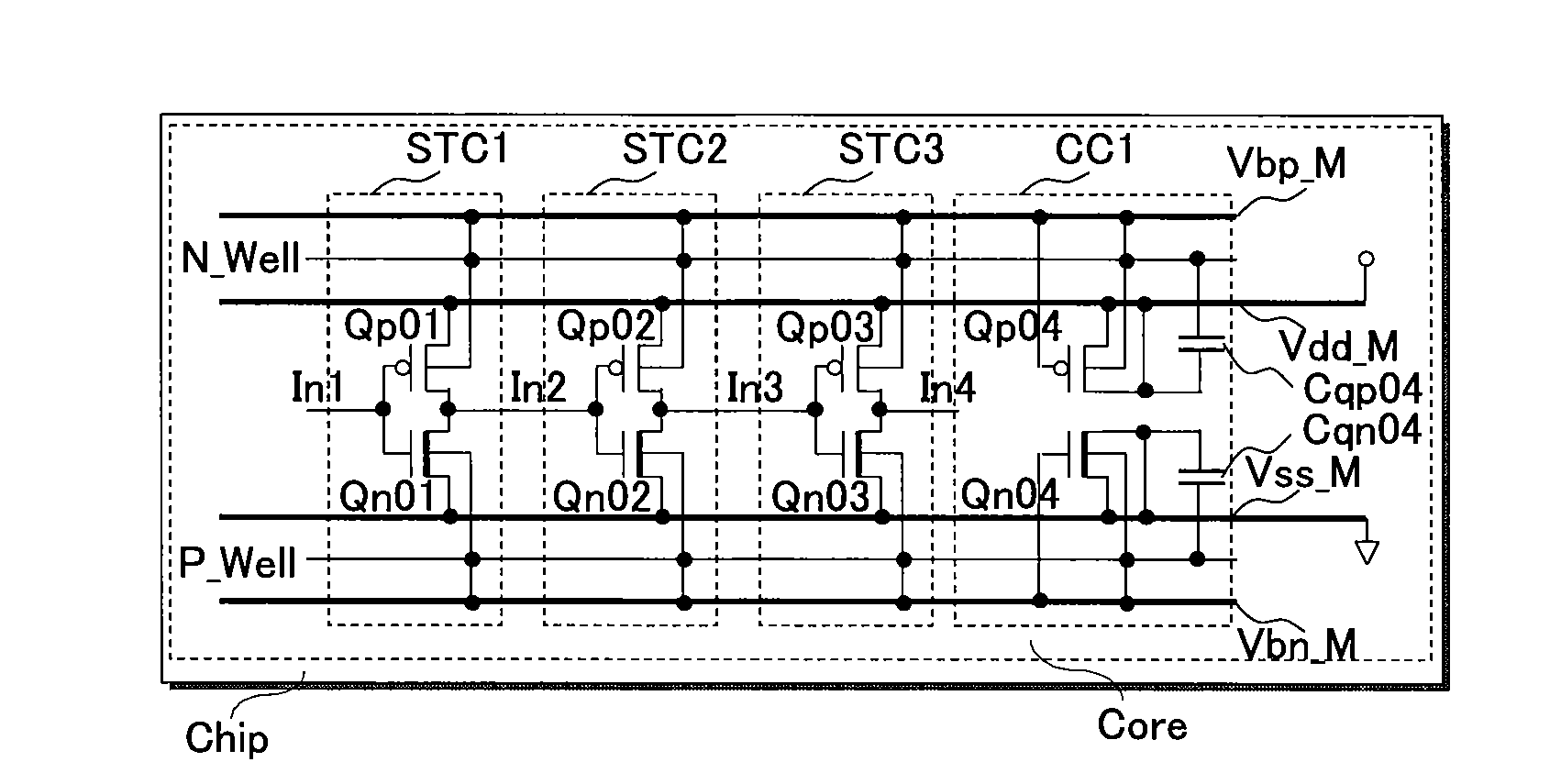

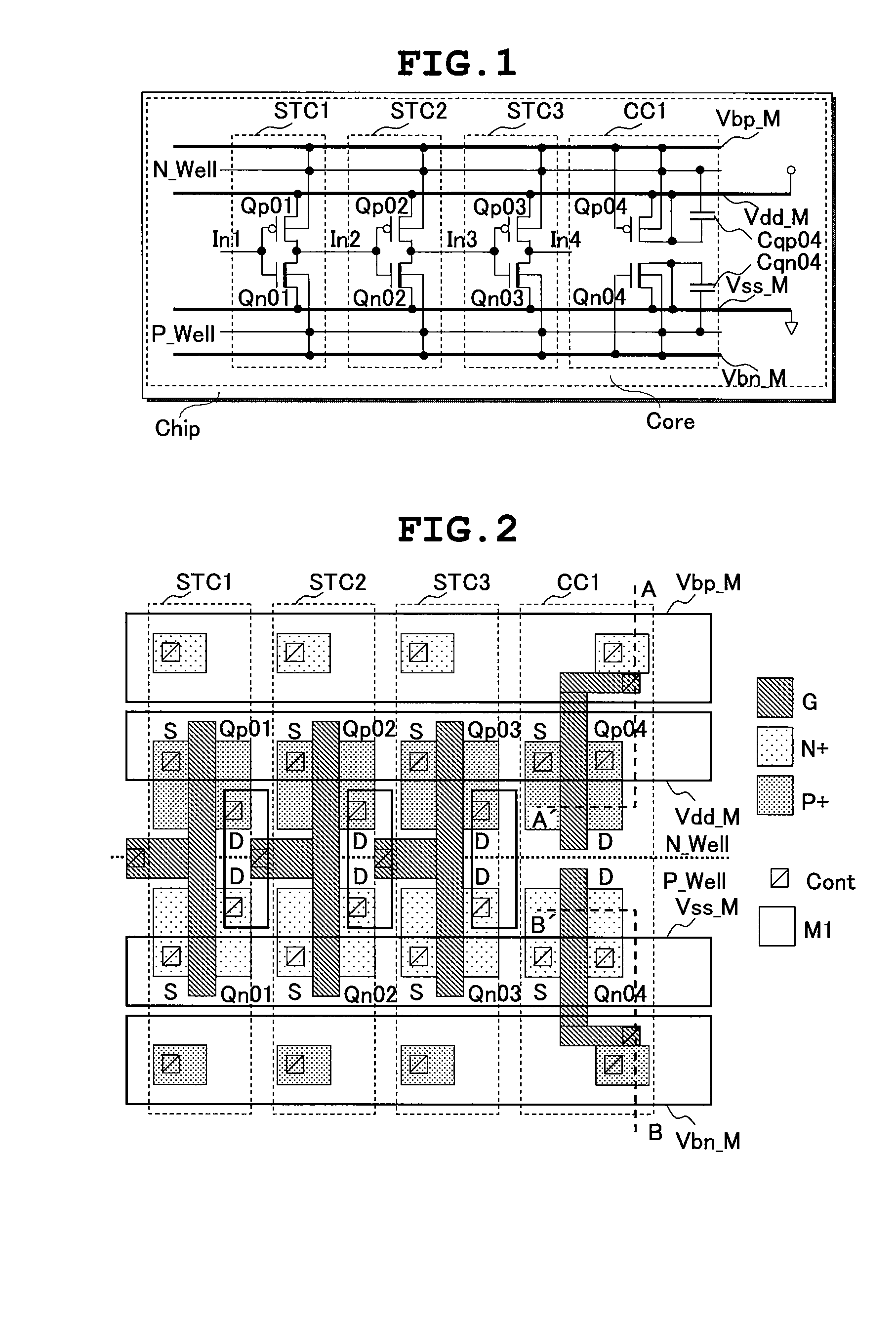

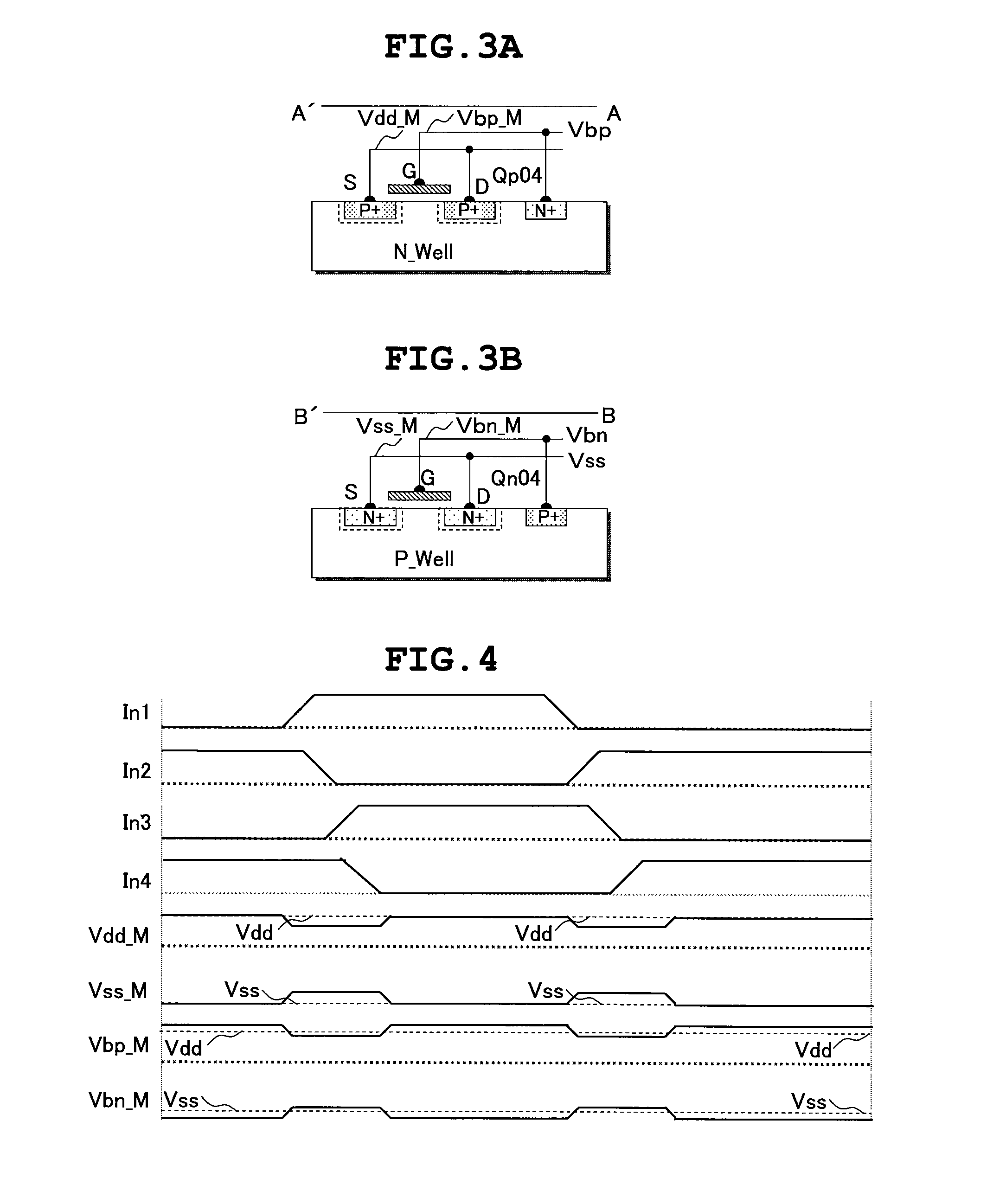

Semiconductor integrated circuit

InactiveUS20080174359A1High yieldReduce power consumptionPower consumption reductionSemiconductor/solid-state device manufacturingCapacitanceCMOS

A substrate bias technique is used in an active mode enabling a high yield, and an operating consumption power and the fluctuation of a signal delay in signal processing are reduced in the active mode. The additional PMOS and NMOS of the additional capacitance circuit are produced in the same production process as the PMOSs and the NMOSs of the CMOS circuits. The gate capacitance of the additional PMOS is coupled between the power supply wiring and the N well and the gate capacitance of the additional NMOS is coupled between the ground wiring and the P well. The noise on the power supply wiring is transmitted to the N well through the gate capacitance and the noise on the ground wiring is transmitted to the P well through the gate capacitance. The fluctuation of noise on the substrate bias voltage between the source and the well of PMOS and NMOS of the CMOS circuits is reduced.

Owner:RENESAS ELECTRONICS CORP

Reading configuration data from internal storage node of configuration storage circuit

Some embodiments provide an IC with configuration context switchers. The IC includes several configurable circuits, each of which configurably performs one of several operations at any given time, based on the configuration data set that it receives at that time. The IC includes several storage circuits for storing several configuration data sets for each of the configurable circuits. The IC also includes a context switching interconnect circuit for switchably connecting the configurable circuit to different sets of storage circuits to receive different sets of configuration data sets. The context switcher includes one or more stages for re-timing the data coming from the configuration storage elements. The stages can include interconnect circuitry or storage circuitry. Some embodiments build one of the stages in the configuration data storage elements. Some embodiments encode the configuration data bits and hence utilize a decoder in the context switcher to decode the encoded configuration data.

Owner:ALTERA CORP

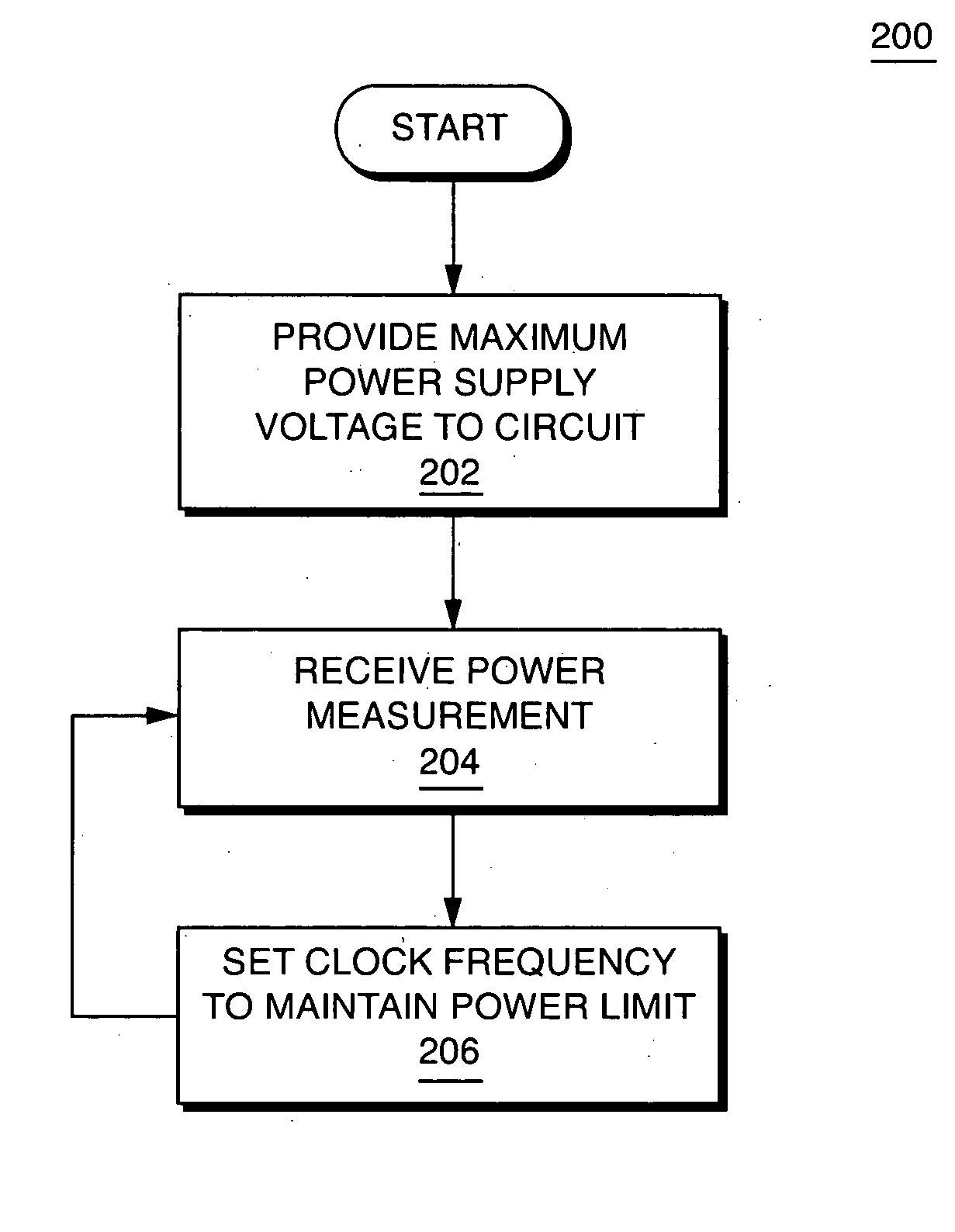

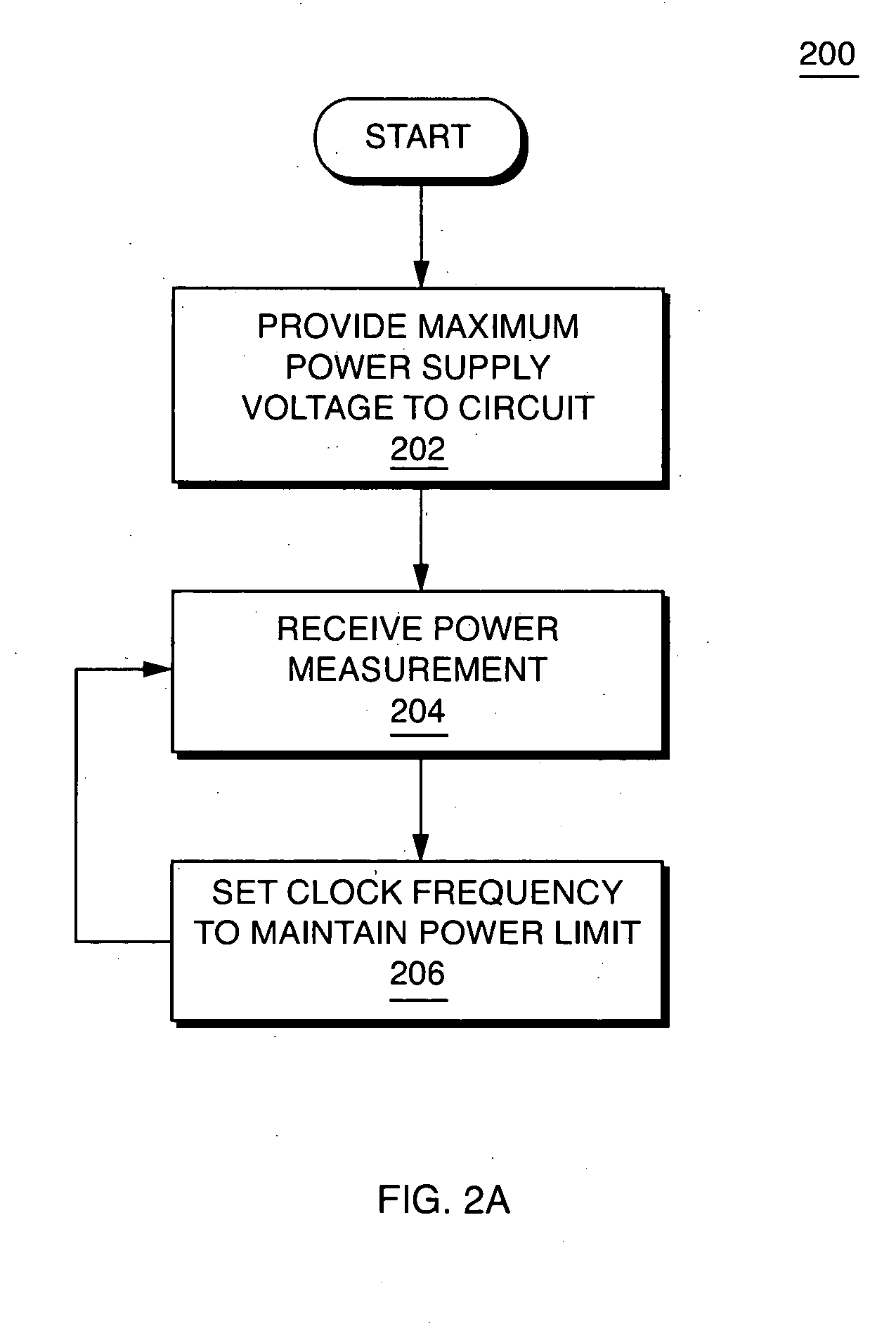

Voltage modulation for increased reliability in an integrated circuit

Techniques are disclosed for increasing reliability of an integrated circuit. In one embodiment, an integrated circuit includes core chip circuitry. The integrated circuit includes means for increasing a power supply voltage V provided to the core chip circuitry, such as by increasing the voltage V to a maximum value. The integrated circuit also includes means for identifying a clock frequency F for which F<Pmax / (CV2), where C is a switching capacitance and where Pmax is a predetermined maximum power consumption of the core chip circuitry. The integrated circuit also includes means for providing a clock signal having frequency F to the circuit.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

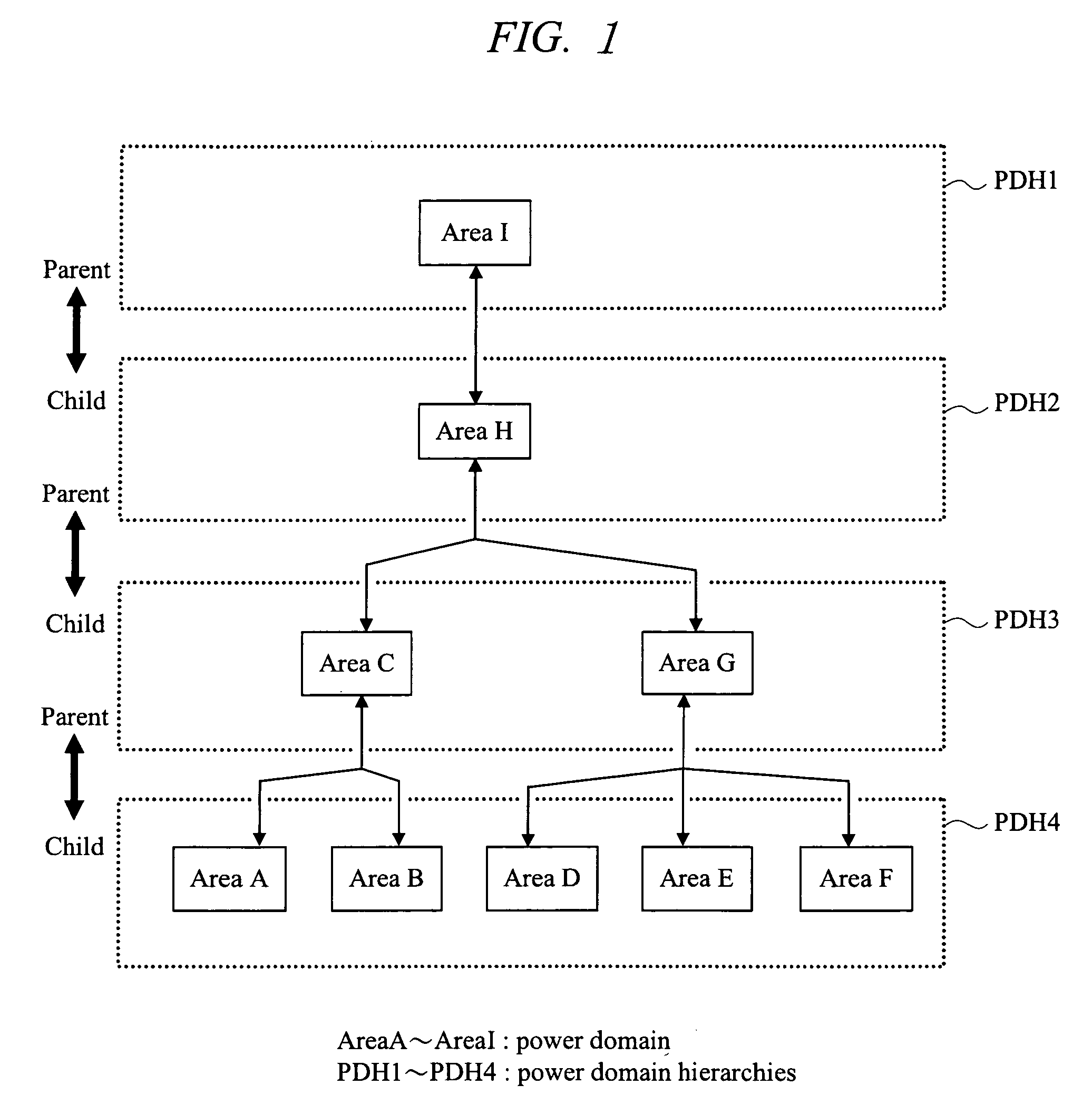

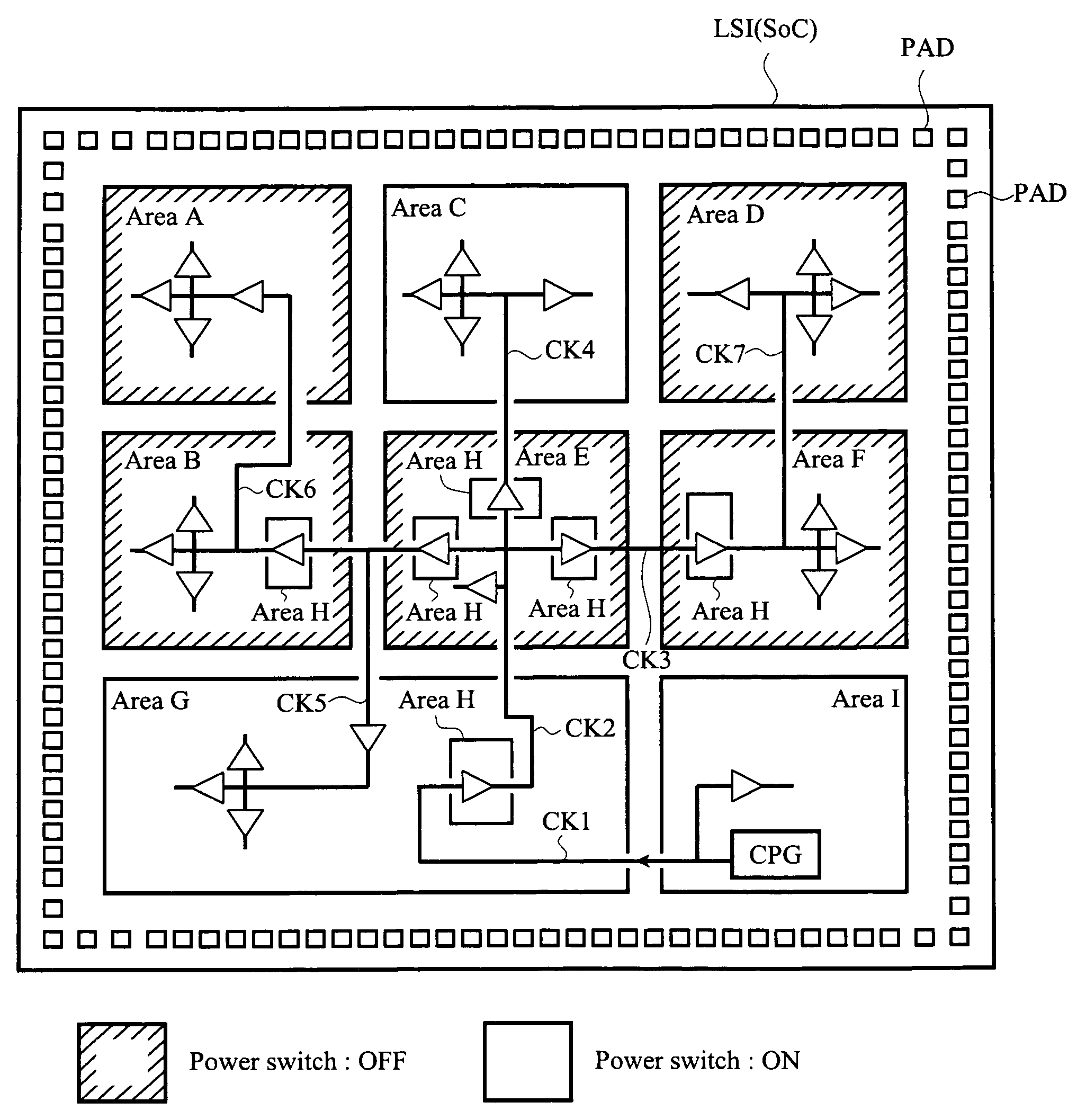

Semiconductor integrated circuit device

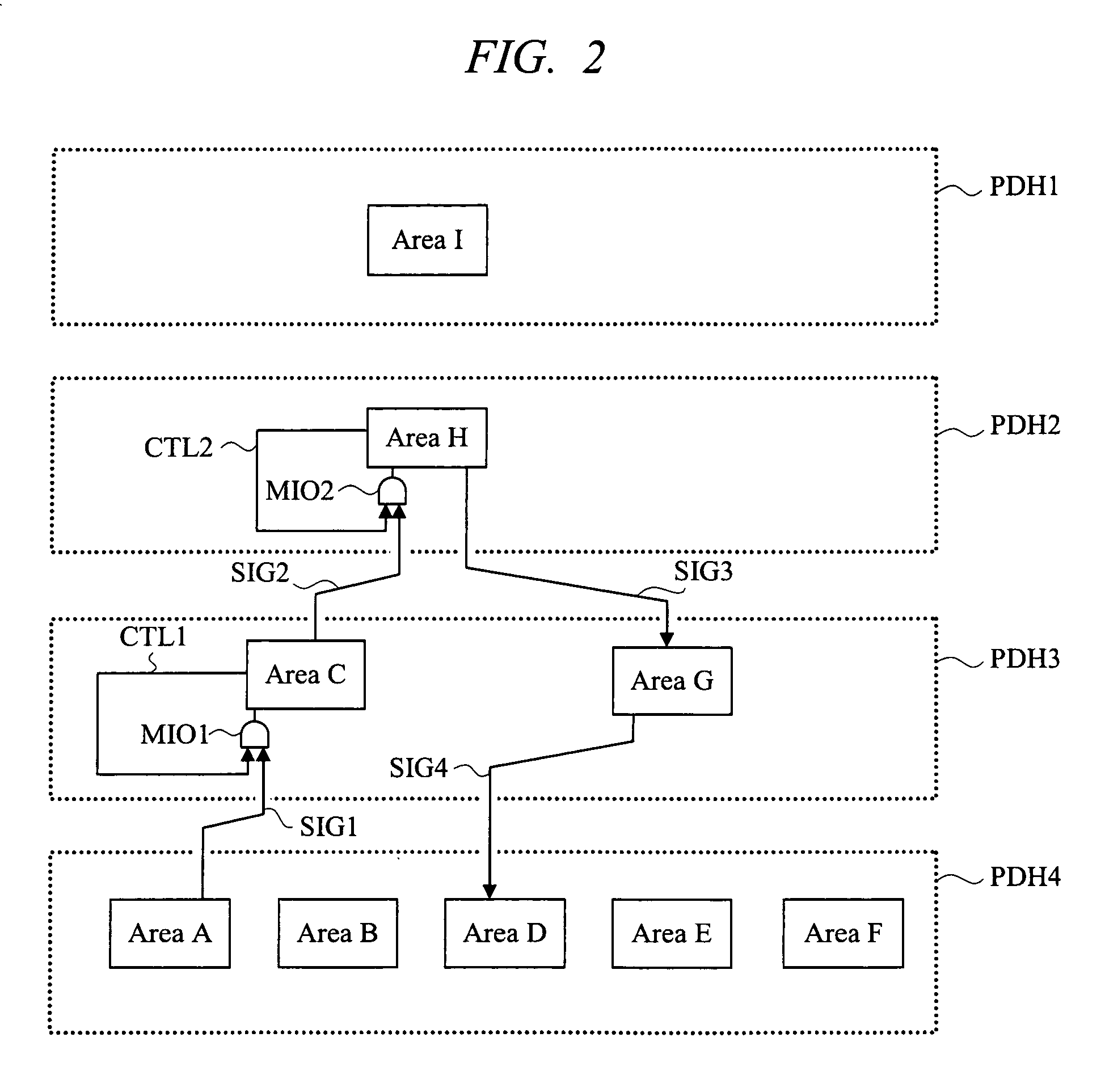

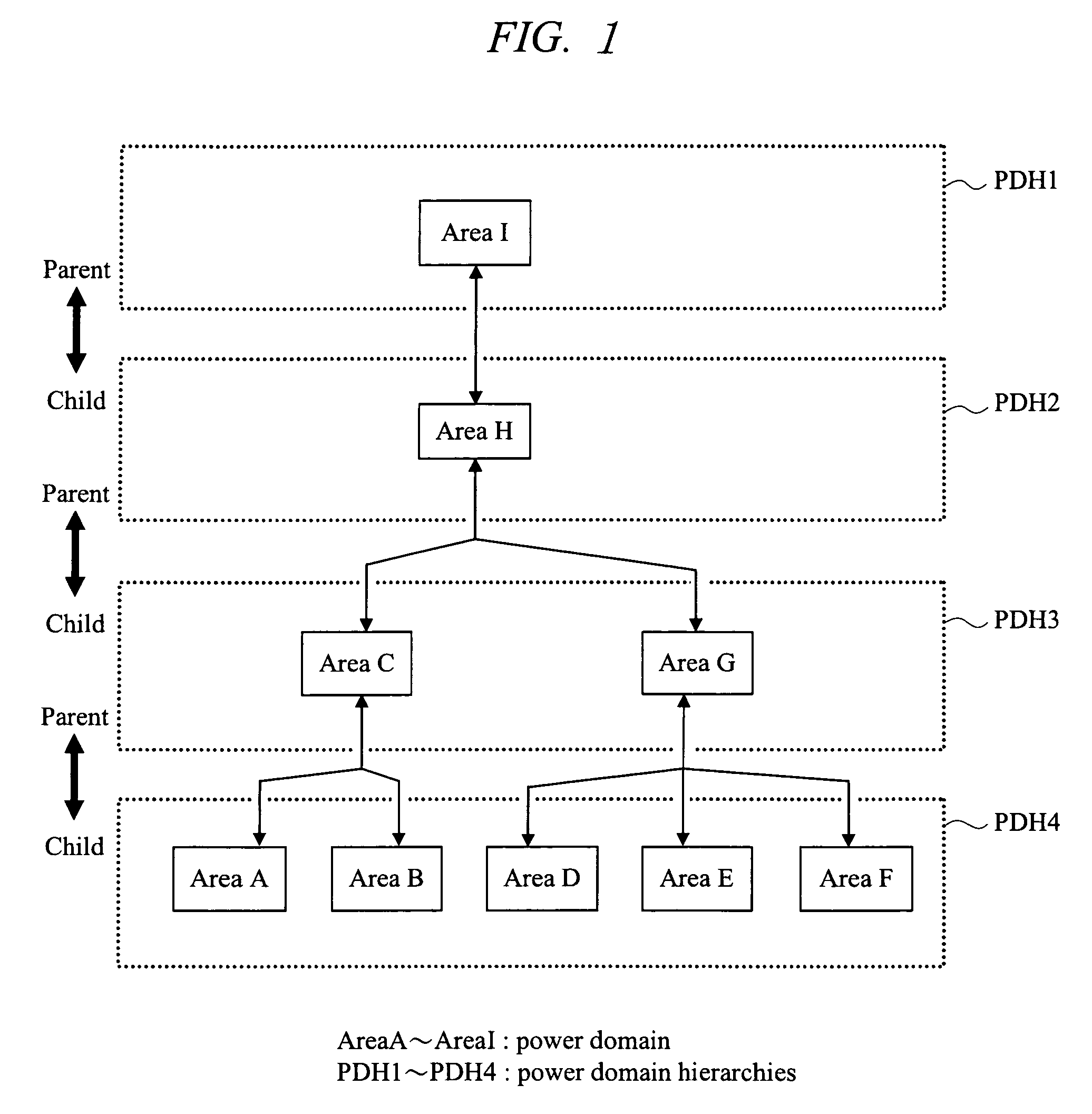

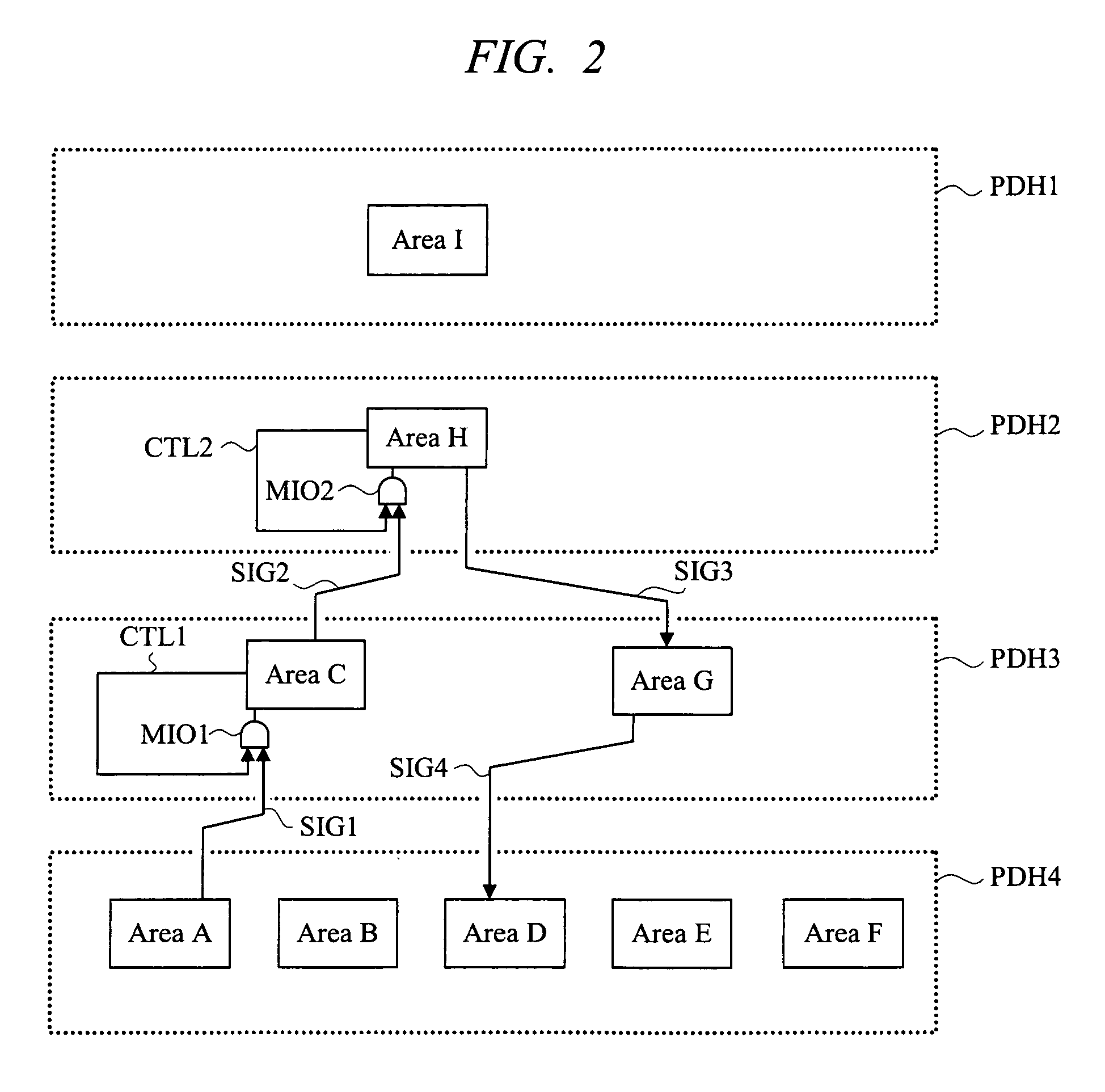

ActiveUS20060291110A1Facilitate power shutdown control inside of a chipPower consumption reductionSemiconductor/solid-state device detailsControl signalEngineering

A semiconductor integrated circuit device is provided, the circuit being capable of arranging a control signal system, avoiding a danger of failure to check an indefinite signal propagation prevention circuit or the like, further facilitating a check oriented to mounting on an automated tool, and facilitating power shutdown control inside of a chip. In the semiconductor integrated circuit device, power shutdown priorities are provided by independent power domains Area A to Area I. A rule is provided, the rule defining that, in the case where a circuit having a high priority is turned ON, a power domain having its lower priority cannot be turned OFF, thereby facilitating a designing method. In addition, areas capable of applying still another power supply are provided in the independent power areas Area A to Area I. In that area, a relay buffer (repeater) and a clock buffer or an information retaining latch for saving information are integrated. A layout may be provided in a direction vertical to a direction in which cells are arranged in a row direction for the purpose of dispersing a current of a light supply line.

Owner:RENESAS ELECTRONICS CORP

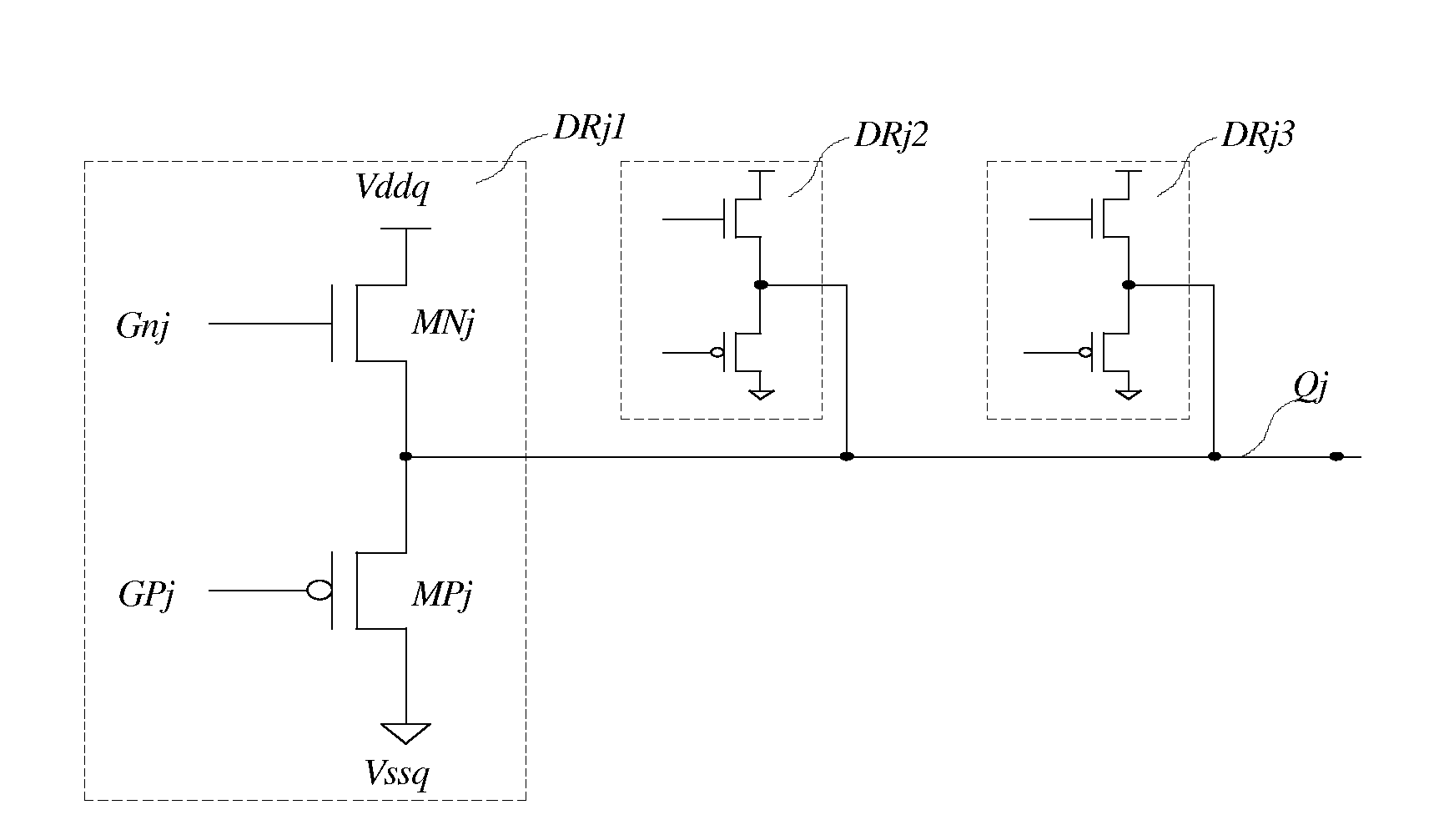

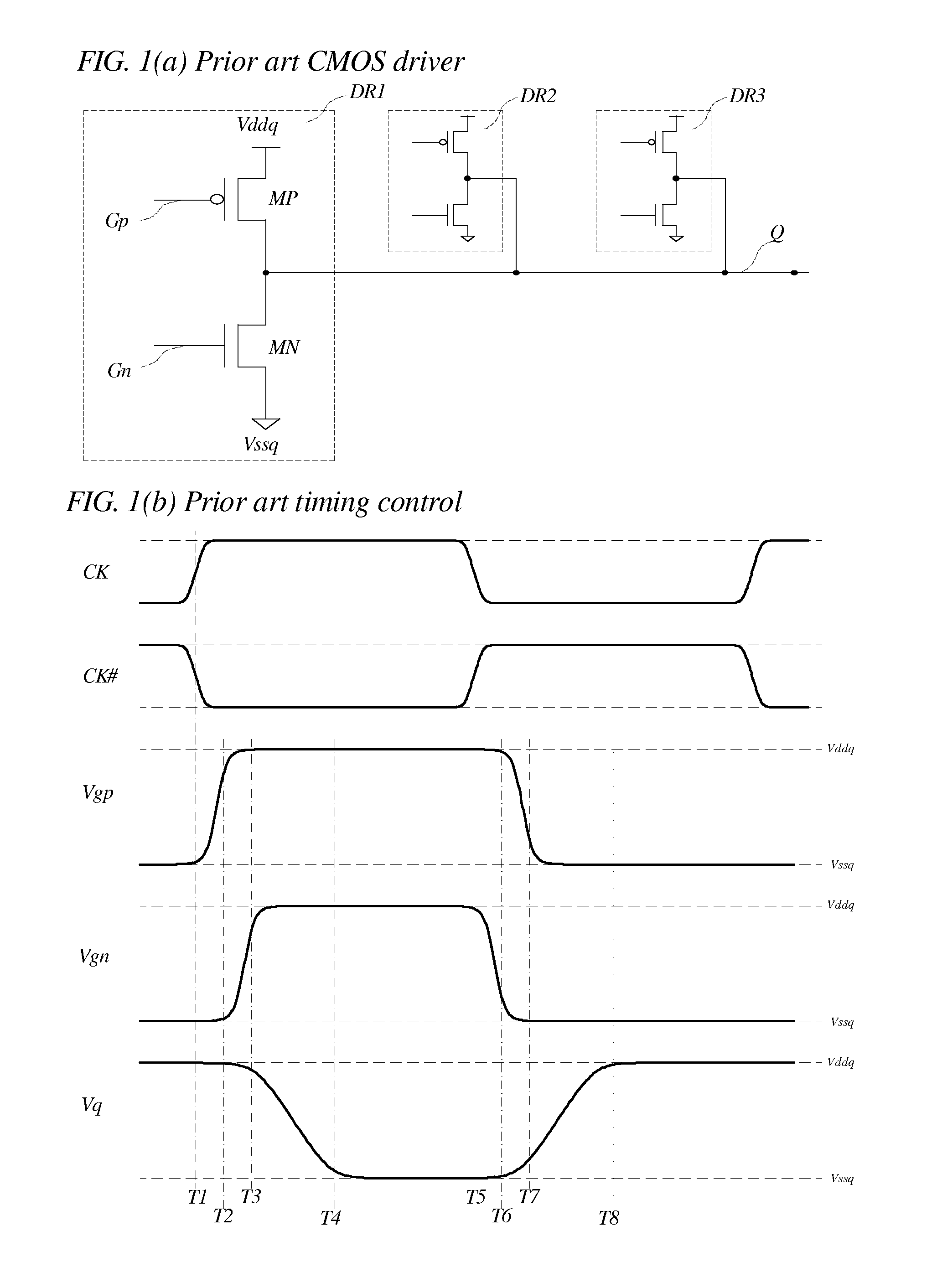

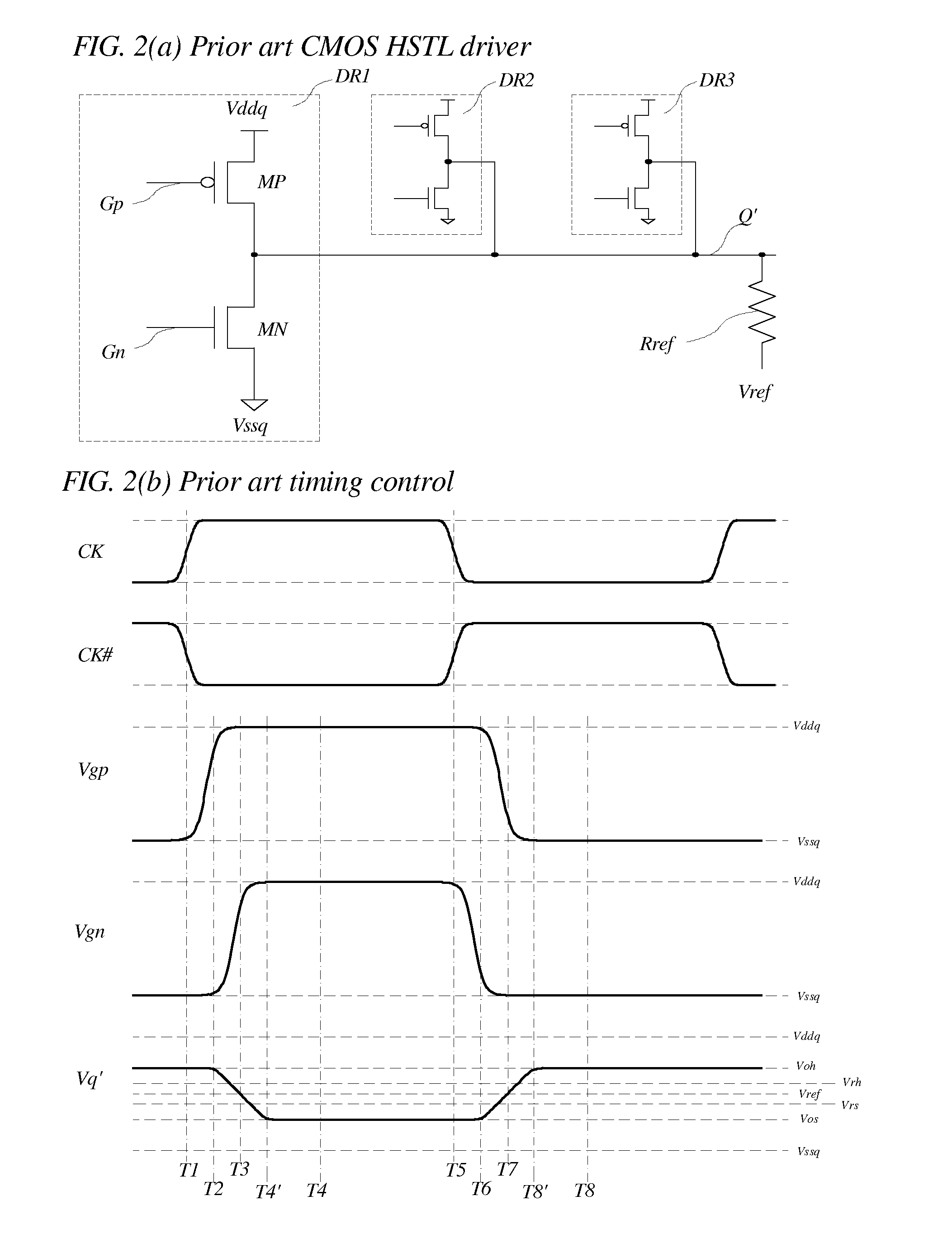

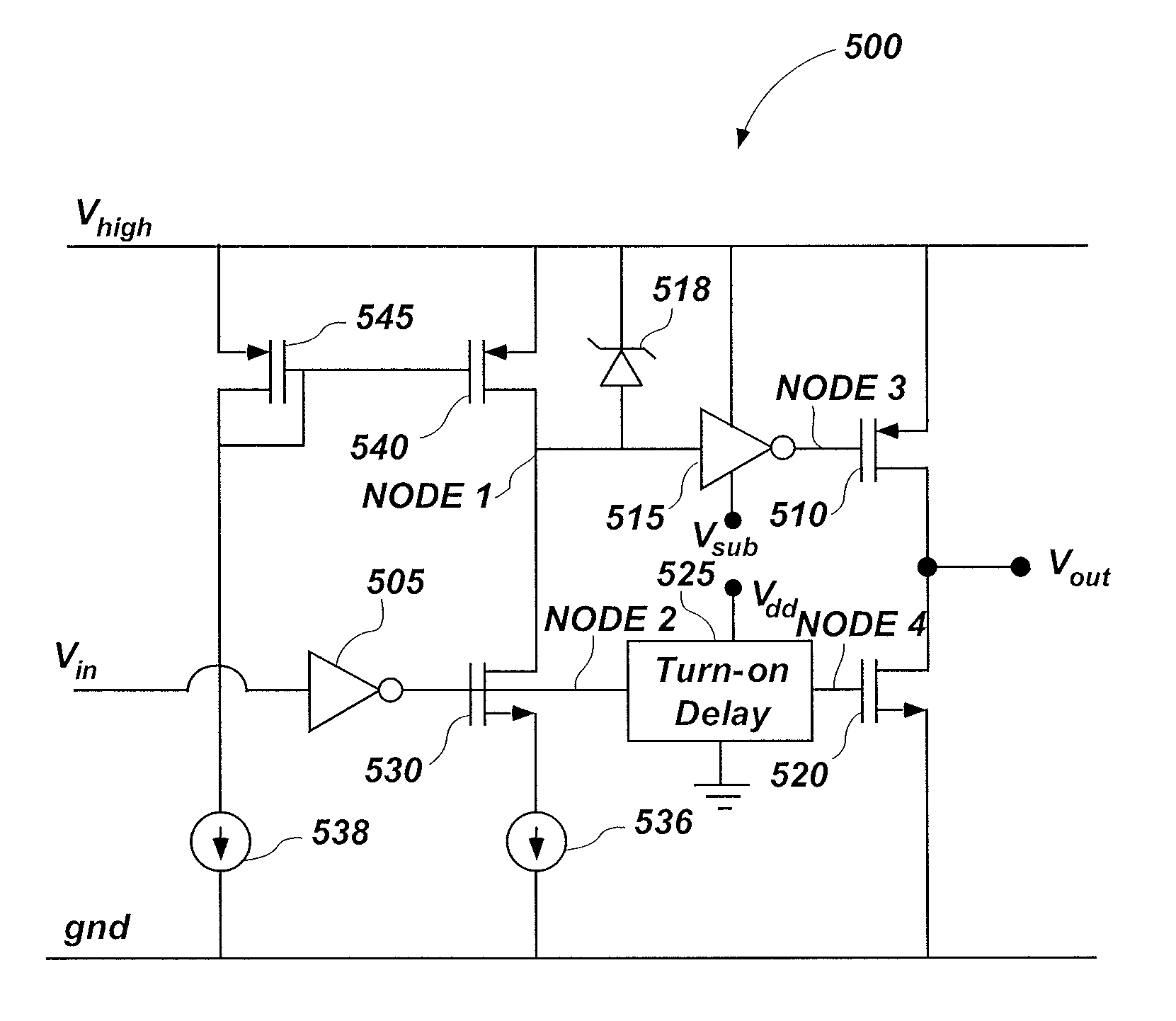

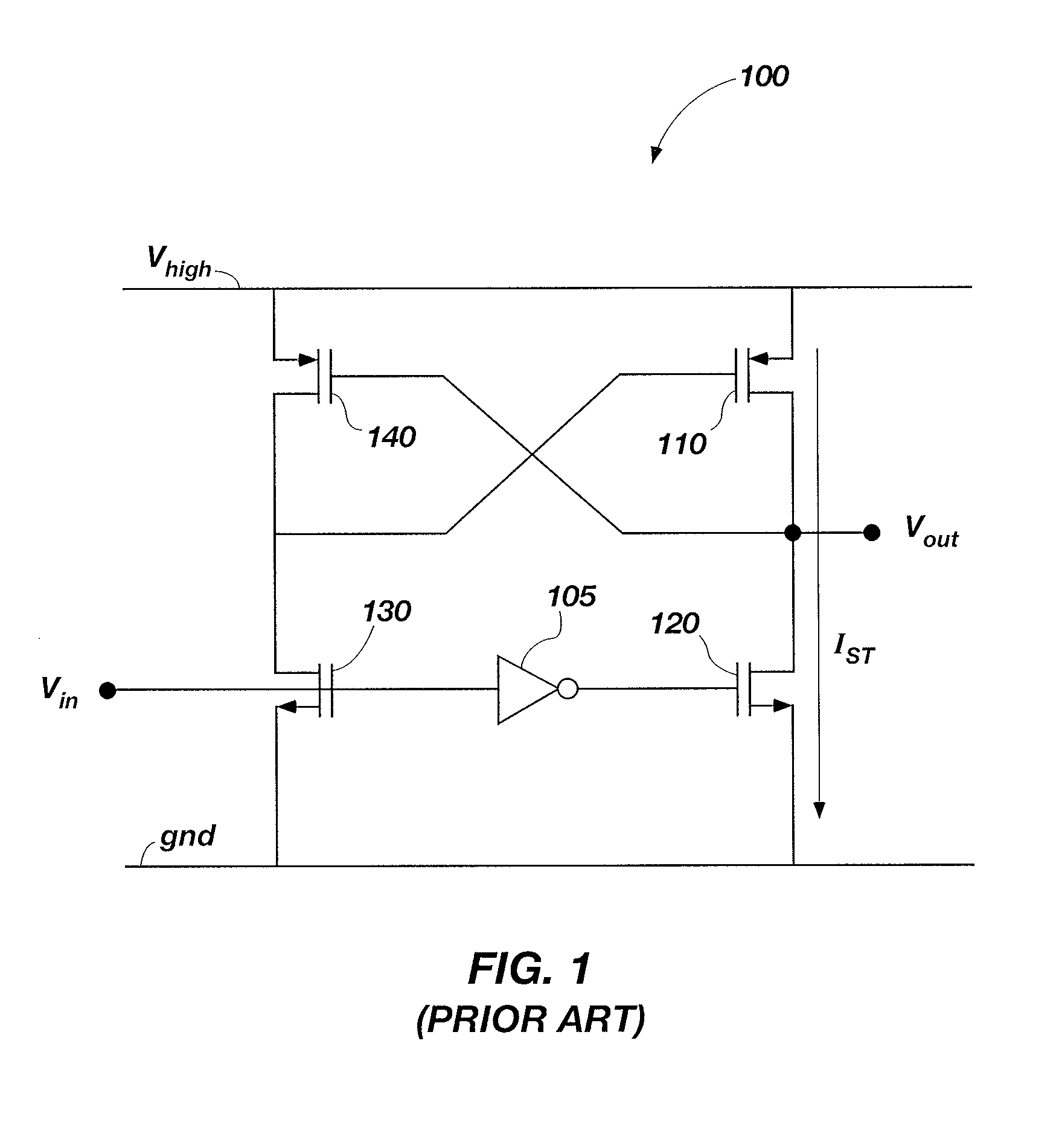

High Performance Low Power Output Drivers

InactiveUS20110133772A1Reduce power consumptionConsuming less powerReliability increasing modificationsPower consumption reductionHemt circuitsControl theory

Long existing performance, noise, and power consumption problems of known output drivers are solved by using n-channel transistors as pull up transistors and / or p-channel transistors as pull down transistors for high performance output drivers. In combination with RC termination circuits, output drivers of the present invention can be fully compatible with HSTL, SSTL, GTL, BTL, SATA, PCIe, LVDS, MIPI, MDDI or other partial voltage interfaces.

Owner:UNIRAM TECH

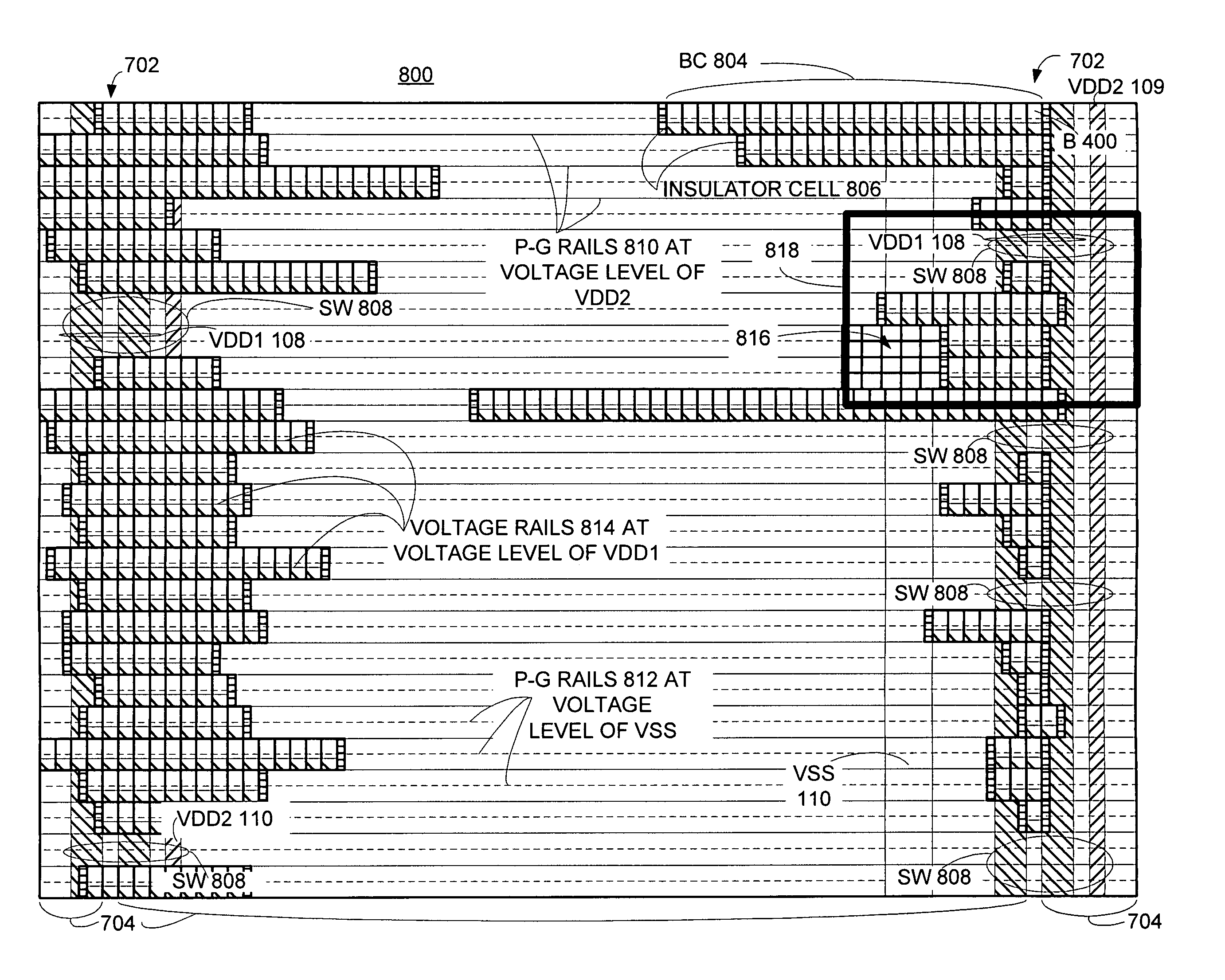

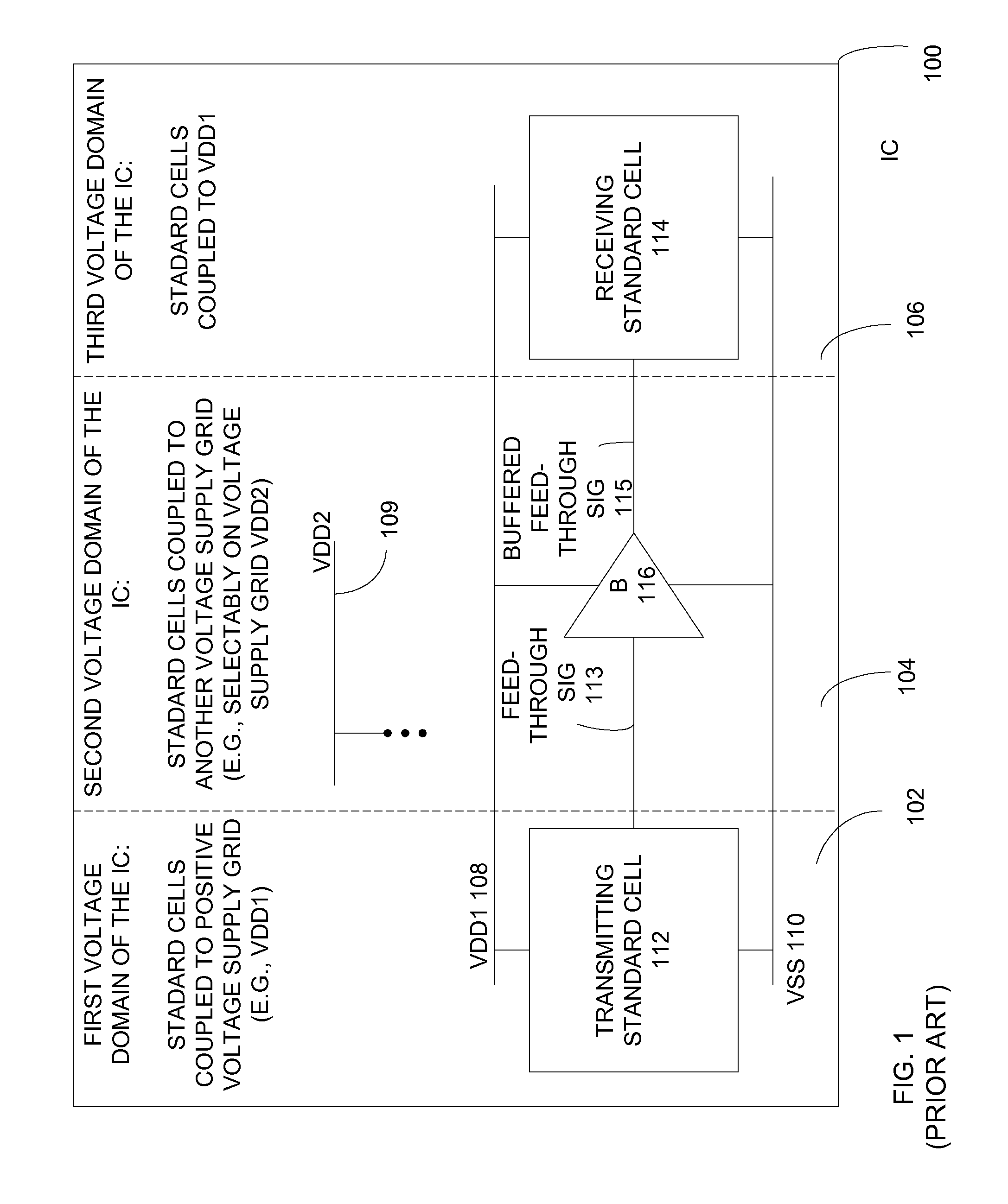

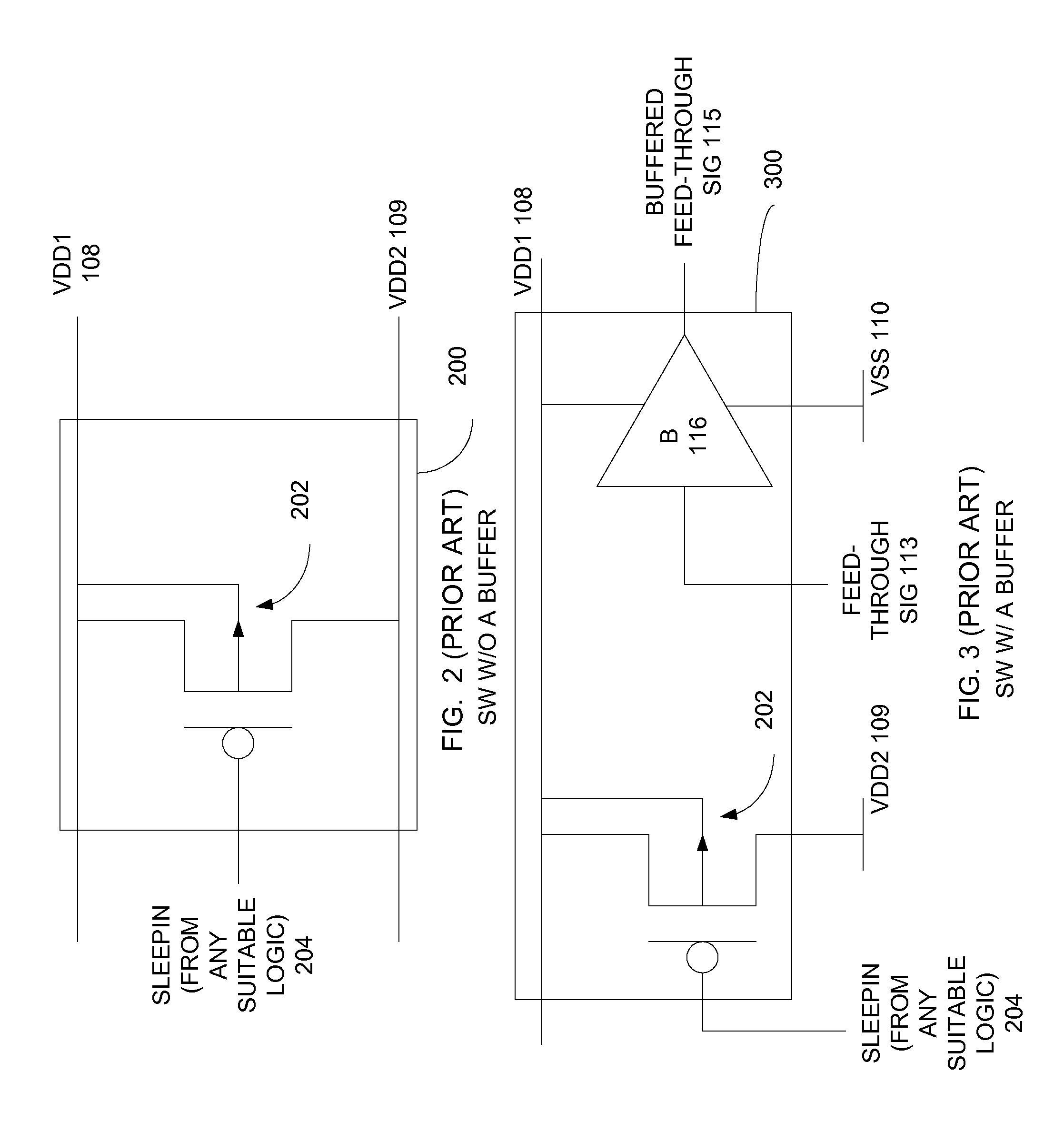

Method and apparatus for buffering signals in voltage domains

An integrated circuit includes first and second voltage domains. The first voltage domain is associated with a positive voltage supply grid and the second voltage domain is associated with a selectably on voltage supply grid. A switch is used to selectably switch on and off the selectably on voltage supply grid to power the second voltage domain. A buffer cell cluster of at least on initial buffer cell and a pair of insulator cells is coupled to the positive voltage supply grid electrically independent of the nodes of a switch and is capable of buffering a feed-through signal having a logic one voltage level defined substantially at the voltage level of the positive voltage supply grid. The buffer cell cluster has two distal ends. buffer cell cluster, at one distal end, is coupled to a first insulator cell of the pair of cells while, at the other distal end, the buffer cell cluster is coupled to a second insulator cell of the pair of the cells.

Owner:ATI TECH INC

Semiconductor integrated circuit device with independent power domains

ActiveUS7610572B2Facilitate power shutdown control inside of a chipPower consumption reductionSemiconductor/solid-state device detailsControl signalEngineering

A semiconductor integrated circuit device having a control signal system for avoiding failure to check an indefinite signal propagation prevention circuit, for facilitating a check included in an automated tool, and for facilitating a power shutdown control inside a chip. In the semiconductor integrated circuit device, power shutdown priorities are provided by independent power domains (Area A to Area I). A method for preventing a power domain having a lower priority from being turned OFF when a circuit having a high priority is turned ON is also provided.

Owner:RENESAS ELECTRONICS CORP

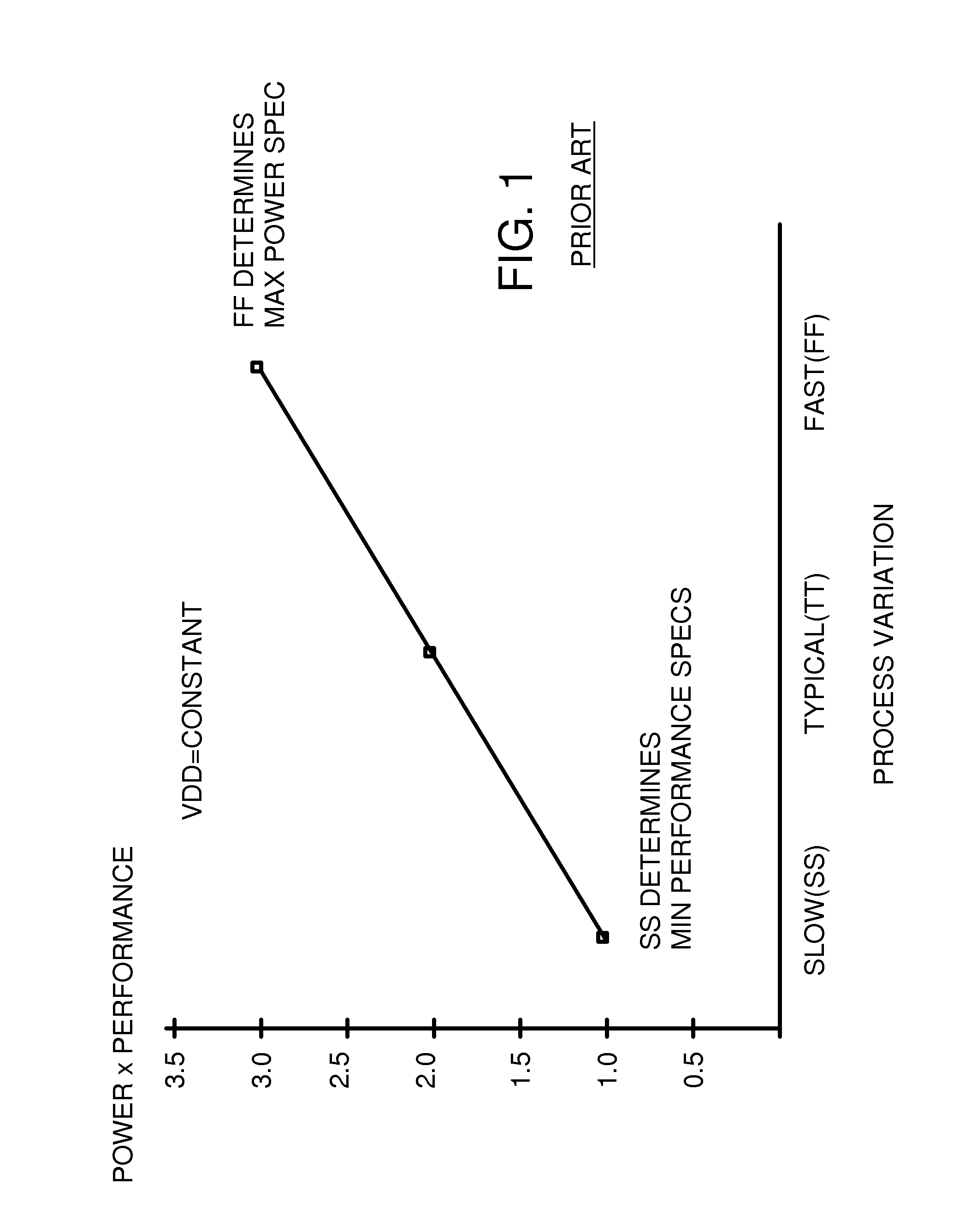

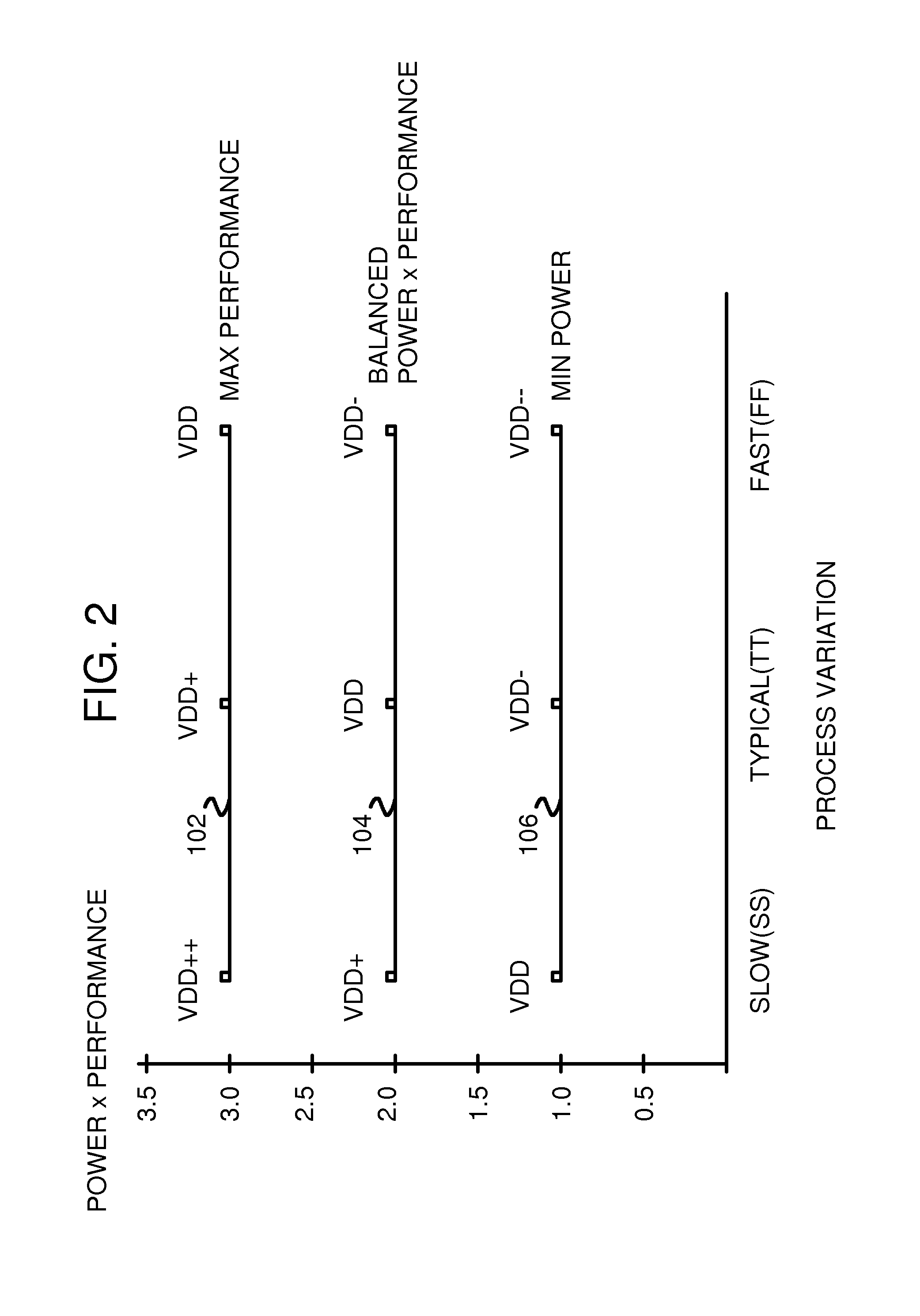

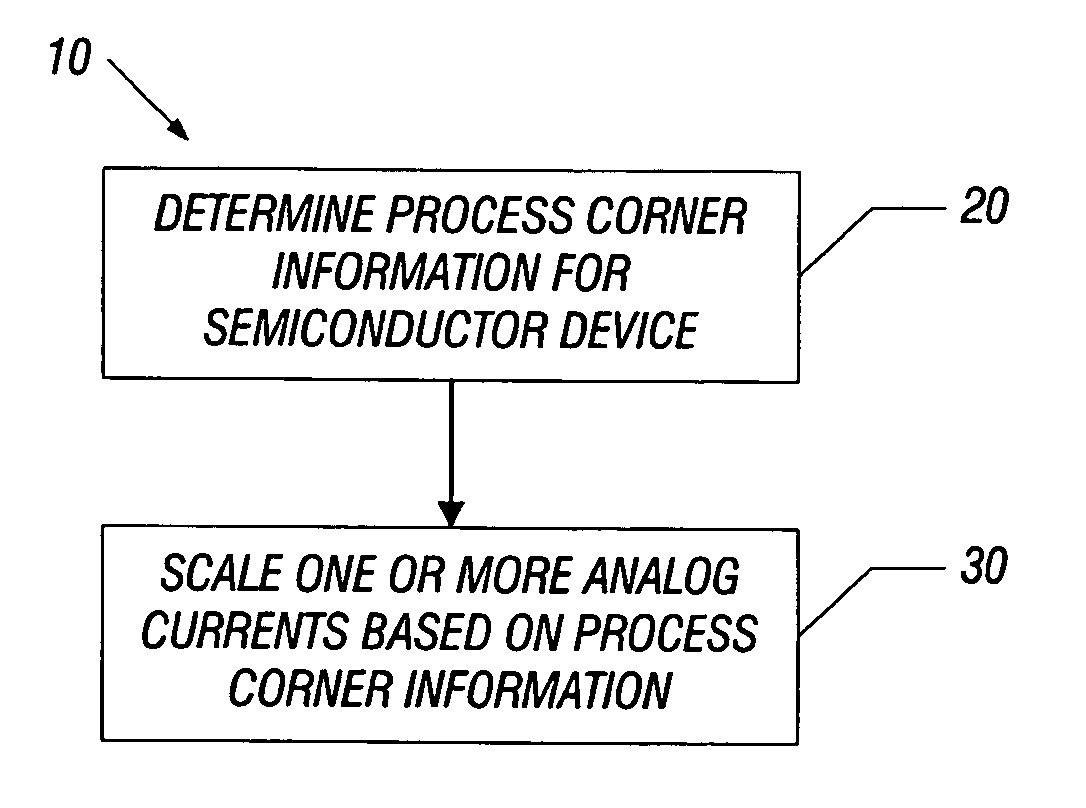

Reducing power dissipation using process corner information

InactiveUS20080076372A1Scale downIncrease currentPower consumption reductionTransmission monitoringCurrent consumptionEngineering

In one embodiment, the present invention includes a method for determining process corner information of an integrated circuit (IC) and controlling at least one analog current for at least one analog circuit of the IC based on the process corner information. More specifically, if the process corner information is indicative of a fast corner IC, the analog current may be scaled down. At the same time that the analog current is scaled down, a current consumption level of digital circuitry of the IC may increase. In this way, overall power consumption of the IC may be reduced to the extent that the analog current(s) are scaled.

Owner:SILICON LAB INC

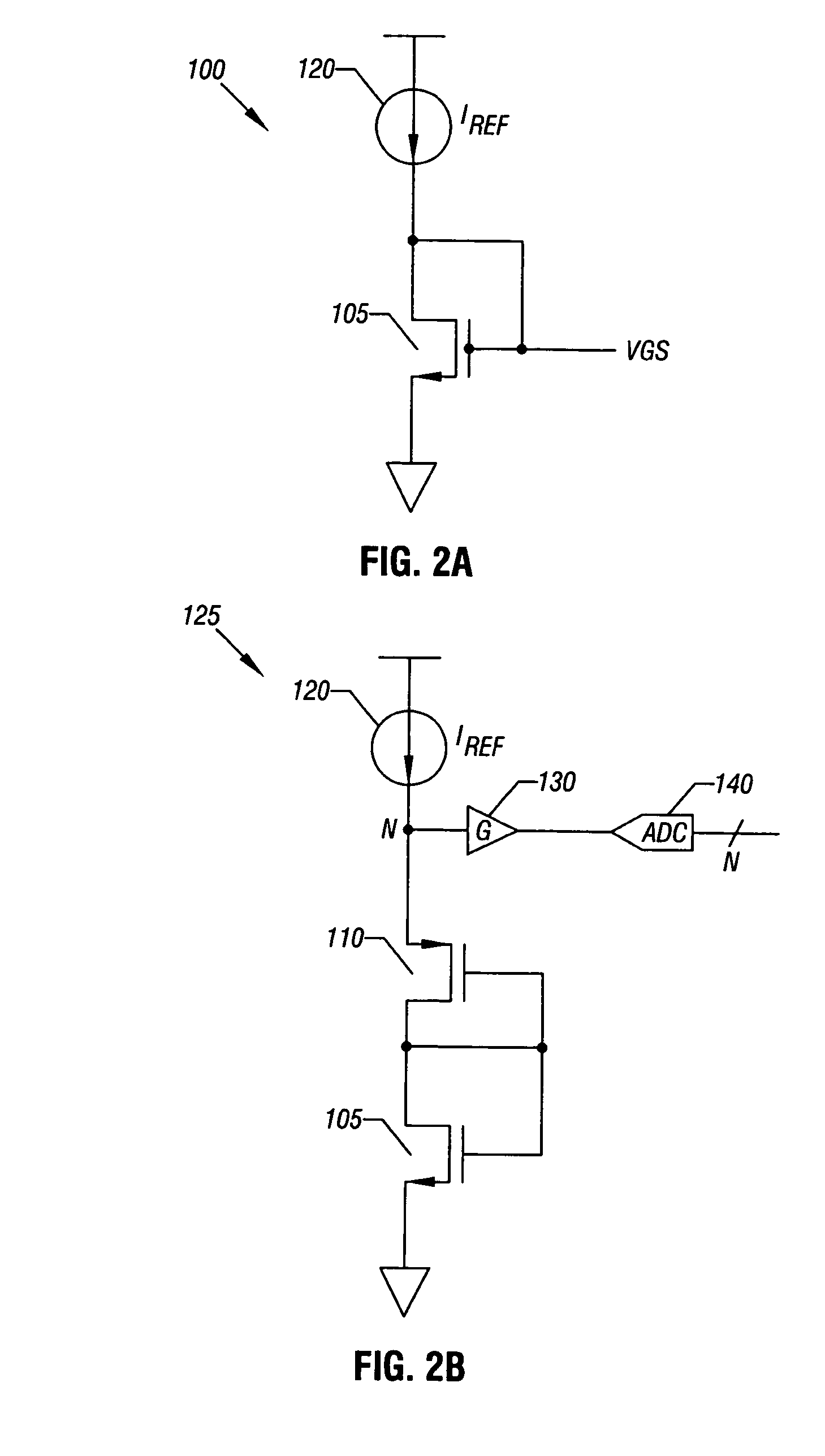

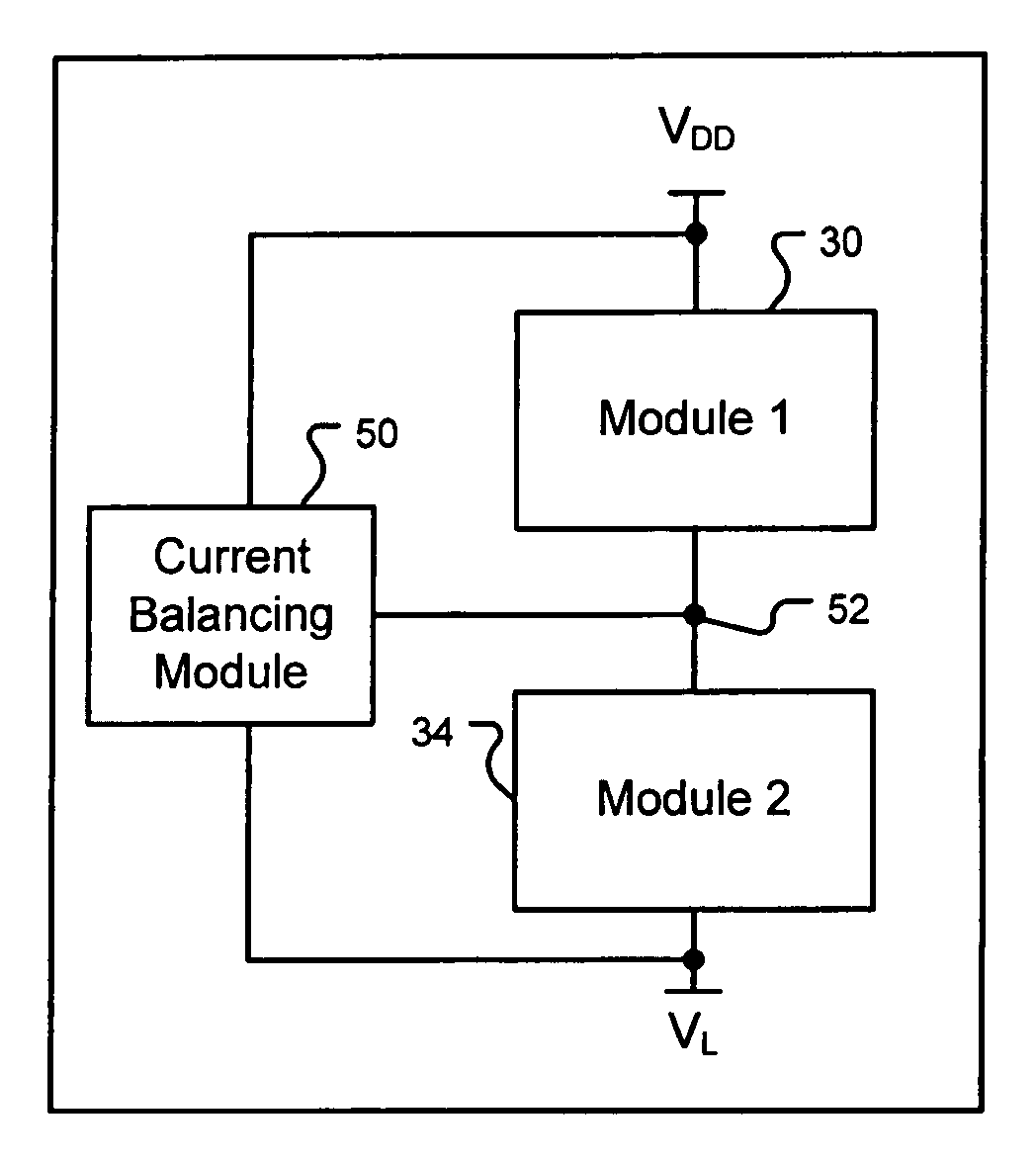

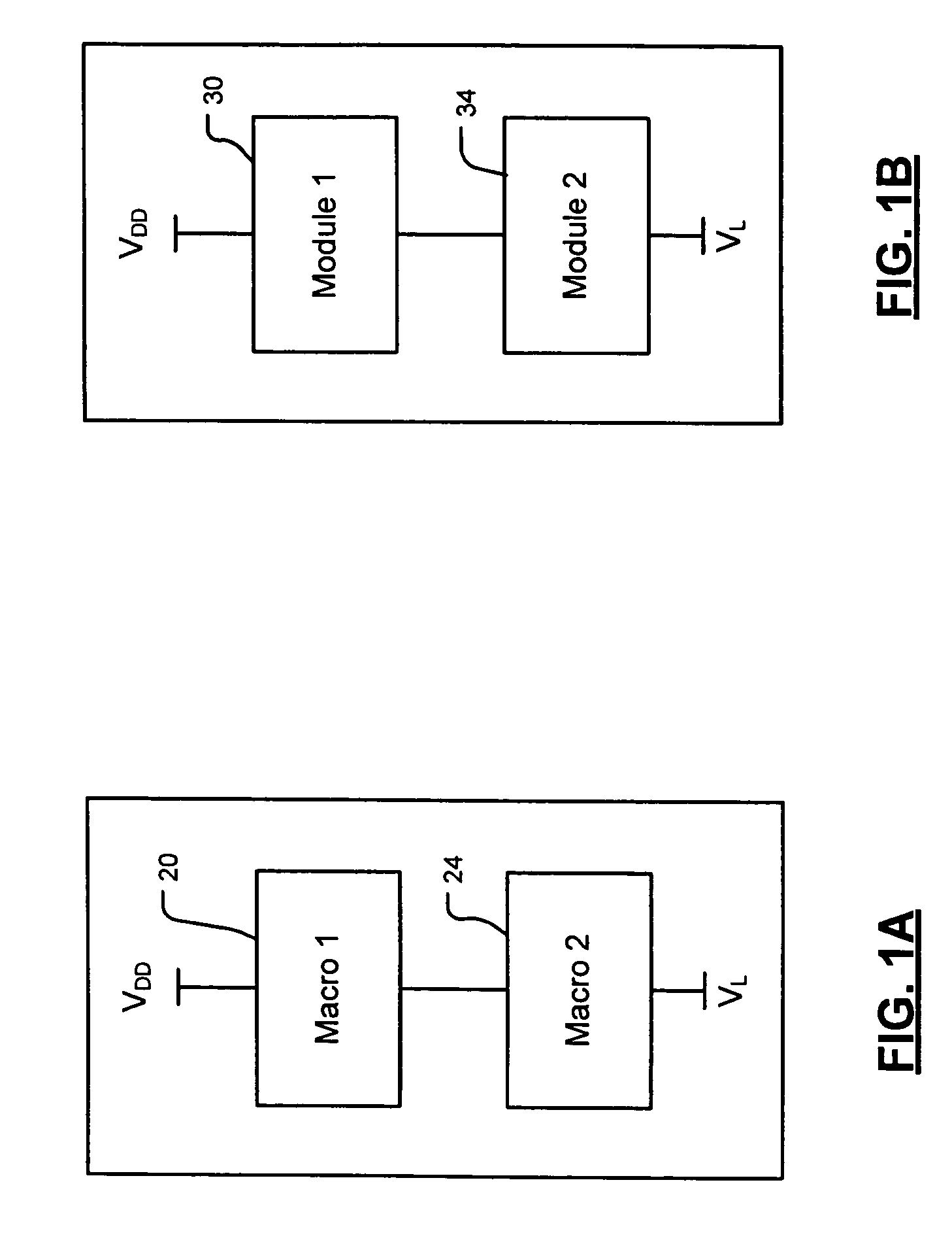

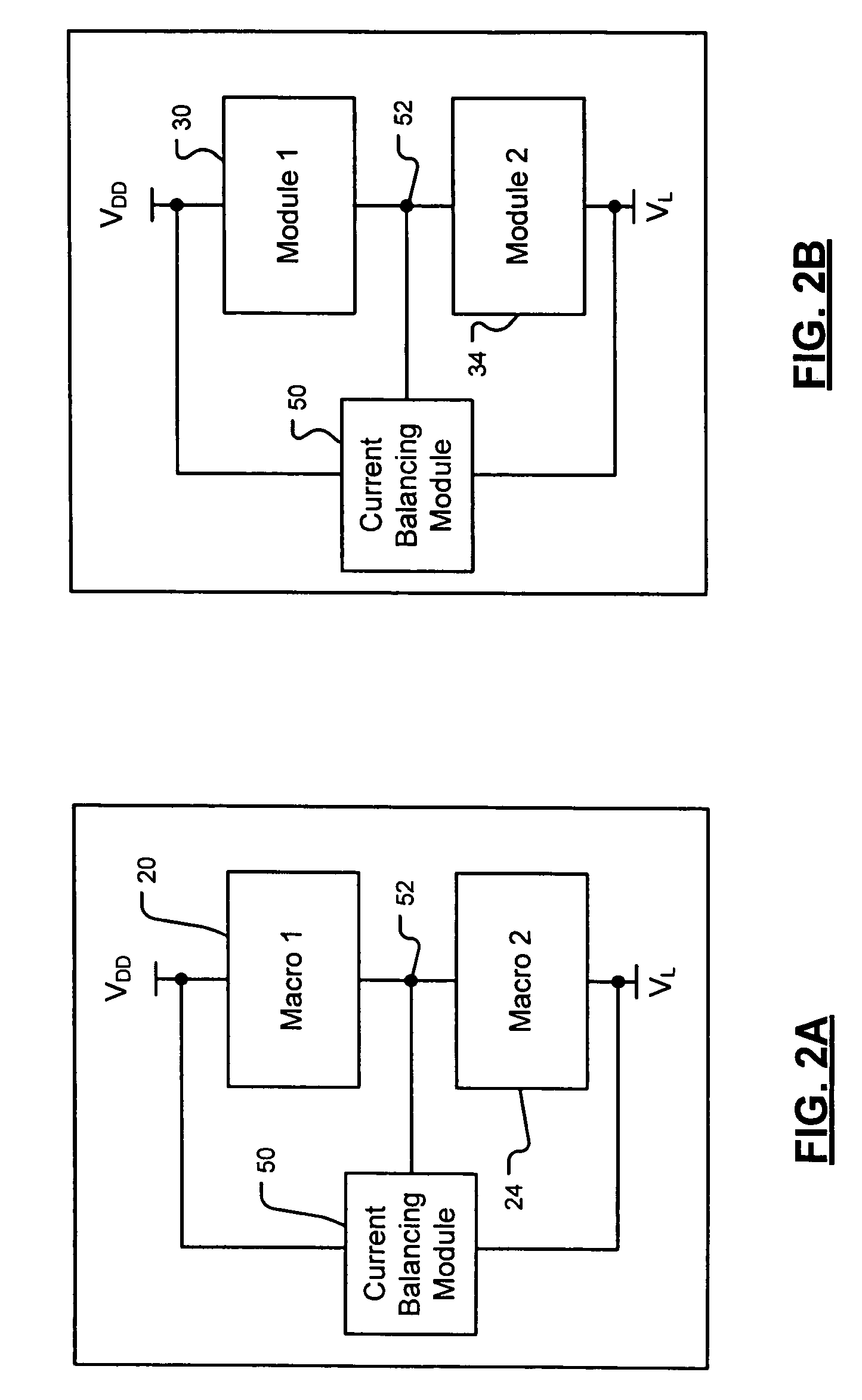

Low voltage logic operation using higher voltage supply levels

ActiveUS7594127B2Reduce the differenceCharge equalisation circuitPower consumption reductionPower flowLow voltage

A circuit comprises a first module and a second module that communicates with the first module. The first and second modules are connected in series between first and second reference potentials. A current balancing module communicates with a node between the first and second modules and reduces a difference in current consumption between the first and second modules.

Owner:MARVELL ASIA PTE LTD

Apparatuses and methods for a level shifter with reduced shoot-through current

A level-shifting circuit with reduced shoot-through current includes an output circuit comprising high-voltage devices with a pull-up circuit configured for pulling up a voltage on an output signal to a high voltage responsive to a high-side control signal. The output circuit may also include a pull-down circuit configured for pulling down the voltage on the output signal to a low voltage in responsive to a low-side control signal. The level-shifting circuit can also include a high-side inverting buffer operably coupled between an edge-controlled signal and the high-side control signal, and a low-side buffer configured for driving the low-side control signal responsive to an input signal. The level-shifting circuit may also include an edge-control buffer operably coupled between the input signal and the high-side inverting buffer and configured to generate the edge-controlled signal with a slow rise time relative to a fall time.

Owner:INTEGRATED DEVICE TECH INC

Popular searches

Diode Digital storage Logic circuits using specific components Nanoinformatics Electronic switching Logic circuits using superconductive devices Hardware monitoring Power supply for data processing Logic circuits using elementary logic circuit components Computation using denominational number representation