Patents

Literature

800523results about How to "Simple structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Color el display and method for producing the same

ActiveUS20080129195A1Quality improvementHigh color purityDischarge tube luminescnet screensLamp detailsDisplay deviceEngineering

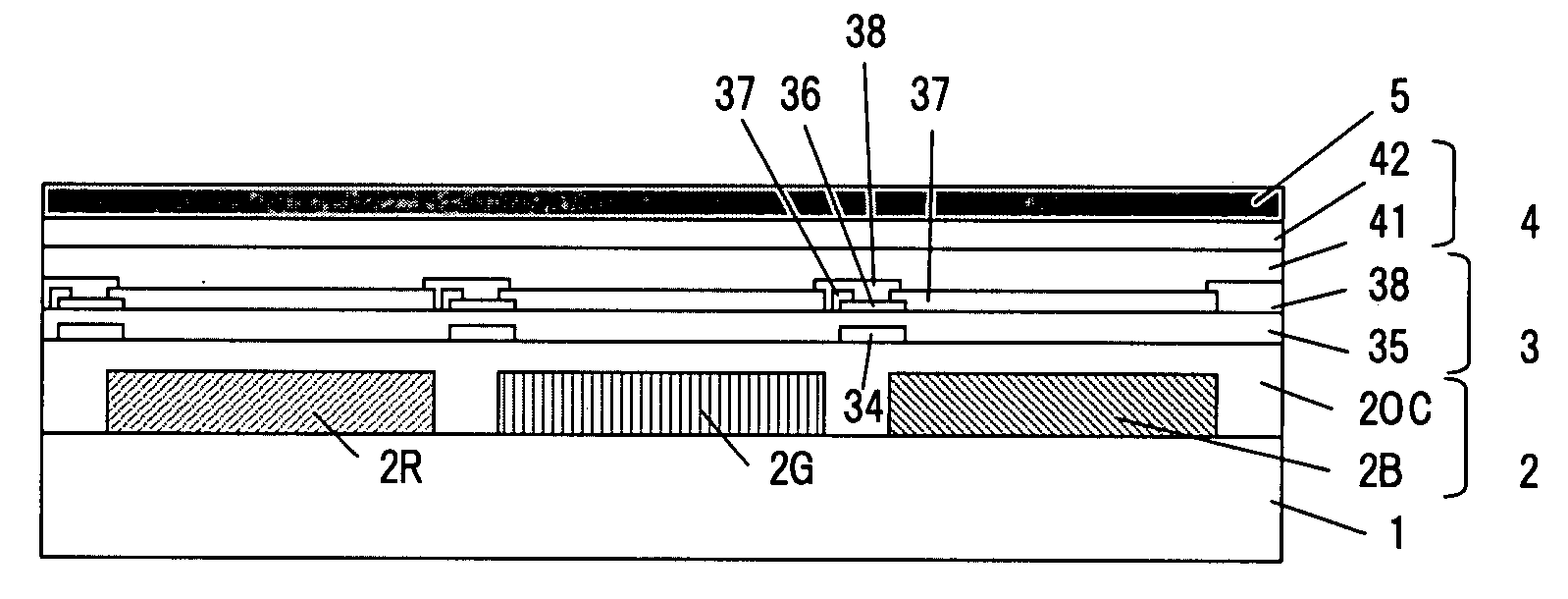

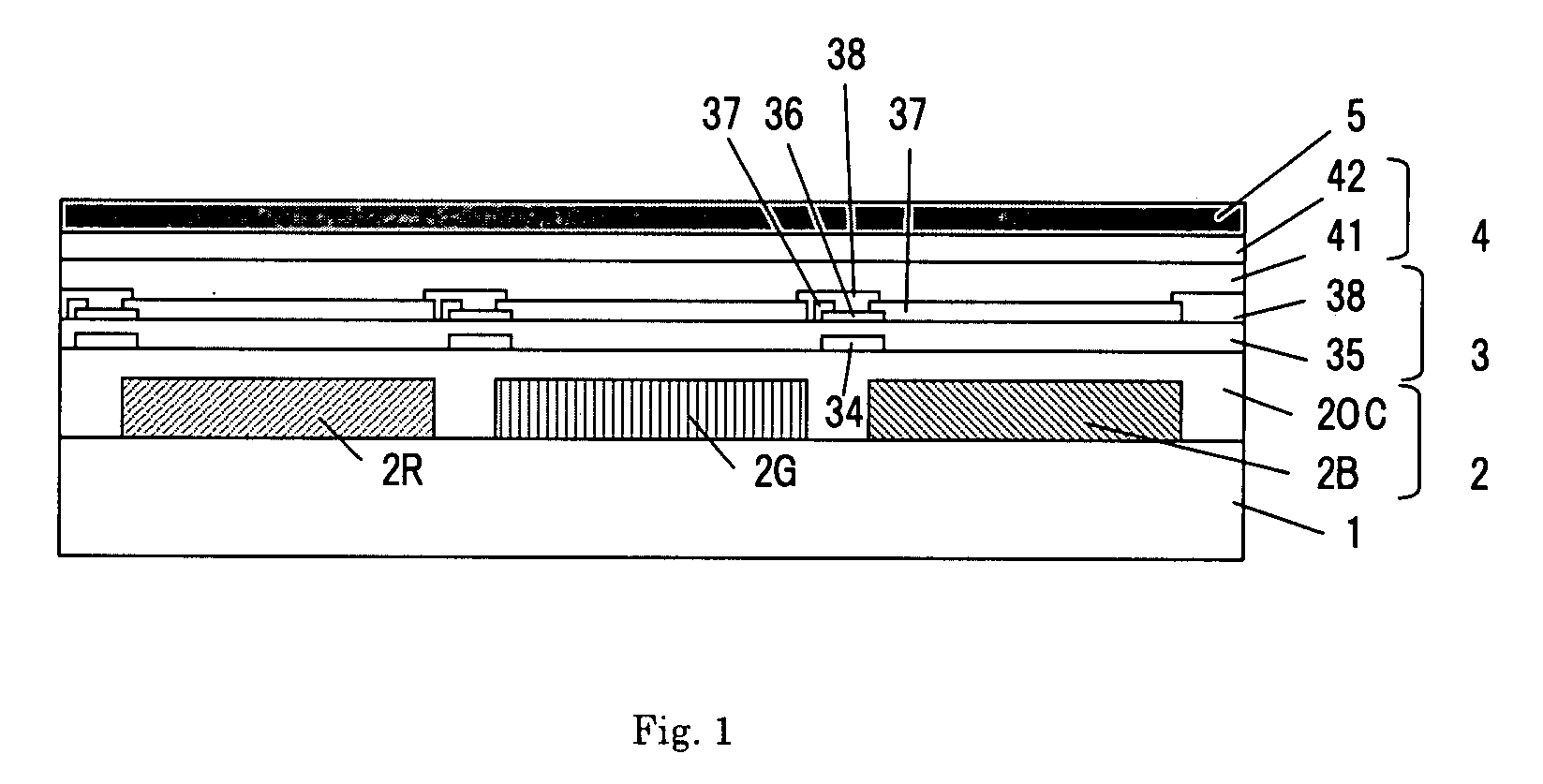

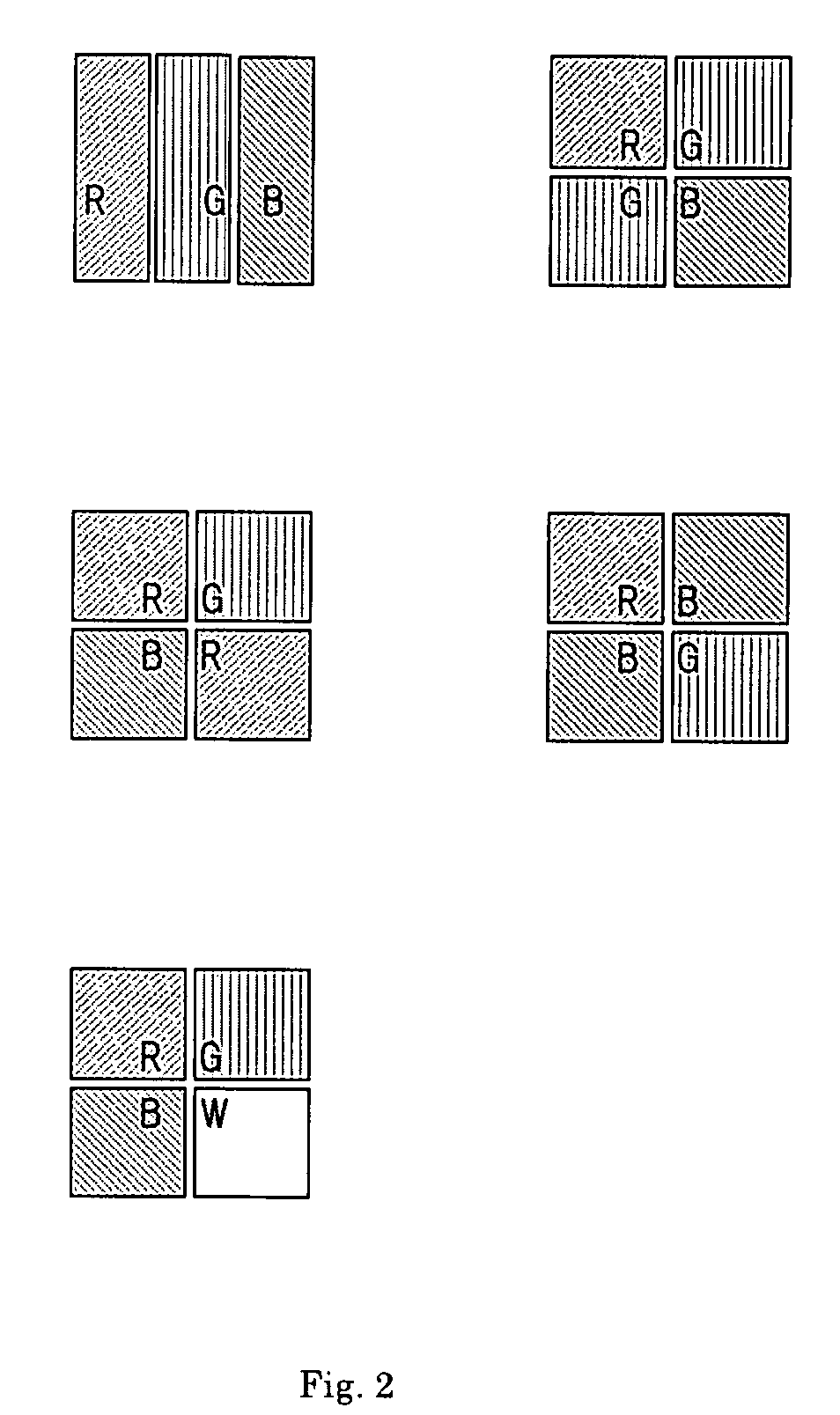

One embodiment of the present invention is a color EL display characterized in that at least color filters, a thin film transistor circuit, an organic EL layer, and a common electrode are laminated in this order on a transparent substrate. Another embodiment of the invention is a method for producing a color EL display comprising the steps of forming color filters or a transparent substrate; forming a thin film transistor circuit; forming an organic EL layer; and forming a common electrode, wherein process temperatures of the steps of forming the thin film transistor circuit and subsequent steps are 200° C. or less.

Owner:TOPPAN PRINTING CO LTD

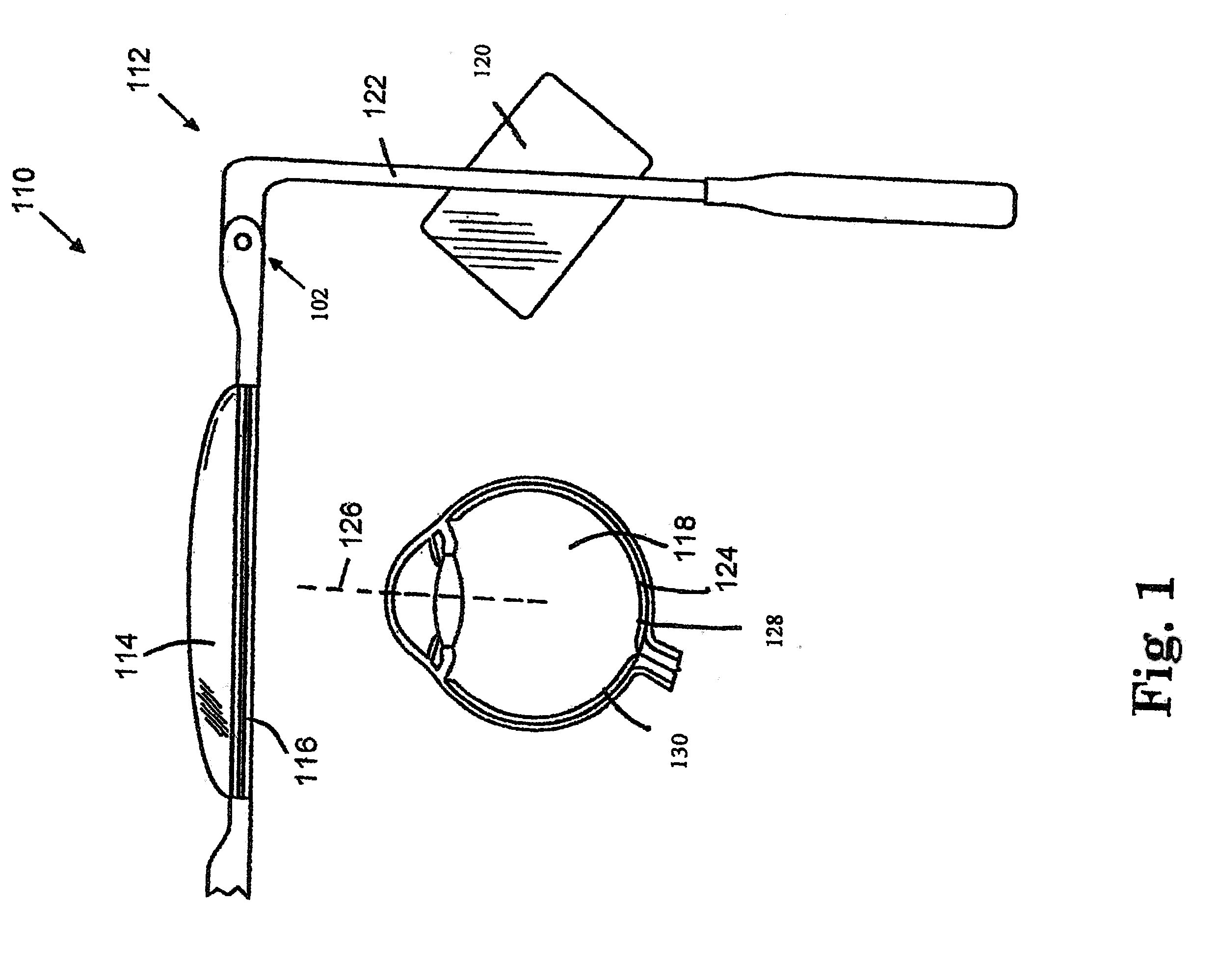

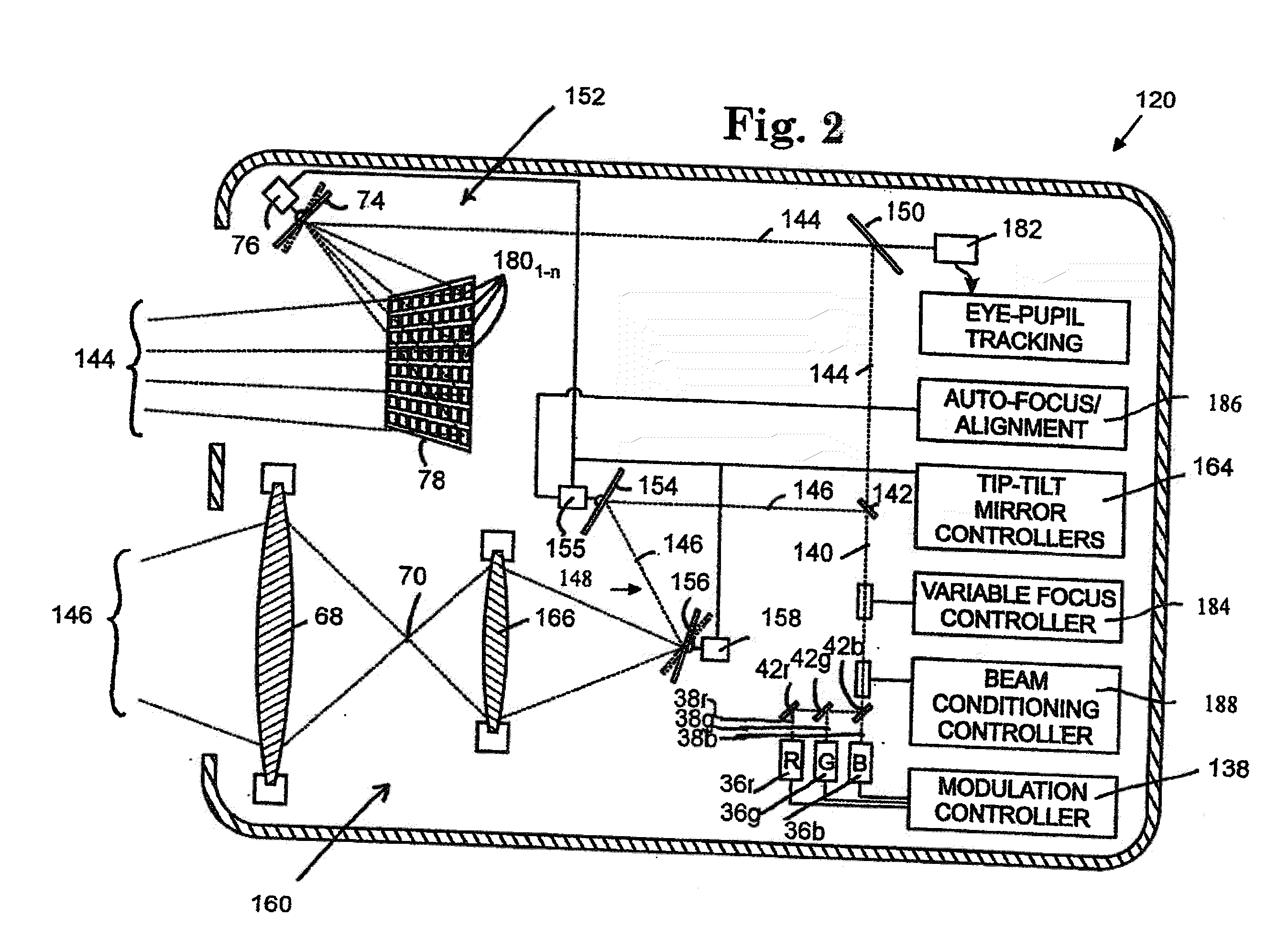

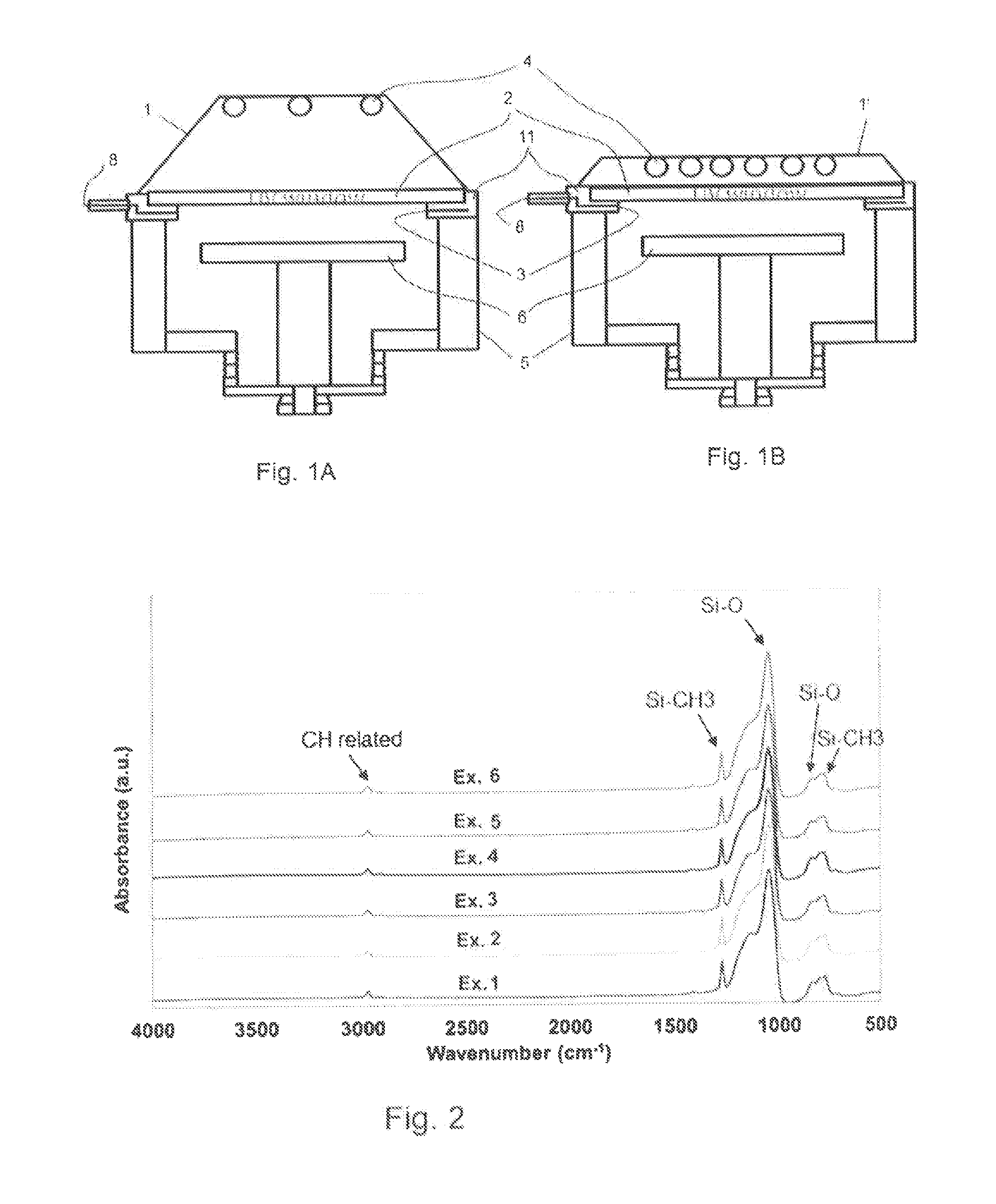

Near to Eye Display System and Appliance

InactiveUS20100149073A1High resolutionCompact and economicalCathode-ray tube indicatorsOptical elementsLight beamPupil

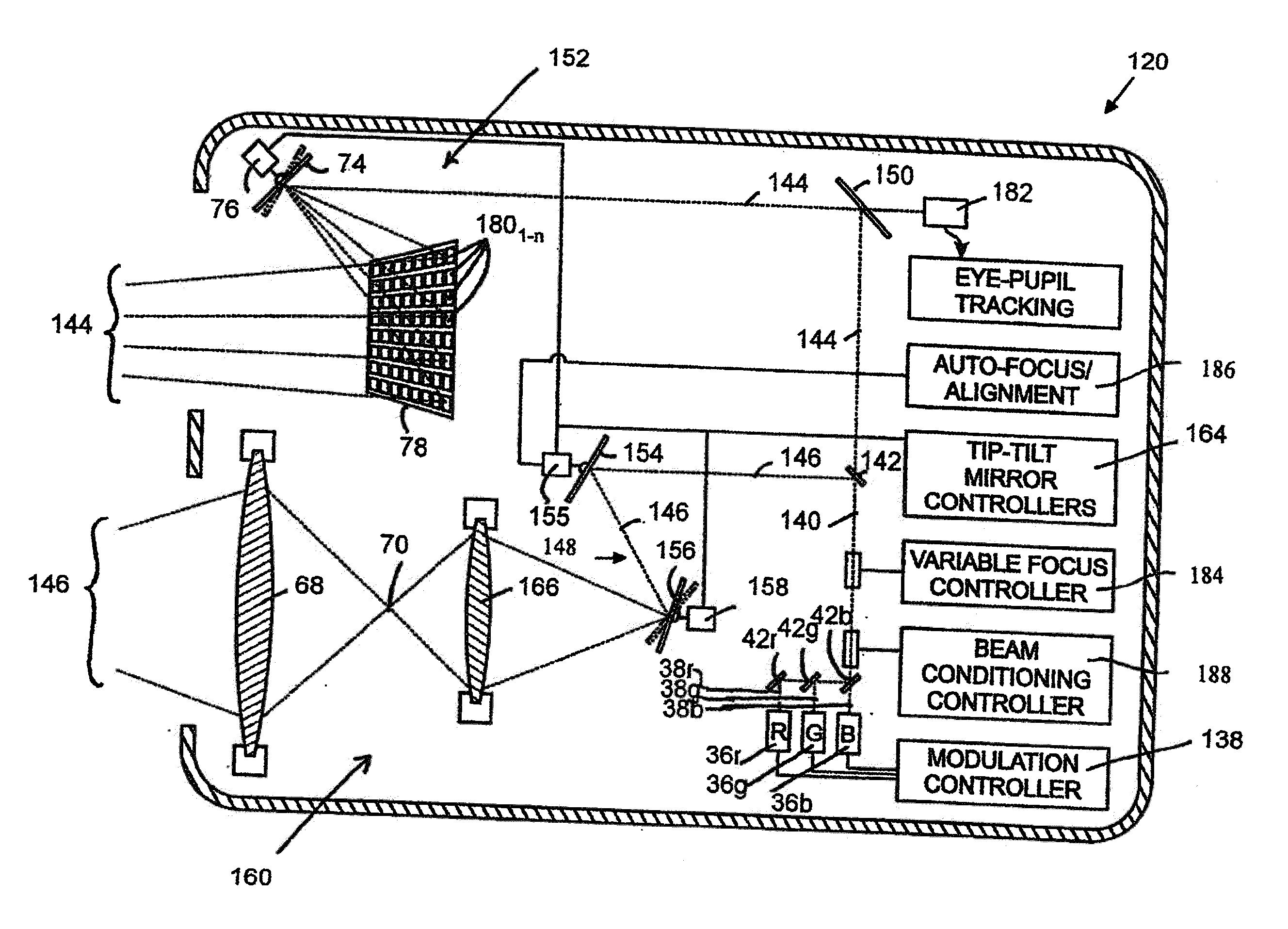

A near-to-eye display system for forming an image as an illuminated region on a retina of at least one eye of a user is disclosed. The system includes a source of modulated light, a proximal optic positionable adjacent an eye of the user to receive the modulated light. The proximal optic has a plurality of groups of optically redirecting regions. The optically redirecting regions are configured to direct a plurality of beams of the modulated light into a pupil of the eye to form a contiguous illuminated portion of the retina of the eye. A first group of the optically redirecting regions is configured to receive modulated light from the source and redirect beams of the modulated light into the pupil of the eye for illumination of a first portion of the retina. A second group of the optically redirecting regions is configured to receive modulated light from the source and redirect beams of the modulated light into the pupil of the eye for illumination of a second portion of the retina.

Owner:CHAUM DAVID +2

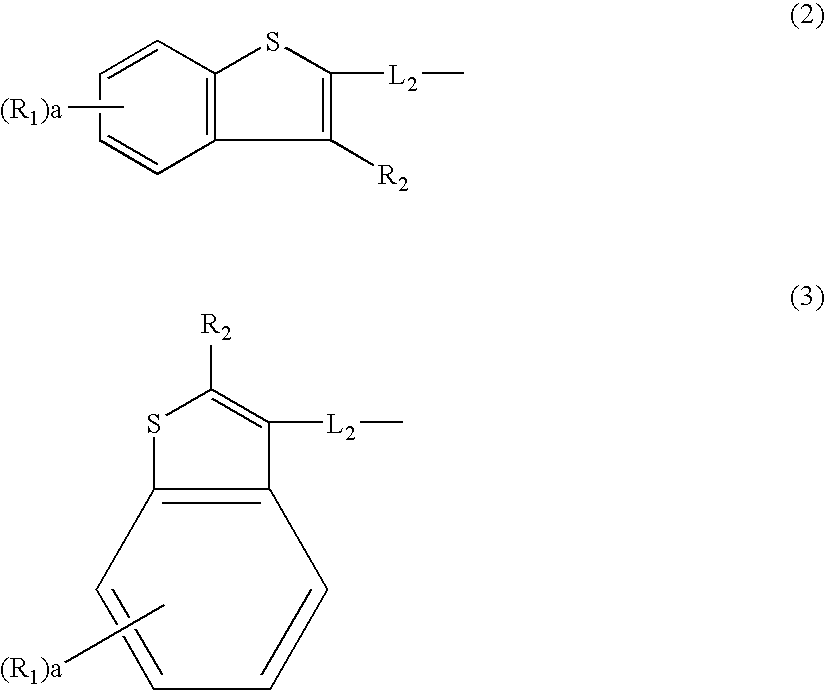

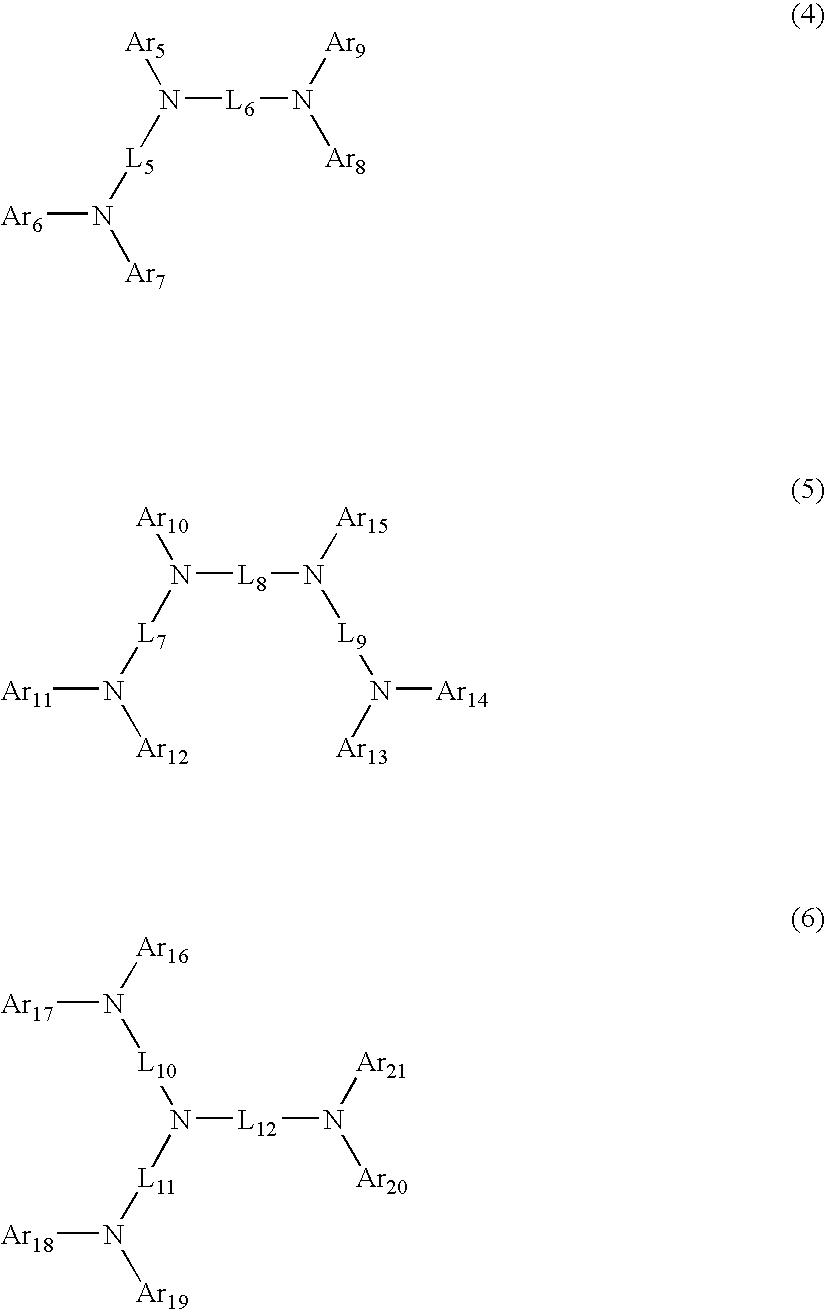

Aromatic amine derivatives and organic electroluminescent device using same

InactiveUS20080106190A1Less liableImproved in yield in producingOrganic chemistryDischarge tube luminescnet screensHole transport layerOrganic electroluminescence

The present invention provides a novel aromatic amine derivative having a specific structure and an organic electroluminescence device in which an organic thin film layer comprising a single layer or plural layers including at least a light emitting layer is interposed between a cathode and an anode, wherein at least one layer in the above organic thin film layer, particularly a hole transporting layer contains the aromatic amine derivative described above in the form of a single component or a mixed component. Use of the aromatic amine derivative described above materialize an organic electroluminescence device which reduces a driving voltage and makes molecules less liable to be crystallized and which enhances a yield in producing the organic EL device and has a long lifetime.

Owner:IDEMITSU KOSAN CO LTD

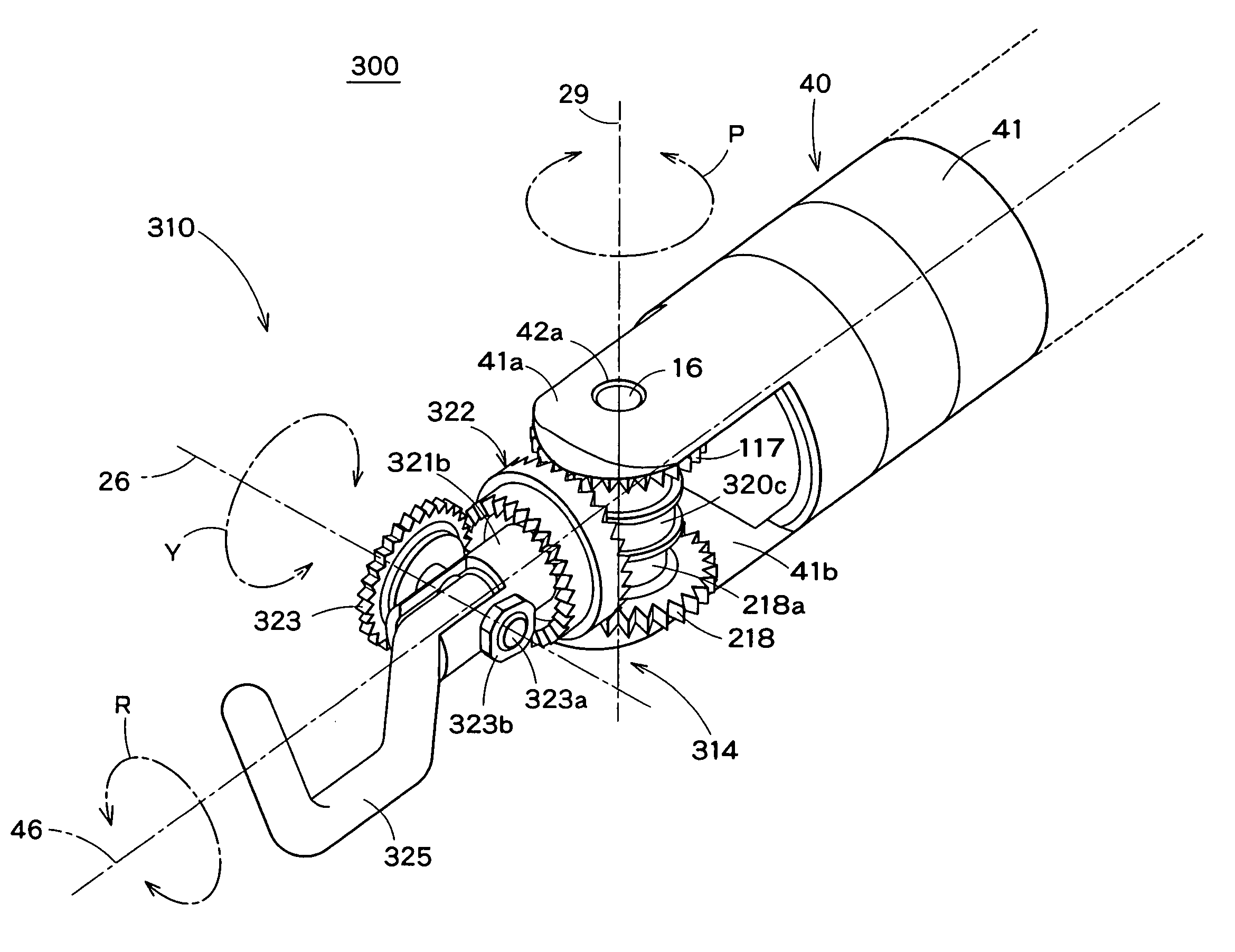

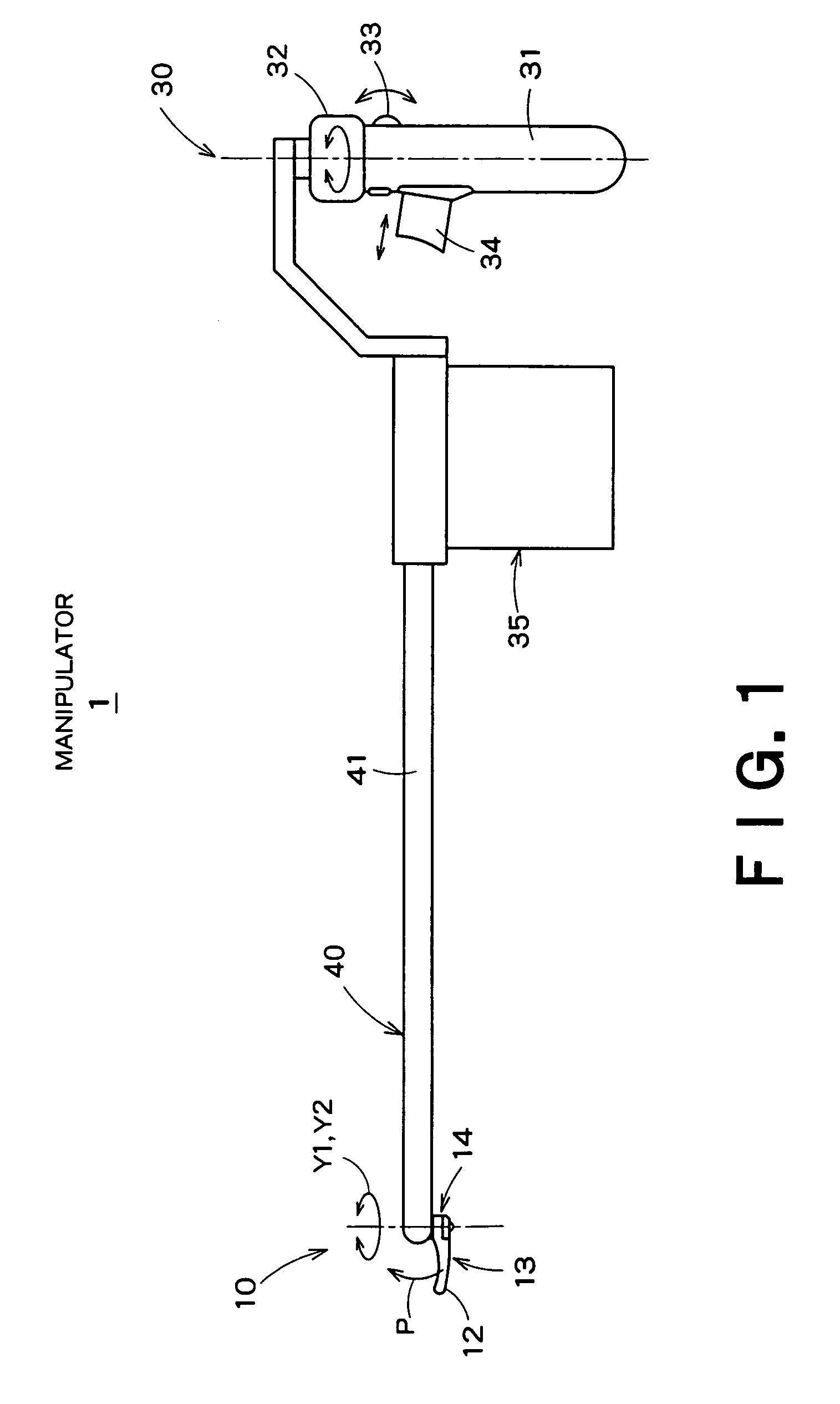

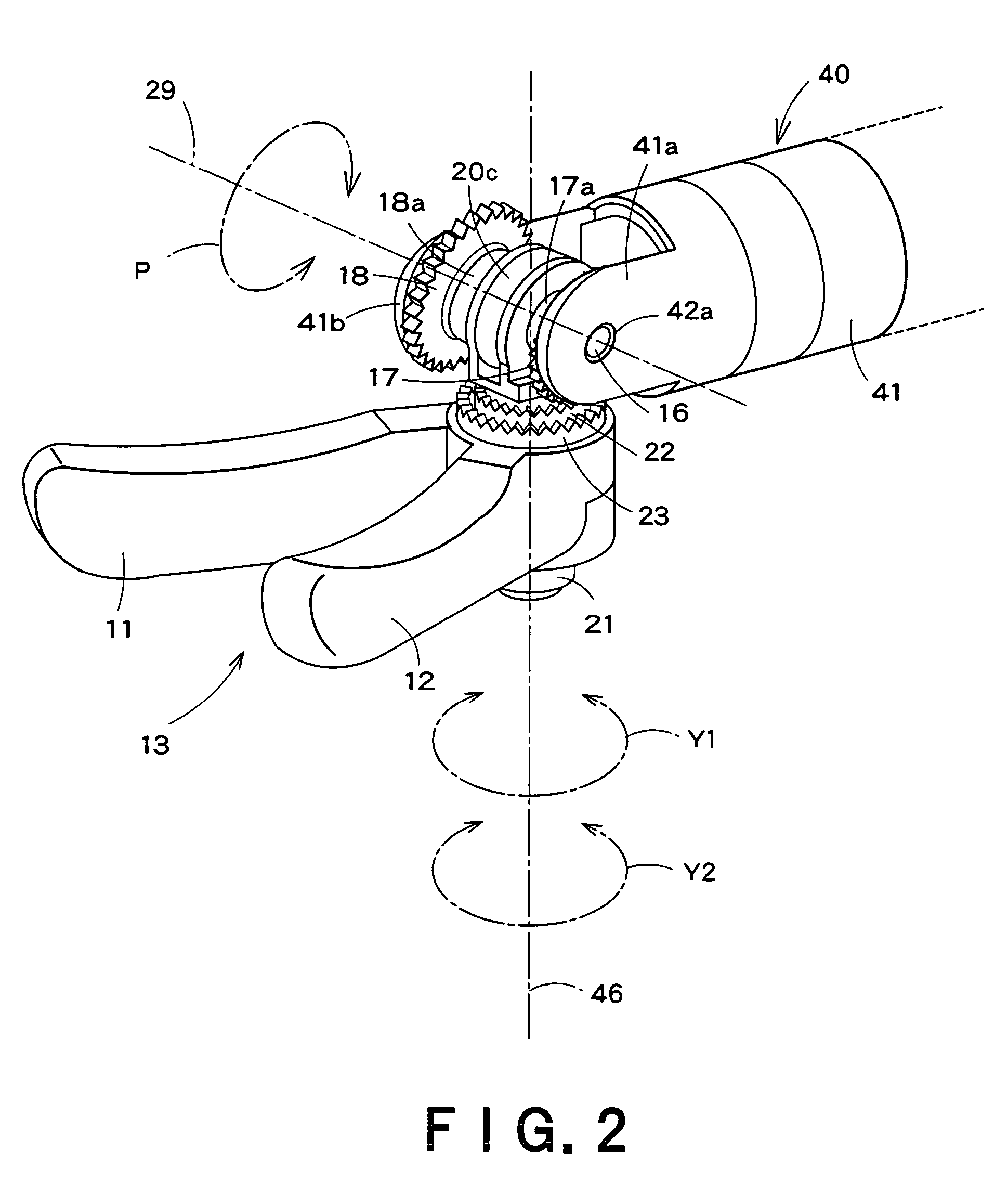

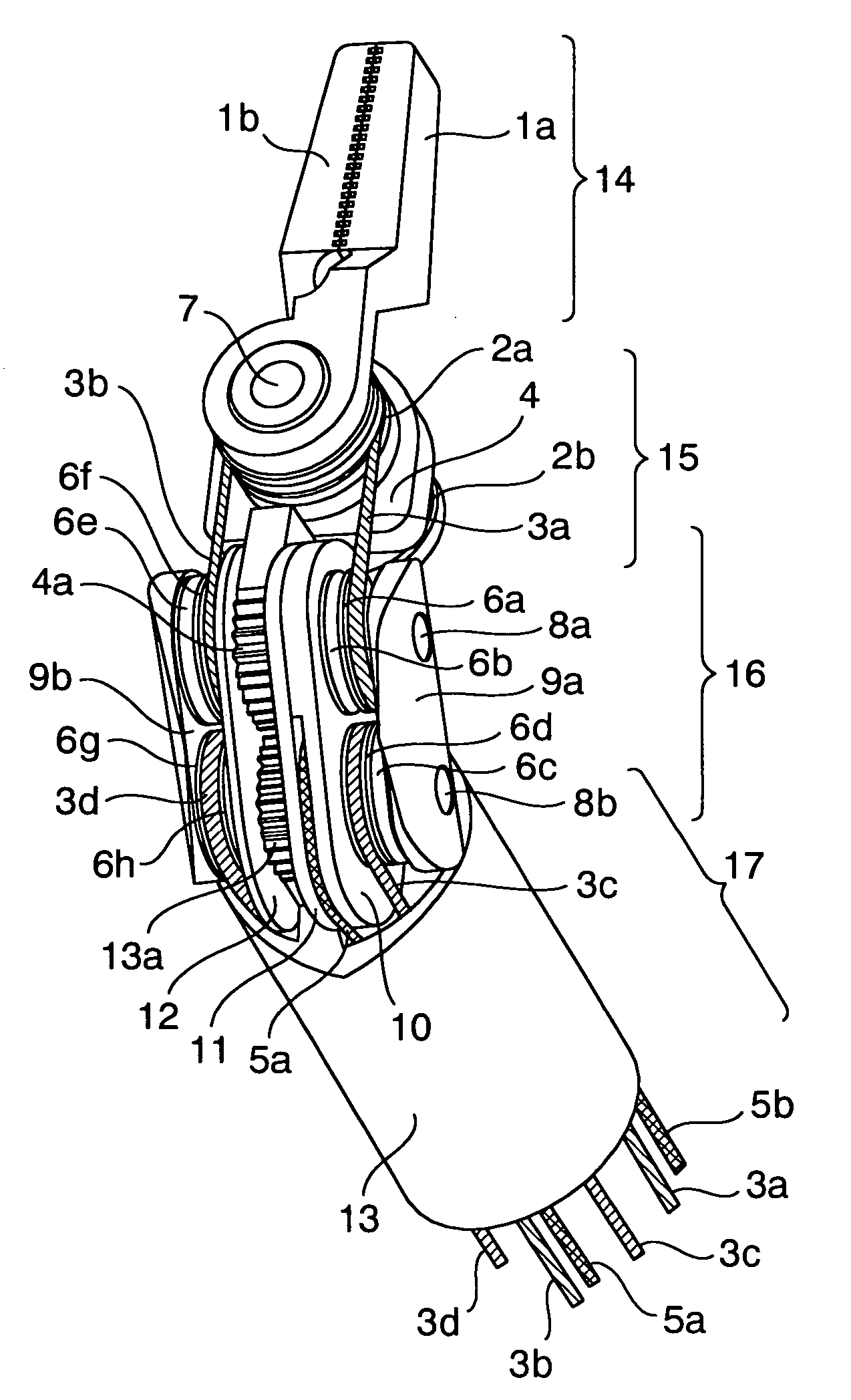

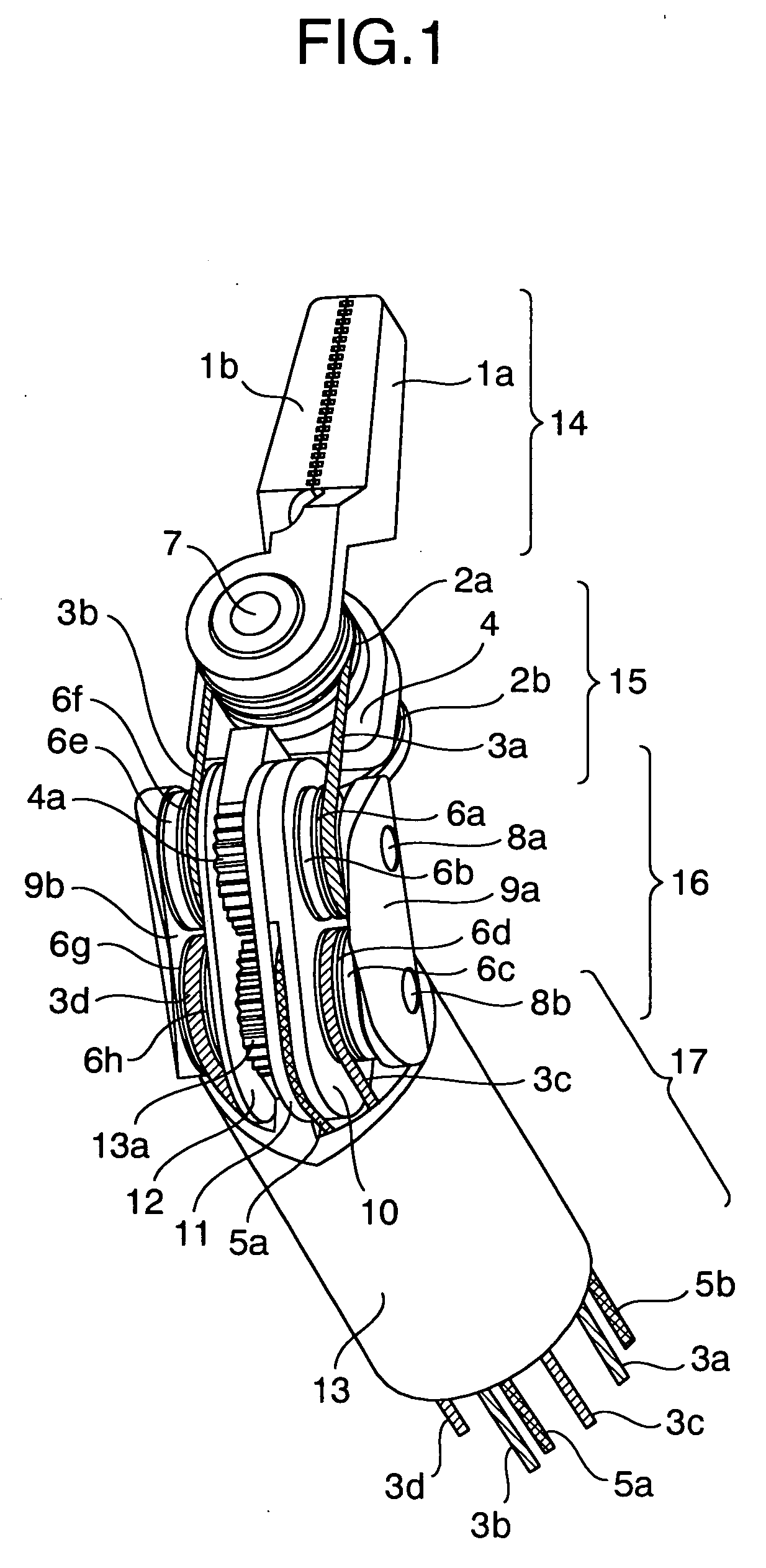

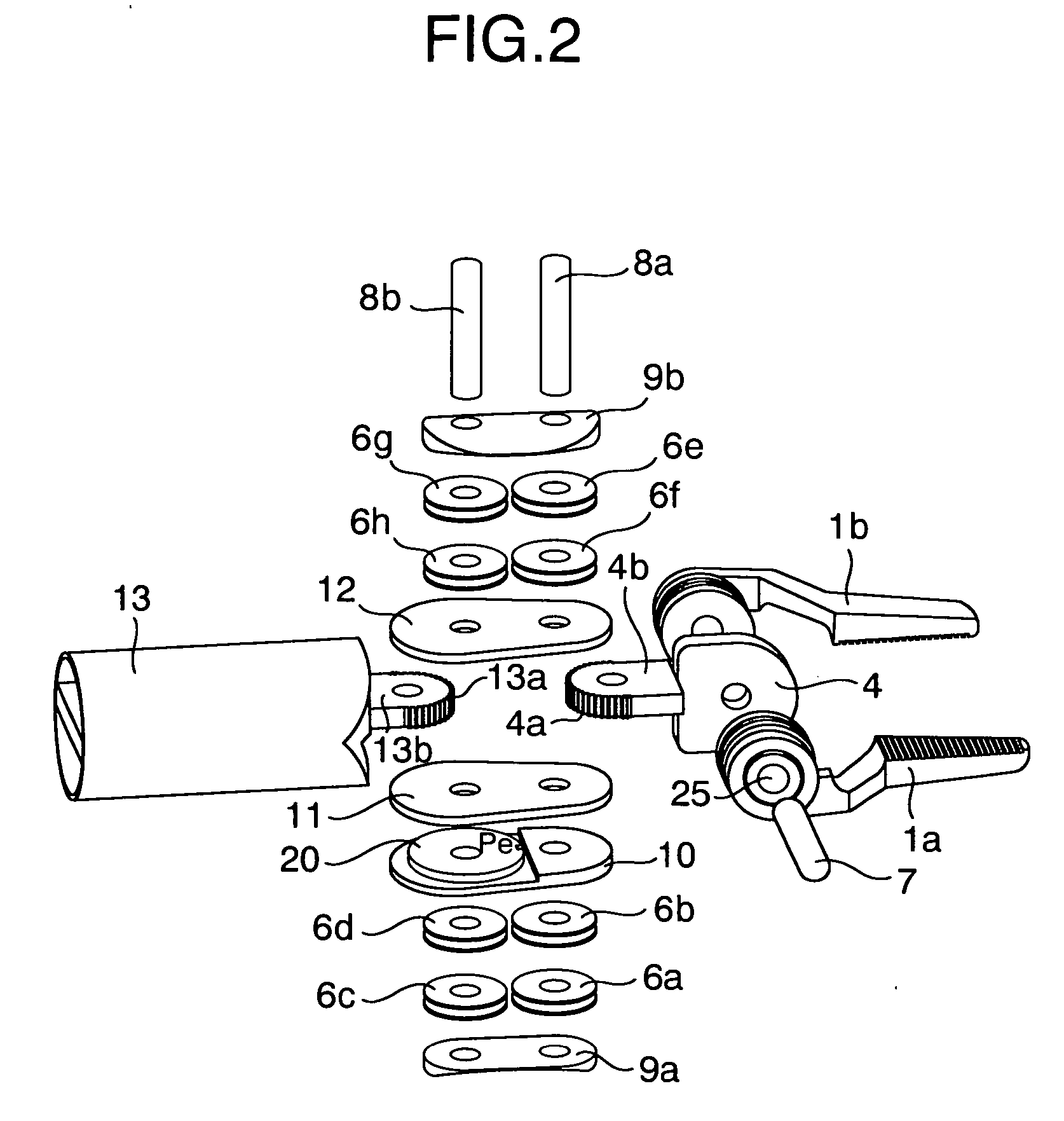

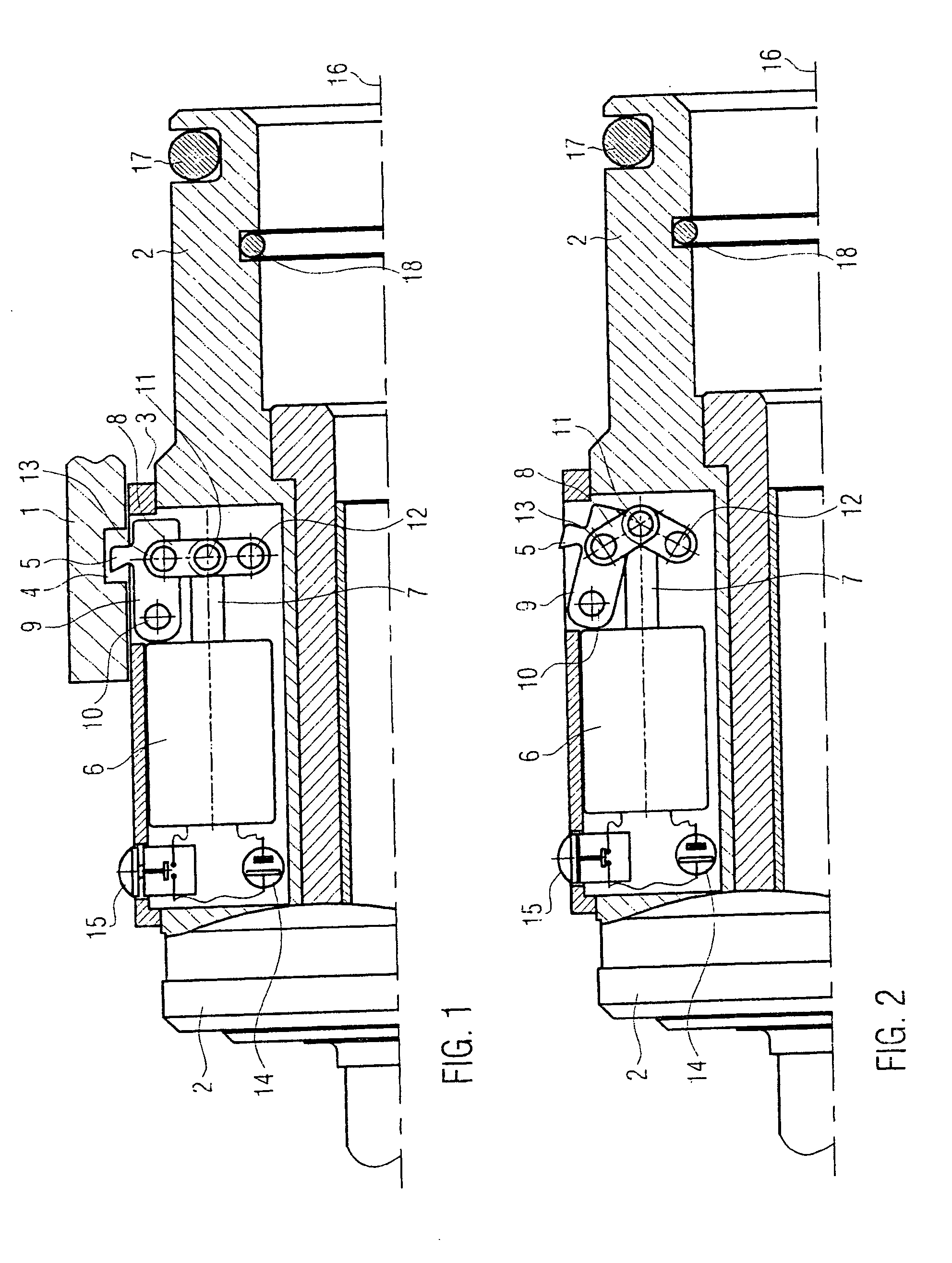

Manipulator

ActiveUS7540867B2Increase freedomSimple structureMechanical apparatusDiagnosticsEngineeringManipulator

A manipulator has a treating portion, a driving portion which are connected by a connecting portion, a first pulley on which a first wire which passes through inside of the connecting portion and is driven by the driving portion is hung for rotation, and a main shaft portion which rotatably supports the treating portion around a main shaft along a direction different from a first rotor axis that the first pulley rotates, one end portion of which is fixed to the first pulley.

Owner:TERUMO KK

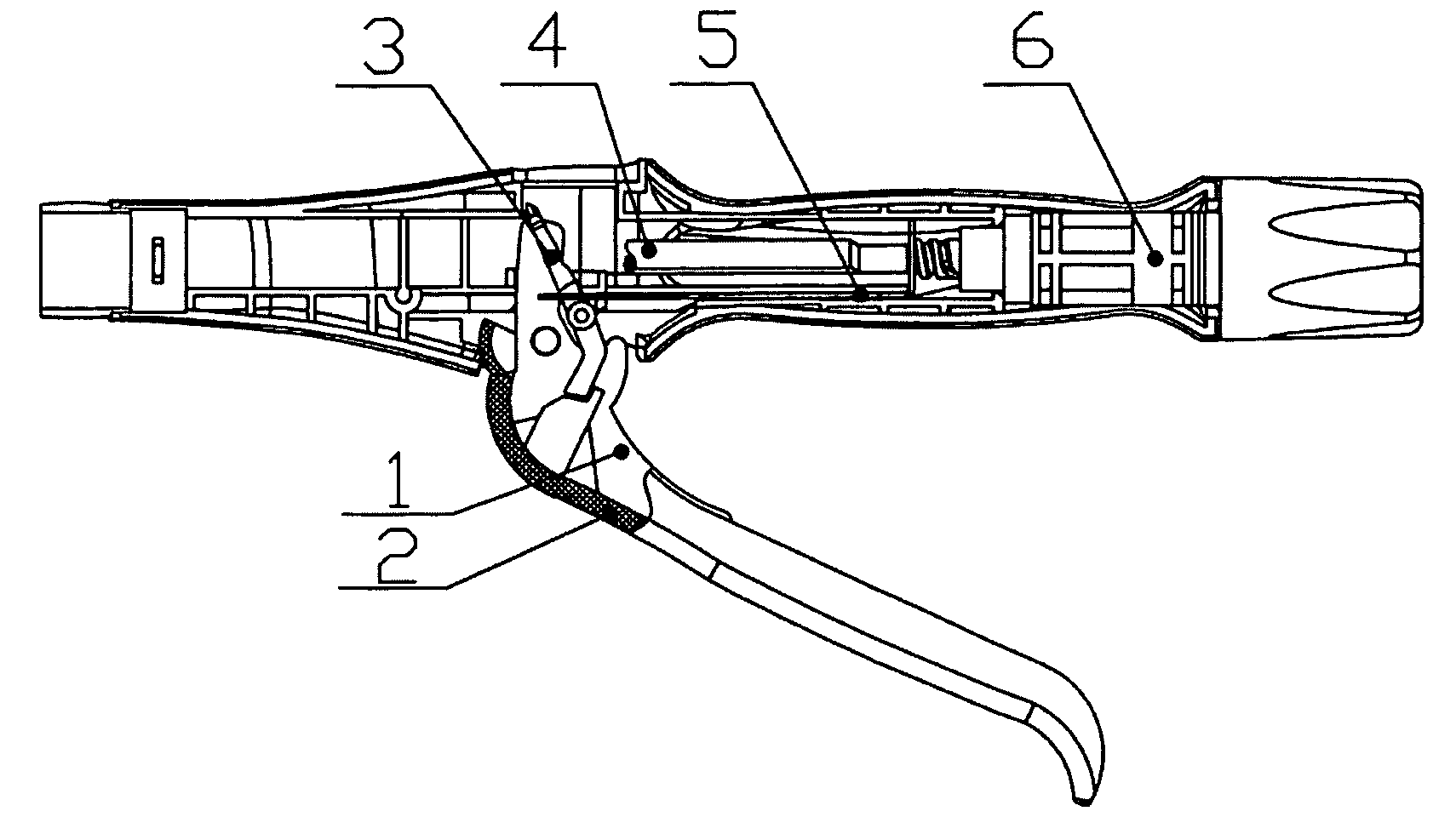

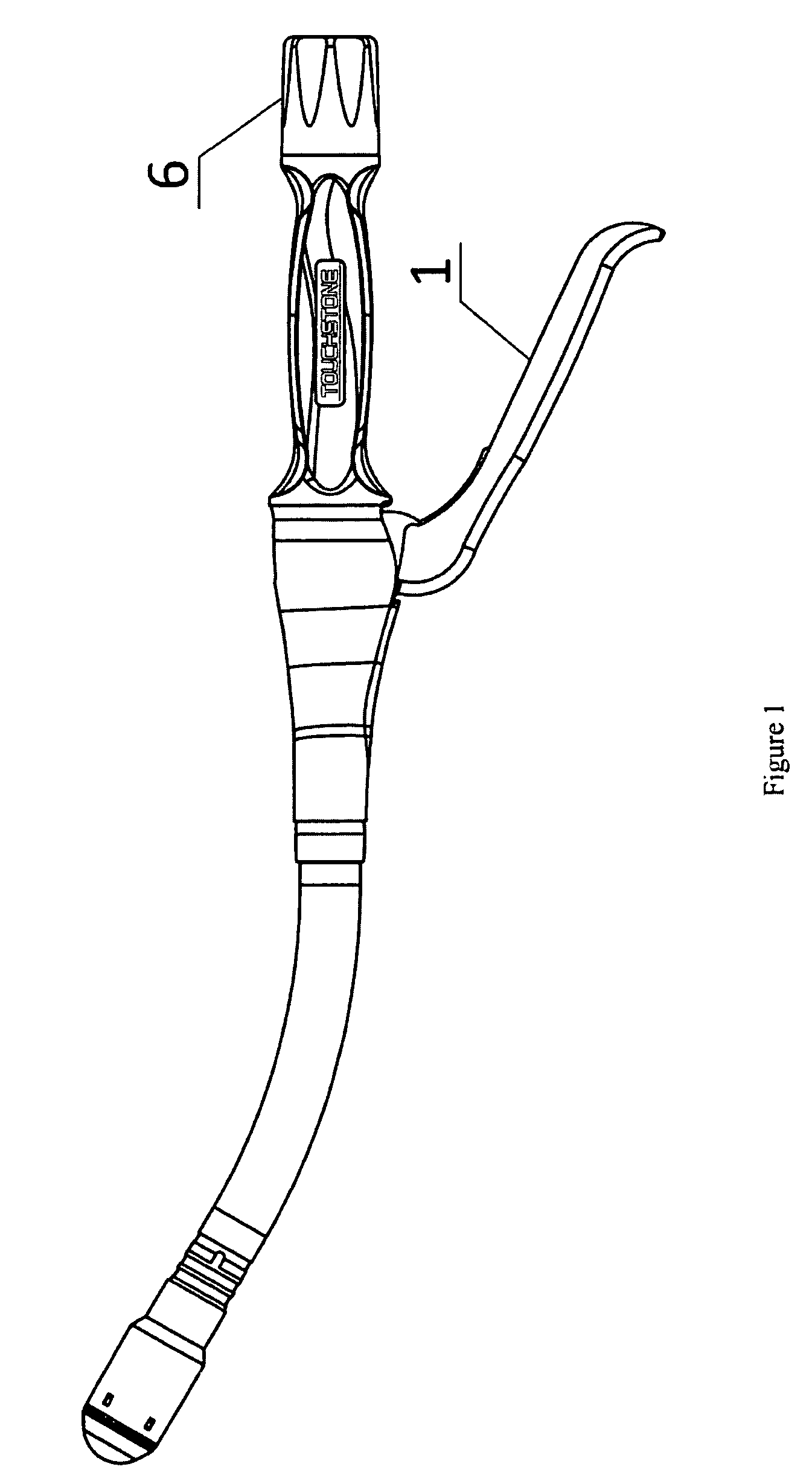

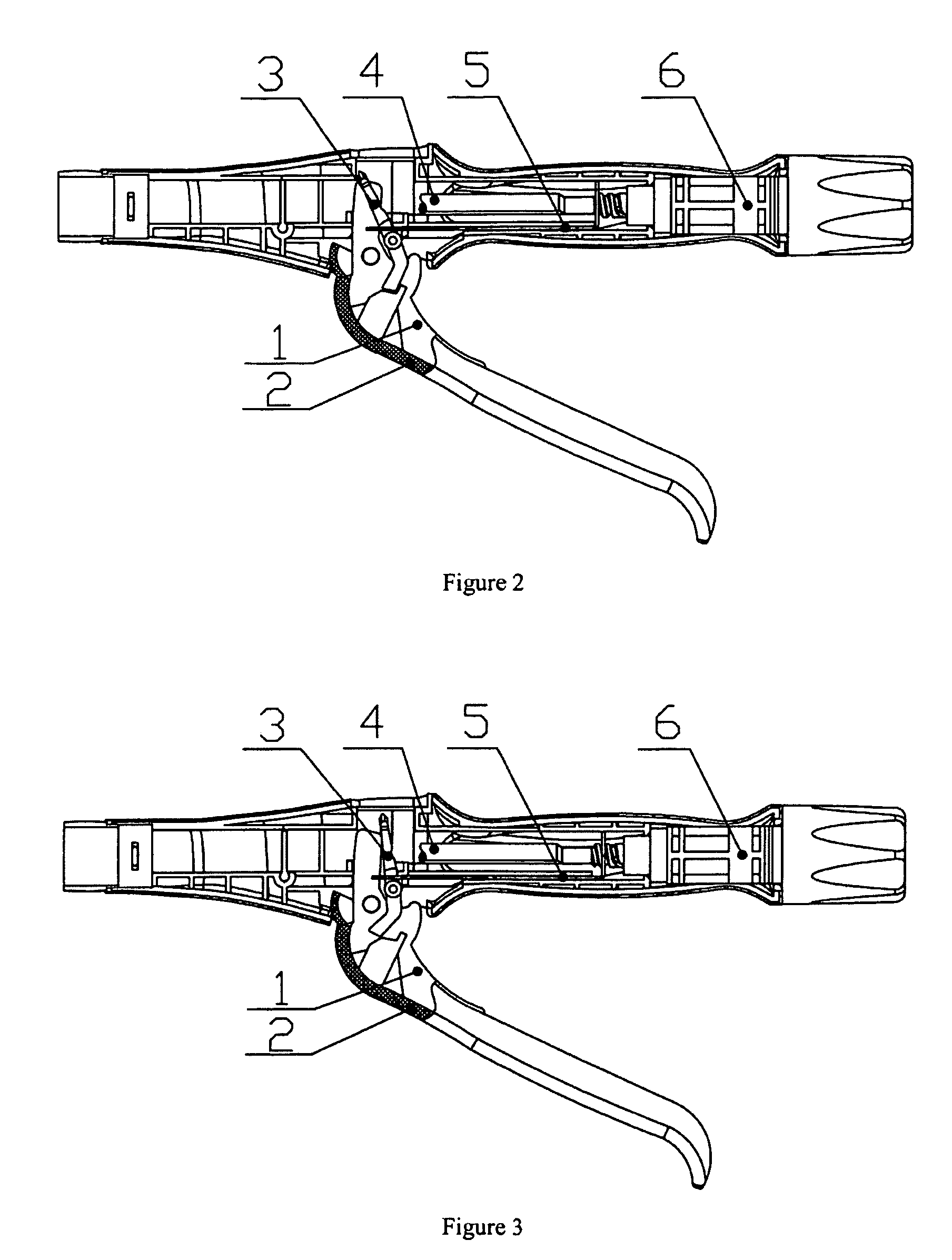

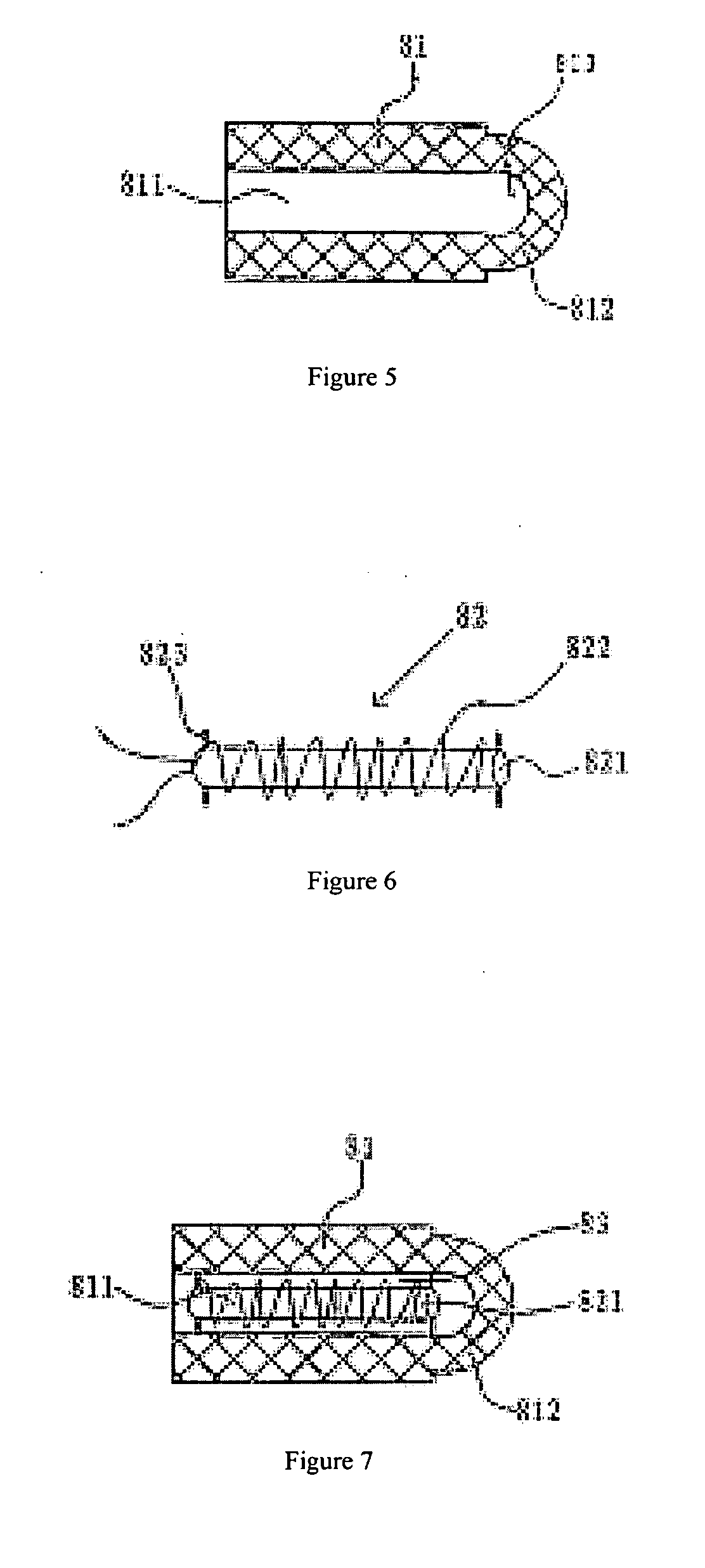

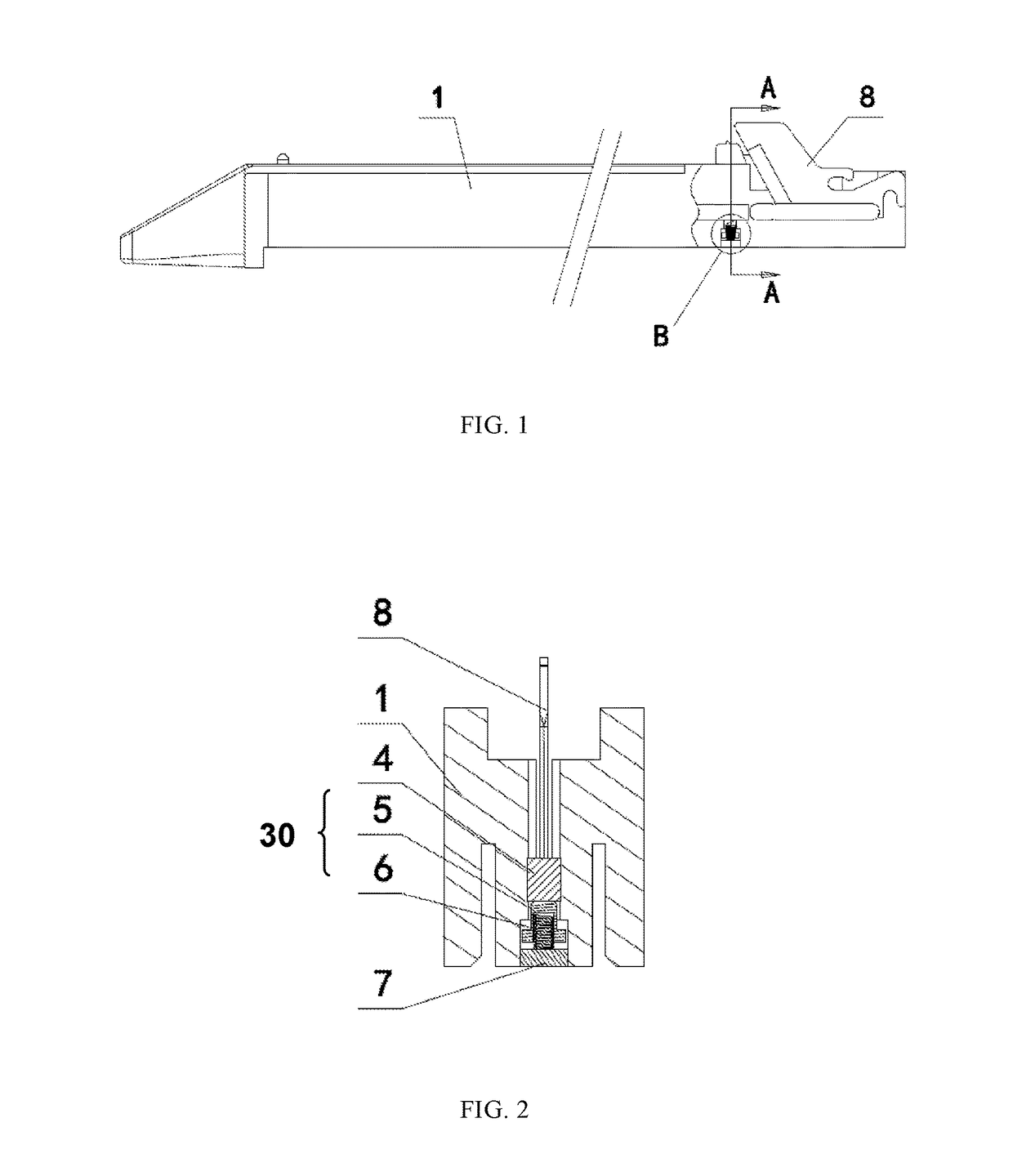

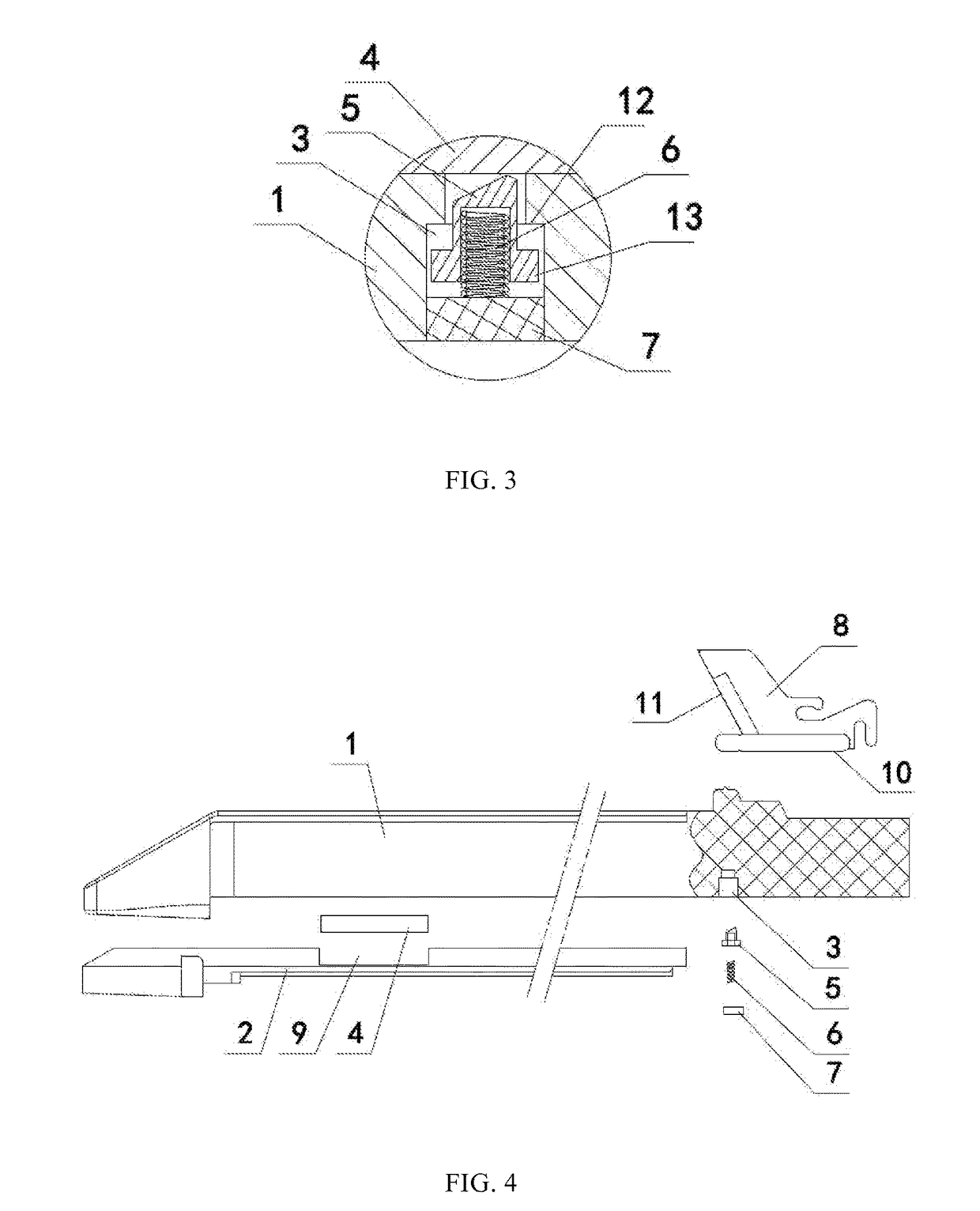

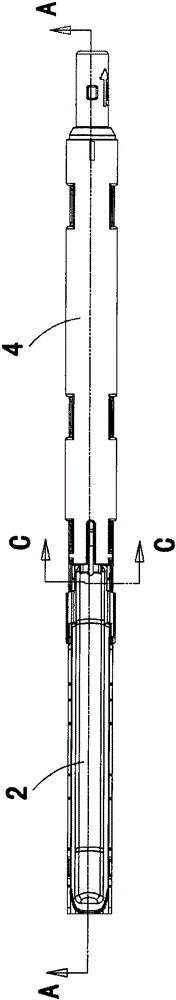

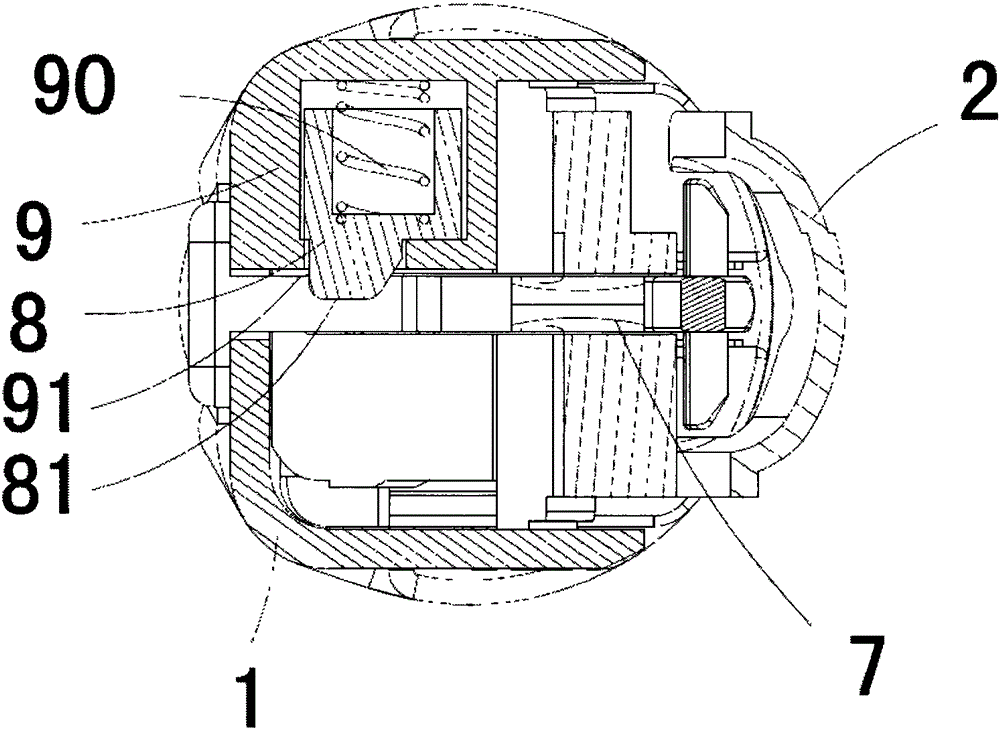

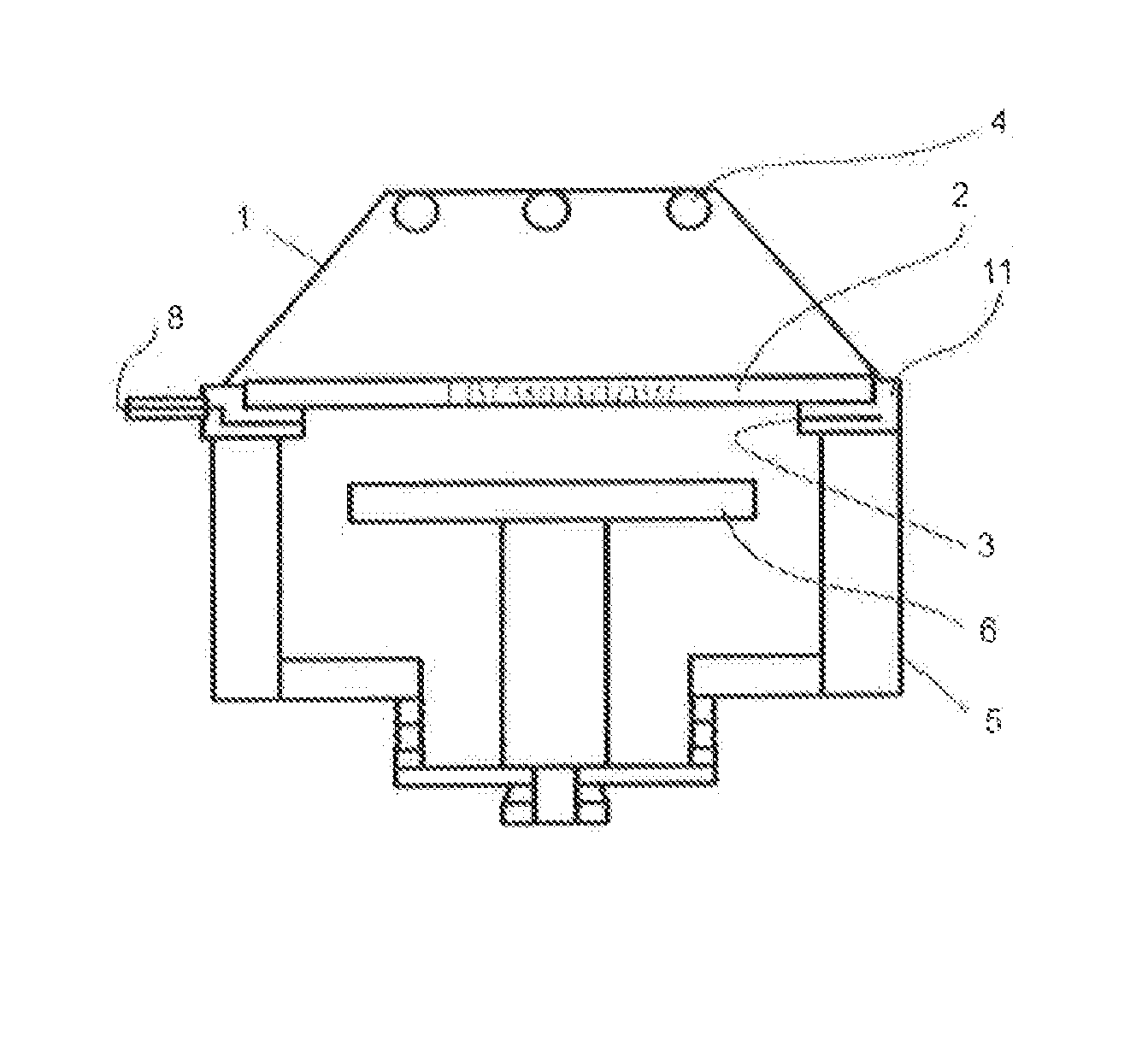

Circular stapler with an automatic safety mechanism

ActiveUS7900806B2Improving safety and reliabilitySimple structureSuture equipmentsStapling toolsEngineeringMechanical engineering

A circular stapler with an automatic safety mechanism comprises a stapler body, a stapler head, an actuating mechanism and a transmission adjusting mechanism; wherein the actuating mechanism comprises a handle and a handle coat, the transmission adjusting mechanism comprises a screw rod and an adjusting knob; a stopper is disposed either inside said handle or said handle coat; a safety rod and a pulling sheet are further provided, the safety rod has a safety block on one end and has a protruding block and a pin hole as its middle portion, a cylindrical pin is inserted into the pin hole so as to get the safety rod to be pivotally connected with the stapler body; the pulling sheet has a rear portion mounted on the screw rod and has a pulling hook at its front portion, the pulling hook hooks with the protruding block.

Owner:TOUCHSTONE INTERNATIONAL MEDICAL SCIENCE CO LTD

Surgical device

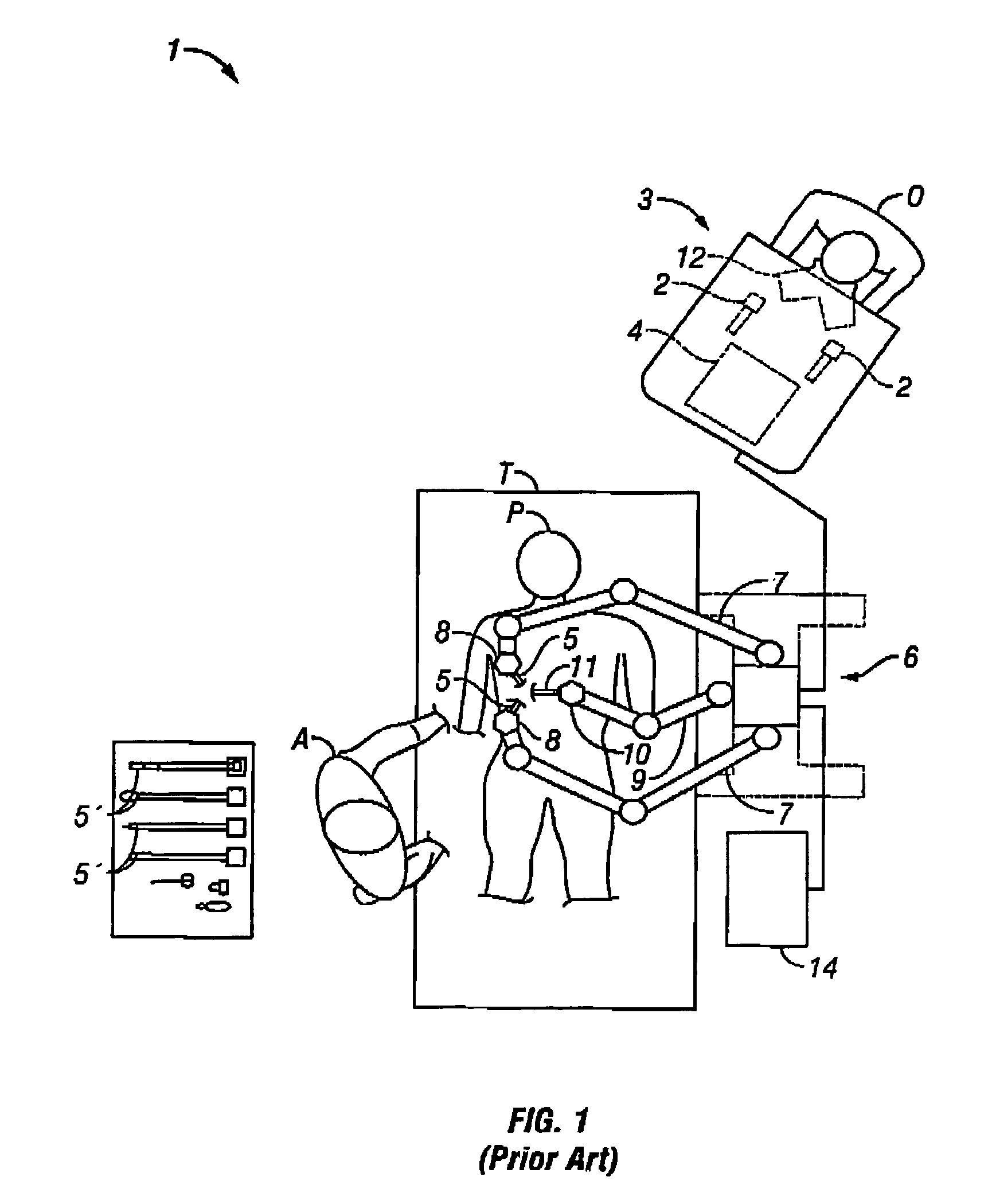

InactiveUS20070208375A1Without requiring lot of skillSimple structureDiagnosticsSurgical manipulatorsForcepsMulti degree of freedom

The invention provides a surgical device which can control a position and an attitude of a multi degree of freedom type grip portion (forceps) in a dummy manner on the basis of an operation of an operator in an operating portion. In a surgical device provided with a leading end joint portion having a leading end grip portion, a near-side joint portion having an operation portion, a handle portion supporting the operation portion, and an arm portion storing a wire for linking motions of the leading end joint portion and the near-side joint portion, the leading end joint portion is moved downward and upward by operating the operation portion and the handle portion upward and downward around the near-side joint portion, and the leading end joint portion is moved rightward and leftward by operating the operation portion and the handle portion leftward and rightward, thereby making the leading end joint portion execute a swing motion, and the leading end grip portion is opened and closed by opening and closing finger rests of the operation portion.

Owner:HITACHI LTD

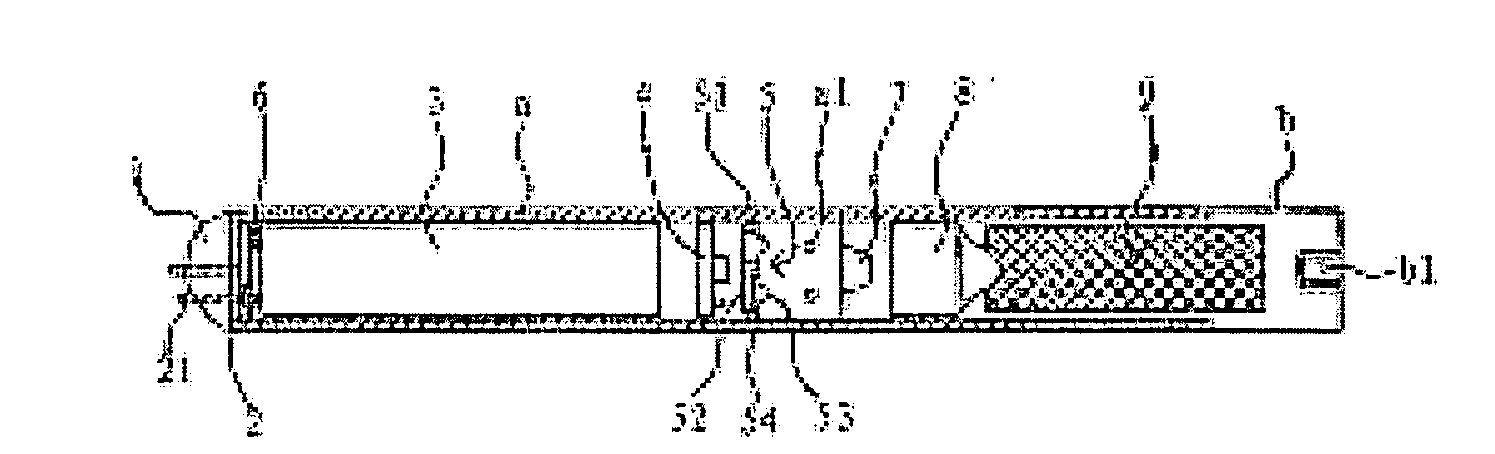

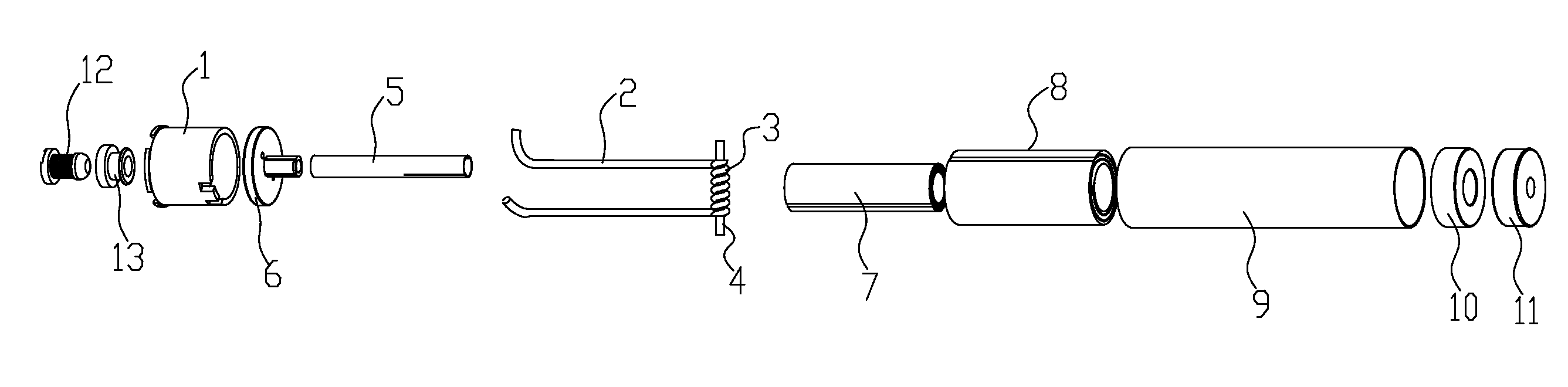

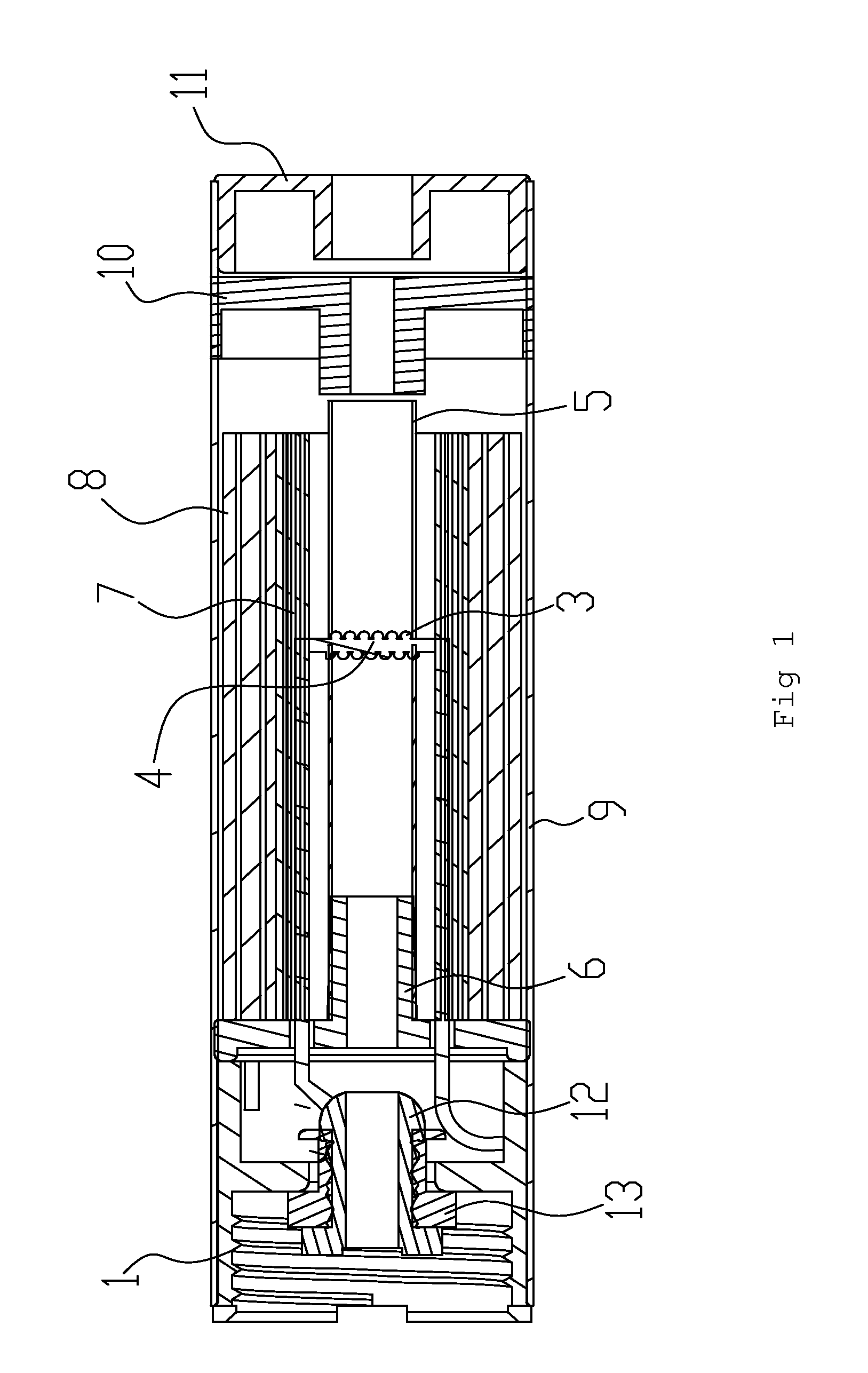

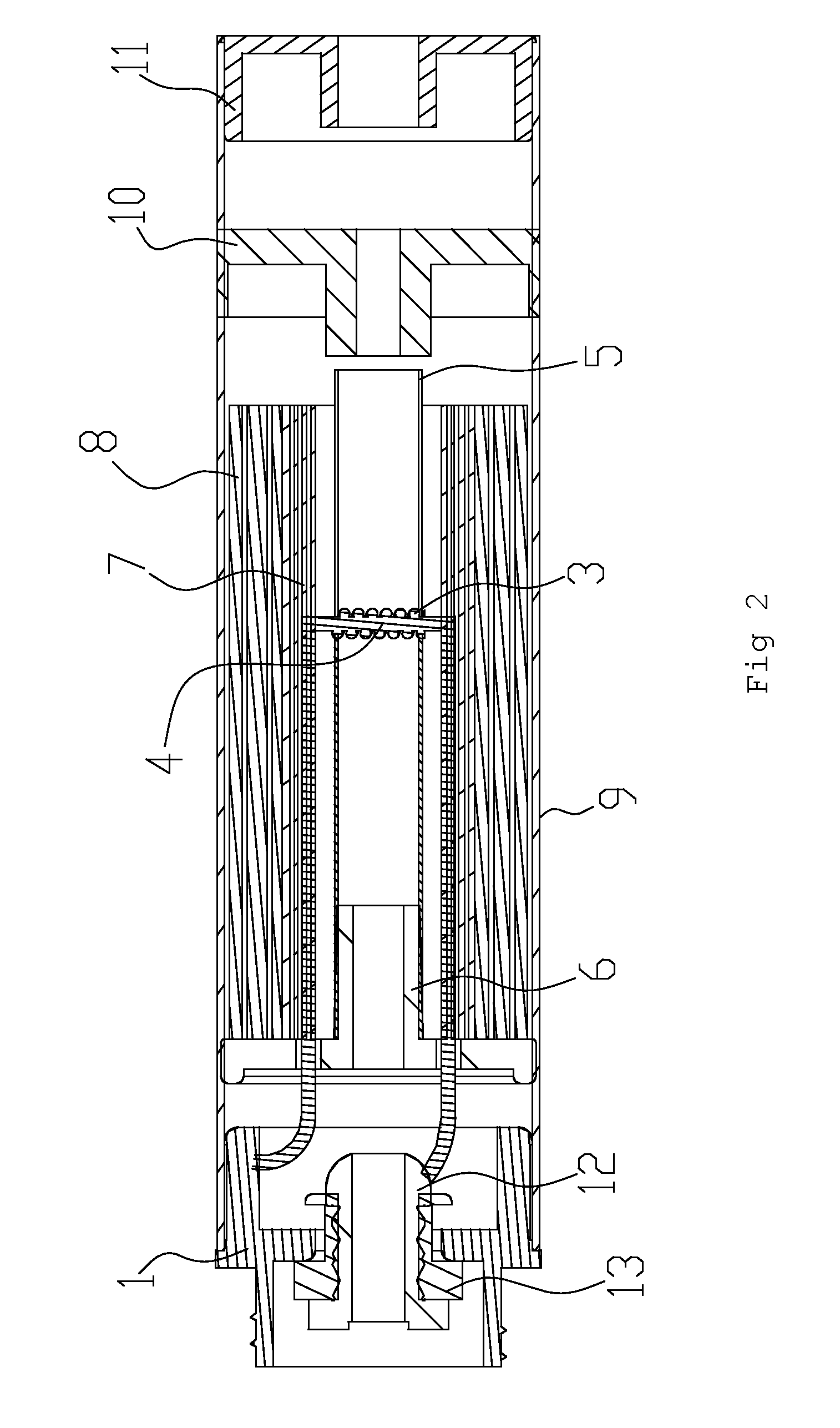

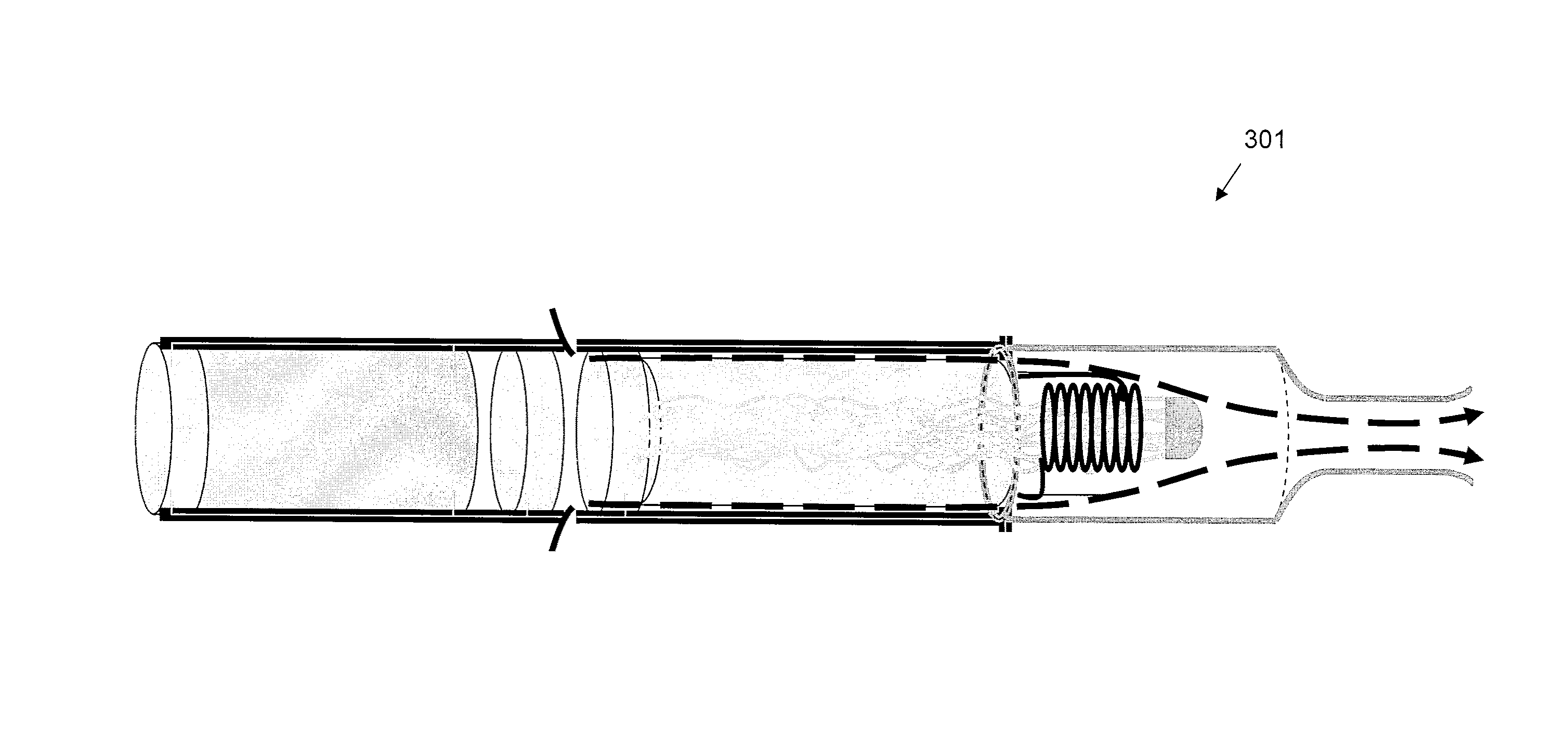

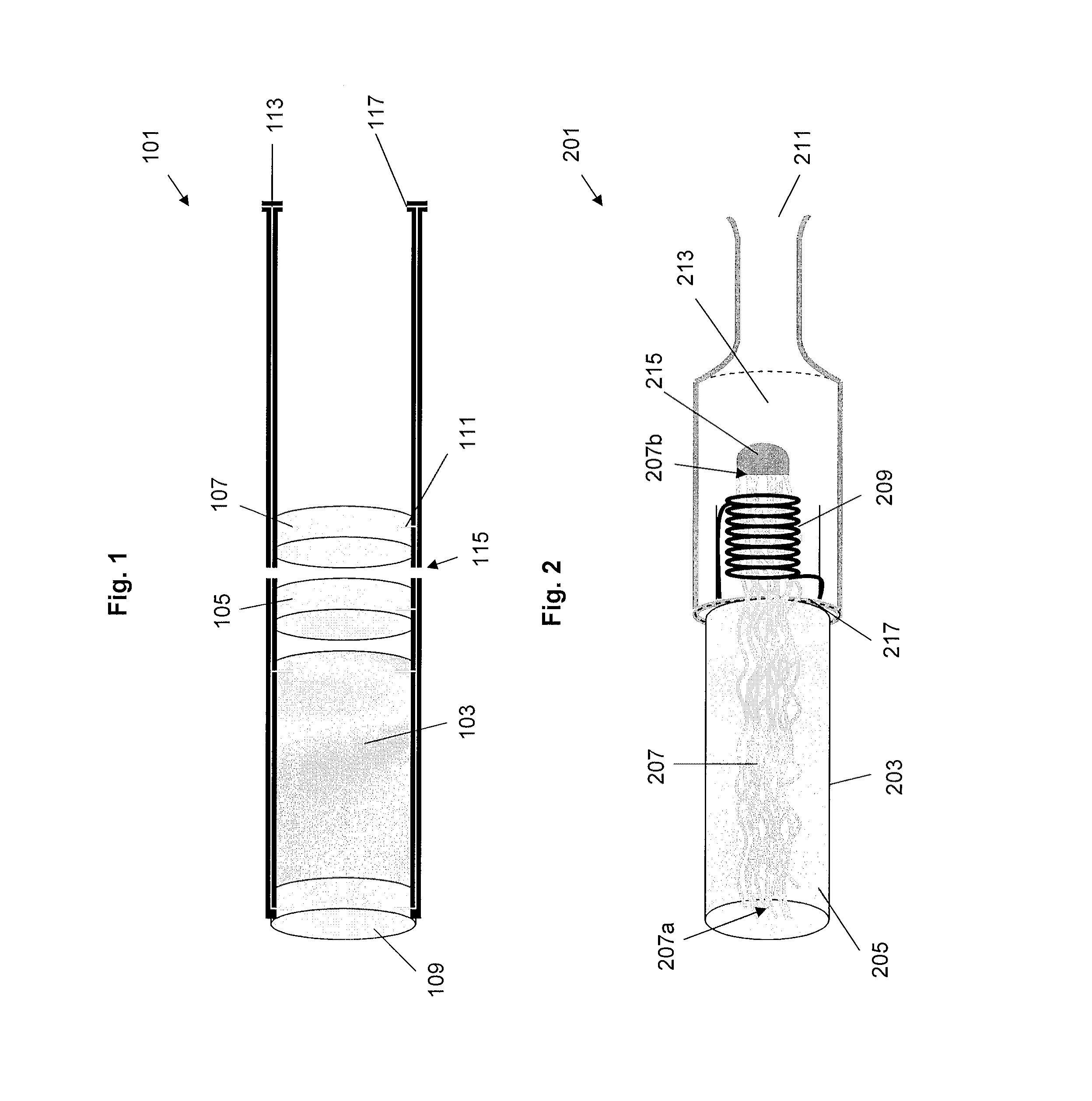

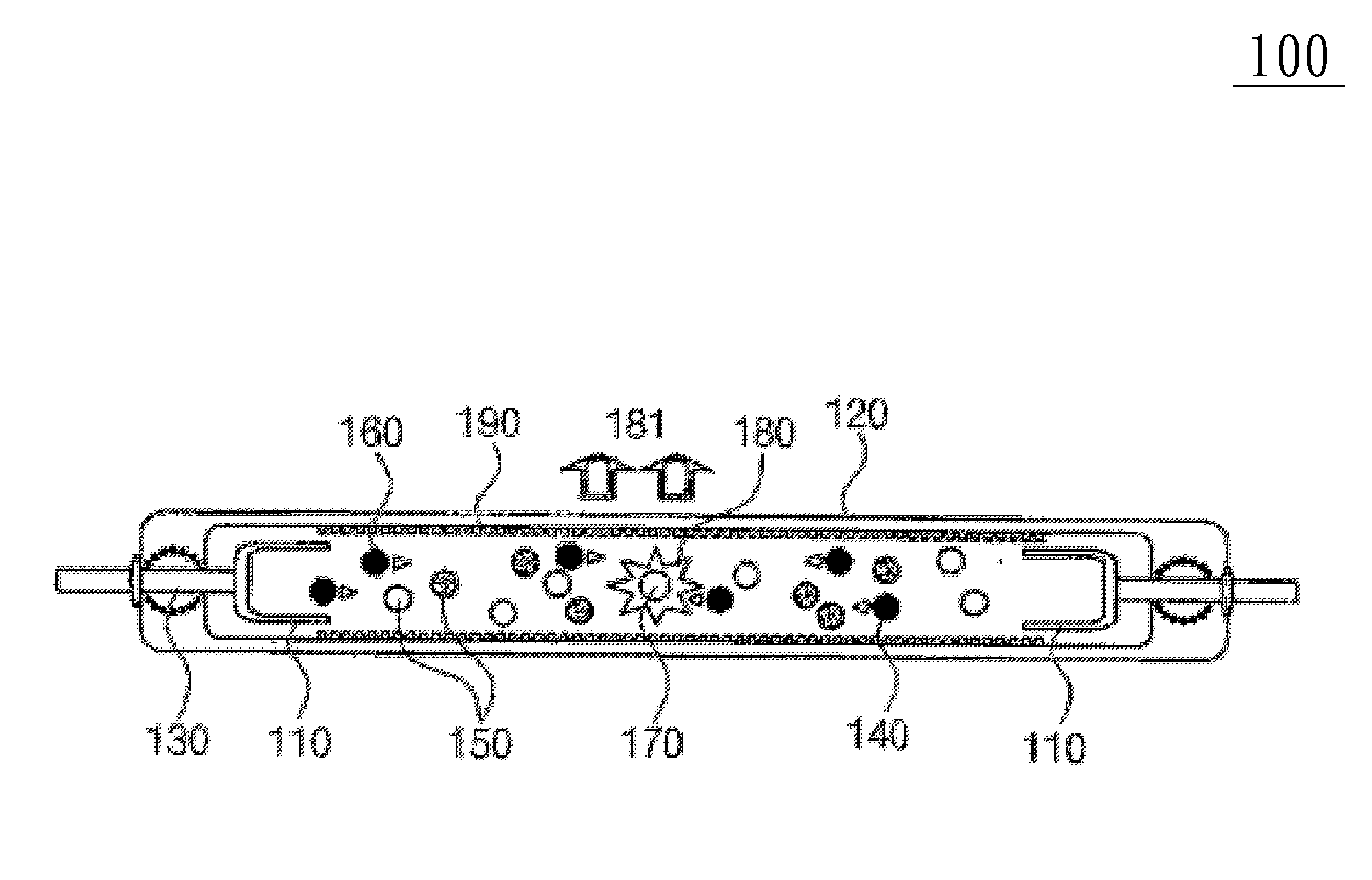

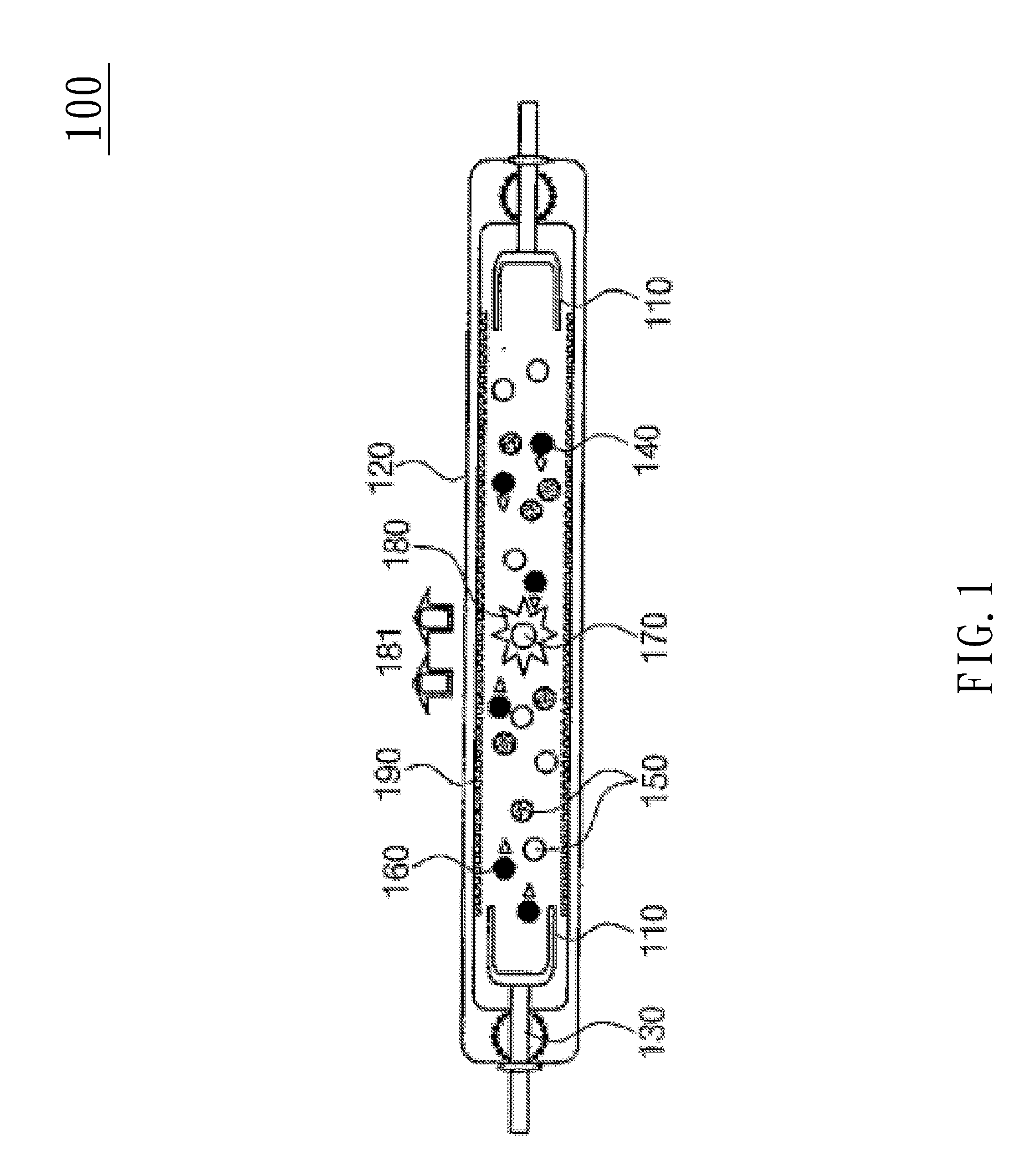

Aerosol Electronic Cigarette

ActiveUS20090095311A1Reduce cancer riskSimple structureBatteries circuit arrangementsTobacco treatmentElectronic cigaretteBottle

An aerosol electronic cigarette includes a battery assembly, an atomizer assembly and a cigarette bottle assembly and also includes a shell (a) which is hollow and integrally formed. Said battery assembly connects with said atomizer assembly and both are located in said shell (a). Said cigarette bottle assembly is located in one end of the shell (a), which is detachable. Said cigarette bottle assembly fits with said atomizer assembly. Said shell (a) has through-air-inlets (a1).

Owner:FONTEM VENTURES

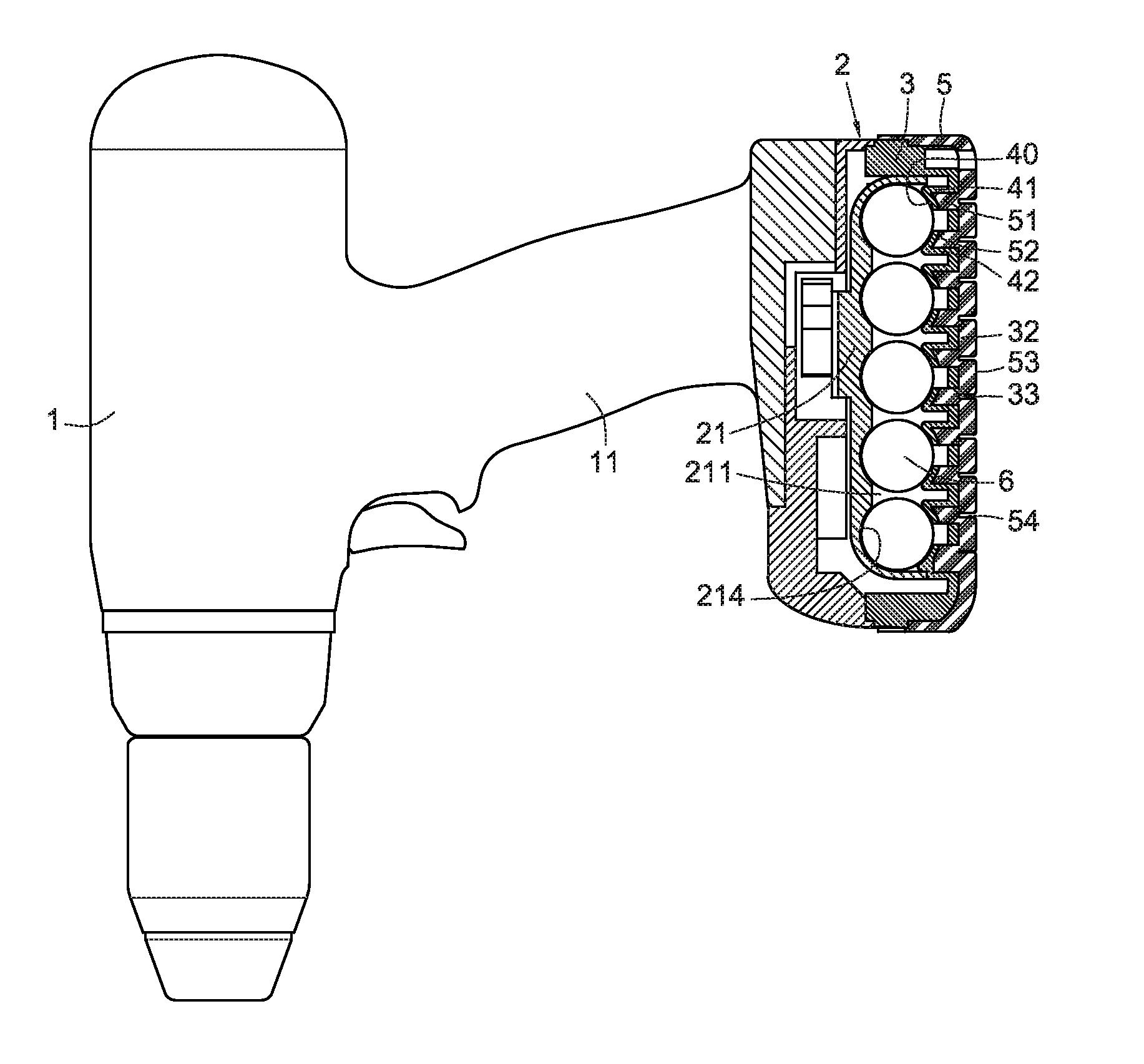

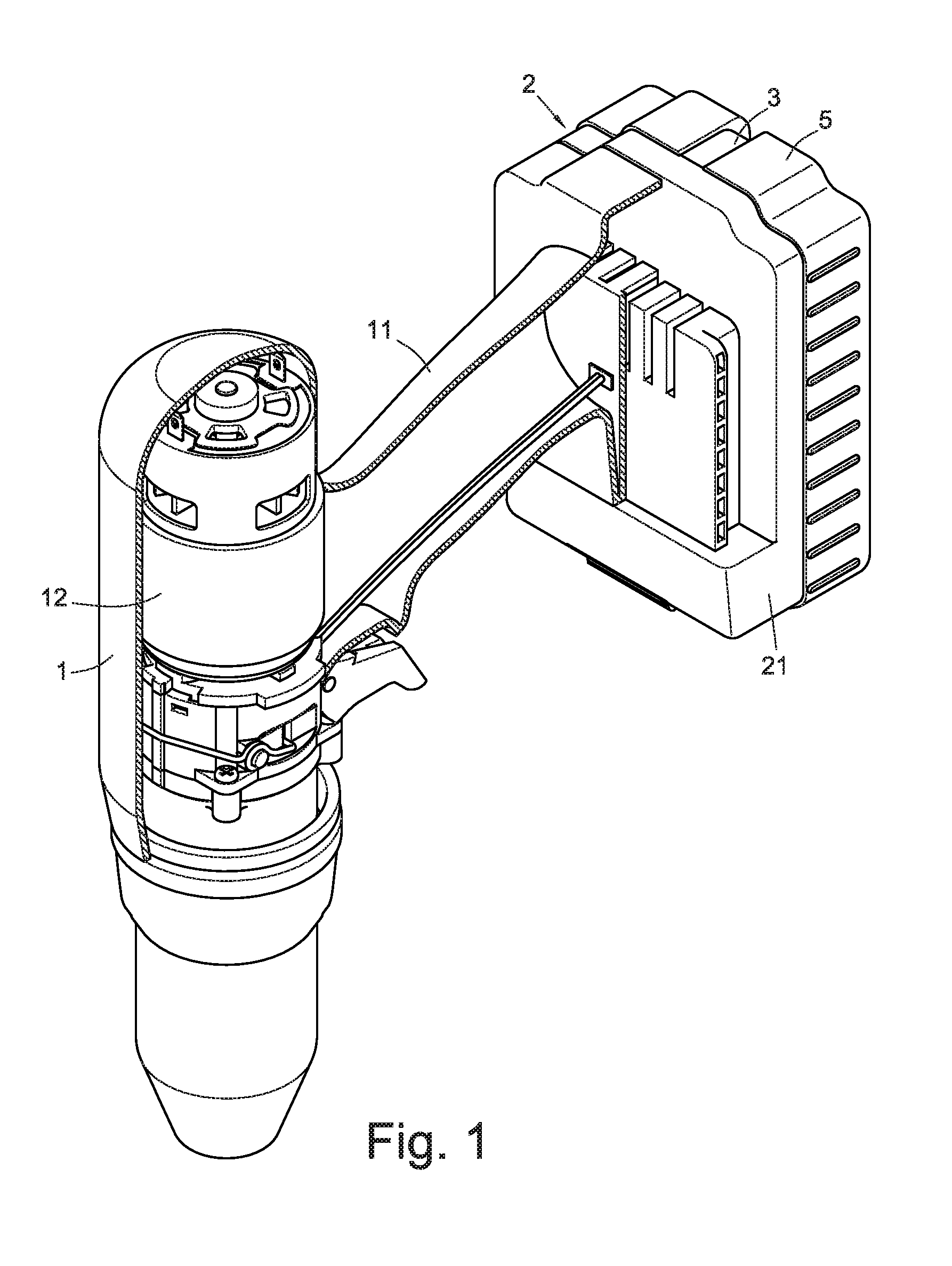

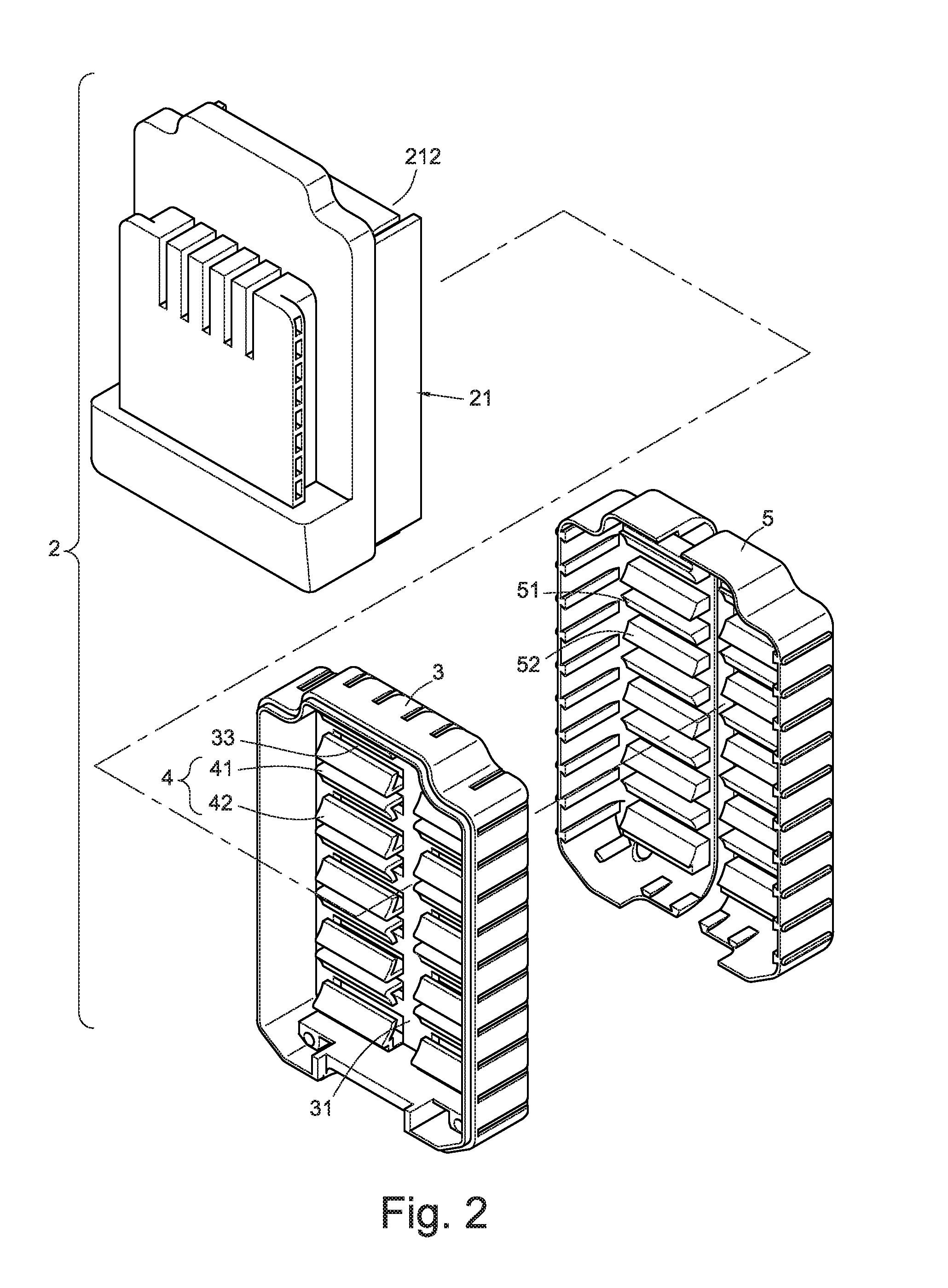

Shock proof structure of battery pack for receiving battery cell

InactiveUS20120251861A1Simple structureUpgrades stabilityBattery isolationPortable power-driven toolsEngineeringAbsorbance

A shock proof structure of a battery pack for receiving a battery cell is formed in an electrical tool. The battery pack includes a base having a space for receiving the battery cell and a lid for opening or closing the space. The space has a plurality of first buckling portions separated by a gap disposed at a bottom side thereof. A plurality of second buckling portions with shock absorbance is formed at an inner sidewall of the lid. The plate sets include two plates separated by a gap are symmetrically positioned. The plates of each plate set have a second buckling portion with a stretching gap formed in between. The second buckling portion is positioned at the opposite end of the first buckling portion to provide the battery cell to be steadily buckled between the first and the second buckling portions.

Owner:DE POAN PNEUMATIC

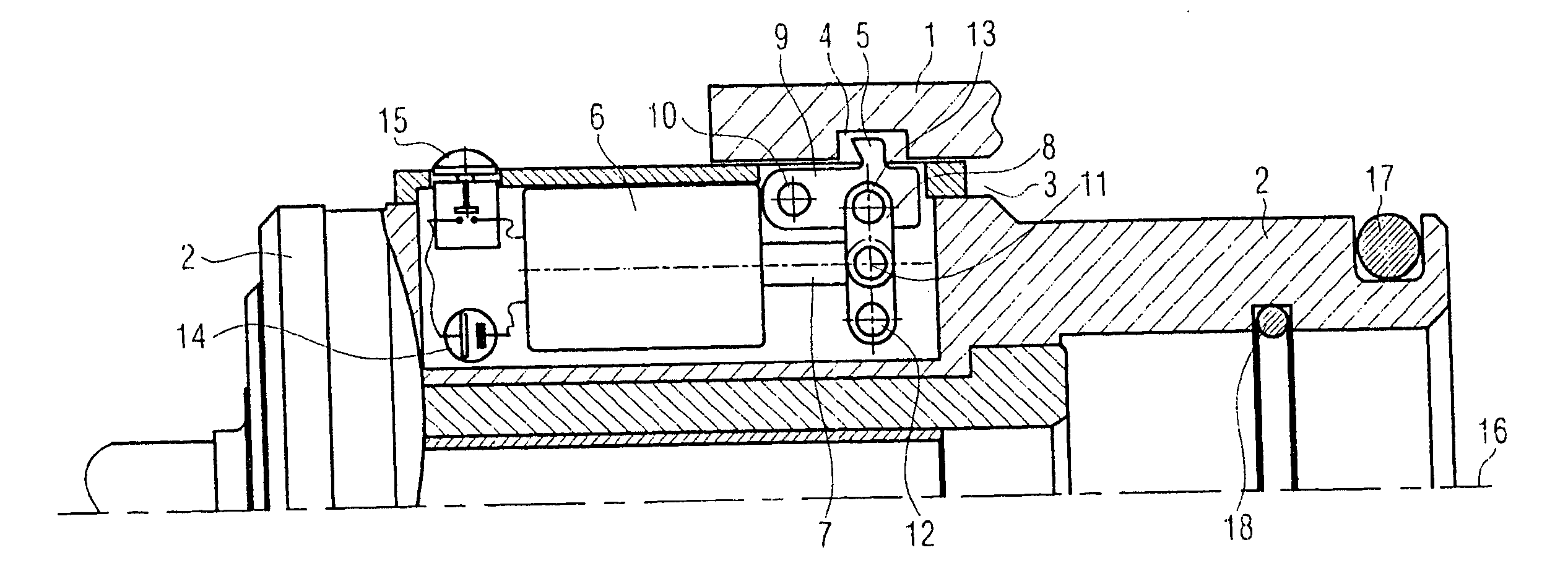

Surgical coupling device

InactiveUS20070179477A1Simple structureSimple and safe operationDiagnosticsSpannersCouplingEngineering

A surgical coupling device detachably connects a tool holder to a surgical instrument, wherein the tool holder is provided with a recess into which a coupling portion of the instrument can be inserted detachably, wherein a locking recess is provided in an inner wall of the recess, with which a locking member can be engaged detachably, the locking member being supported at the instrument, wherein the locking member is selectively movable into a locking position and a release position by a servo drive.

Owner:GEBR BRASSELER GMBH & CO KG

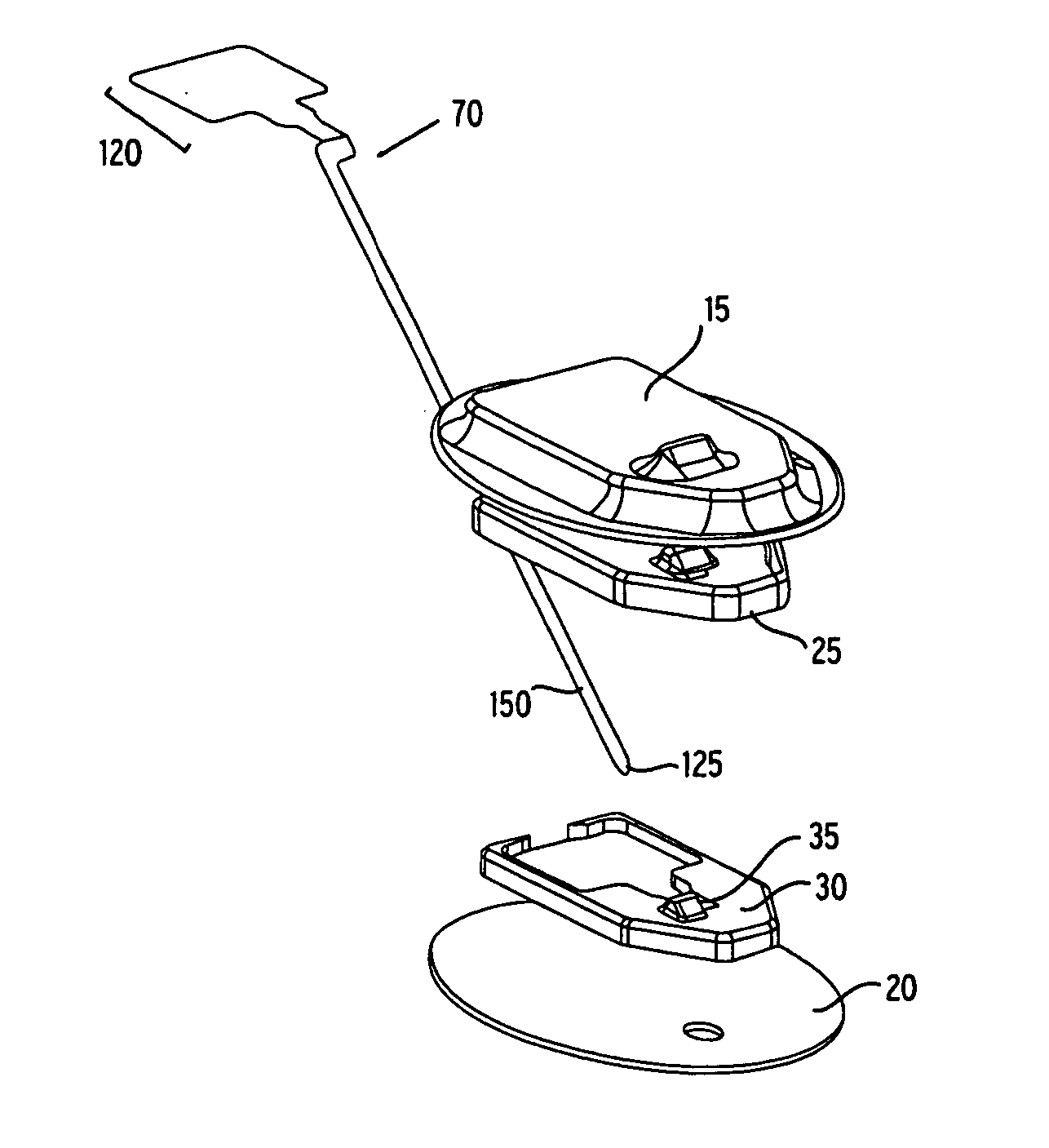

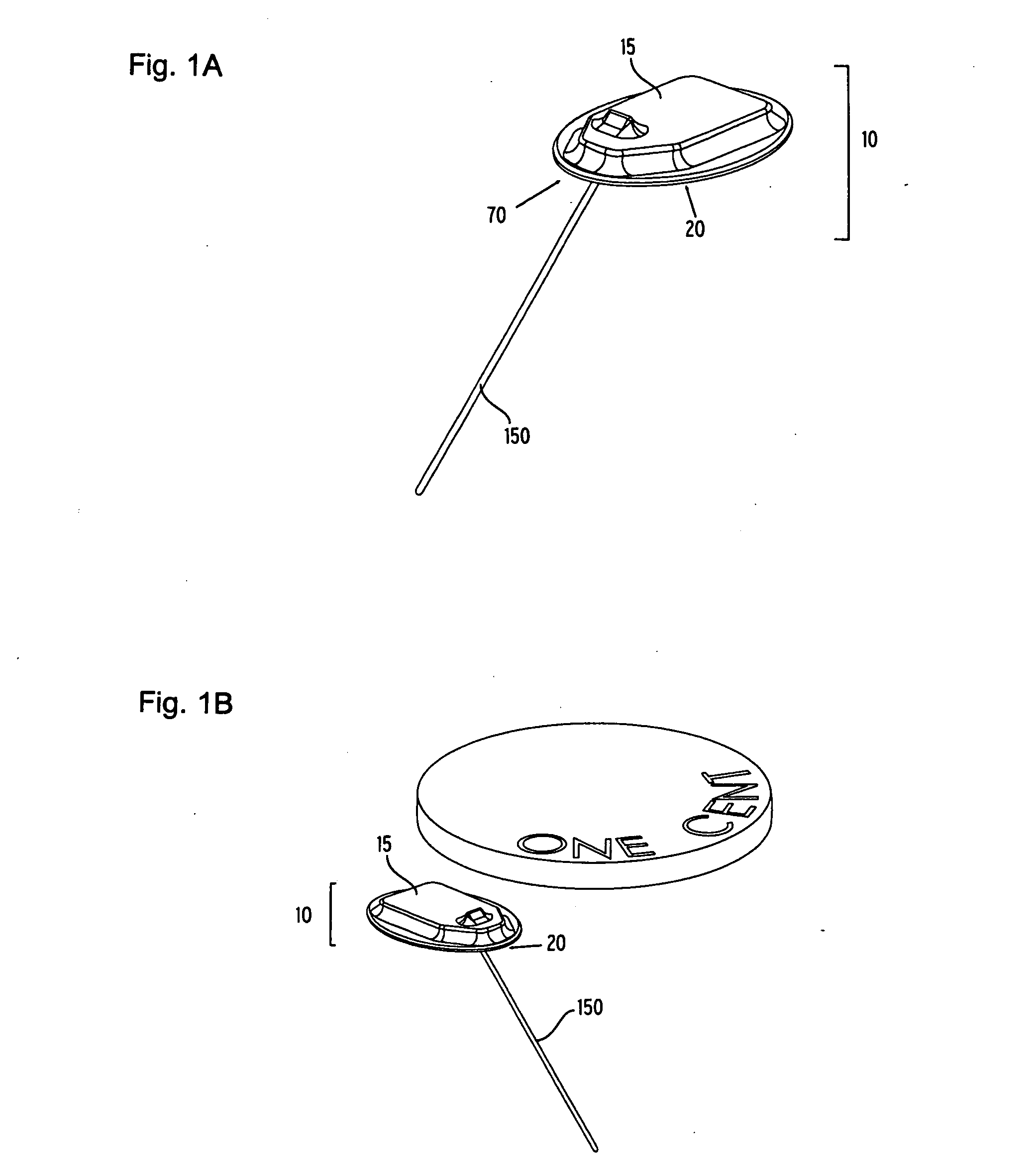

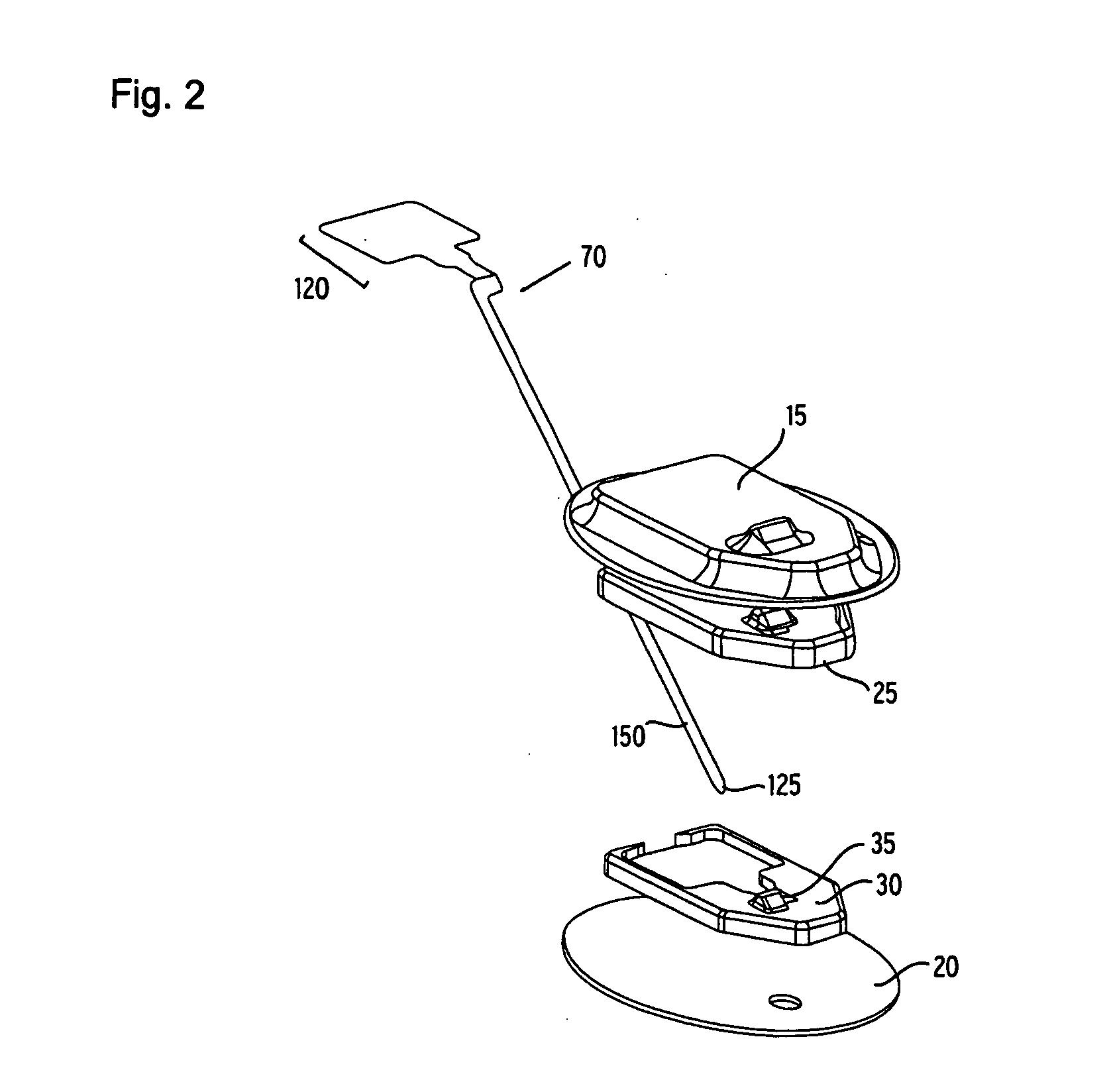

Flexible sensor apparatus

ActiveUS20070073129A1Quick and easy transcutaneous placementImprove stabilitySurgical needlesCatheterAnalyteAdhesive

A flexible mounting base to hold a sensor at an infusion site, the sensor being a removable in vivo sensor for monitoring analyte concentration level in a patient, such as blood glucose (BG) level. The mounting base comprises a flexible adhesive that anchors the flexible sensor set at an infusion site to provide stability for the sensor set in a convenient and comfortable manner. Placement of the mounting base onto the patient's skin causes the insertion needle to pierce the skin for transcutaneous placement of the cannula with the sensor therein. The insertion needle can then be withdrawn to leave the cannula and sensor at the selected insertion position, with the distal segment of the sensor being exposed to patient extracellular fluid via apertures formed in the cannula.

Owner:MEDTRONIC MIMIMED INC

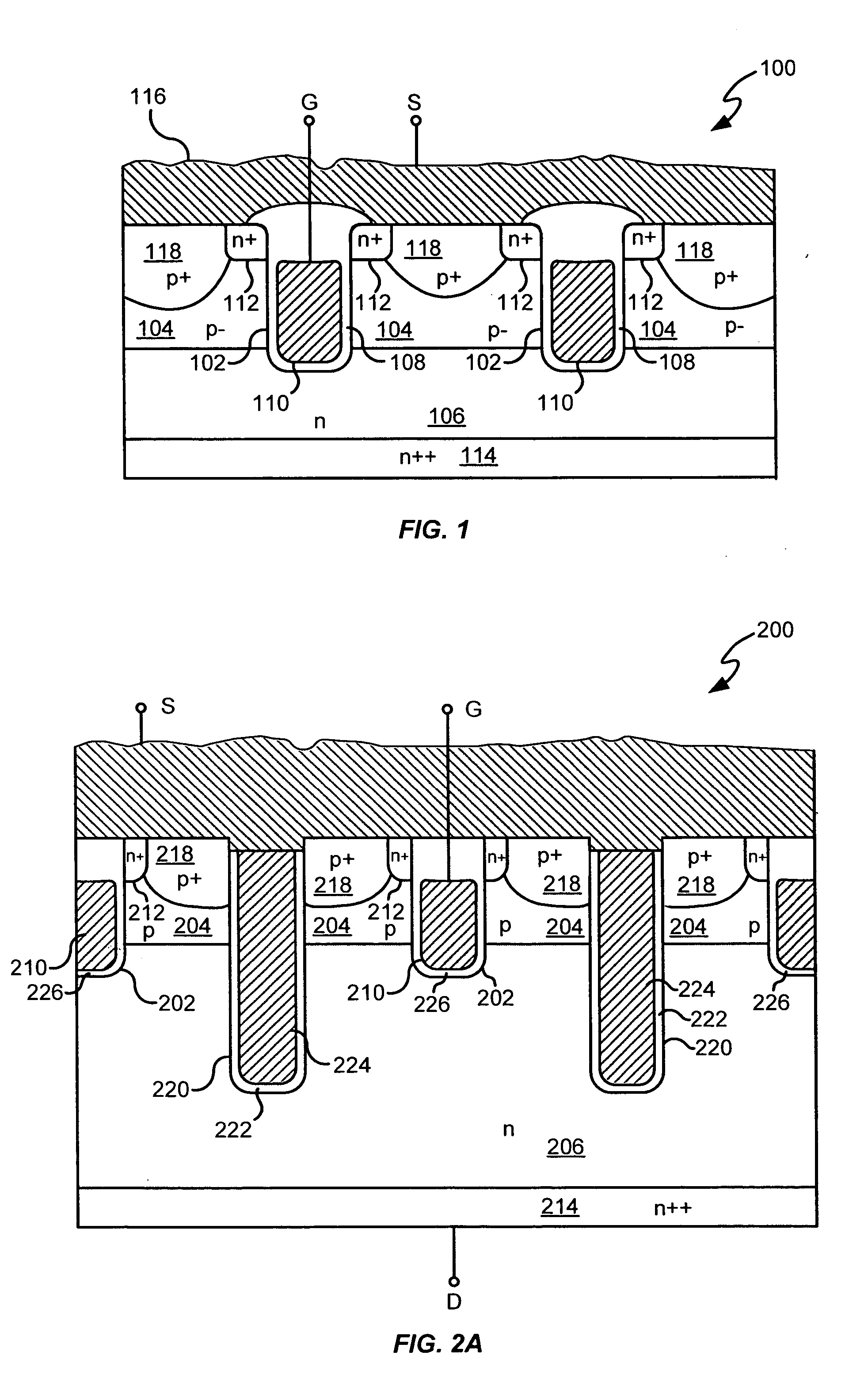

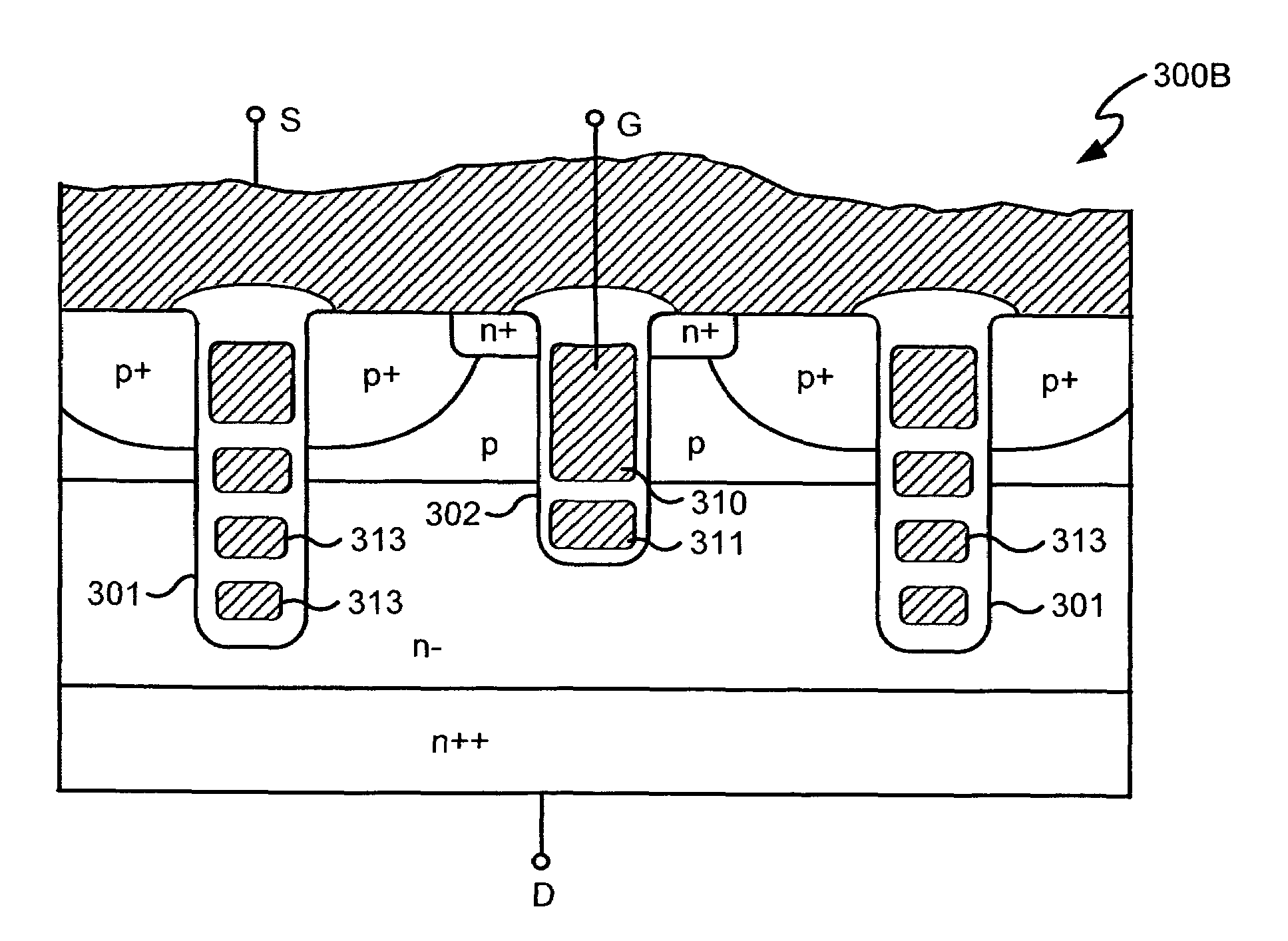

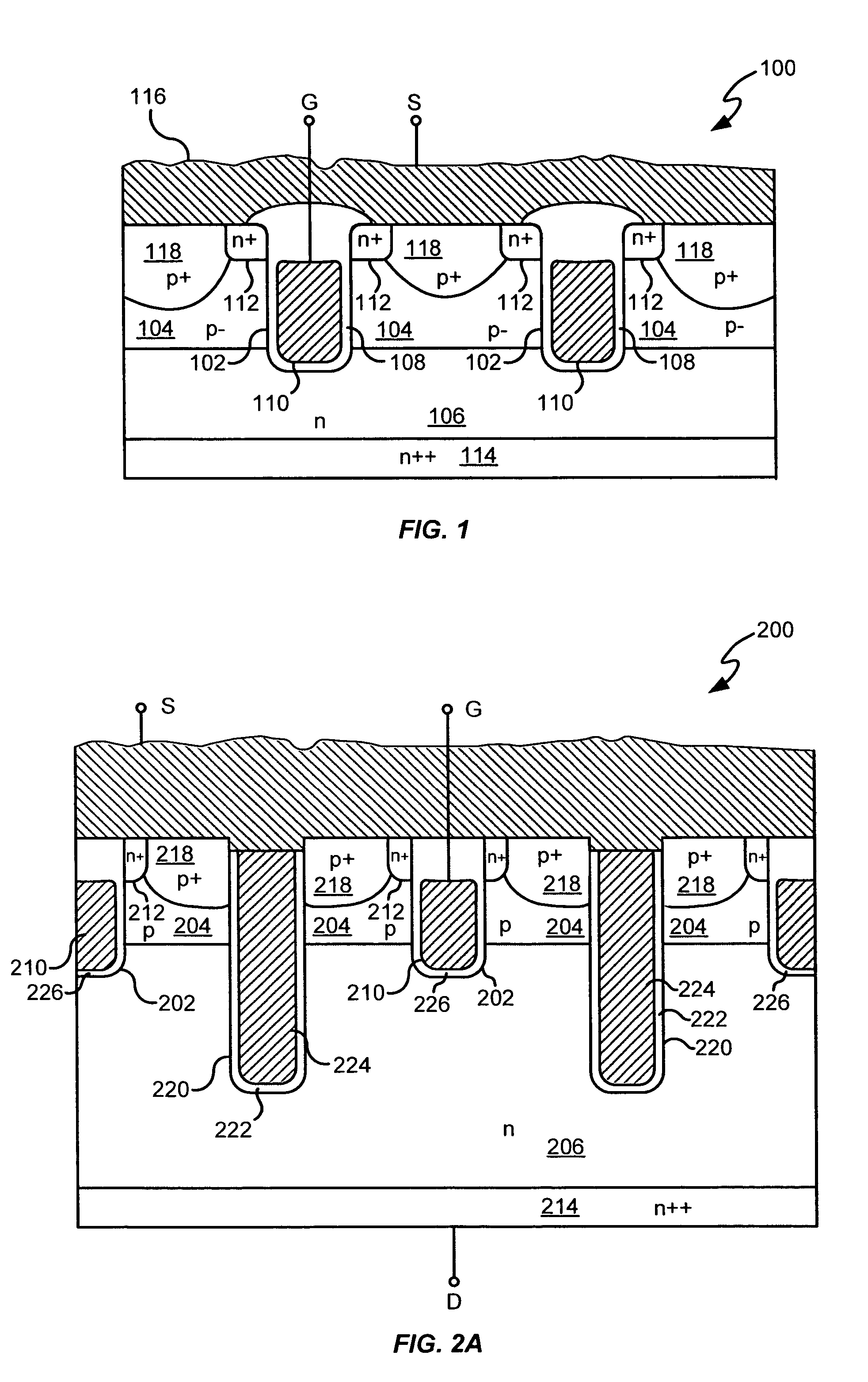

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

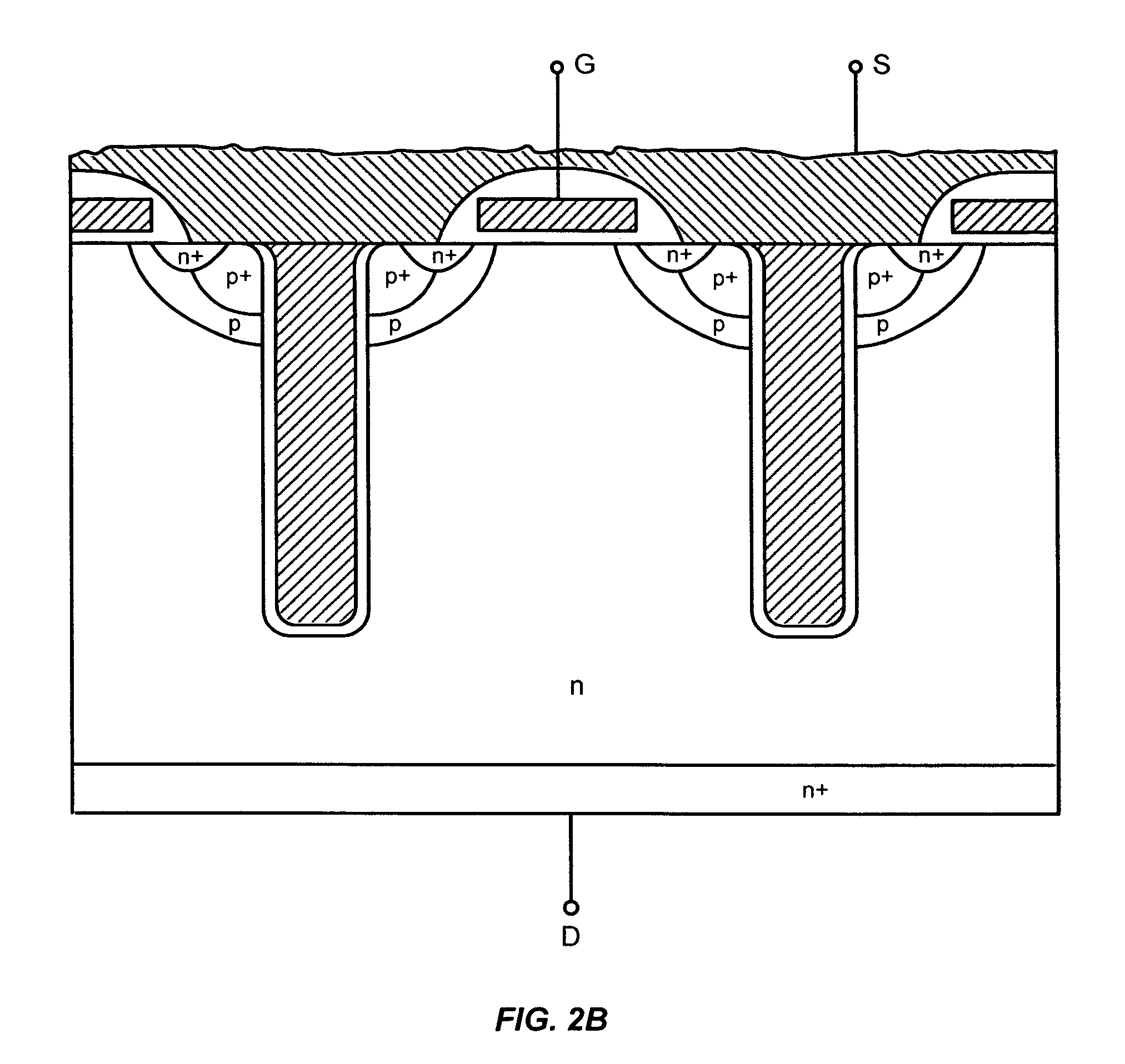

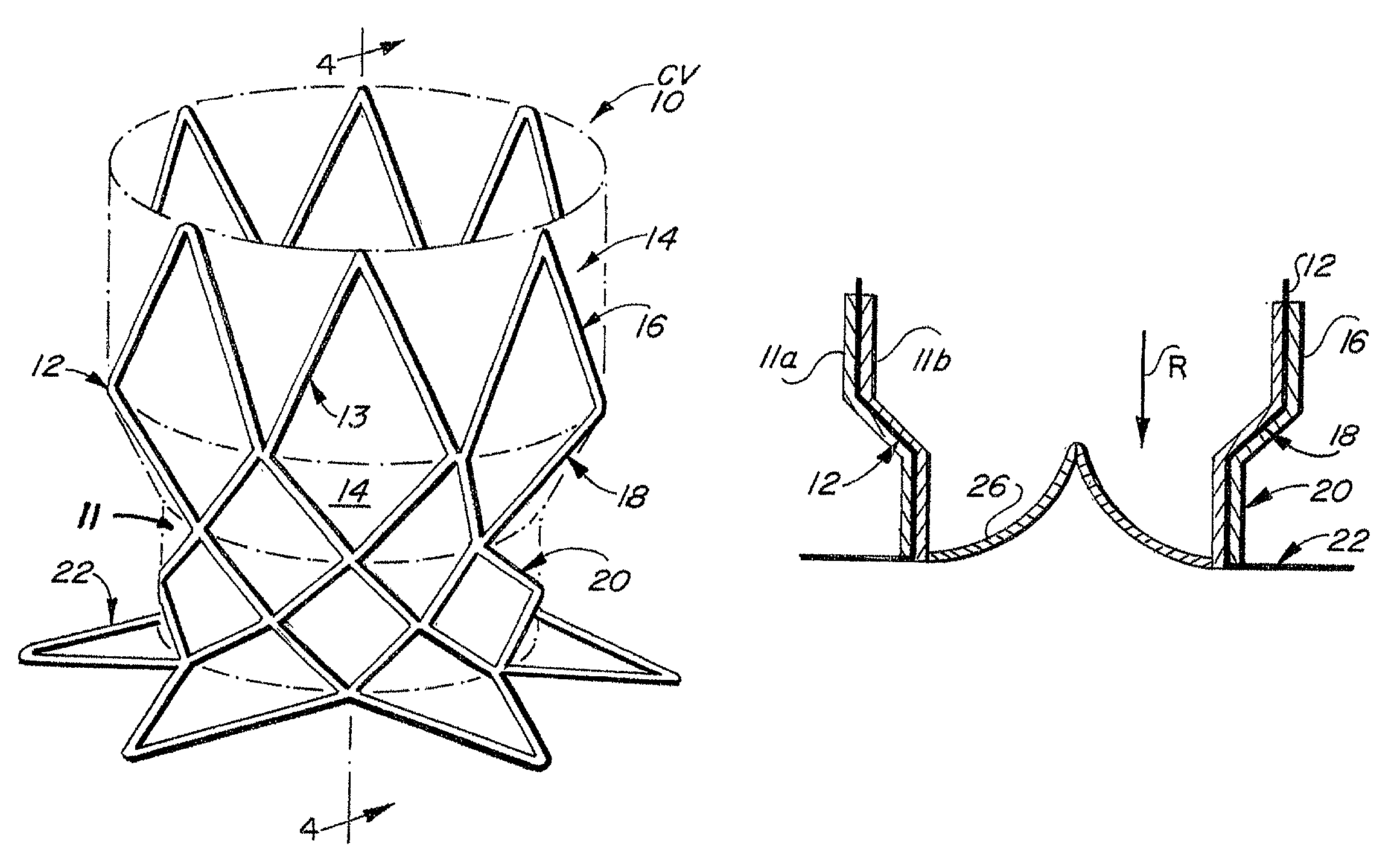

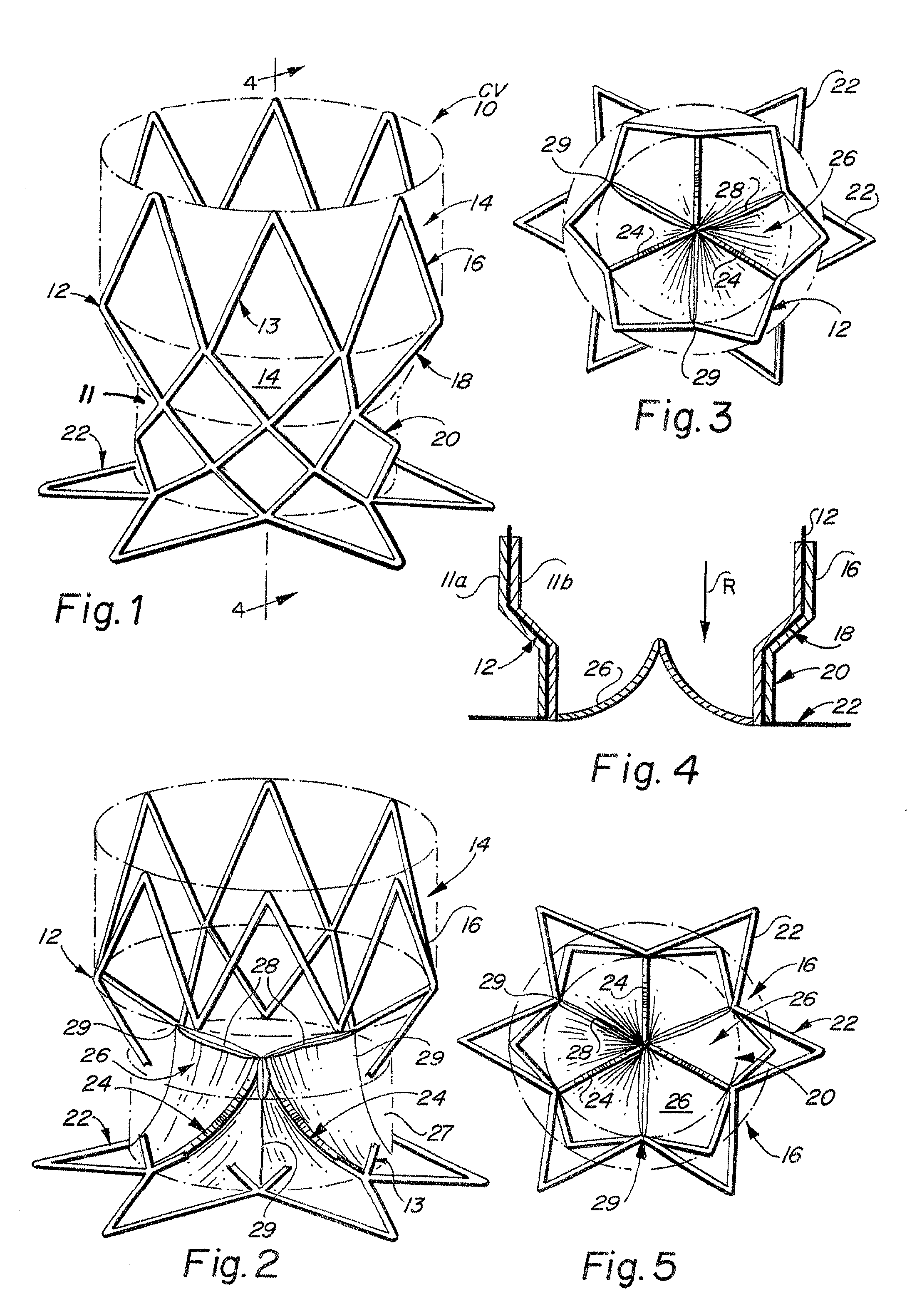

Valvular prostheses having metal or pseudometallic construction and methods of manufacture

InactiveUS7195641B2Promote migrationImprove film structureStentsVenous valvesVenous ValvesProsthesis

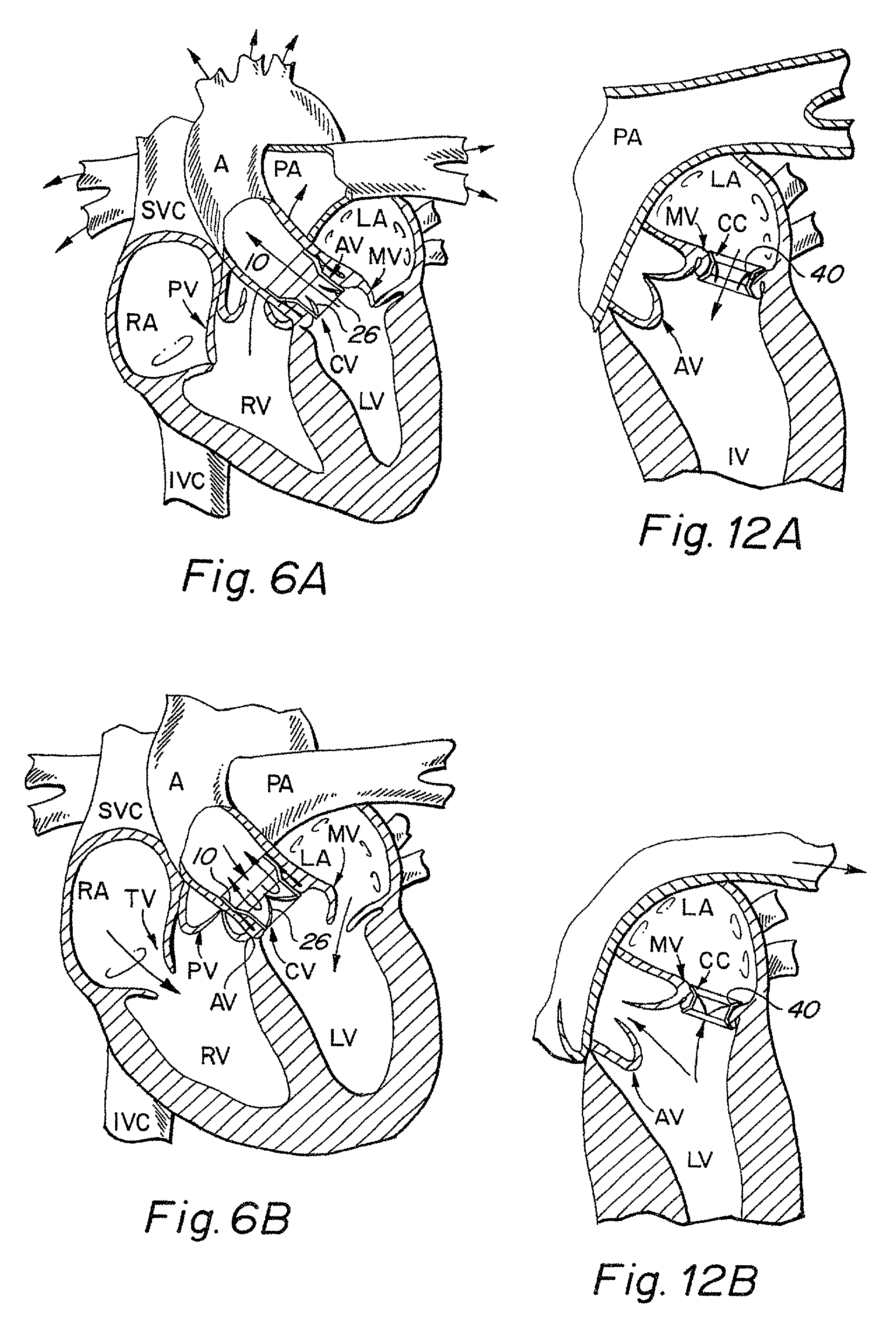

This invention relates to improvements in prosthetic cardiac and venous valves and implantable medical devices having moveable septa. The inventive prosthetic cardiac and venous valves have metallic or pseudometallic valves coupled to metallic or pseudometallic stents that permit percutaneous delivery of the devices.

Owner:VACTRONIX SCI LLC

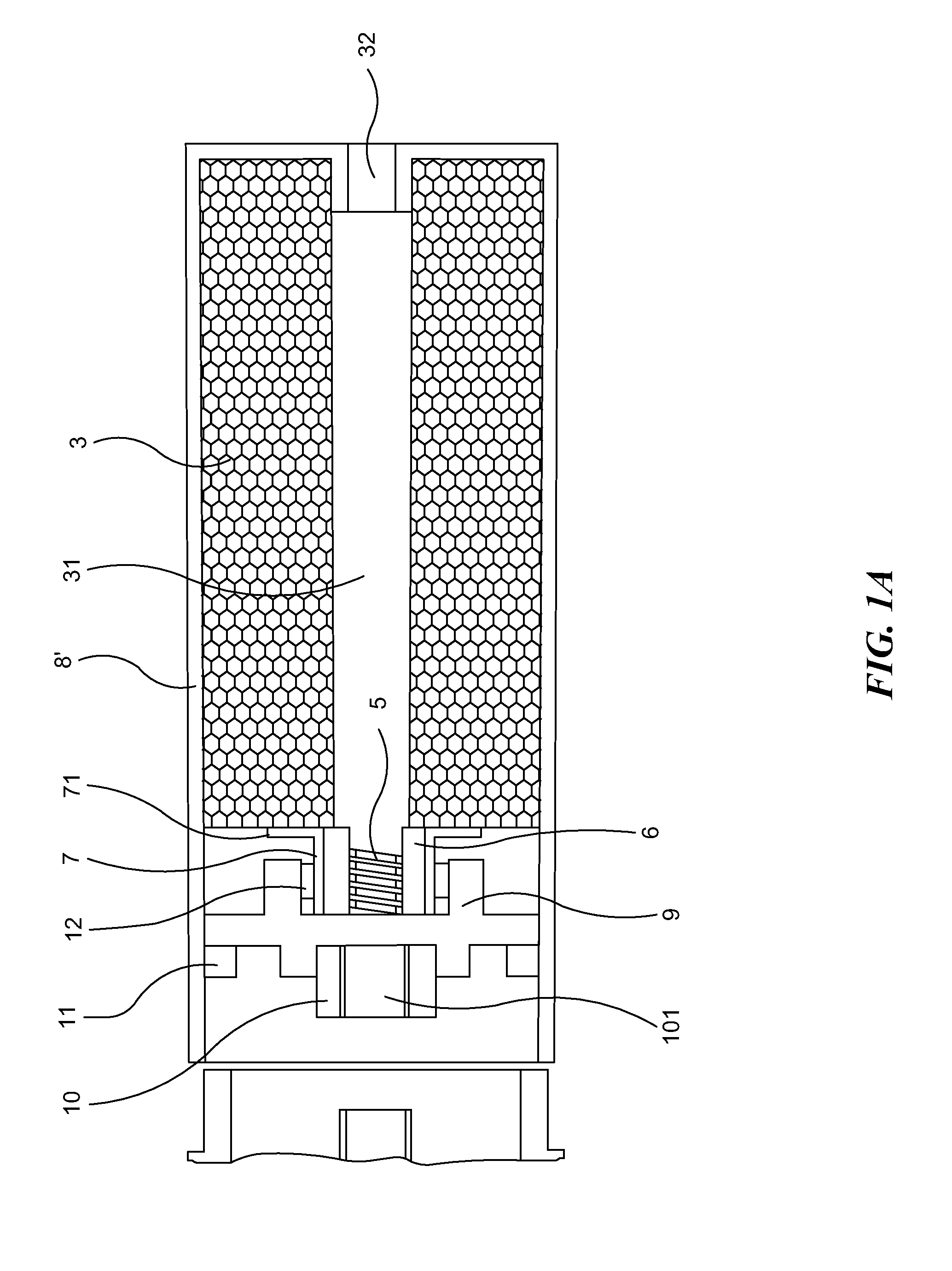

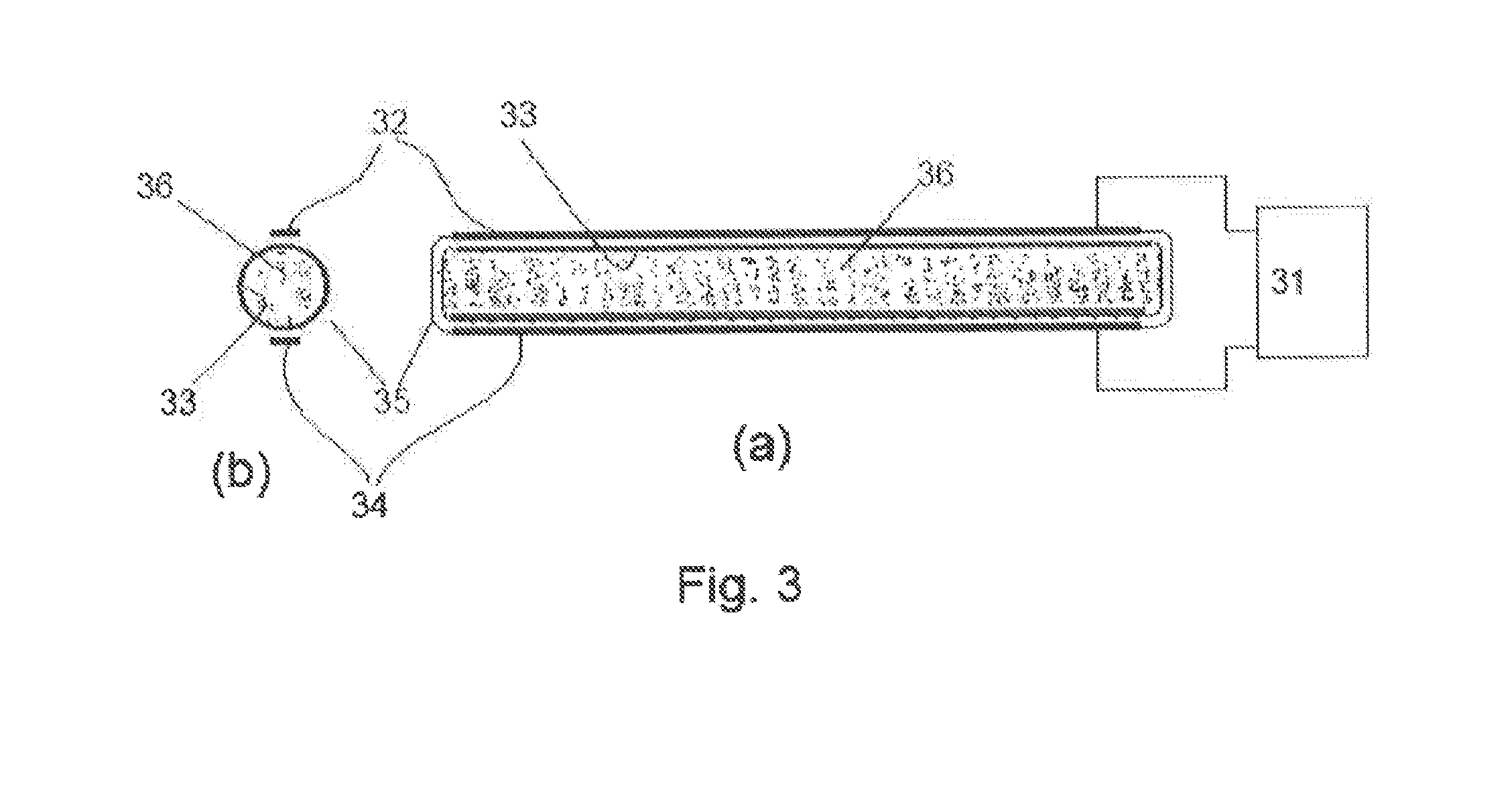

Heater for generating flavor and flavor generation appliance

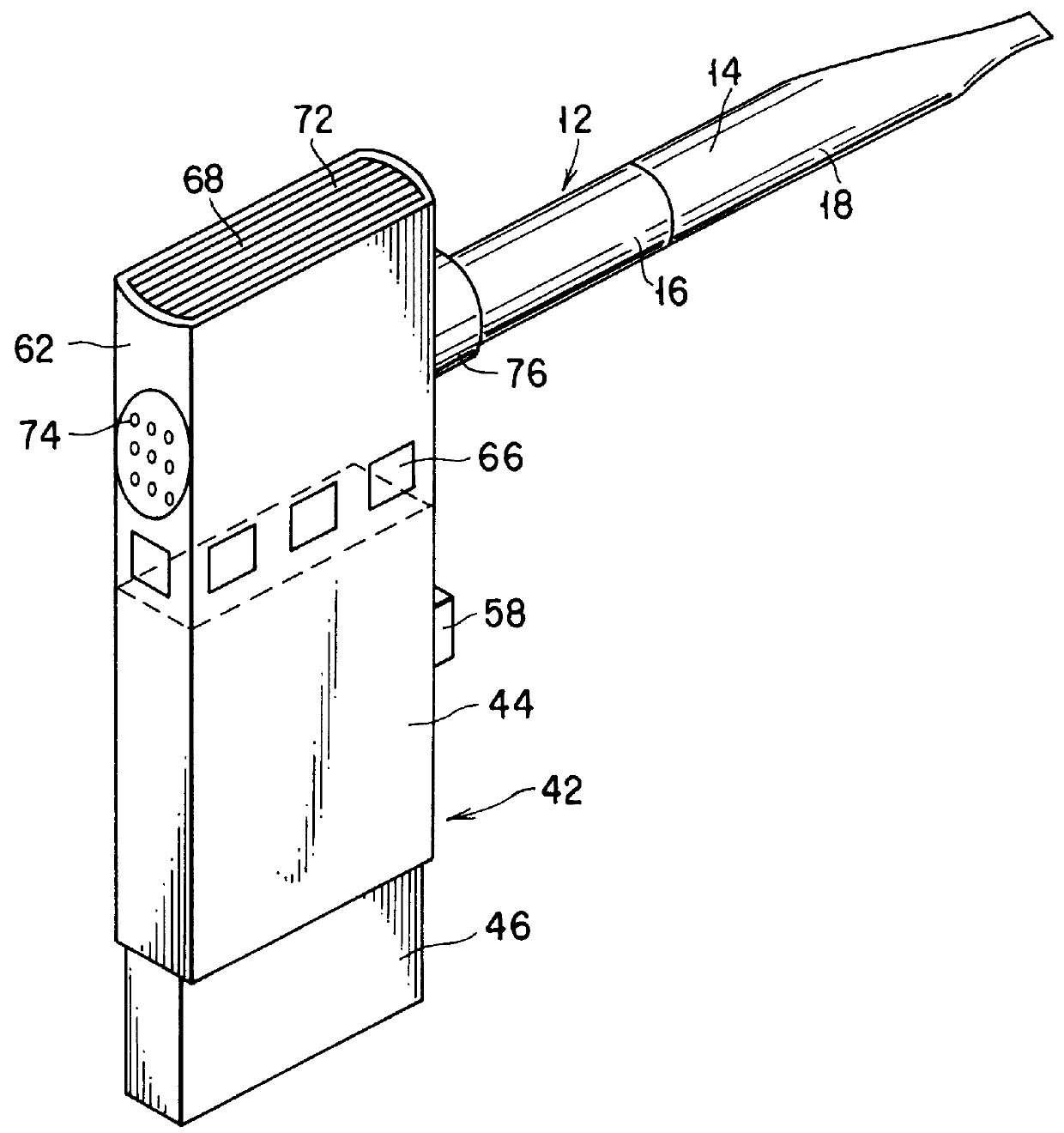

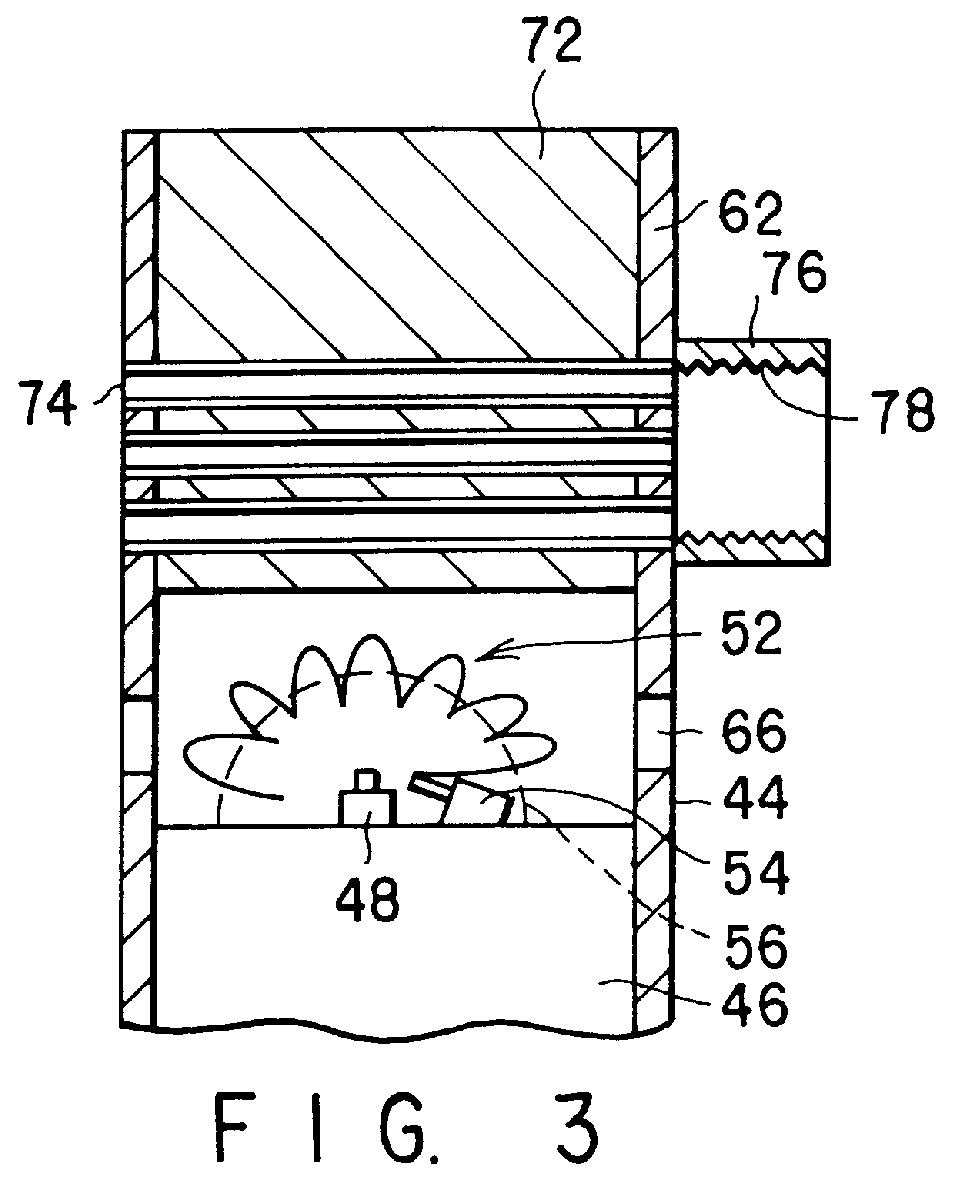

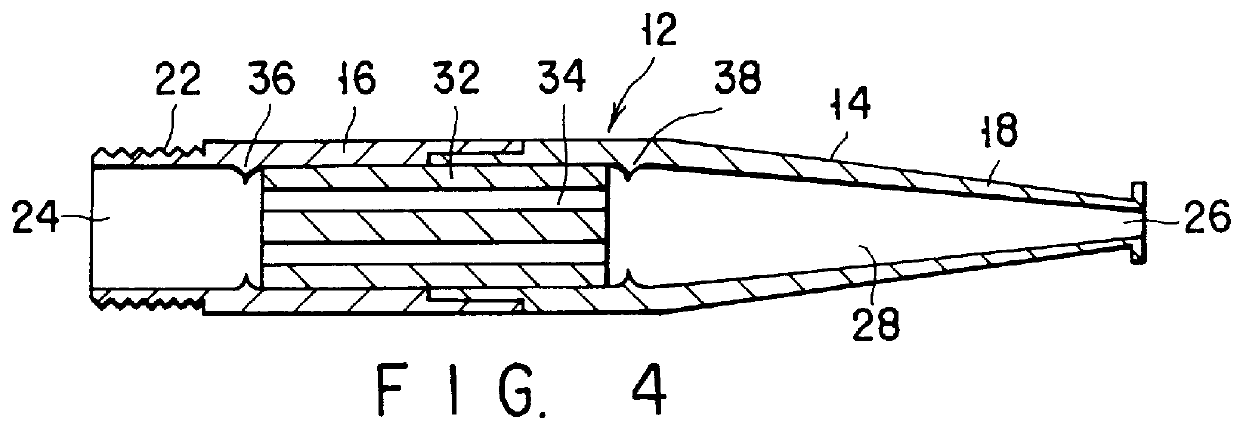

PCT No. PCT / JP97 / 01954 Sec. 371 Date Feb. 20, 1998 Sec. 102(e) Date Feb. 20, 1998 PCT Filed Jun. 9, 1996 PCT Pub. No. WO97 / 48294 PCT Pub. Date Dec. 24, 1997A flavor generation piece (12) incorporates a formed body (32) of a material containing a flavor substance. A heater (42) heats the flavor generation piece (12) without burning it, thereby generating a flavor. The heater (42) has a tank (46) mounted in a heat-insulating holder (44) to store a combustible gas. A combustion portion (52) for burning the combustible gas is disposed on the tank (46). Ignition or extinction of the combustion portion (52) is selected by a switch (58). The upper portion of the heat-insulating holder (44) forms a heat exchange duct (62) surrounding the combustion portion (52) and providing an exhaust path (64). An air pipe (74) is disposed to cross the heat exchange duct (62) transversely in the exhaust path (64). Heat exchange is performed between a fluid flowing in the exhaust path (64) and a fluid flowing in the air pipe (74). A socket (76) communicating with the air pipe (74) to detachably mount the flavor generation piece (12) is disposed on the outer side surface of the heat-insulating holder (44).

Owner:JAPAN TOBACCO INC

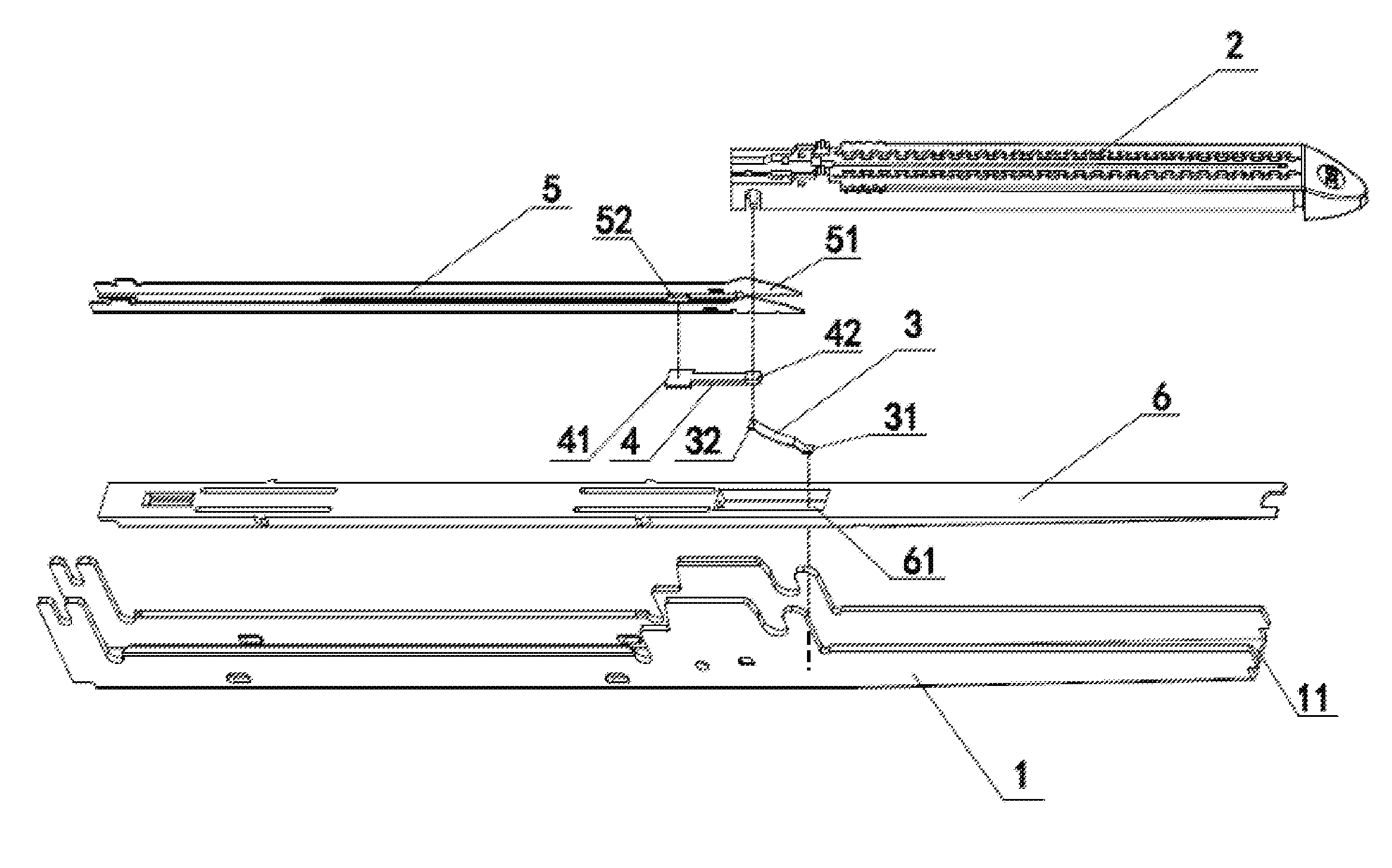

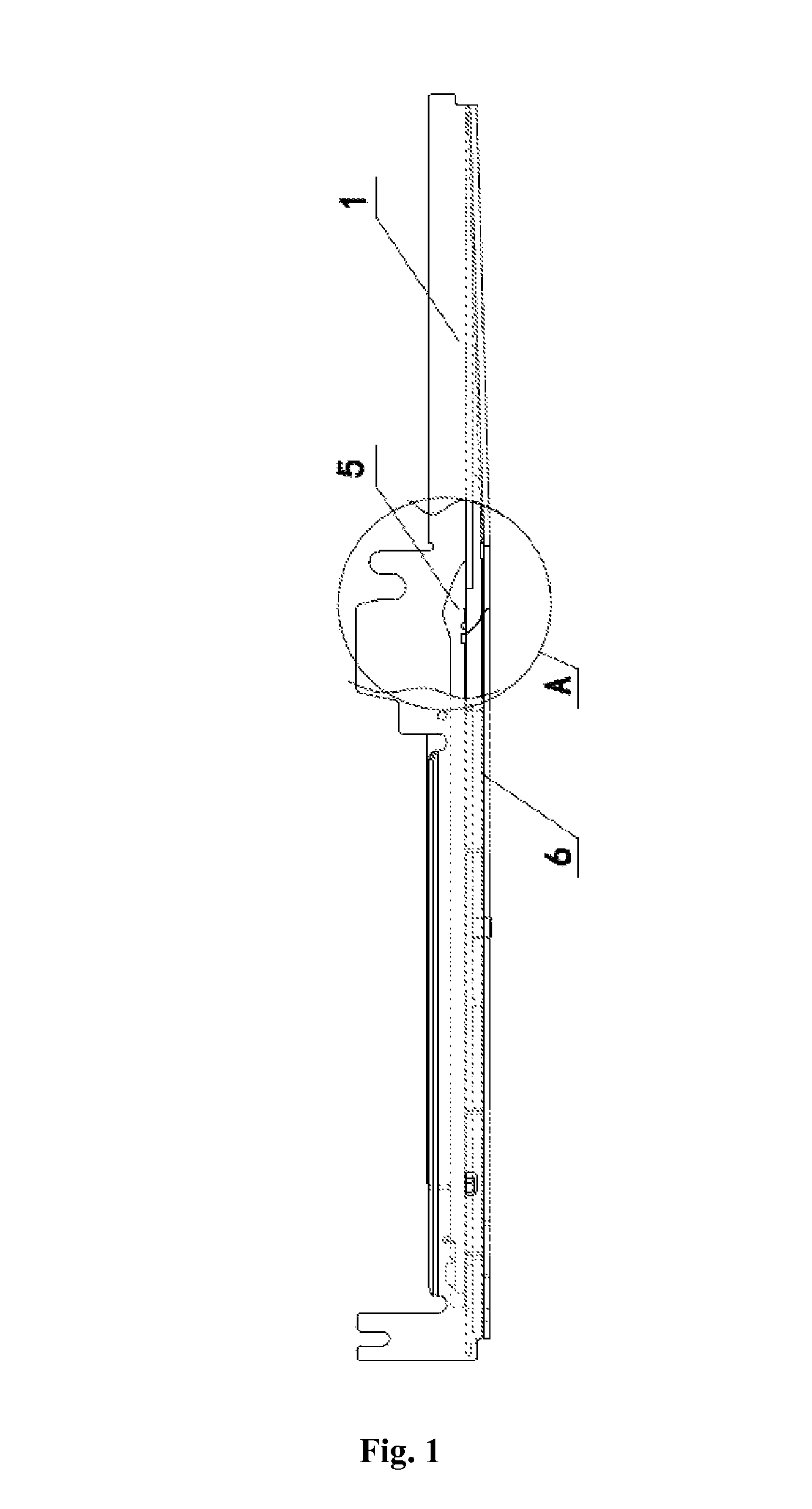

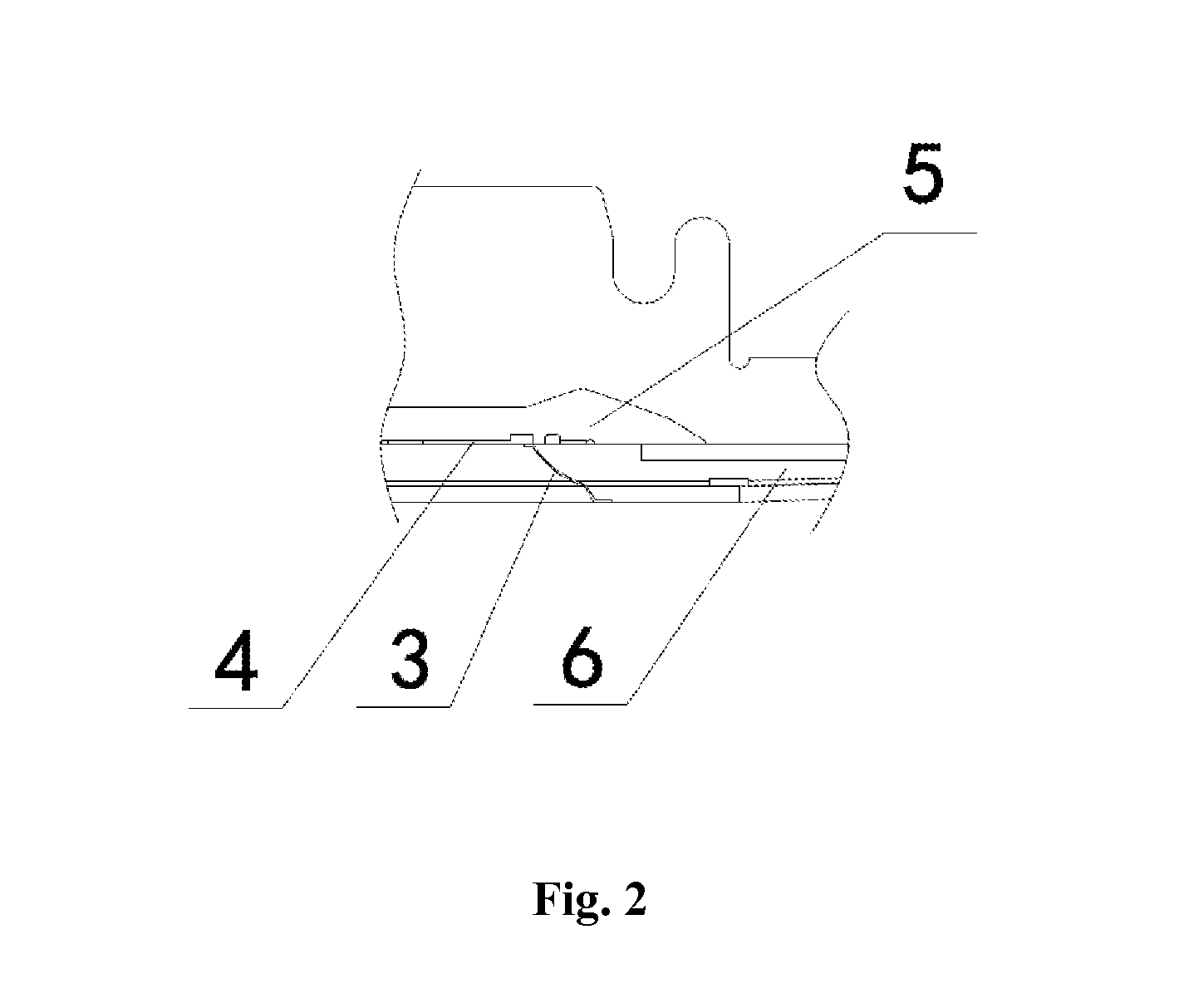

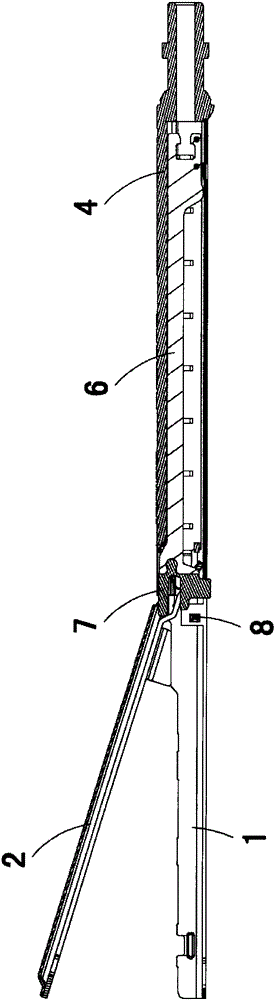

Linear cutting stapler

ActiveUS9433414B2Simple structureEasy to manufactureSuture equipmentsStapling toolsEngineeringCutting stapler

Owner:TOUCHSTONE INTERNATIONAL MEDICAL SCIENCE CO LTD

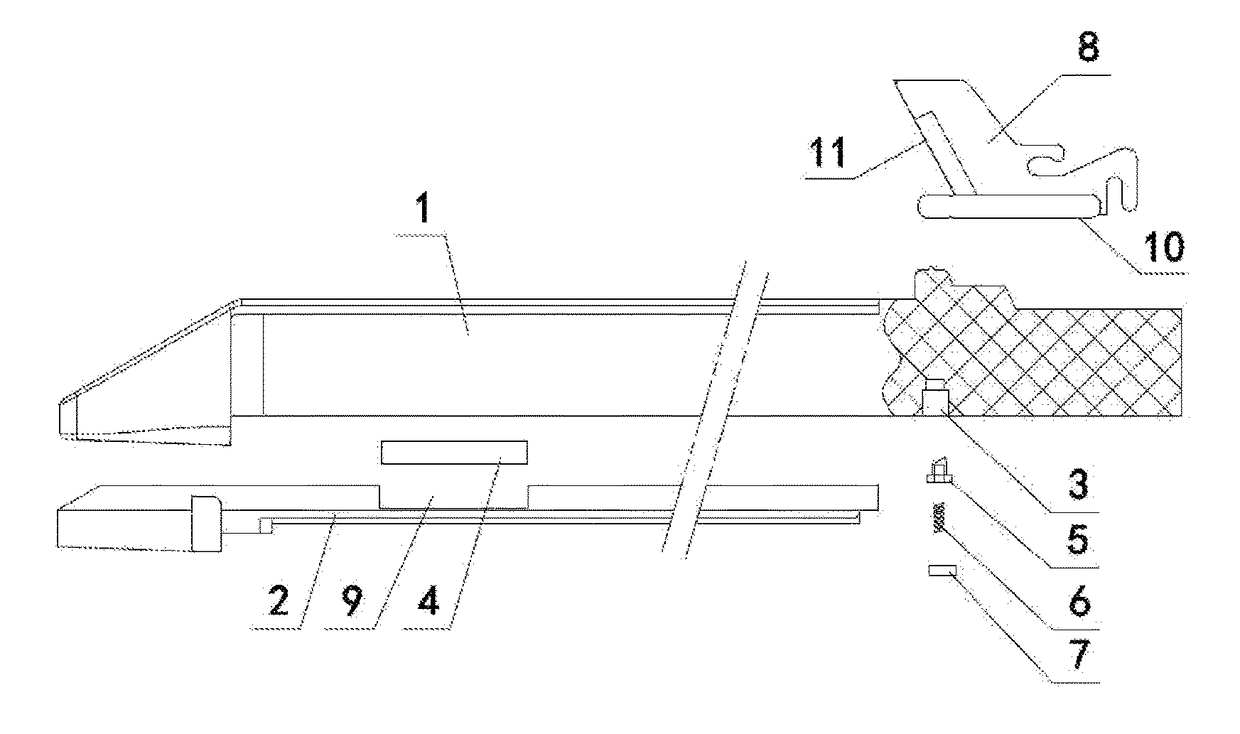

Staple chamber assembly and linear surgical stitching device using said staple chamber assembly

ActiveUS9931120B2Preventing error firingSimple structureSuture equipmentsStapling toolsReciprocating motionFar-red

A linear surgical stapler includes an upper staple cartridge receiving half-section, a lower staple cartridge receiving half-section and a staple cartridge assembly. The staple cartridge assembly includes a cutting groove in which a reciprocating movement cutter is mounted. The cutter includes a bottom surface and a knife blade located at a far end of the cutter. The staple cartridge assembly includes a restricting member mounted therein and an elastic stopper. The elastic stopper abuts against the restricting member when the staple cartridge assembly is in an initial state. The restricting member breaks away from the staple cartridge assembly when the staple cartridge assembly is in a firing complete state, thereby preventing the cutter from sliding towards the far end of the staple cartridge. As a result, misfiring throughout the whole operation of the linear surgical stapler is prevented.

Owner:TOUCHSTONE INTERNATIONAL MEDICAL SCIENCE CO LTD

Straight seam cutter

ActiveCN103860225BAvoid surgeryAvoid medical malpracticeEndoscopic cutting instrumentsSurgical staplesLinear motionEngineering

The invention discloses a linear type suturing and excising device, comprising a body, a staple cartridge rack, a staple anvil, a staple cartridge, a cocking block and a knife pushing rod, wherein the staple cartridge rack, the staple anvil and the staple cartridge are arranged at the far end of the body, the cocking block is used for pushing a staple pushing piece and is arranged in a chute of the staple cartridge, the knife pushing rod pushes the cocking block to move, the staple cartridge rack is provided with a safety block for preventing secondary cocking, the safety block has a linear motion trail, the moving direction of the safety block is vertical to the moving direction of the knife pushing rod, and the safety block is arranged at the far end of the knife pushing rod and the excising knife, and is used for limiting the movement of the knife pushing rod and the excising knife from the near end of the linear suturing and excising device to the far end of the linear suturing and excising device when the linear type suturing and excising device is under the initial state and under the state of cocking completion. The linear type suturing and excising device has the beneficial effects that a doctor is effectively prevented from performing the next operation under the condition of not replacing a cocked staple cartridge, the occurrence of medical negligence is avoided, and the structure is simple and effective.

Owner:TOUCHSTONE INTERNATIONAL MEDICAL SCIENCE CO LTD

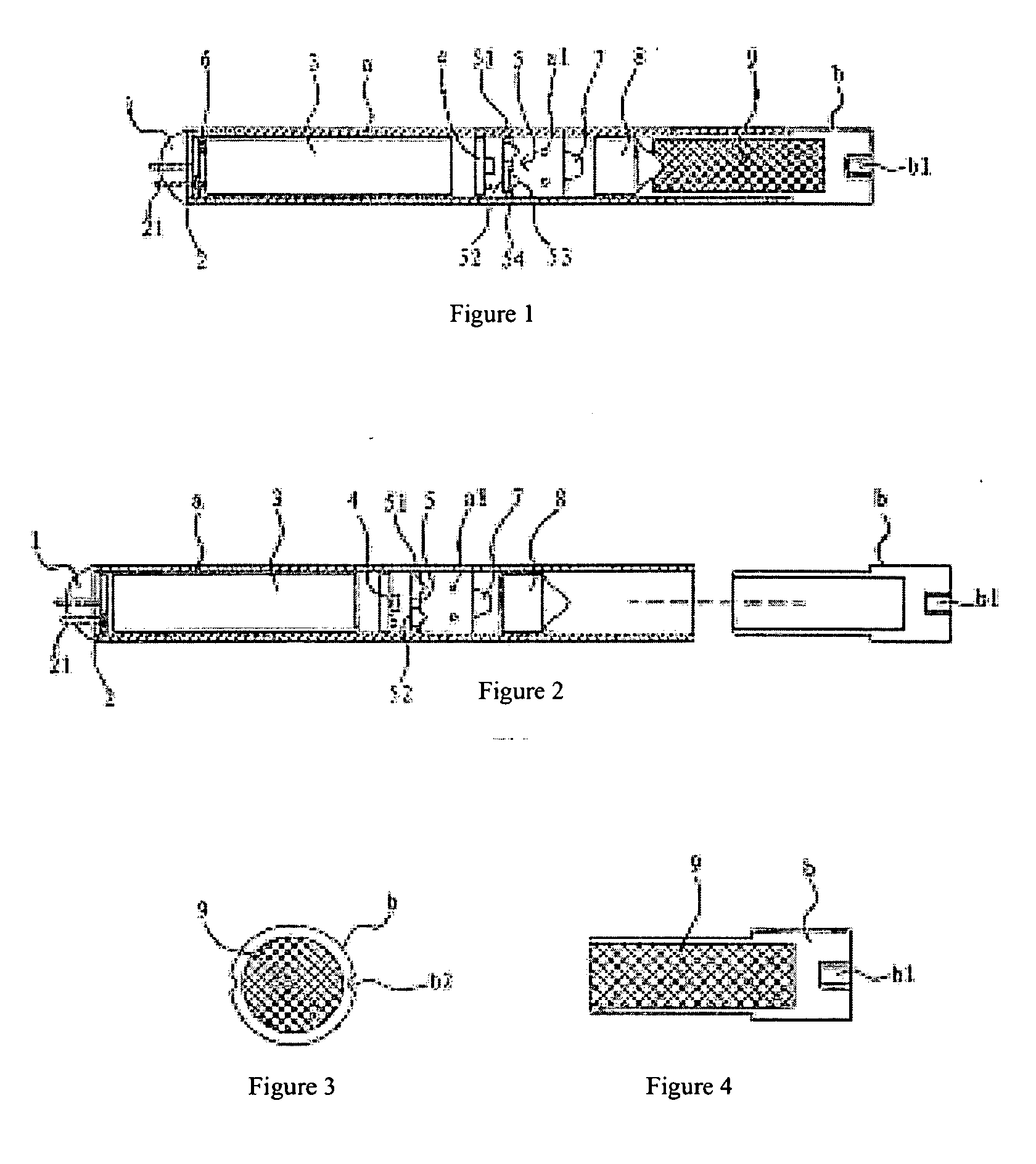

Tobacco Solution Atomizing Device For Electronic Cigarette

A tobacco solution atomizing device for electronic cigarette is disclosed the device comprises an atomizer installed in a fixing sleeve; a suction nozzle component and electrode connectors coupled on respective ends of the fixing sleeve, wherein the electrode connectors comprises a positive electrode connector and a negative electrode connector; the atomizer comprising a glass fiber tube, a glass fiber yarn, a heating coil, a cotton cloth layer and a synthetic fiber layer, wherein the glass fiber yarn is insert into the heating coil which is then located inside the glass fiber tube; the ends of the glass fiber silk and two wires which are used to electronically connect the heating coil to the positive and negative electrode connectors extends outward through the glass fiber tube; the cotton cloth layer enwraps the outside wall of the glass fiber tube and reveal ends of the glass fiber yarn are pressed tightly between the cotton cloth layer and the glass fiber tube; a synthetic fiber layer is filled within the annular shape space between the cotton cloth layer and the fixing sleeve for holding the tobacco solution.

Owner:LI YONGHAI +1

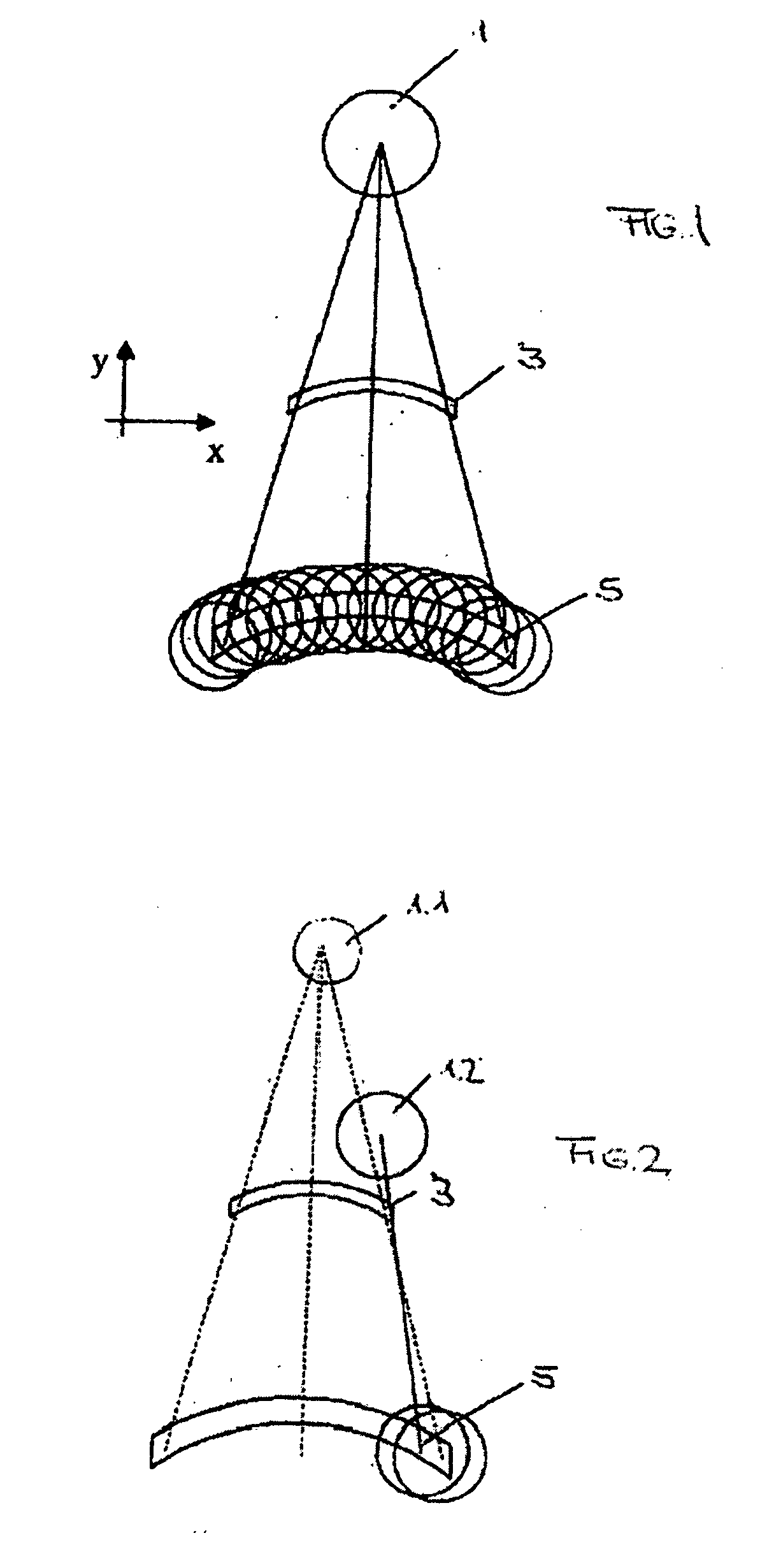

Rotational antenna and semiconductor device including the same

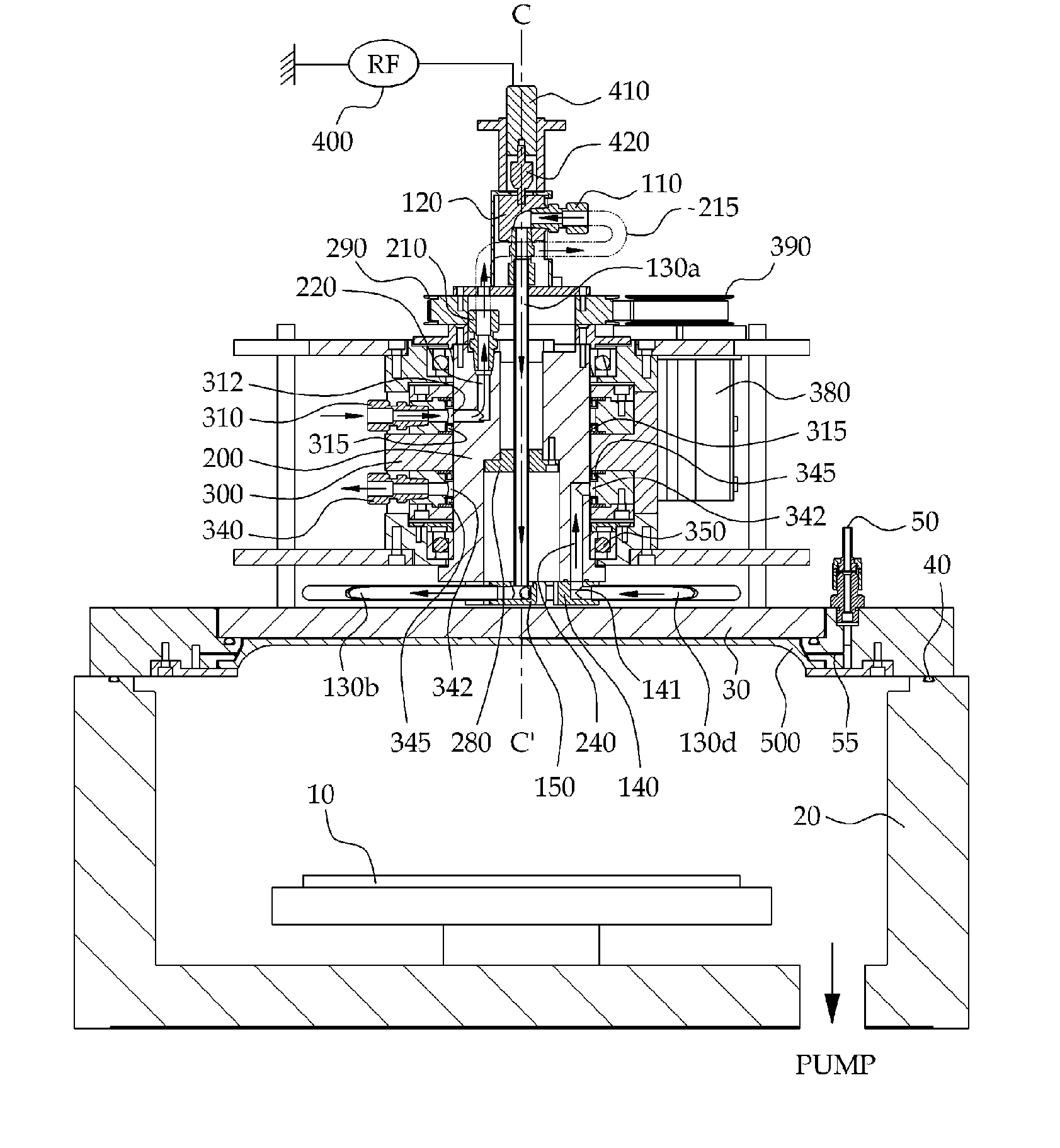

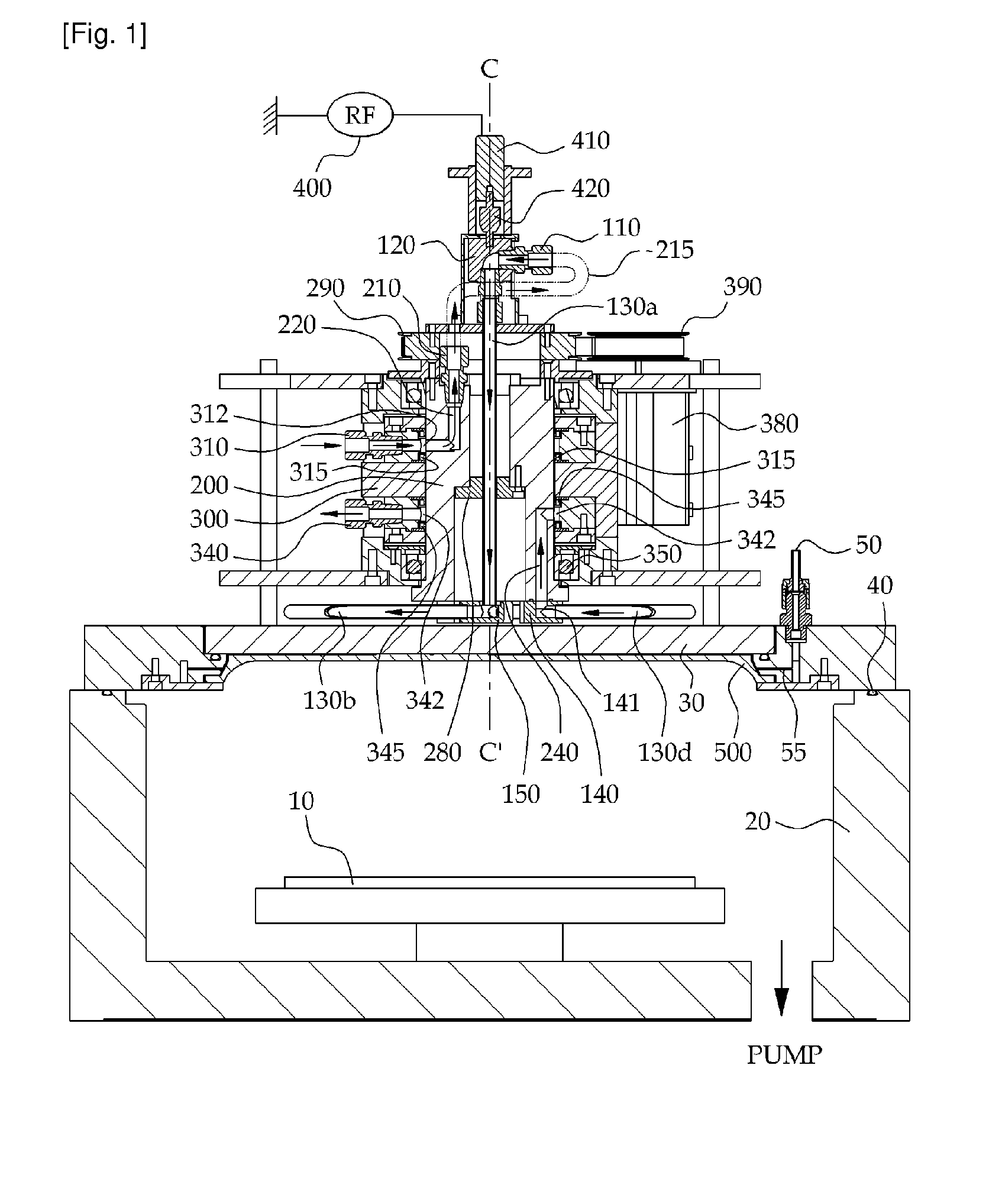

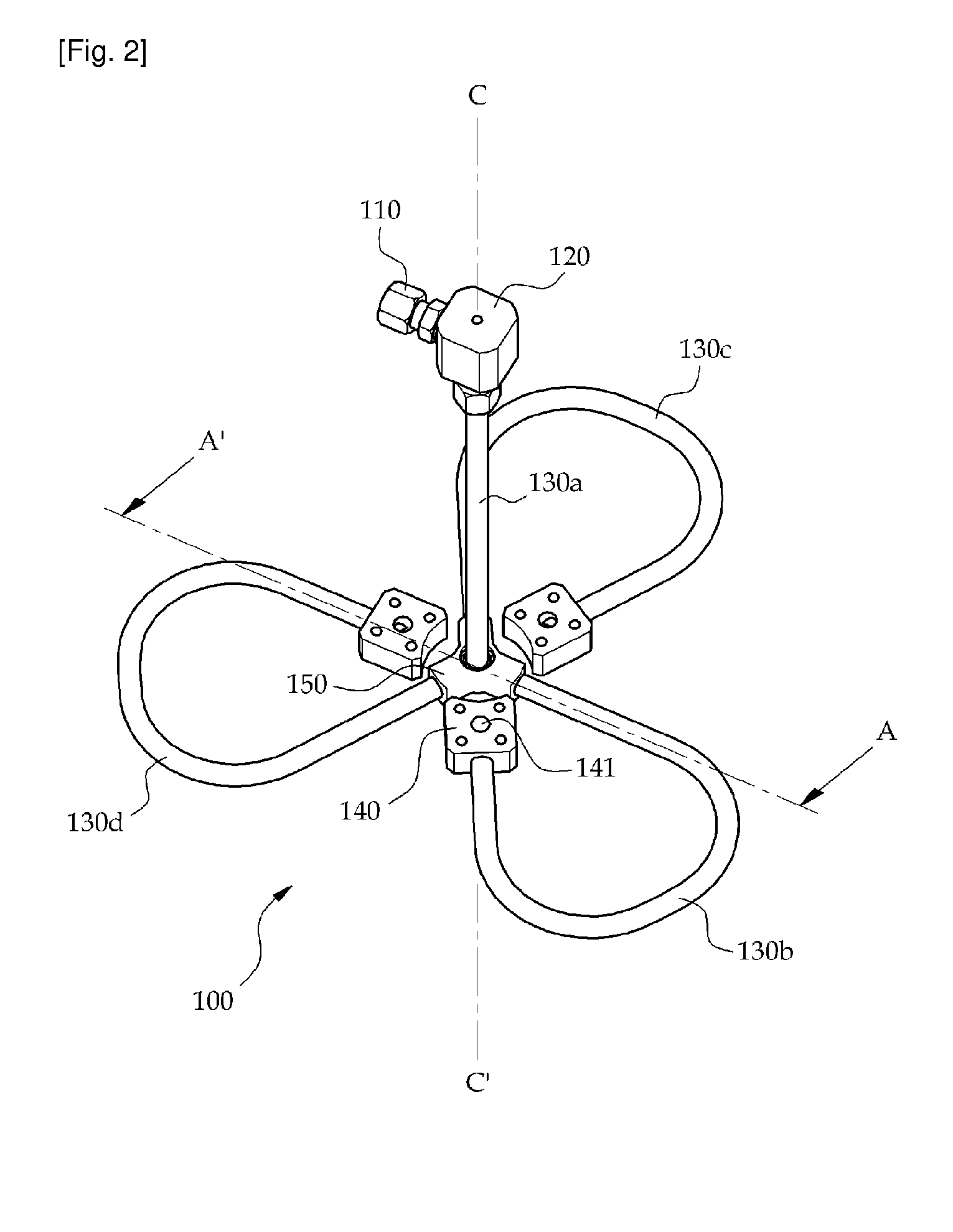

ActiveUS20110000619A1Easy to optimizeReduce lossesElectric discharge tubesSemiconductor/solid-state device manufacturingHigh frequency powerDevice material

A rotational antenna and a semiconductor manufacturing device provided with the same are disclosed. The rotational antenna includes a plurality of coils connected in parallel to a high frequency power source and arranged at a regular interval around an axis in a symmetrical relationship with respect to the axis, wherein an electromagnetic field for generating inductively coupled plasma is uniformly formed when the coils are rotated about the axis.

Owner:ALLIED TECHFINDERS

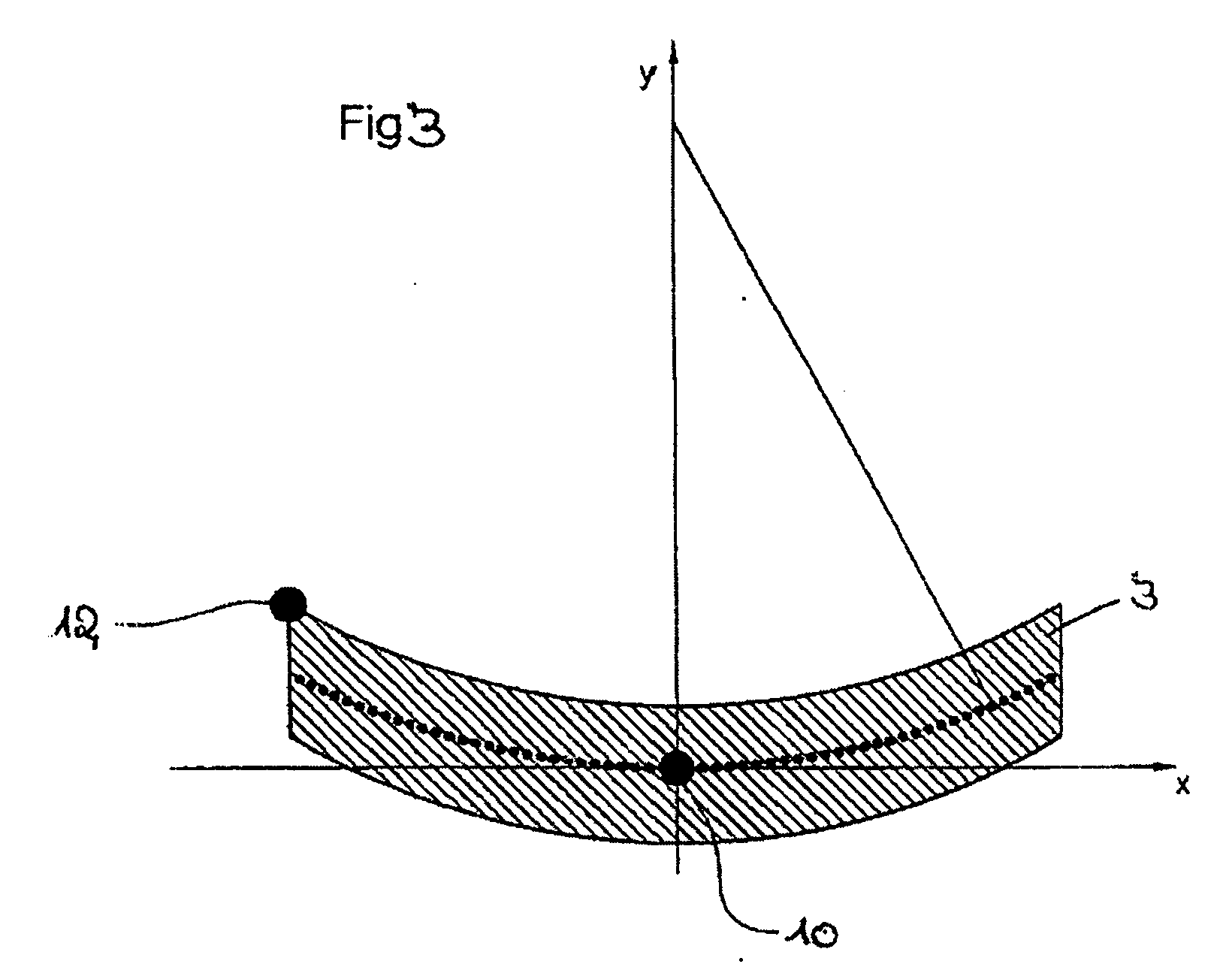

Optical element for an illumination system

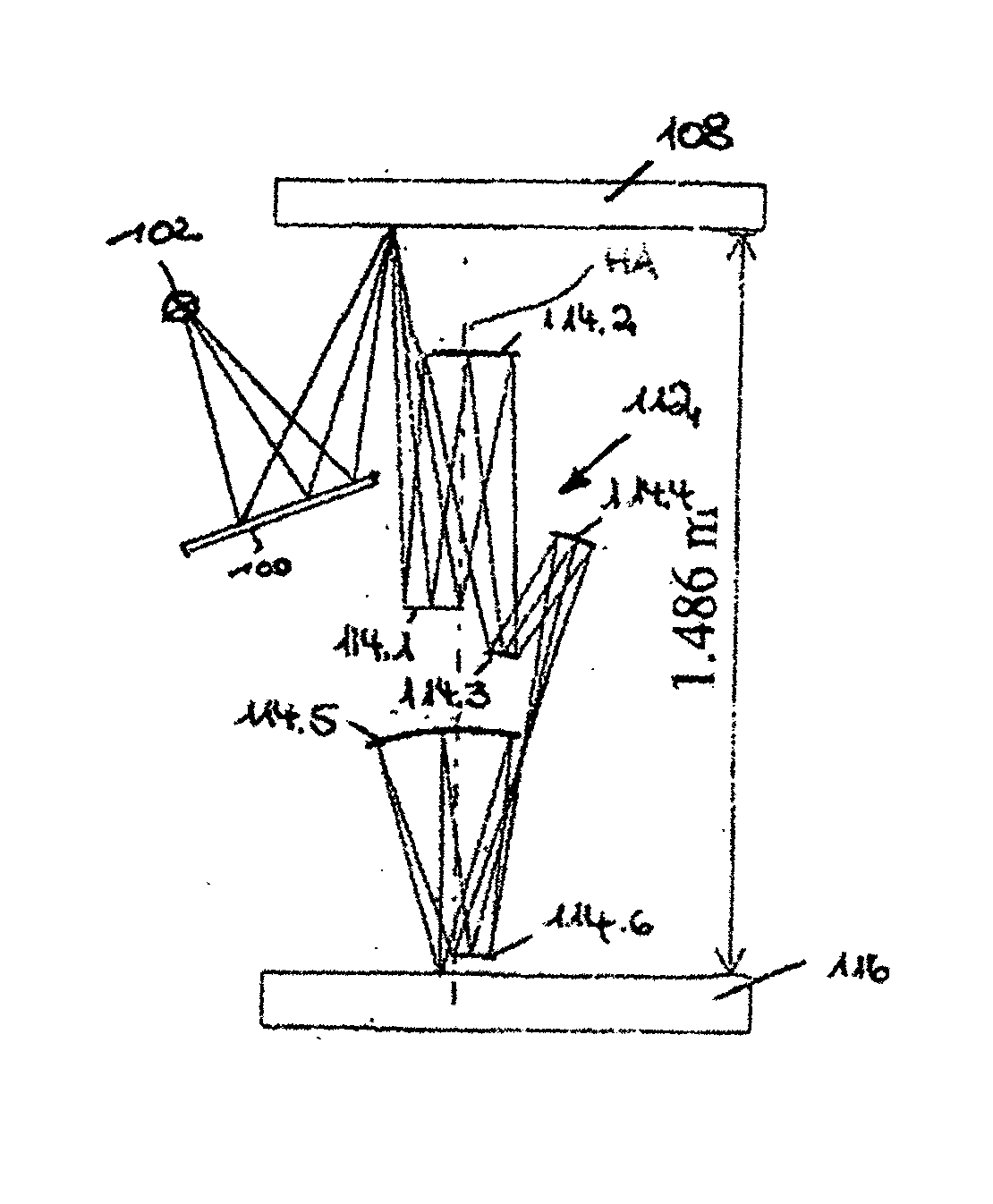

InactiveUS20060132747A1Reduce in quantityReduce light lossPhotomechanical exposure apparatusMicrolithography exposure apparatusExit pupilLength wave

There is provided an optical element for an illumination system for wavelengths of ≦193 nm. The illumination sytem includes a light source, a field plane, an exit pupil, and a plurality of facets. The plurality of facets receives light from the light source and guides the light to a plurality of discrete points in the field plane. The plurality of discrete points collectively illuminate a field in the field plane, and each of the plurality of facets illuminates a region of the exit pupil.

Owner:CARL ZEISS SMT GMBH

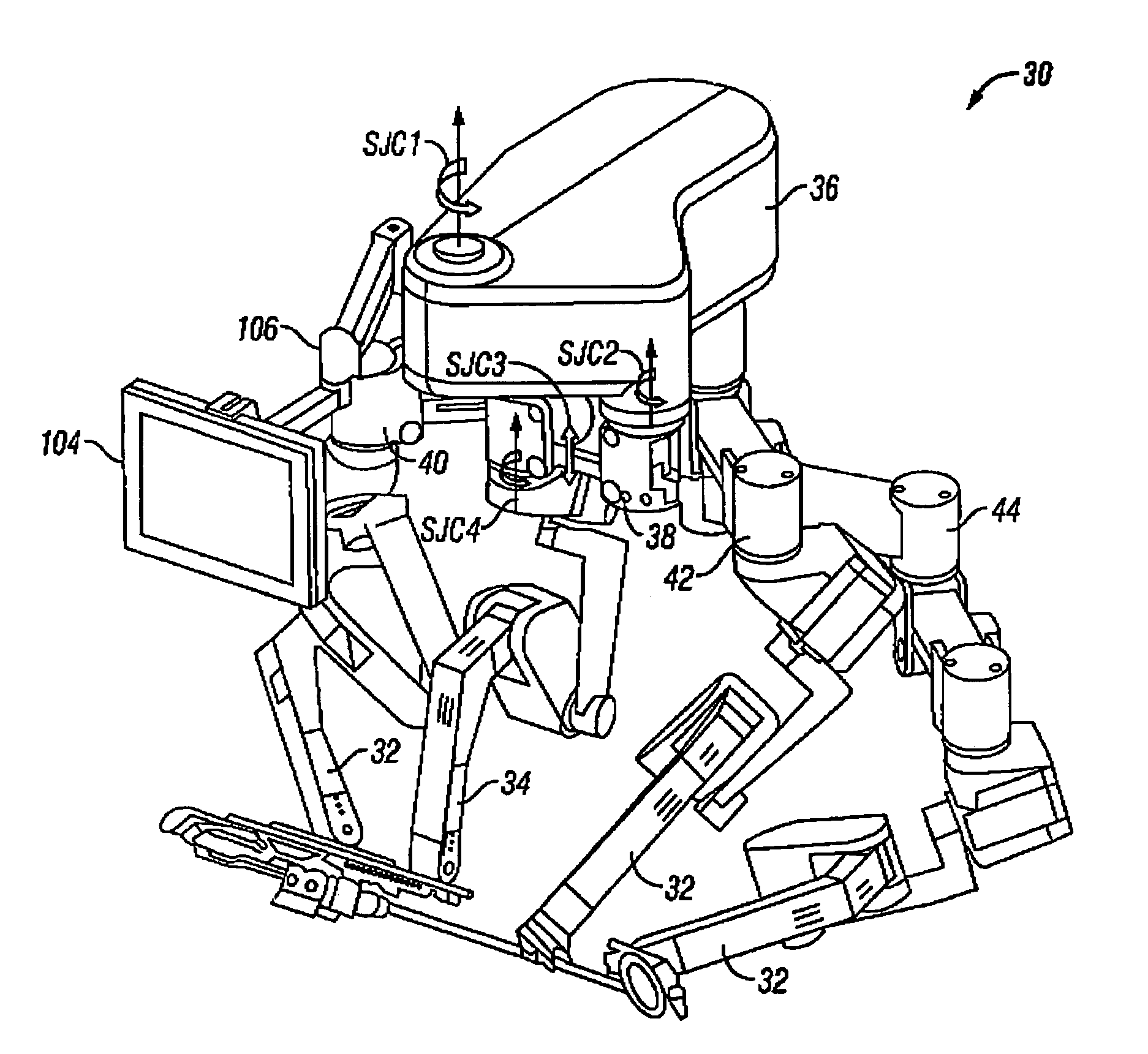

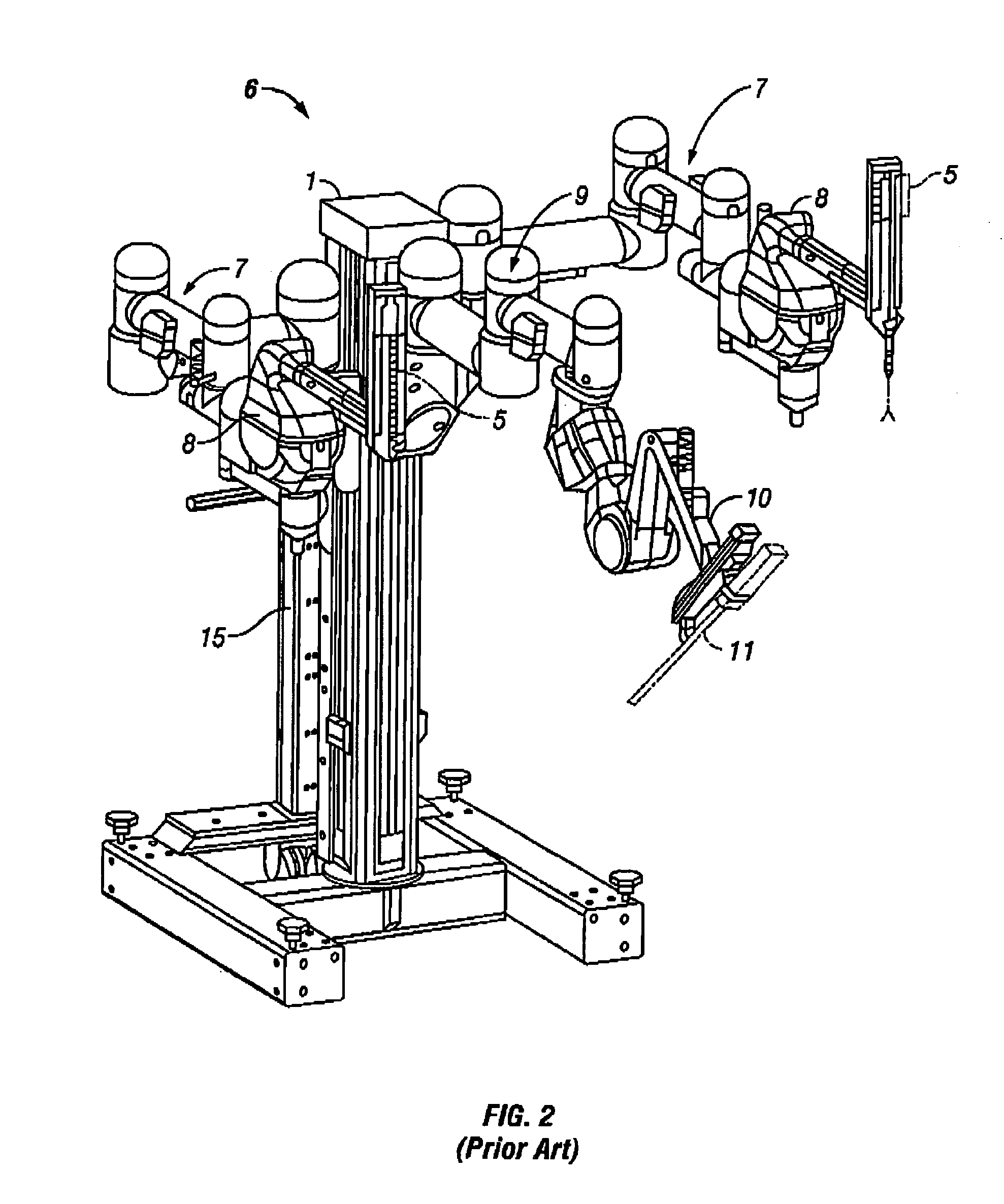

Modular manipulator support for robotic surgery

InactiveUS7763015B2Simple structureReduce complexityDiagnosticsRobotSurgical instrumentationModularity

A robotic surgery system comprises a mounting base, a plurality of surgical instruments, and an articulate support assembly. Each instrument is insertable into a patient through an associated minimally invasive aperture to a desired internal surgical site. The articulate support assembly movably supports the instruments relative to the base. The support generally comprises an orienting platform, a platform linkage movably supporting the orienting platform relative to the base, and a plurality of manipulators mounted to the orienting platform, wherein each manipulator movably supports an associated instrument.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

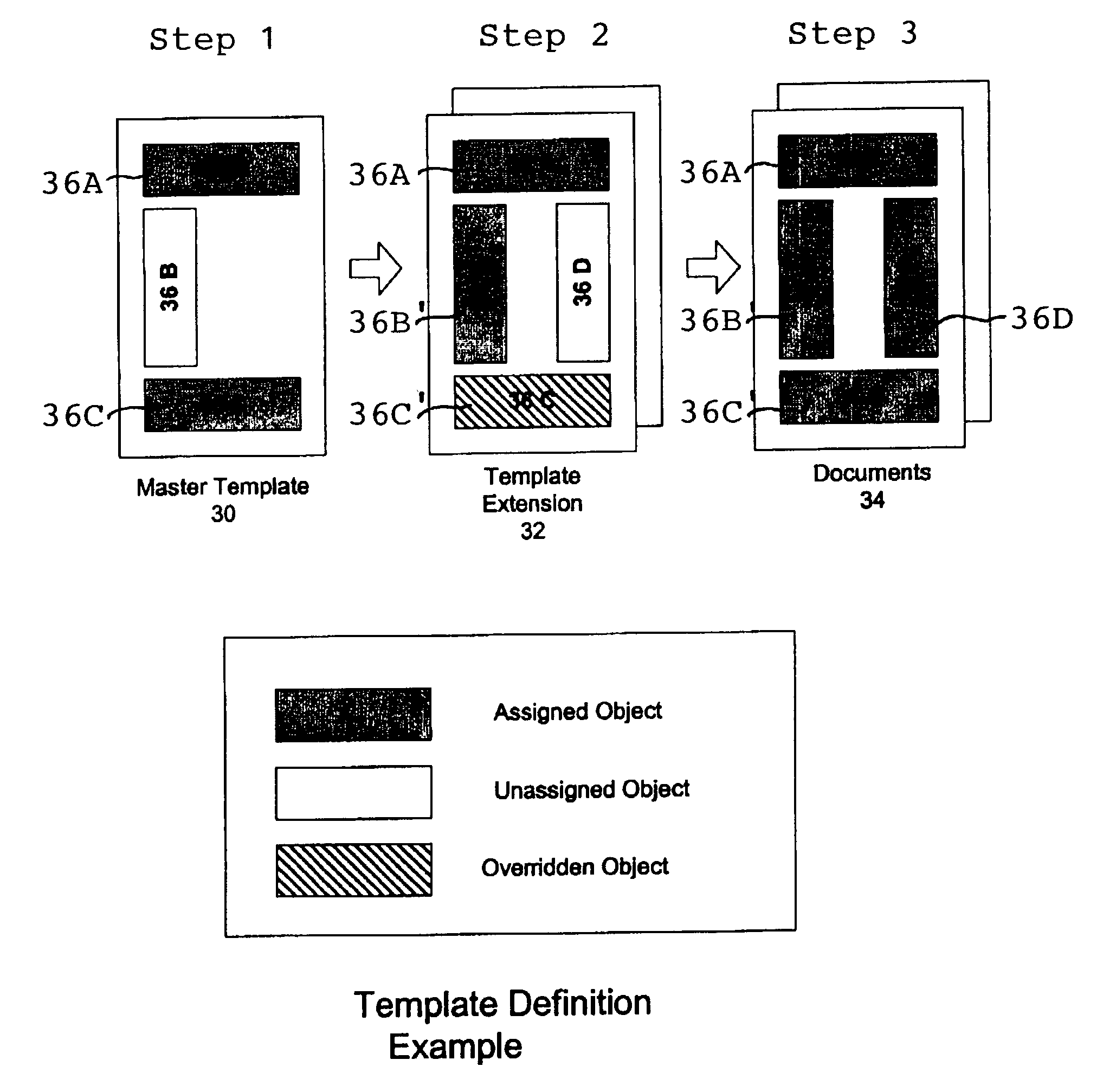

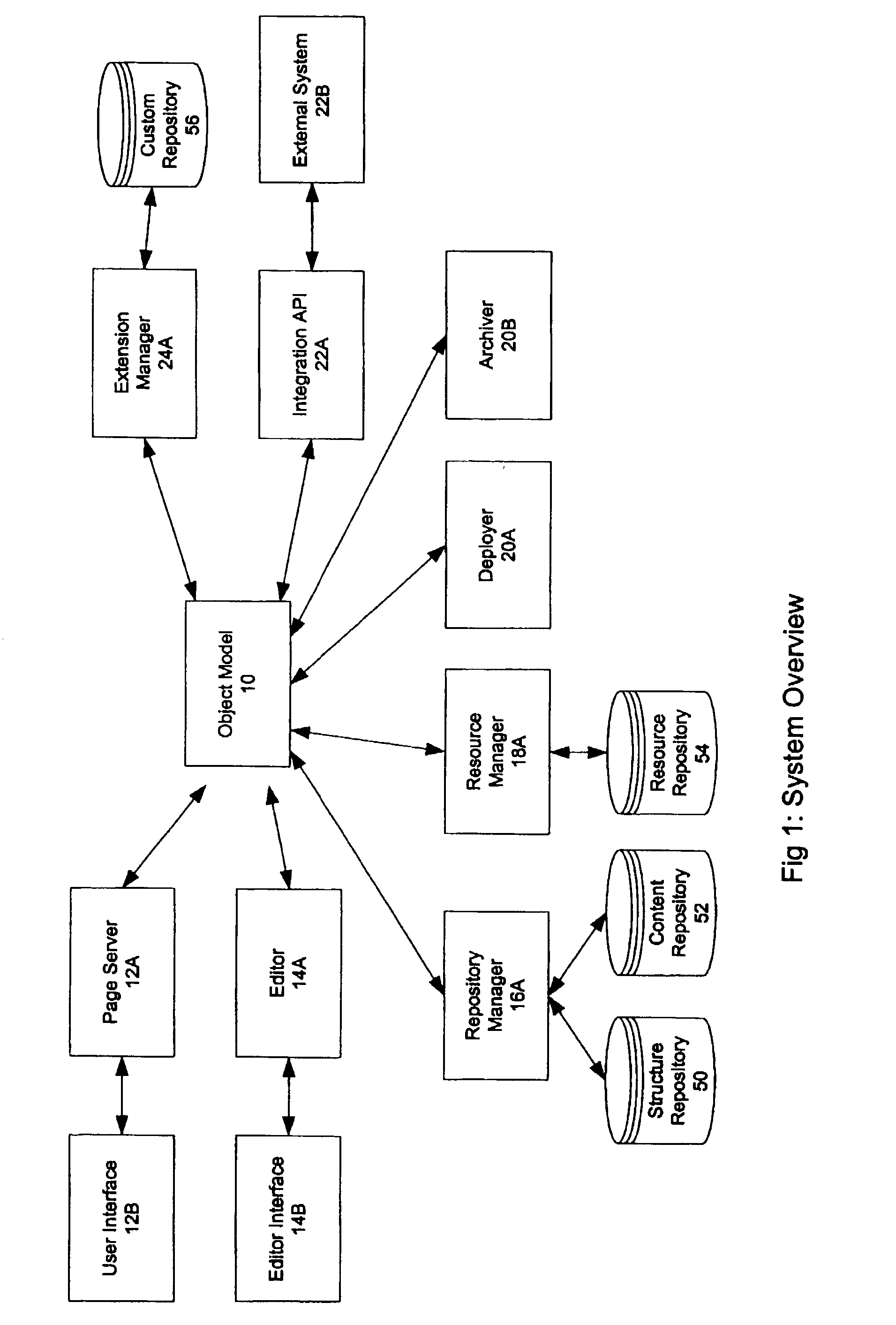

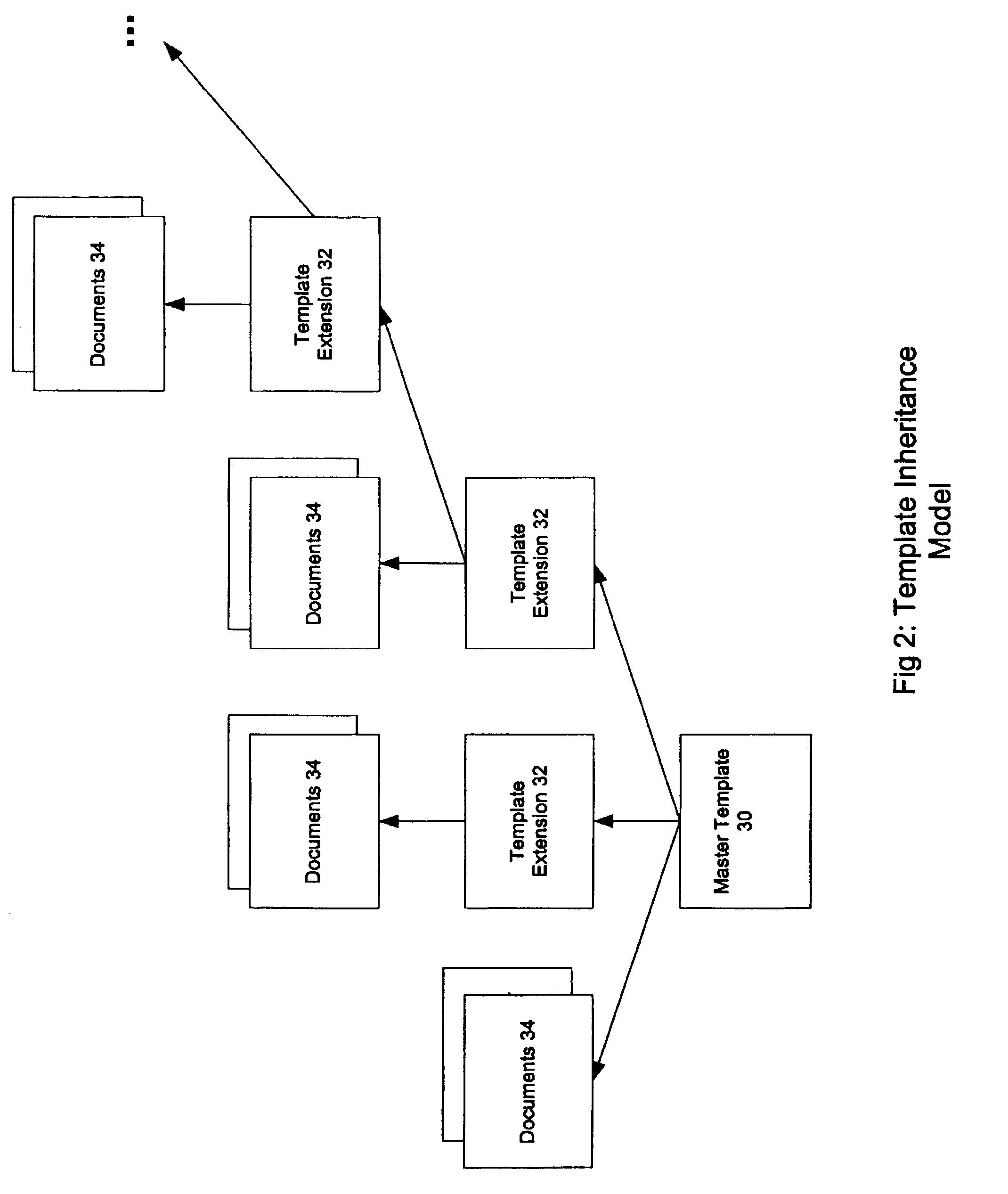

Web site application development method using object model for managing web-based content

InactiveUS20030014442A1Simplify the management processEasy to customizeDigital computer detailsSoftware designWeb siteWeb application

A system and method for developing an application for serving a document to a client in a client / server network employs an Object Model which defines templates, extensions, documents, and content objects in a template inheritance model. The Object Model serves a document, such as a webpage of a Web site application, by combining the structure and content inherited from a template and extensions in the template hierarchy. The templates specify the structure of the document and include tags as placeholders for content objects to be incorporated in the document. Extensions descend from either a template or another extension, and can expand upon the number of tags specified in a parent, add additional formatting to the layout, and / or refine the definition of tags that already exist in the inheritance hierarchy. When a document is to be viewed or served, a page server retrieves the template hierarchy and incorporates all tagged content in the structure inherited from the template and its extensions. The Object Model provides a framework for developing Web sites and other applications that is more robust and simpler to manage than the traditional file directory model of conventional Web applications. This framework makes it possible to create complex and highly structured Web applications that are efficient to develop and easier to maintain, and without ever having to write source code.

Owner:DH LABS

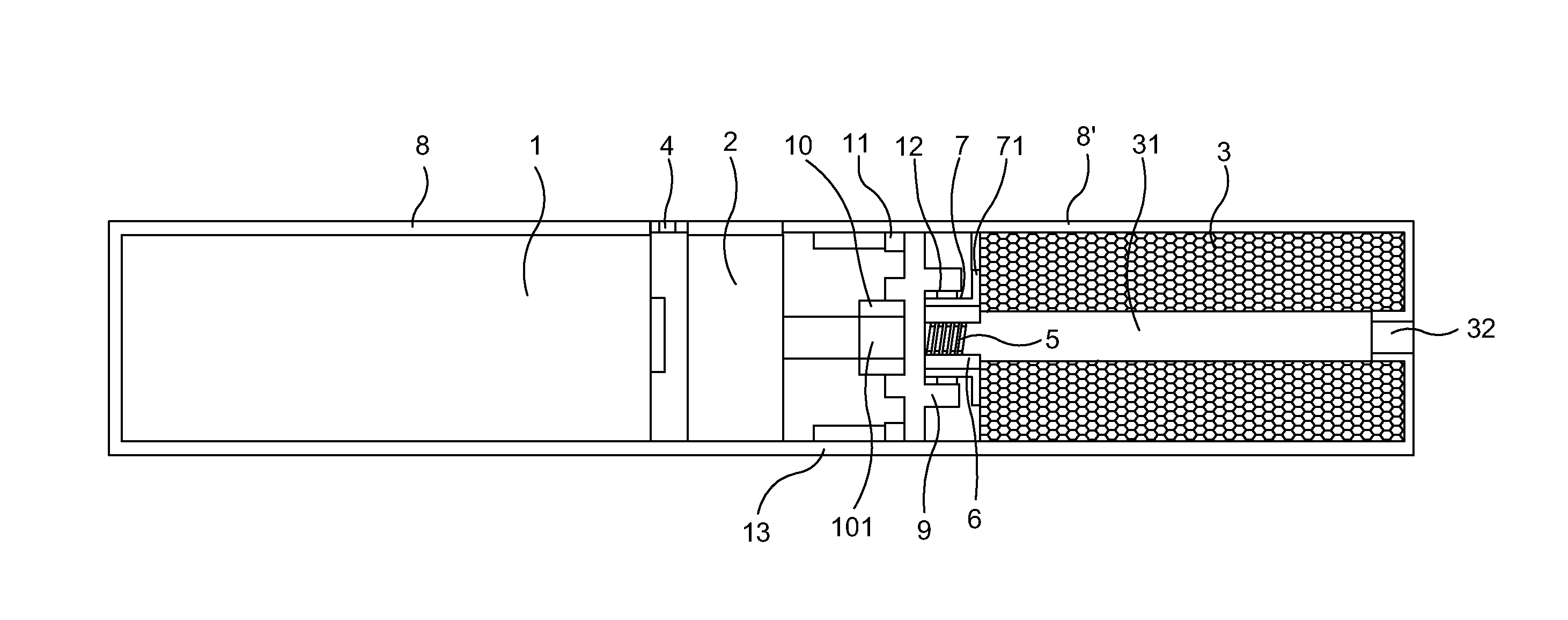

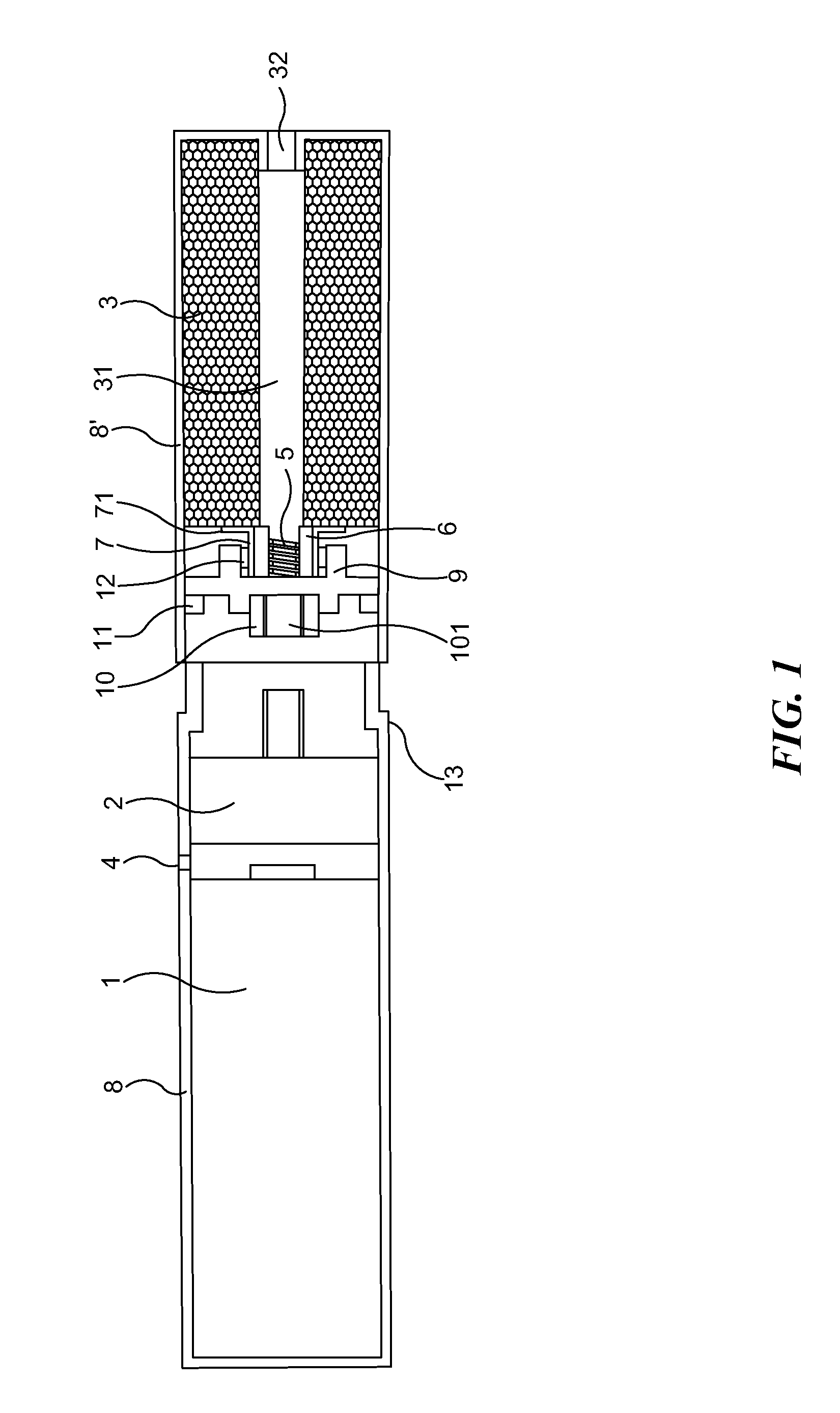

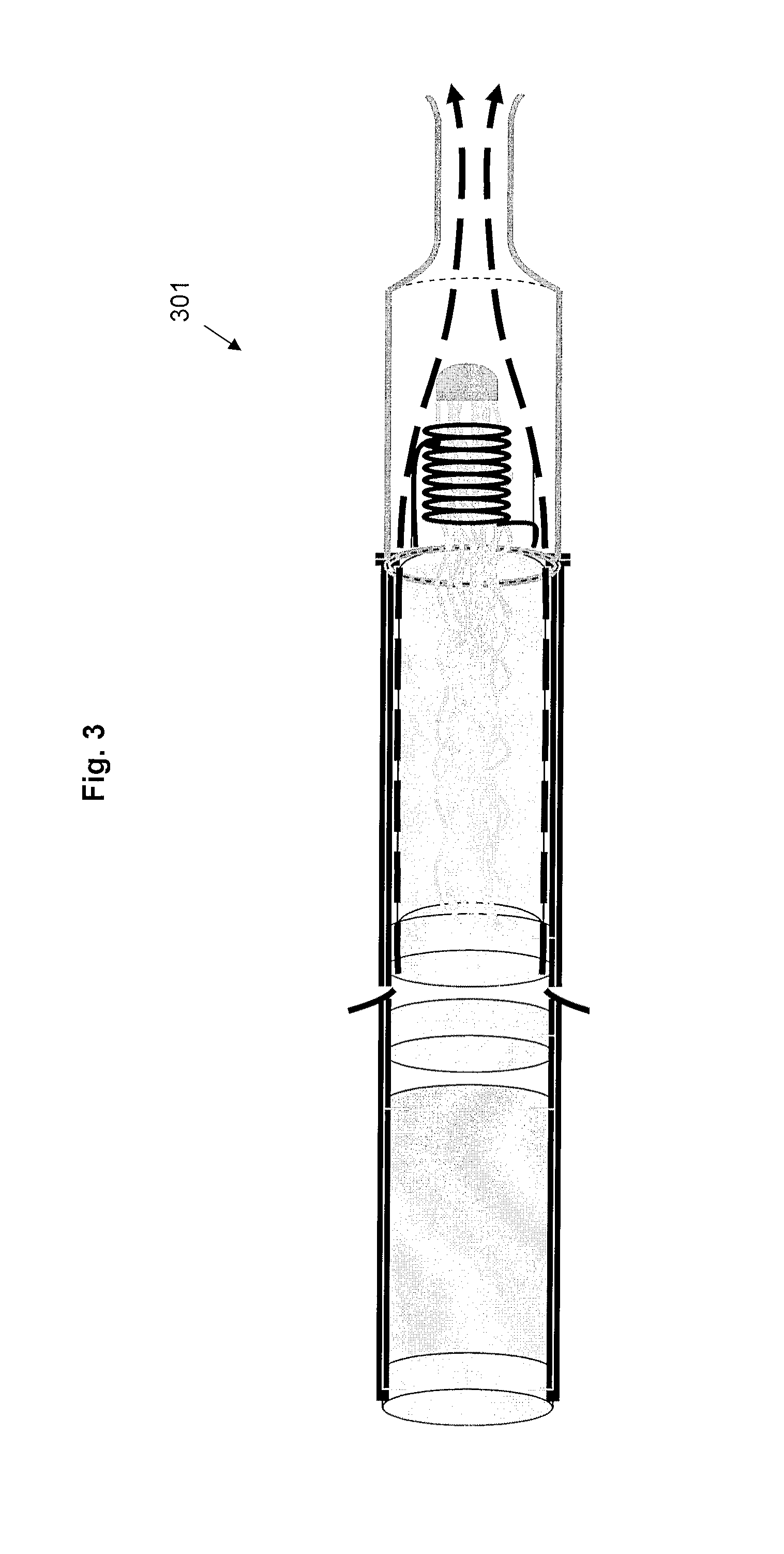

Electronic cigarette

ActiveUS20120279512A1Promote atomizationEfficient productionRespiratorsHeater elementsEngineeringElectronic cigarette

Owner:FONTEM VENTURES

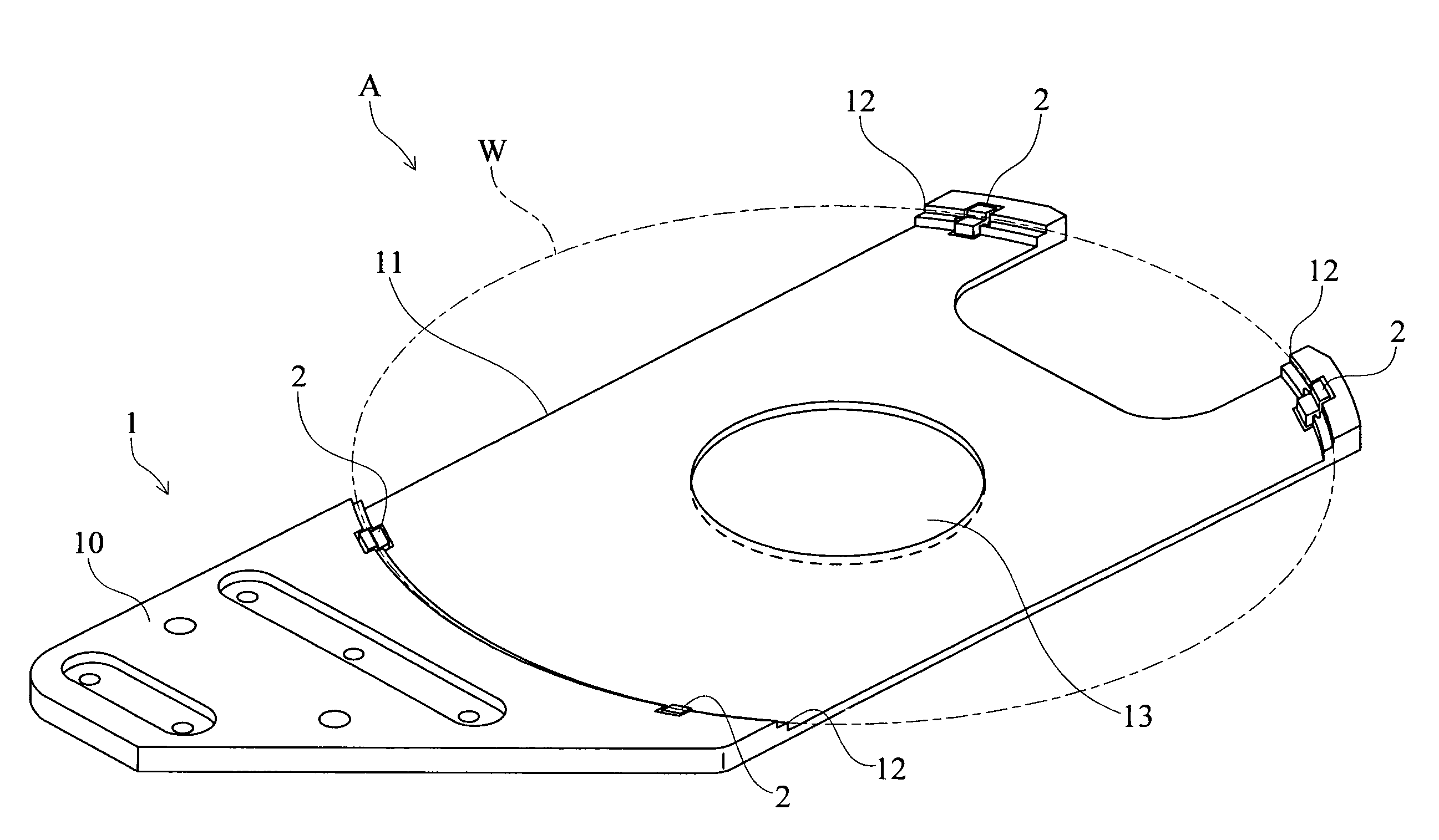

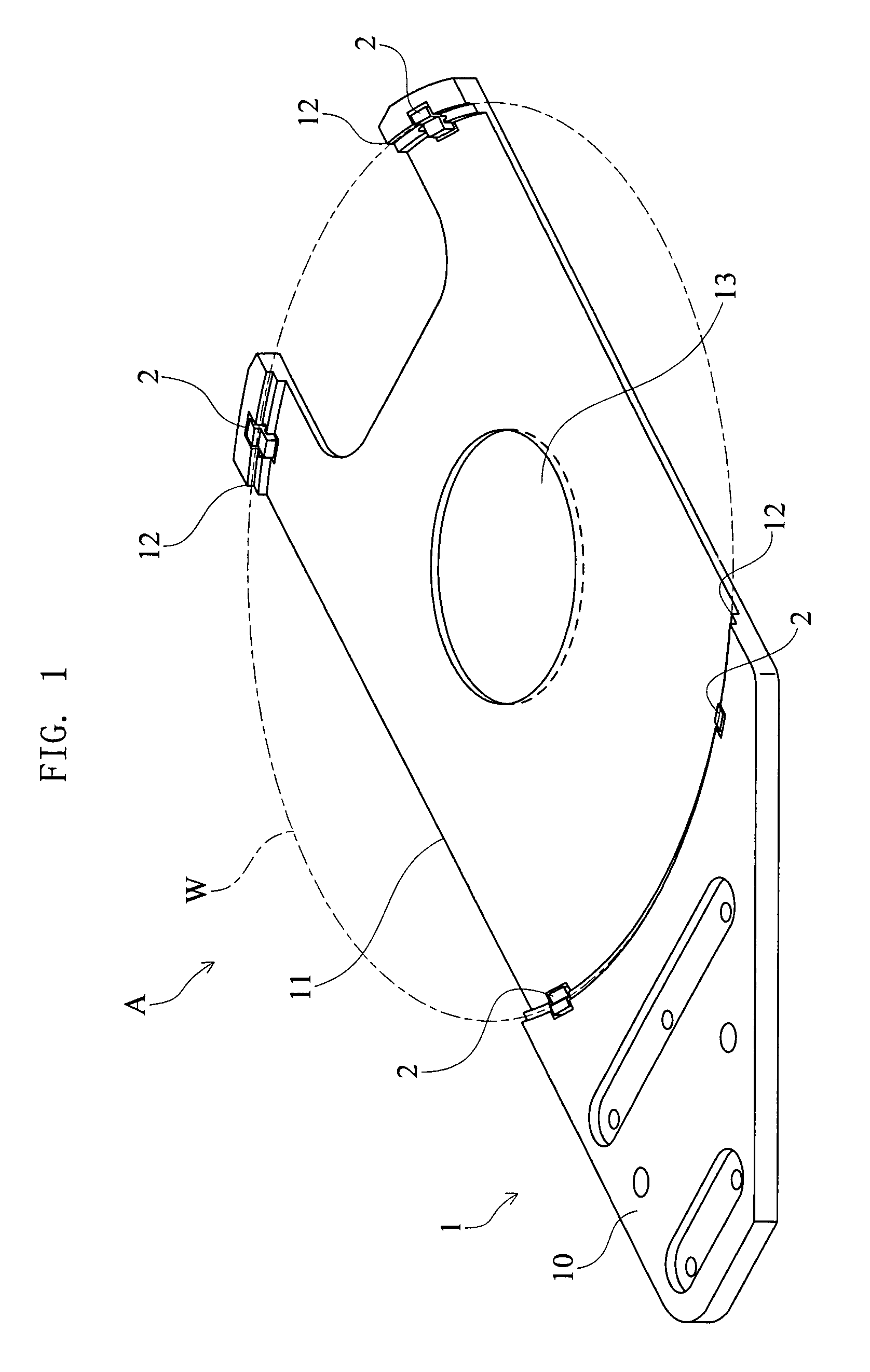

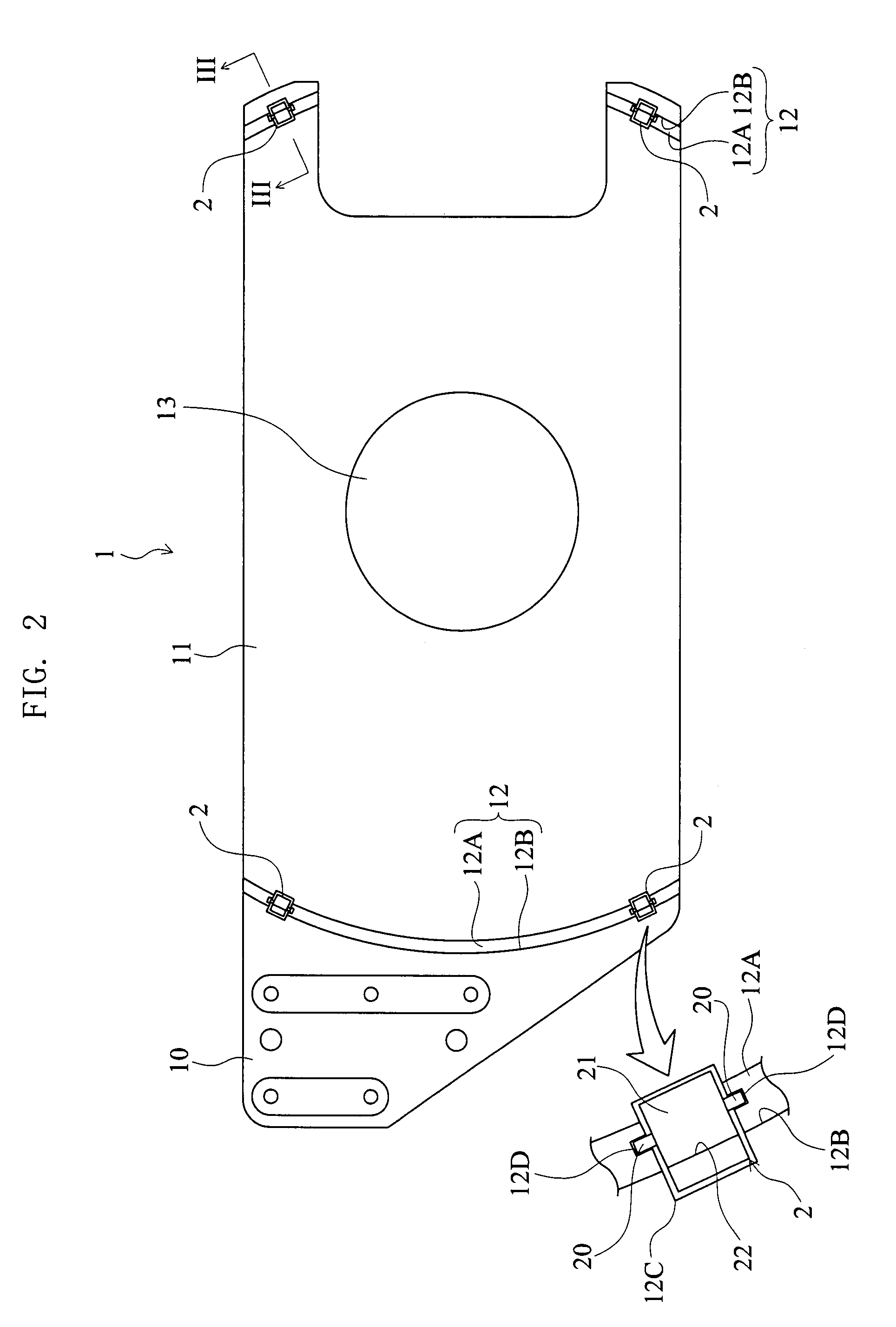

Work holding mechanism

ActiveUS7748760B2Improve shipping speedVacuum operationGripping headsSemiconductor/solid-state device manufacturingEngineeringMechanical engineering

Owner:DAIHEN CORP

Electrically heated smoking system having a liquid storage portion

ActiveUS8794231B2Avoid wastingReduce riskOhmic-resistance heating circuitsCigar manufactureElectricityElectrical connection

An electrically heated smoking system includes a shell and a replaceable mouthpiece. The shell includes an electric power supply and electric circuitry. The mouthpiece includes a liquid storage portion and a capillary wick having a first end and a second end. The first end of the wick extends into the liquid storage portion for contact with liquid therein. The mouthpiece also includes a heating element for heating the second end of the capillary wick, an air outlet, and an aerosol forming chamber between the second end of the capillary wick and the air outlet. When the shell and mouthpiece are engaged or connected, the heating element is in electrical connection with the power supply via the circuitry, and a flowpath for air is defined from at least one air inlet to the air outlet via the aerosol forming chamber. In use, liquid is transferred from the liquid storage portion towards the heating element by capillary action in the wick. Liquid at the second end of the capillary wick is vaporized by the heating element. The supersaturated vapor created, is mixed and carried in the air flow from the at least one air inlet to the aerosol forming chamber. In the aerosol forming chamber, the vapor condenses to form an aerosol, which is carried towards the air outlet.

Owner:PHILIP MORRIS USA INC

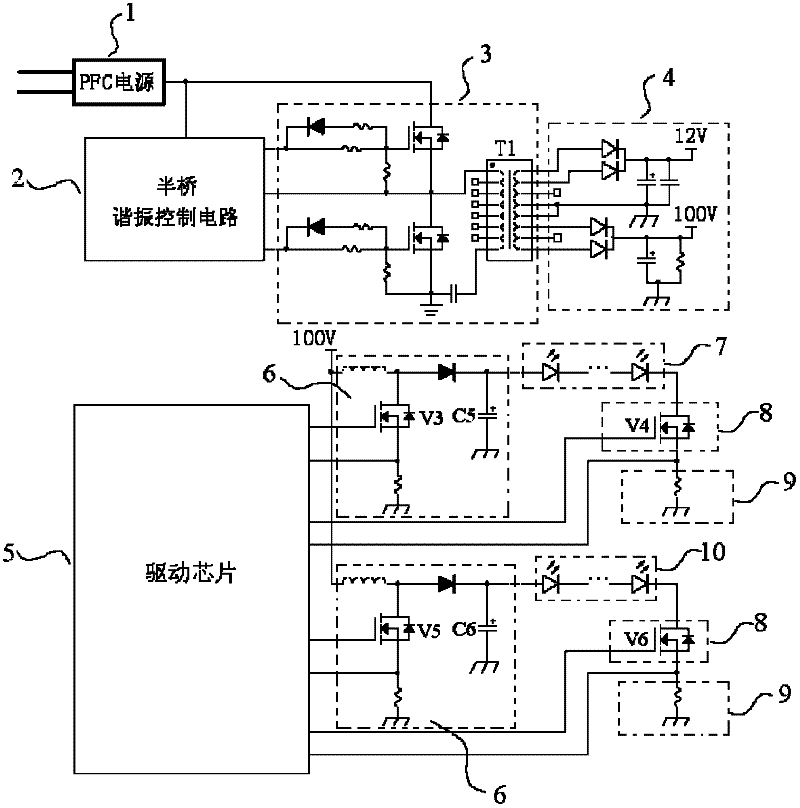

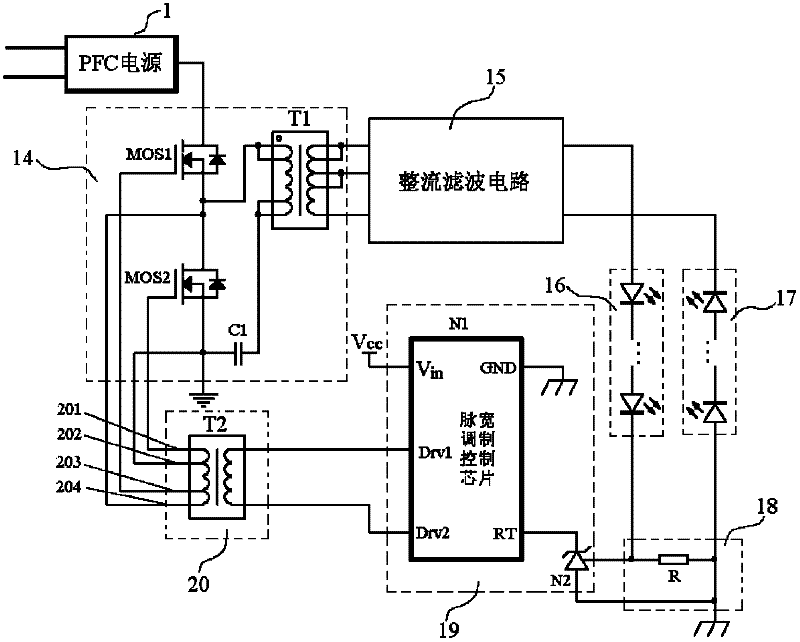

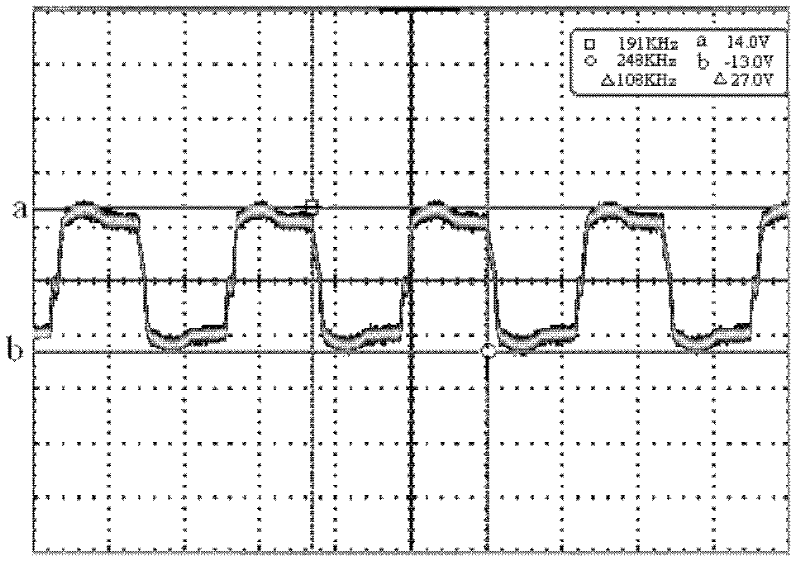

Backlight source driving circuit and driving circuit thereof as well as liquid crystal television

ActiveCN102243850ASimple and easy circuit implementationSimple circuit structureTelevision system detailsStatic indicating devicesMultiple componentLiquid crystal

The invention discloses a backlight source driving circuit and a driving circuit thereof as well as a liquid crystal television which are provided mainly aiming at the problems of multiple components, complicated structure and the like of the existing backlight source driving circuit. The backlight source driving circuit disclosed by the invention comprises a backlight source power supply circuitand a control circuit, wherein the backlight source power supply circuit supplies the voltage which is needed by the operation to a backlight source load according to the received driving pulse signals which are output by the control circuit; and the control circuit responses to control voltage signals, samples the operating current of the backlight source load in real time, and generates and outputs the corresponding driving pulse signals according to the sampled current signals. The backlight source driving circuit disclosed by the invention has the advantages of simple structure and stabledriving.

Owner:HISENSE VISUAL TECH CO LTD

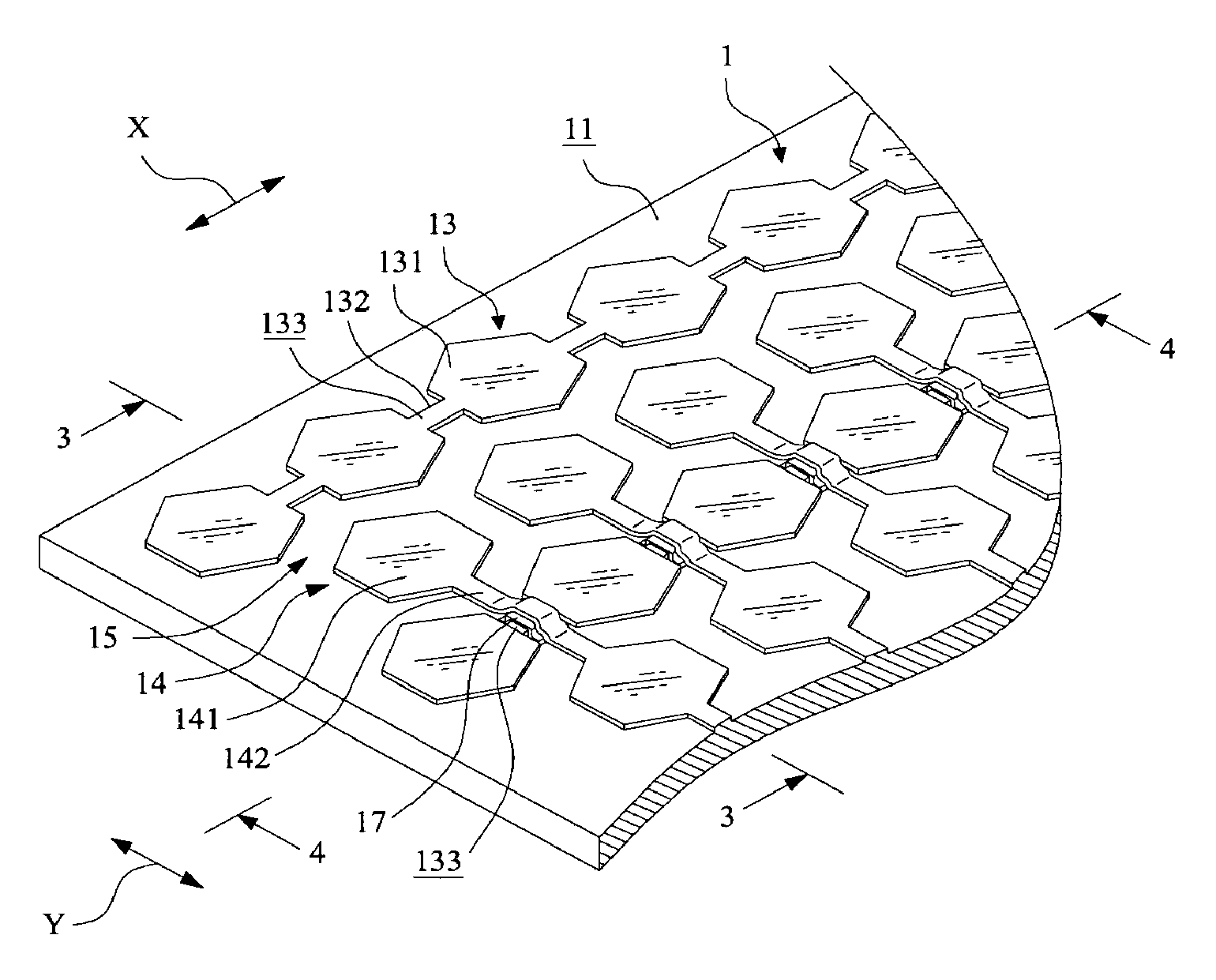

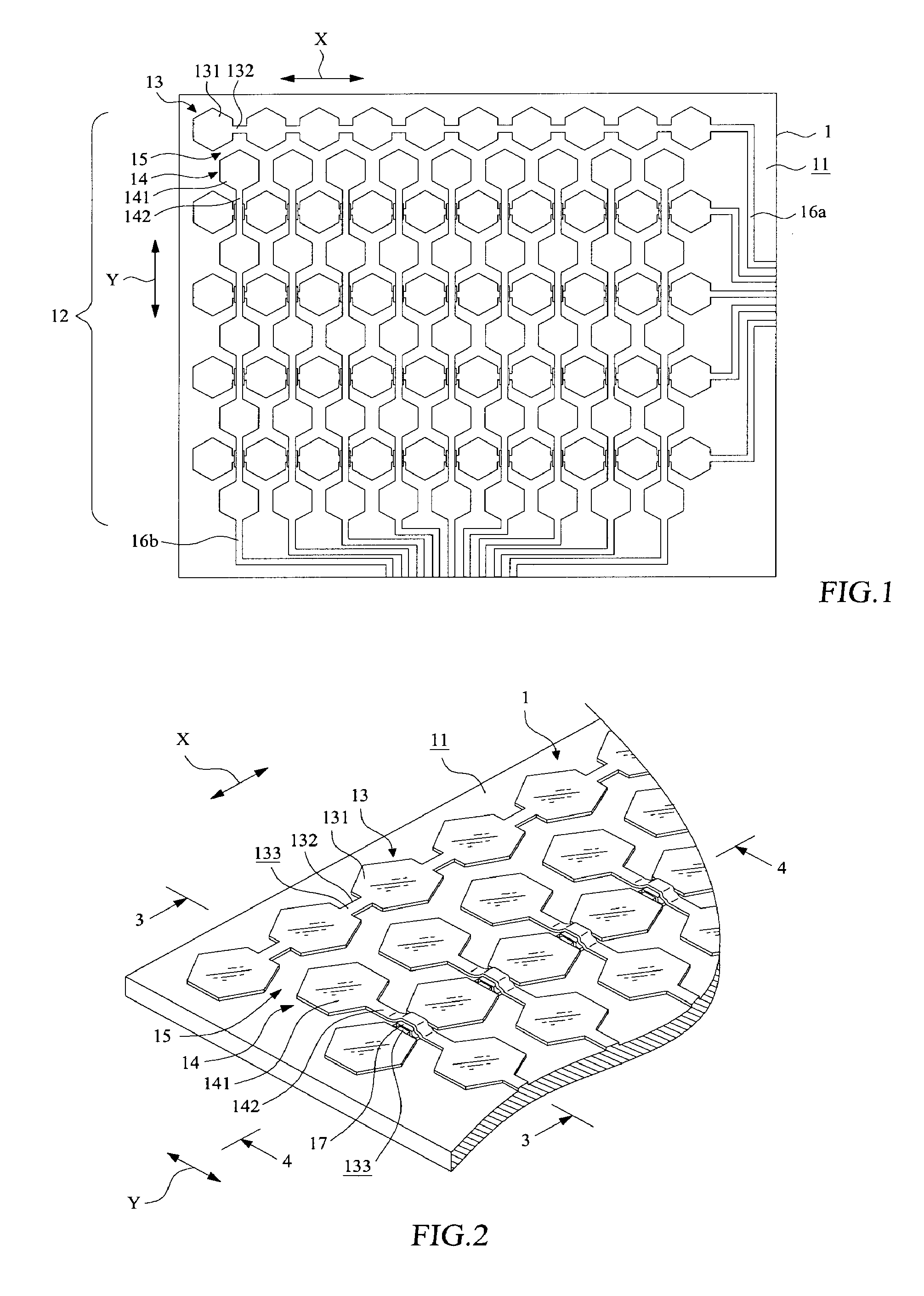

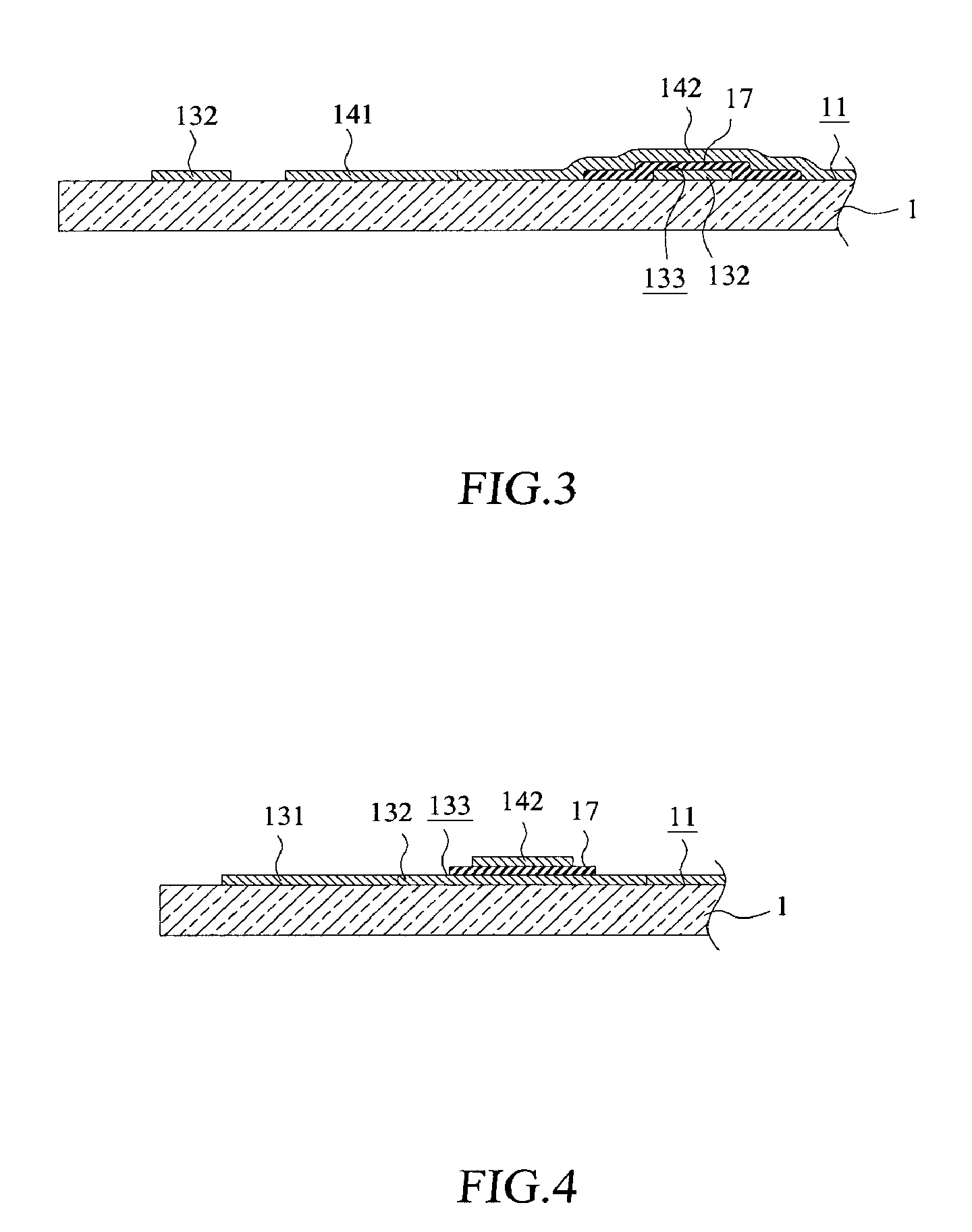

Conductor pattern structure of capacitive touch panel

ActiveUS20080264699A1Simple structureReduce the thickness of the structureTransmission systemsResistance/reactance/impedenceElectrical conductorEngineering

Disclosed is a conductor pattern structure of a capacitive touch panel. First-axis conductor assemblies and second-axis conductor assemblies are formed on a surface of a substrate. Each first-axis conductor assembly includes a plurality of first-axis conductor cells that are interconnected by first-axis conduction lines. An insulation layer is formed on a surface of each first-axis conduction line. Each second-axis conductor assembly includes a plurality of second-axis conductor cells that are interconnected by second-axis conduction lines. Each second-axis conduction line extends across the insulation layer of the associated first-axis conduction line.

Owner:TRENDON TOUCH TECHNOLOGY CORPORATION

UV-Curing Apparatus Provided With Wavelength-Tuned Excimer Lamp and Method of Processing Semiconductor Substrate Using Same

InactiveUS20140099798A1Prevents unnecessary riseLow costMaterial analysis by optical meansSemiconductor/solid-state device manufacturingFluorescenceUltraviolet

A UV irradiation apparatus for processing a semiconductor substrate includes: a UV lamp unit having at least one dielectric barrier discharge excimer lamp which is constituted by a luminous tube containing a rare gas wherein an inner surface of the luminous tube is coated with a fluorescent substance having a peak emission spectrum in a wavelength range of 190 nm to 350 nm; and a reaction chamber disposed under the UV lamp unit and connected thereto via a transmission window.

Owner:ASM IP HLDG BV

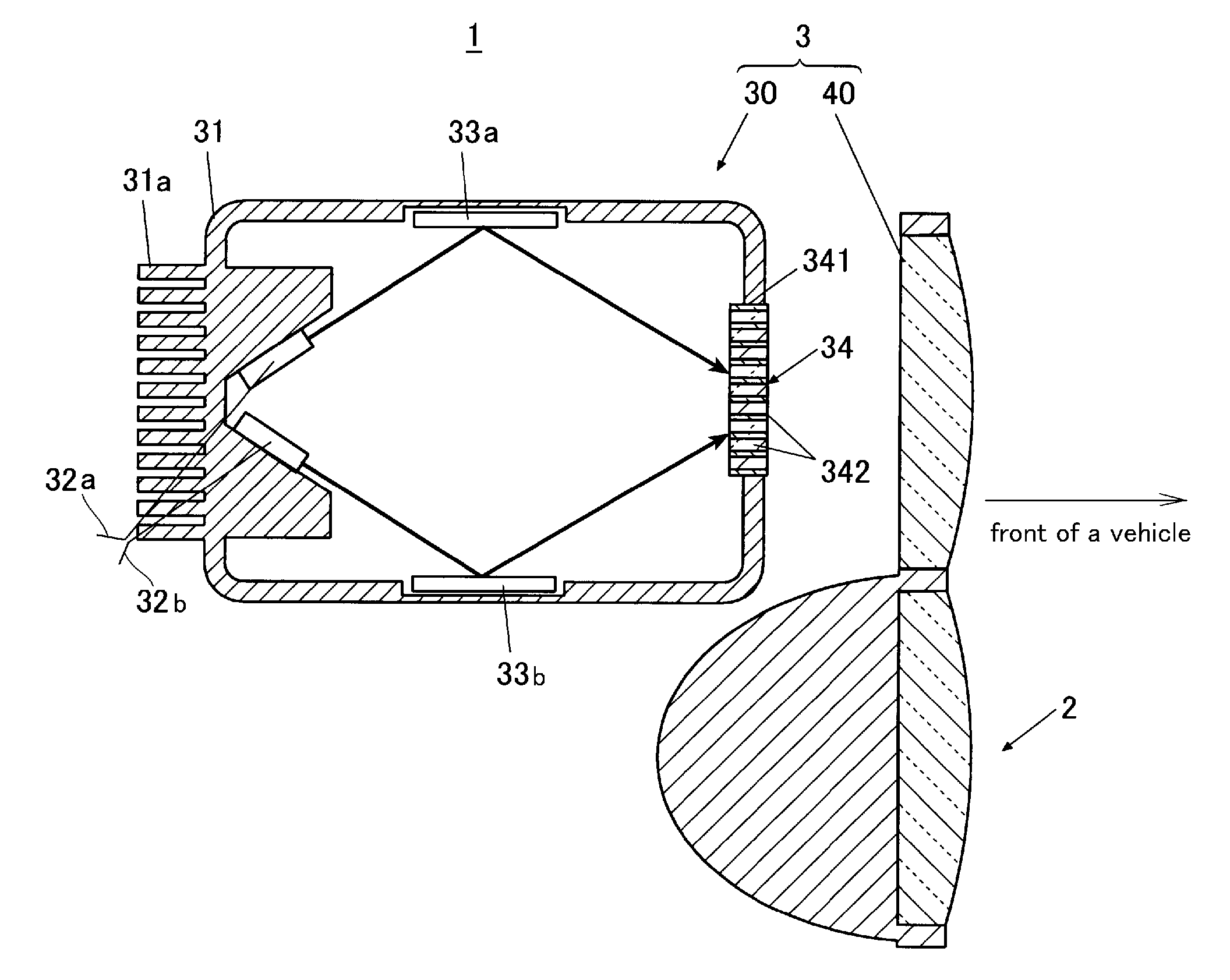

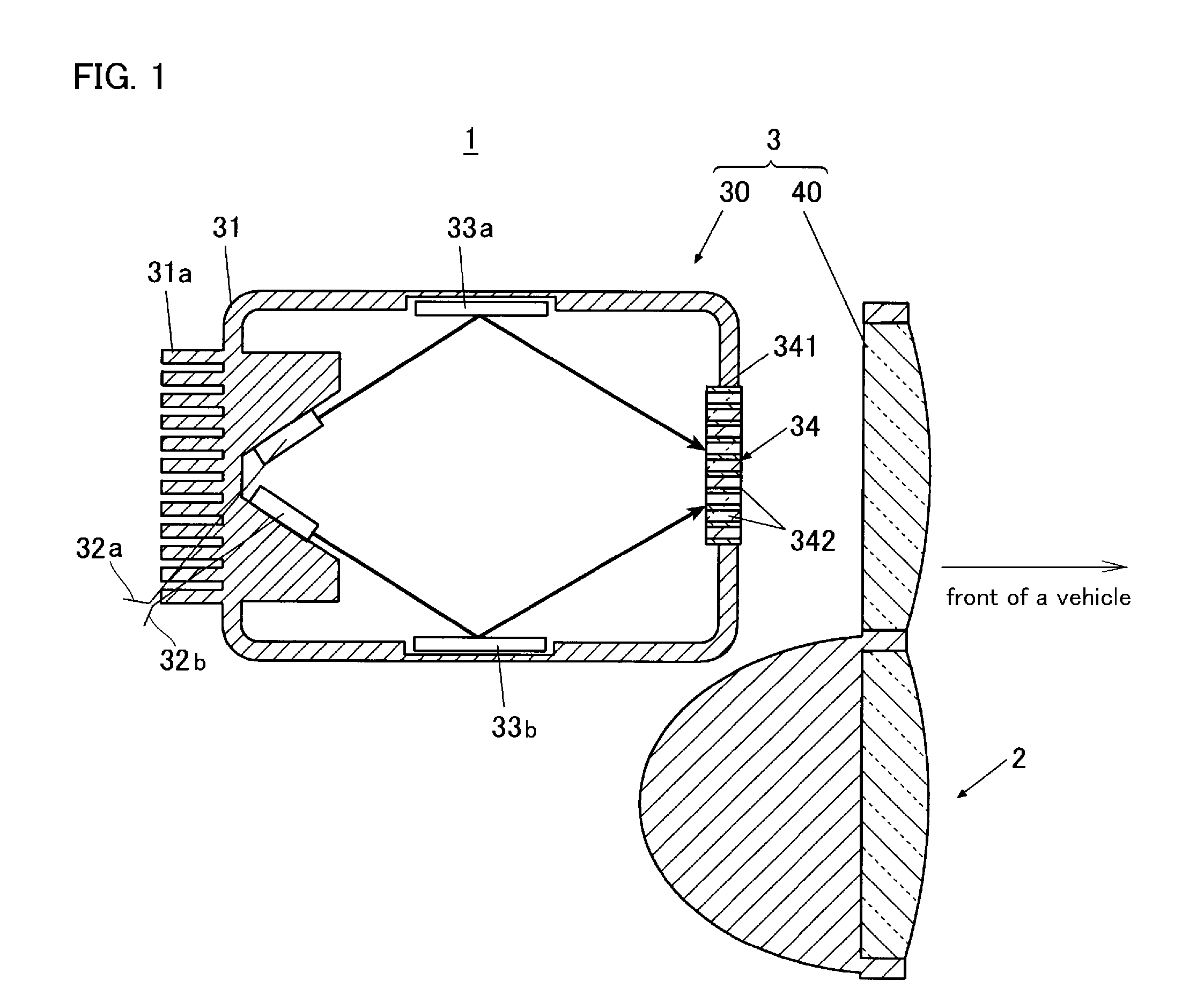

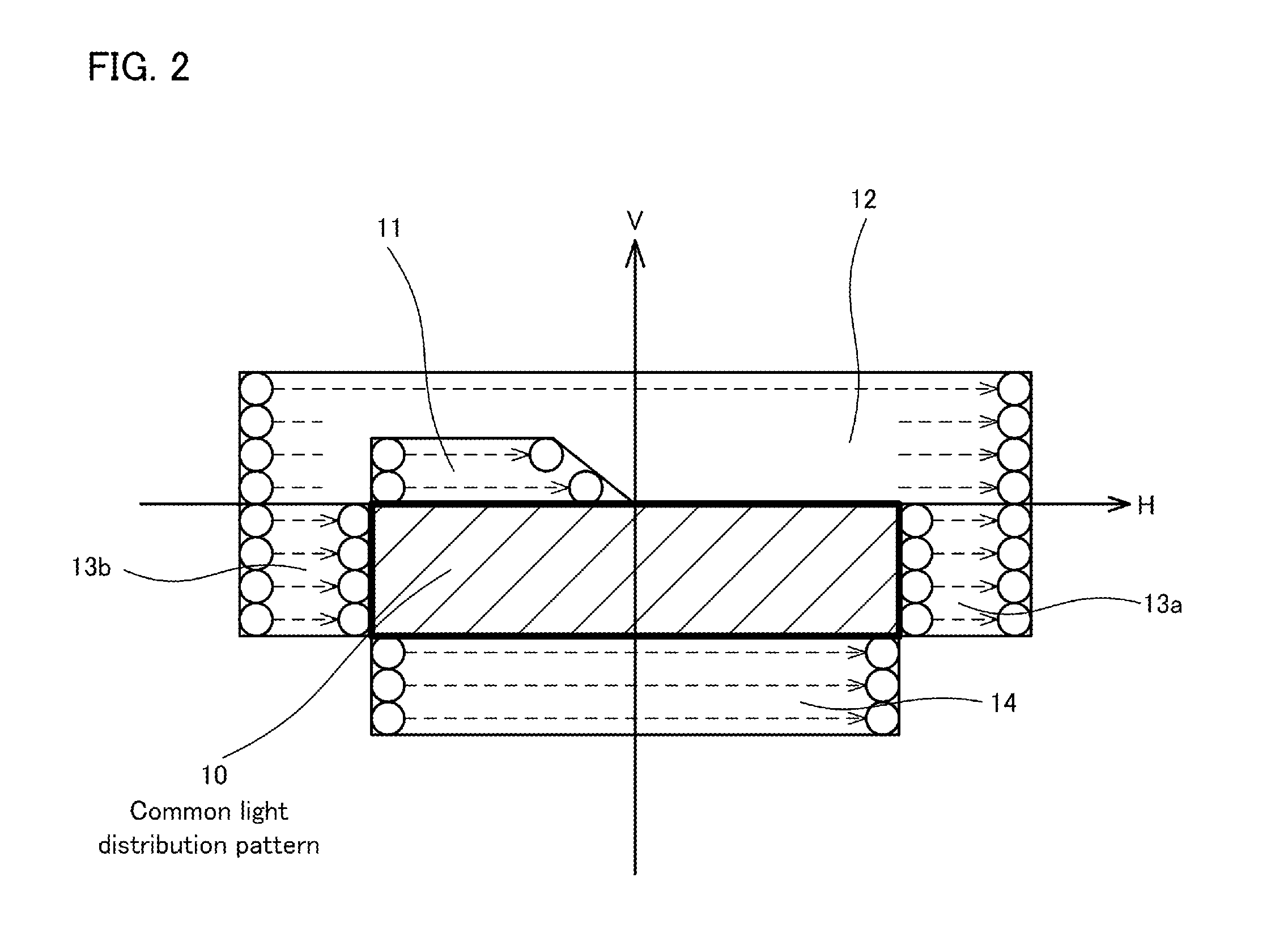

Vehicle headlight

ActiveUS20110249460A1Good light distributionIncrease awarenessNon-electric lightingVehicle headlampsPhosphorSubject matter

A vehicle headlight including a common light distribution unit and a variable light distribution unit and a headlight system including the headlight can form a common light distribution pattern and a variable light distribution pattern using the common and the variable light distribution units. The variable distribution unit can include a light source, a phosphor panel, a mirror reflecting / scanning light emitted from the light source onto the phosphor panel and a projector lens projecting the scanning light adjacent the common light distribution pattern. The headlight system can include a front sensor detecting a surrounding condition, and can control the common and the variable light distribution units to form an optimum light distribution pattern in accordance with surrounding conditions. Thus, the disclosed subject matter can provide a headlight system including a headlight that can form an optimum light distribution pattern in accordance with surrounding conditions and can have a simple structure.

Owner:STANLEY ELECTRIC CO LTD

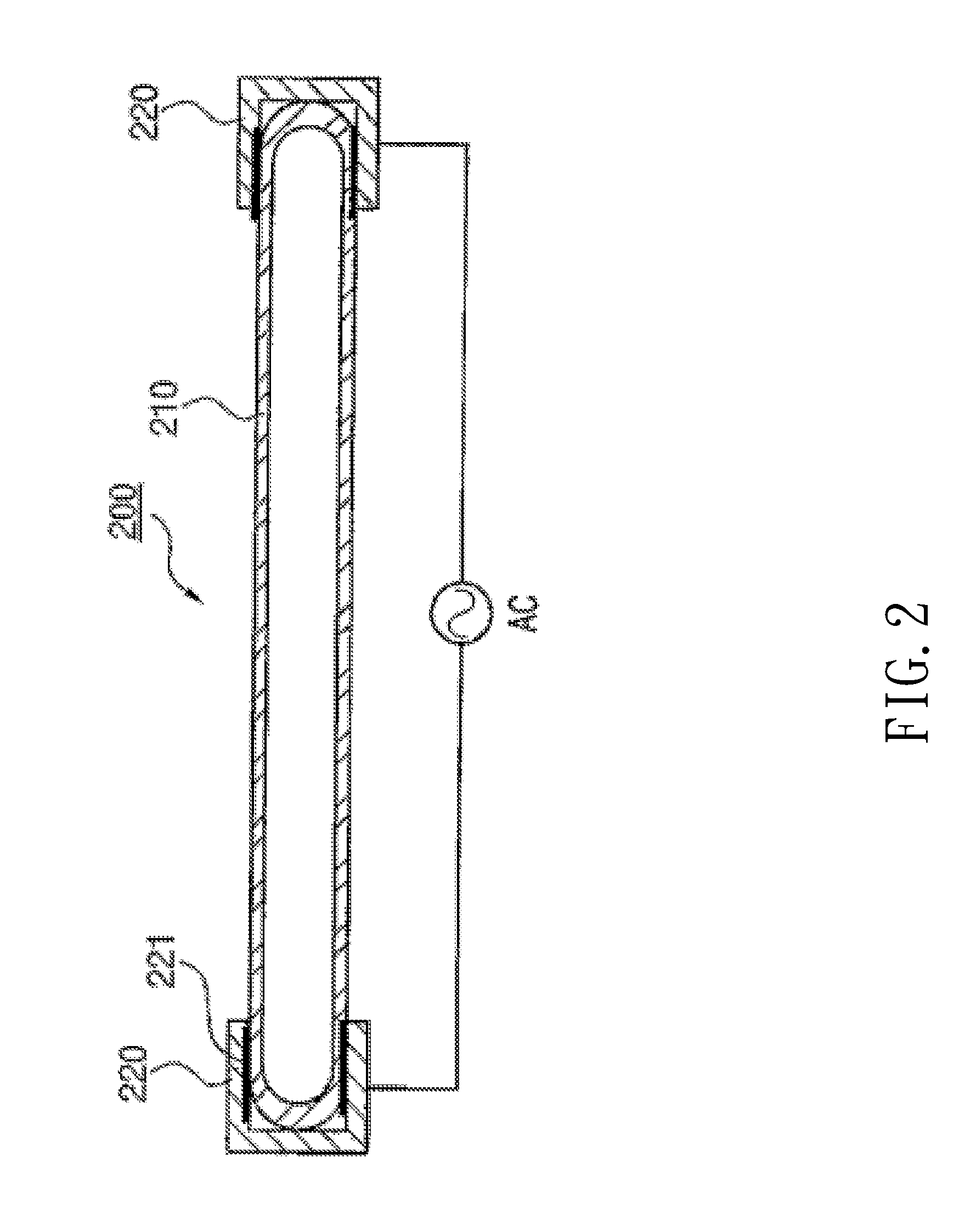

Ceramic-glass composite electrode and fluorescent lamp having the same

InactiveUS20120212121A1Low costSimple structureDischarge tube luminescnet screensLamp detailsGlass compositesAdhesive

The present invention provides a ceramic-glass composite electrode and a fluorescent lamp having the same. The ceramic-glass composite electrode according to the present invention is a ceramic-glass composite, which is disposed at the ends of a glass tube of the fluorescent lamp. A stopper is disposed at the end of the glass tube for pushing against the ceramic-glass composite electrode and limiting the position of the ceramic-glass composite electrode slipped on the glass tube. Thereby, flowing of adhesives into the glass tube is avoided when the adhesives are used for gluing the glass tube and the ceramic-glass composite electrode, and hence extending the lifetime of the fluorescent lamp.

Owner:SANTOMA