Patents

Literature

2486 results about "Layout" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

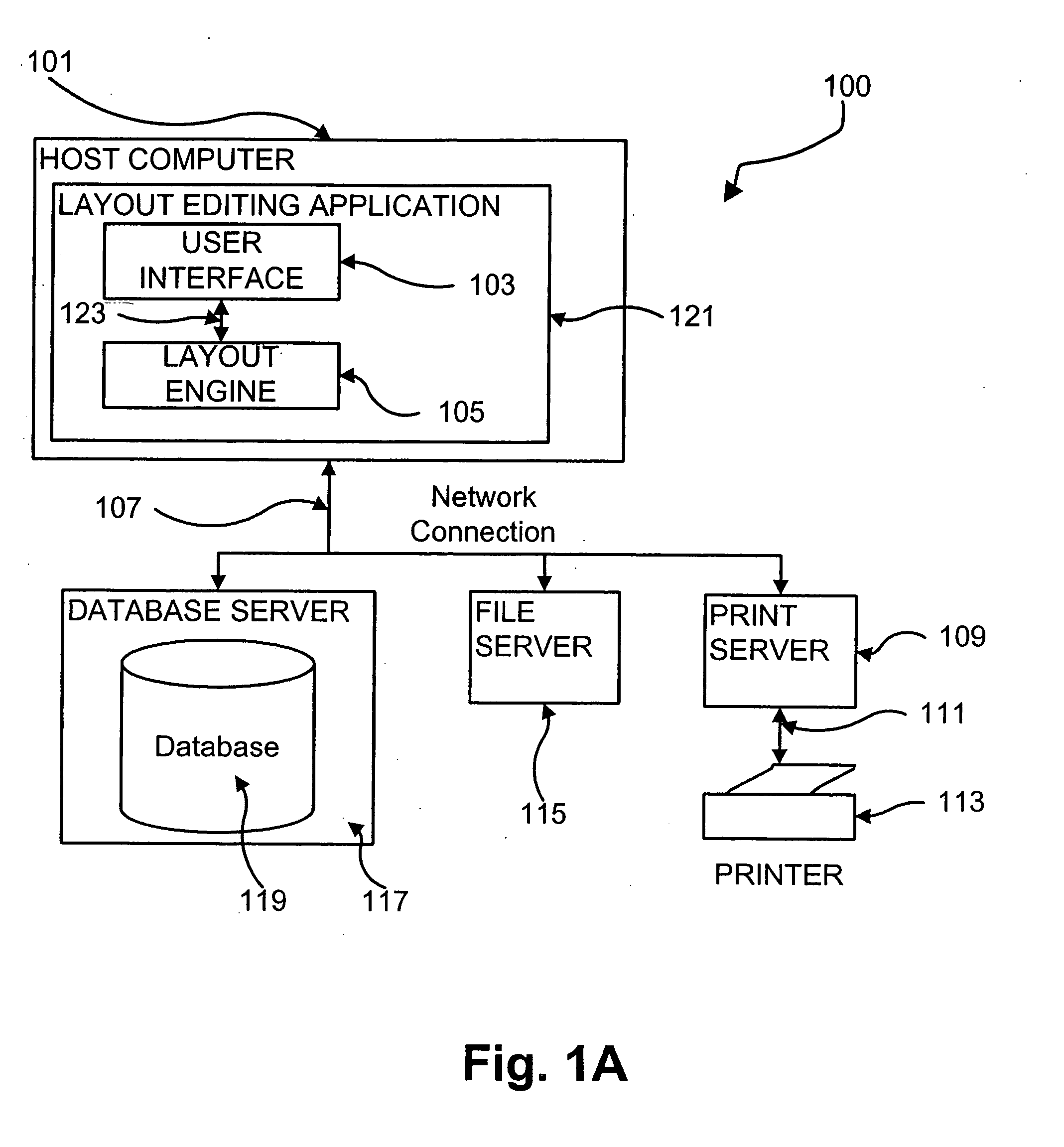

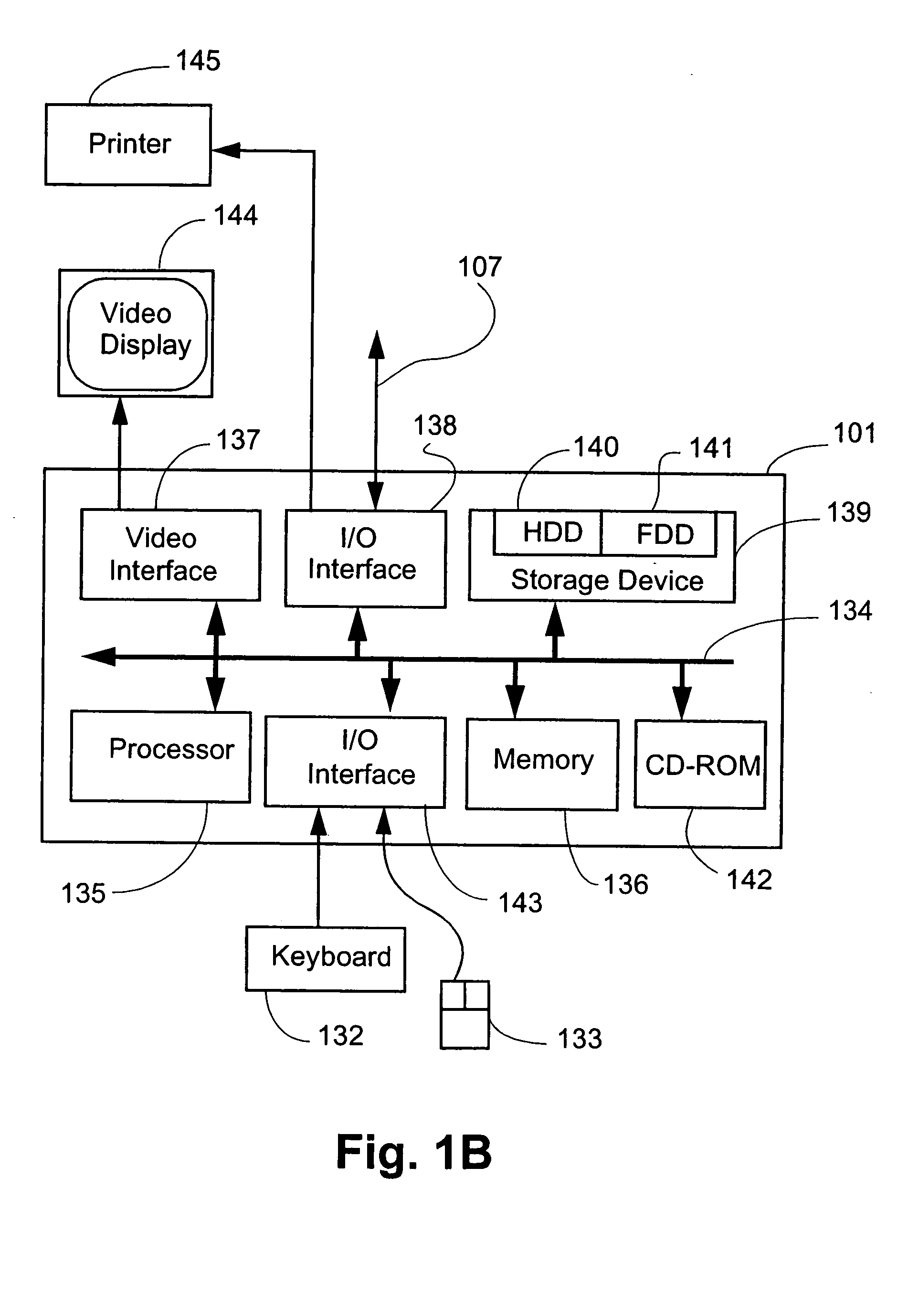

In computing, layout is the process of calculating the position of objects in space subject to various constraints. This functionality can be part of an application or packaged as a reusable component or library.

Method of optimizing customizable filler cells in an integrated circuit physical design process

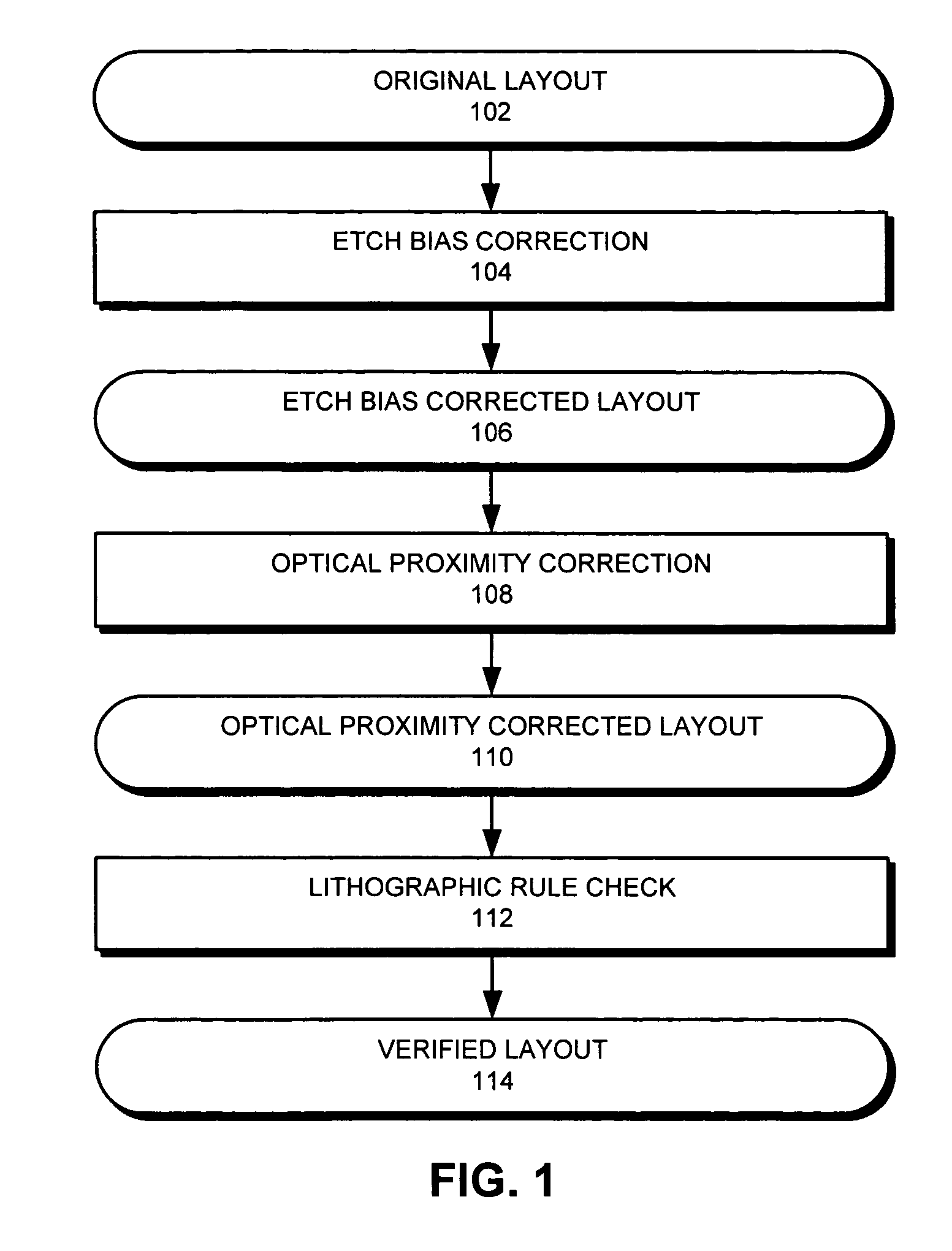

ActiveUS20080005712A1Reduce traceabilityComputer aided designSoftware simulation/interpretation/emulationIntegrated circuitEngineering

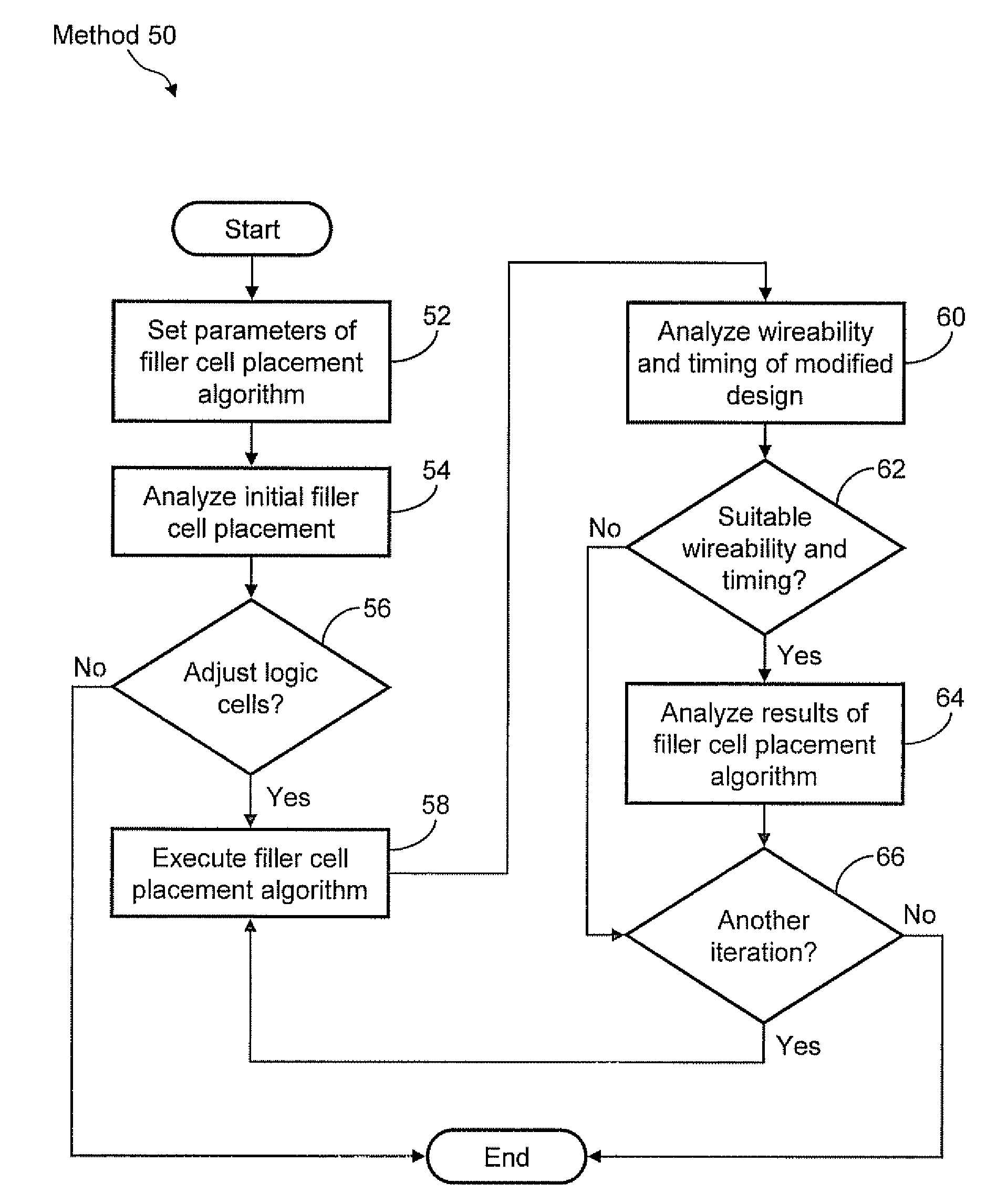

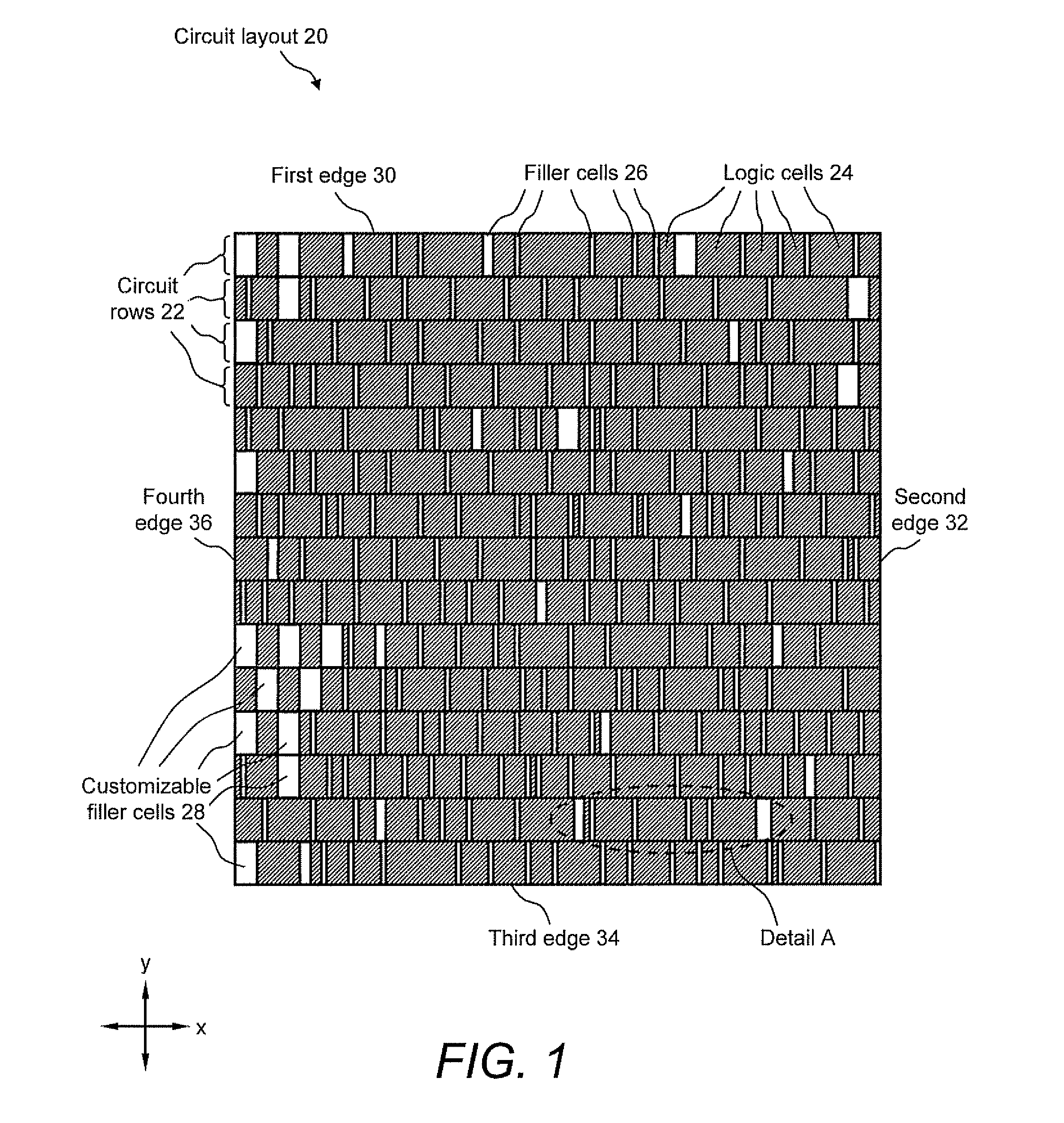

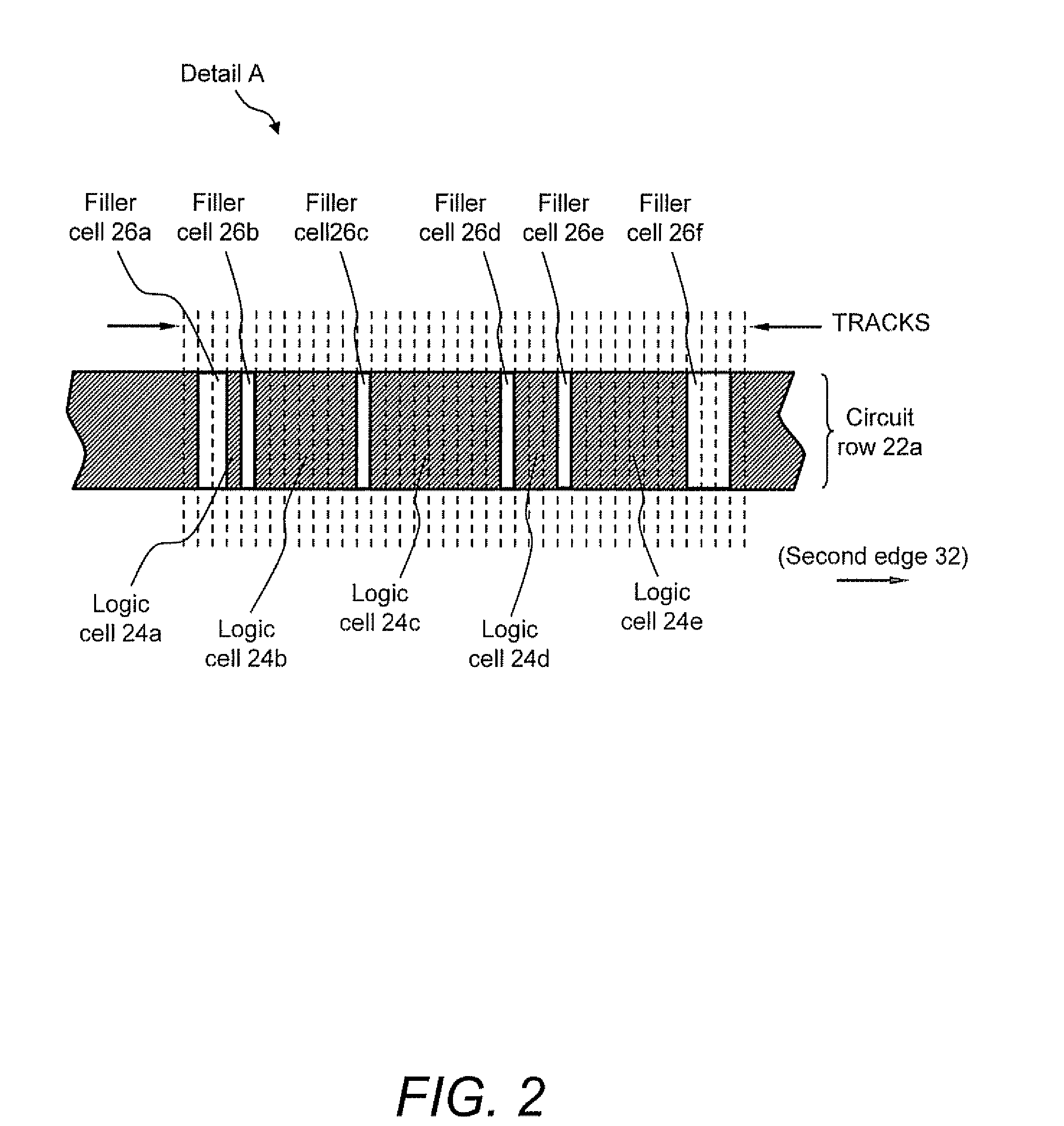

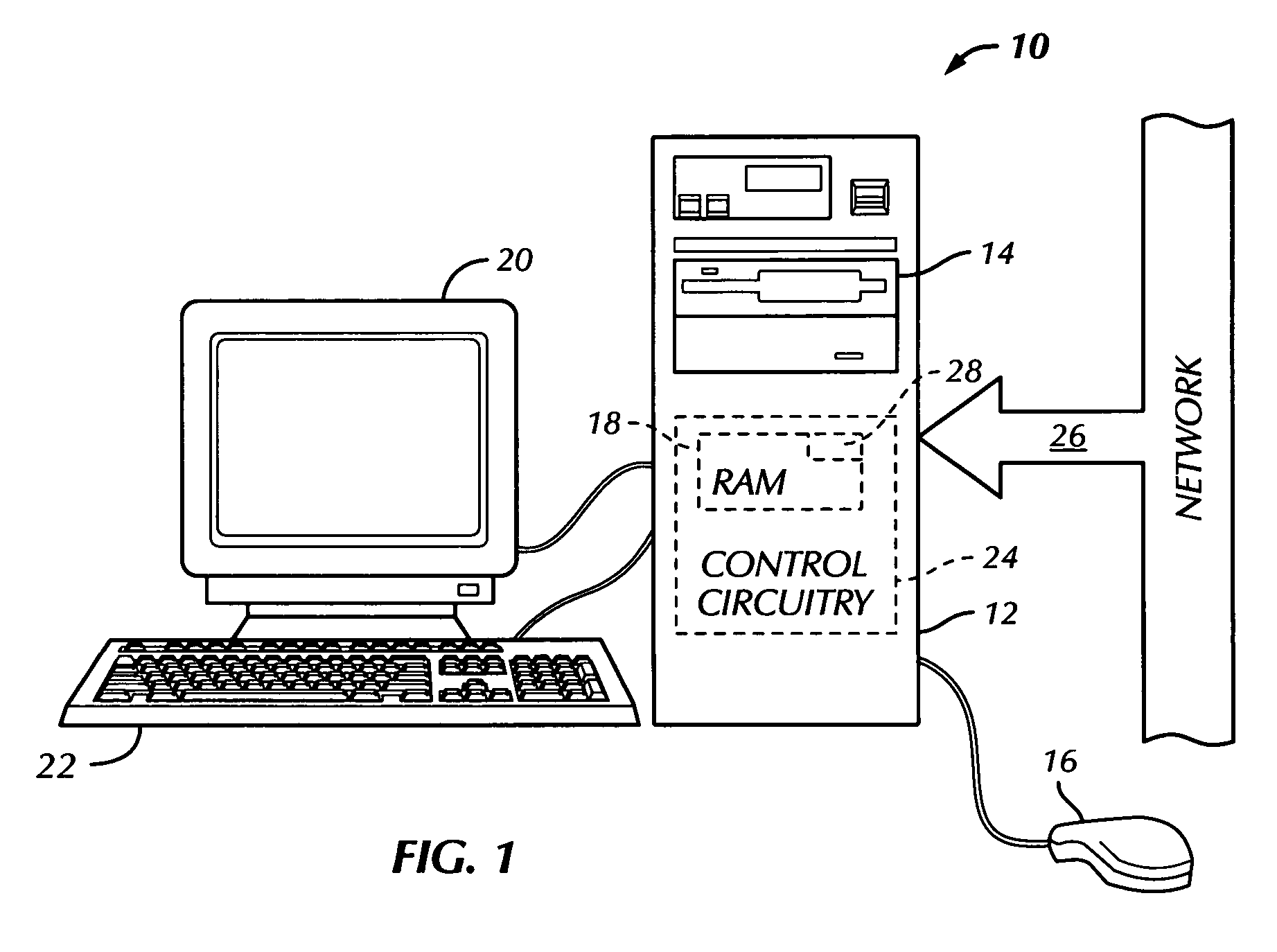

A system and method for optimizing customizable filler cells in an integrated circuit physical design process. In particular, a filler cell placement algorithm of the present disclosure is utilized in the method to optimize the customizable filler cells in a circuit layout. The filler cell placement algorithm performs the operation of selecting a starting point within a given circuit layout, selecting a direction in which the position of logic cells is adjusted, adjusting the position of logic cells and, thereby, combining filler cells in order to increase the accumulated area thereof; suspending the adjustment operation when a customizable filler cell is formed; and resuming the adjustment operation from the point of the newly formed customizable filler cell. Additionally, a method of optimizing the locations, number, and distribution of the customizable filler cells in an integrated circuit design by use of the filler cell placement algorithm is provided.

Owner:GLOBALFOUNDRIES US INC

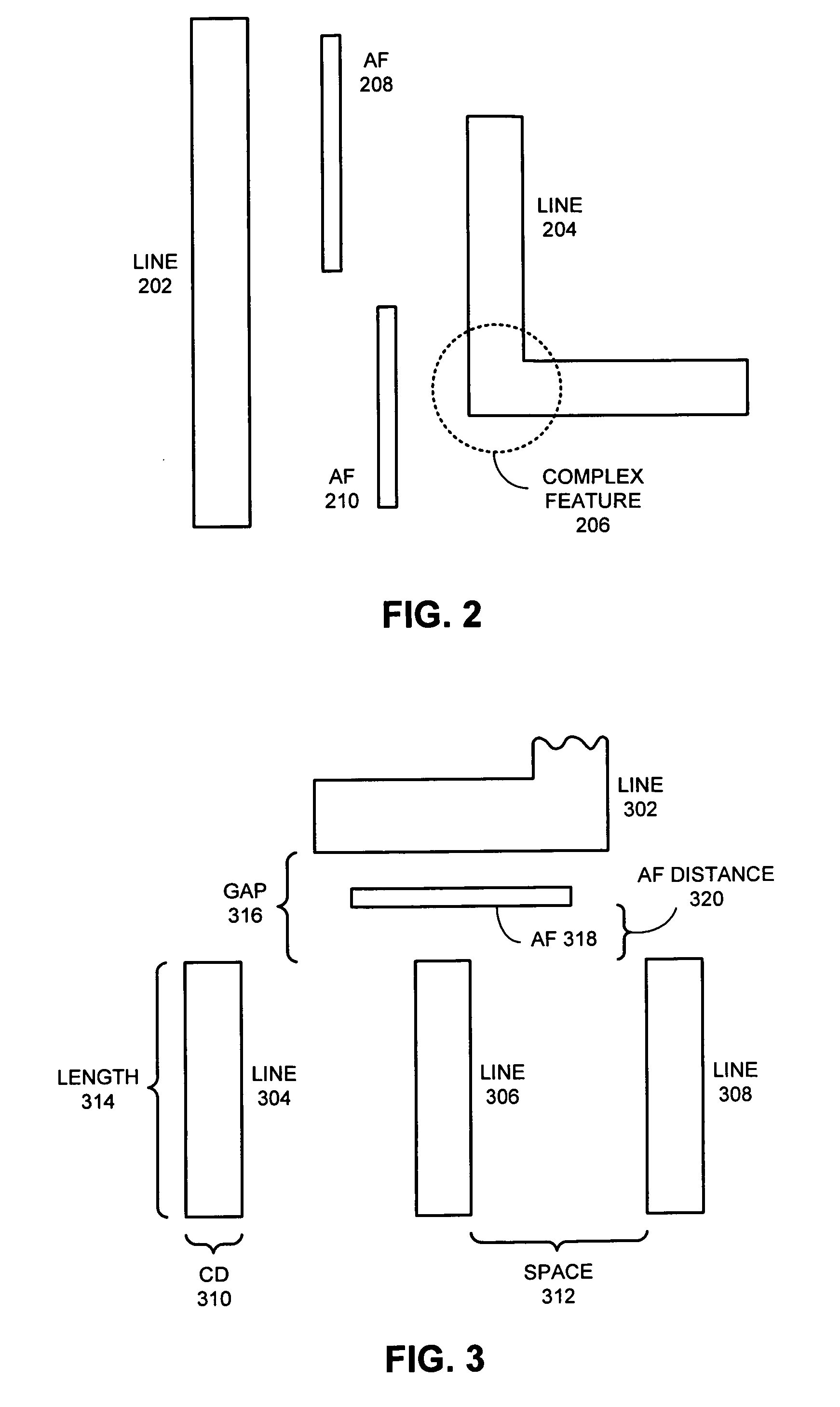

Method and apparatus for quickly determining the effect of placing an assist feature at a location in a layout

ActiveUS20070038973A1Quick effectOptimize locationPhotomechanical apparatusCAD circuit designEngineeringSystem usage

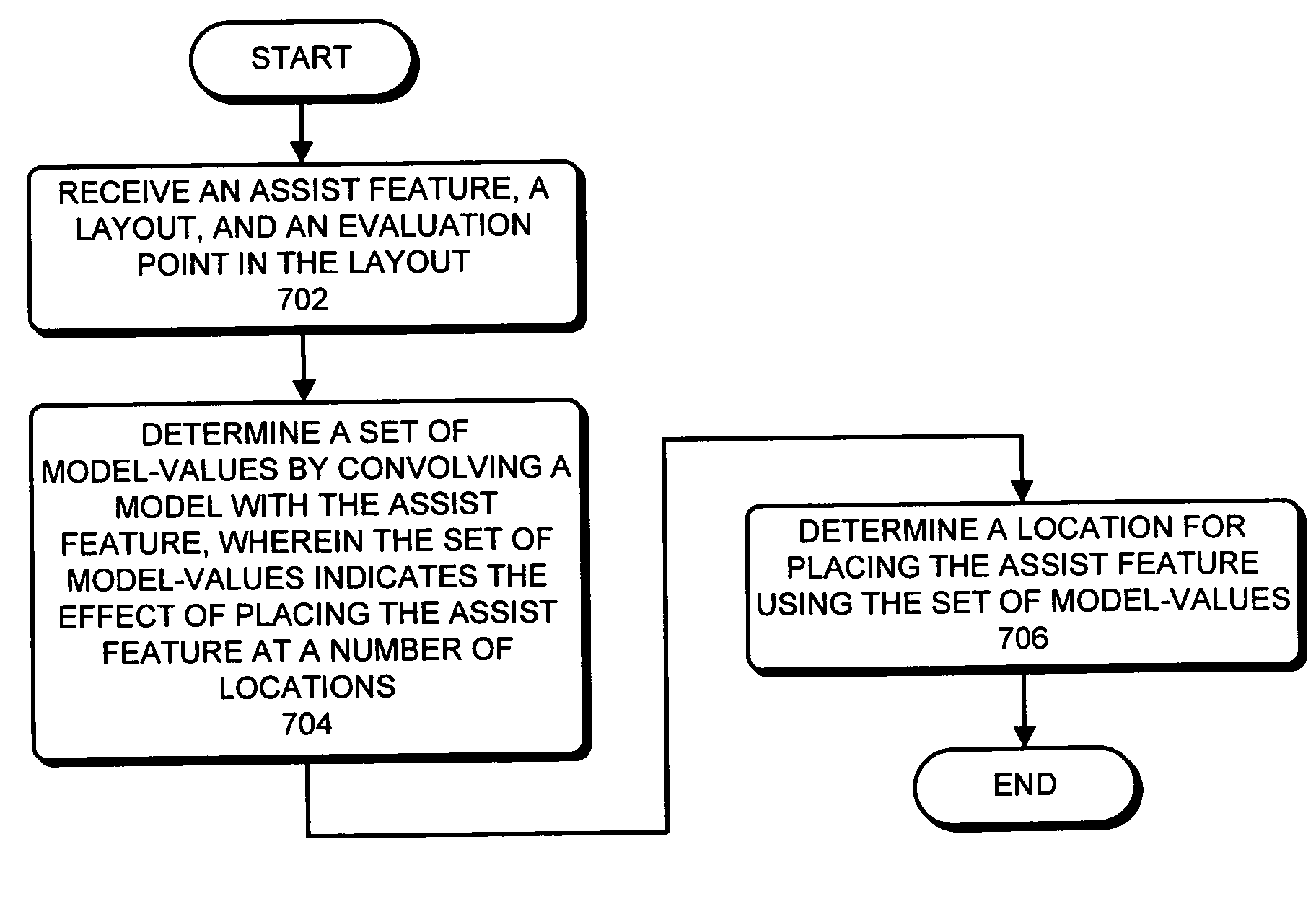

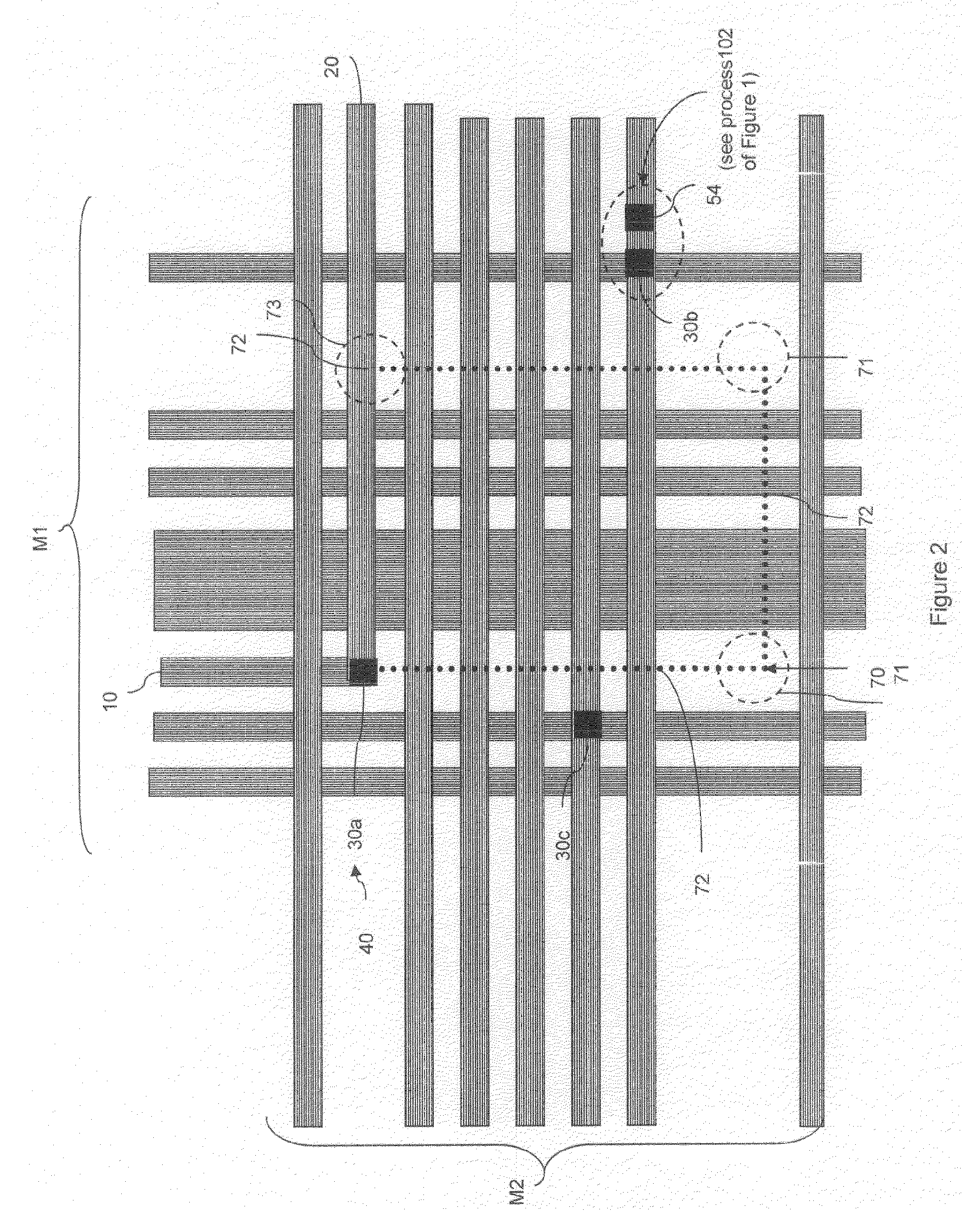

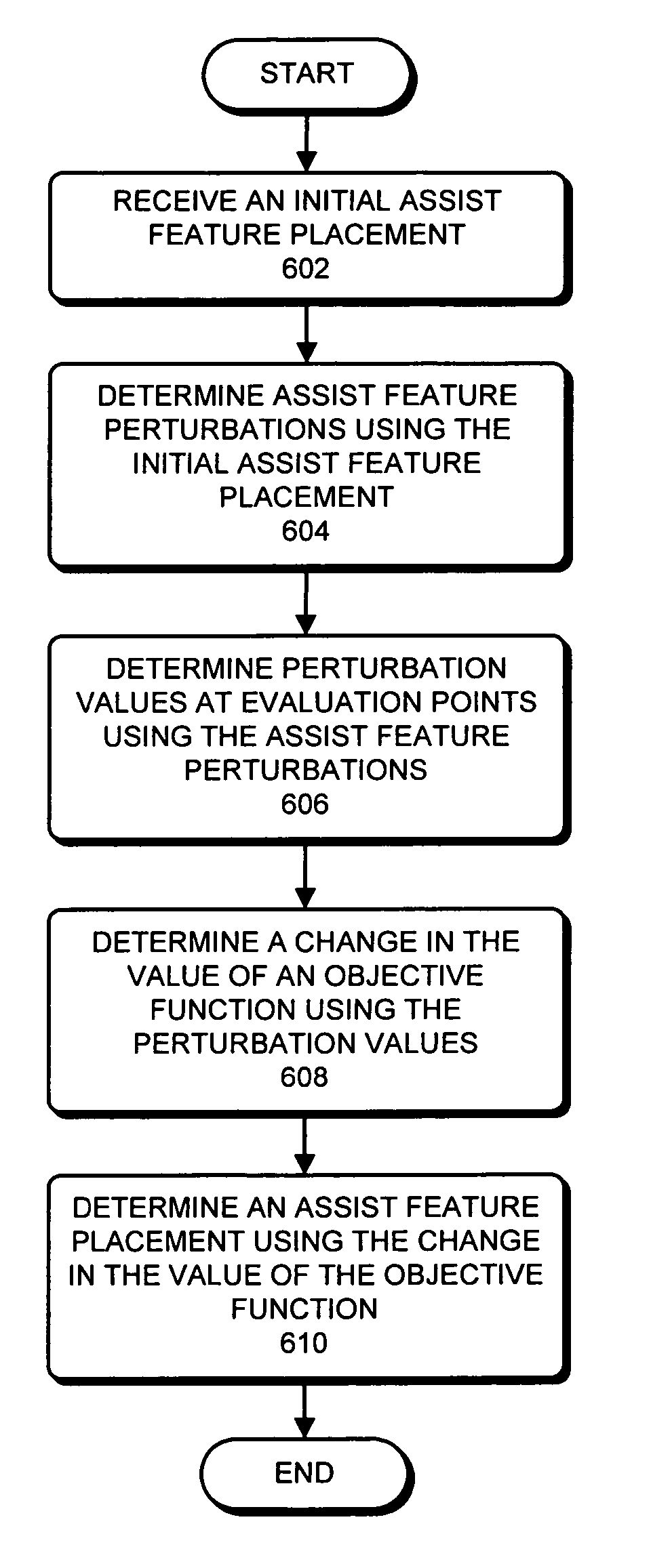

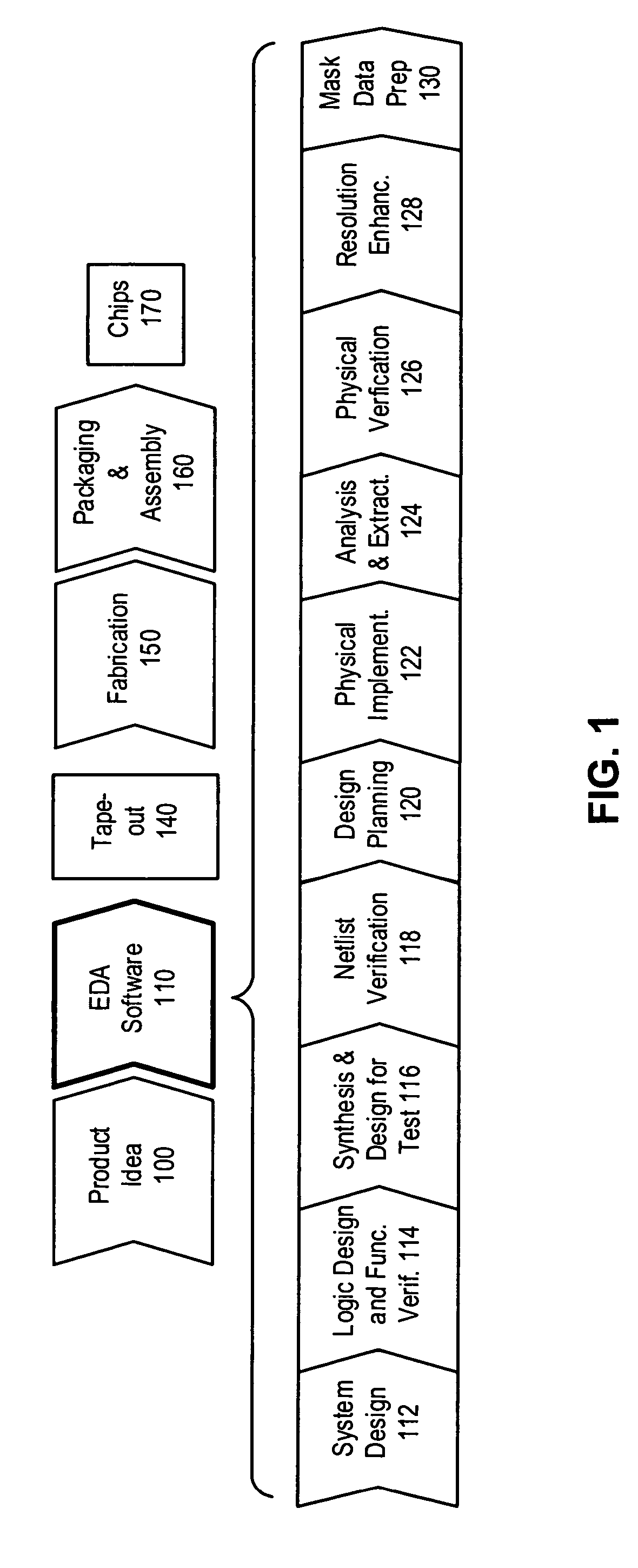

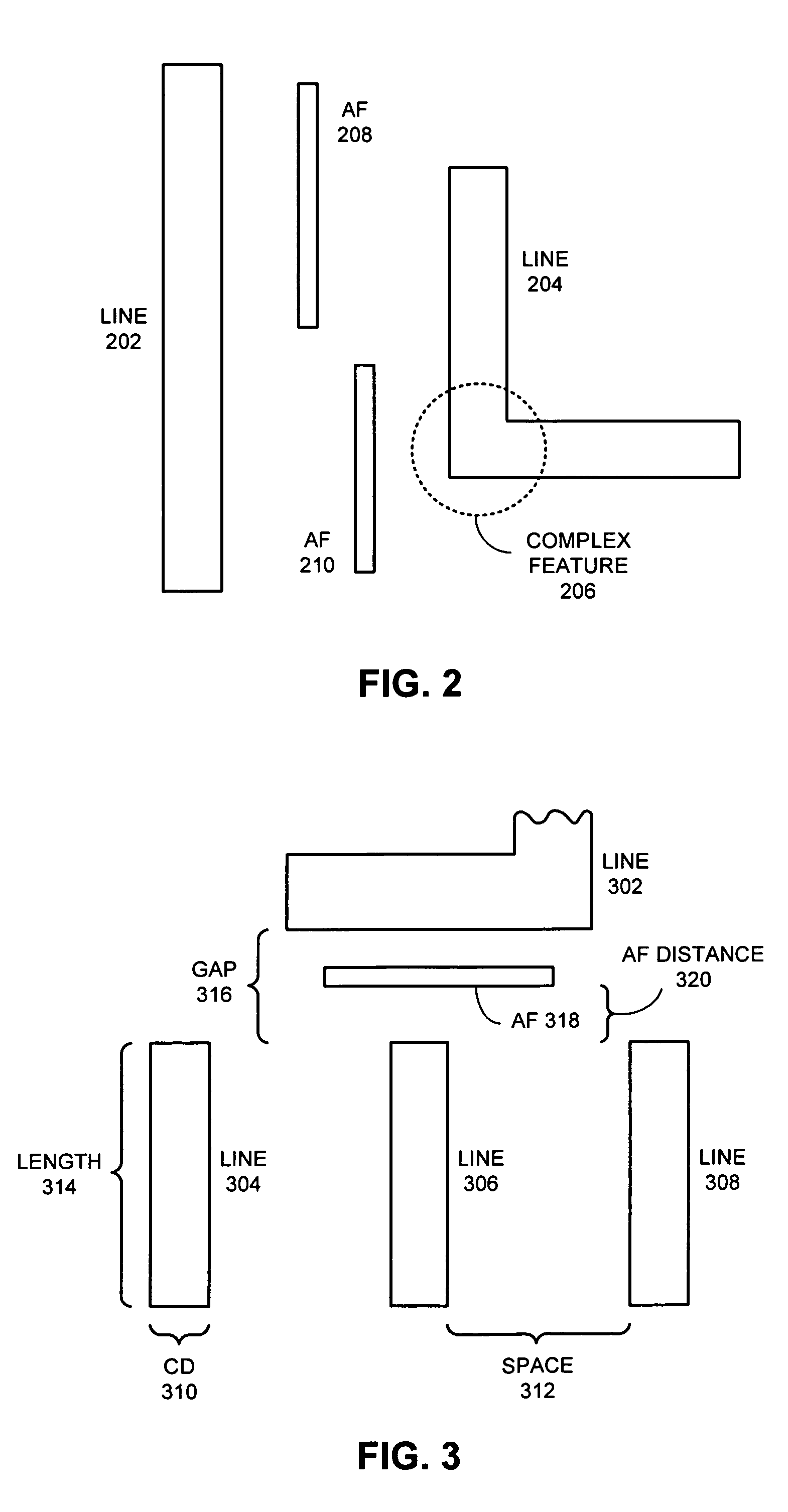

One embodiment of the present invention determines the effect of placing an assist feature at a location in a layout. During operation, the system receives a first value which was pre-computed by convolving a model with a layout at an evaluation point, wherein the model models semiconductor manufacturing processes. Next, the system determines a second value by convolving the model with an assist feature, which is assumed to be located at a first location which is in proximity to the evaluation point. The system then determines the effect of placing an assist feature using the first value and the second value. An embodiment of the present invention can be used to determine a substantially optimal location for placing an assist feature in a layout.

Owner:SYNOPSYS INC

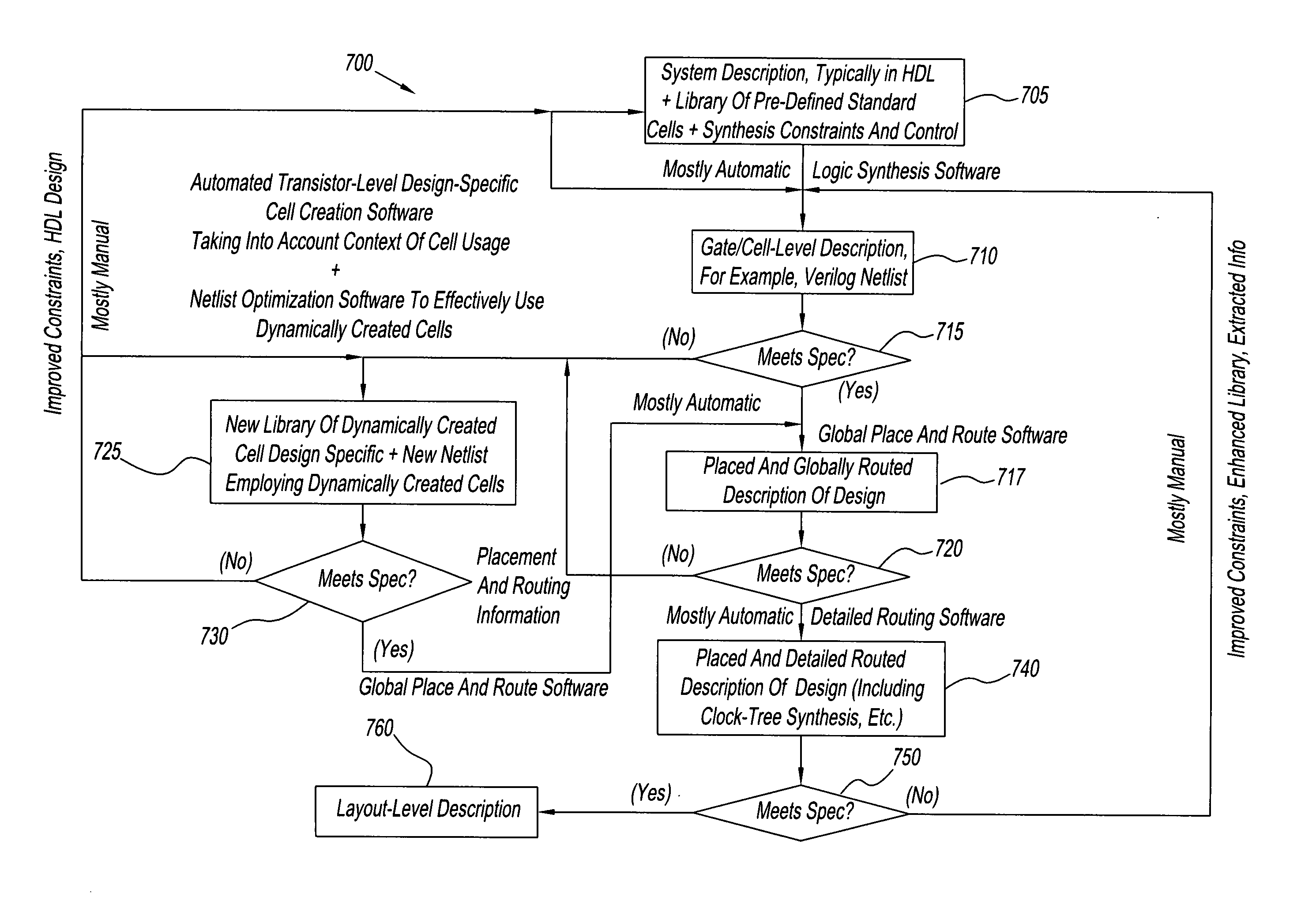

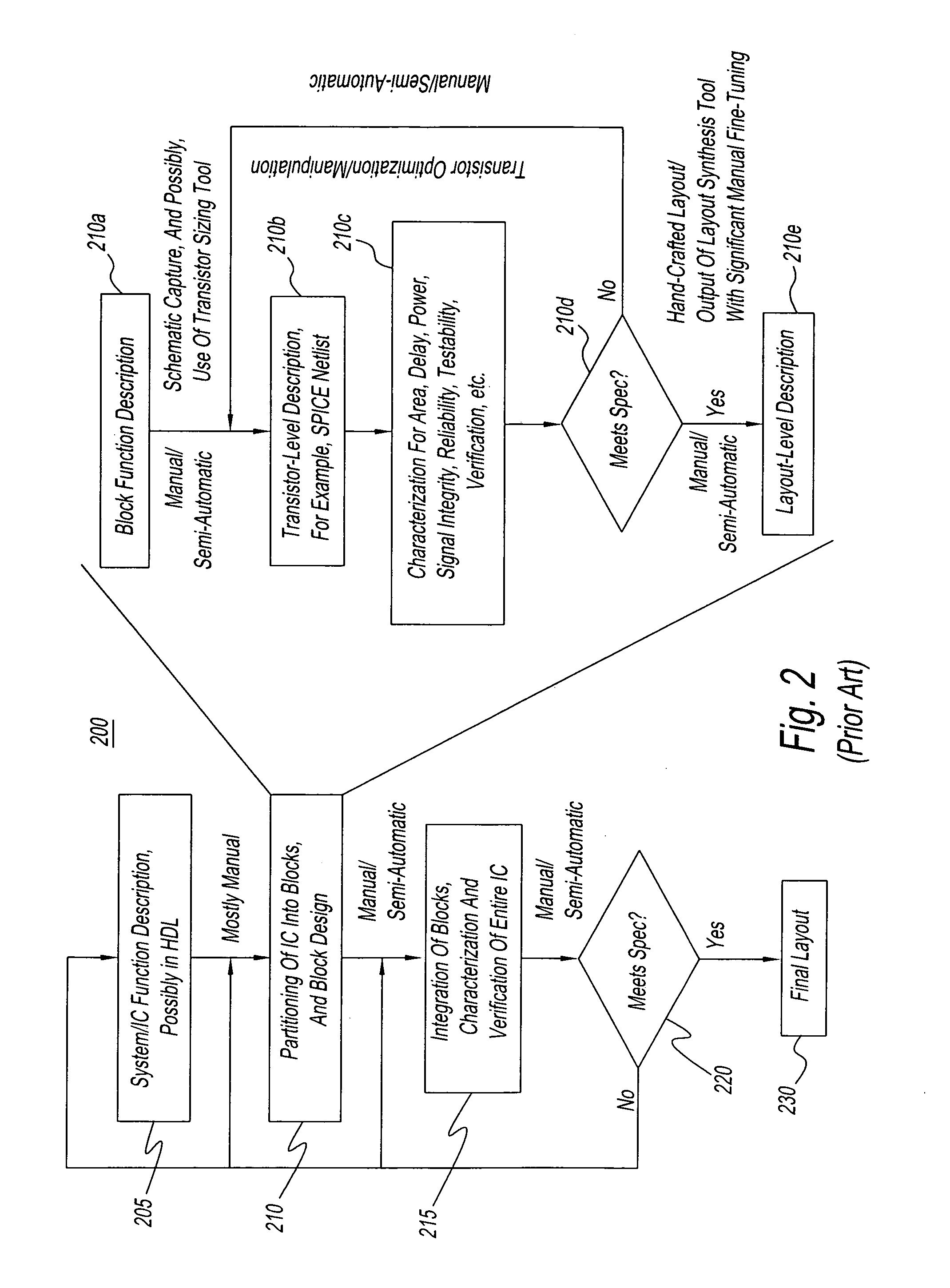

Method for automated design of integrated circuits with targeted quality objectives using dynamically generated building blocks

InactiveUS7225423B2Improve propertiesMinimize the numberCAD circuit designSoftware simulation/interpretation/emulationTarget analysisComputer architecture

A system and method for designing ICs, including the steps of: analyzing and optimizing a target IC design based on design-specific objectives; partitioning the optimized target IC design into pre-defined standard-cells from one or more libraries and creating design-specific cells specifically having unique functionality and characteristics not found amongst the standard-cells; identifying and determining a minimal subset of the standard-cells and design-specific cells, the interconnection of which represents the target IC design; generating the necessary views, including layout and characterizing of the design-specific cells included in a unique, minimal subset, wherein the IC design is subject to objectives and constraints of the target IC.

Owner:OPEN-SILICON

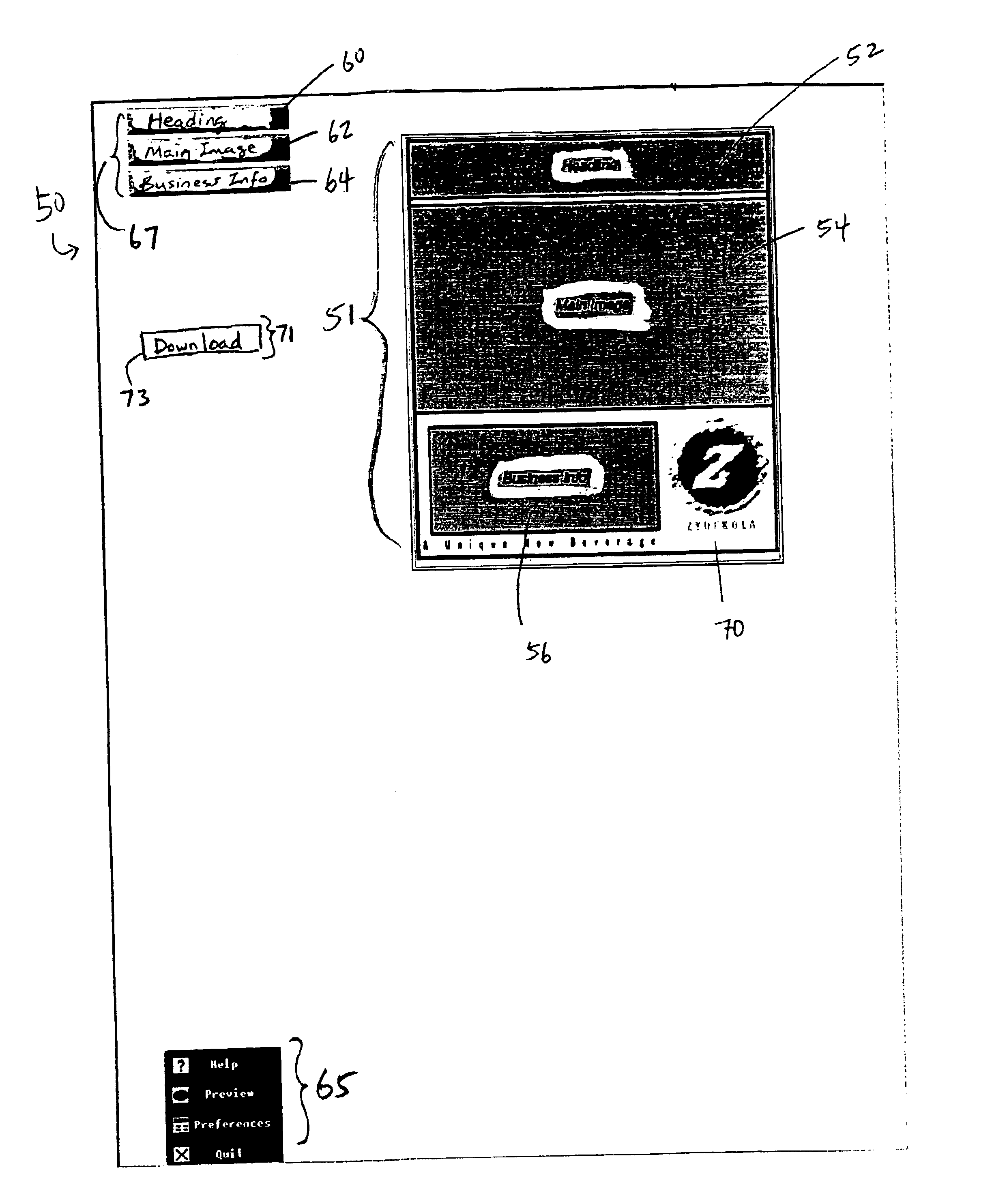

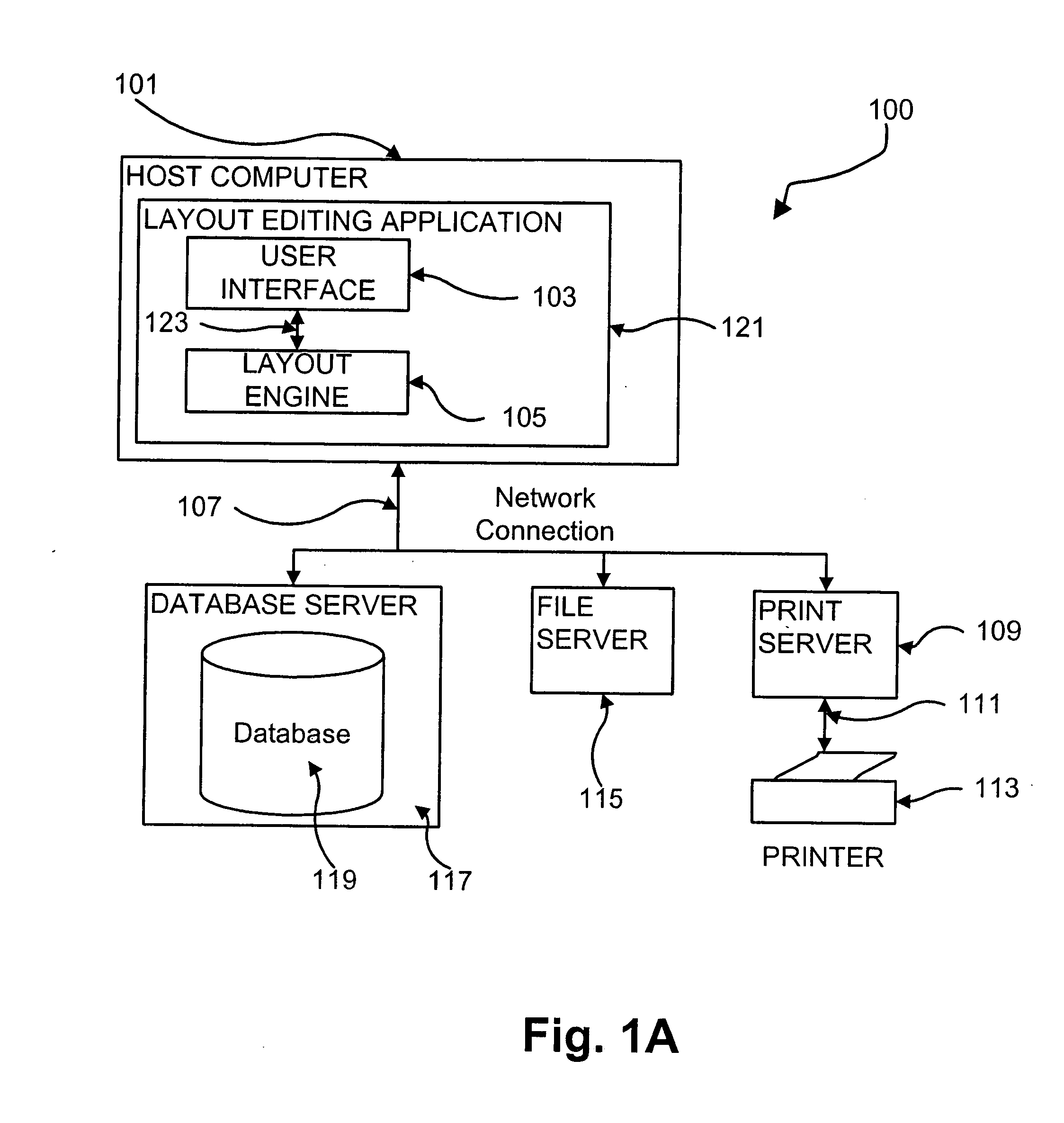

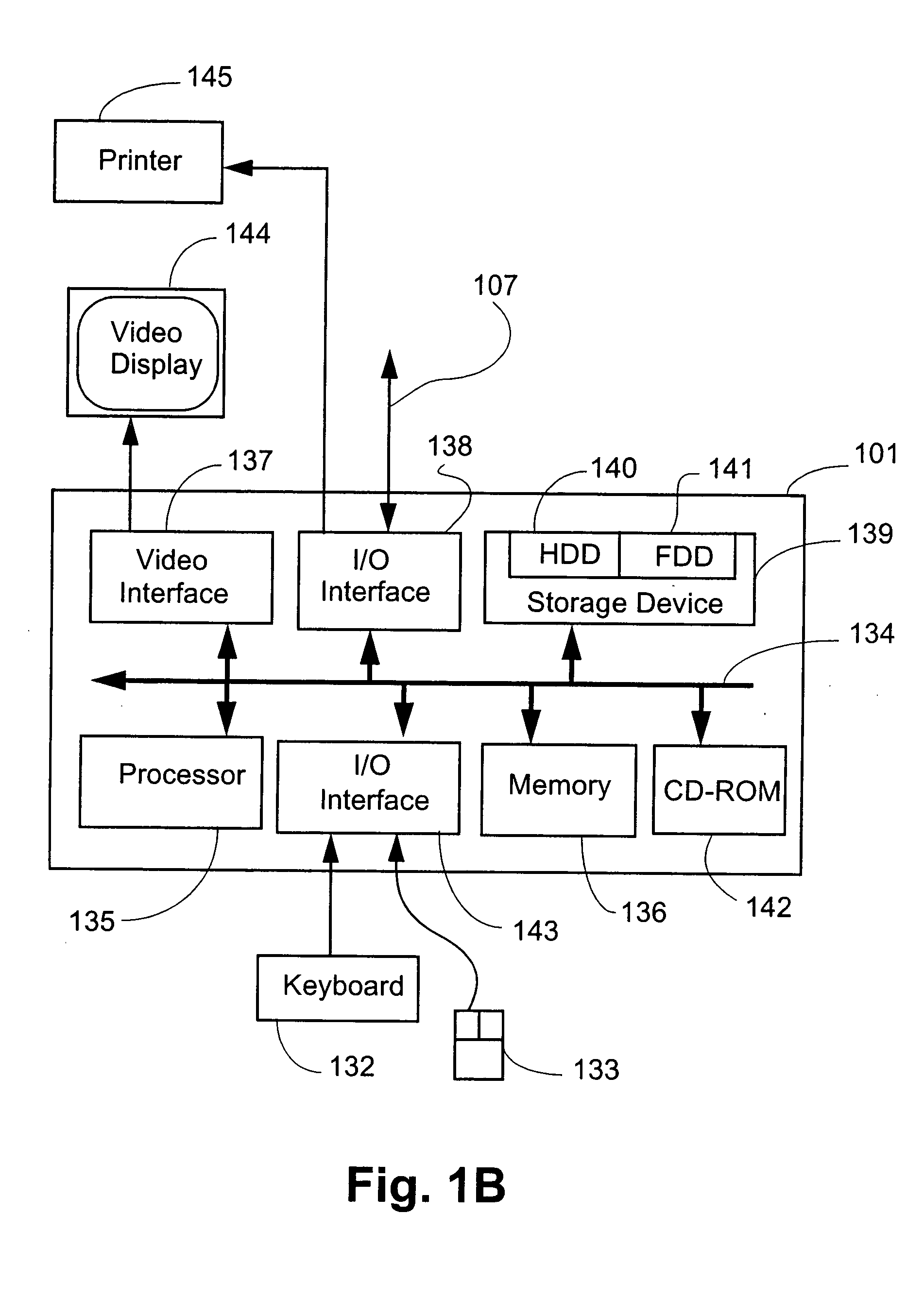

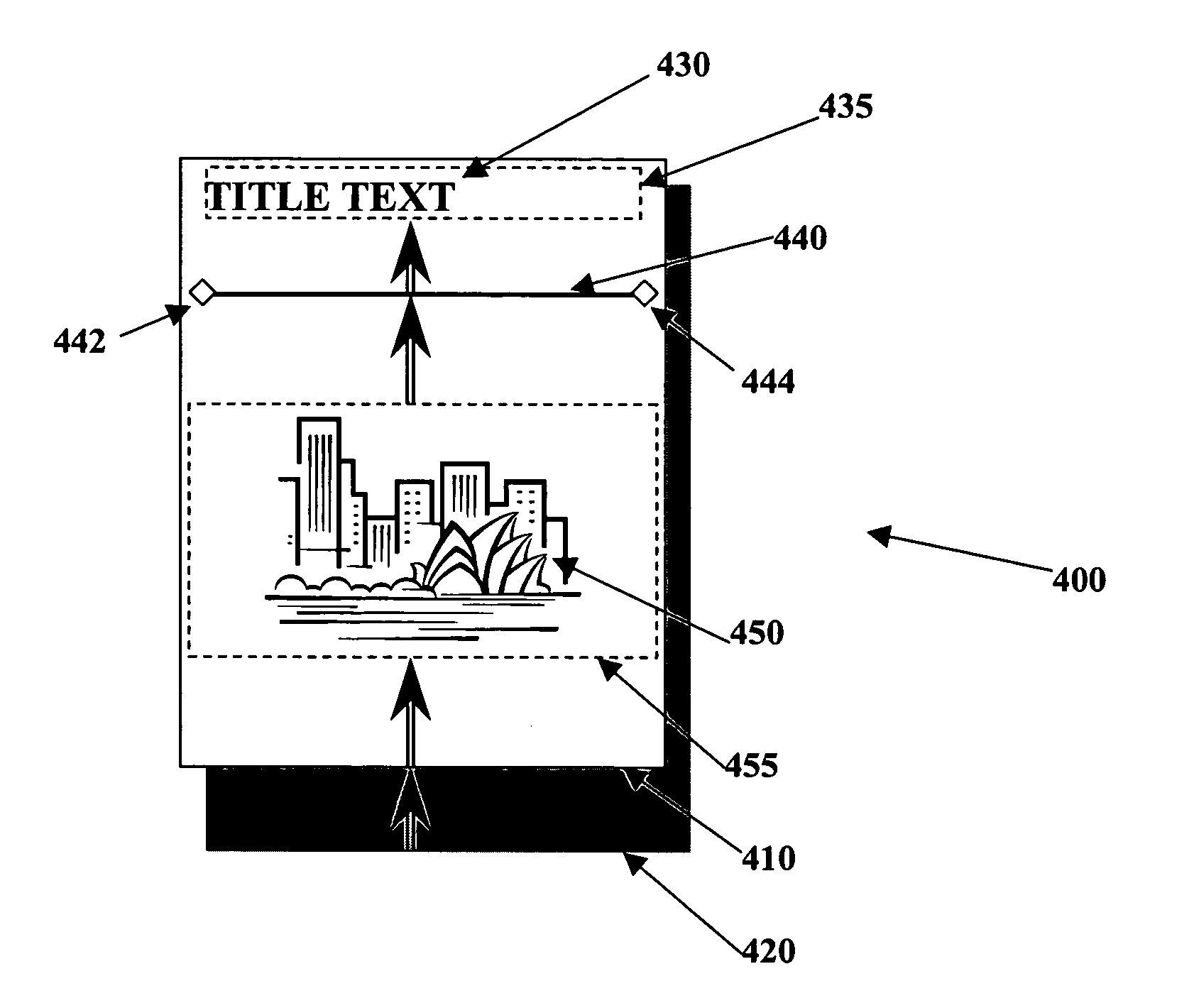

Publishing layout wizard

InactiveUS6931591B1Expensive to maintainExpensive to updateCathode-ray tube indicatorsNatural language data processingGraphicsWeb browser

The present invention facilitates the specification and distribution of templated content materials by a content provider over an information exchange network such as the Internet. The present invention incorporates a system for managing inventories of graphical elements and their relationships to pre-defined page templates. A database capable of keeping track of users and their corresponding access privileges within the system is employed to monitor user activity. Ultimately, through the use of a software component delivered over the Internet for use within standard web browsers, end-users are able to populate templates under the constraints imposed by the rules of the manufacturers at the time of template design. These population elements which “fill in the blanks” of the pre-defined templates may be either of type IMAGE or TEXT. Image regions are populated by choosing from a subset of the entire image inventory, while TEXT types can be completely free form, with specific rules guiding justification, point size, font, and leading, or “fill in the blank” form with the same constraint rules as free form. Once the end user has met all of the criteria for a fully populated template, the system provides sophisticated means for downloading a high resolution file (such as a print-ready file or other file representation of the composed publication) which encapsulates all resources needed (layout, images, fonts, and constraint geometries) to fulfill the requirements of the publication. The downloaded file may be printed or published by electronic transfer, e.g., to a publisher for printing of the actual publication.

Owner:SAEPIO TECH

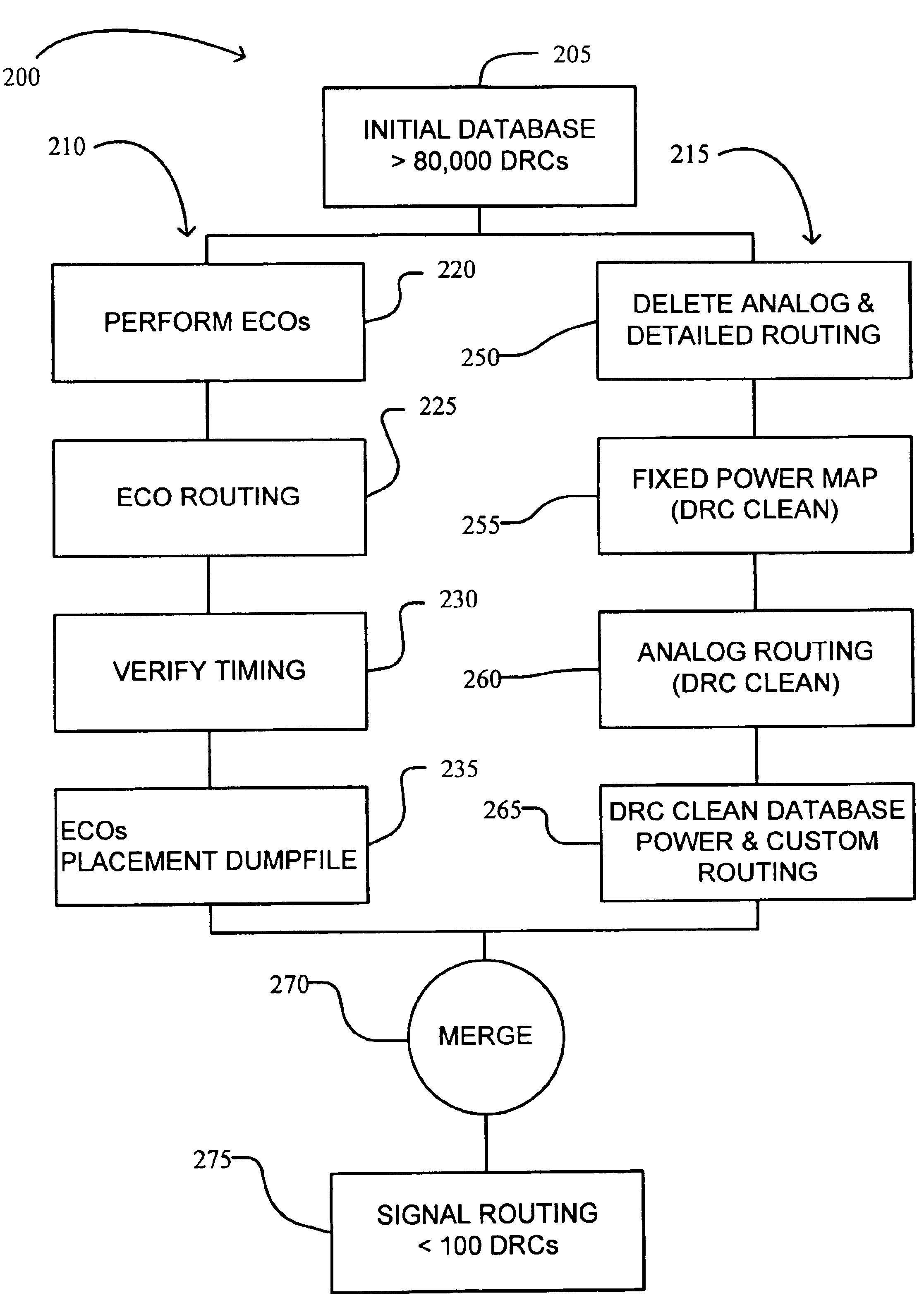

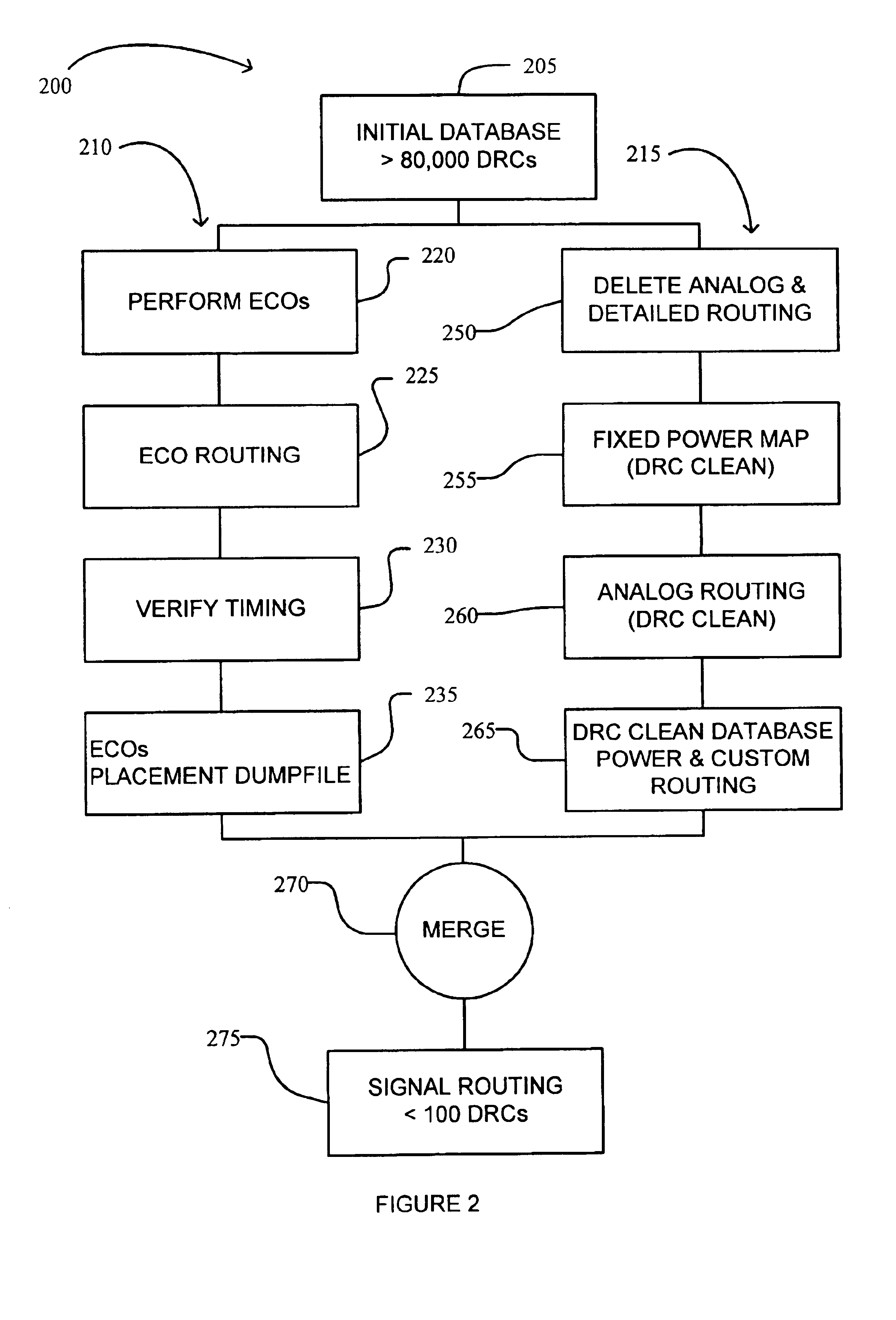

Split and merge design flow concept for fast turnaround time of circuit layout design

ActiveUS6898770B2Increase turnaround timeAccurate verificationComputer aided designSoftware simulation/interpretation/emulationSufficient timeTurnaround time

A method and system is disclosed to improve the turnaround time to provide adequate time to meet project schedules in the event that adjustments or modifications to the design are necessary. A method for improving a turnaround time for design verification of a process database representing a semiconductor design includes the steps of (a) deriving a timing database and a (DNE) database from the process database; (b) performing, using the timing database, one or more design changes and one or more timing verifications and corrections to generate a modified timing database; (c) initiating, using the process database, physical validation of the semiconductor design prior to completion of step (b) to generate a modified DNE database; (d) merging the modified timing database with the modified DNE database to form a modified process database; and (e) performing, using the modified process database, one or more design verification checks of the semiconductor design.

Owner:BELL SEMICON LLC

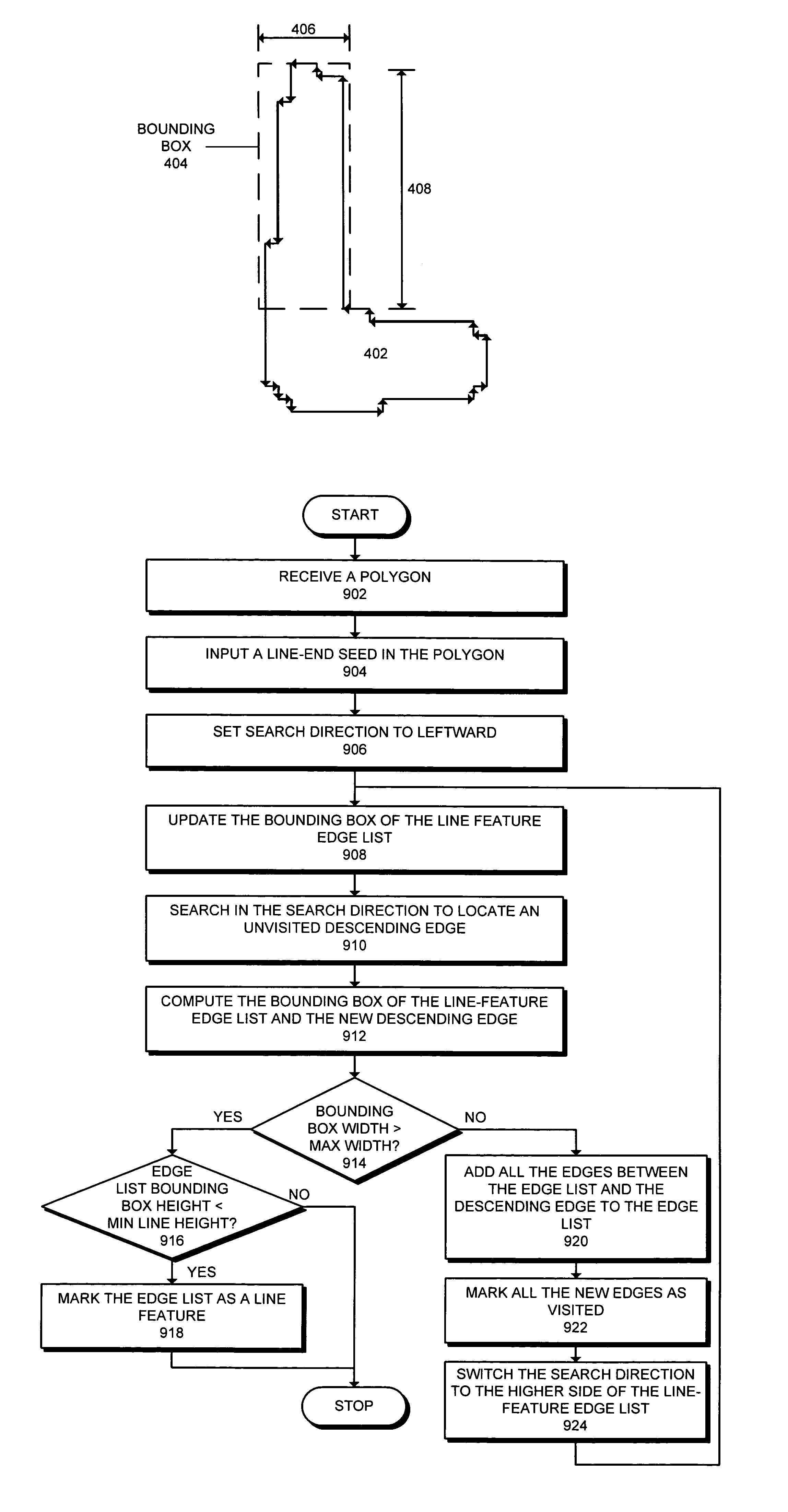

Method and apparatus for identifying line-end features for lithography verification

ActiveUS7194712B2Facilitates identifying line-end featureComputer aided designSpecial data processing applicationsLithographic artistEngineering

One embodiment of the invention provides a system that facilitates identifying line-end features in a layout for an integrated circuit. The system operates by first receiving the layout for the integrated circuit. Next, the system selects a polygon from the layout and marks a line-end seed on the polygon. The system then determines if the line-end seed is associated with a line feature, and if so, the system marks the line-end feature inside the line feature.

Owner:SYNOPSYS INC

Use of redundant routes to increase the yield and reliability of a VLSI layout

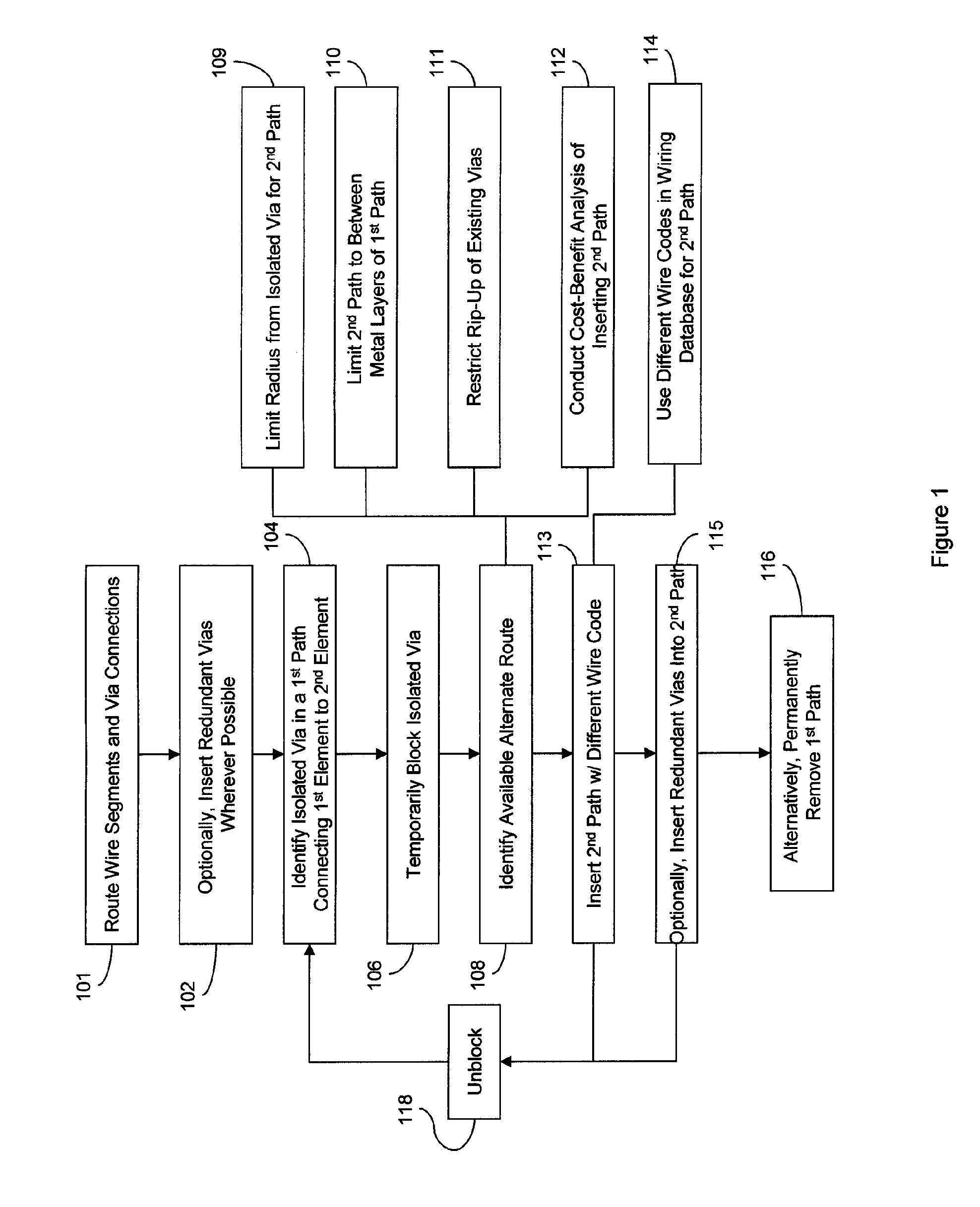

ActiveUS7308669B2Increase redundancyReduce sensitivityCAD circuit designSoftware simulation/interpretation/emulationEngineeringVlsi layout

Disclosed is a method and system for inserting redundant paths into an integrated circuit. Particularly, the invention provides a method for identifying a single via in a first path connecting two elements, determining if an alternate route is available for connecting the two elements (other than a redundant via), and for inserting a second path into the available alternate route. The combination of the first and second paths provides greater redundancy than inserting a redundant via alone. More importantly, such redundant paths provide for redundancy when congestion prevents a redundant via from being inserted adjacent to the single via. An embodiment of the method further comprises removing the single via and any redundant wire segments, if all of the additional vias used to form the second path can be made redundant.

Owner:GLOBALFOUNDRIES US INC

Assist feature placement using a process-sensitivity model

Owner:SYNOPSYS INC

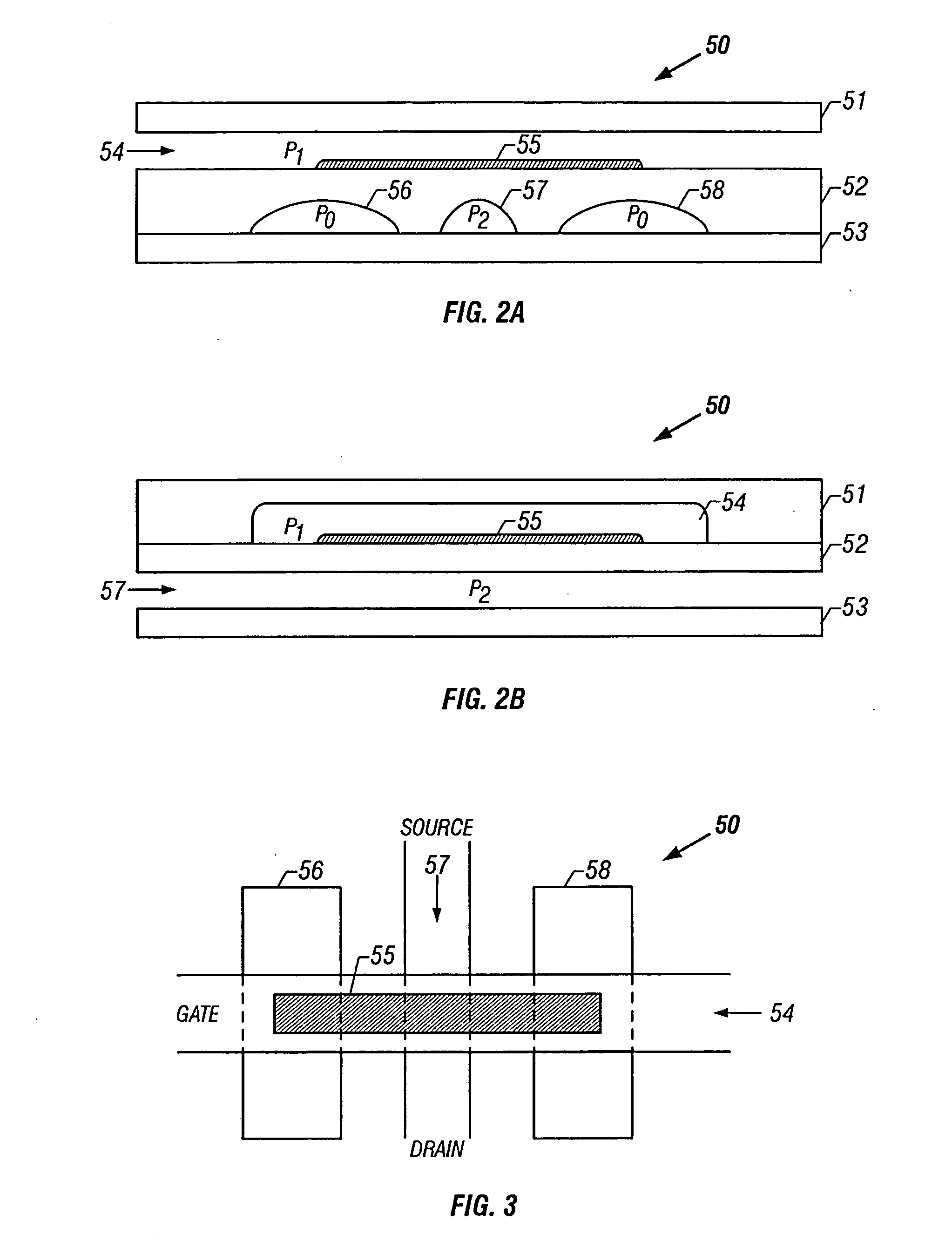

Physical realization of dynamic logic using parameterized tile partitioning

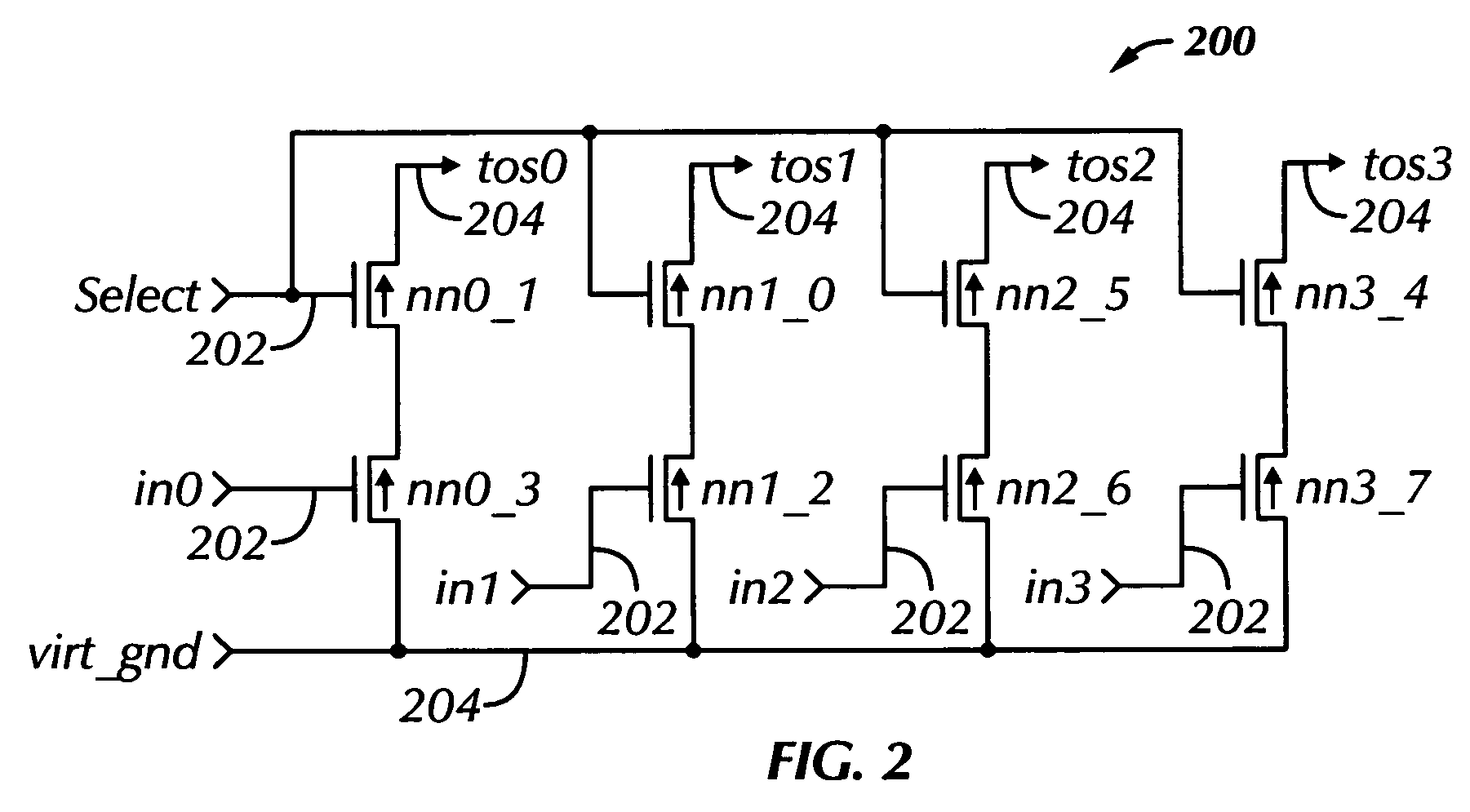

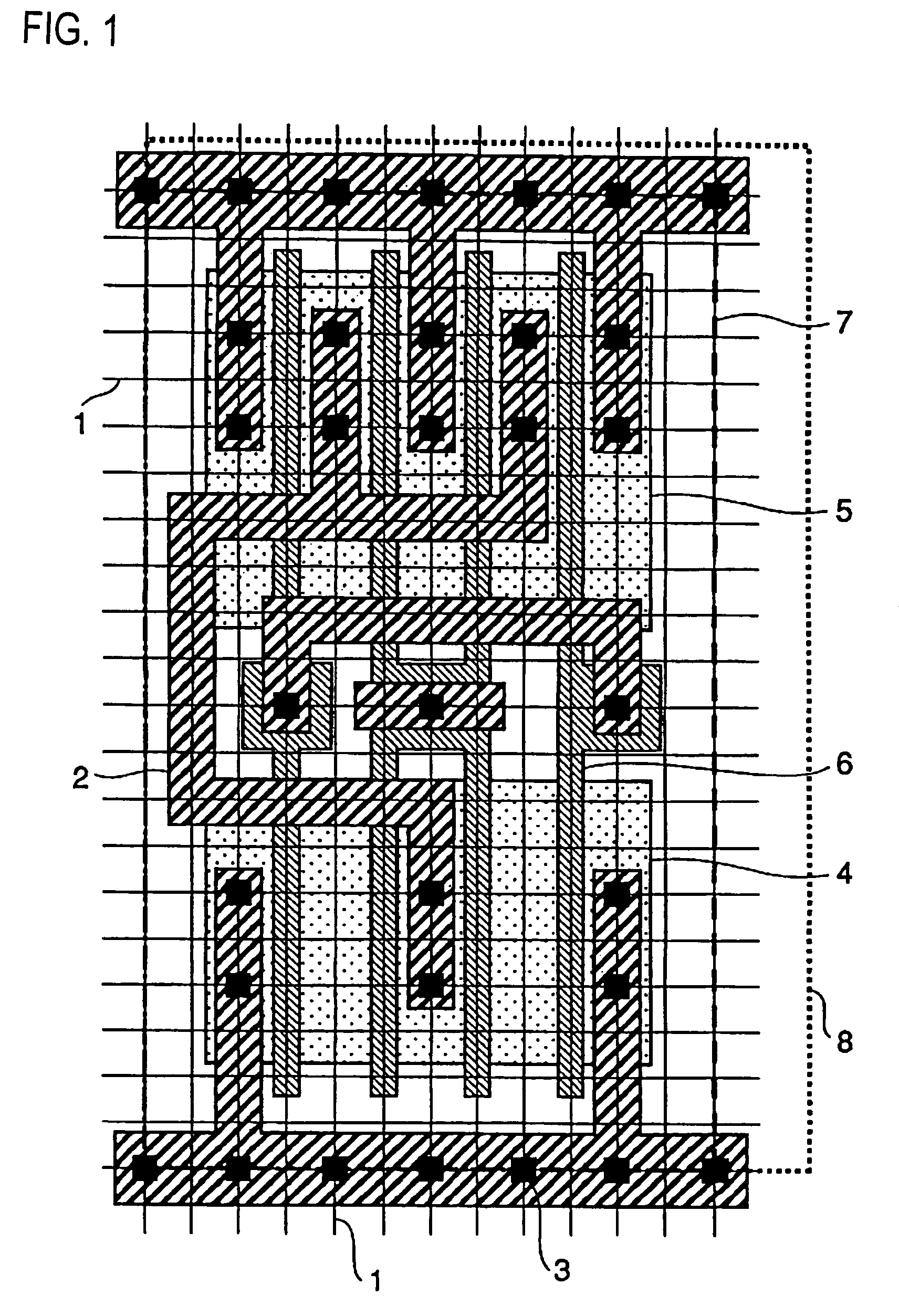

The matching algorithm of the layout synthesis method and apparatus disclosed locates transistor pattern matches in a design, links a parameterized tile to each identified match, and adjusts certain variable parameters of the linked parameterized tile to meet the physical design requirements of each located match. Each transistor pattern corresponds to a parameterized tile, which is an actual physical representation of the corresponding pattern and includes variable parameters, which may include transistor size. The matching algorithm locates matches in the design for an ordered list of patterns, names each located match, links the proper parameterized tile to each named match, and adjusts the tile's variable parameters as required. Transistors in the design are included in one and only one named located match.

Owner:APPLE INC

Circuit layout methodology using a shape processing application

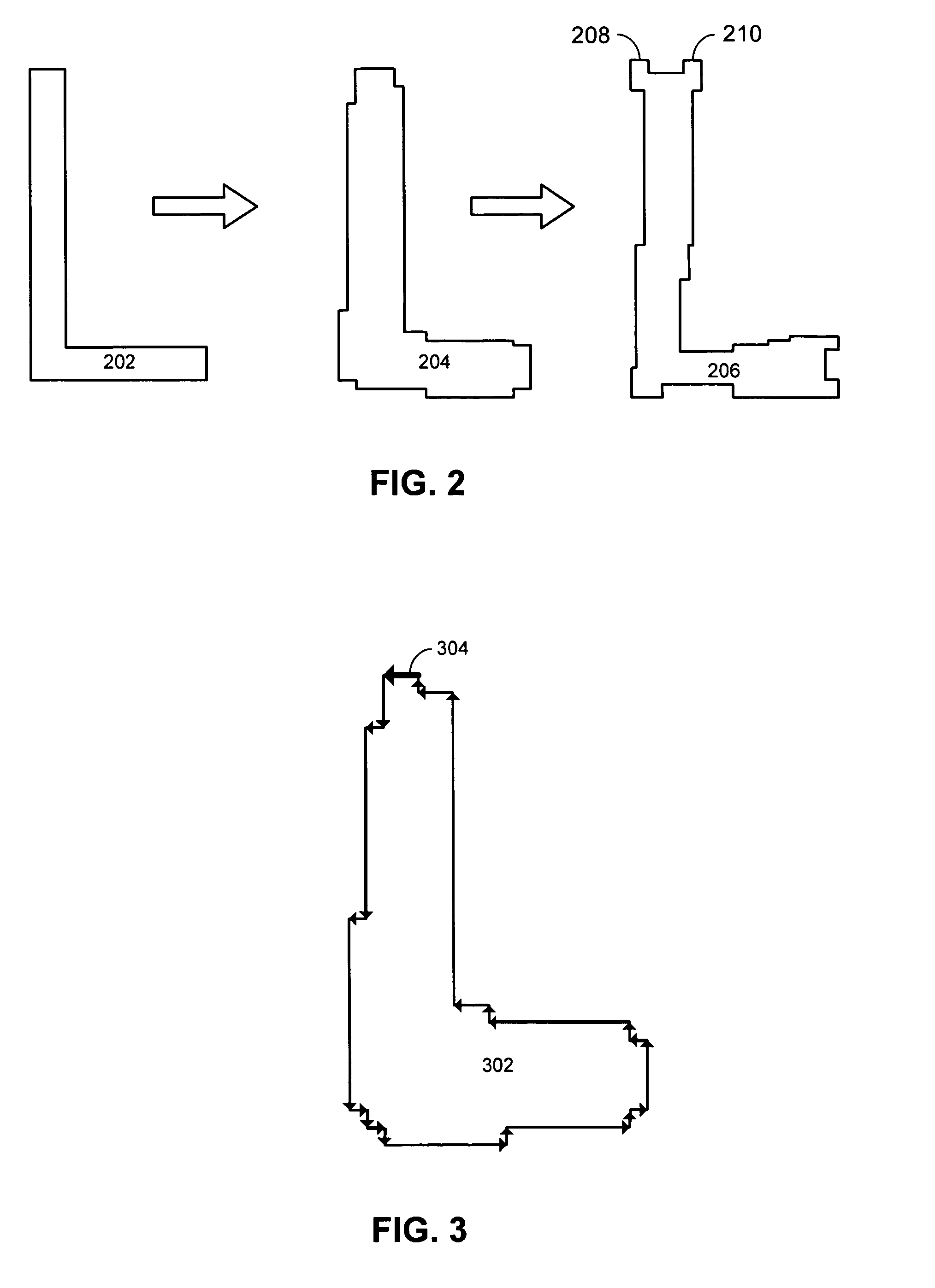

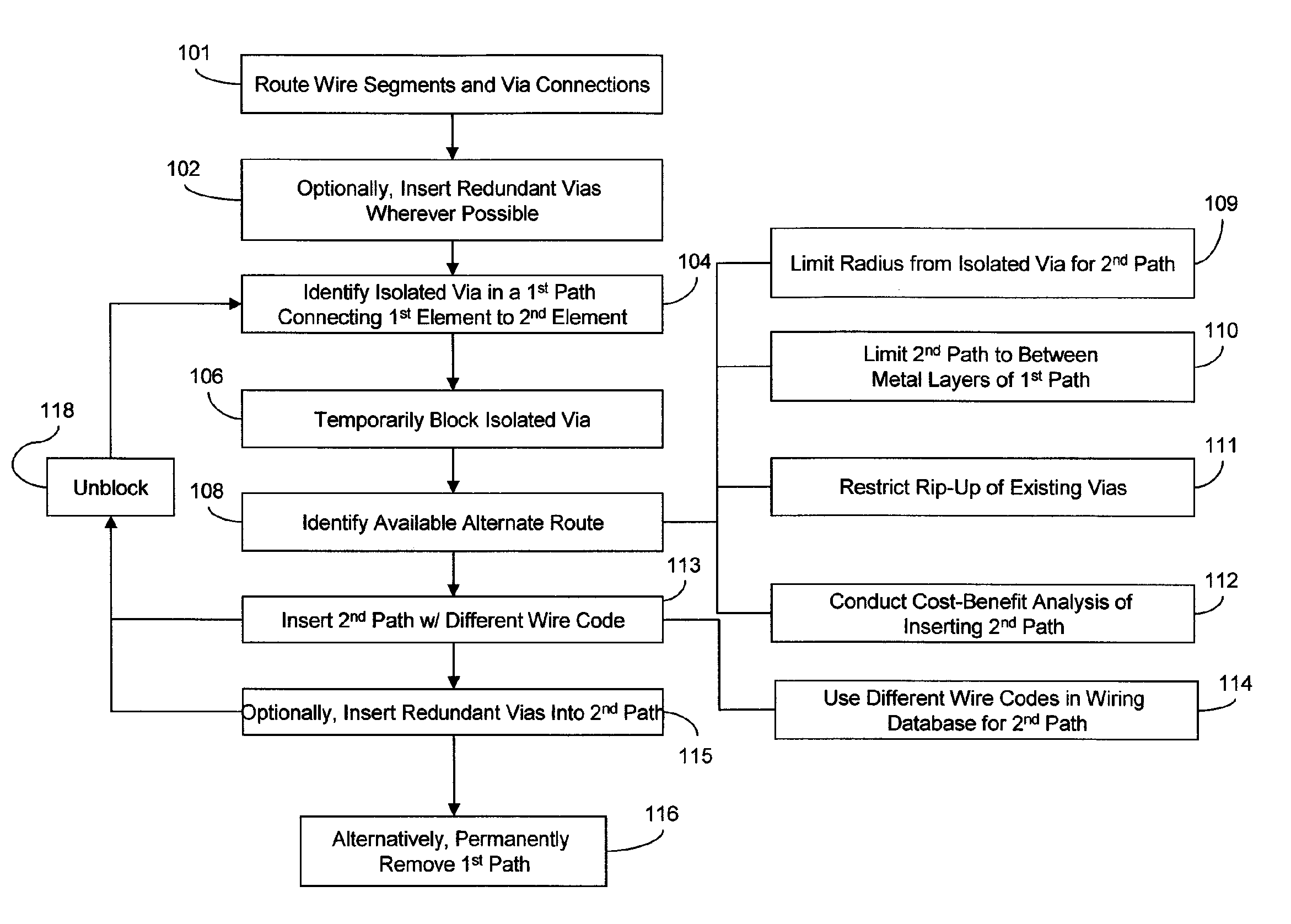

InactiveUS7188322B2Low costSmall sizeCAD circuit designSpecial data processing applicationsManufacturing technologySoftware engineering

Owner:INT BUSINESS MASCH CORP

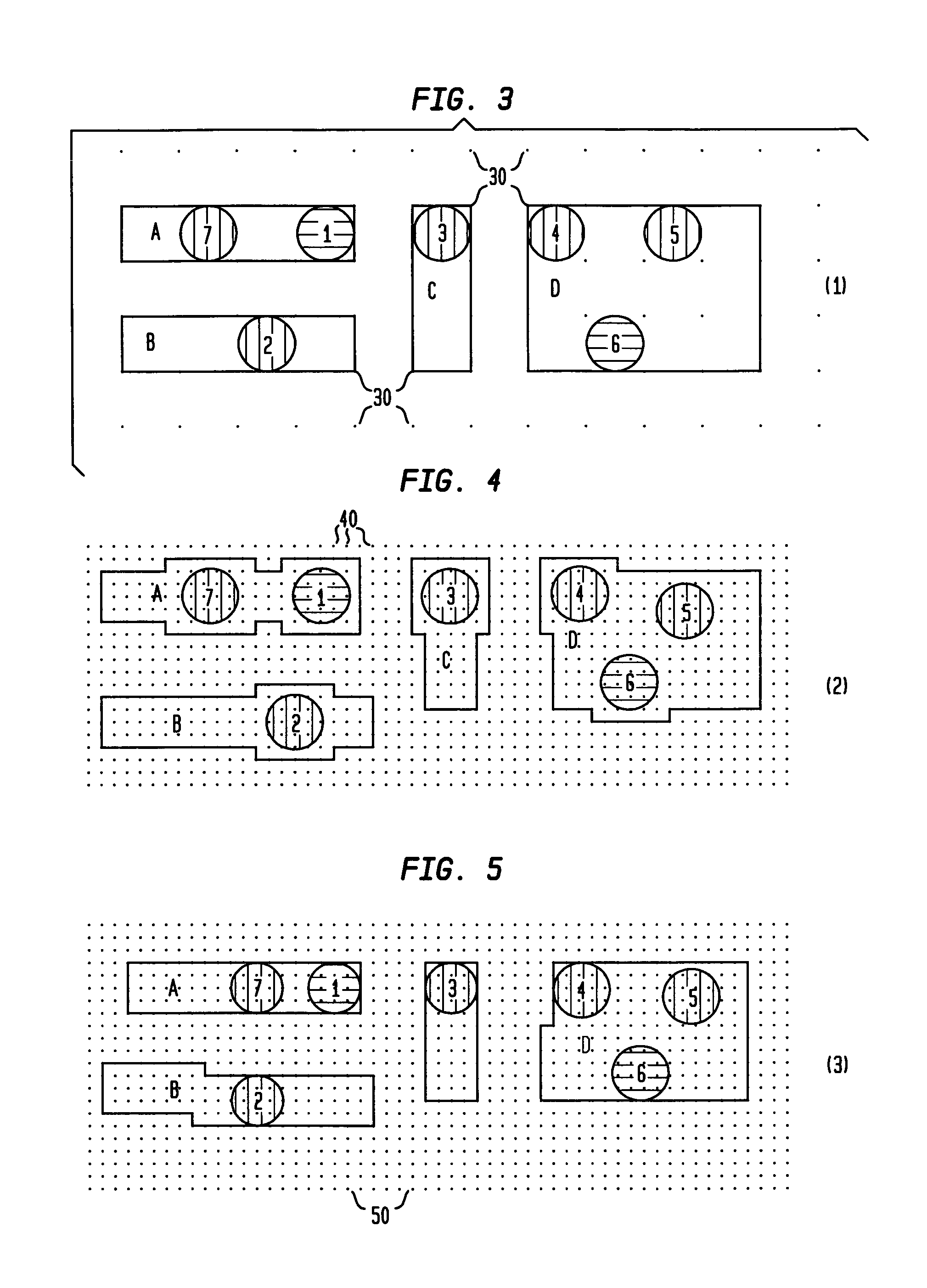

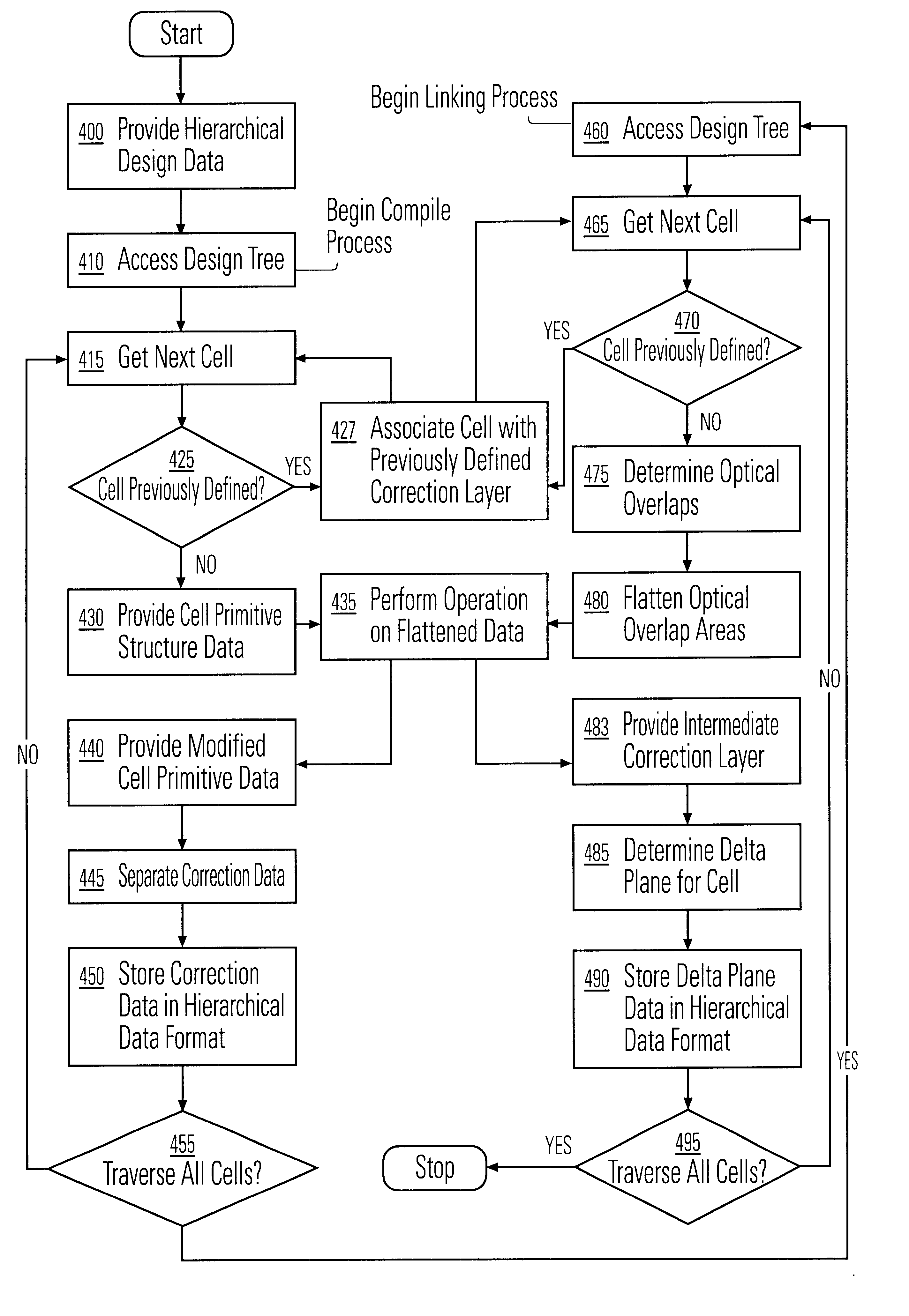

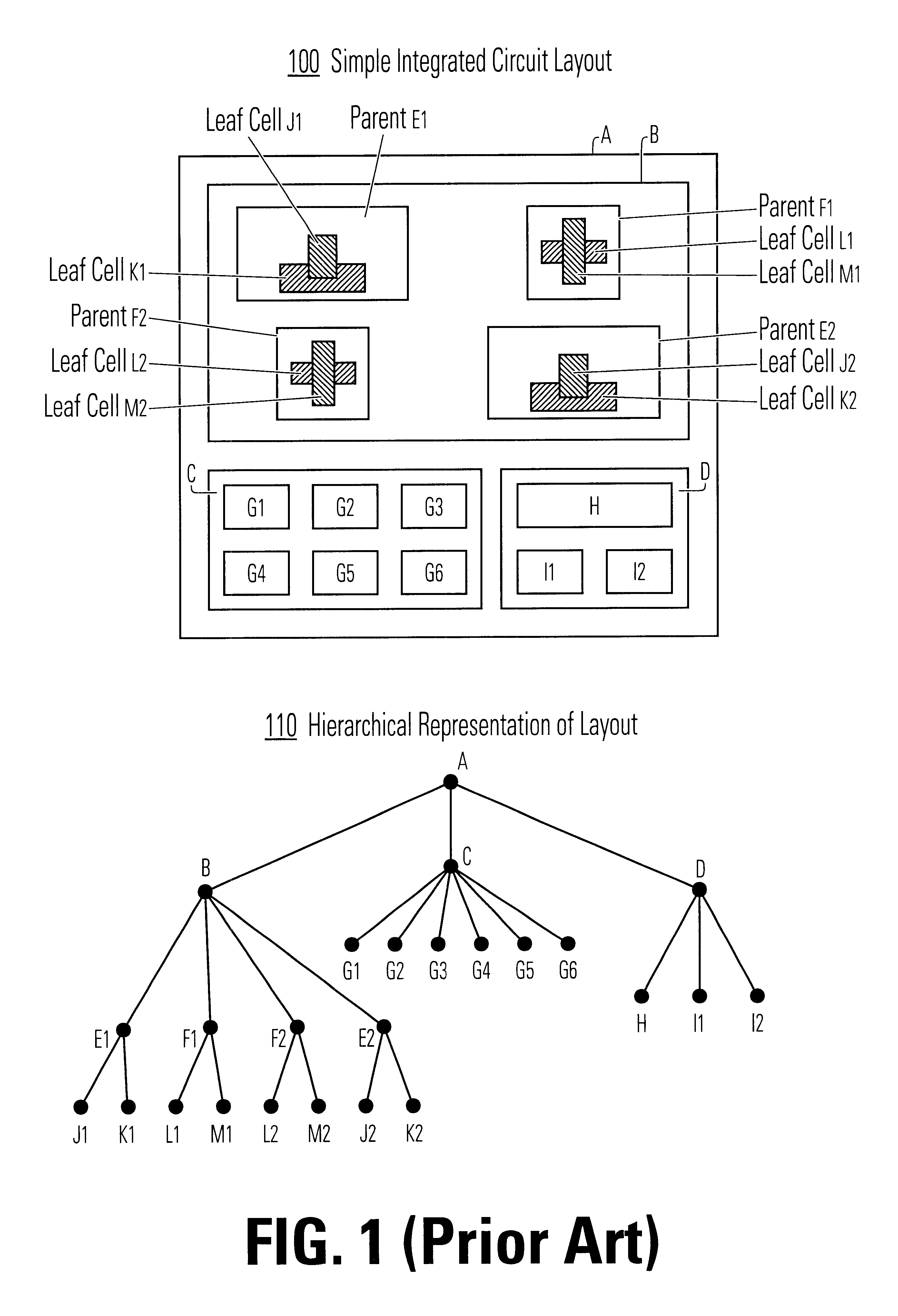

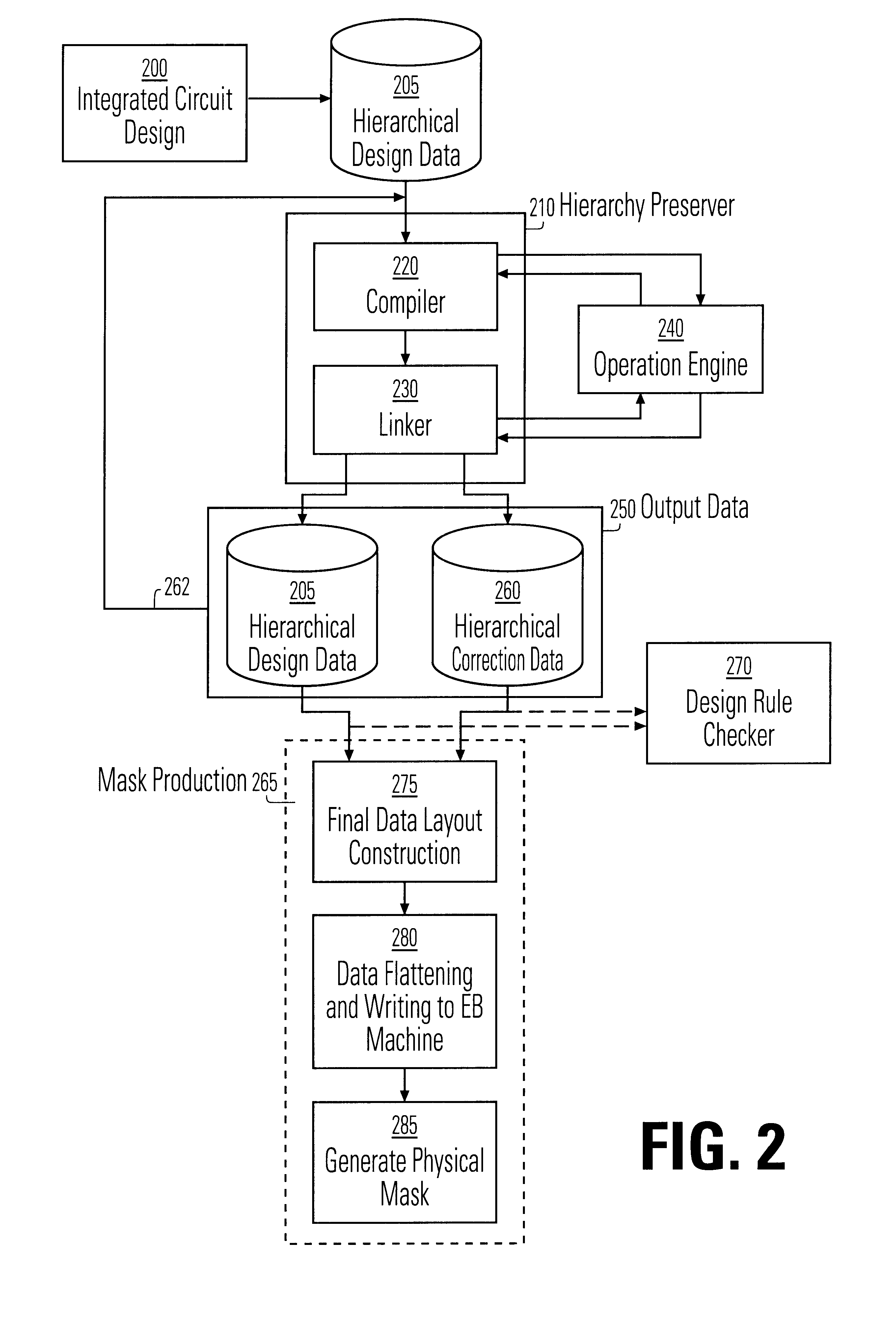

Method and apparatus for data hierarchy maintenance in a system for mask description

InactiveUS6453452B1Data augmentationReduce processing speedCAD circuit designProgram controlComputer architectureLogical operations

A method and apparatus for performing an operation on hierarchically described integrated circuit layouts such that the original hierarchy of the layout is maintained is provided. The method comprises providing a hierarchically described layout as a first input and providing a particular set of operating criteria corresponding to the operation to be performed as a second input. The mask operation, which may include operations such as OPC and logical operations such as NOT and OR, is then performed on the layout in accordance with the particular set of operating criteria. A first program data comprising hierarchically configured correction data corresponding to the hierarchically described layout is then generated in response to the layout operation such that if the first program data were applied to the flattened layout an output comprising data representative of the result of performing the operation on the layout would be generated. As the first program data is maintained in a true hierarchical format, layouts which are operated upon in accordance with this method are able to be processed through conventional design rule checkers. Further, this method is capable of being applied to all types of layouts including light and dark field designs and phase shifting layouts.

Owner:SYNOPSYS INC

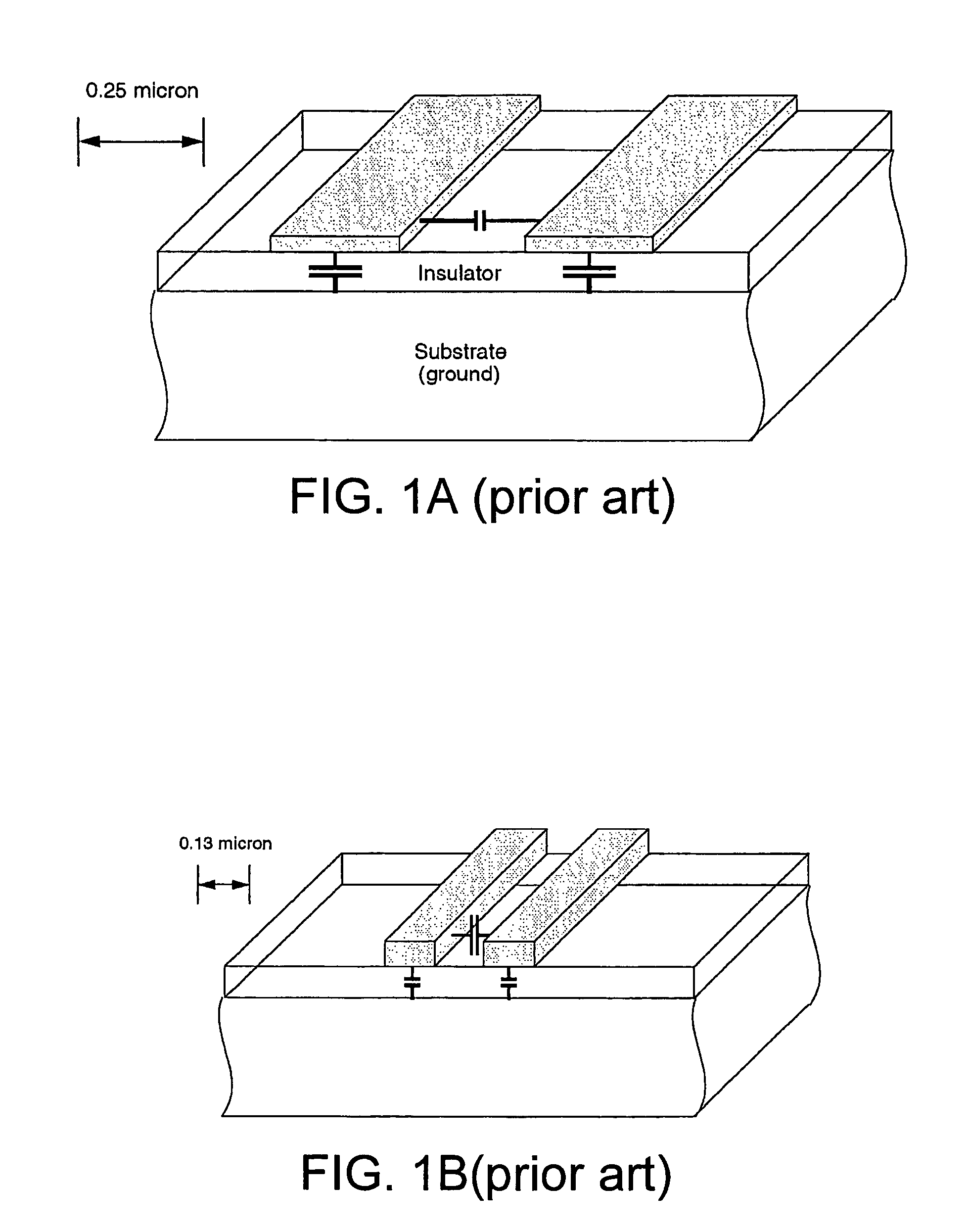

Method for providing layout design and photo mask

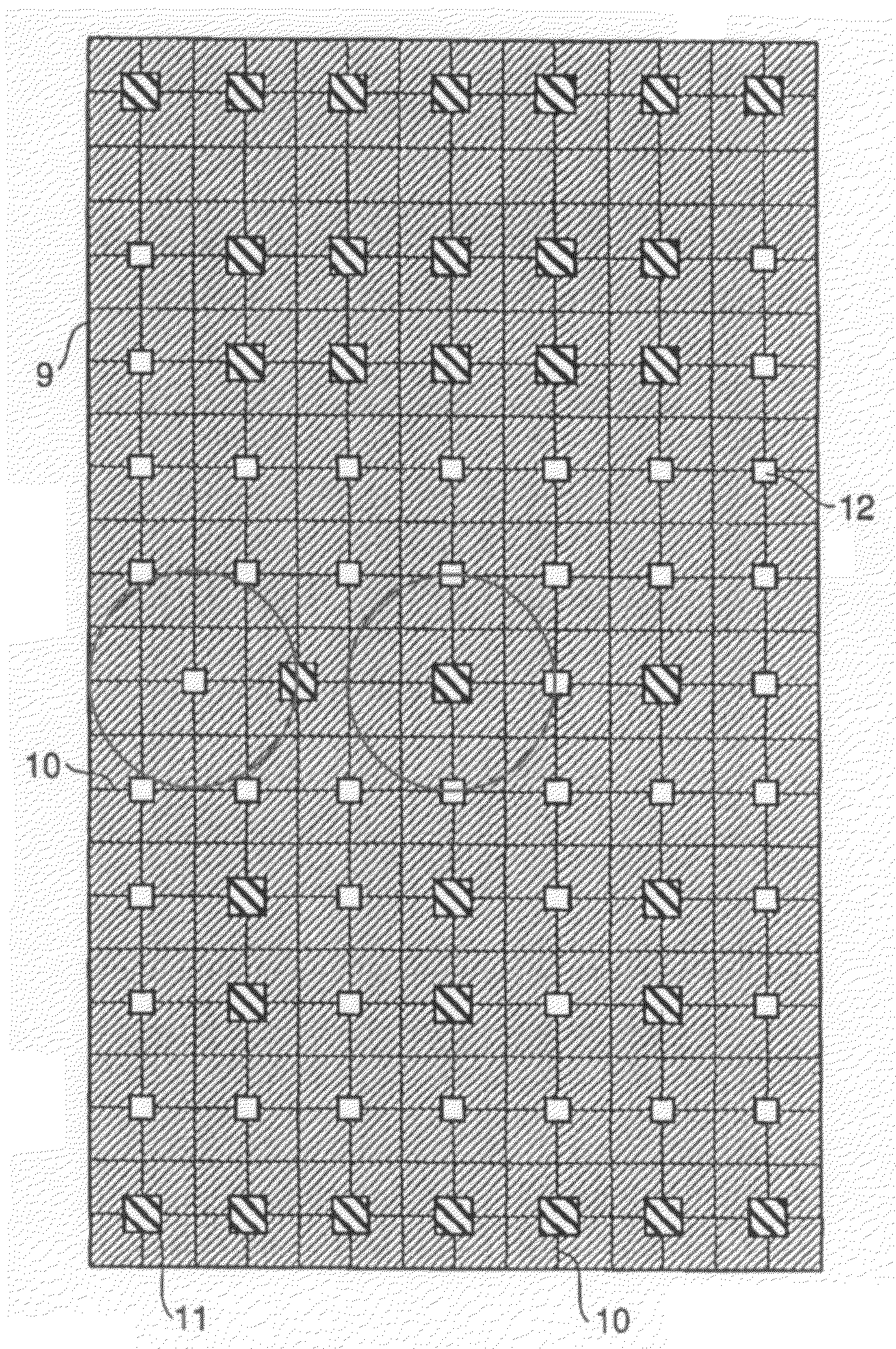

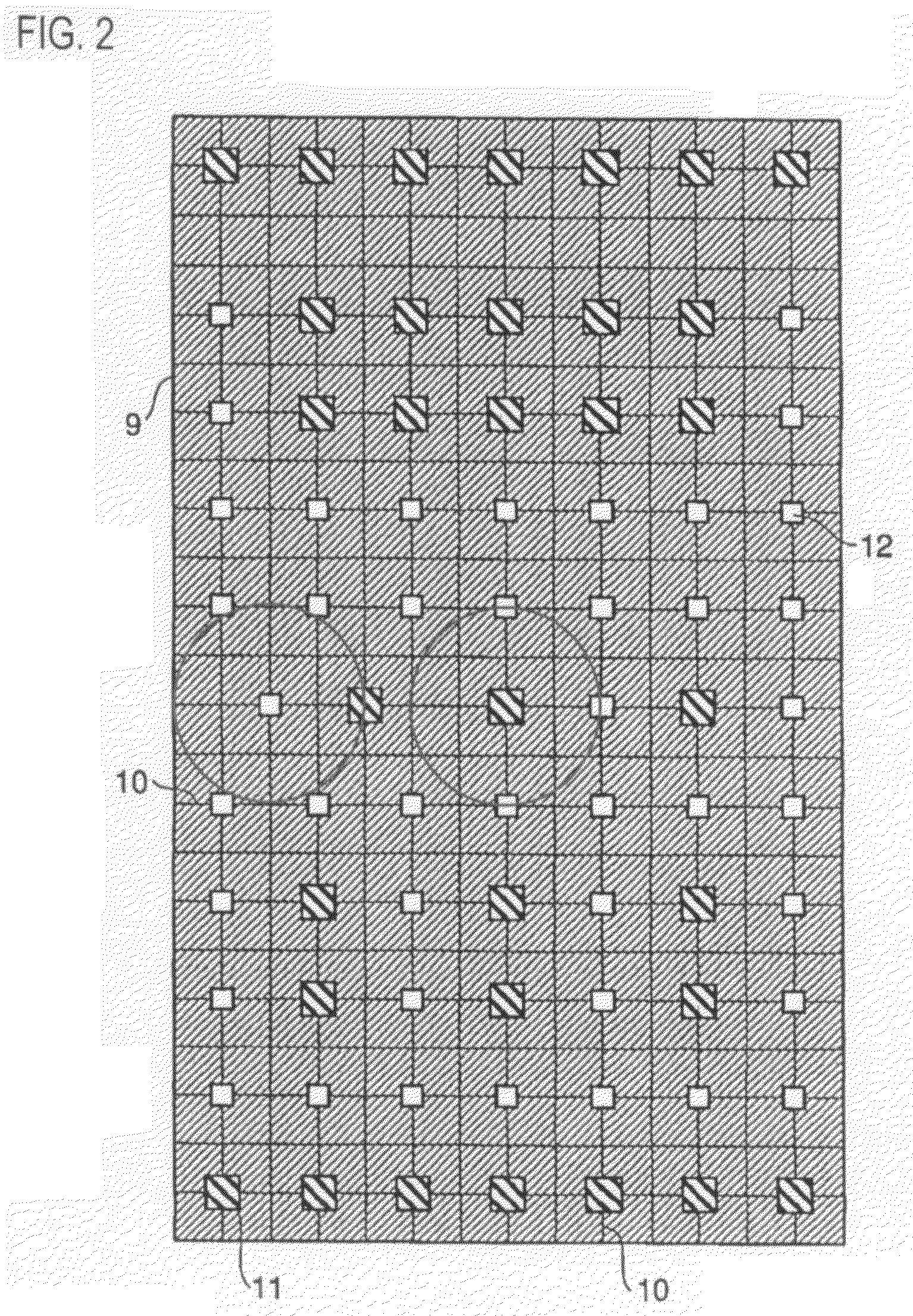

A method for providing the layout design of semiconductor integrated circuit that is capable of promoting the reduction of the circuit pattern area is provided. A hole pattern is disposed at the mesh point which is an intersecting point of mutually orthogonal virtual grid lines and another hole pattern is not disposed at the adjacent mesh point that is the closed mesh point having the hole pattern thereon.

Owner:RENESAS ELECTRONICS CORP

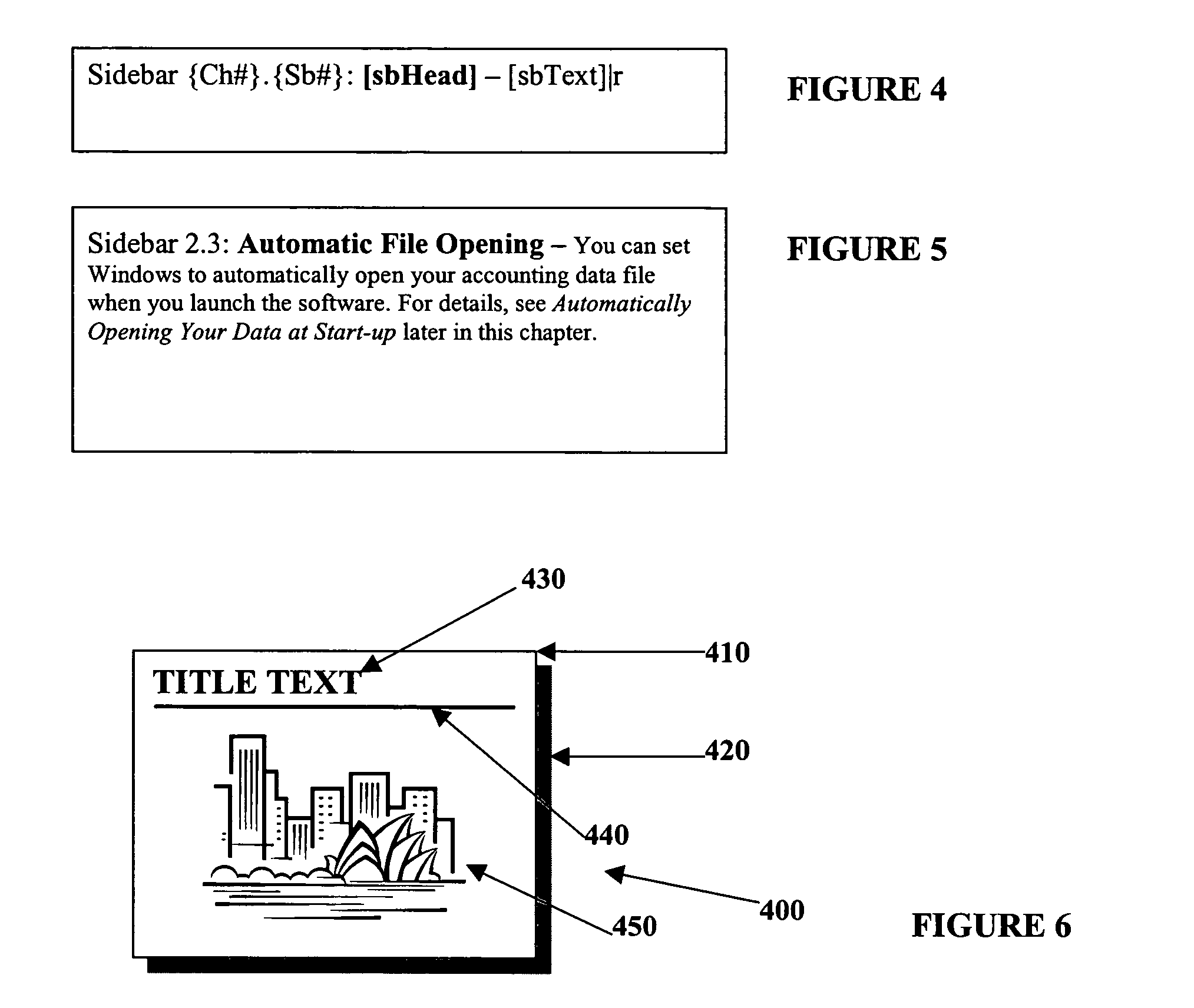

User interface for creation and editing of variable data documents

InactiveUS20050094207A1Visual presentation using printersNatural language data processingGraphical user interfaceLayout

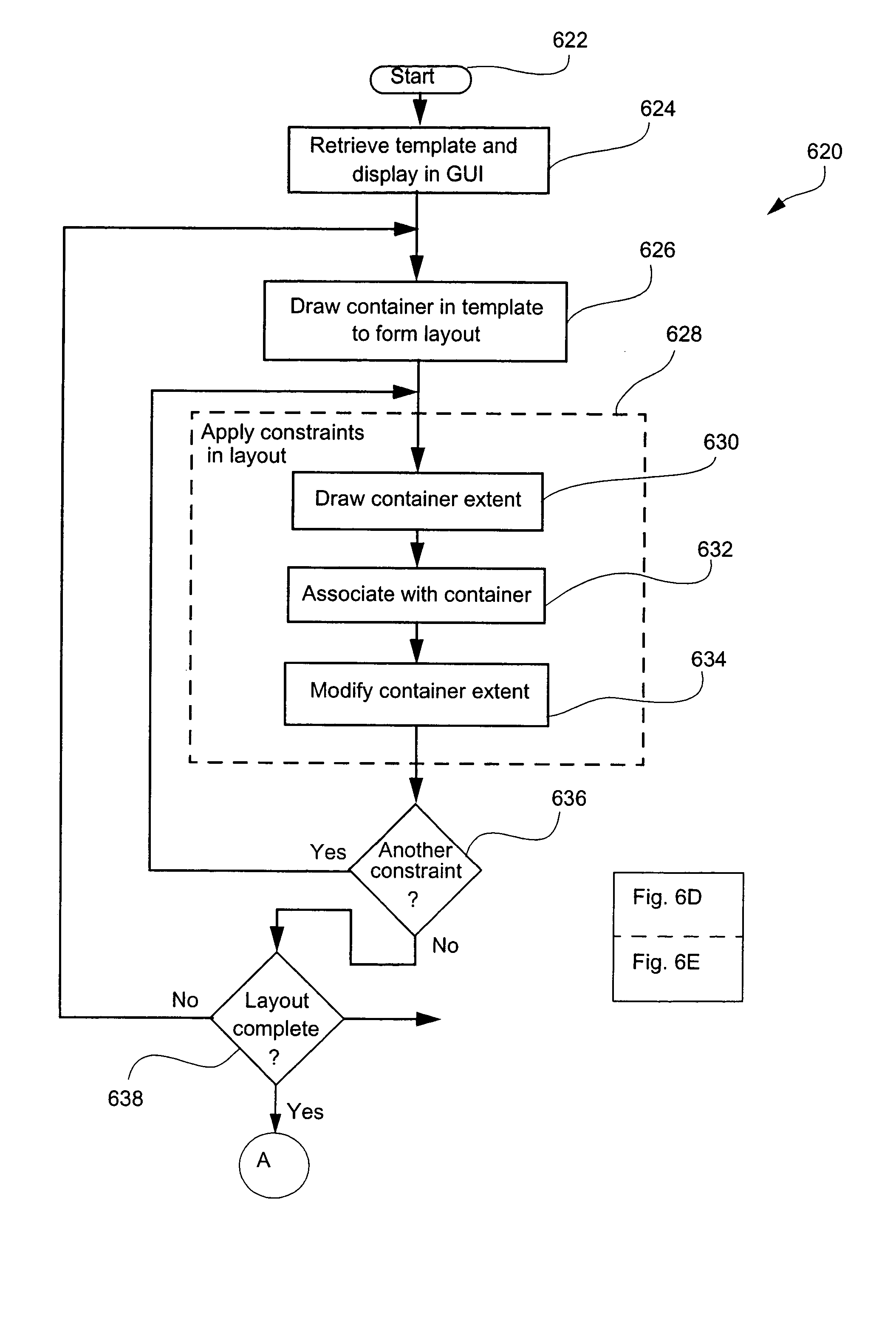

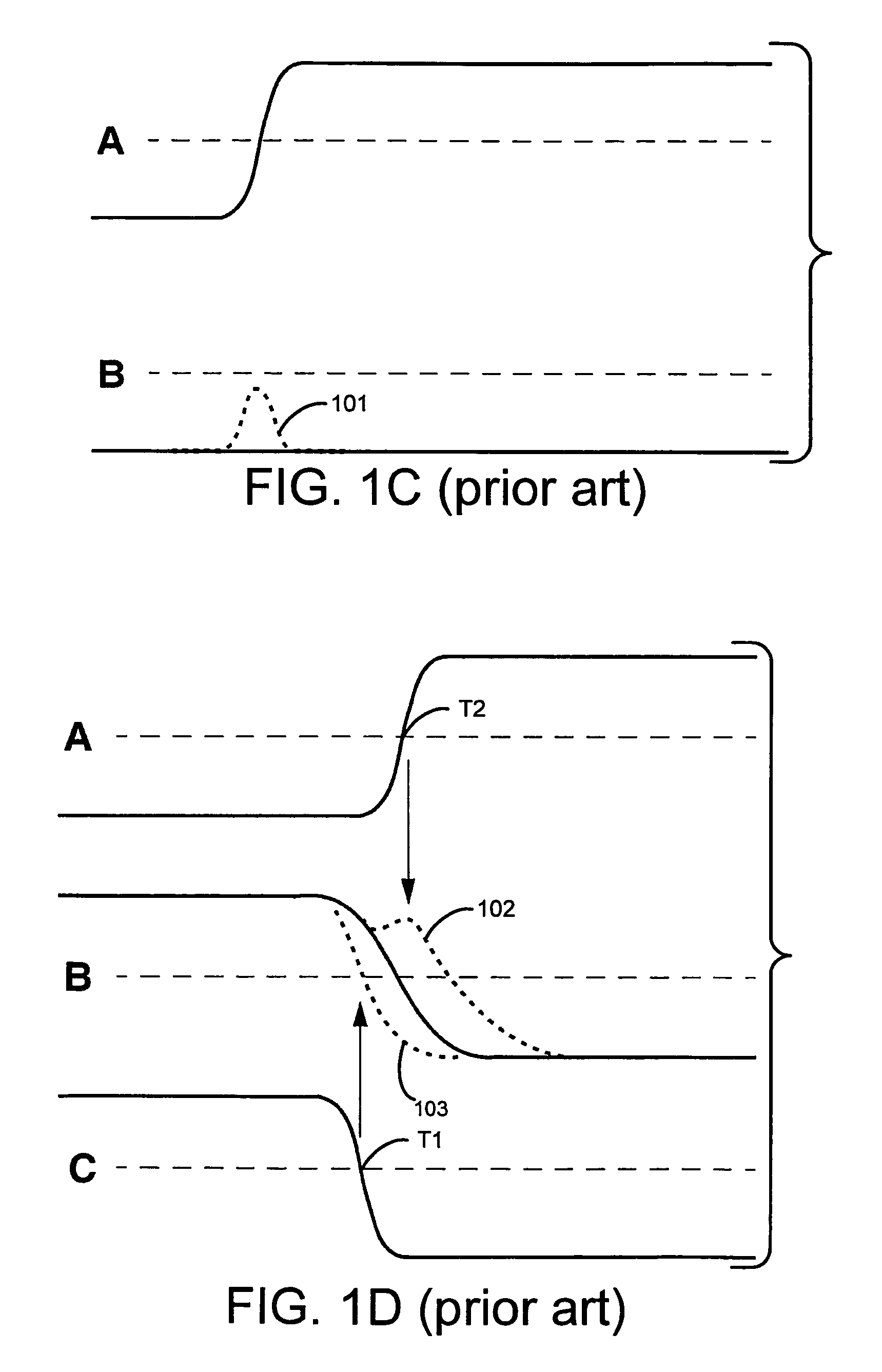

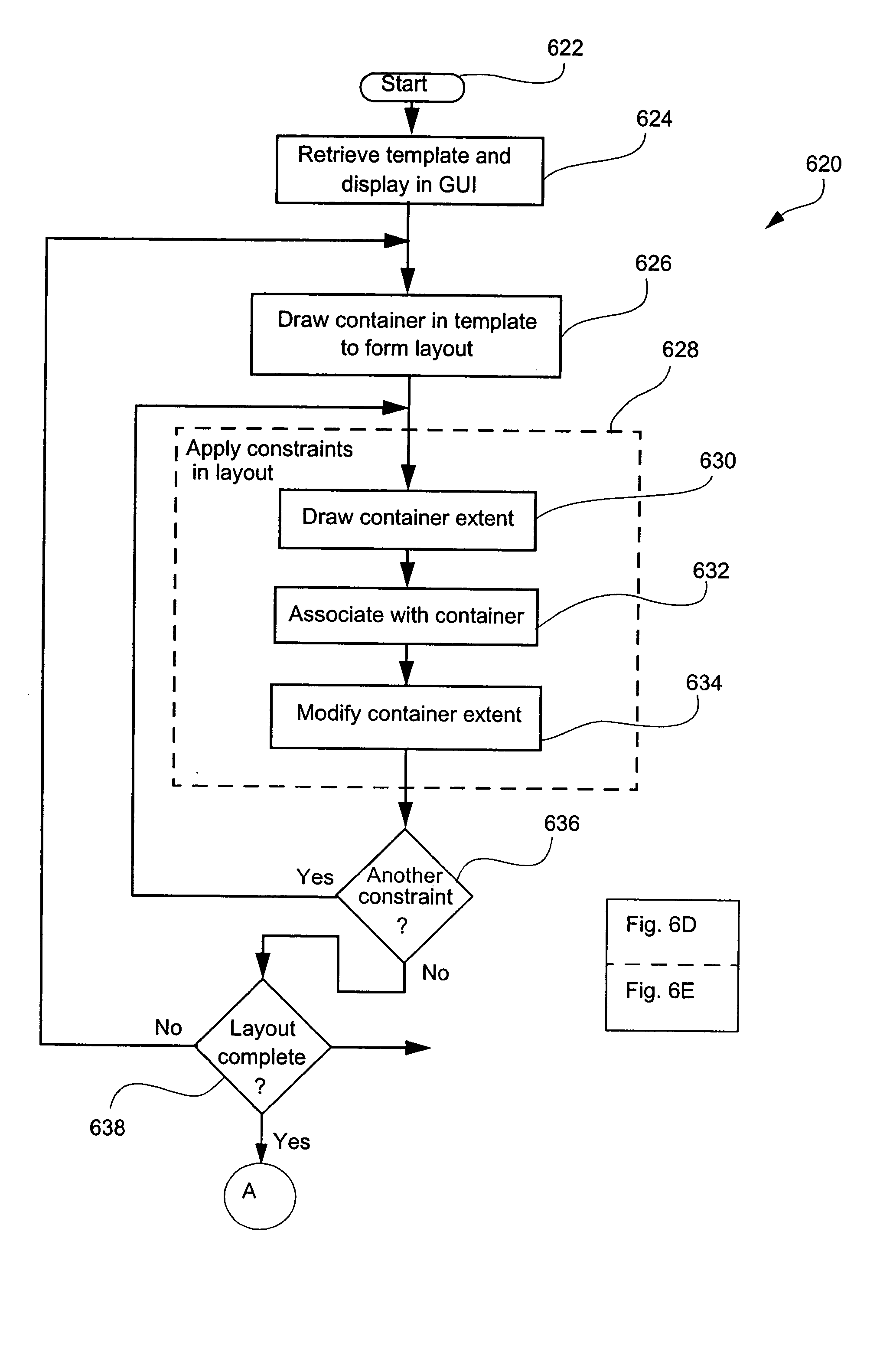

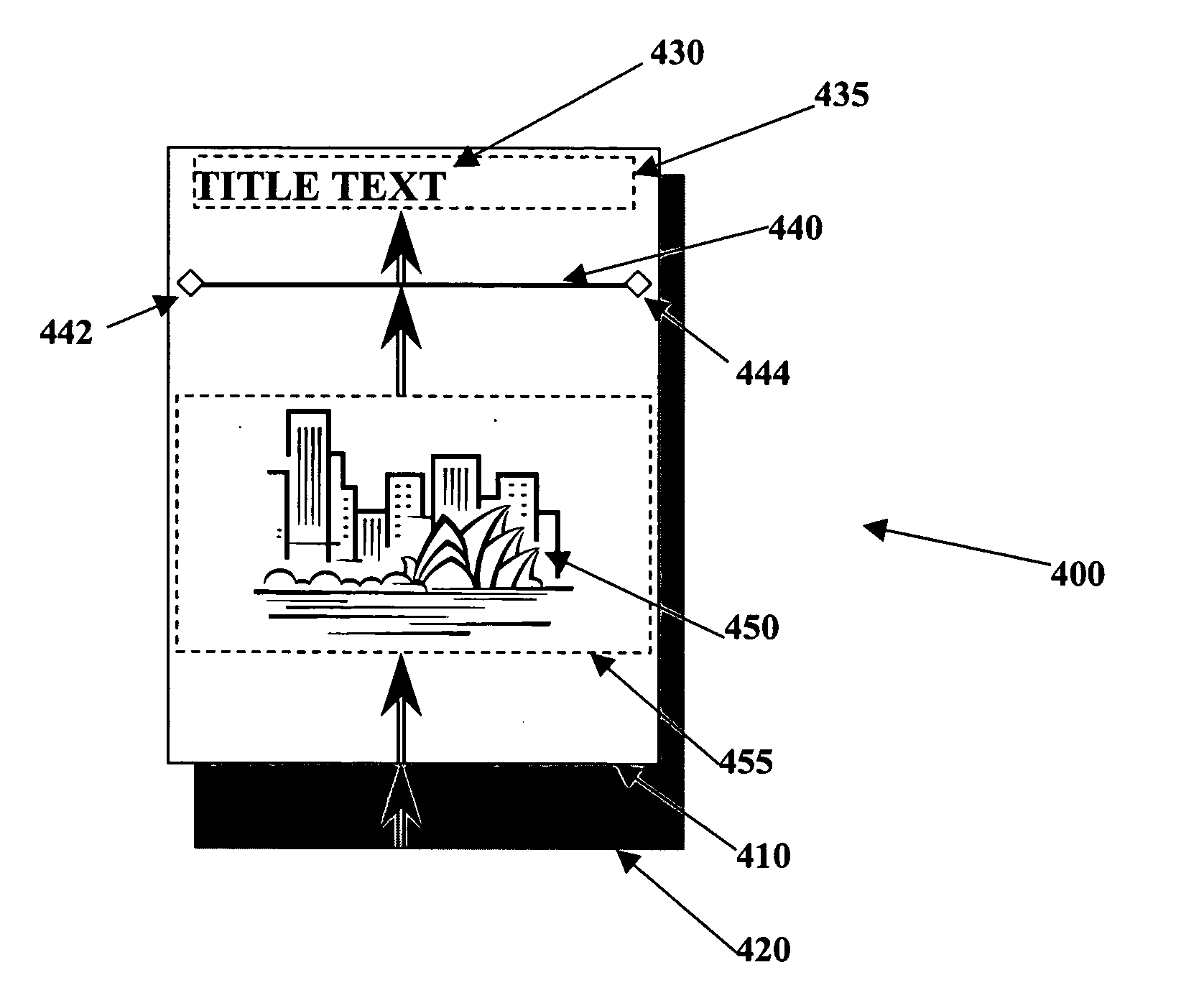

Methods and apparatus for variable document printing are disclosed in which a graphical user interface is configured to allow user manipulation of layout rules associated with content containers within a template for variable document generation. One method involves creating a layout for a variable data document based upon a template. The method firstly sets at least one container in the template to form the layout, and then establishes at least one constraint associated with each selected one of at least one feature of the container, the establishing including, for each feature, detecting a user instigated selection of the corresponding feature. The layout is then modified to thereby generate the document by placing content into the containers, wherein at least one dimension of the least one container and / or a position of the at least one container in the layout are varied based on a property of the placed content on a condition that each constraint in the layout is satisfied.

Owner:CANON KK

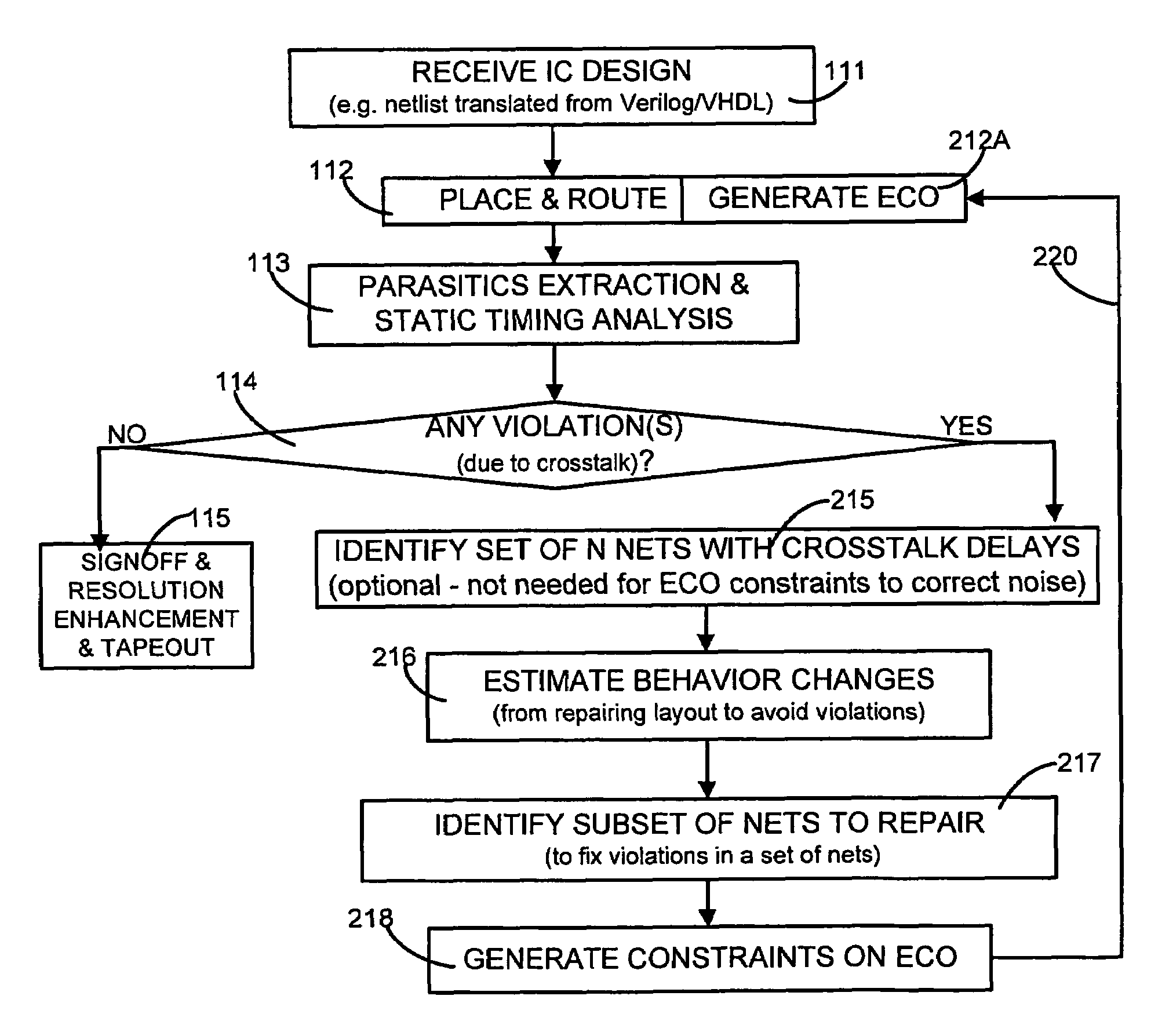

Generation of engineering change order (ECO) constraints for use in selecting ECO repair techniques

ActiveUS7454731B2CAD circuit designSoftware simulation/interpretation/emulationLayoutEngineering change order

Static timing and / or noise analysis are performed on a netlist of an integrated circuit, to estimate behavior of the netlist and to identify at least one violation by said behavior of a corresponding requirement thereon, such as setup time, hold time or bump height in a quiescent net. Thereafter, effect of engineering change order (ECO) to correct the violation are automatically analyzed, based on the layout, the parasitics, the timing and / or noise behavior, and the violation, followed by generation of a constraint on the behavior (called “ECO” constraint), such as a timing constraint and / or a noise constraint. Next, the ECO constraint is automatically used, e.g. in a place and route tool, to select an ECO repair technique, from several ECO repair techniques that can overcome the violation. The selected ECO repair technique is automatically applied to the layout, to generate a modified layout which does not have the violation.

Owner:SYNOPSYS INC

Document layout method

InactiveUS20050094206A1Visual presentation using printersNatural language data processingGraphical user interfaceAlgorithm

Methods and apparatus for variable document printing are disclosed in which a graphical user interface is configured to allow user manipulation of layout rules associated with content containers within a template for variable document generation. One method involves laying out (626) container objects (407, 408) forming part of a template (624) intended for a variable data document. The objects each have a rectangular boundary in two-dimensional space, and the method comprises detecting an operation (628, 2800) to modify a position of at least one edge of at least one of the objects. Then, rules of association between edges of the objects having a corresponding orientation to the one edge are identified. A position of at least the one edge is then modified whilst observing the rules of association between all the correspondingly oriented edges. Finally an objective function derived from the rules of association between the correspondingly oriented edges is minimized (3009) to thereby balance a layout of the objects in at least the dimension of modification. Other methods involve maintaining the objective function for a group of edges, the addition and removal of constraints in respect of correspondingly oriented edges, the removal, addition and then removal of constraints in modifying the width of a container, the calculation of text container sizes, and the creation of tables, particularly for text containers.

Owner:CANON KK

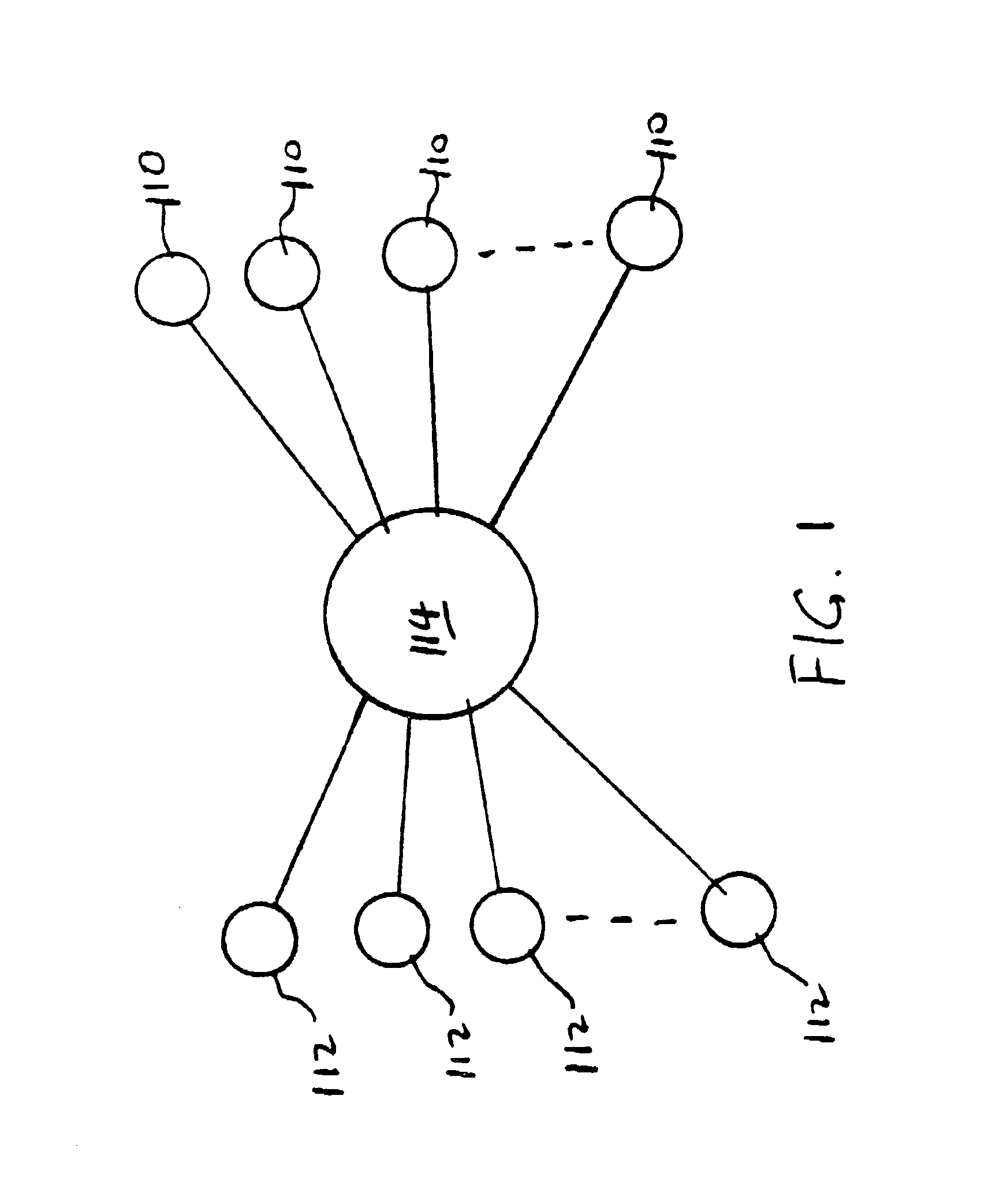

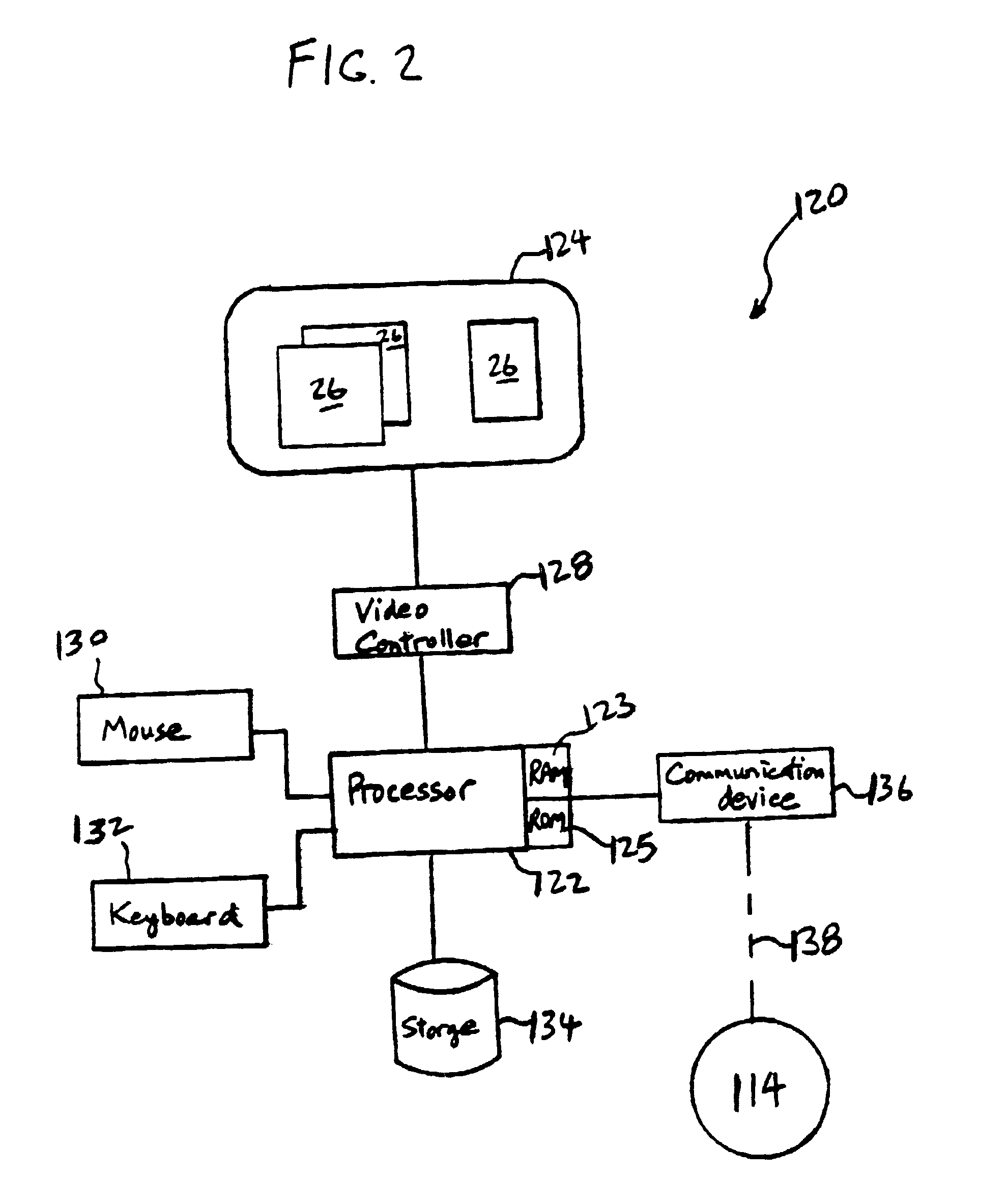

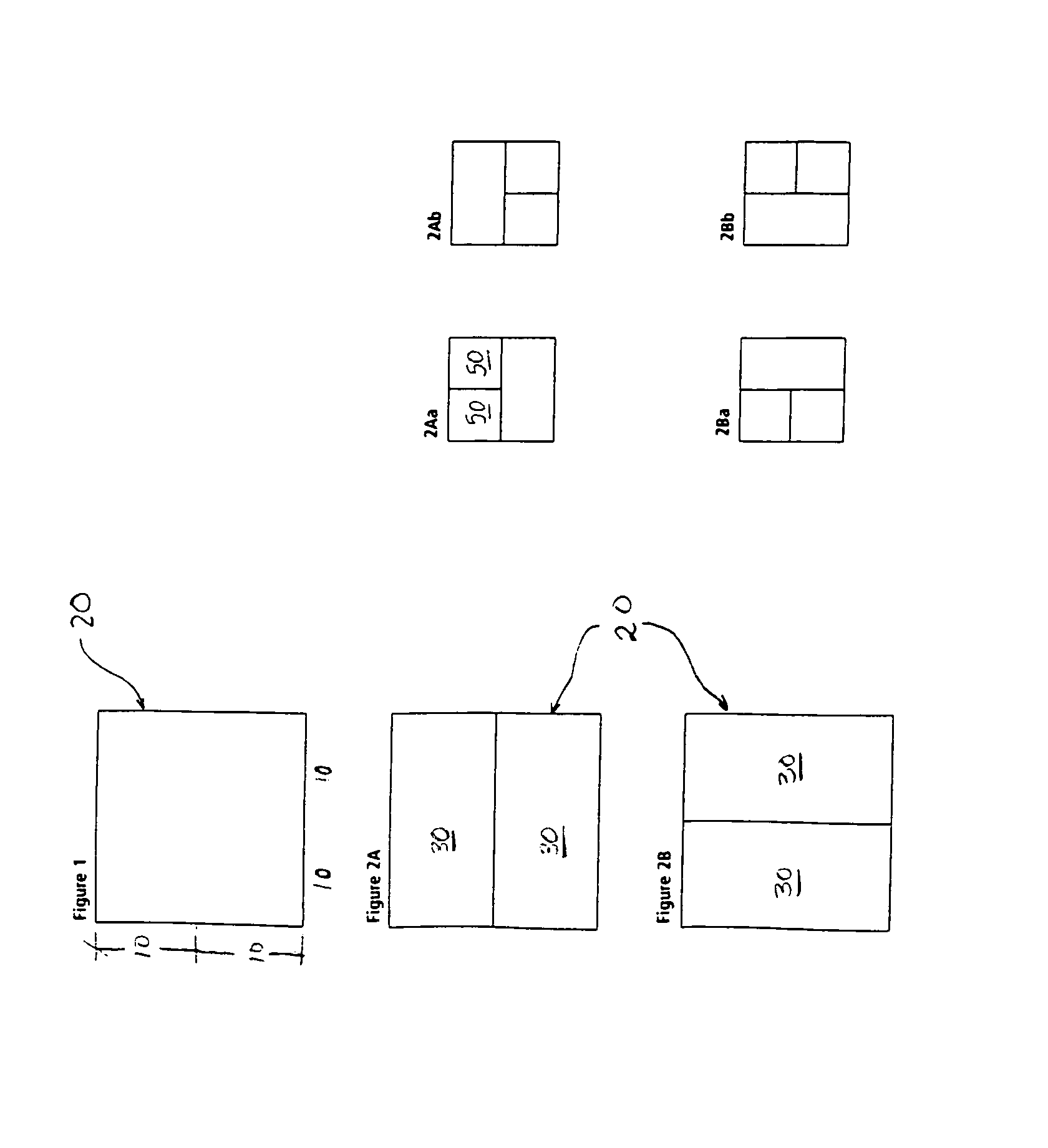

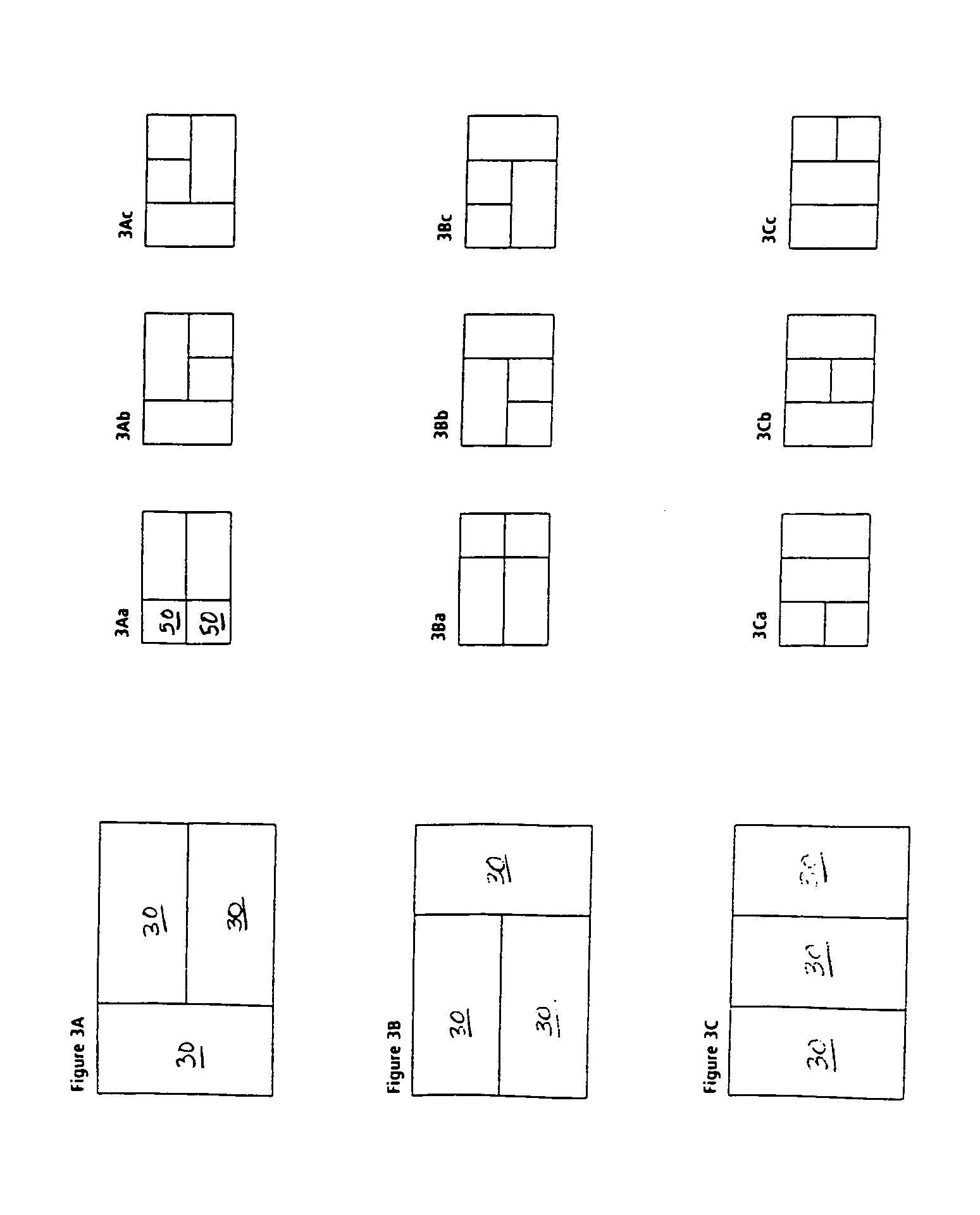

Method and system for computer screen layout based on a recombinant geometric modular structure

InactiveUS7124360B1Simplify informationSimple approachDigital computer detailsCommerceInterface designModular structure

A system comprising templates for entering and displaying information / data, such as in a Web page or browser, or in the interface for software or an operating system is disclosed. The screen is divided into an array of grids filling the entire area of the template. At least one, and preferably a majority of the grids are dimensioned based on the proportions of traditional Japanese tatami mats. The grids guide design decisions made by the interface designer or graphics designer in carving up and organizing a page, creating an underlying structure and framework for laying out and displaying the information / data. A primary application of the template is in interface and website design, in which the template automatically divides the screen into frames, each frame being used to enter, edit and / or display information on the computer screen or Web page. The system optionally allows an end-user to reposition the grids within the template, reorganizing the information / data to suit specific needs. The system also has application to the control of the directional flow of language, wherein repositionable grids are oriented to facilitate vertical or horizontal flow of text positioned within said grids.

Owner:HELFANND DRENTTEL

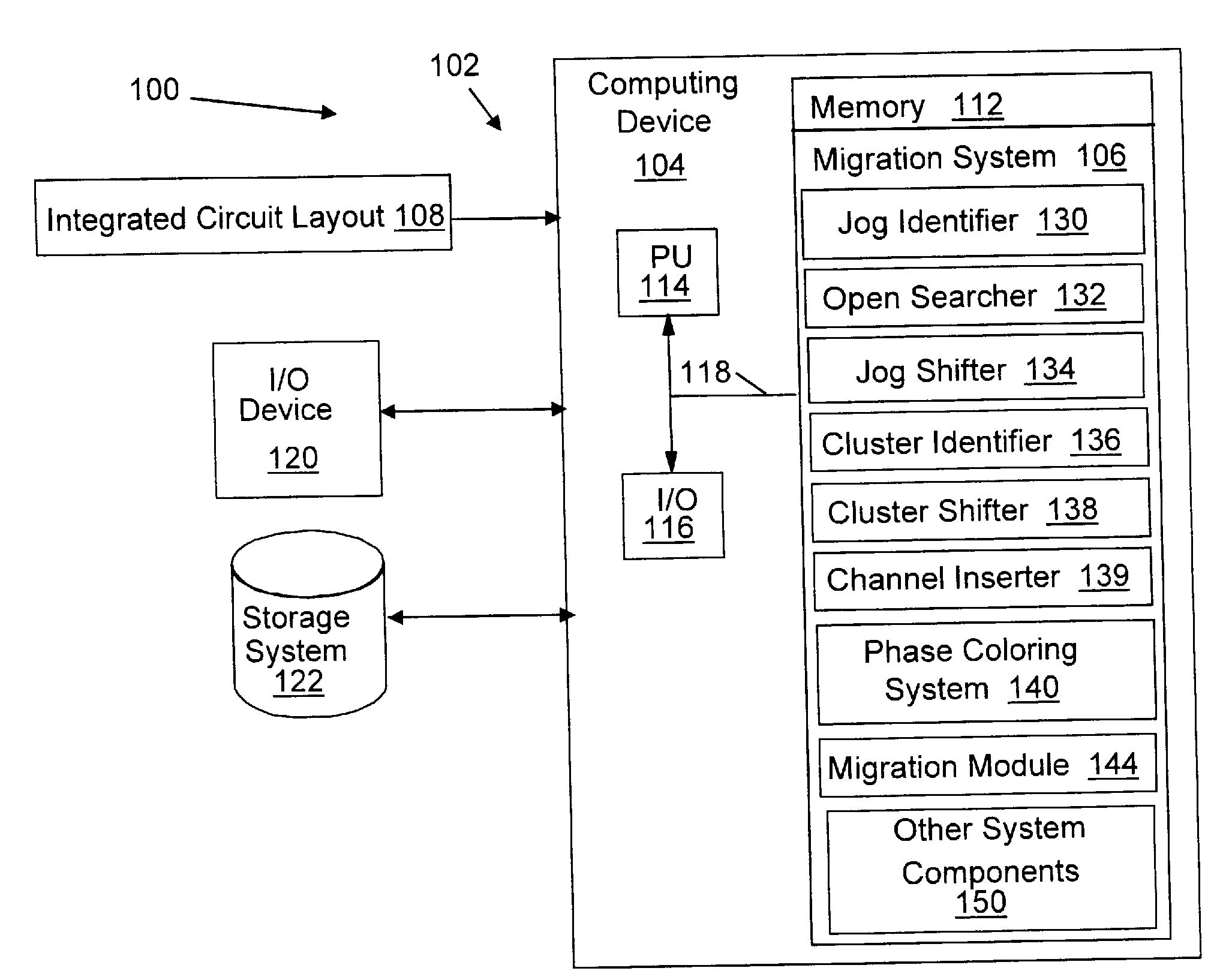

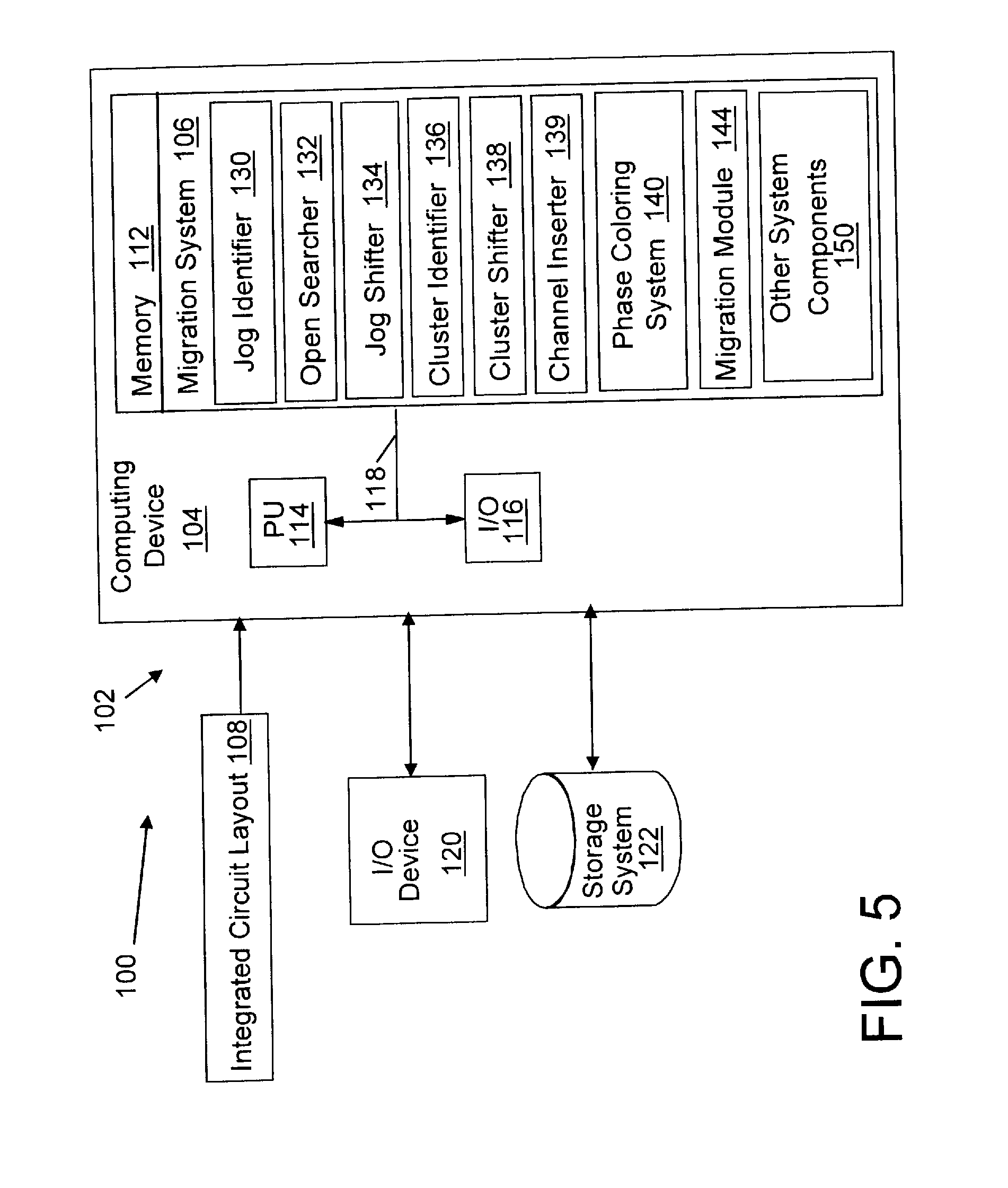

Migration of integrated circuit layout for alternating phase shift masks

InactiveUS20080244494A1Space is requiredCAD circuit designOriginals for photomechanical treatmentPhase shiftedProbable Case

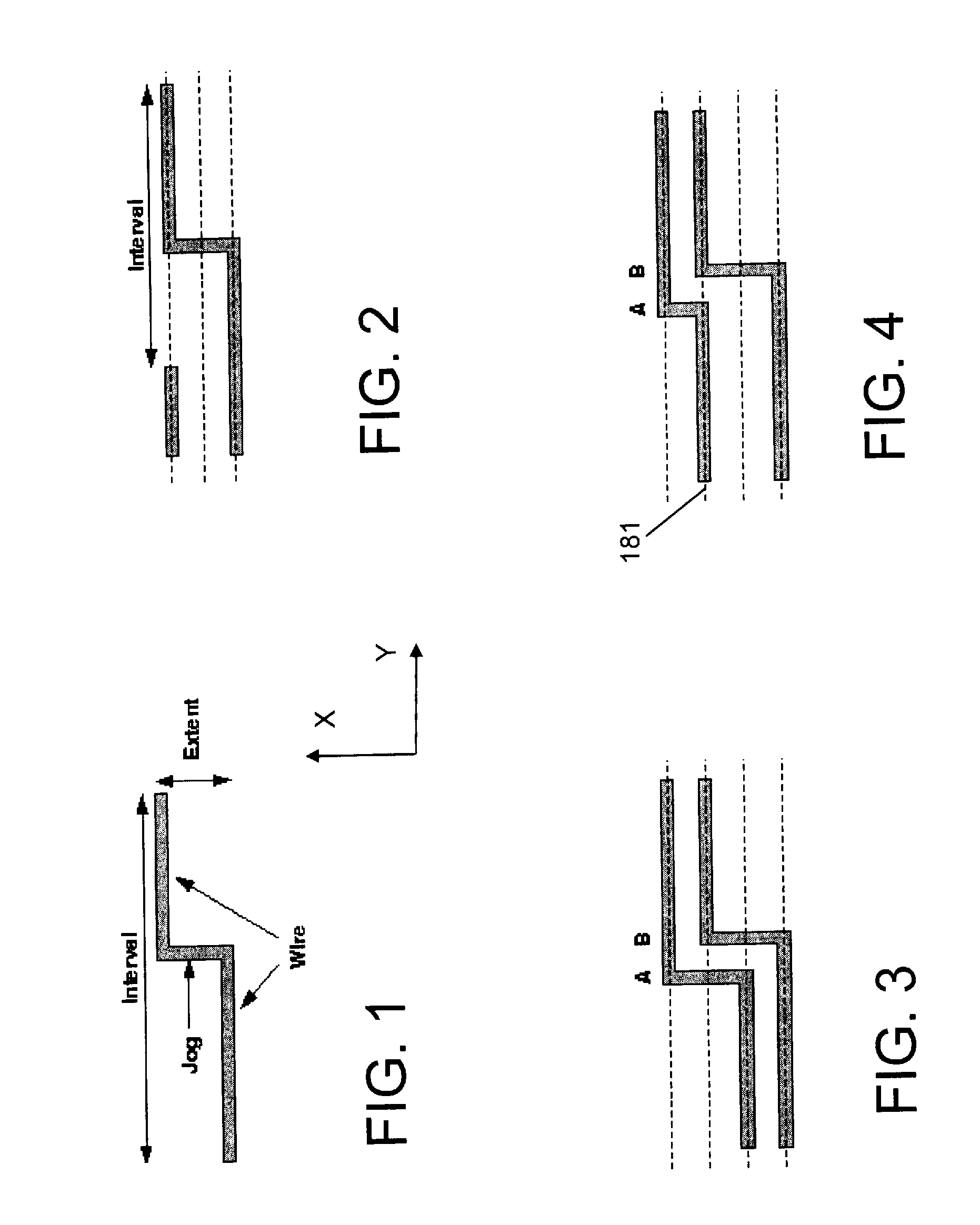

Method, system and program product for migrating an integrated circuit (IC) layout for, for example, alternating aperture phase shift masks (AltPSM), are disclosed. In order to migrate a layout to phase compliance, jogs are identified on a first (AltPSM) layer and shifted to another second layer. Isolated or clustered jogs are shifted into an open channel portions on the second layer where possible. Remaining clustered jogs are shifted into as few new channels as possible on the second layer. The jog removal process leaves unidirectional wires that can be trivially phase colored. Standard technology migration techniques are then used to legalize the results on the layers.

Owner:IBM CORP

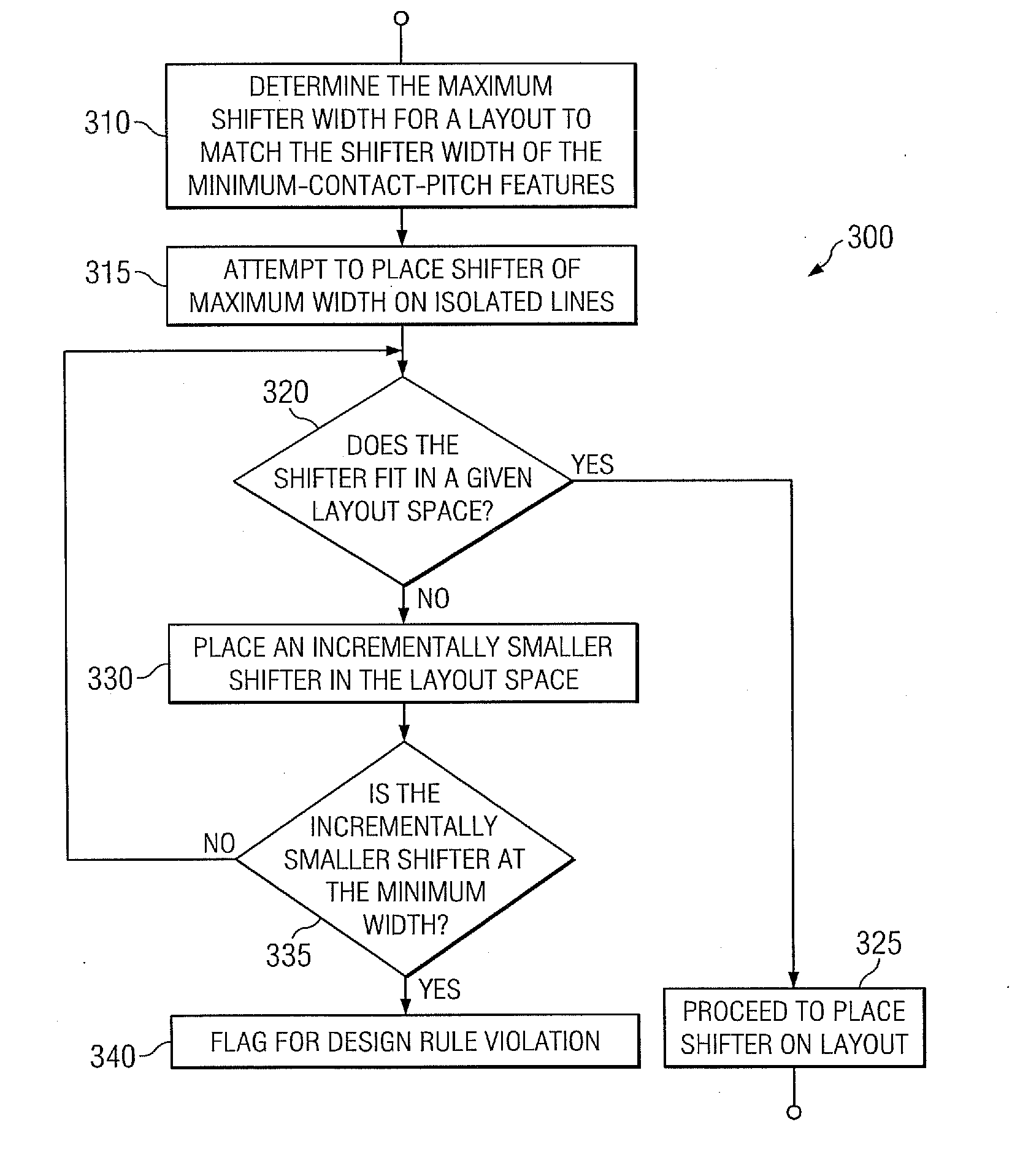

Maximum/variable shifter widths to allow alternating phase-shift implementation for dense or existing layouts

ActiveUS20080134128A1Reduce widthOriginals for photomechanical treatmentSpecial data processing applicationsPhase shiftedEngineering

In accordance with an embodiment of the invention, there is a method of designing a lithography mask. The method can comprise determining a maximum width of a shifter, wherein the maximum width corresponds to a width of a shifter for a first set of features and determining whether the shifter having the maximum width can be placed in a shifter space for a second set of features. The method can also comprise incrementally decreasing the width of the shifter to be placed into the shifter space for the second set of features when the shifter having the maximum width cannot be placed in the shifter space for a feature in the second set of features until an acceptable shifter width can be determined or until the shifter width is reduced to a predetermined minimum shifter width.

Owner:TEXAS INSTR INC

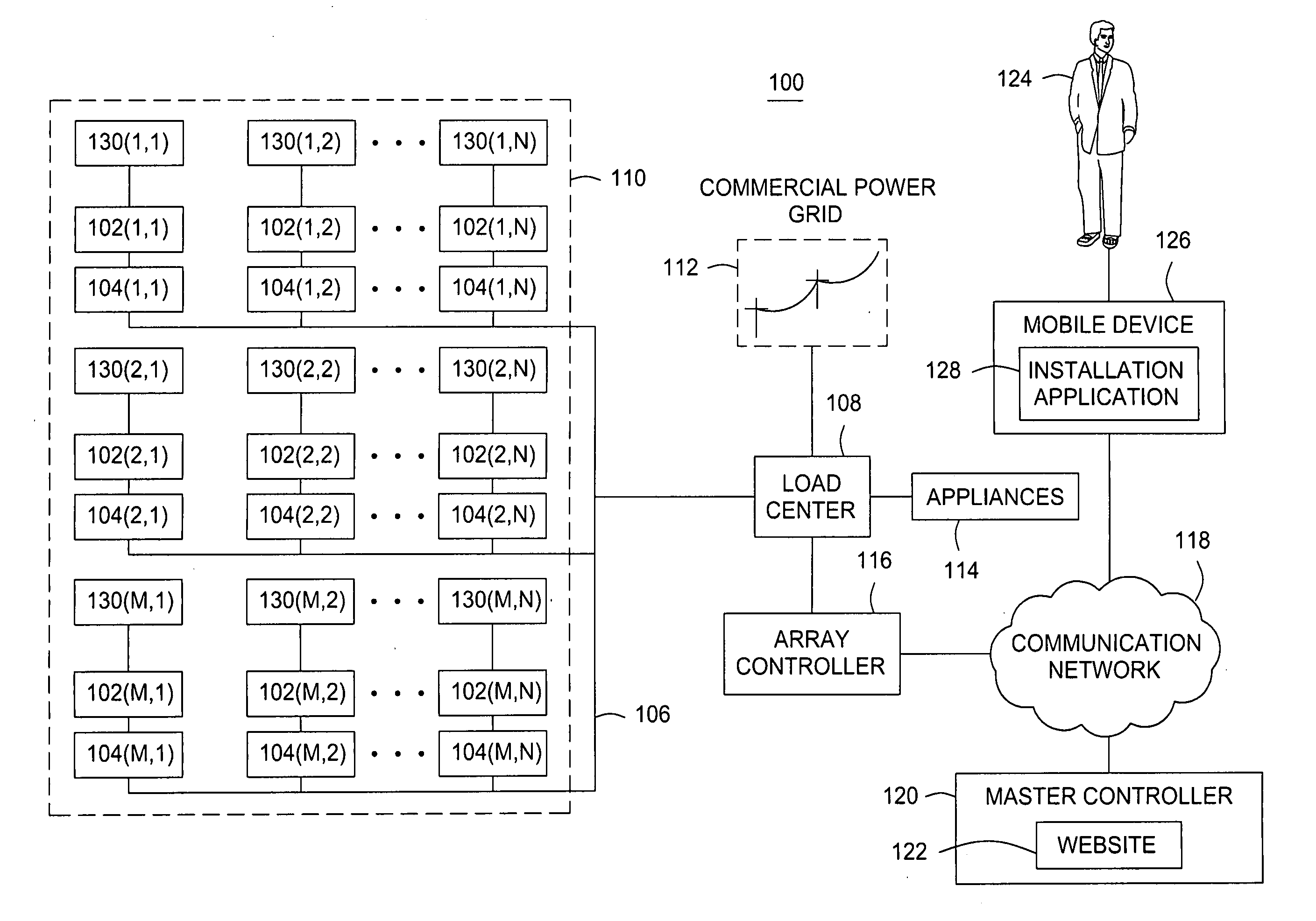

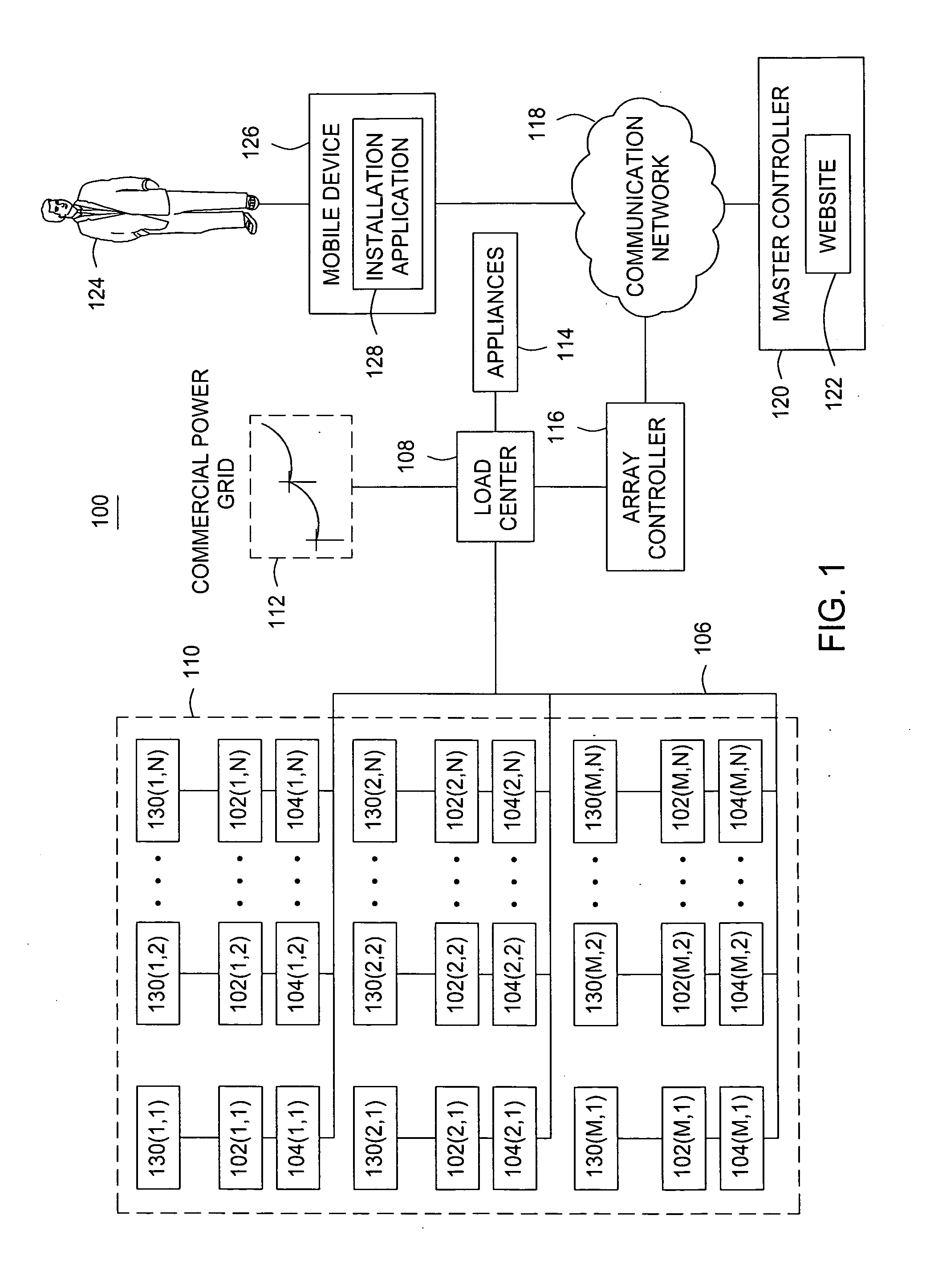

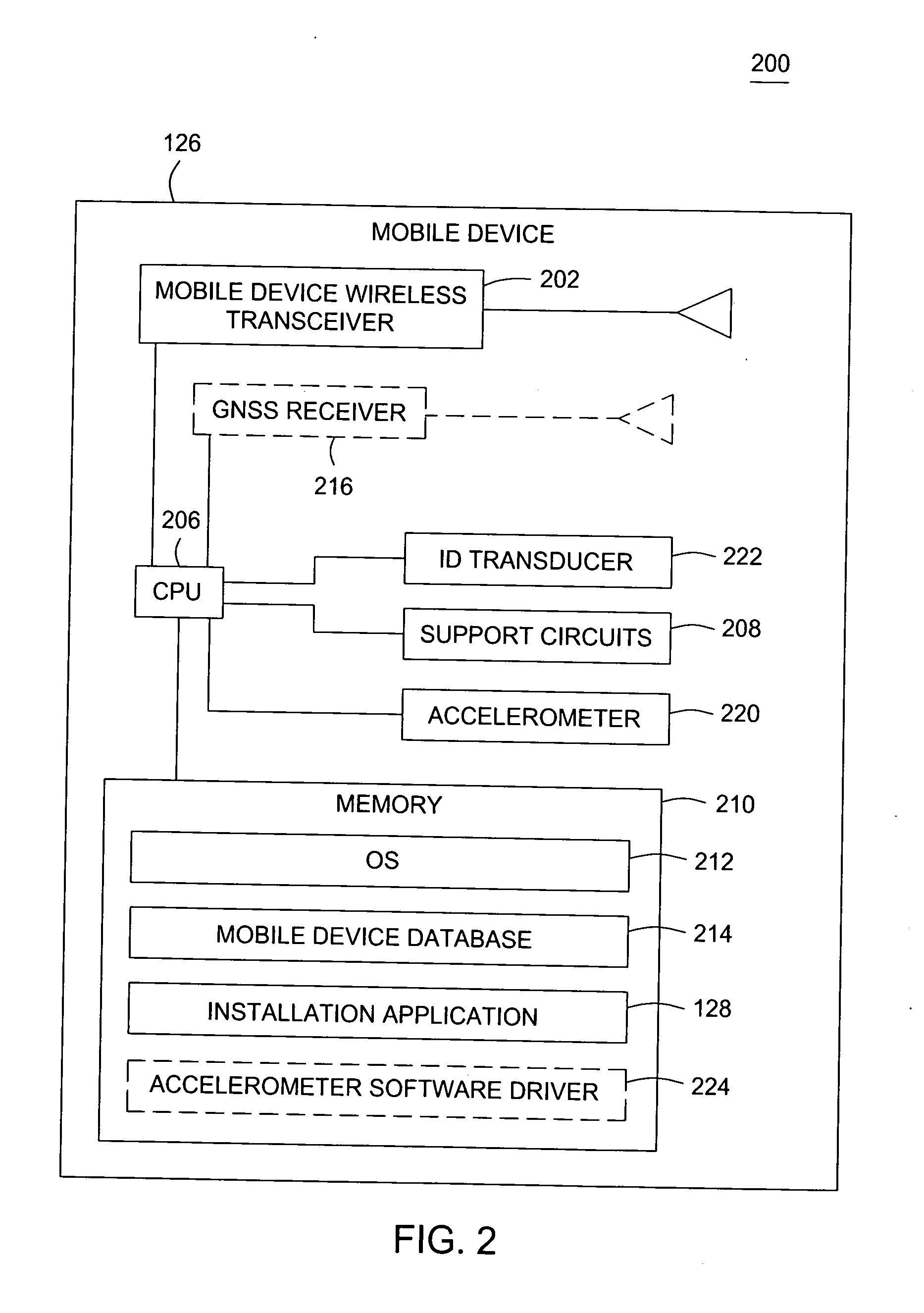

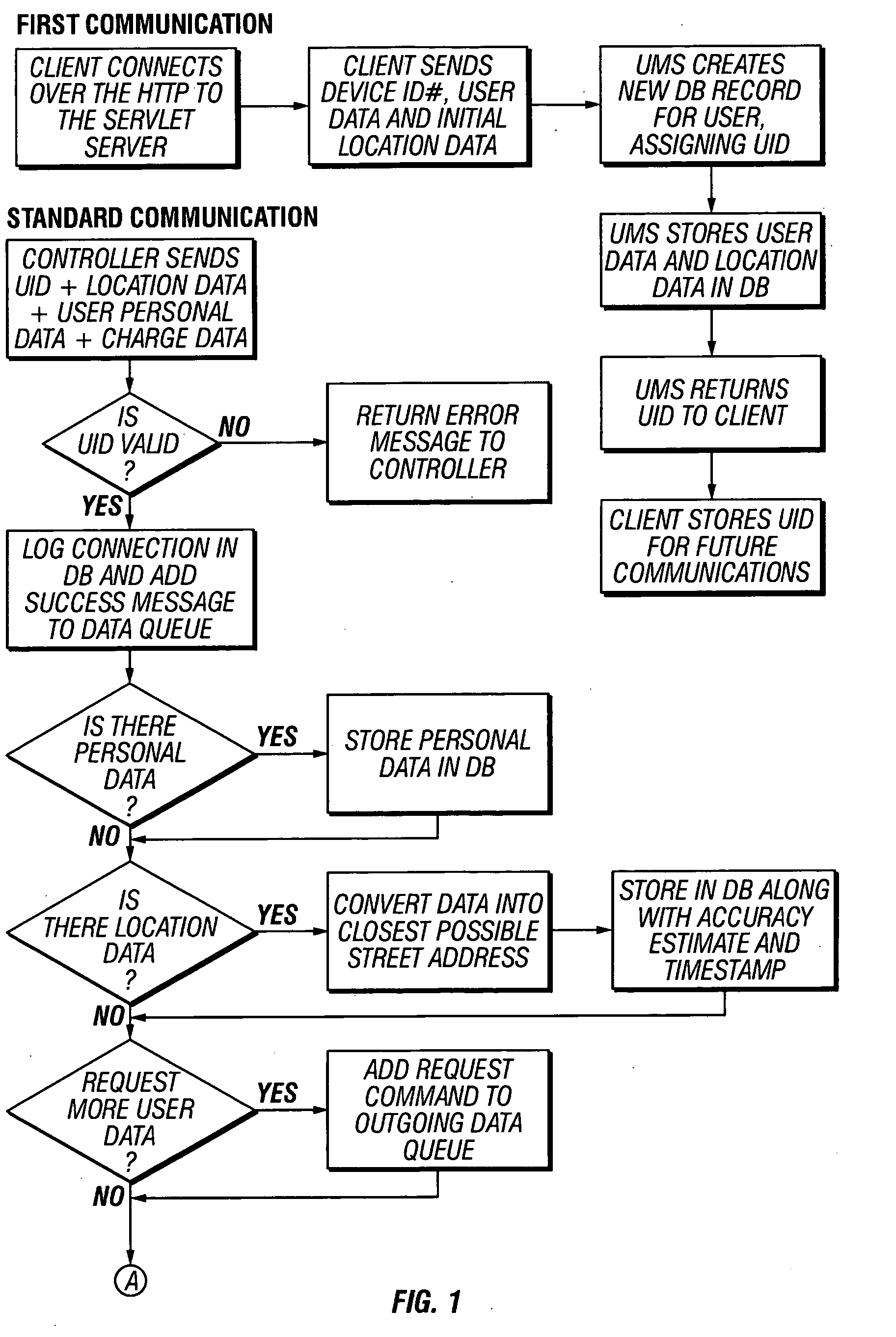

Method and apparatus for managing installation information

ActiveUS20110246338A1Direction finders using radio wavesPosition fixationSoftware engineeringMobile device

A method and apparatus for managing installation information. In one embodiment the method comprises obtaining, via an installation application on a mobile device comprising at least one processor, identification information for at least one component of an installation; obtaining, via the installation application, position information for the at least one component; and generating, via the installation application, a template for indicating a physical layout of at least a portion of the installation based on the identification information and the position information.

Owner:ENPHASE ENERGY

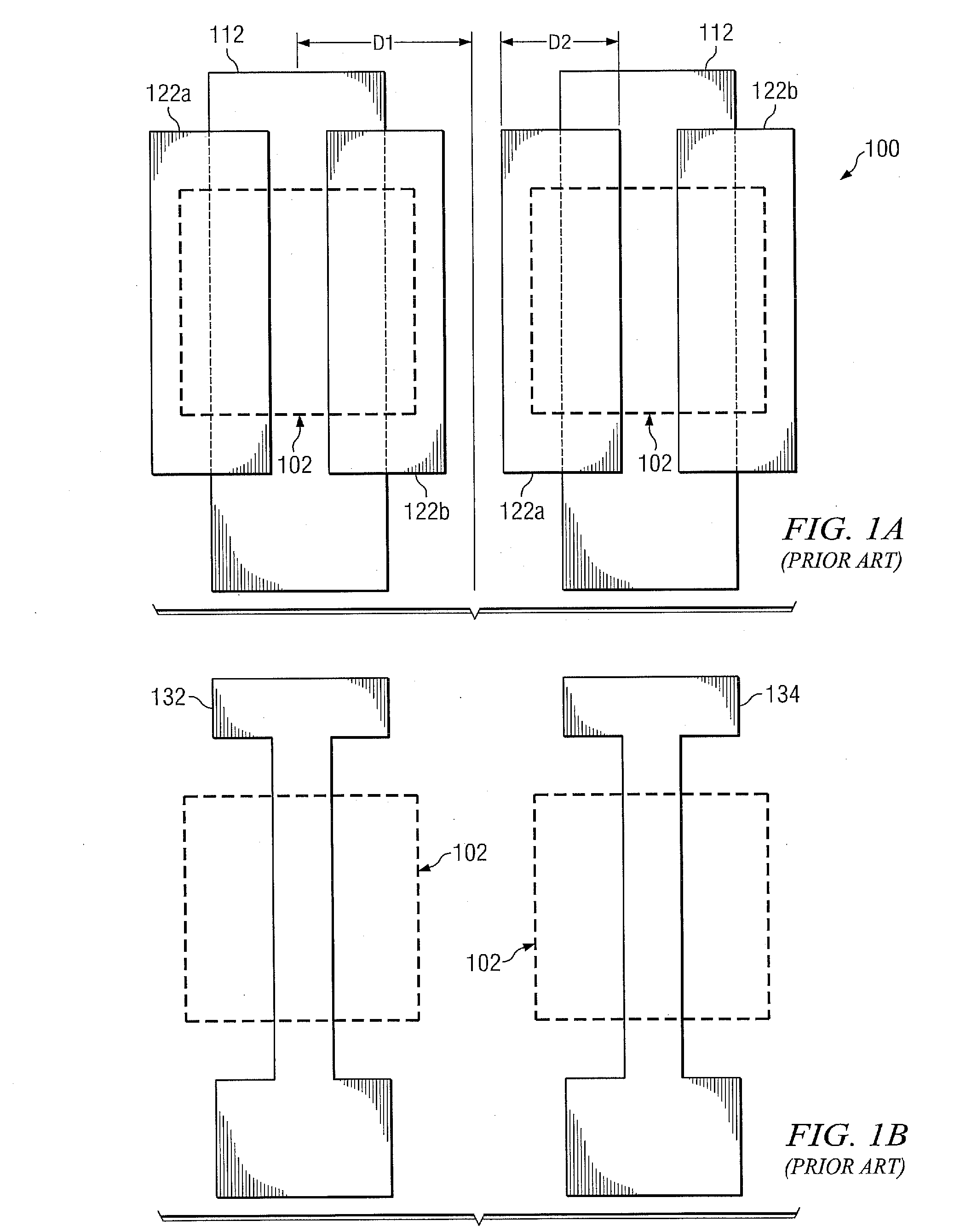

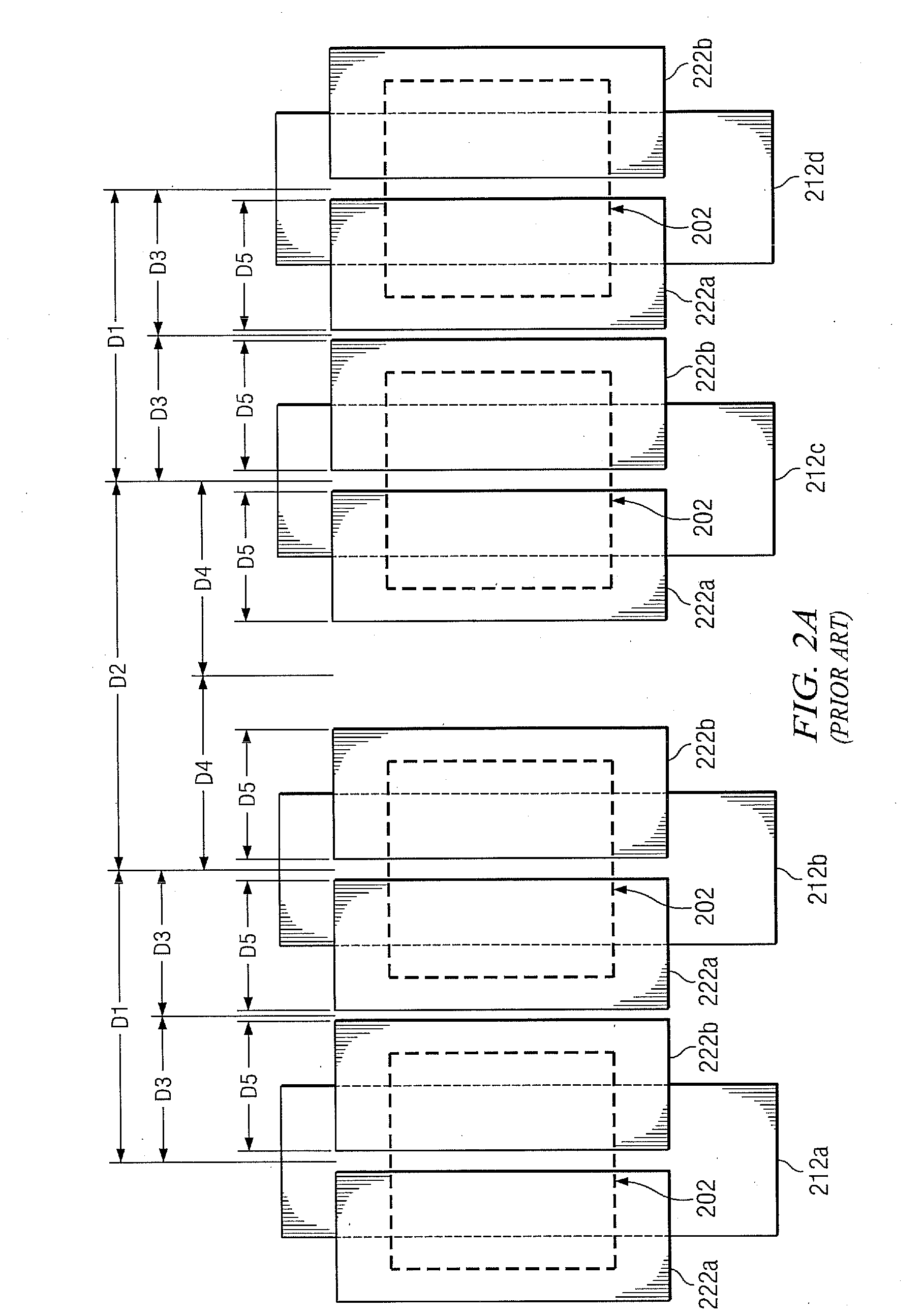

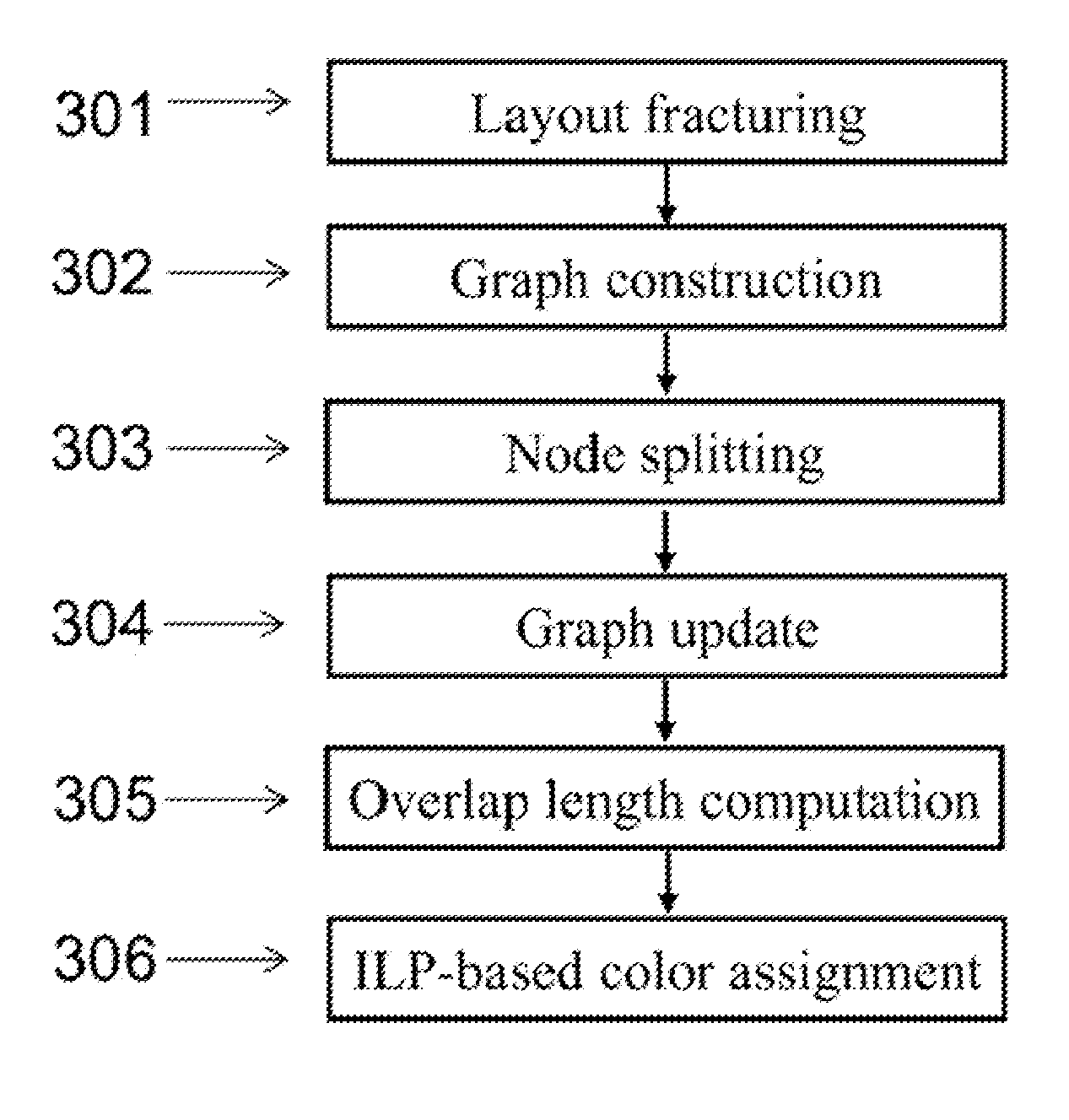

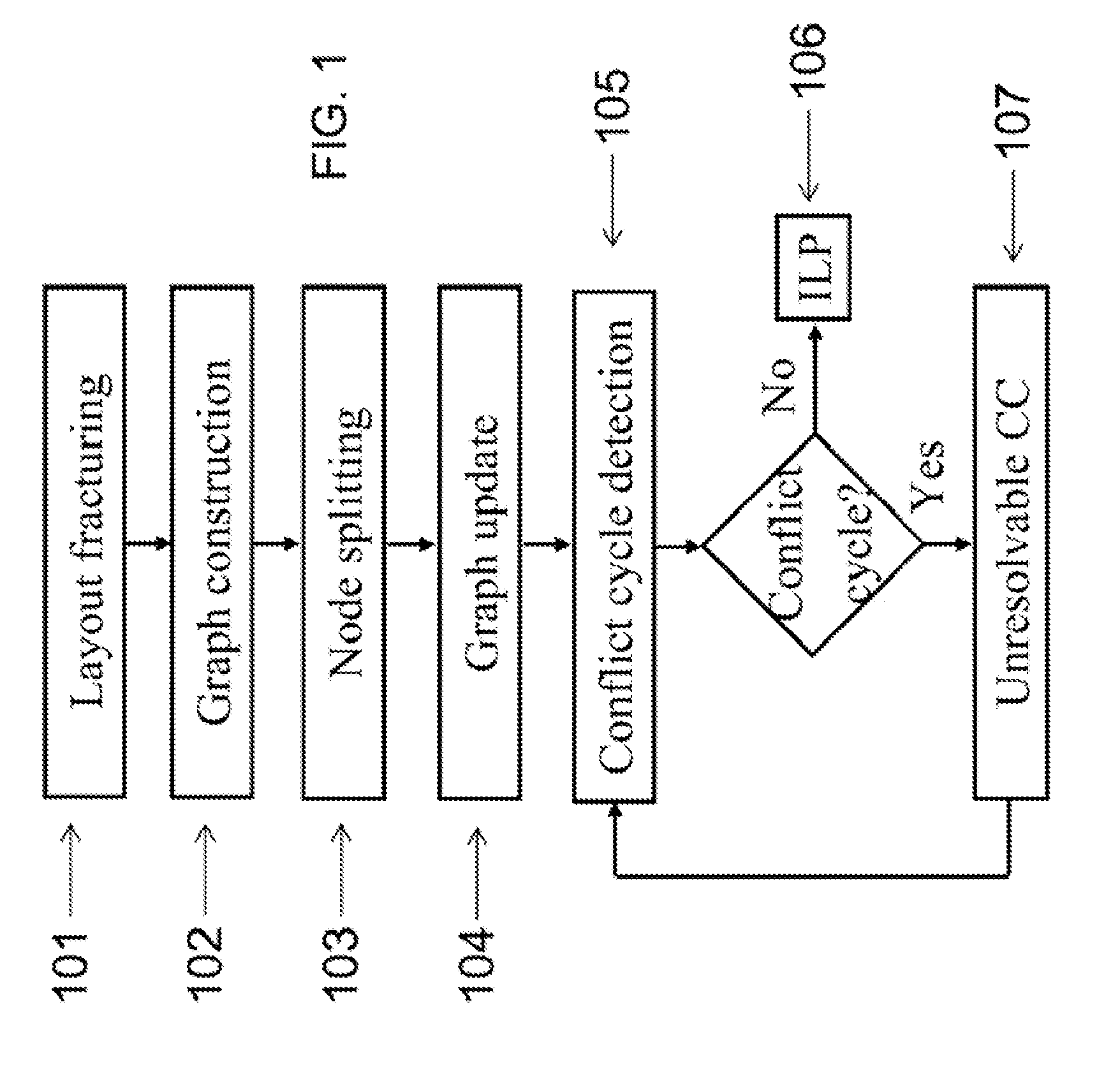

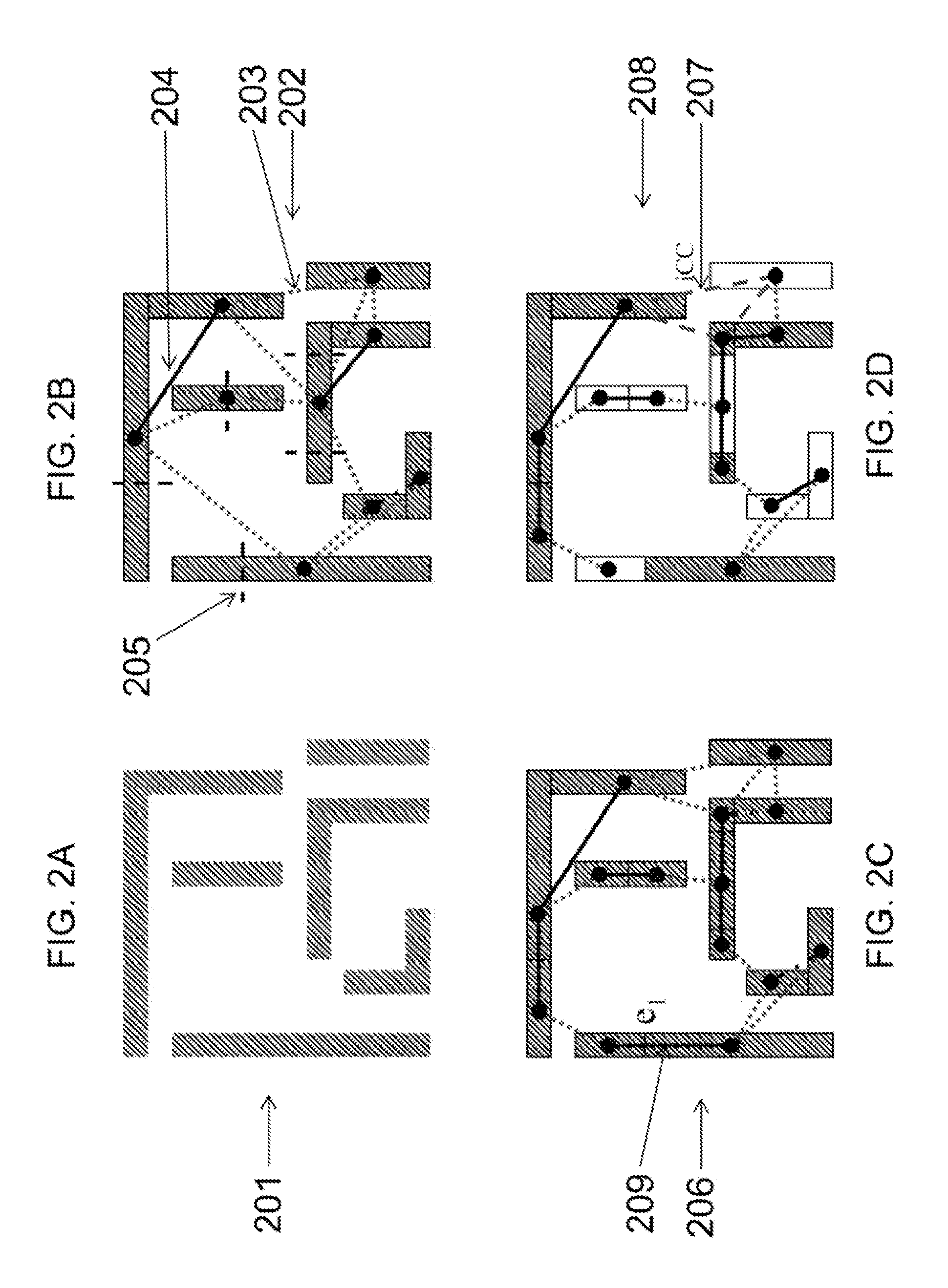

Layout decomposition for double patterning lithography

ActiveUS20110078638A1Low costAvoids small jogging line-endsOriginals for photomechanical treatmentComputer aided designLithographic artistDecomposition

The invention provides systems and methods for layout decomposition to produce exposure layouts that can be used to perform double patterning lithography (DPL). Preferred embodiment methods of the invention are executed by a computer and provide alternate methods for layout decomposition for double patterning lithography (DPL) using integer linear programming (ILP) formulations. Embodiments of the invention meet a key optimization goals, which is to reduce the total cost of layout decomposition, considering the abovementioned aspects that contribute to cost of prior conventional DPL techniques. Embodiments of the invention provide integer linear programming (ILP), phase conflict detection (PCD) and node election bipartization (NBD) formulations for the optimization of DPL layout decomposition, with a process-aware cost function that avoids small jogging line-ends, and maximizes overlap at dividing points of polygons. The cost function can also make preferential splits at landing pads, junctions and long runs.

Owner:RGT UNIV OF CALIFORNIA

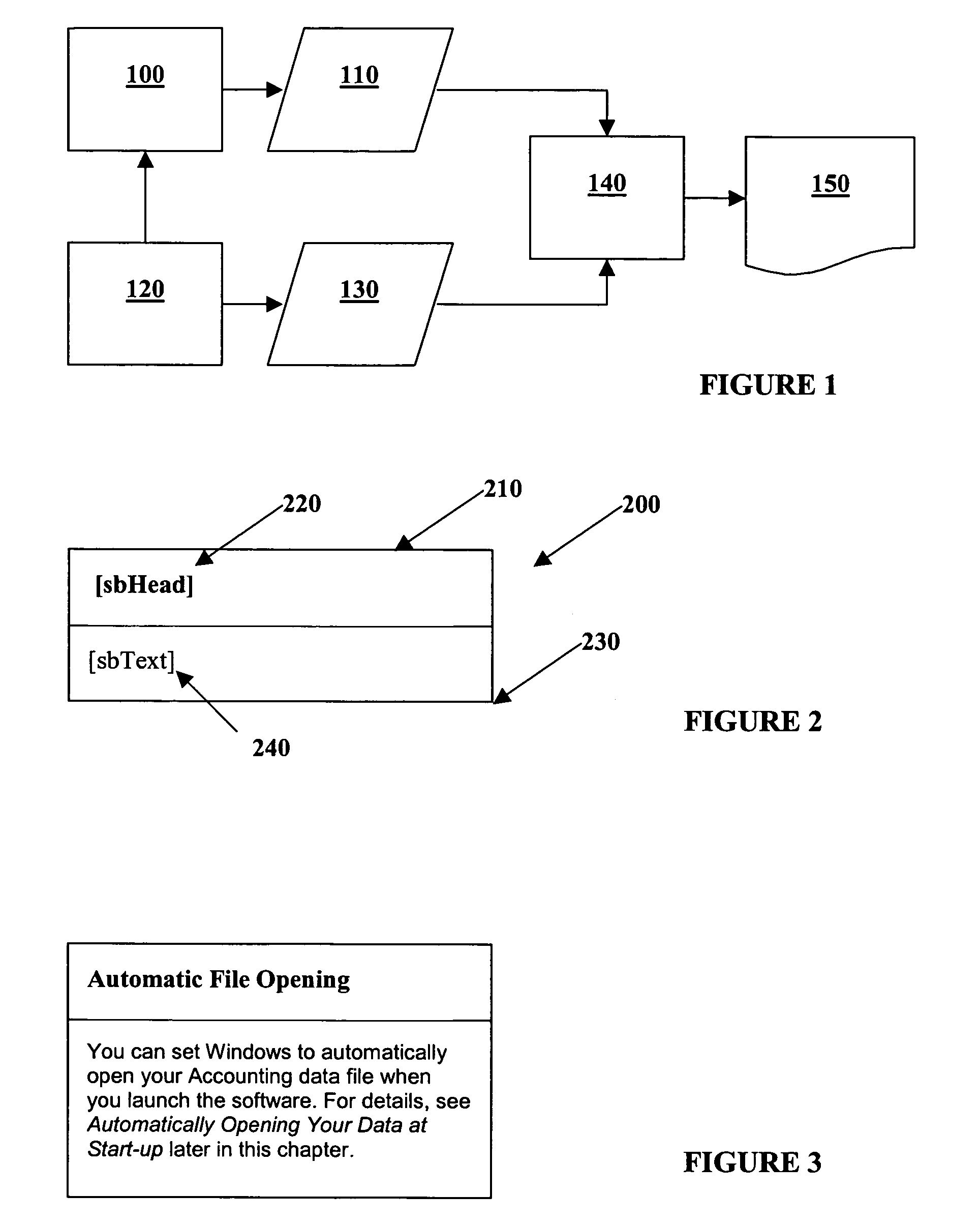

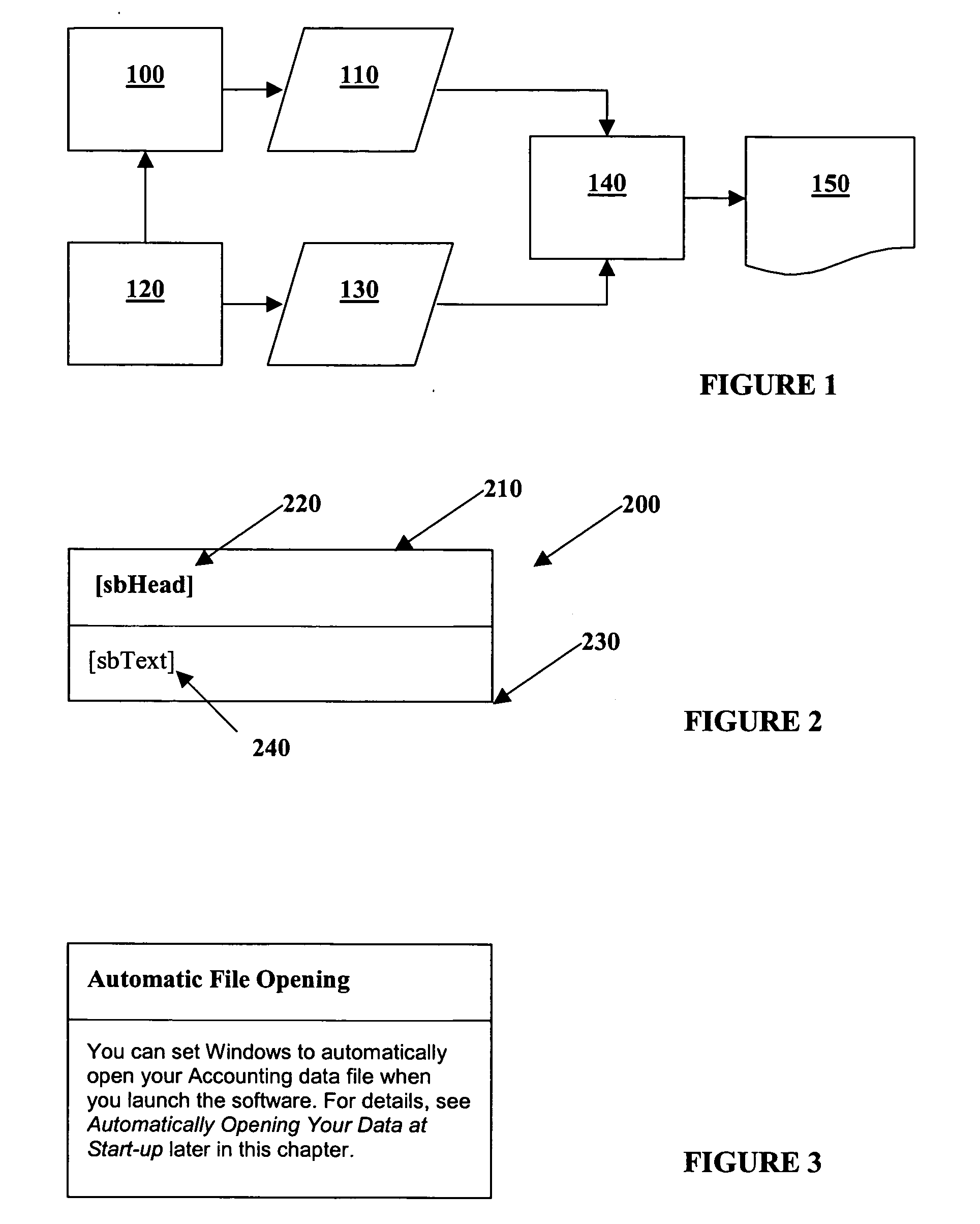

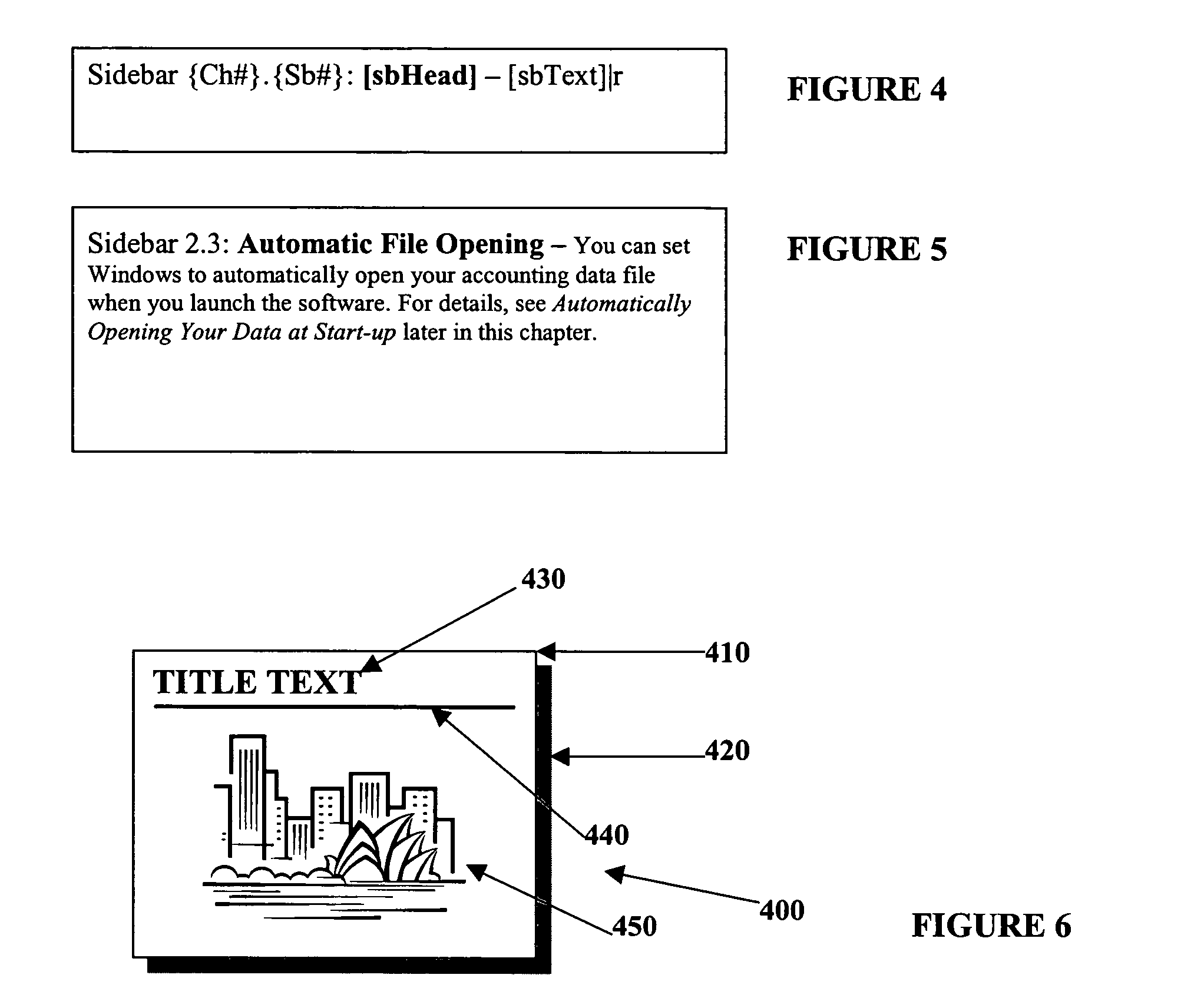

Method of formatting documents

ActiveUS7272789B2Flexible designFlexible presentationNatural language data processingSpecial data processing applicationsGraphicsRating system

Owner:TYPEFI SYST PTY LTD

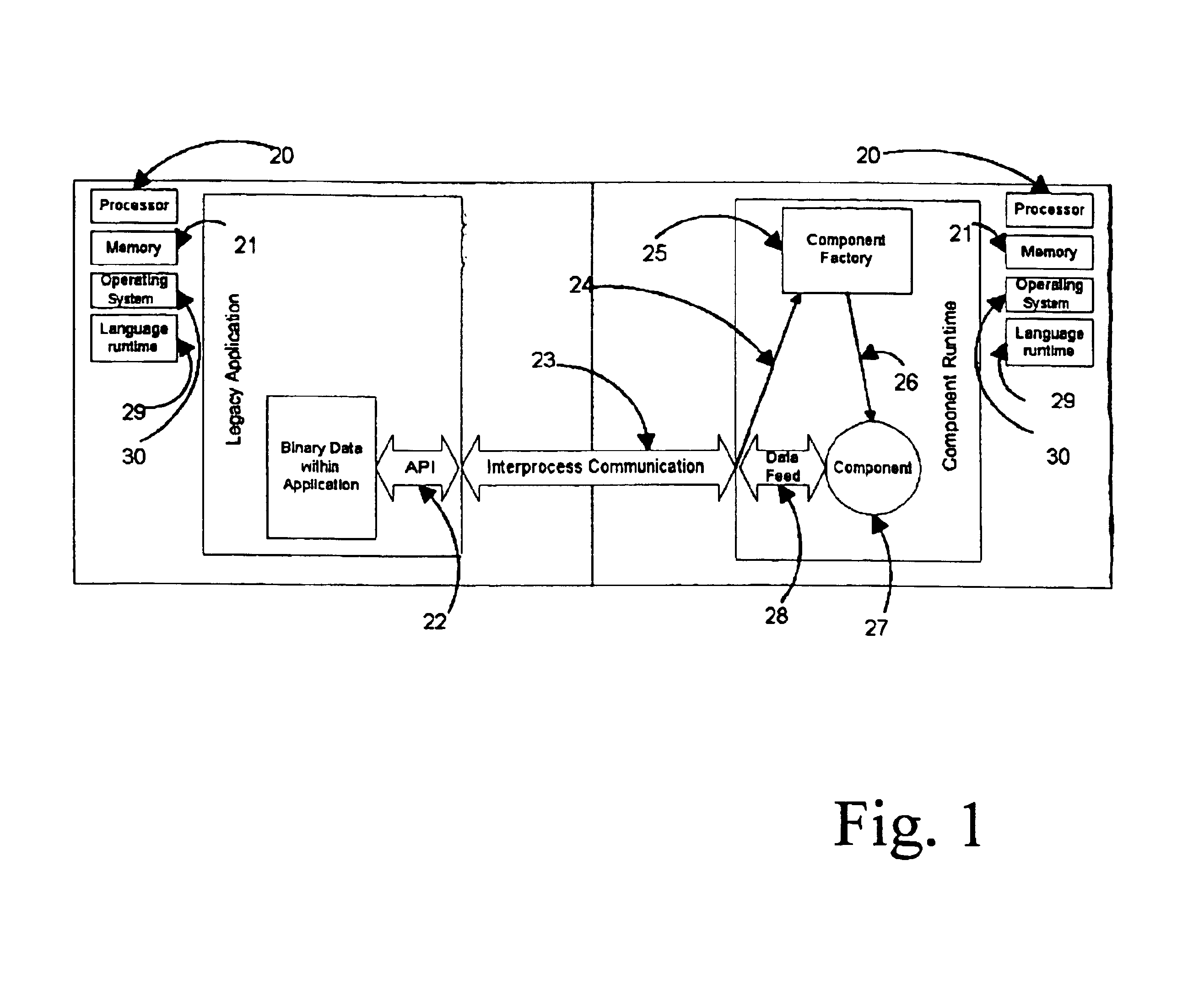

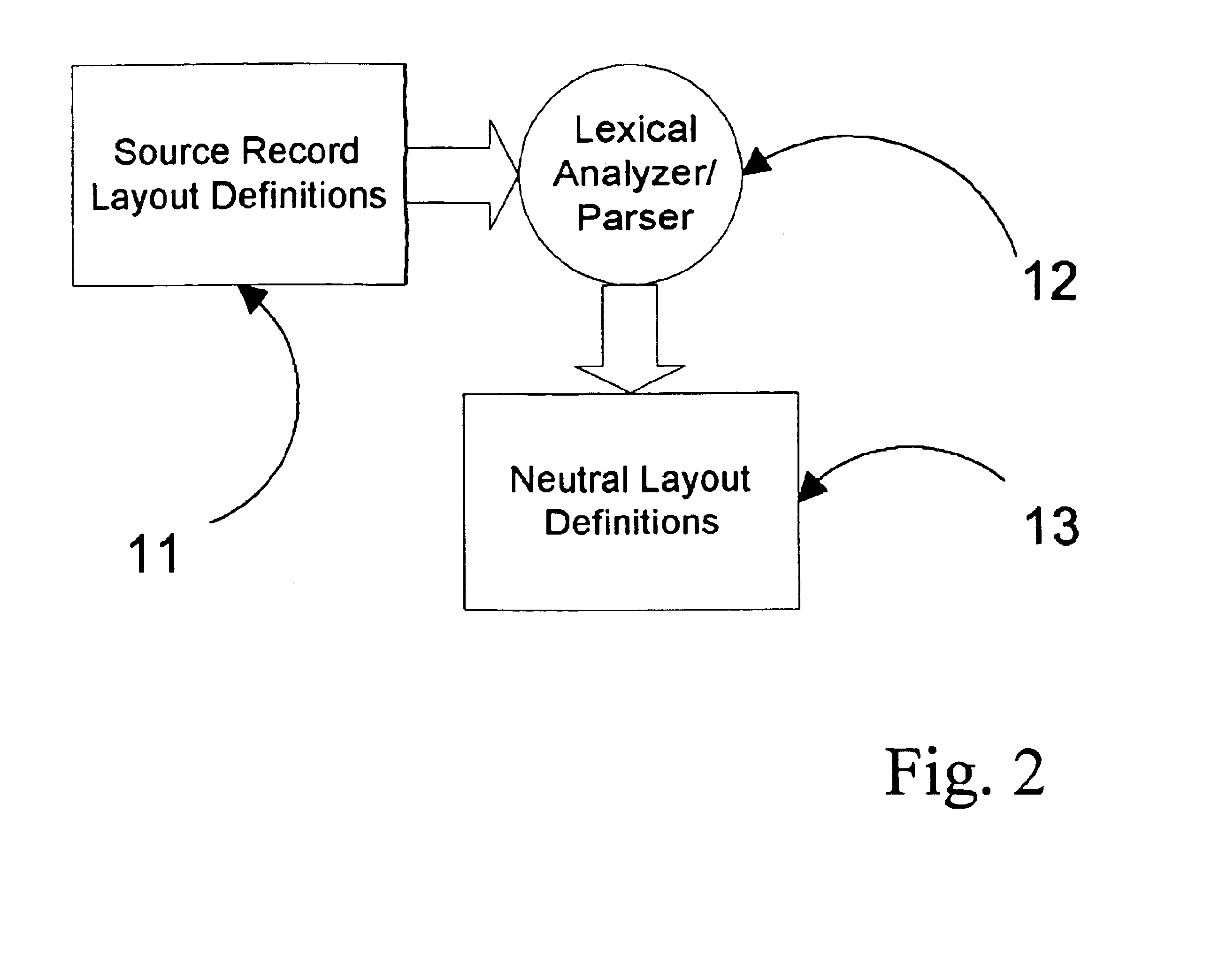

Method of accessing data and logic on existing systems through dynamic construction of software components

InactiveUS6931623B2Easy to reuseMultiprogramming arrangementsSoftware maintainance/managementBinary informationApplication software

A record layout in a legacy application is defined by the record definition in the source code of the language in which the application was written. For each record in a legacy application, the layout of the record is saved in a language-neutral and architecture neutral format in preparation for a runtime invocation. During runtime, for each record, the legacy application can send architecture-specific binary information as it exists in memory on the legacy computer to a component runtime environment that will construct a compatible object-oriented instance of a class to manipulate the information. Once the information is manipulated, the updated information can be represented to the original legacy application in an architecture-specific binary record layout.

Owner:TOUCHNET INFORMATION SYST

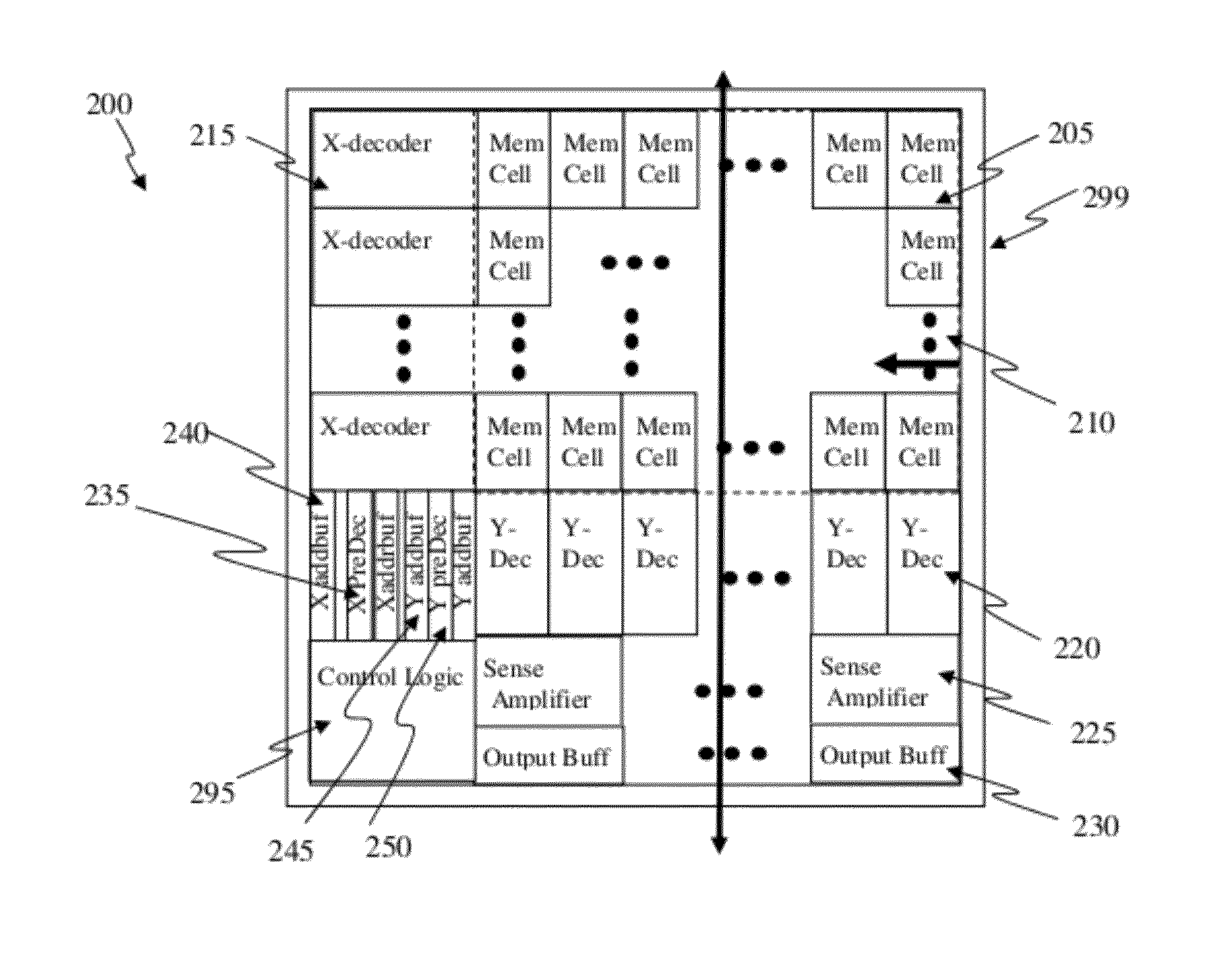

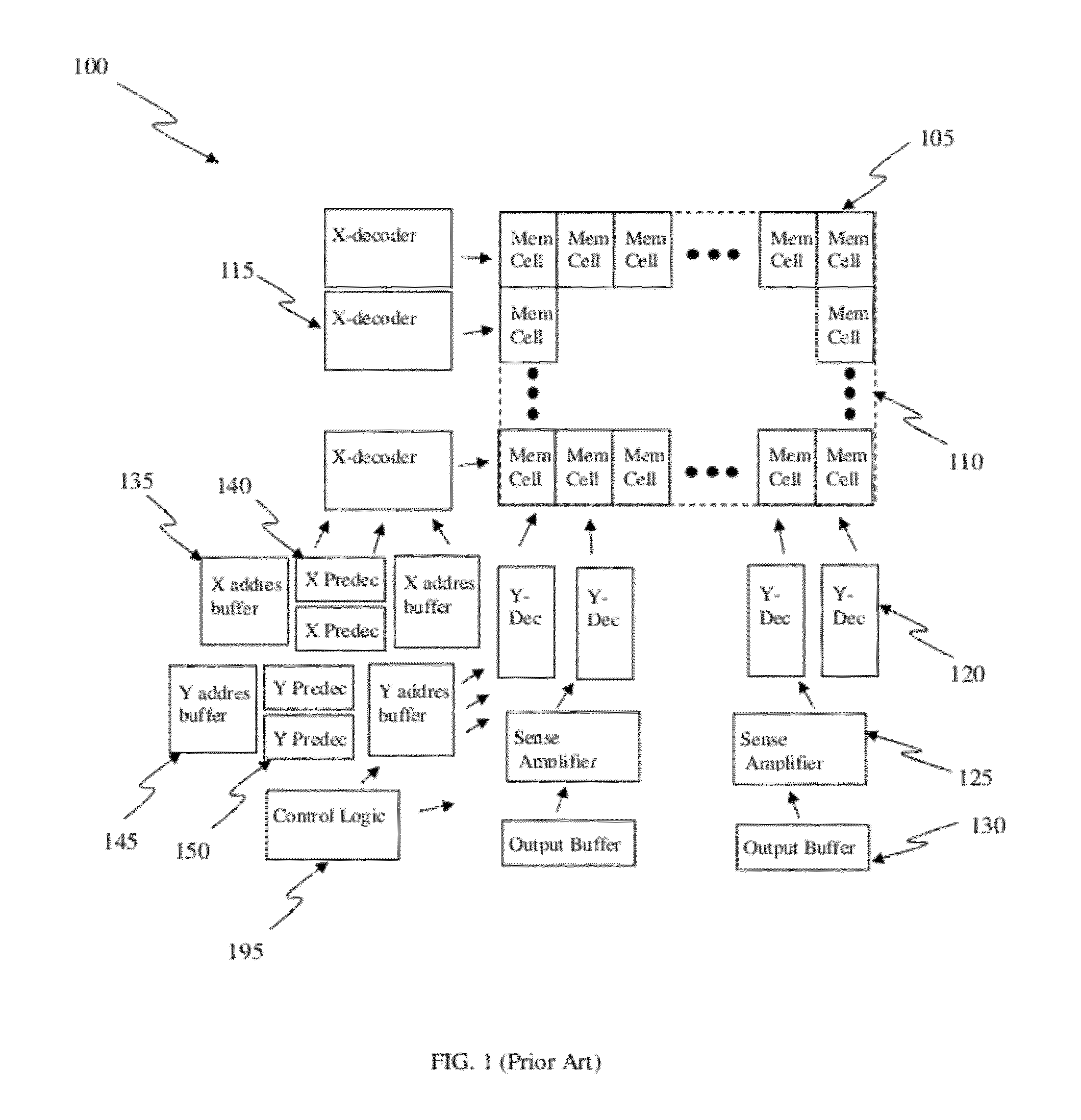

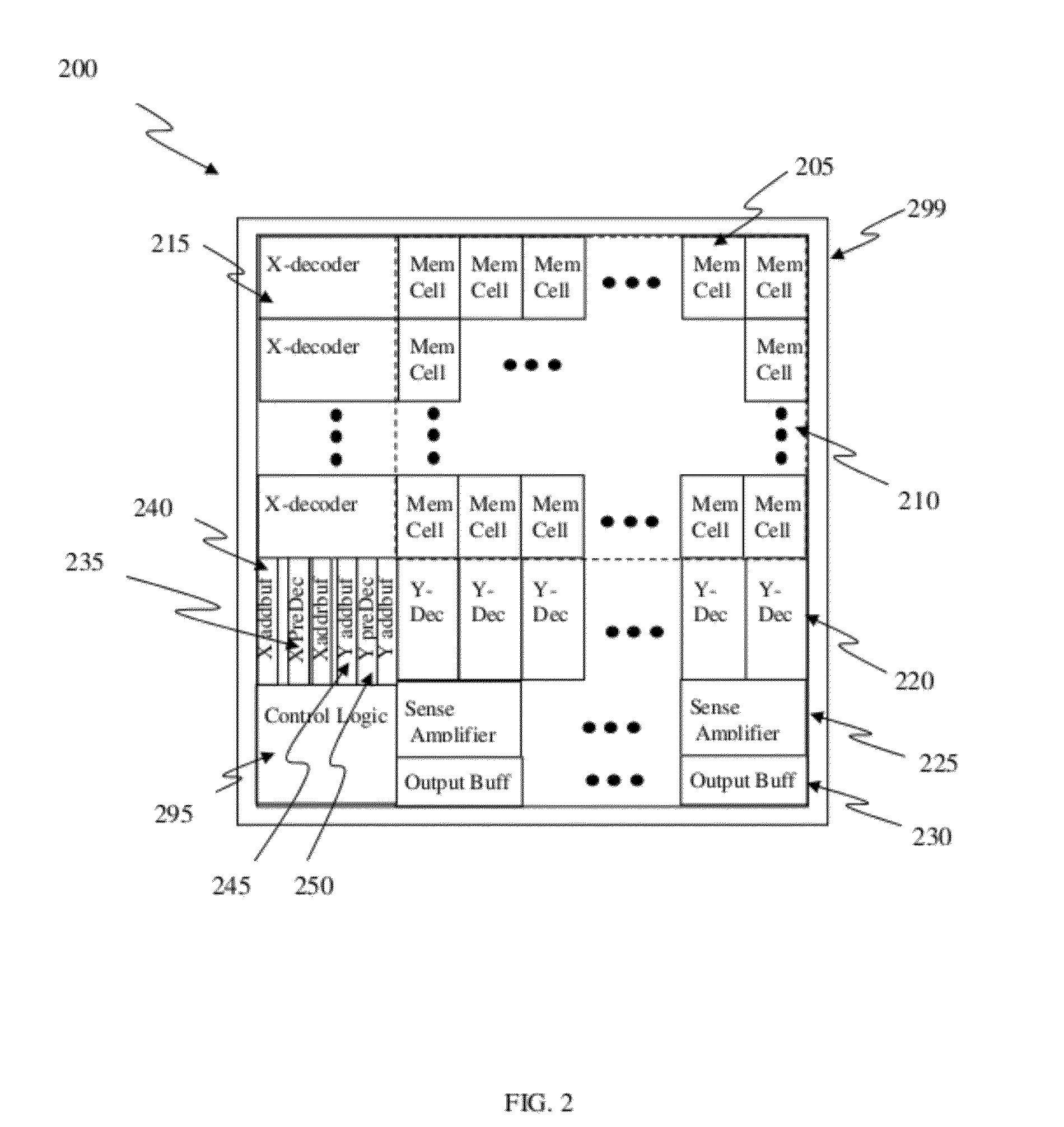

Circuit and Method of a Memory Compiler Based on Subtraction Approach

ActiveUS20120209888A1Digital data processing detailsMemory adressing/allocation/relocationDatasheetParallel computing

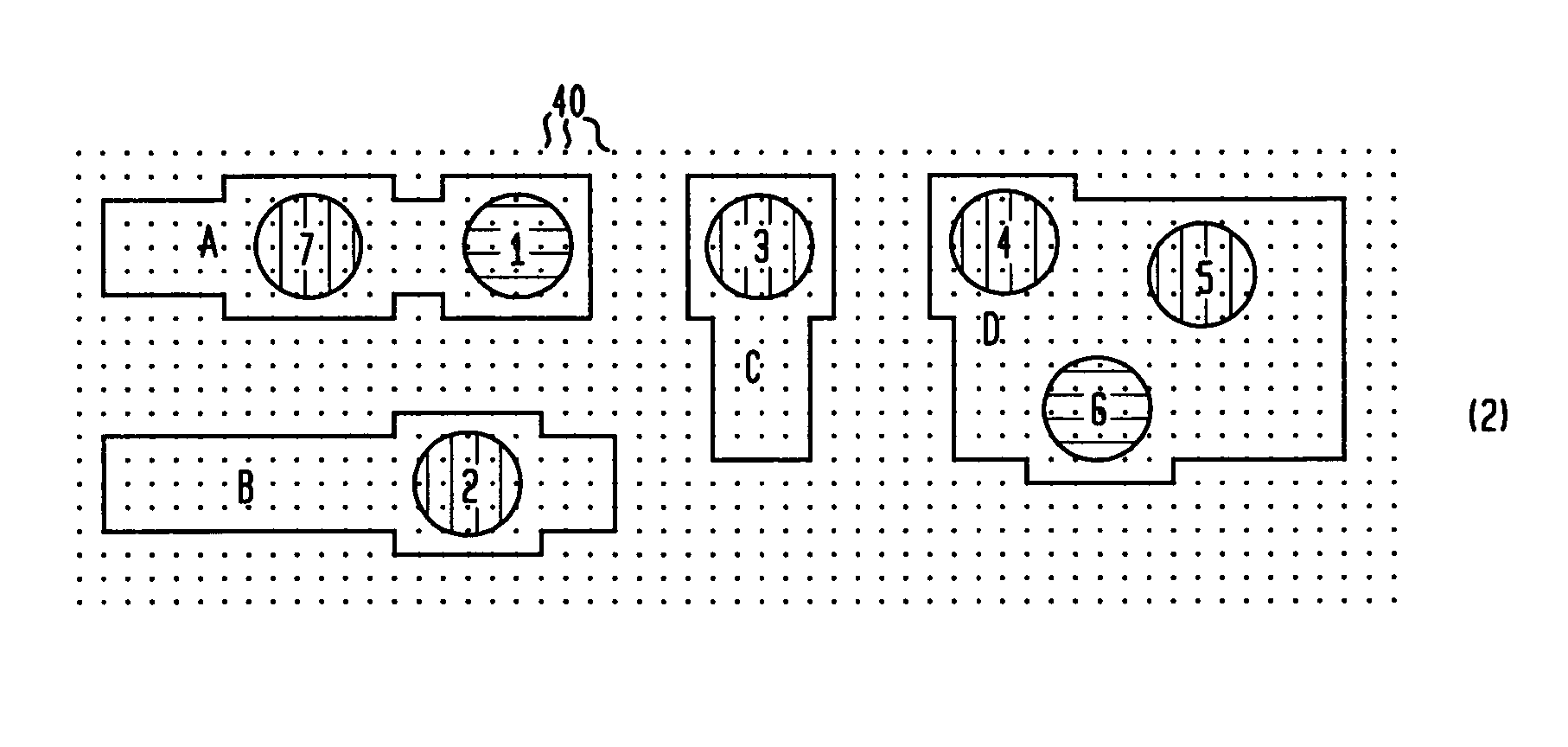

A memory compiler to generate a set of memories is based on a subtraction approach from a set of templates (memory templates), including at least one layout database and auxiliary design databases, by software. The software can be based on general-purpose programming language or a layout-specific language. The compiled memories can be generated by reducing the memory array sizes in row and / or column directions by moving, deleting, adding, sizing, or stretching the layout objects, and disabling the high order addresses, etc. from the memory template by software. The new auxiliary design databases, such as layout phantom, behavior model, synthesis view, placement-and-routing view or datasheet, can also be generated by modifying some parameters from the memory template by software. One-time programmable memory using junction diode, polysilicon diode, or isolated active-region diode as program selector in a cell can be generated accordingly.

Owner:ATTOPSEMI TECH CO LTD

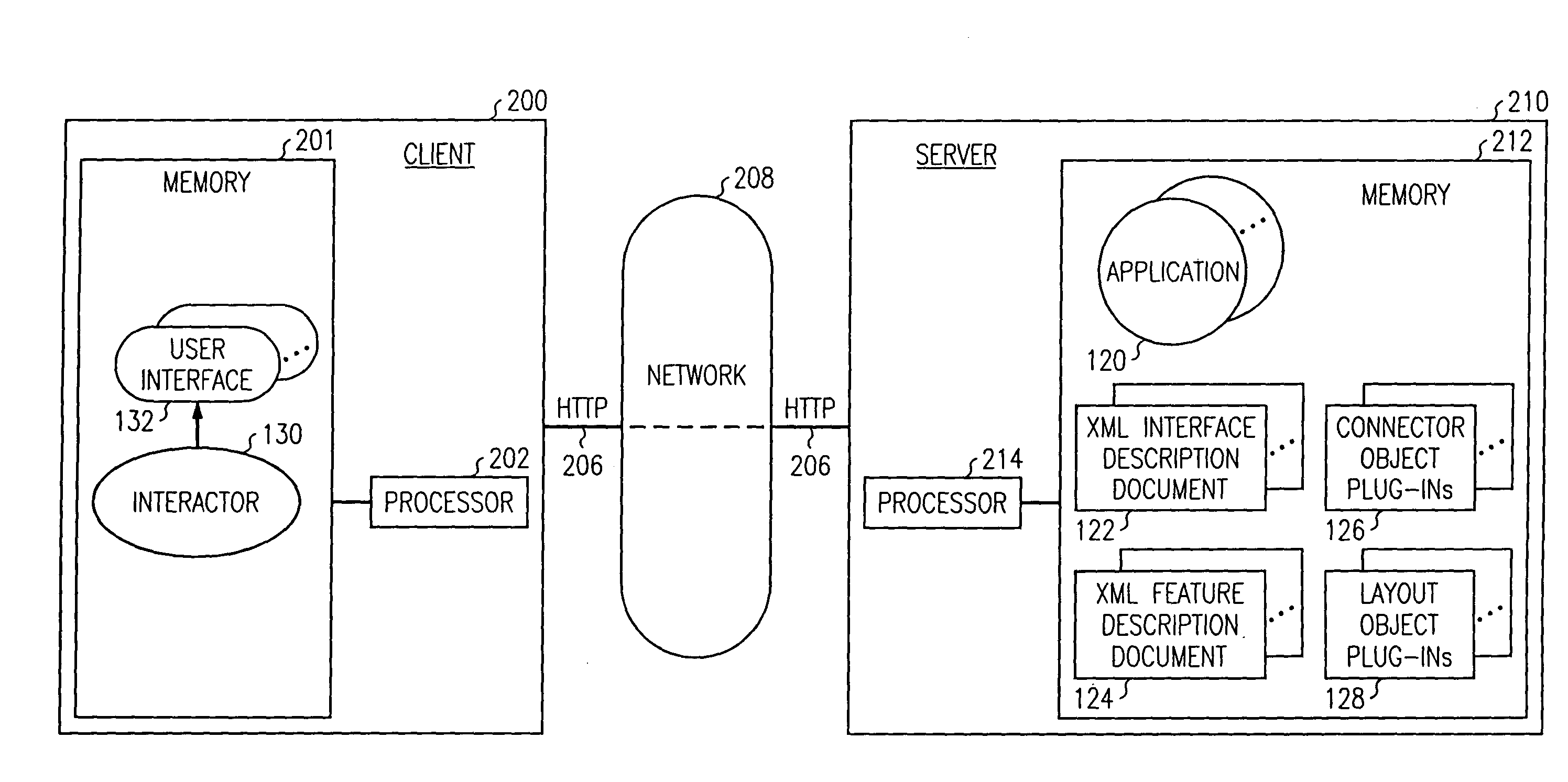

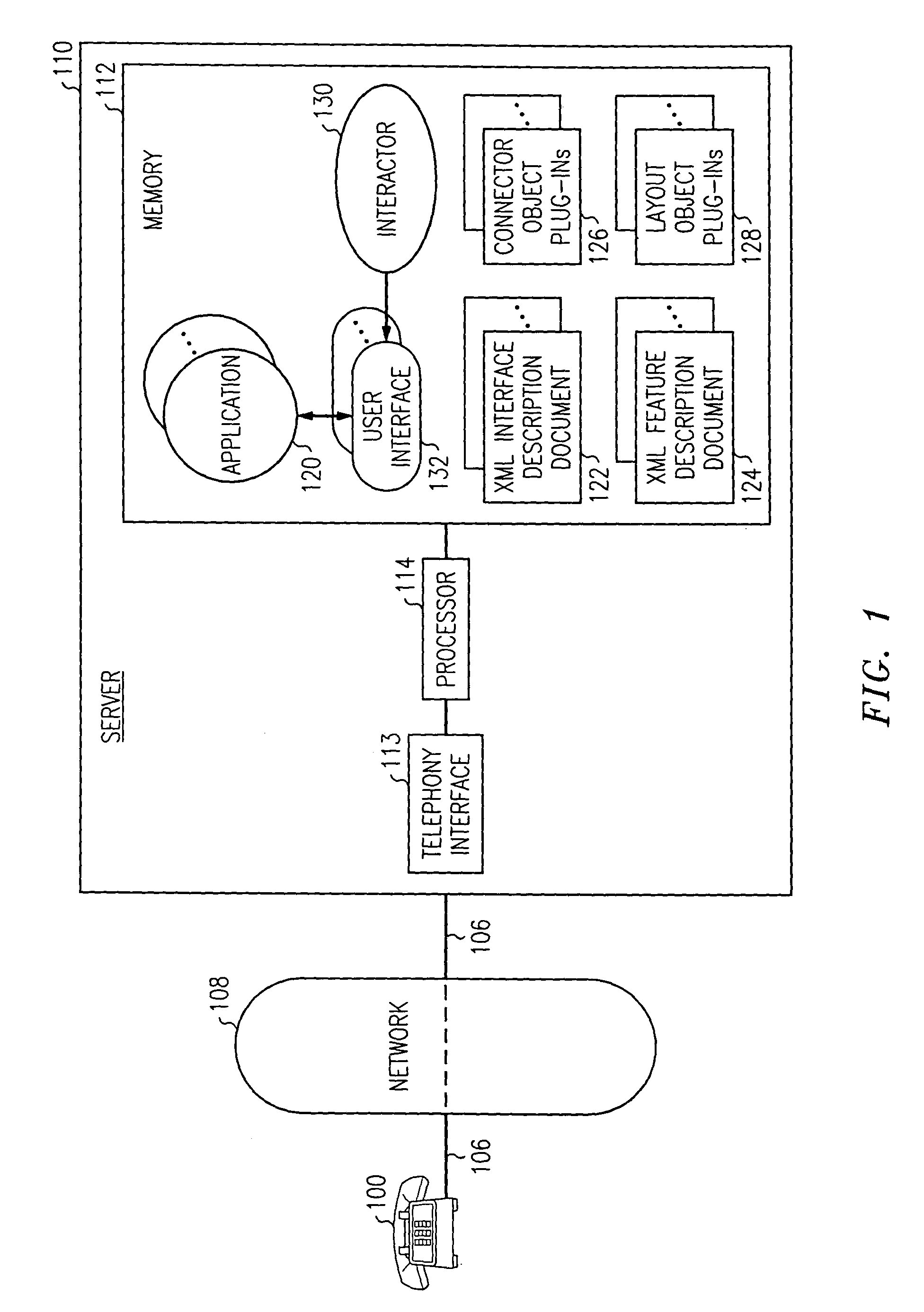

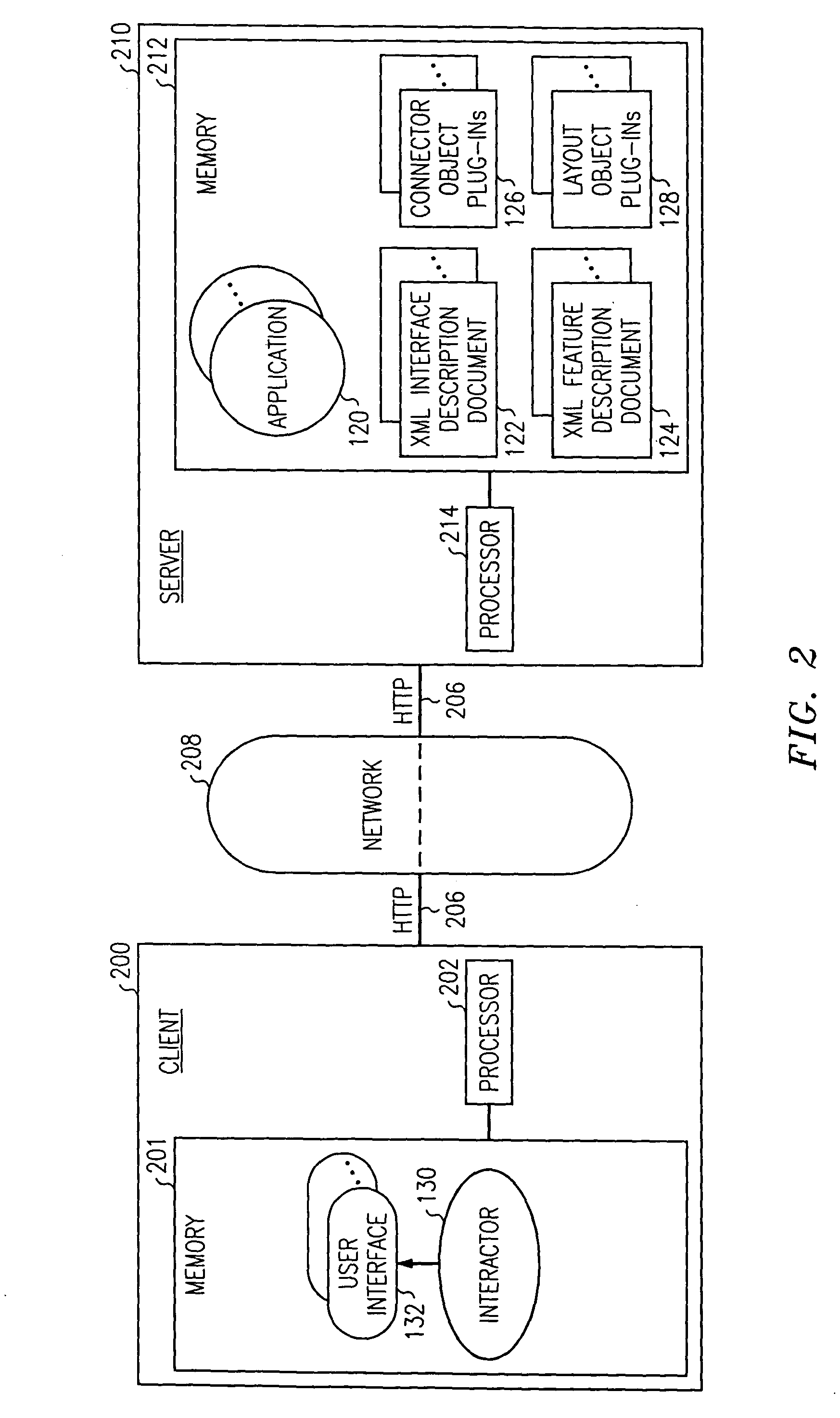

Mark-up language implementation of graphical or non-graphical user interfaces

InactiveUS7219305B2Easy to createSimplify workSoftware engineeringDigital computer detailsHuman–computer interactionInterface (Java)

A user interface (132)—be it graphical (GUI) or telephony (TUI) to an application (120) is defined by stored interface and feature description documents (122,124) written in XML and JavaScript, so that the user interface and changes thereto can be effected without access to source code. Interface description documents define the appearance and the behavior of the user interface toward the user, while feature description documents define the interaction of the user interface with the interfaced-to application, both in conformity with a user-interface object model (310). Stored connector object plug-ins (126) define connector objects for rendering elements of feature description documents, and stored layout object plug-ins (128) define layout objects for rendering elements of interface description documents of one or more interfaces.

Owner:AVAYA TECH LLC

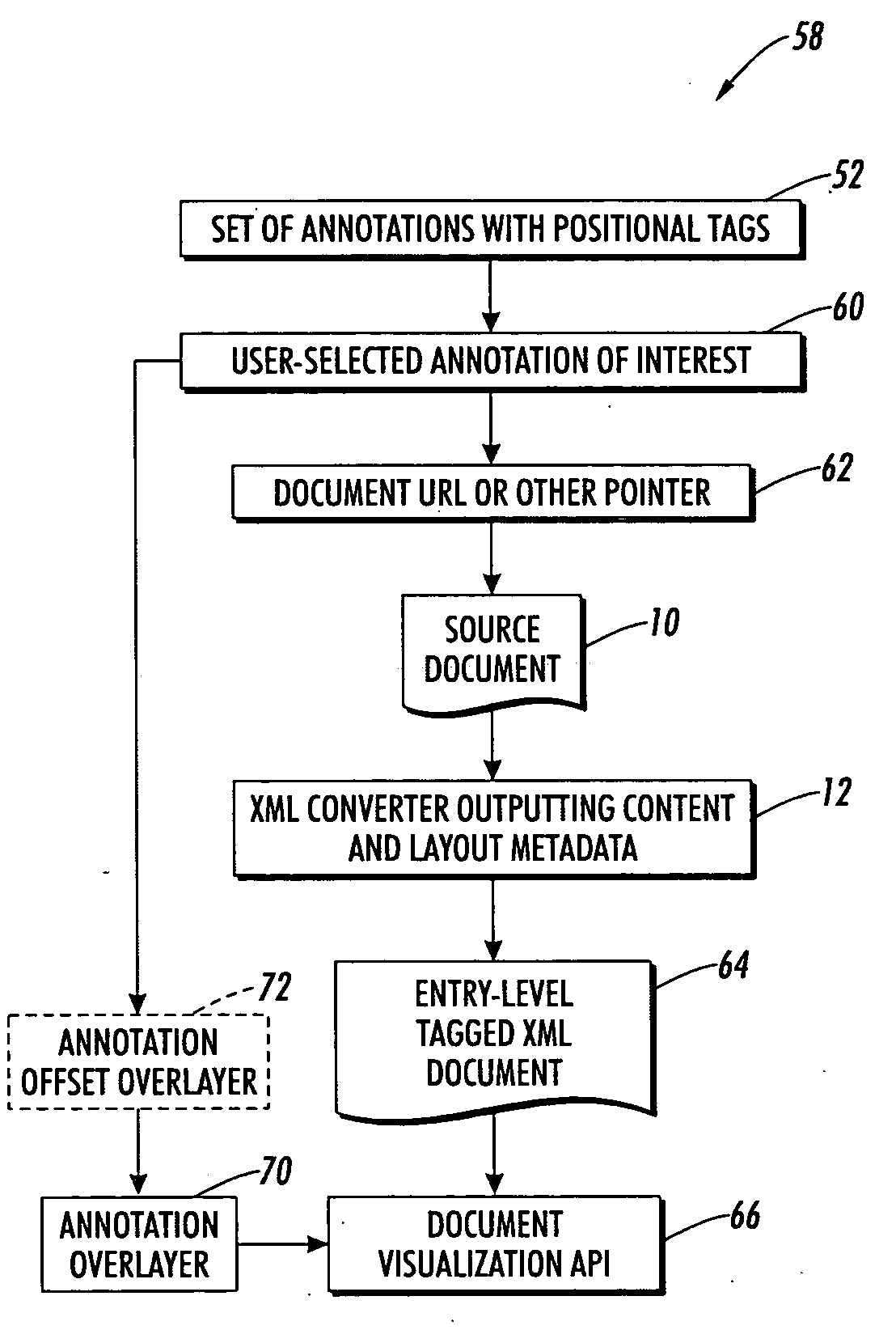

Visualizing document annotations in the context of the source document

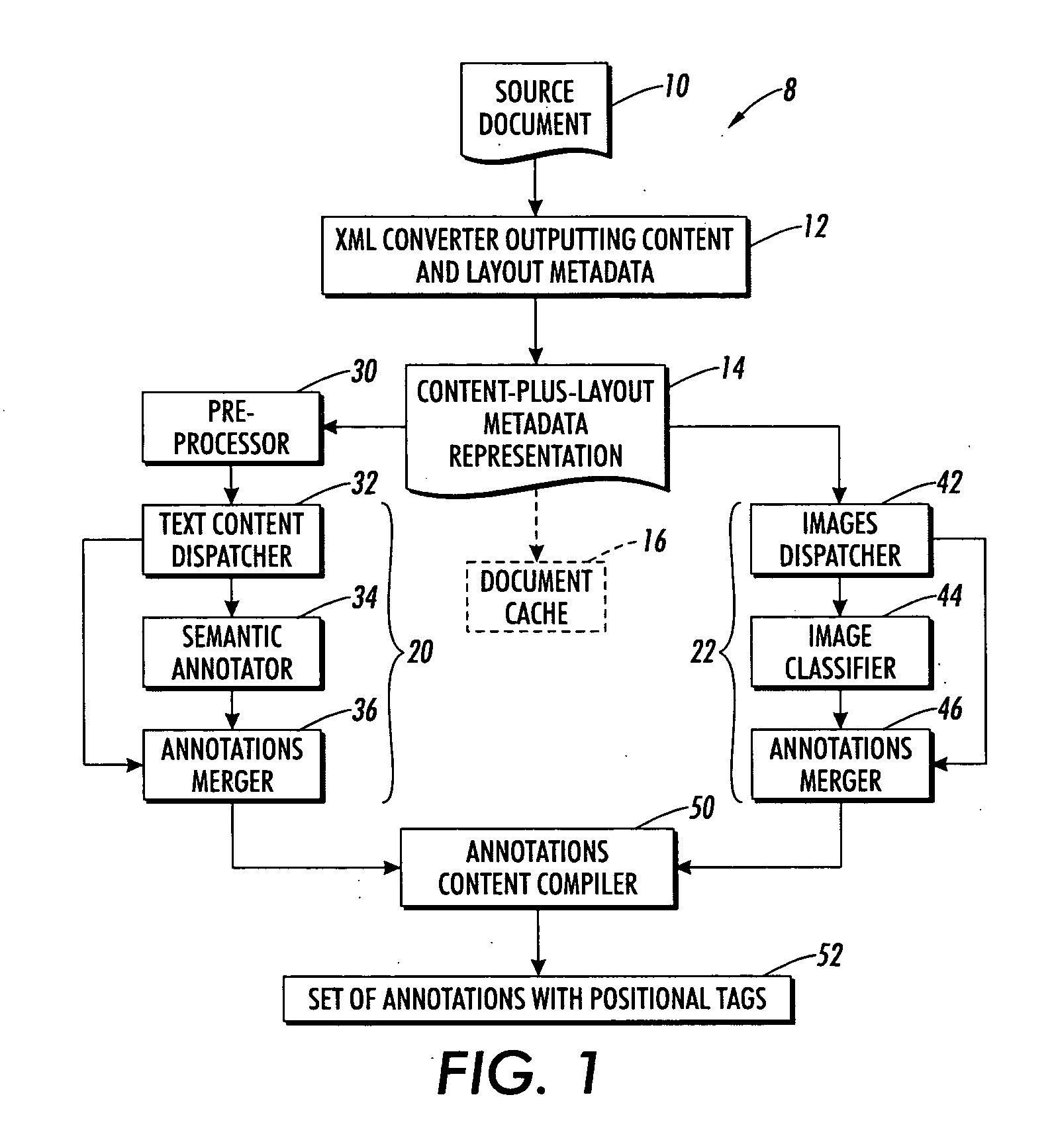

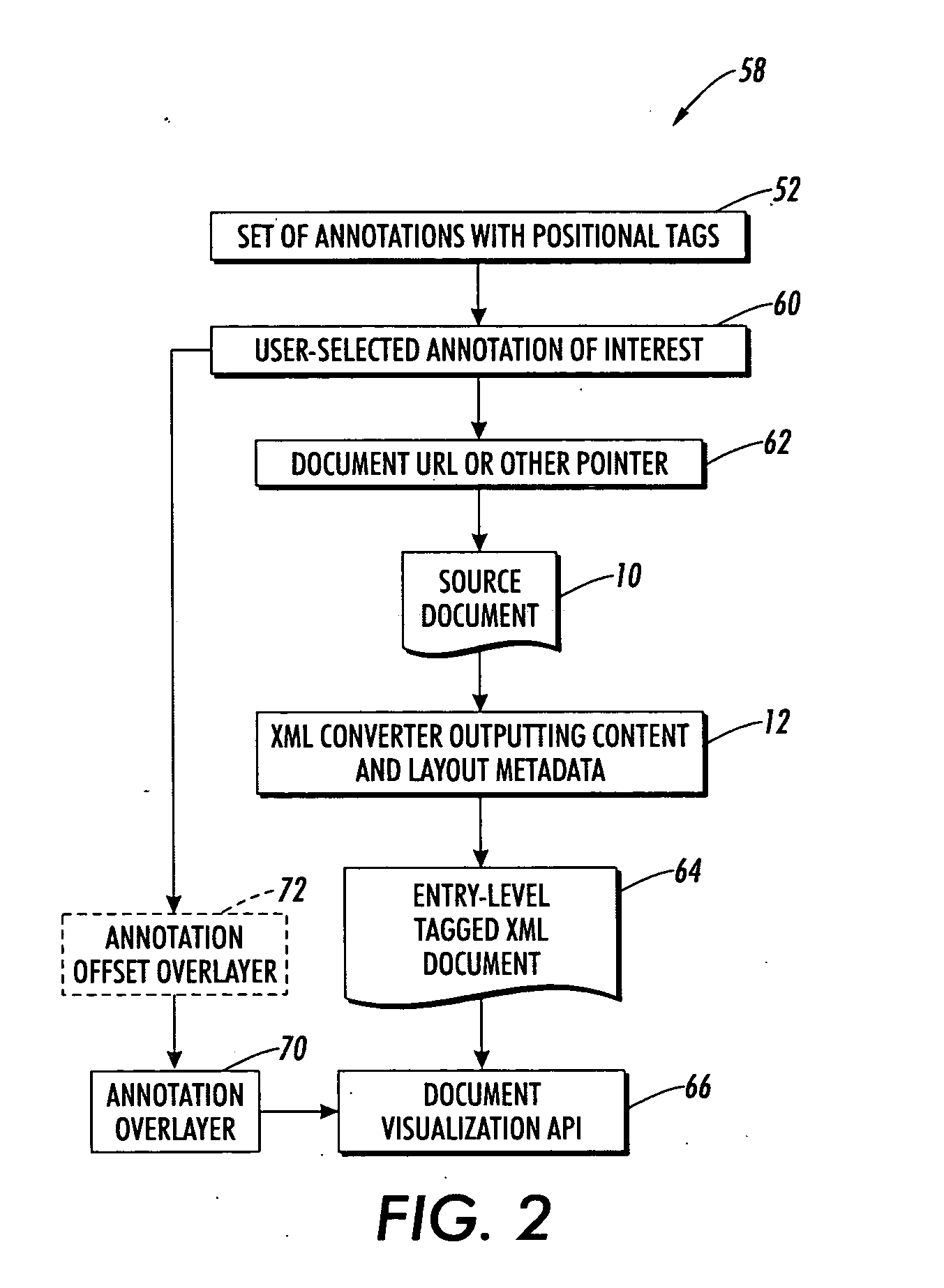

ActiveUS20070294614A1Natural language data processingSpecial data processing applicationsDocument preparationDocumentation

In a document annotator (8), a document converter (12) is configured to convert a source document (10) with a layout to a deterministic format (14, 64) including content and layout metadata. At least one annotation pipeline (20, 22) is configured to generate document annotations respective to received content. A merger (36, 46) is configured to associate the generated document annotations with positional tags based on the layout metadata, which locate the document annotations in the layout. A document visualizer (58) is configured to render at least some content of the deterministic format and one or more selected annotations (60) in substantial conformance with the layout based on the layout metadata and the positional tags associated with the selected one or more annotations (60).

Owner:XEROX CORP

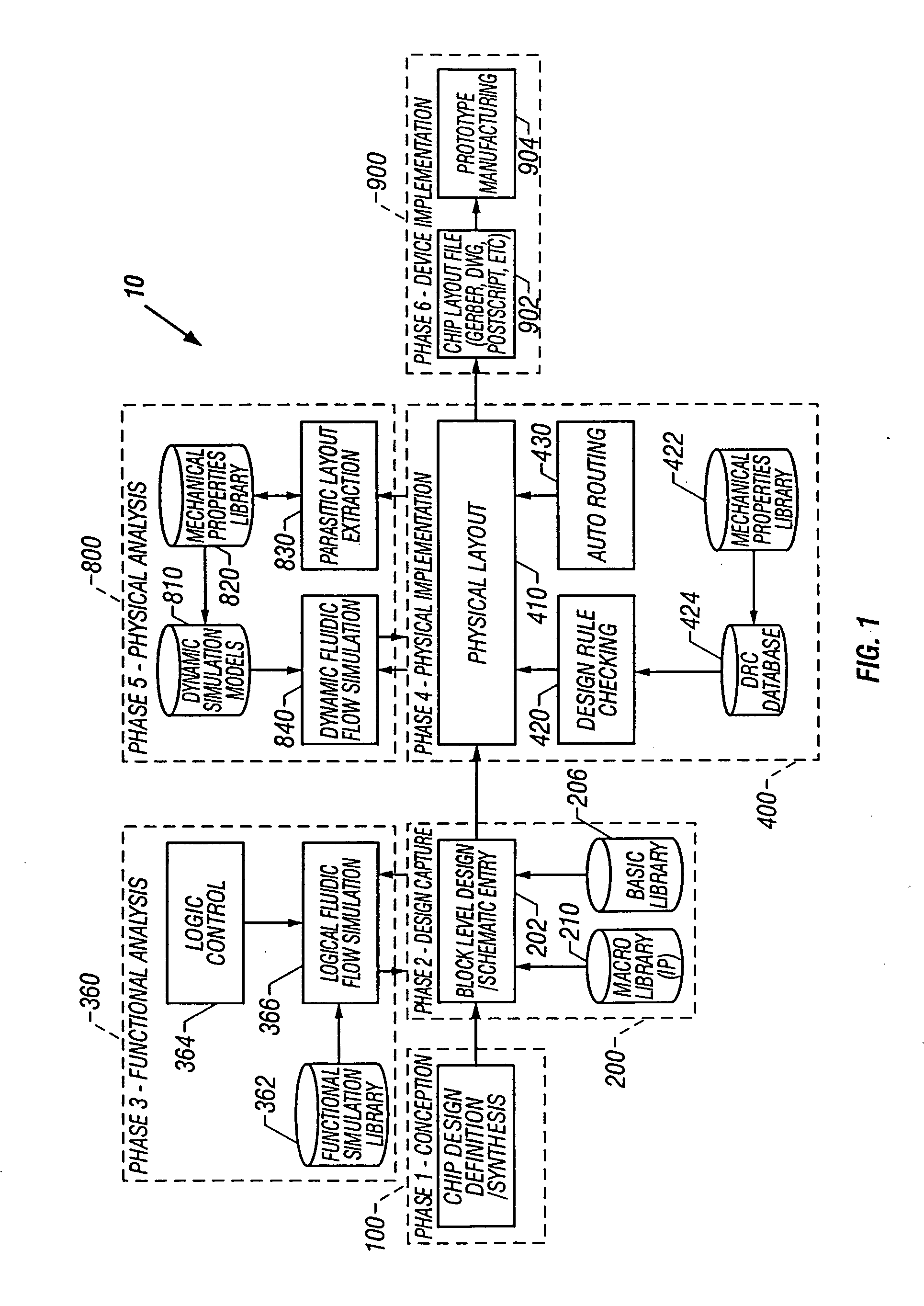

Microfluidic design automation method and system

InactiveUS20050065735A1Shorten the timeEasy placement and routingFixed microstructural devicesVolume/mass flow measurementComputer Aided DesignSystems design

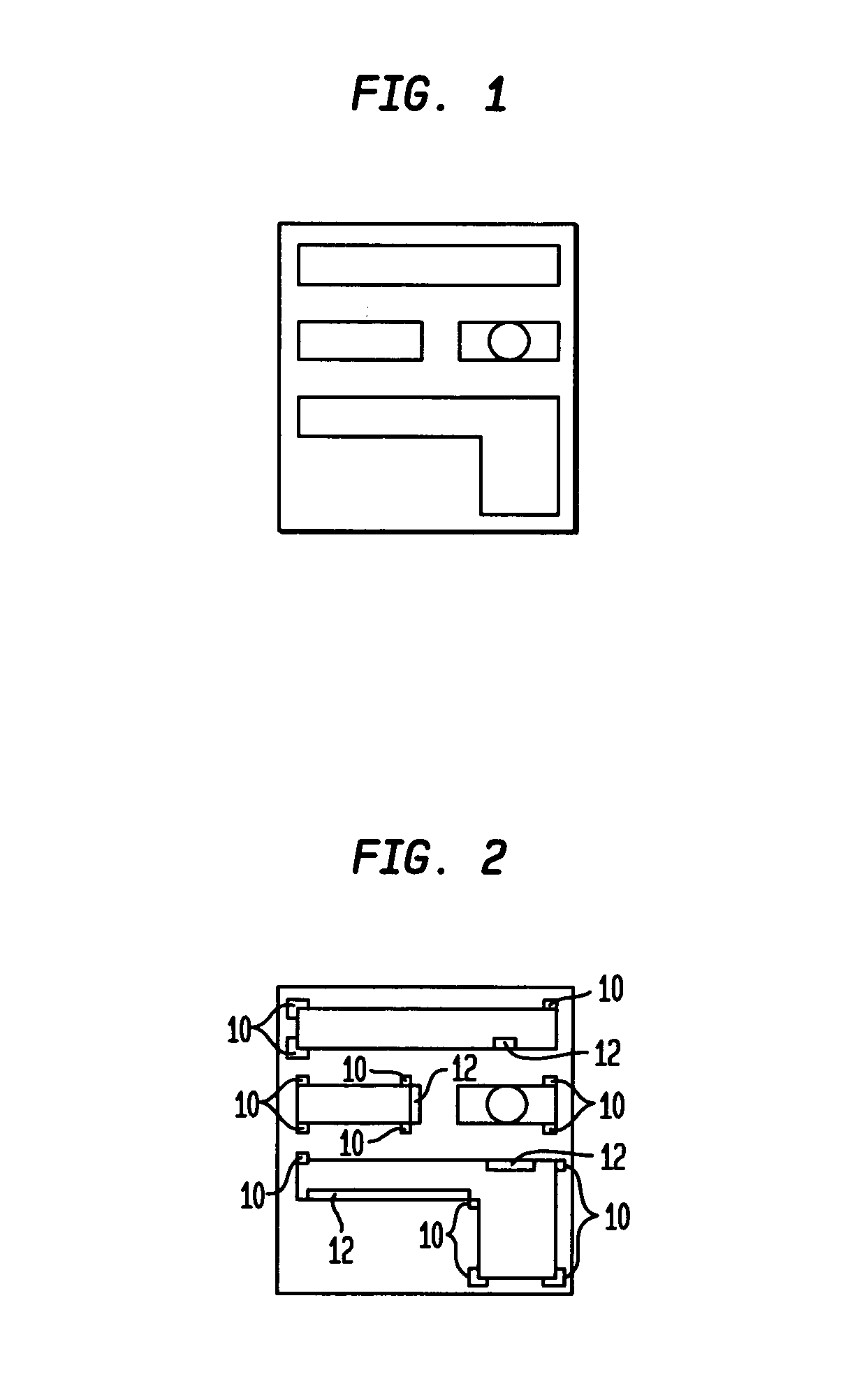

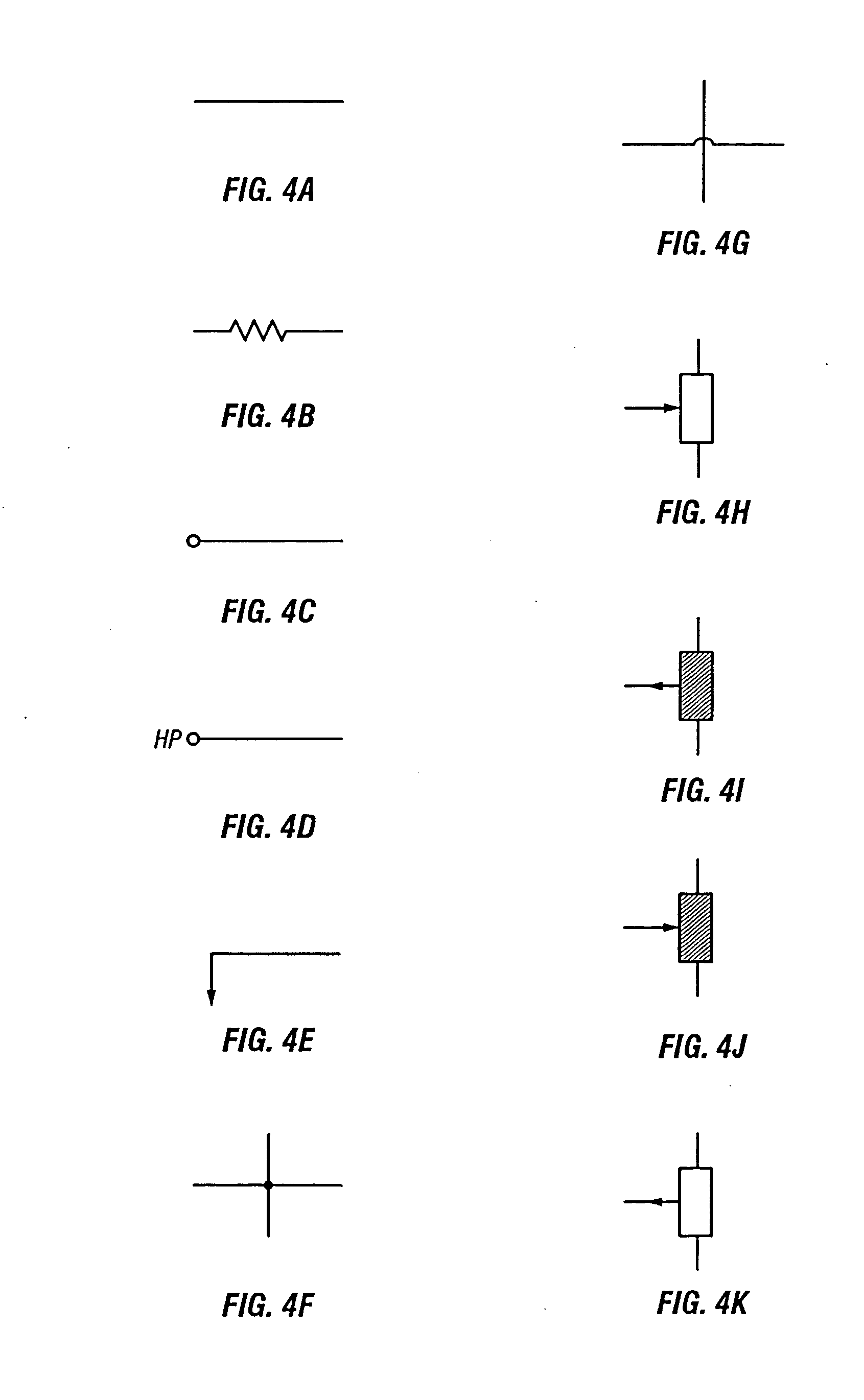

The present invention generally relates to microfluidics and more particularly to the design of customized microfluidic systems using a microfluidic computer aided design system. In one embodiment of the present invention a microfluidic circuit design method is provided. The method includes developing synthesizable computer code for a design. Next, a microfluidic circuit schematic, including a plurality of symbols for microfluidic components, is generated either interactively or using the synthesizable computer code. The microfluidic circuit schematic is then functionally simulated. The microfluidic components are placed and routed on a template to form a physical layout. Then the physical layout is physically simulated using dynamic simulation models of the microfluidic components; and the physical layout is written to a layout file.

Owner:FLUIDIGM CORP

Method of formatting documents

ActiveUS20040194028A1Complex format behaviourParticular utilityNatural language data processingSpecial data processing applicationsAlphanumericRating system

The present invention provides a method of preparing content with design in a presentation that is suitable for printing and / or electronic publishing. The method utilises content data including alphanumeric and / or graphical elements, and design data including a rule or rules associated with a particular alphanumeric element or graphical element. This can be used to define a scoring system which defines a score dependent on a degree of conformance of layouts to the rules, with the layout being selected in accordance with the resulting score.

Owner:TYPEFI SYST PTY LTD

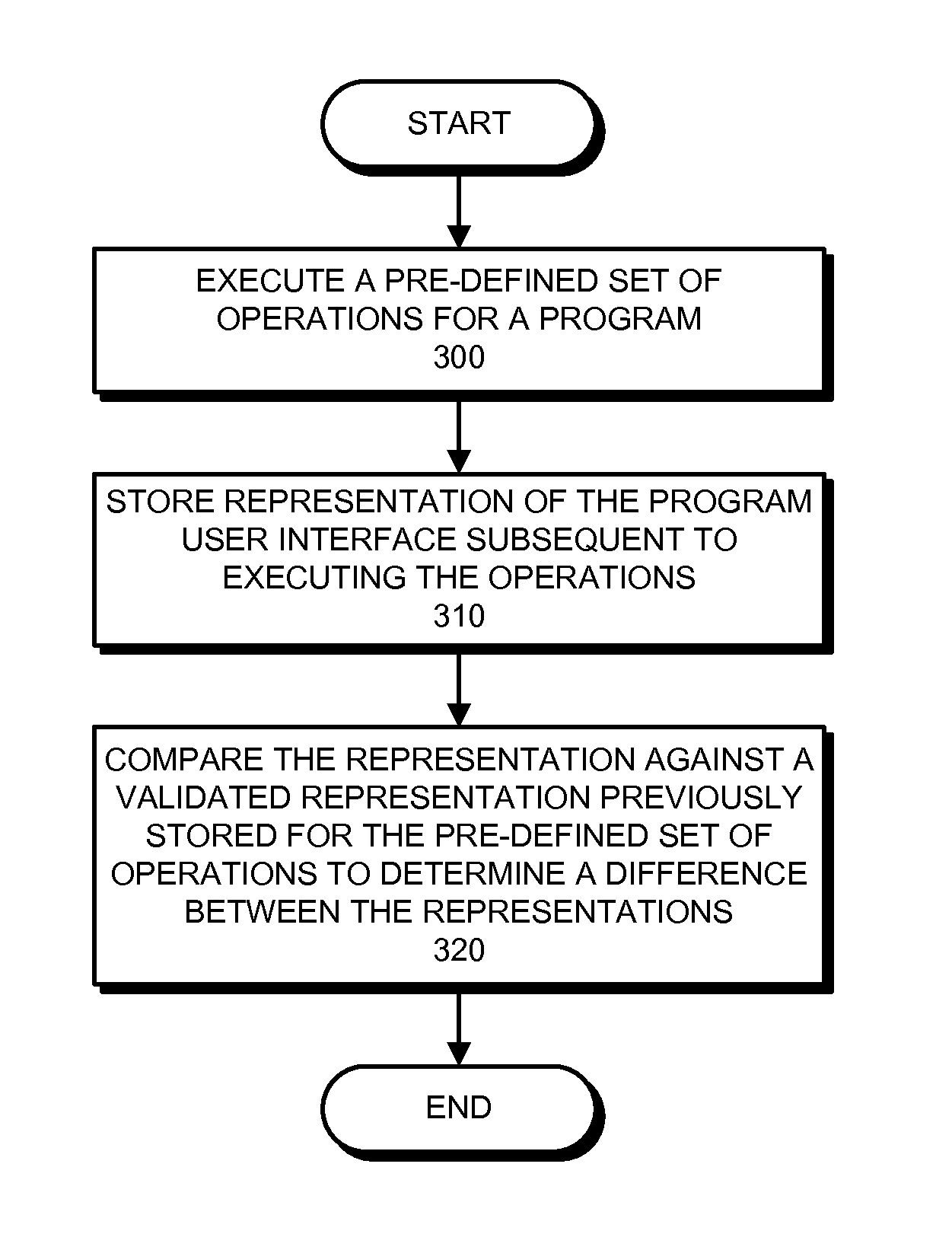

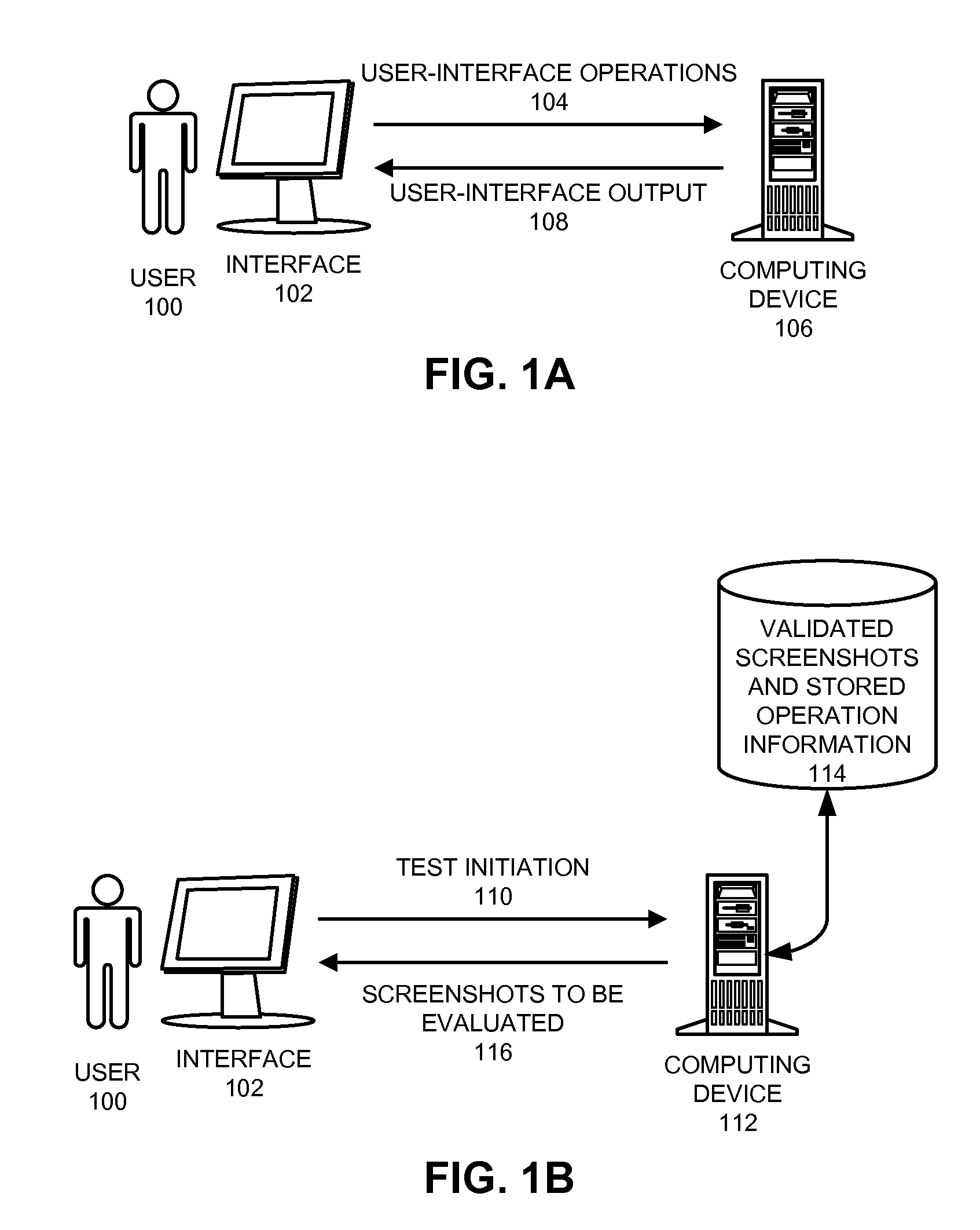

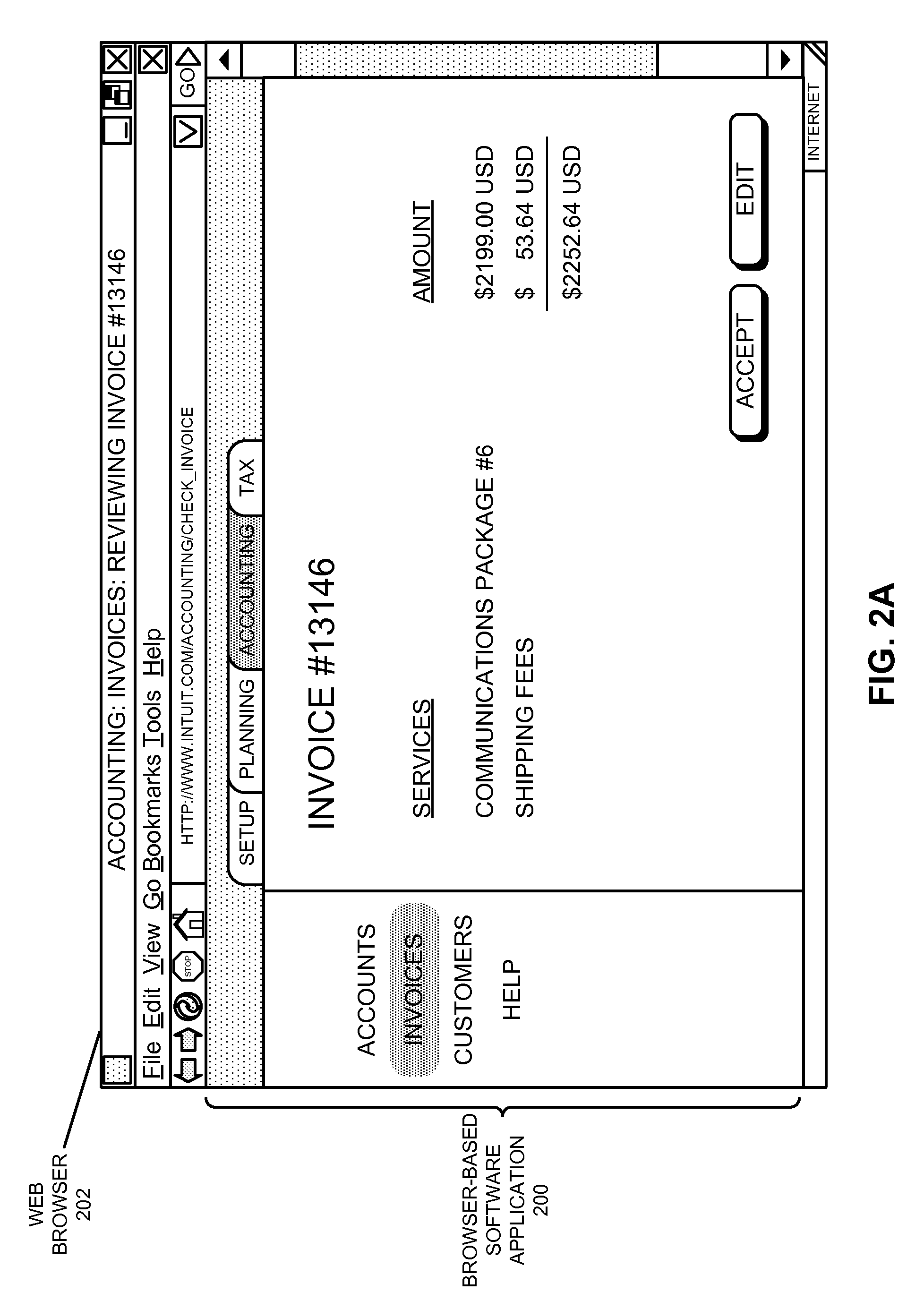

Method and apparatus for performing automated user-interface layout testing

ActiveUS9213625B1Facilitates detecting changeEasy to changeSoftware engineeringSoftware testing/debuggingTheoretical computer scienceUser interface

The disclosed embodiments provide a system that performs automated user-interface layout testing. During operation, the system executes a pre-defined set of operations for a program. After these operations have executed, the system then stores a representation (e.g., a snapshot) of the program user interface. The system then compares this representation against a validated representation that was previously stored for the pre-defined set of operations to determine a difference between the representations. This process facilitates detecting changes to the program (and / or the environment in which the program executes) that affect the user interface that is presented to a user.

Owner:INTUIT INC

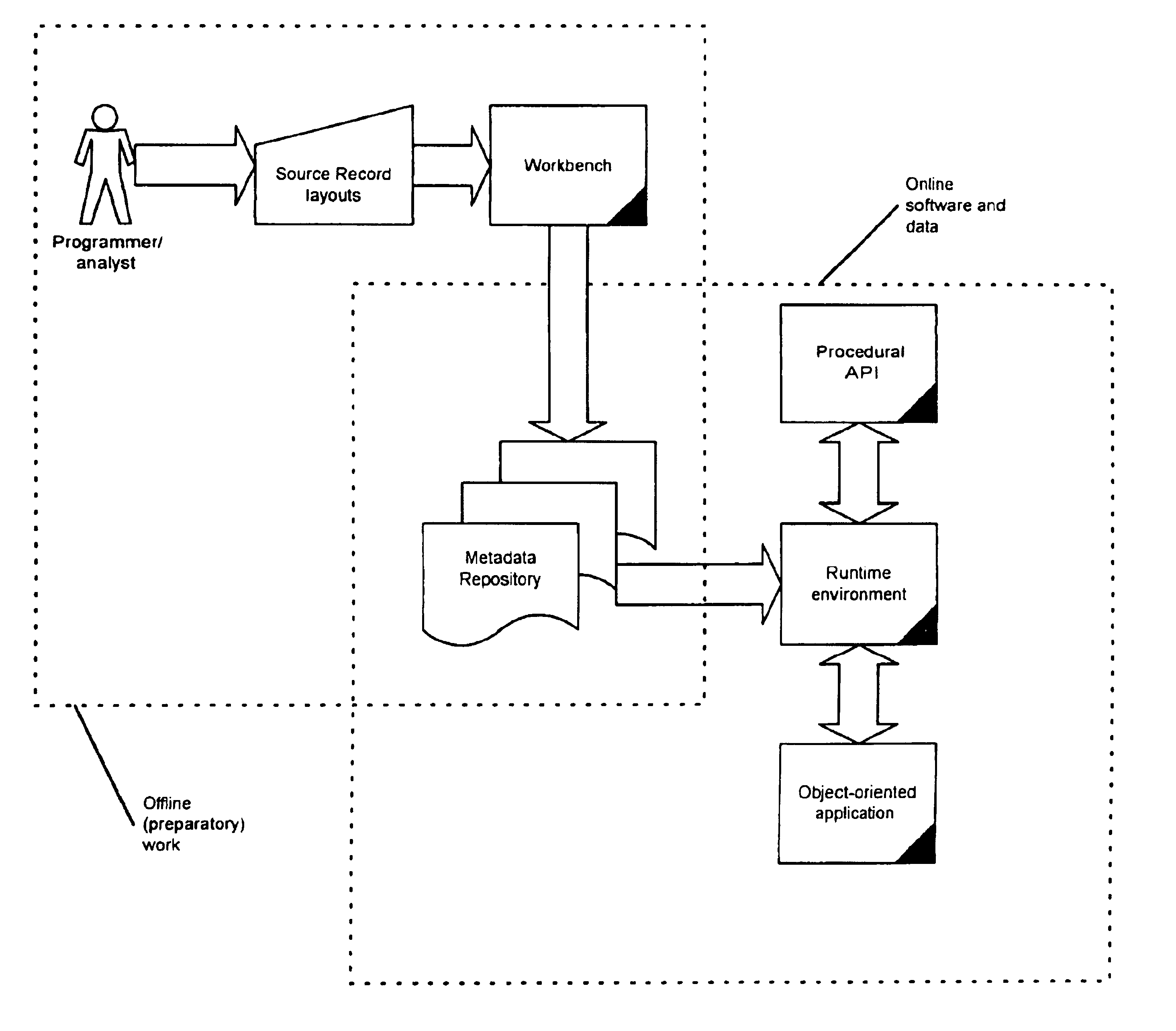

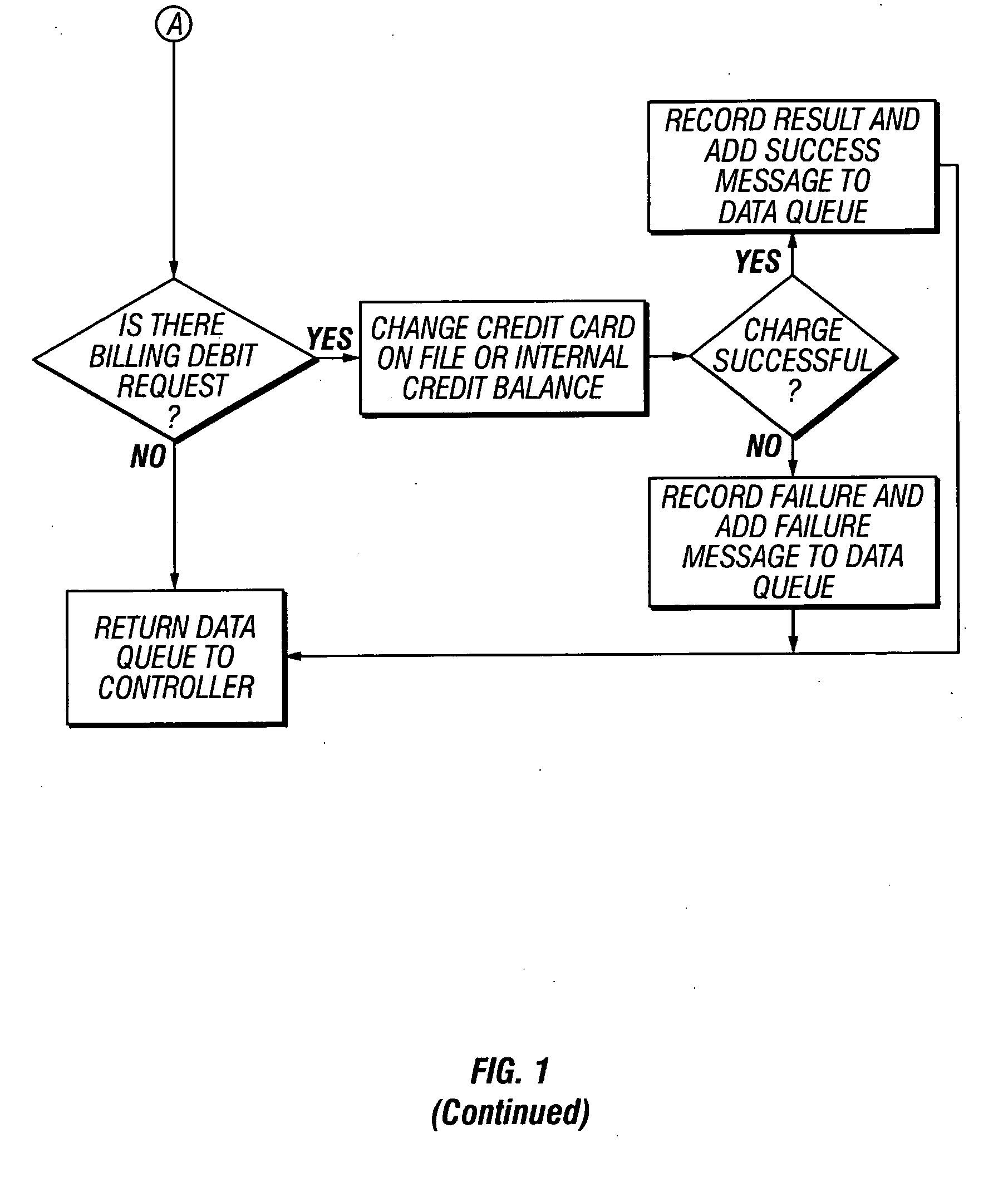

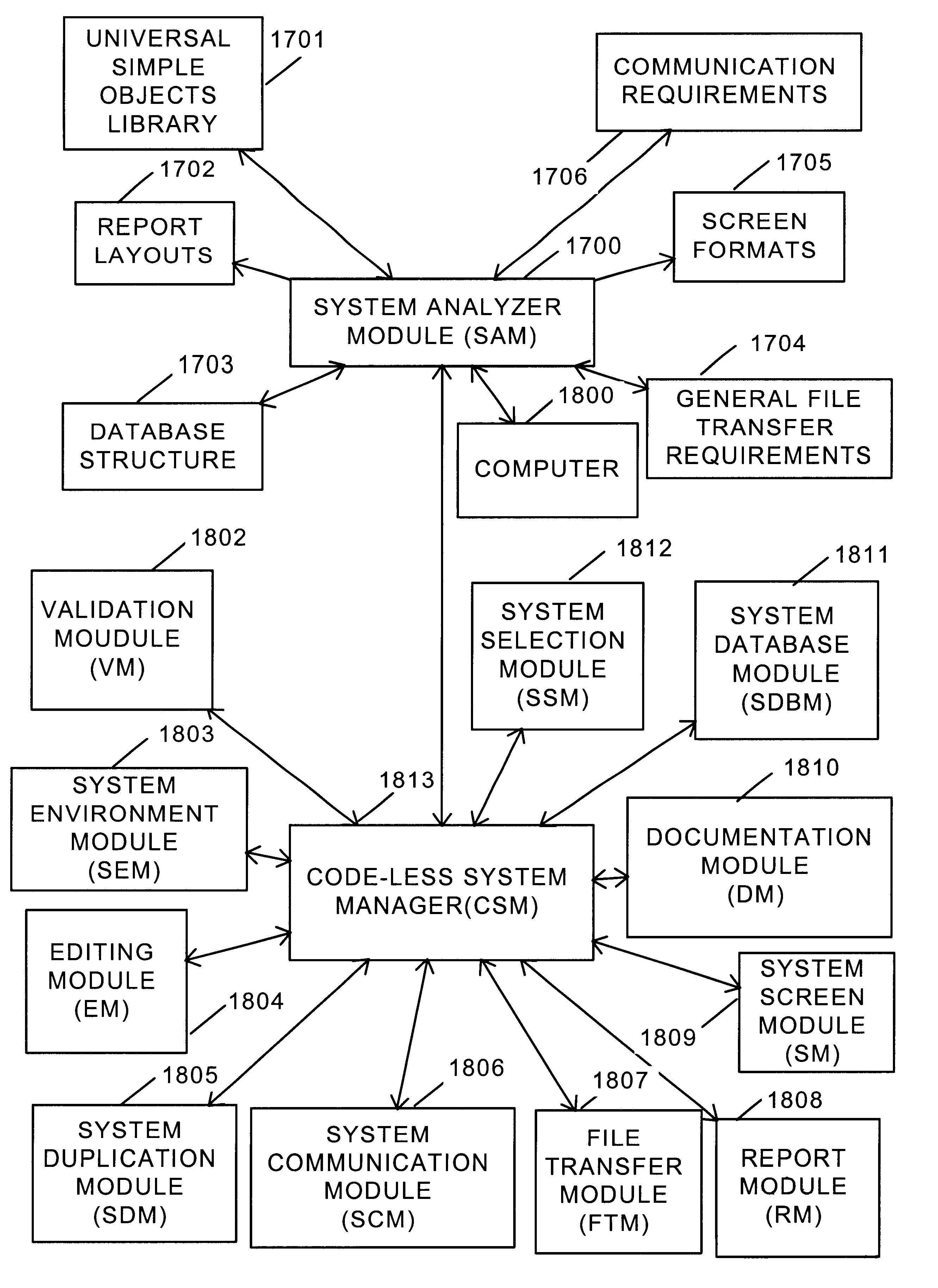

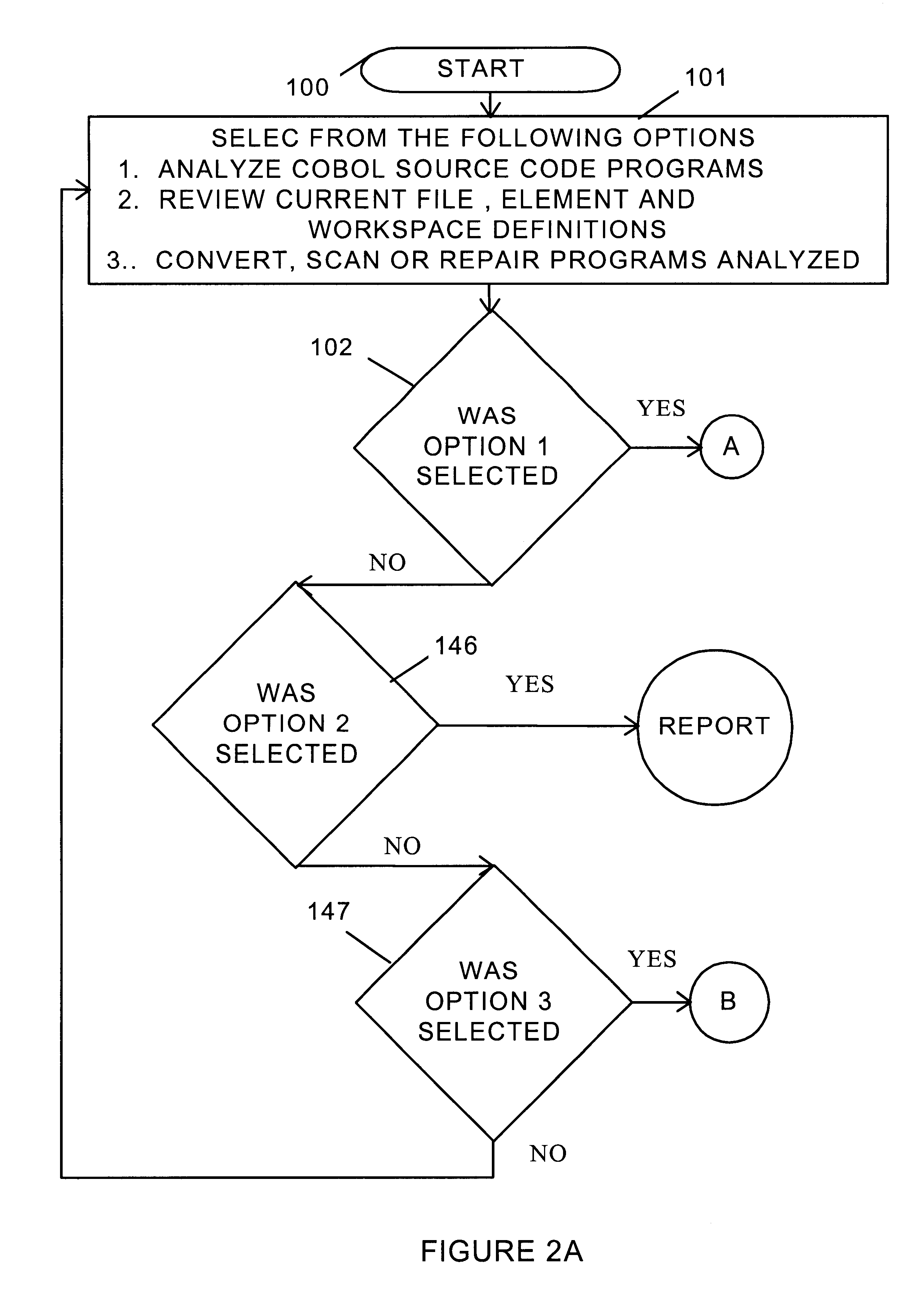

Software re-engineering system

InactiveUS6269474B1Improve system performanceSoftware maintainance/managementProgram loading/initiatingData fileApplication software

An optimization system including an option to convert existing code to a code-less environment or to create a codeless environment by the establishment of all essential application elements in files. The code-less environment is created through a design and analysis step, an environmental step and an installation step. An application map is prepared during the design and analysis step which defines where information enters into the system, where information is used, and where used information is changed. The application map is also used to verify that all information is accounted for. The design and analysis step also includes the generation of default database structures, screen formats, print layouts, file transfer protocols, validation tables and communication specifications. The environmental step includes modifying specifications in accordance with user preferences, simulating performance of the specifications with test data, preparing existing data files for conversion to the code-less system, and implementing parallel processing. The installation step includes final testing of selected hardware platforms and maintenance on a development system.

Owner:INT VERONEX RESOURCES