Patents

Literature

33 results about "Vlsi layout" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

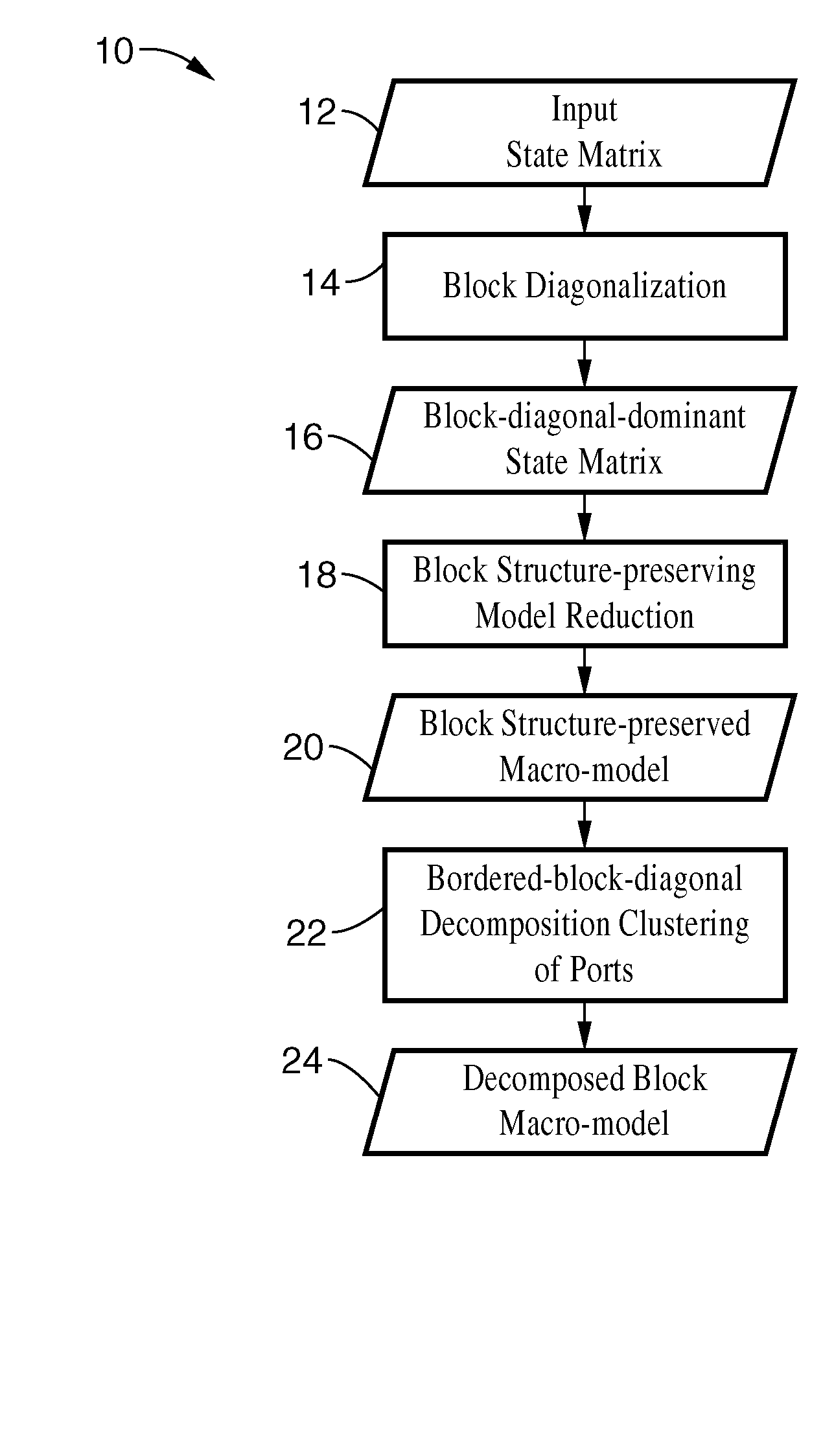

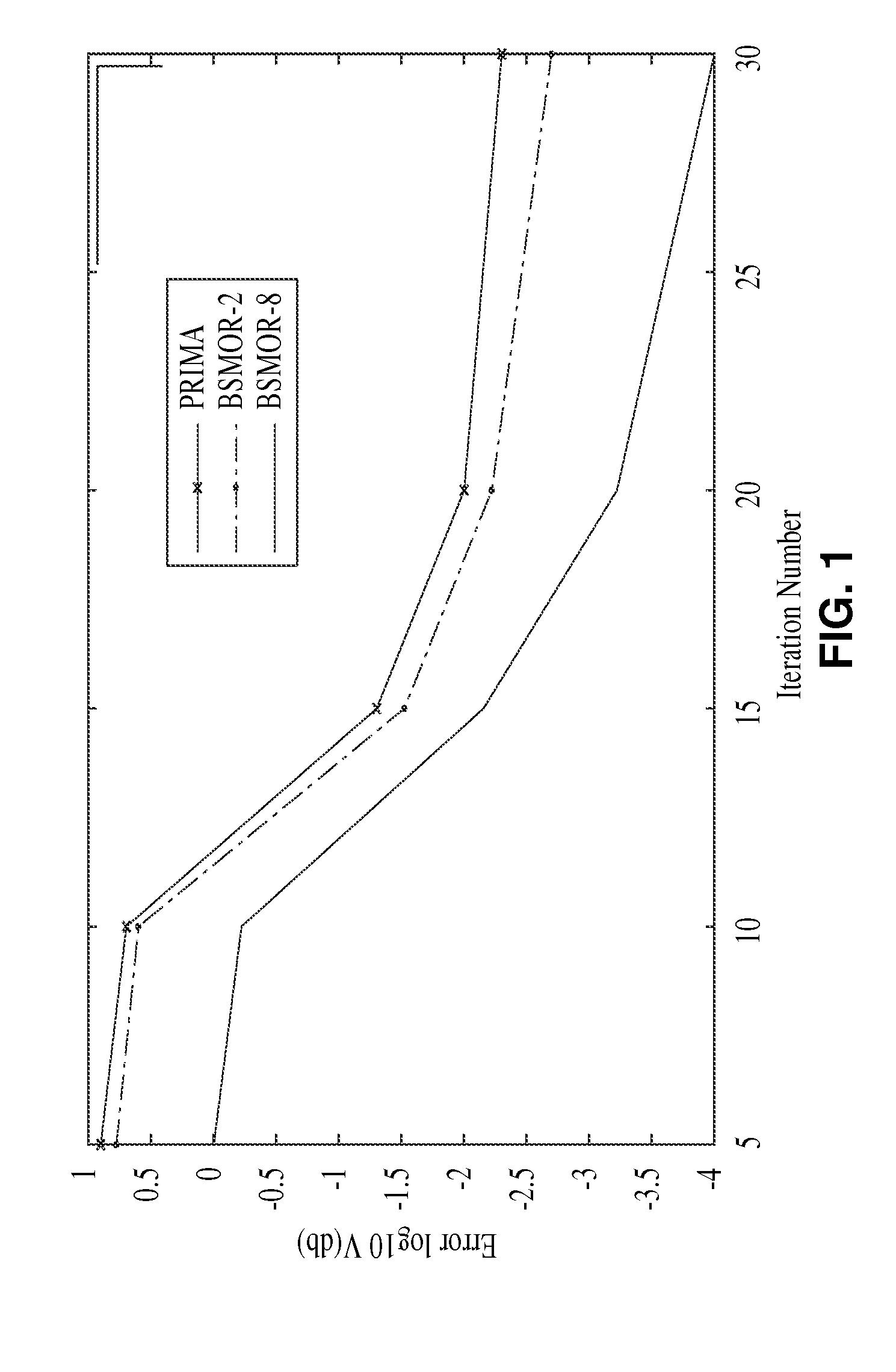

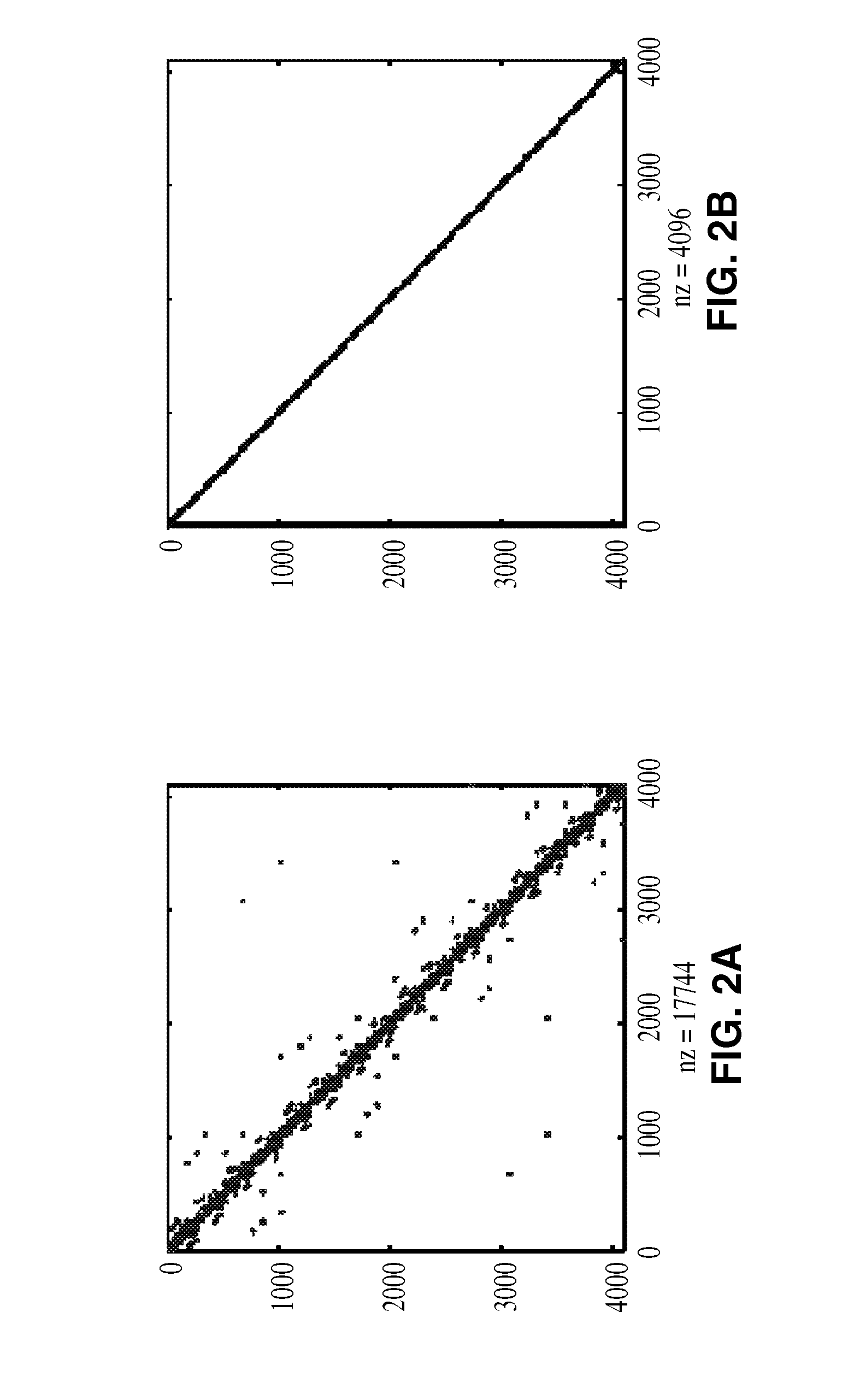

Structured and parameterized model order reduction

InactiveUS20080072182A1Reduce redundancyNon-uniformity is constantDetecting faulty computer hardwareComputation using non-denominational number representationStructured modelOrder reduction

Model-order reduction techniques are described for RLC circuits modeling the VLSI layouts. A structured model order reduction is developed to preserve the block-level sparsity, hierarchy and latency. In addition, a structured and parameterized model order reduction is developed to generate macromodels for design optimizations of VLSI layouts. The applications are thermal via allocation under the dynamic thermal integrity and via stapling to simultaneously optimize thermal and power integrity.

Owner:RGT UNIV OF CALIFORNIA

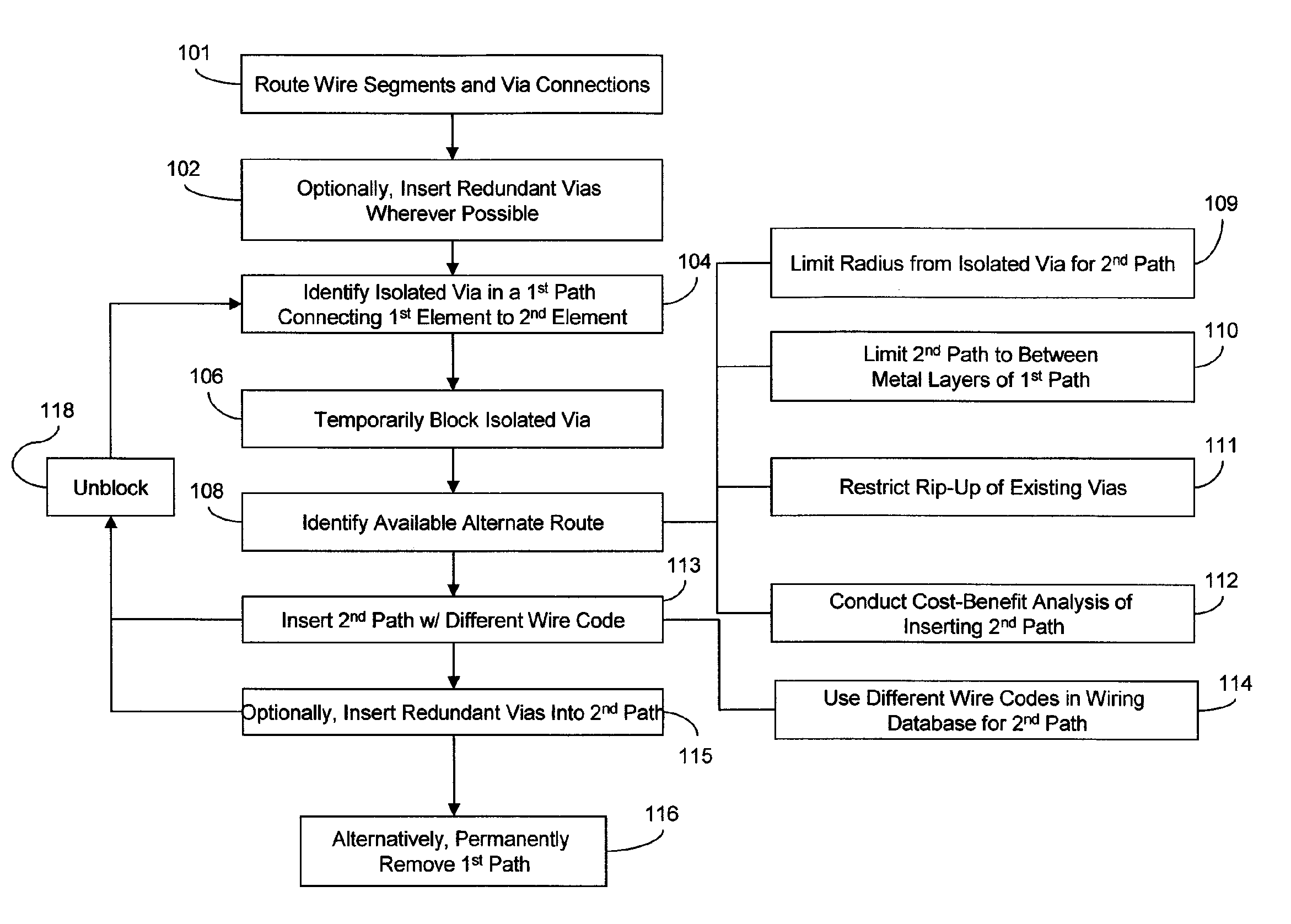

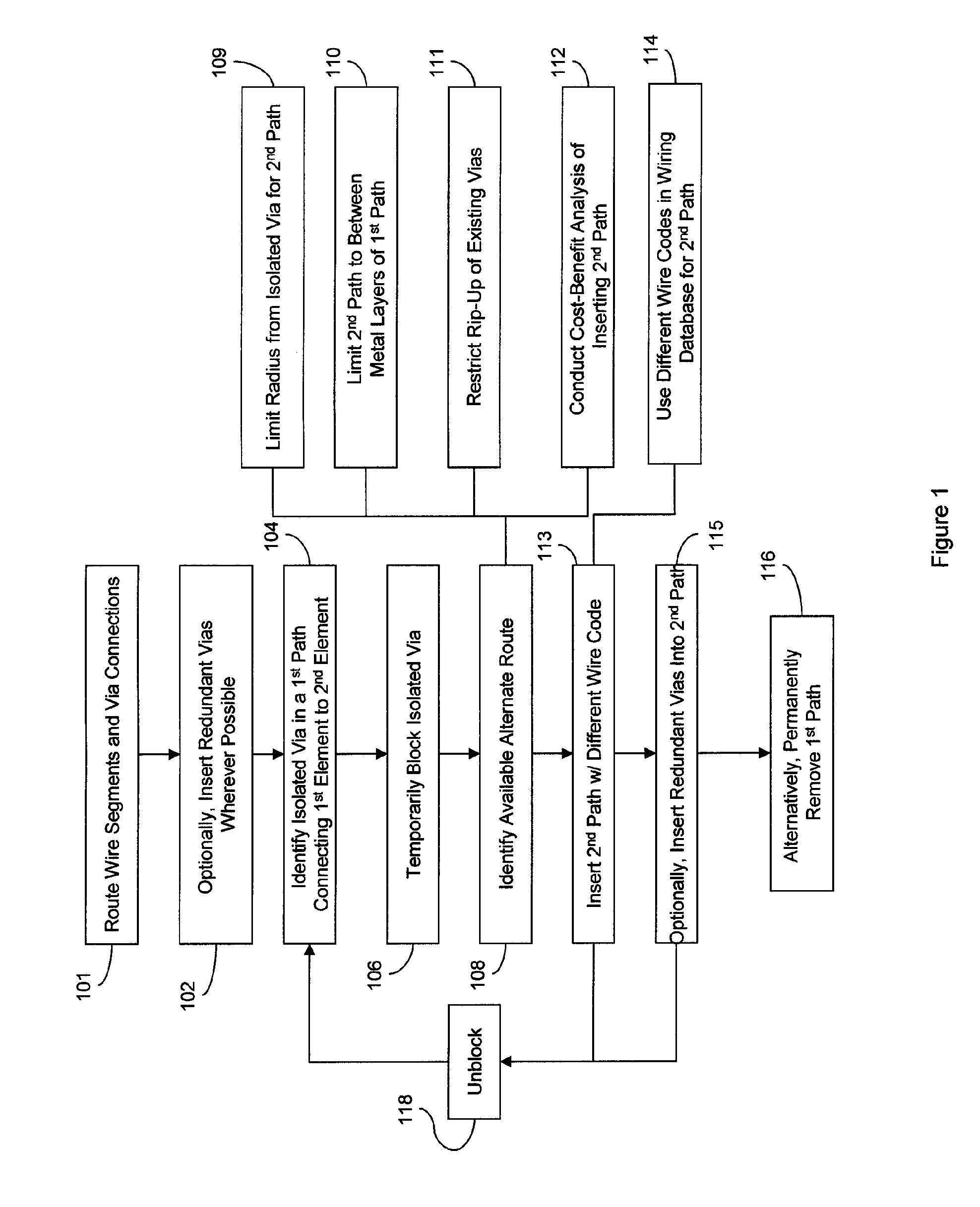

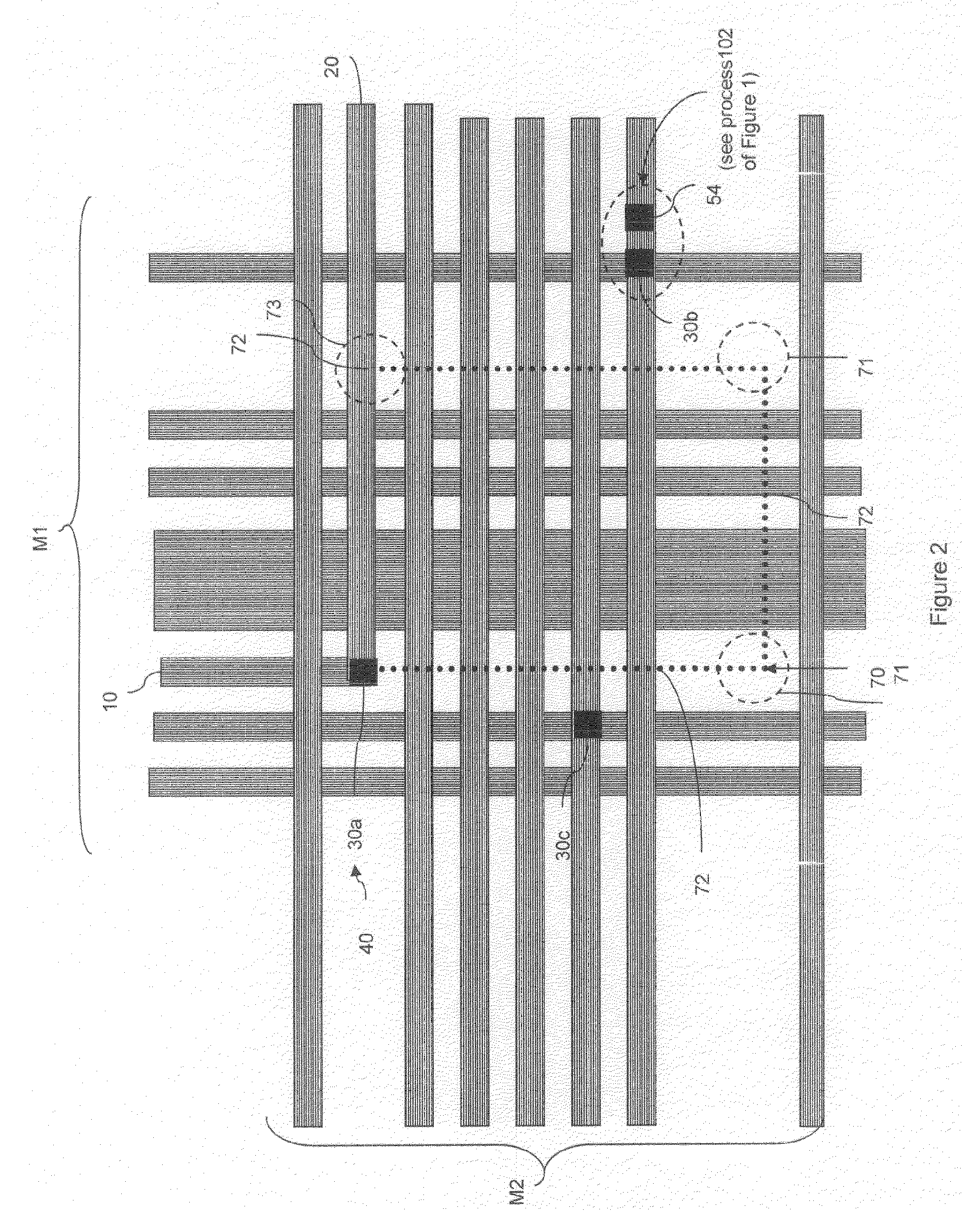

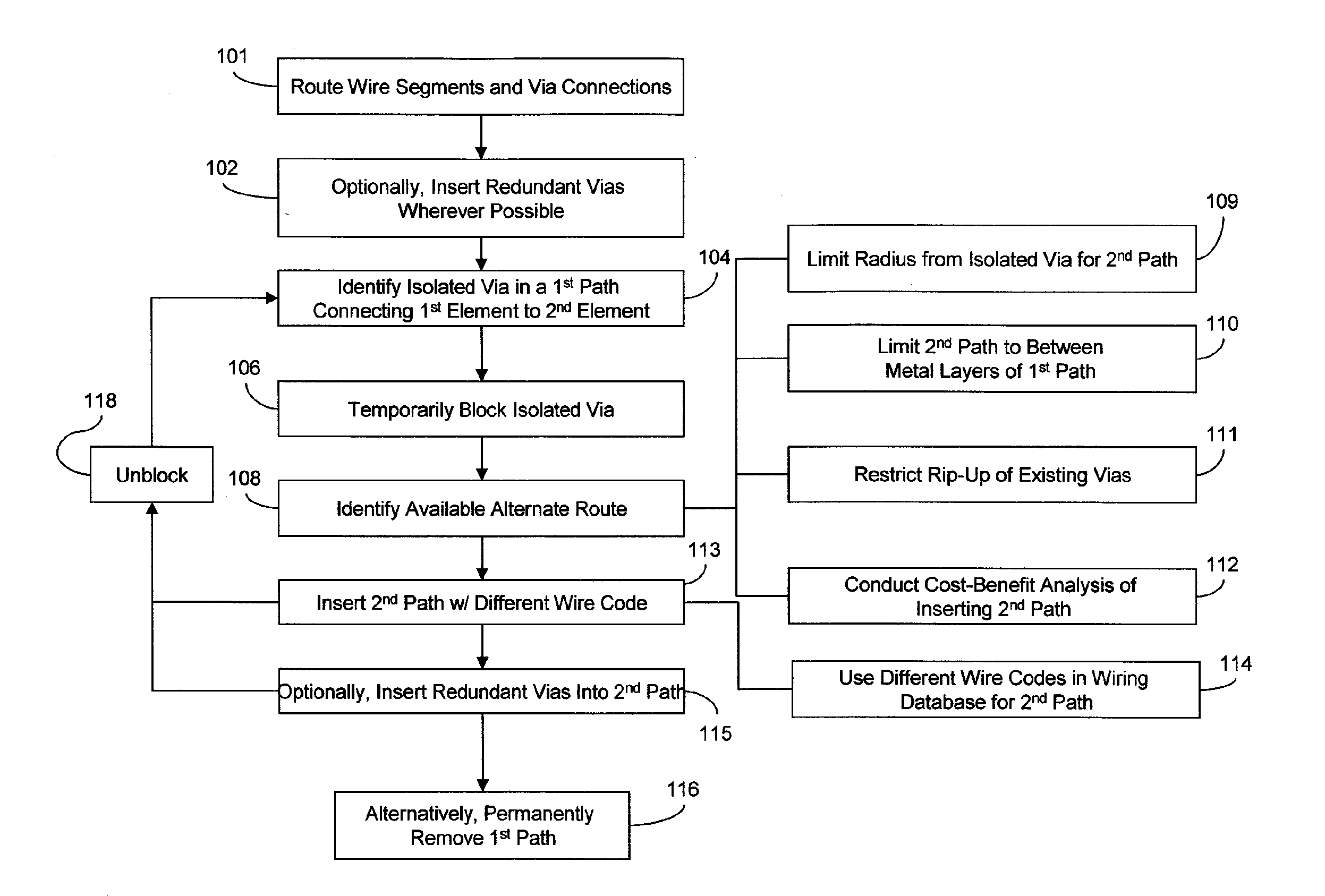

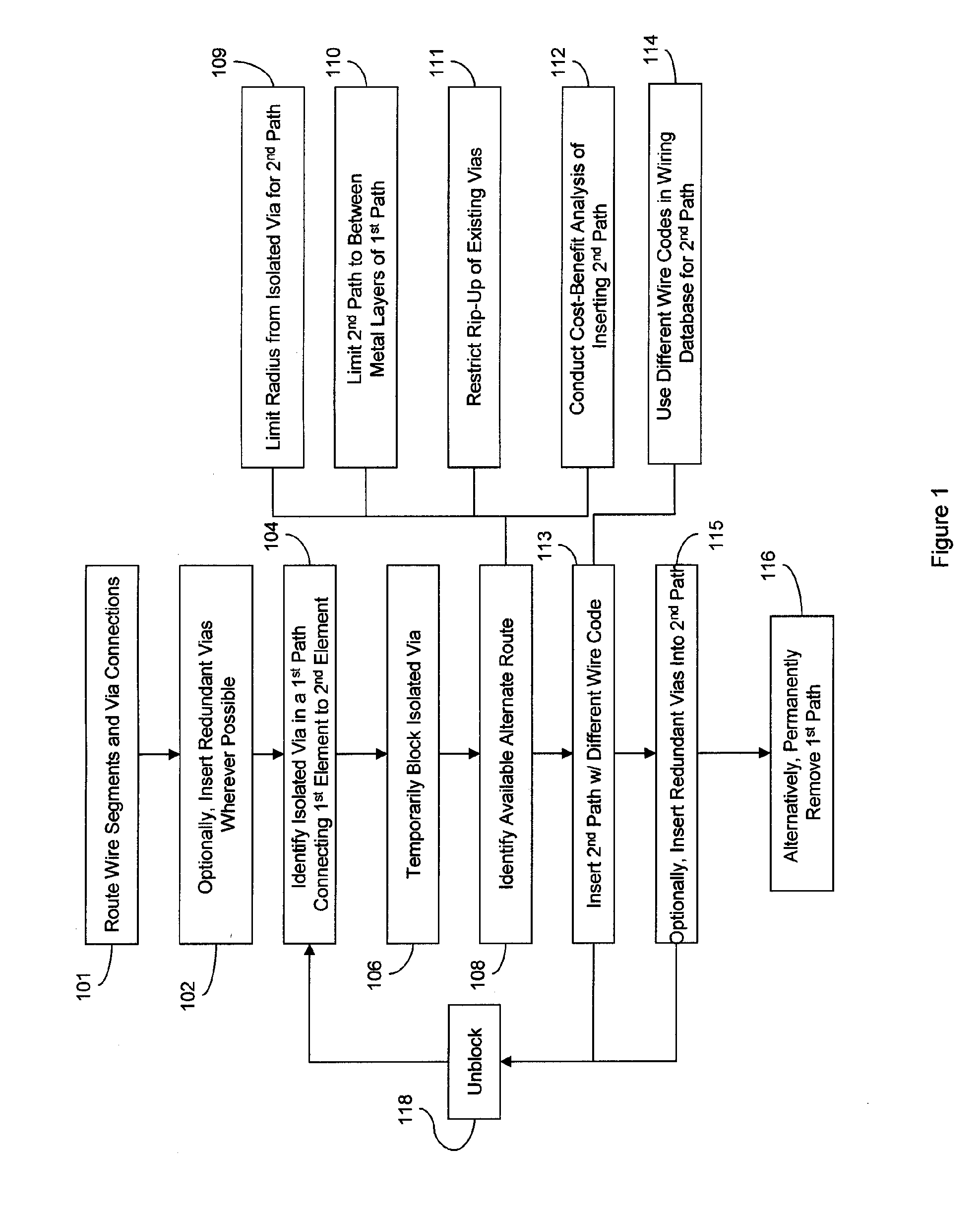

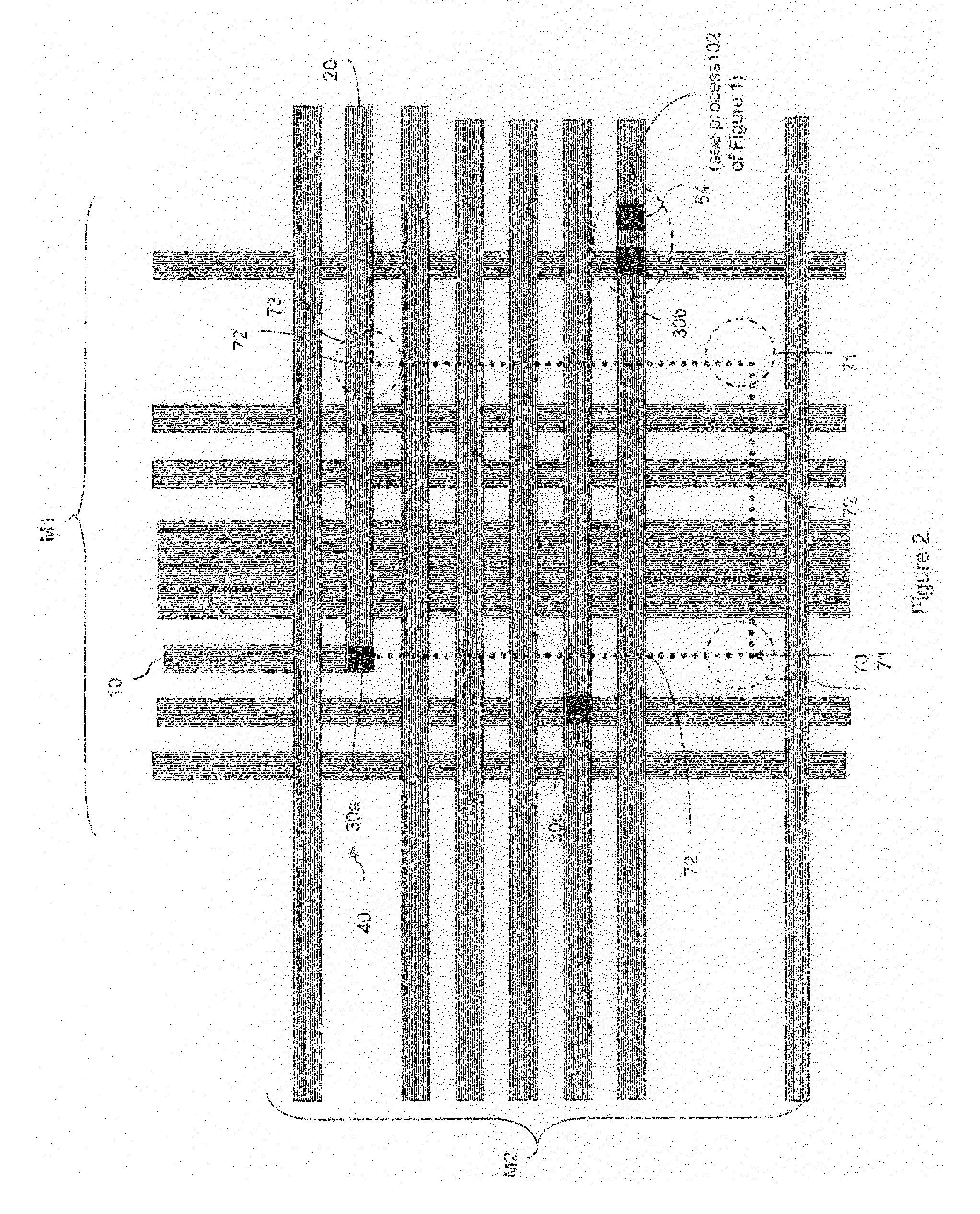

Use of redundant routes to increase the yield and reliability of a VLSI layout

ActiveUS7308669B2Increase redundancyReduce sensitivityCAD circuit designSoftware simulation/interpretation/emulationEngineeringVlsi layout

Disclosed is a method and system for inserting redundant paths into an integrated circuit. Particularly, the invention provides a method for identifying a single via in a first path connecting two elements, determining if an alternate route is available for connecting the two elements (other than a redundant via), and for inserting a second path into the available alternate route. The combination of the first and second paths provides greater redundancy than inserting a redundant via alone. More importantly, such redundant paths provide for redundancy when congestion prevents a redundant via from being inserted adjacent to the single via. An embodiment of the method further comprises removing the single via and any redundant wire segments, if all of the additional vias used to form the second path can be made redundant.

Owner:GLOBALFOUNDRIES US INC

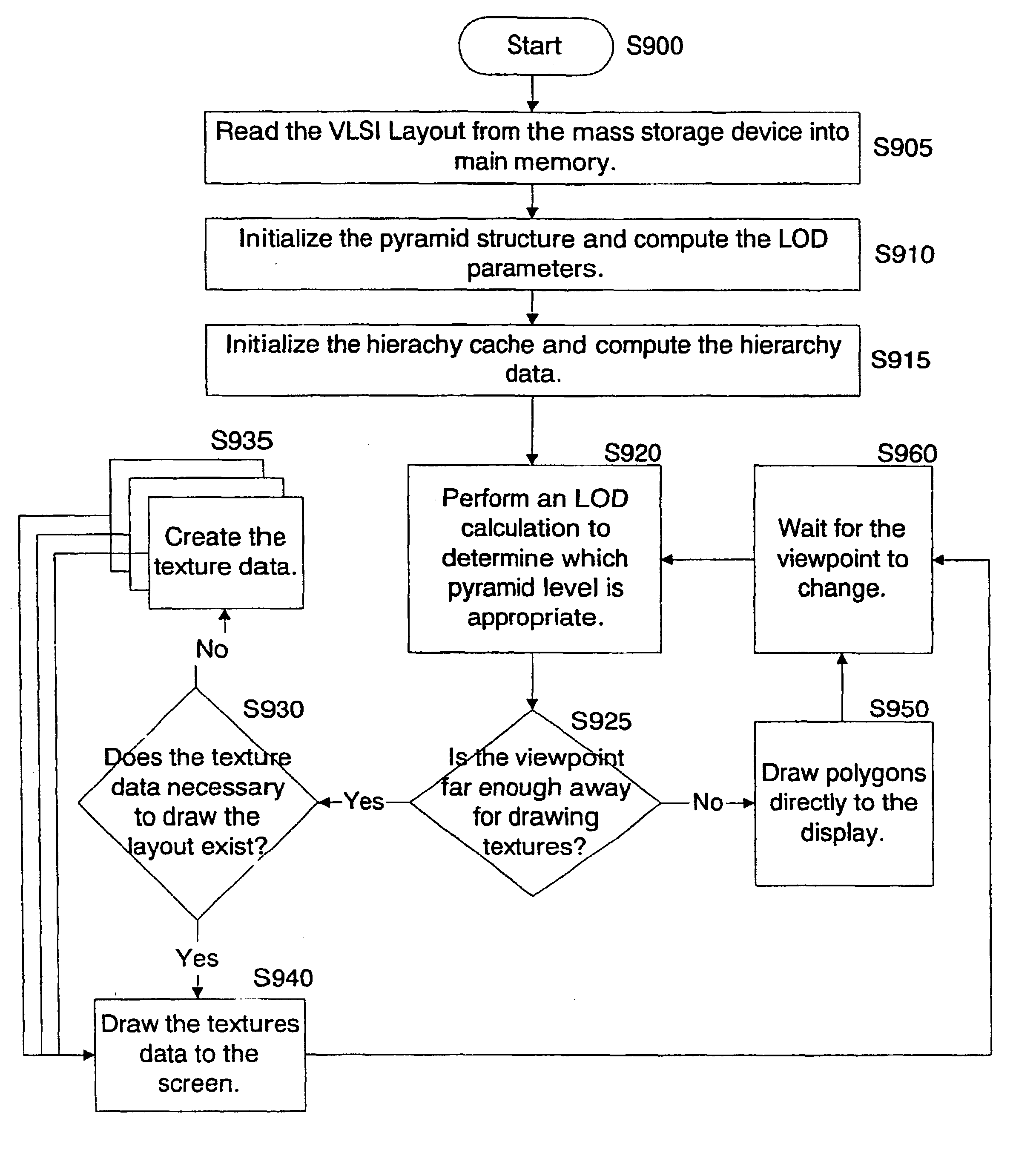

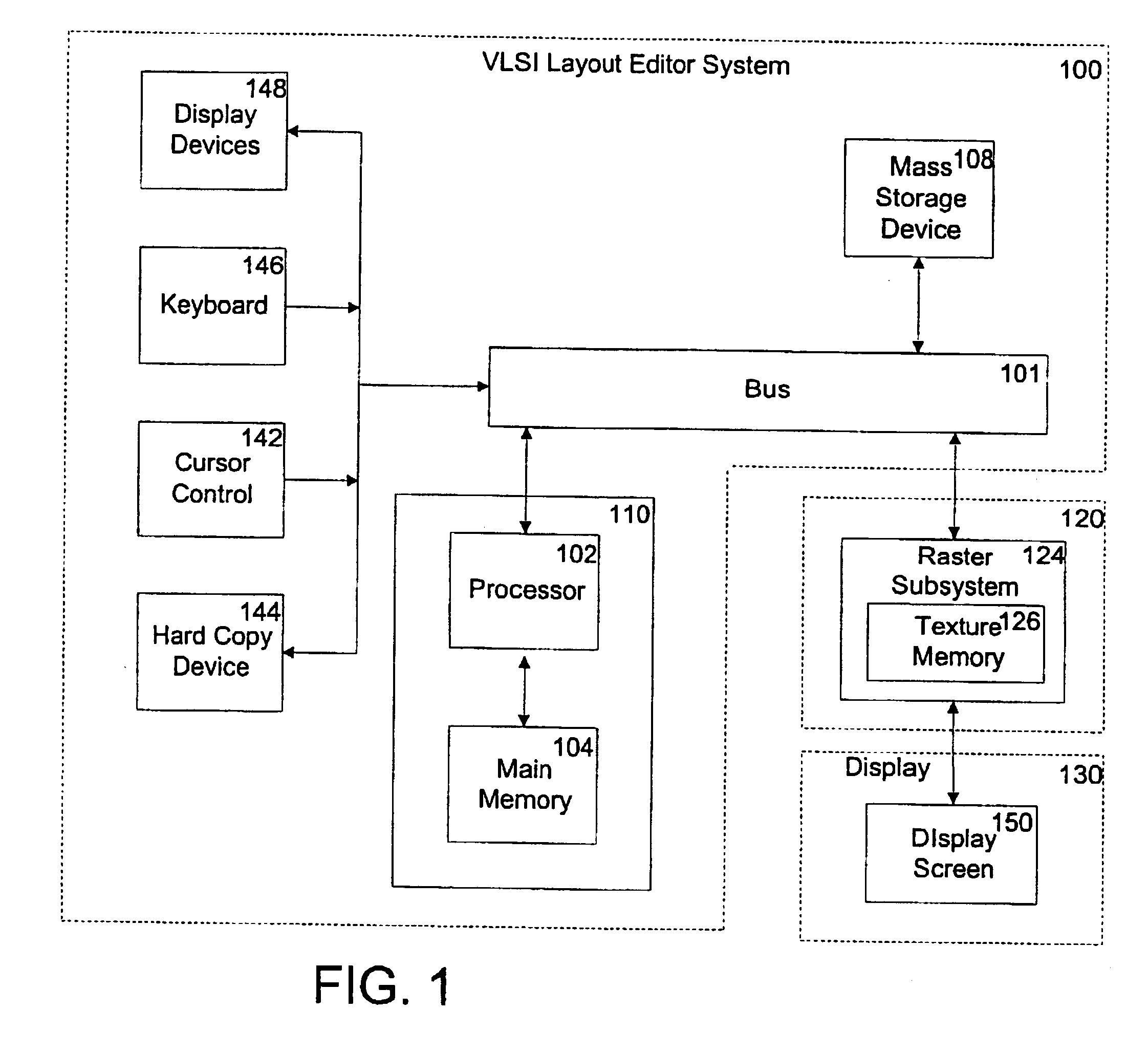

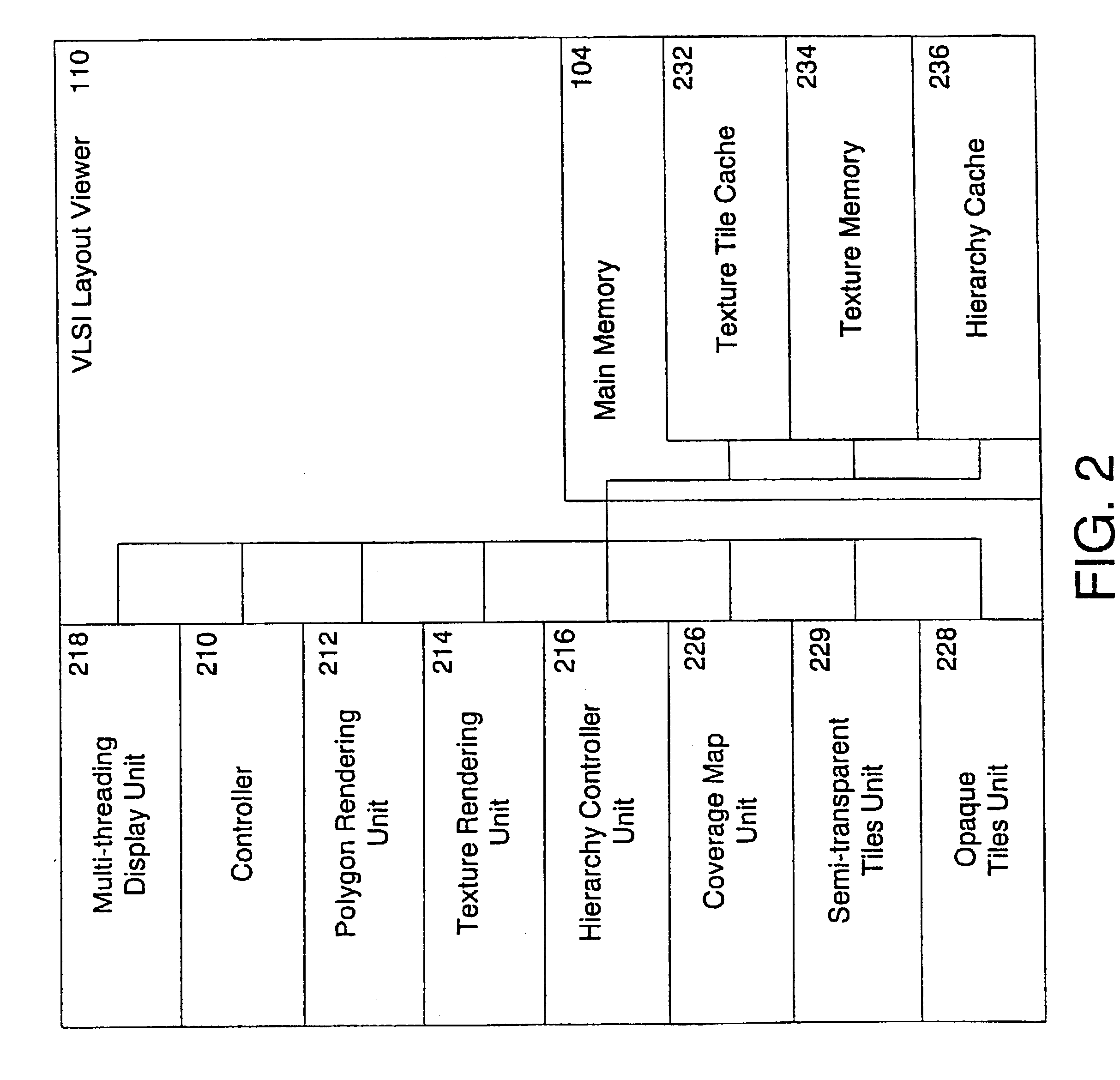

Method and system for displaying VLSI layout data

InactiveUS6886148B2Accurate photo-realistic representationAccurate real-time navigationDigital storageComputer programmed simultaneously with data introductionGeometric propertyComputer graphics (images)

A VLSI layout editor and method for using same that increases display and re-display speed and accuracy uses properties inherent to VLSI layouts that allows them to be displayed efficiently and accurately independent of the canonical expression of the VLSI design. The VLSI layout editor and methods for using same use precomputed images that each represent a portion of the VLSI layout, a hierarchy cache that includes multiple LOD versions of selected sub-designs in the pre-computed images, and selected direct determination of the viewable representation from the canonical expression for at least one LOD. Apparatus and methods according to the present invention can render a particular type of data whose canonical form is smaller than its corresponding displayed image thereof when the displayed image has geometric properties that allow heuristics and rasterization for dynamic and accurate expansion using selected combined techniques. Texture mapping and mipmapping can be used to accurately reduce, expand and reorder layers in a viewable image expanded from a canonical expression of the VLSI layout.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

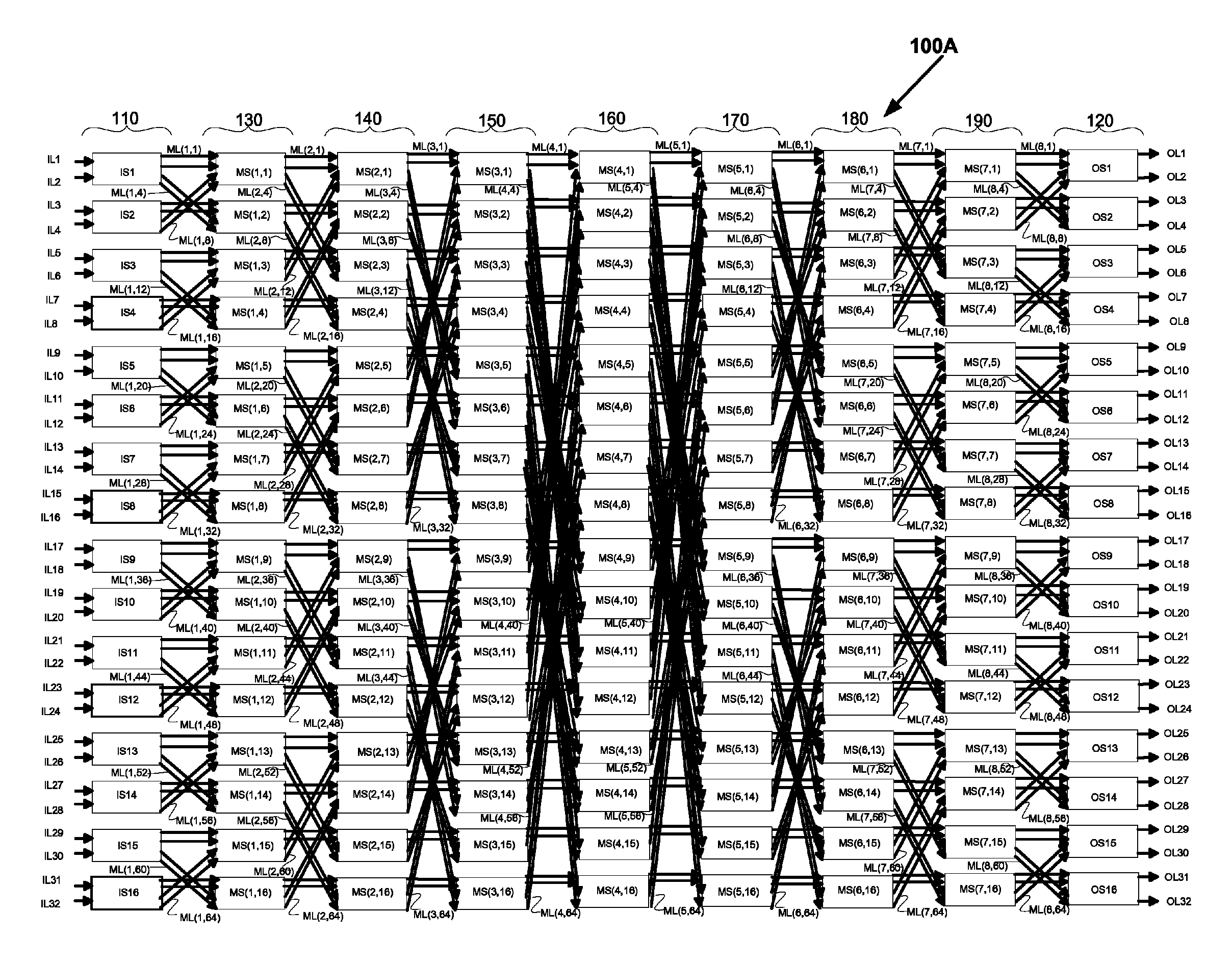

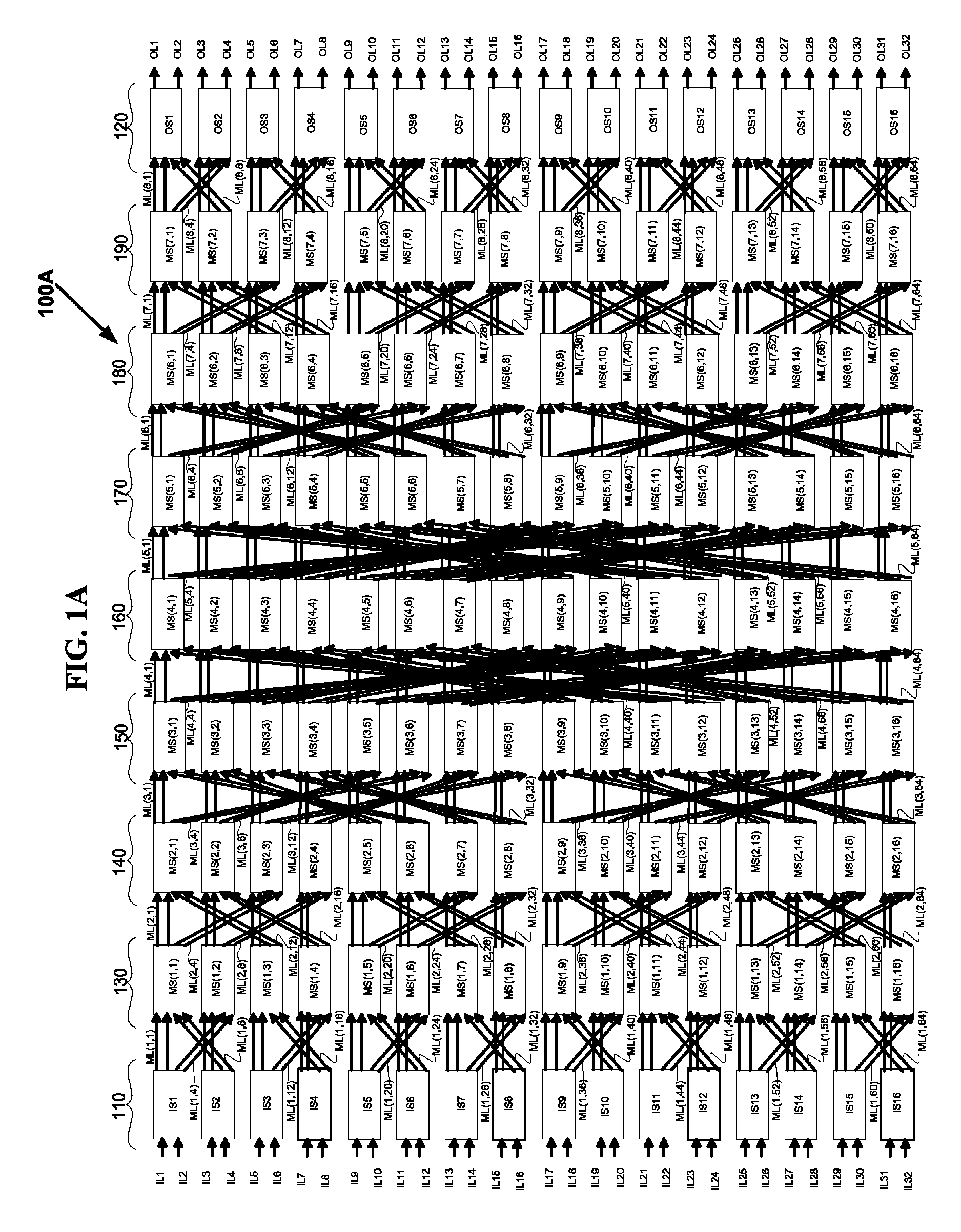

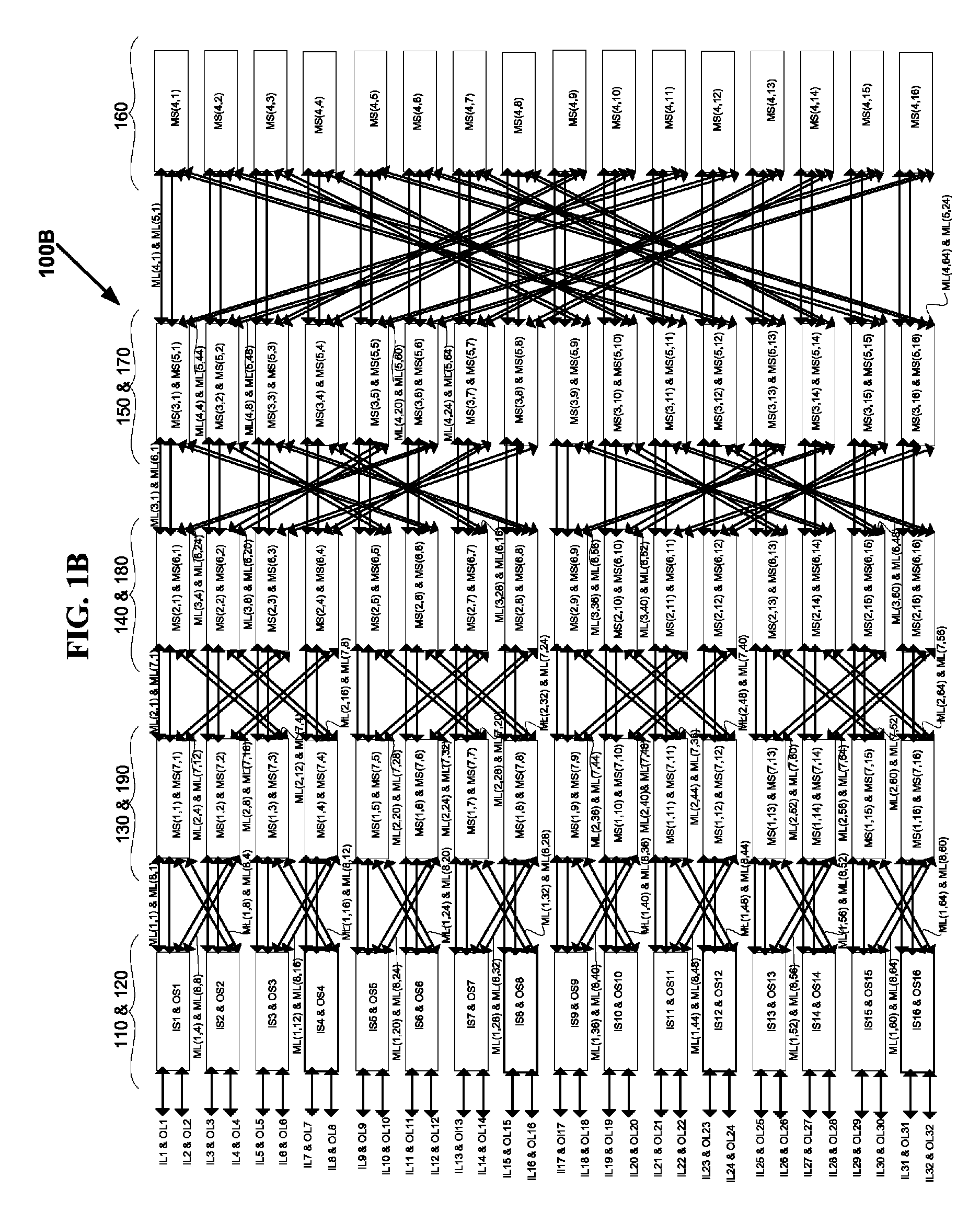

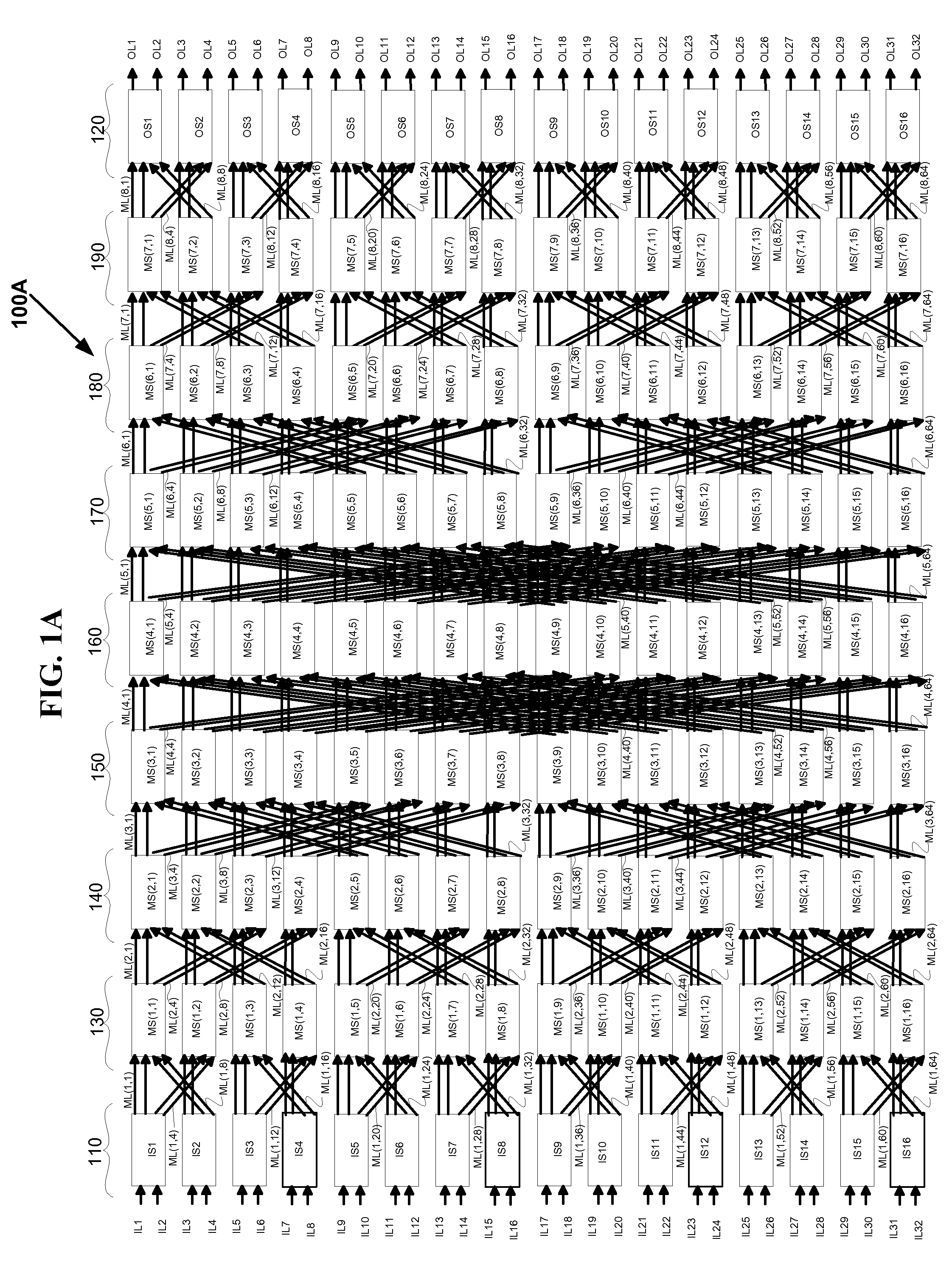

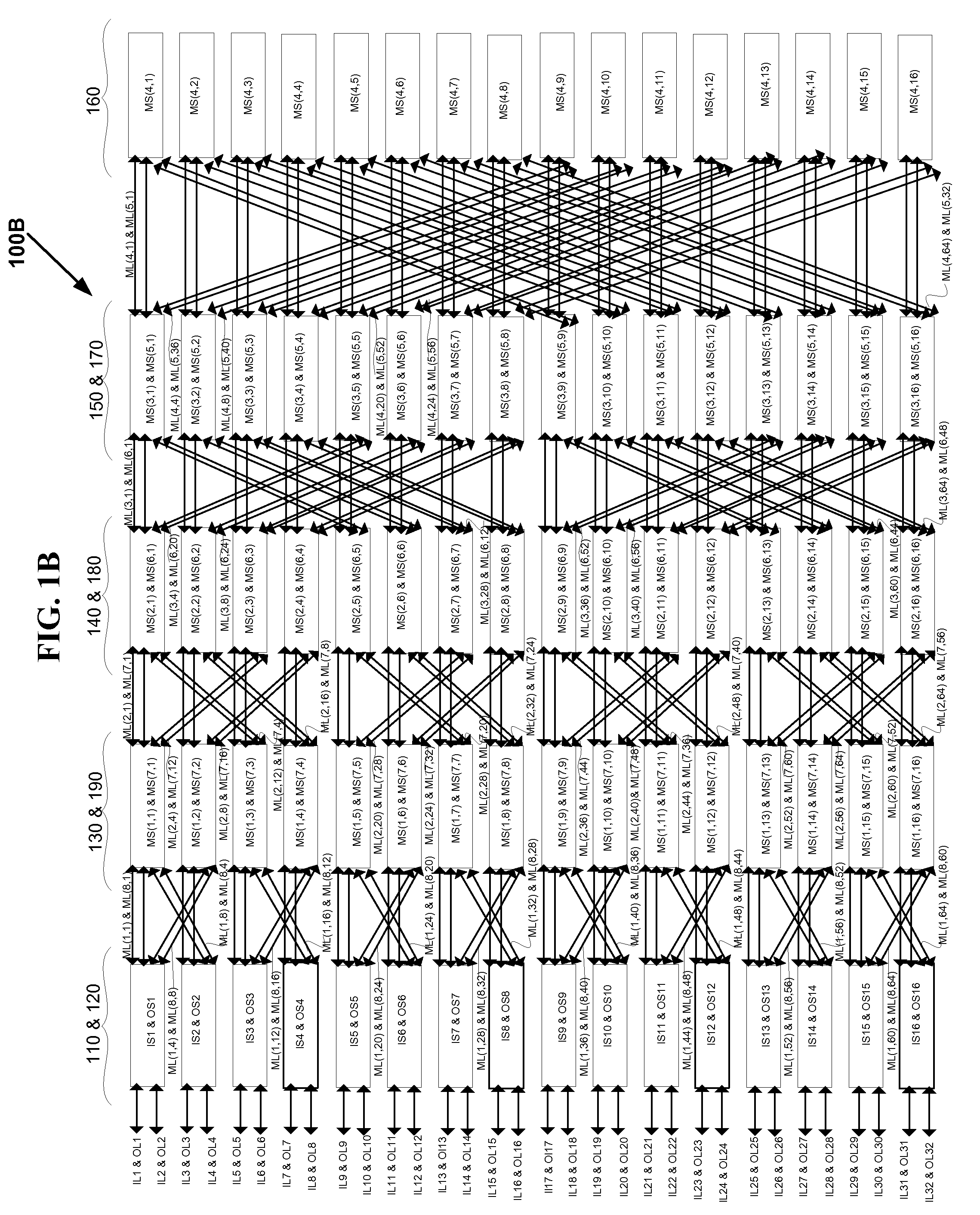

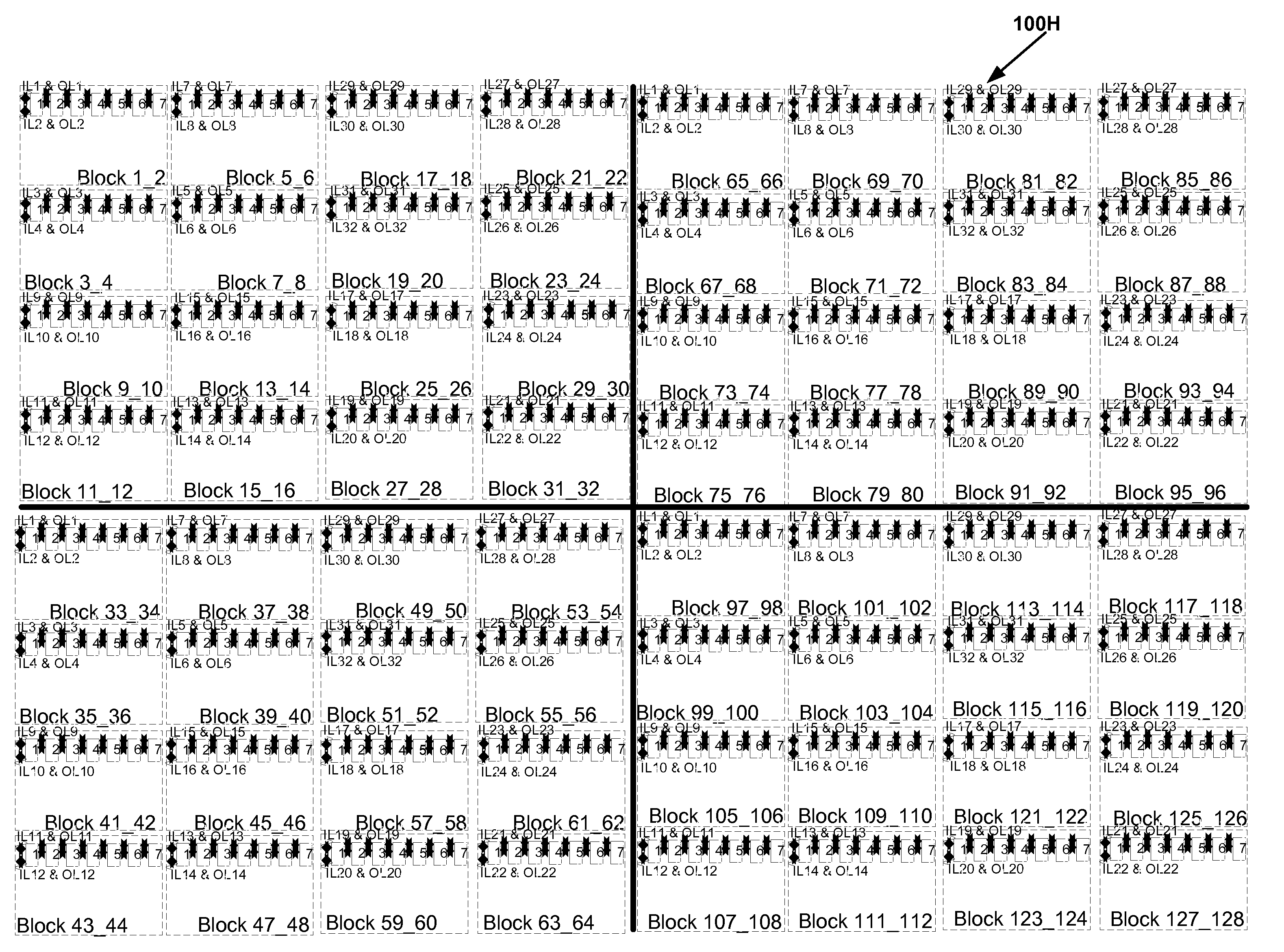

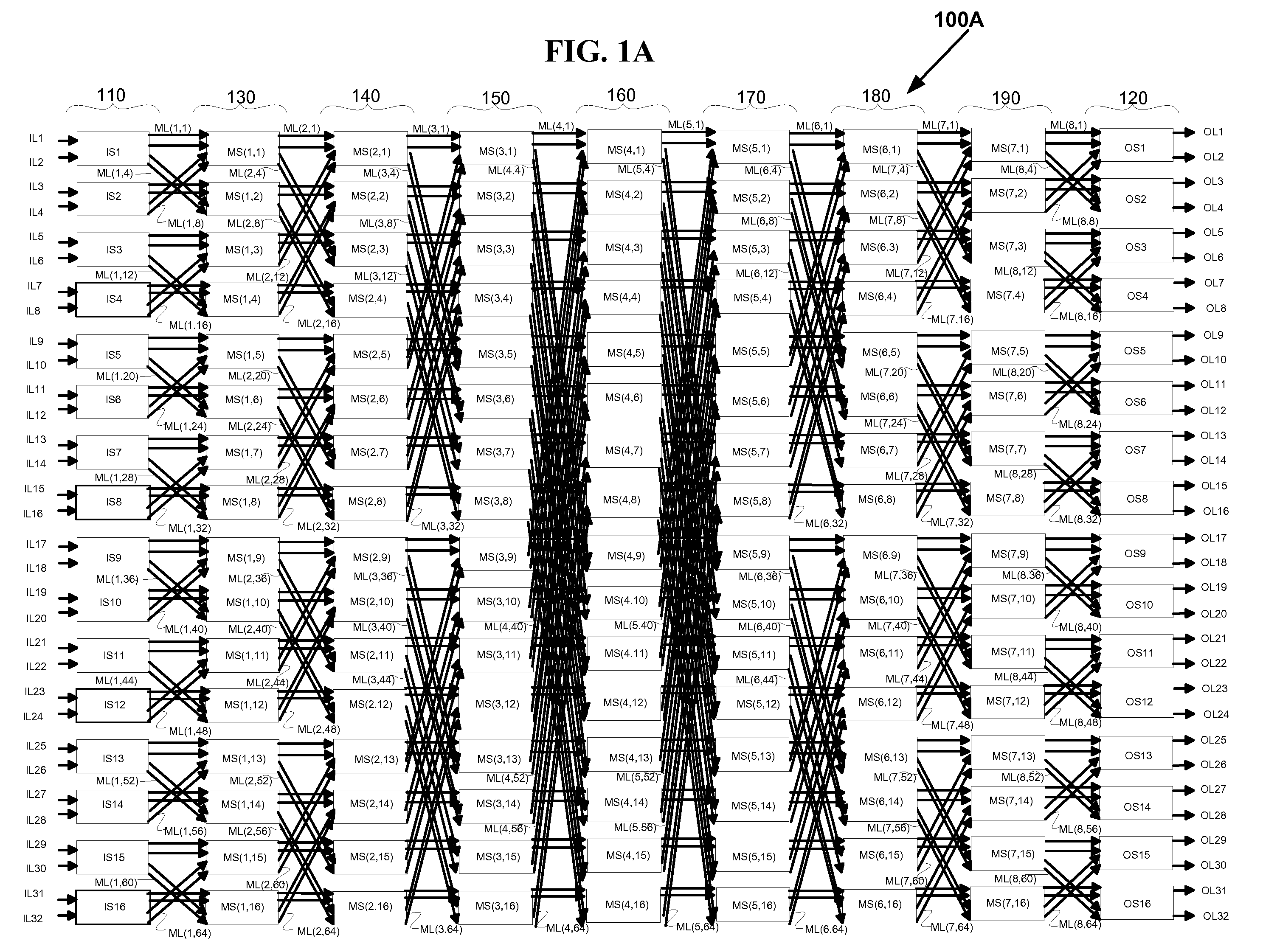

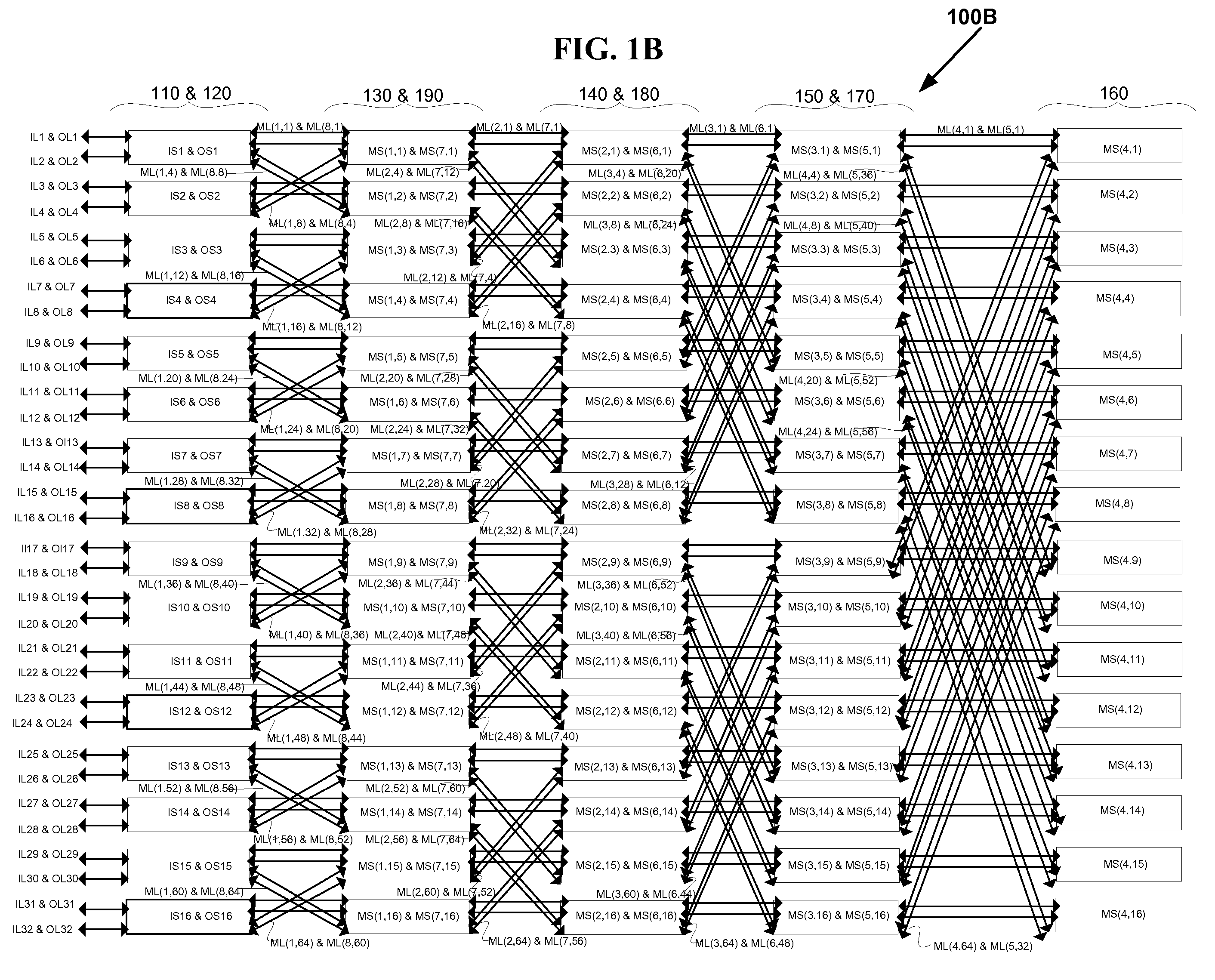

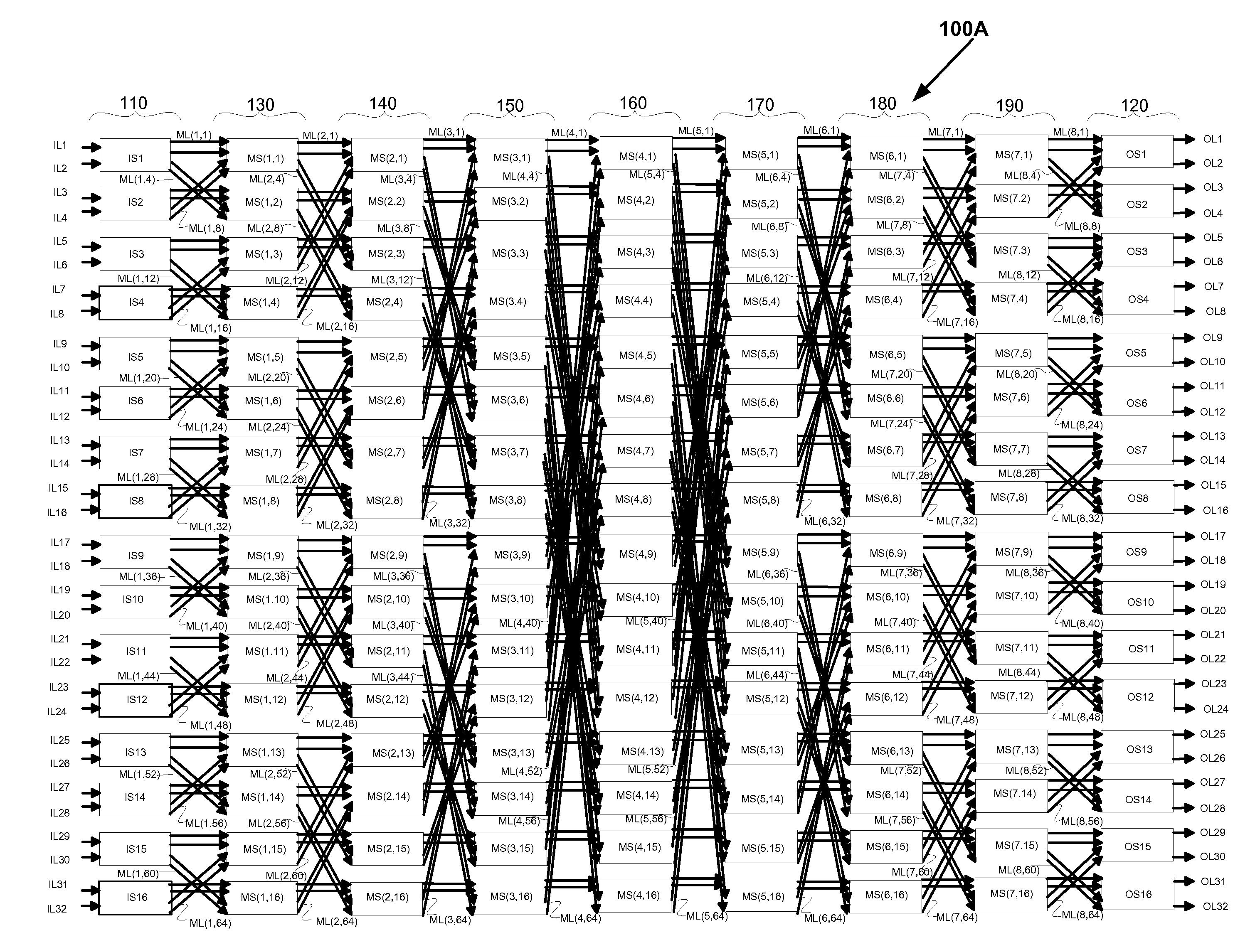

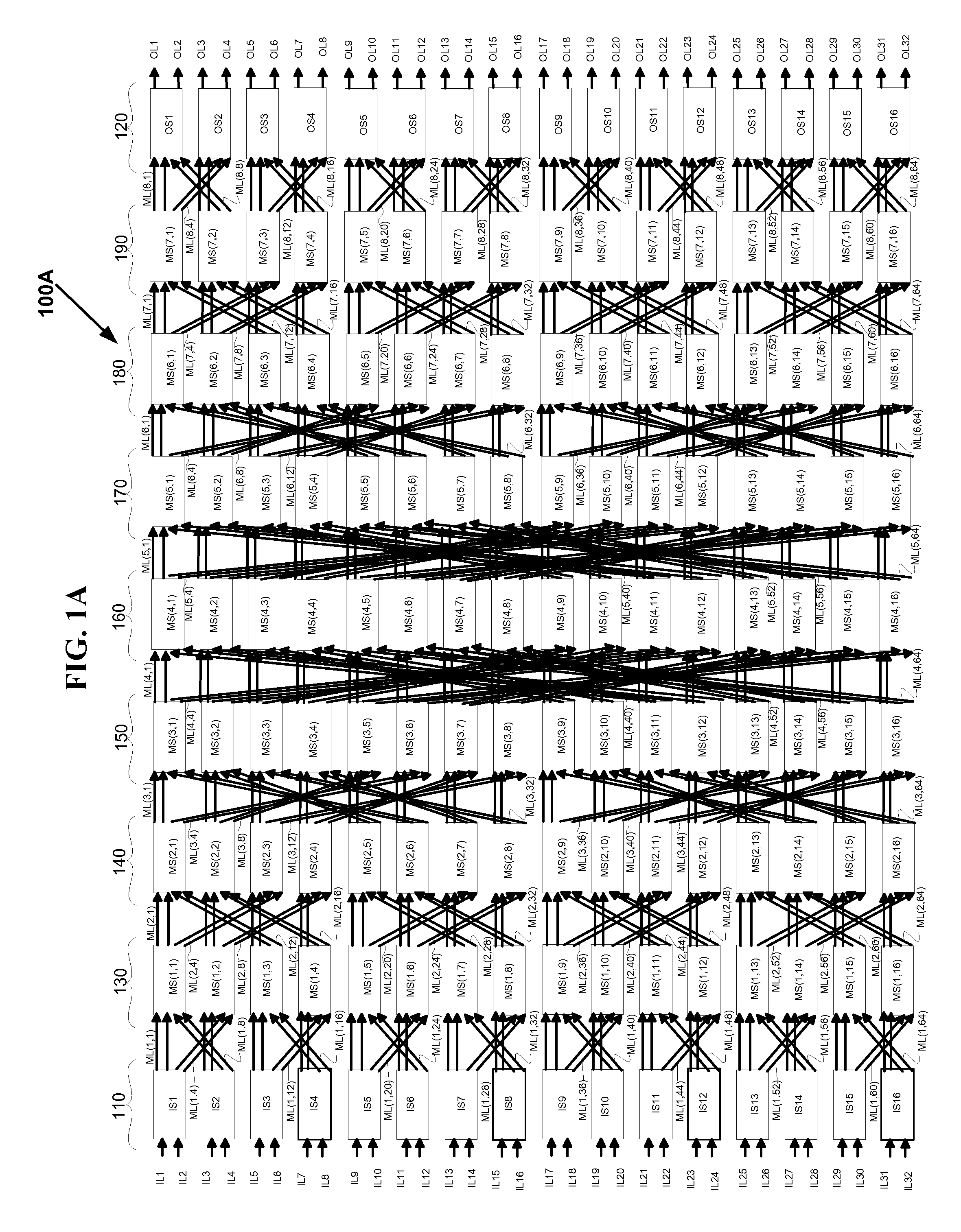

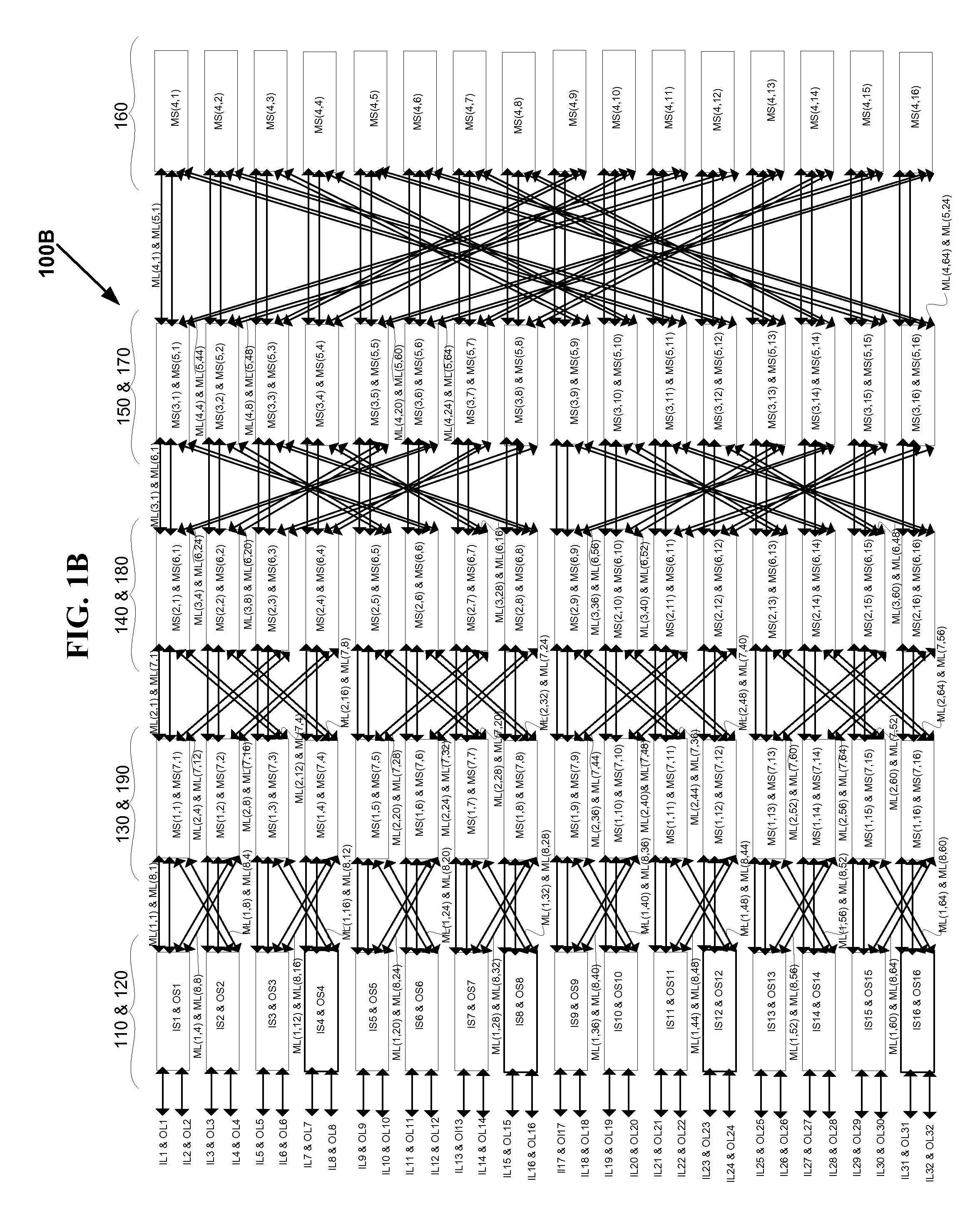

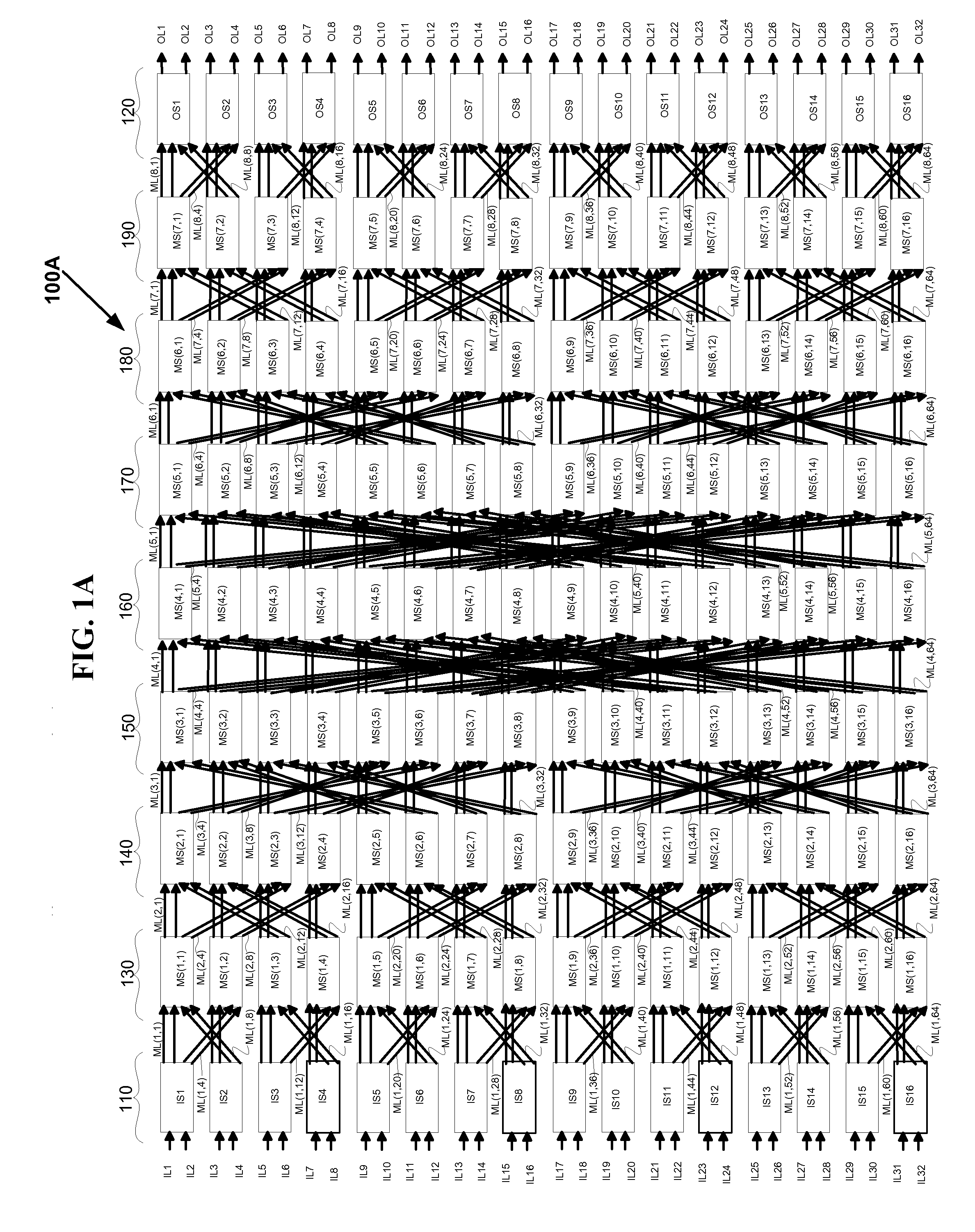

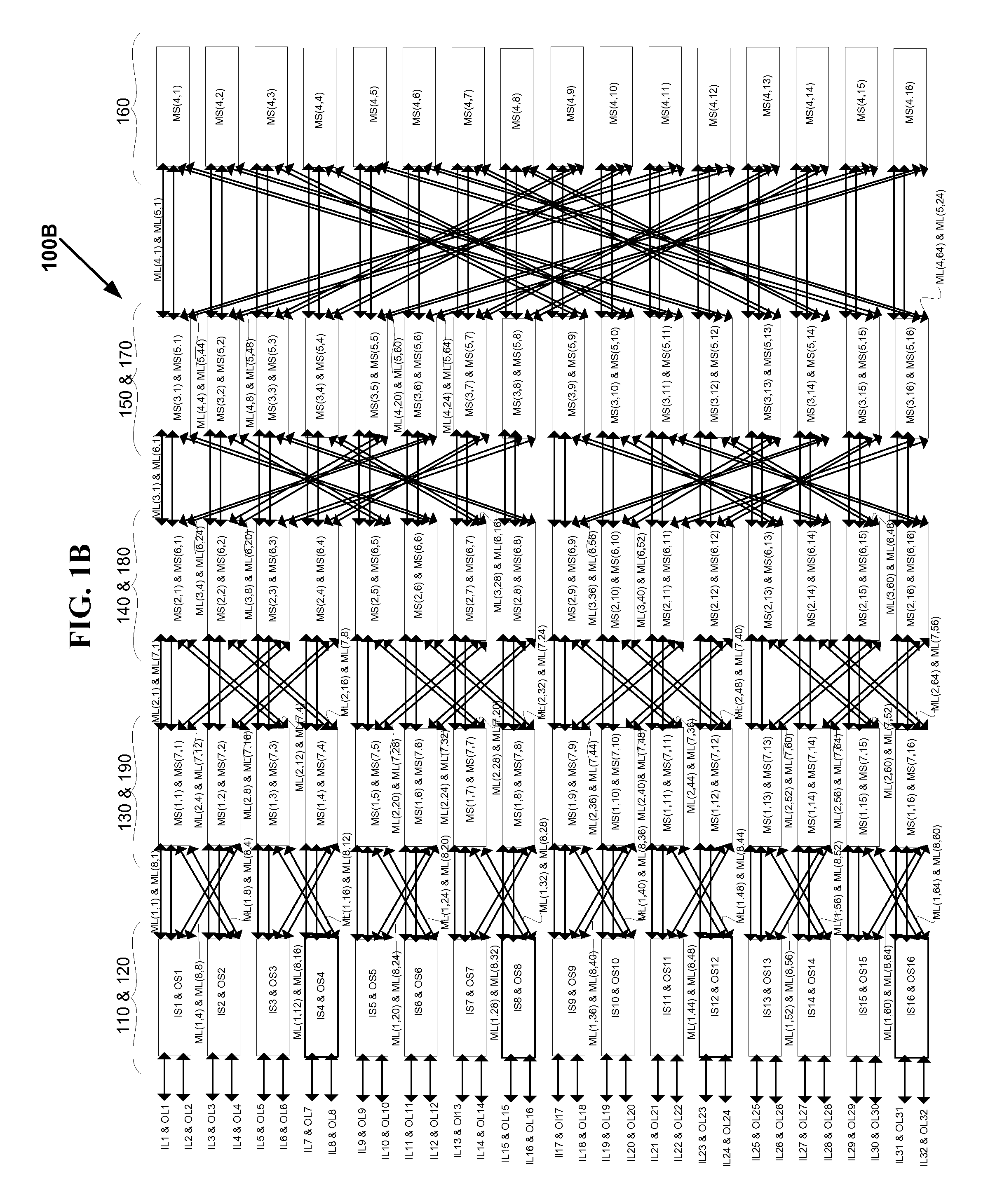

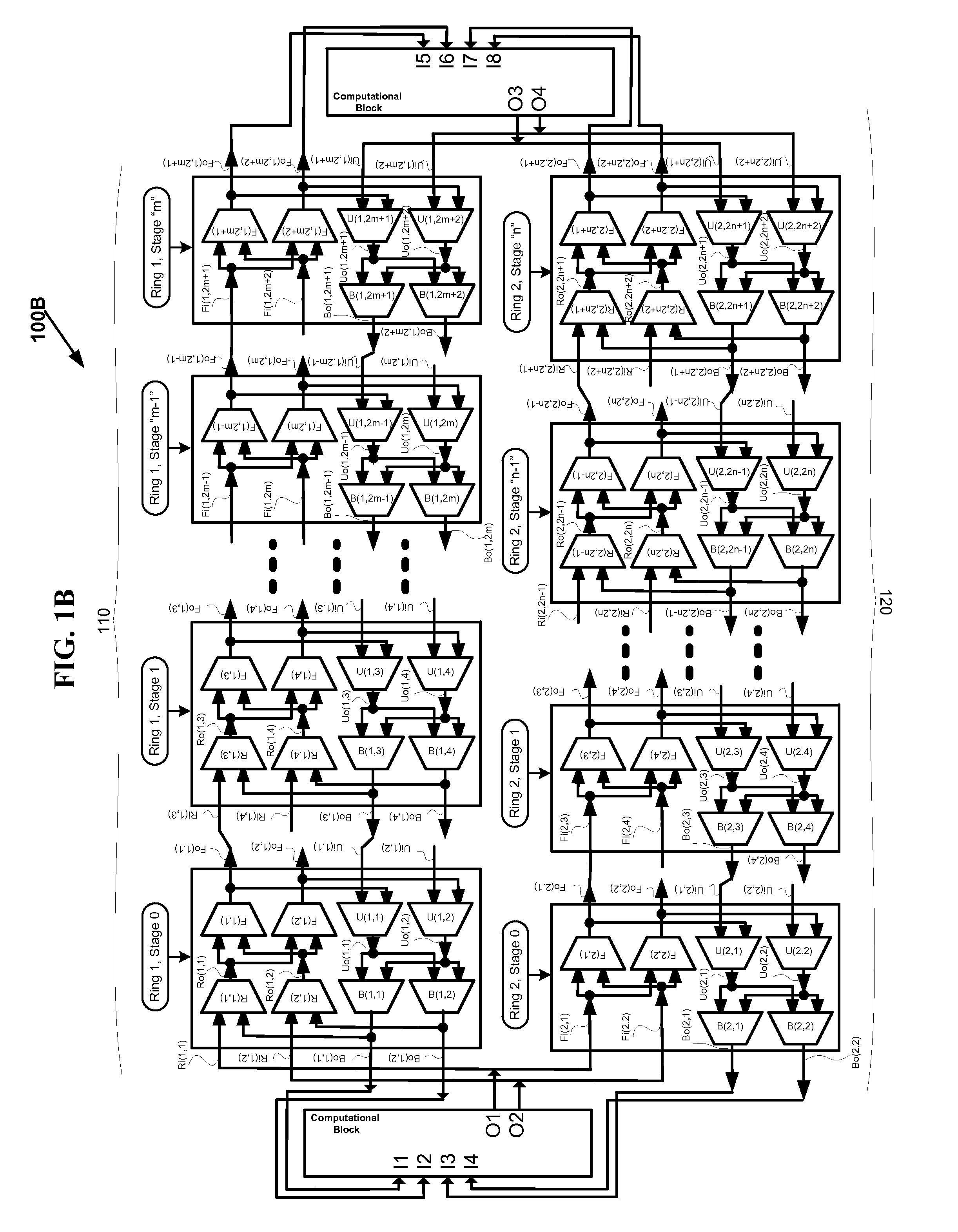

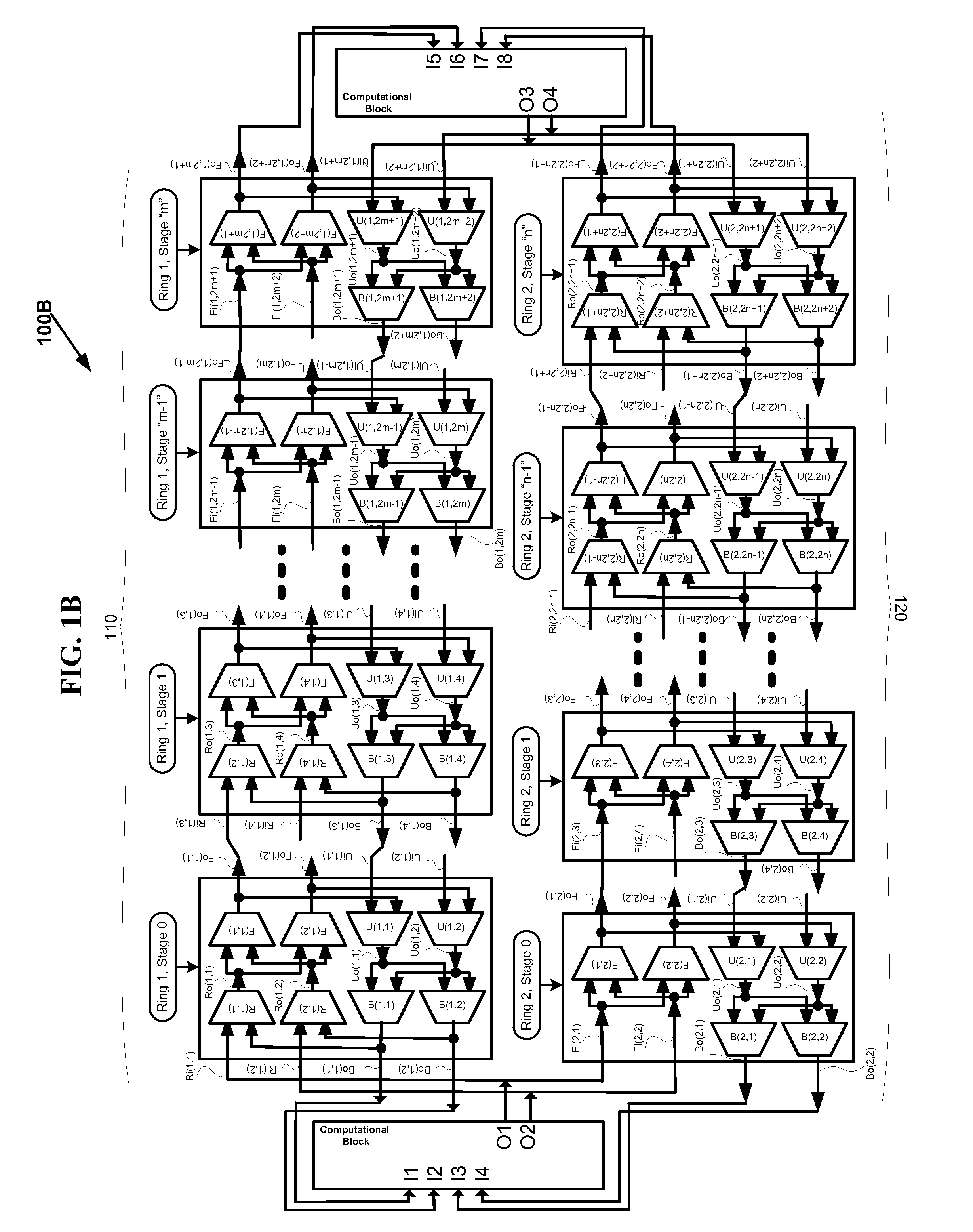

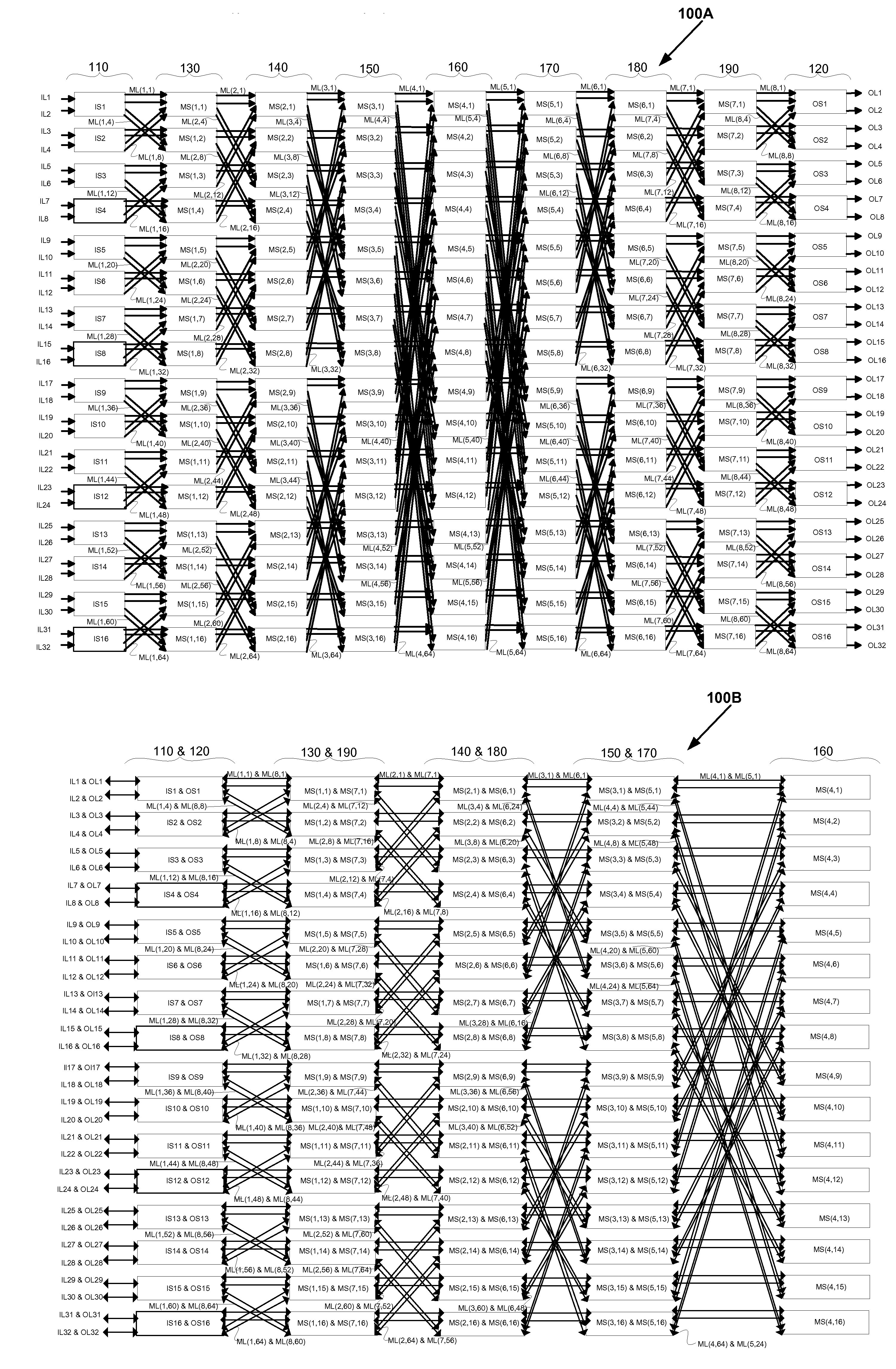

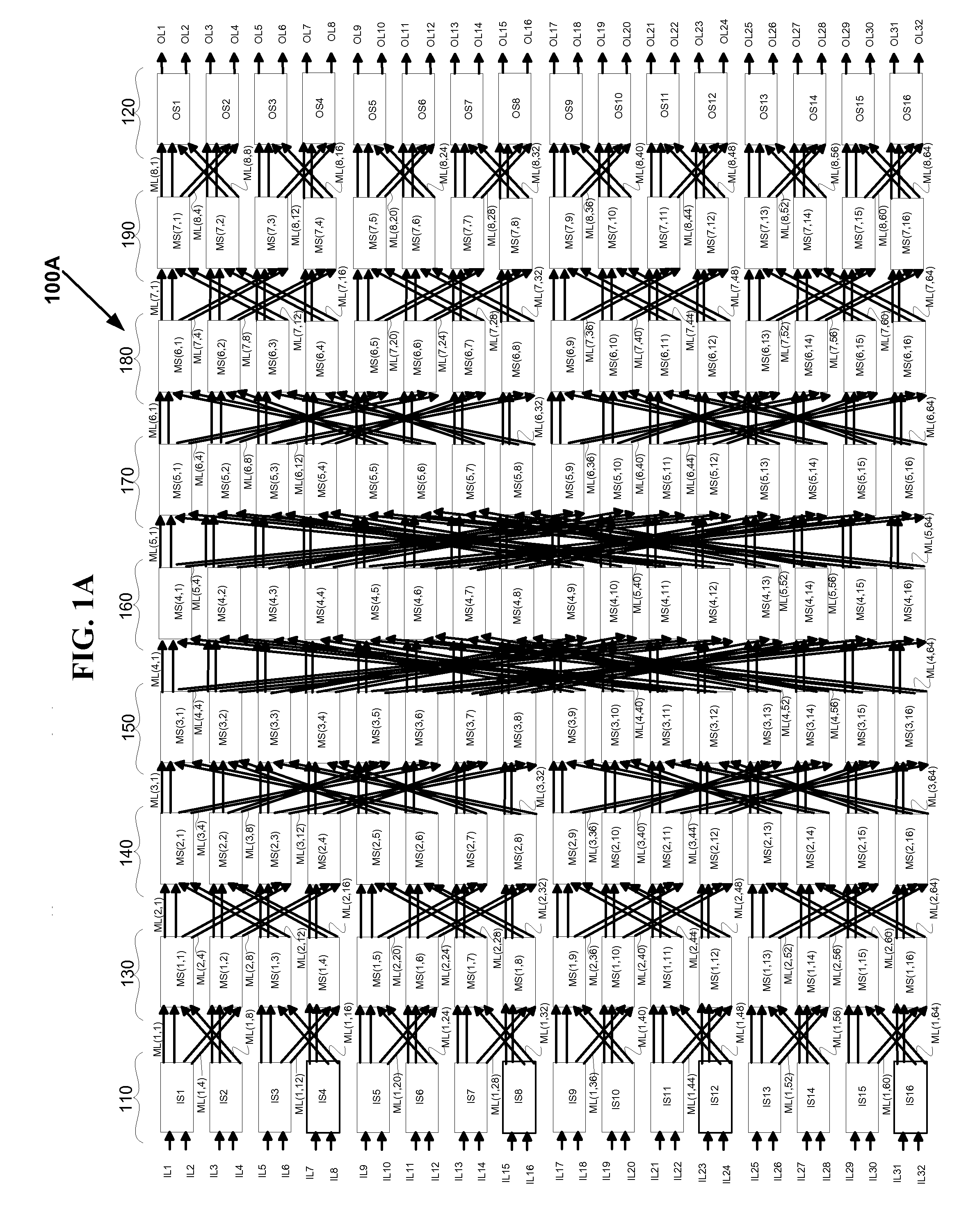

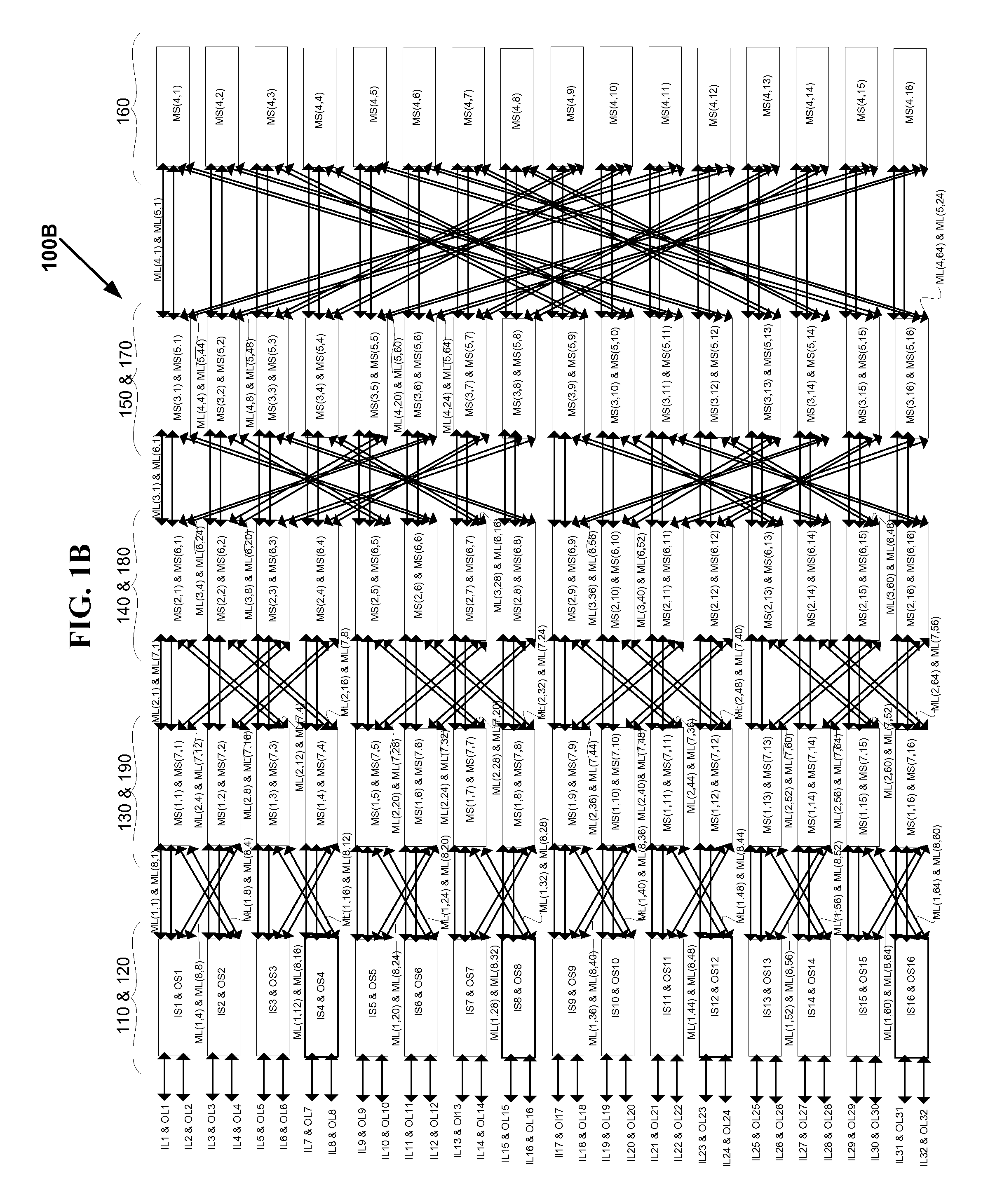

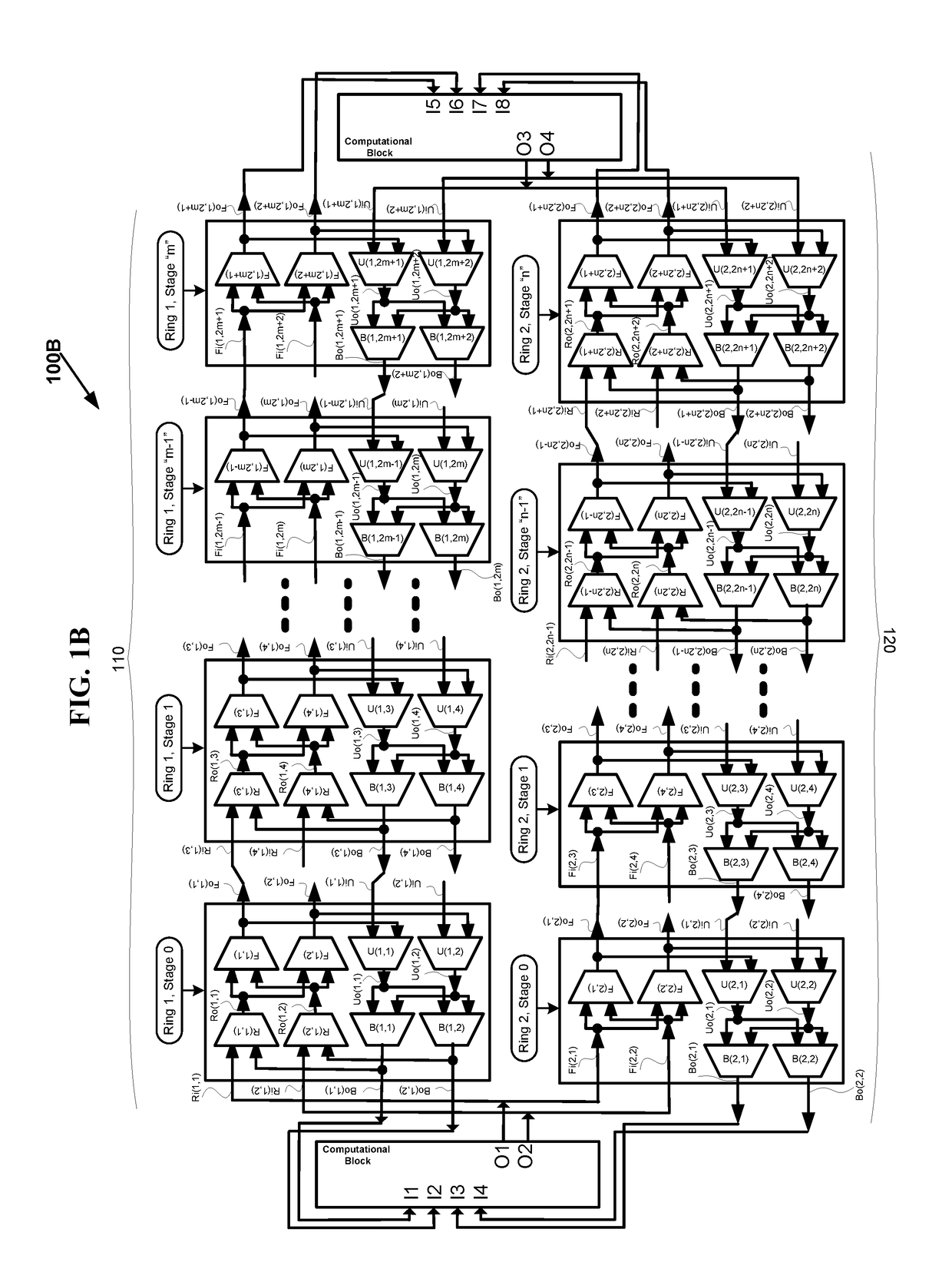

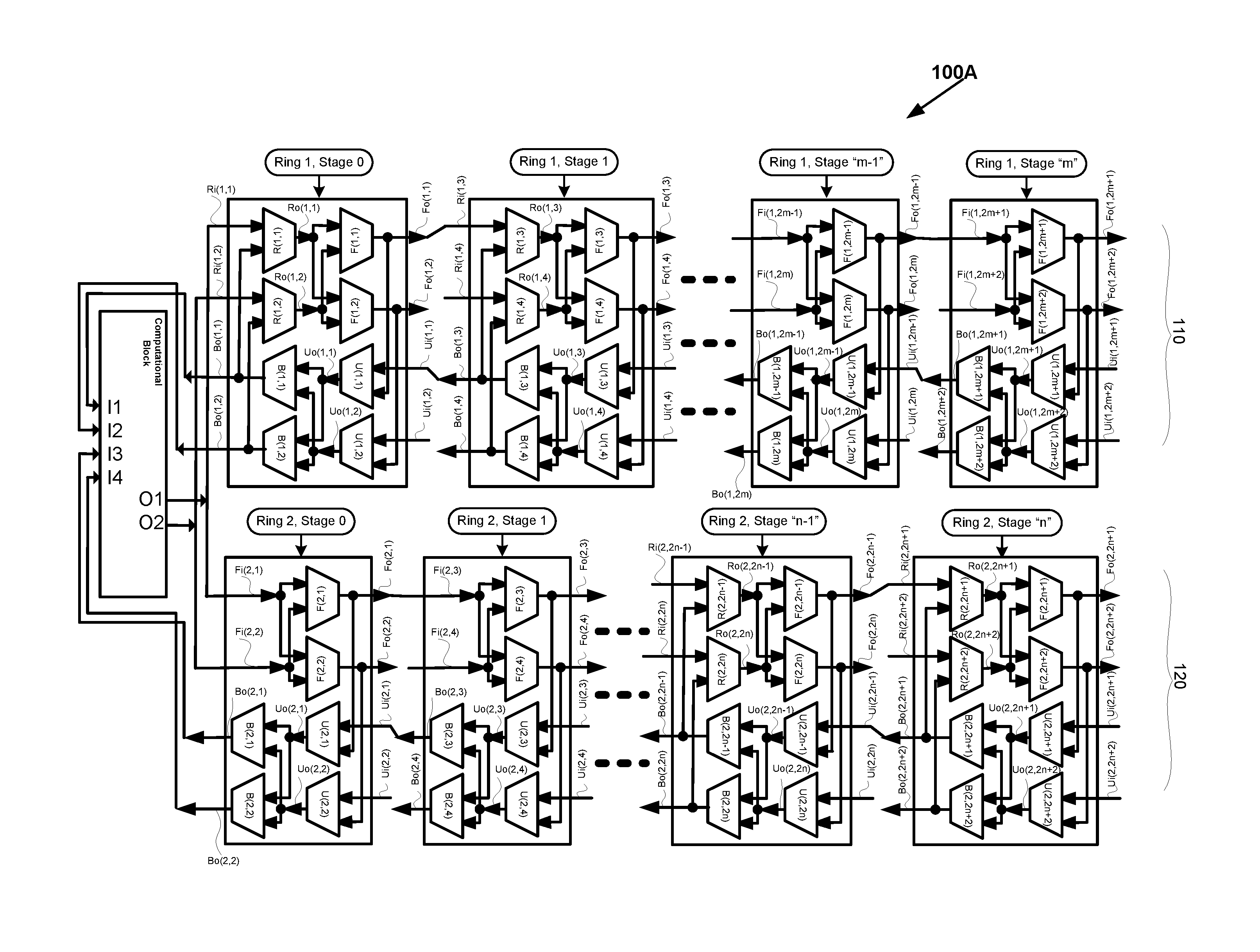

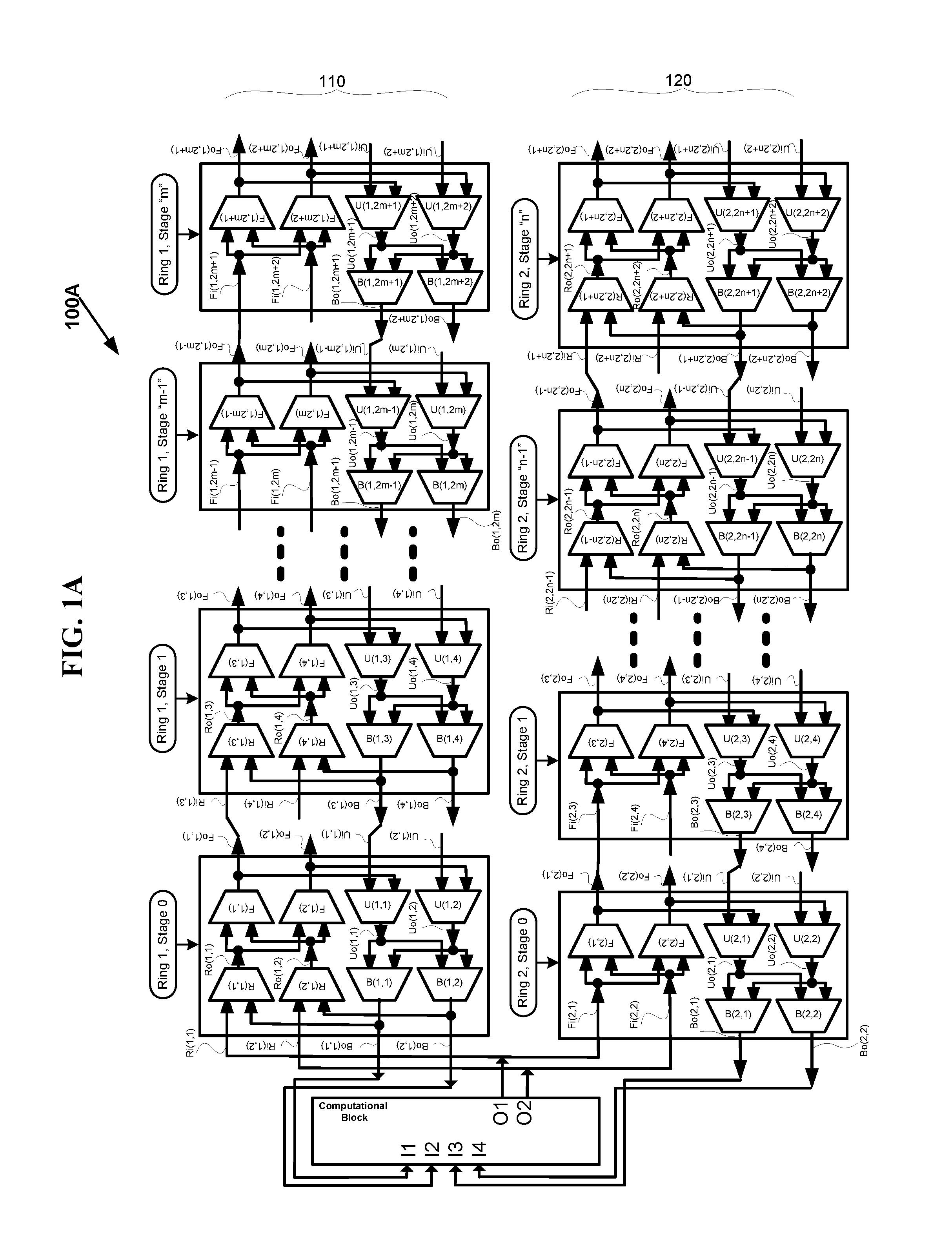

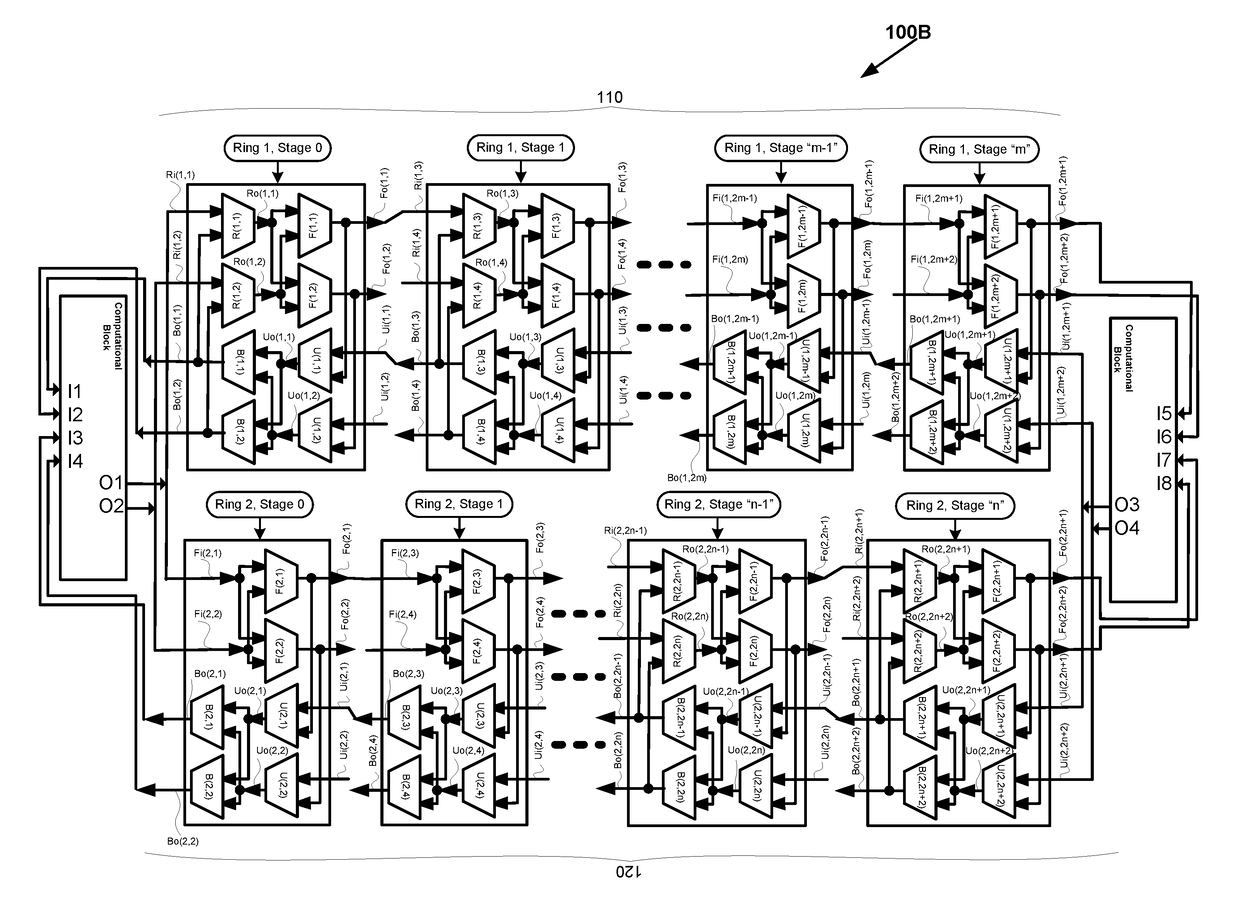

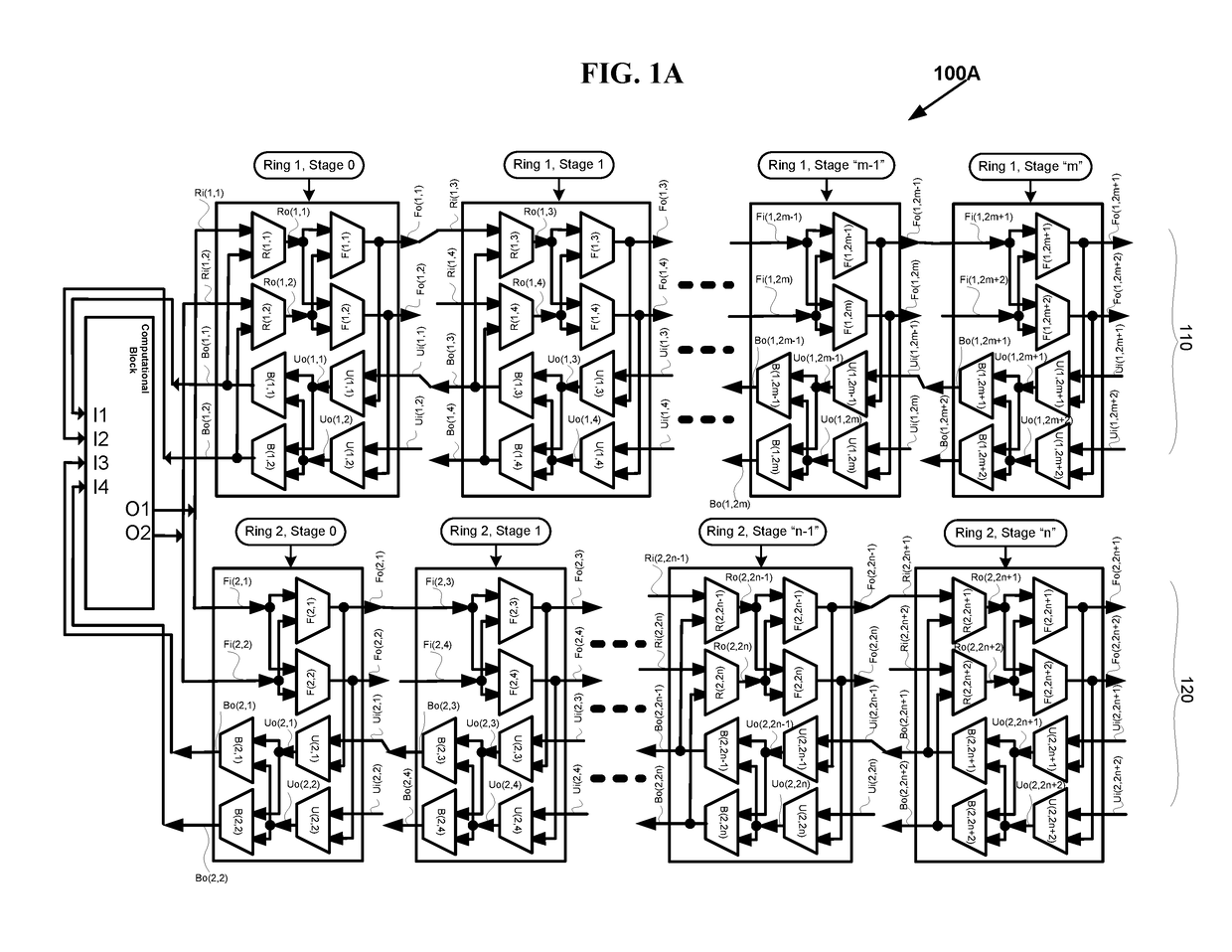

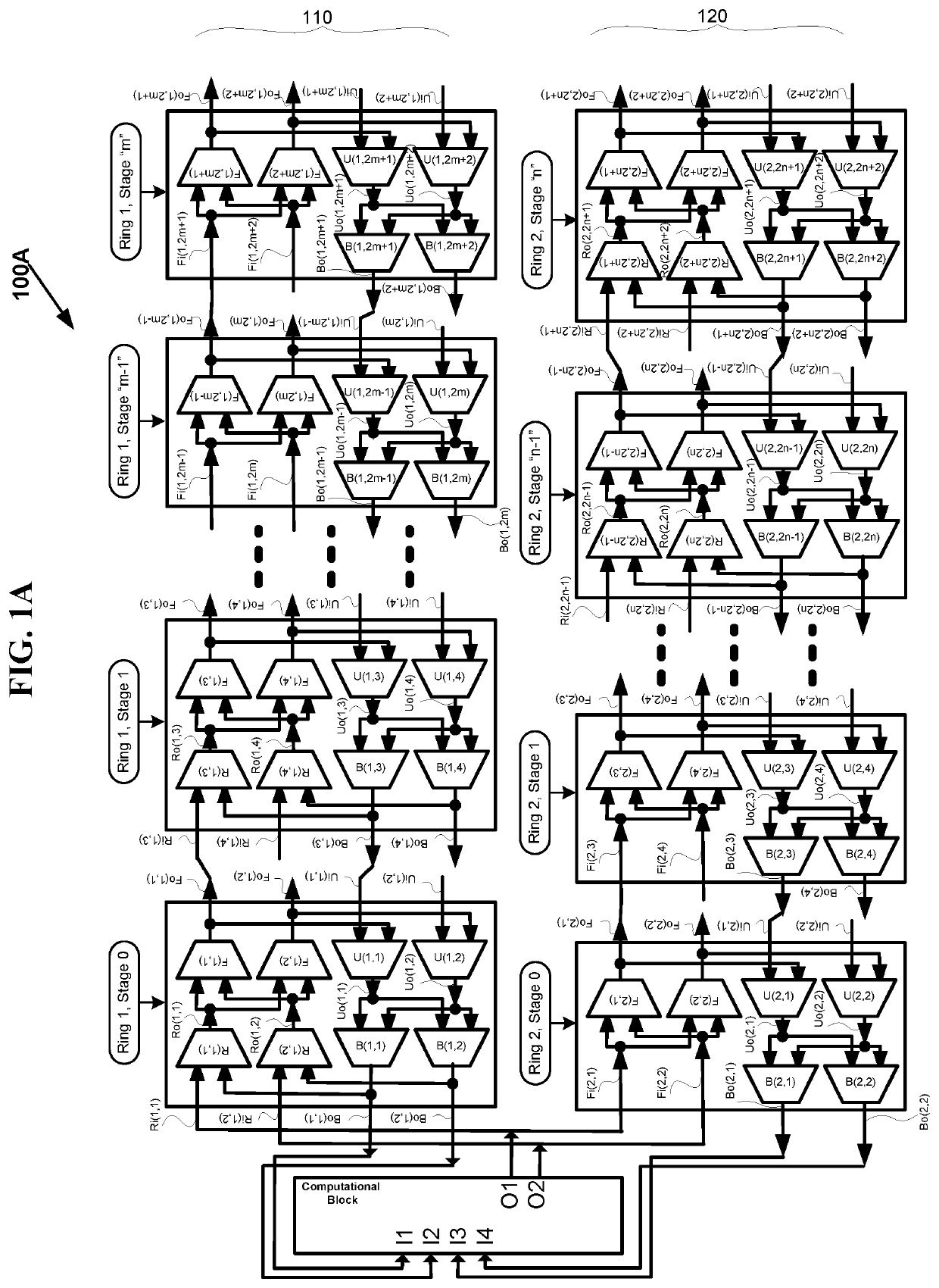

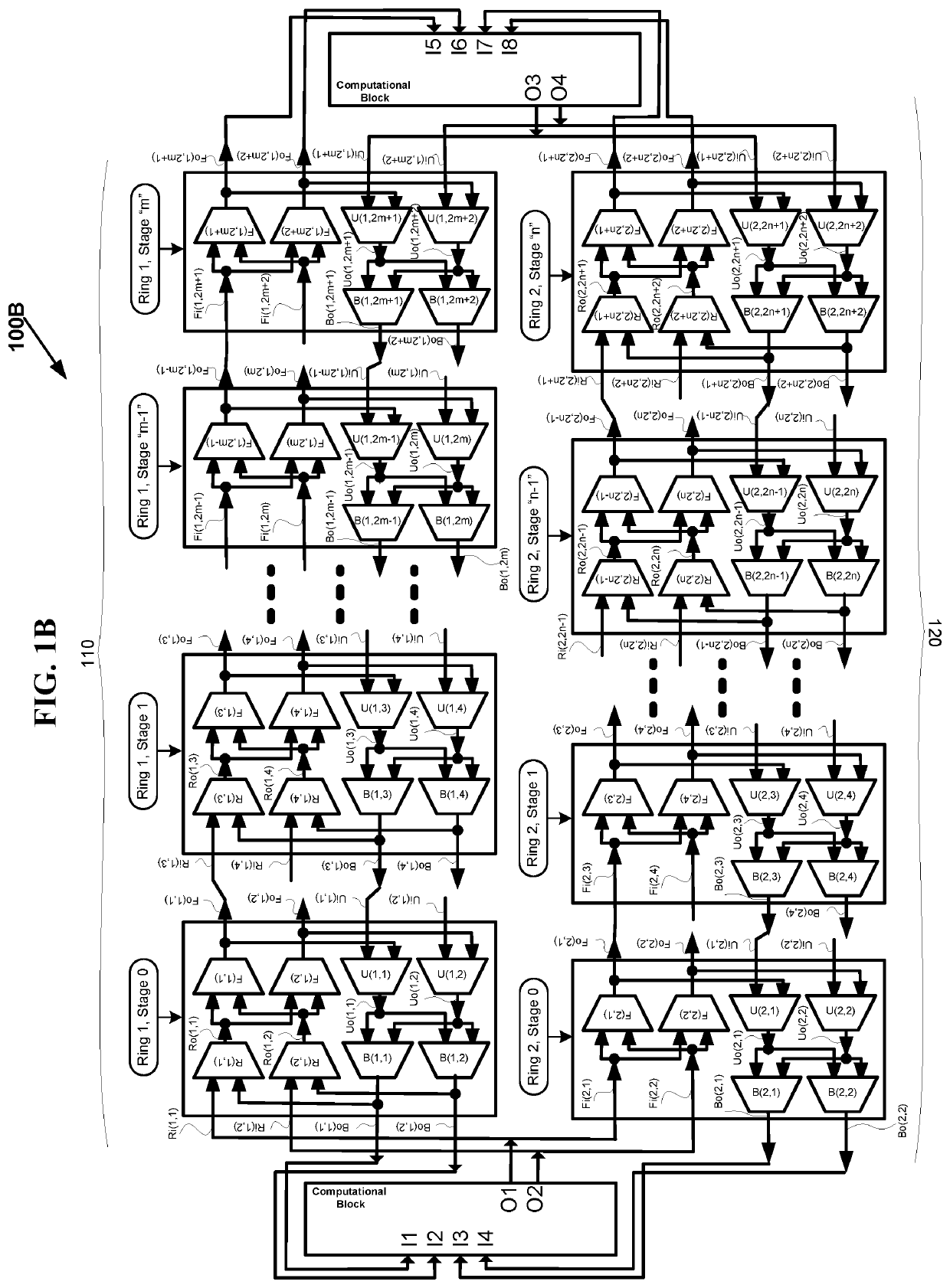

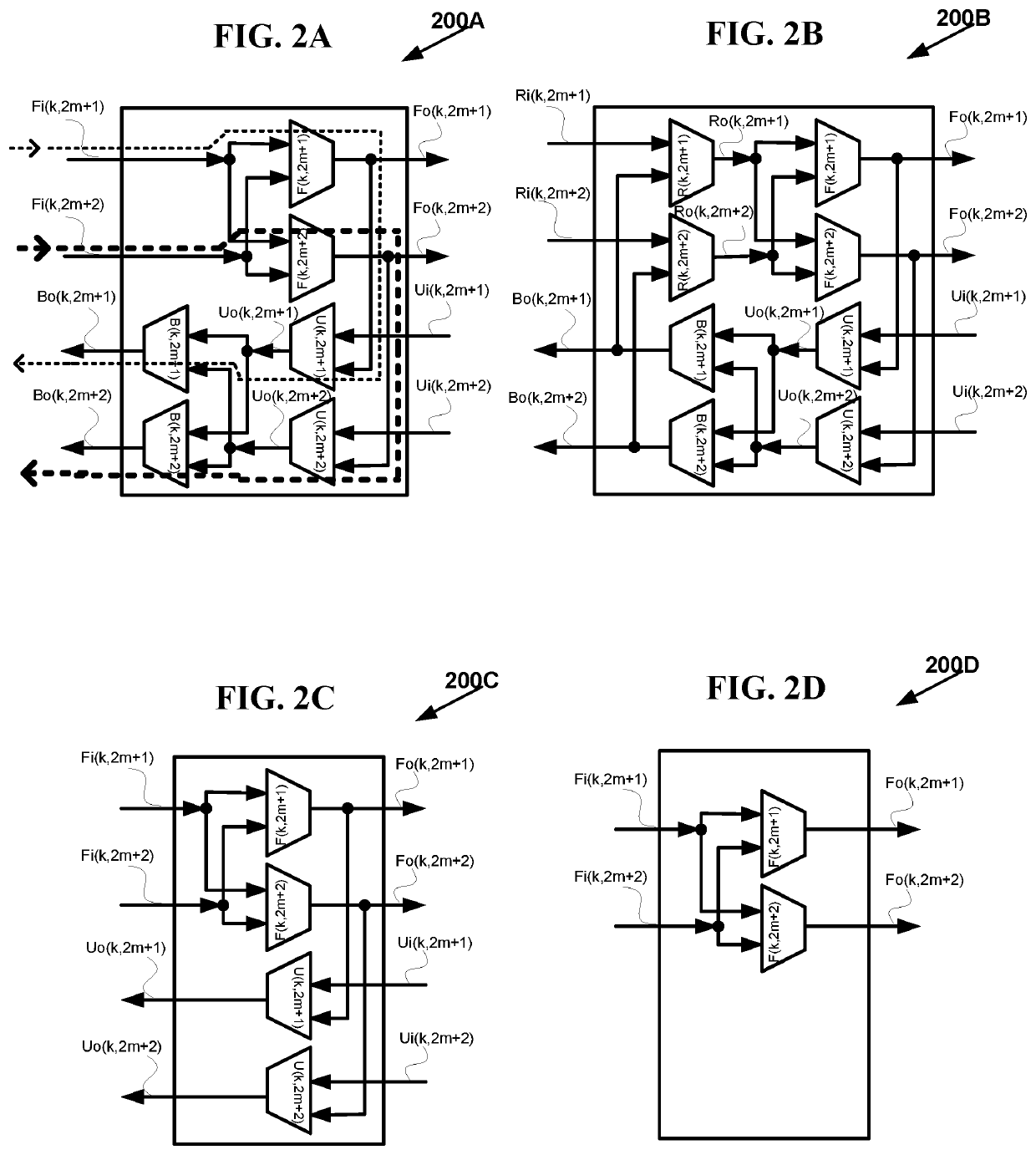

VLSI layouts of fully connected generalized and pyramid networks with locality exploitation

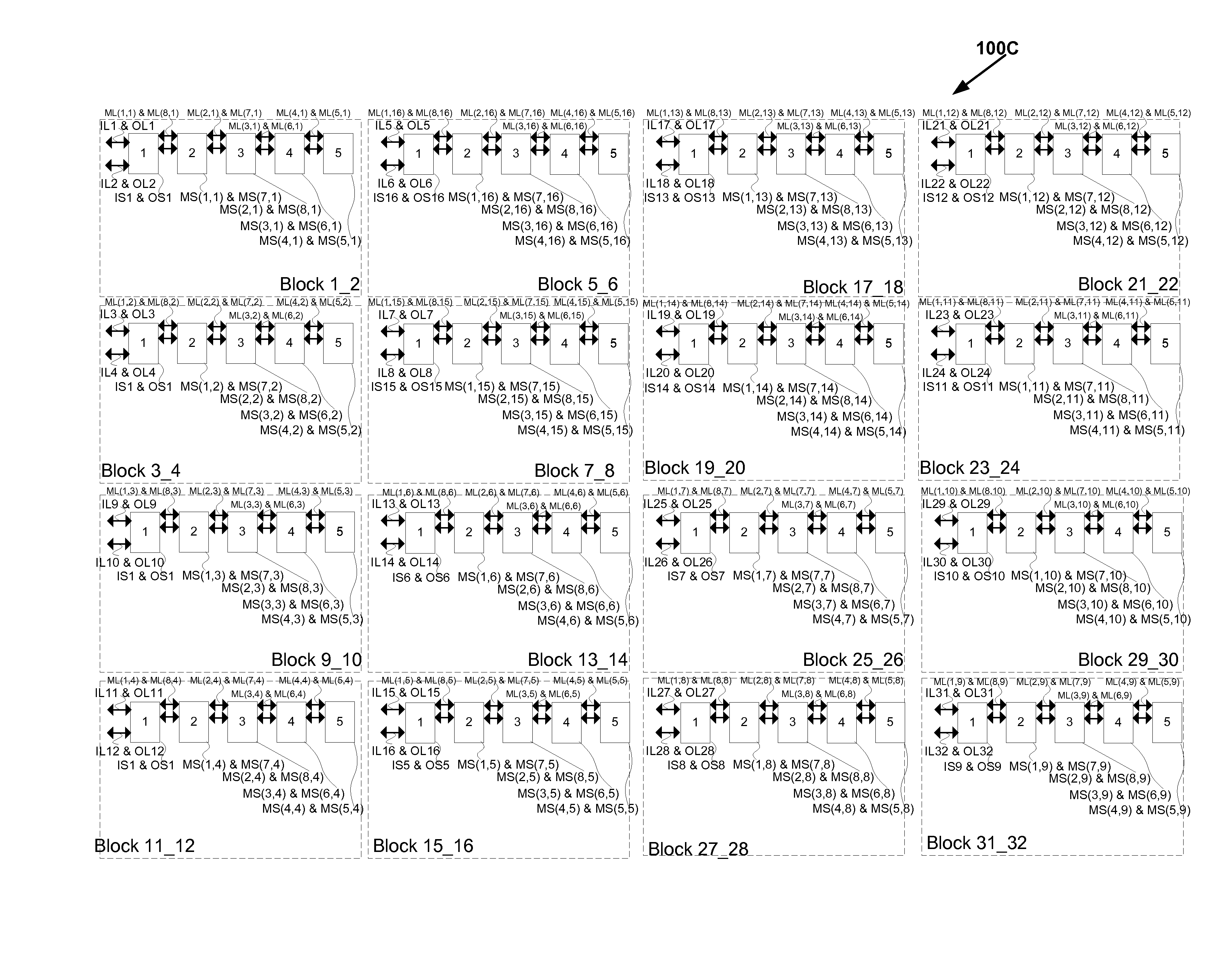

ActiveUS8898611B2Low pour pointReduce signal delayMultiplex system selection arrangementsGeometric CADCross-linkMulti link

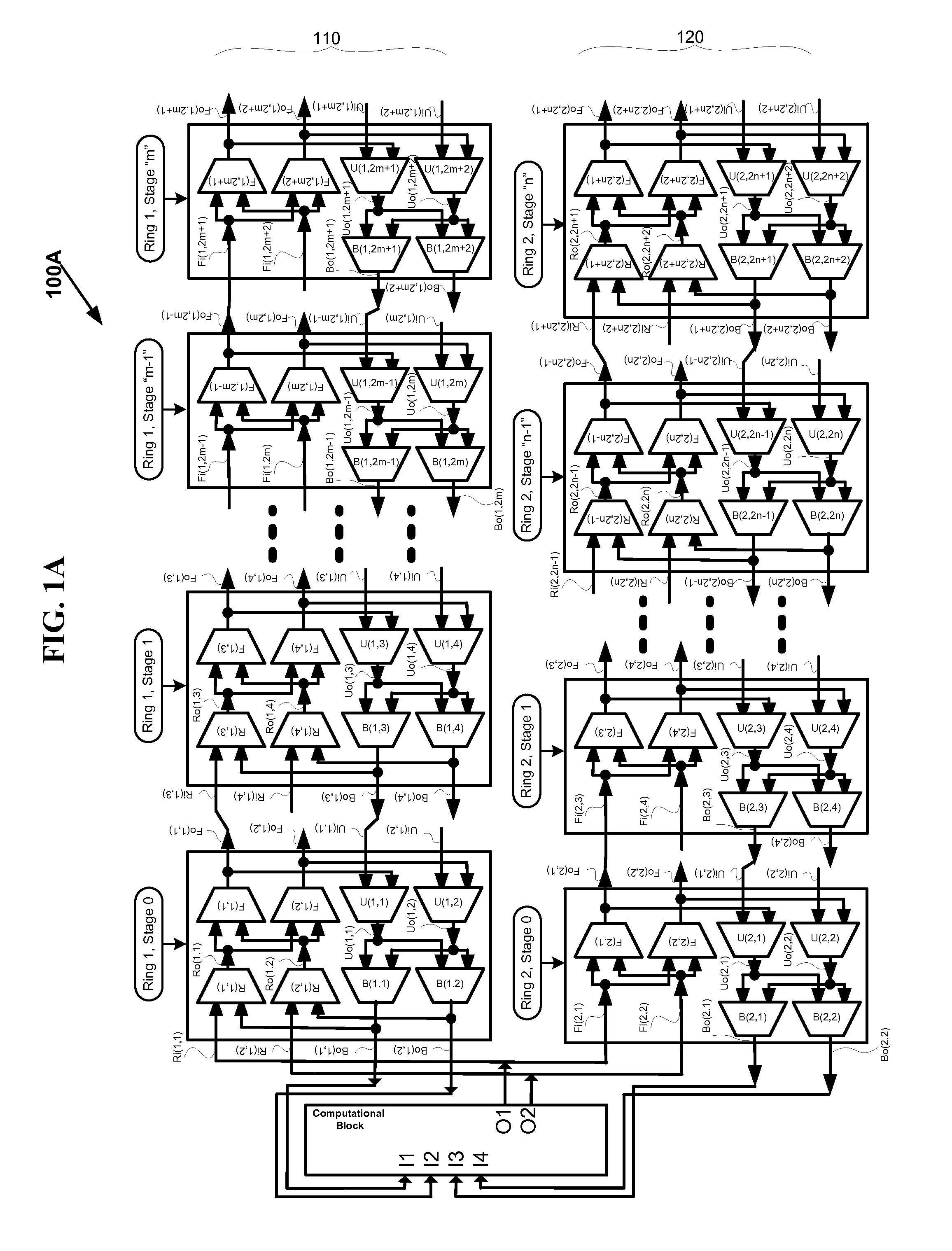

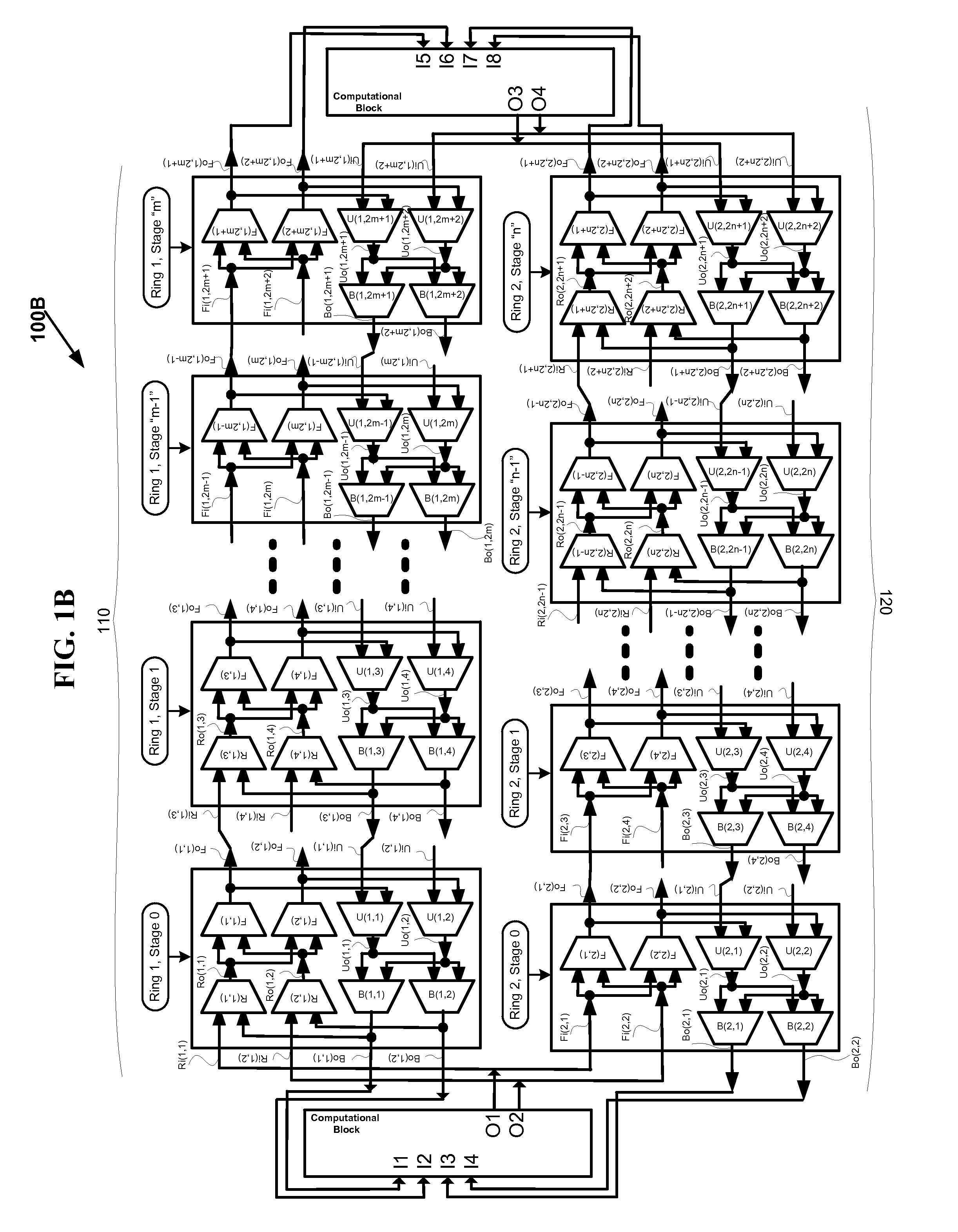

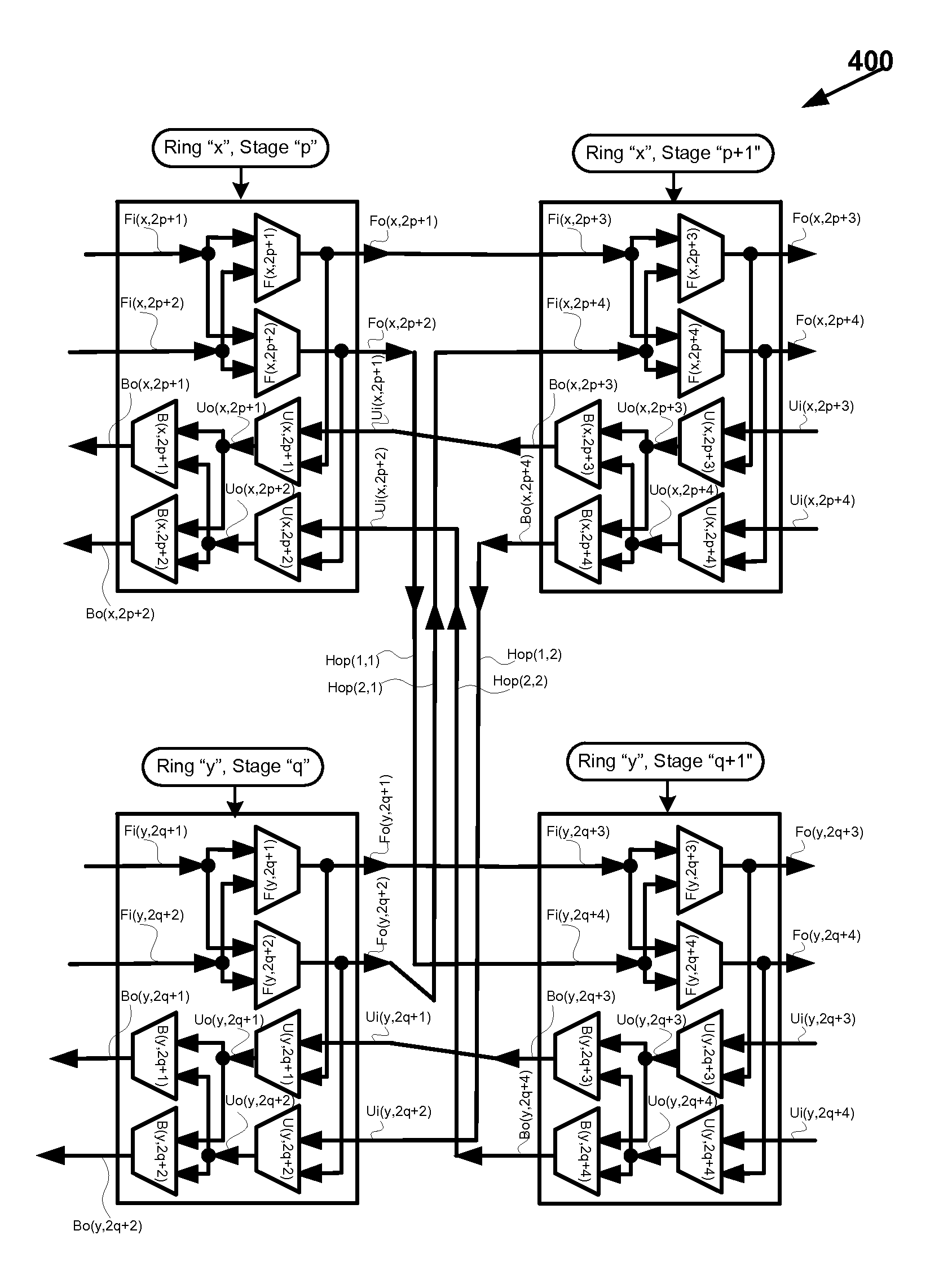

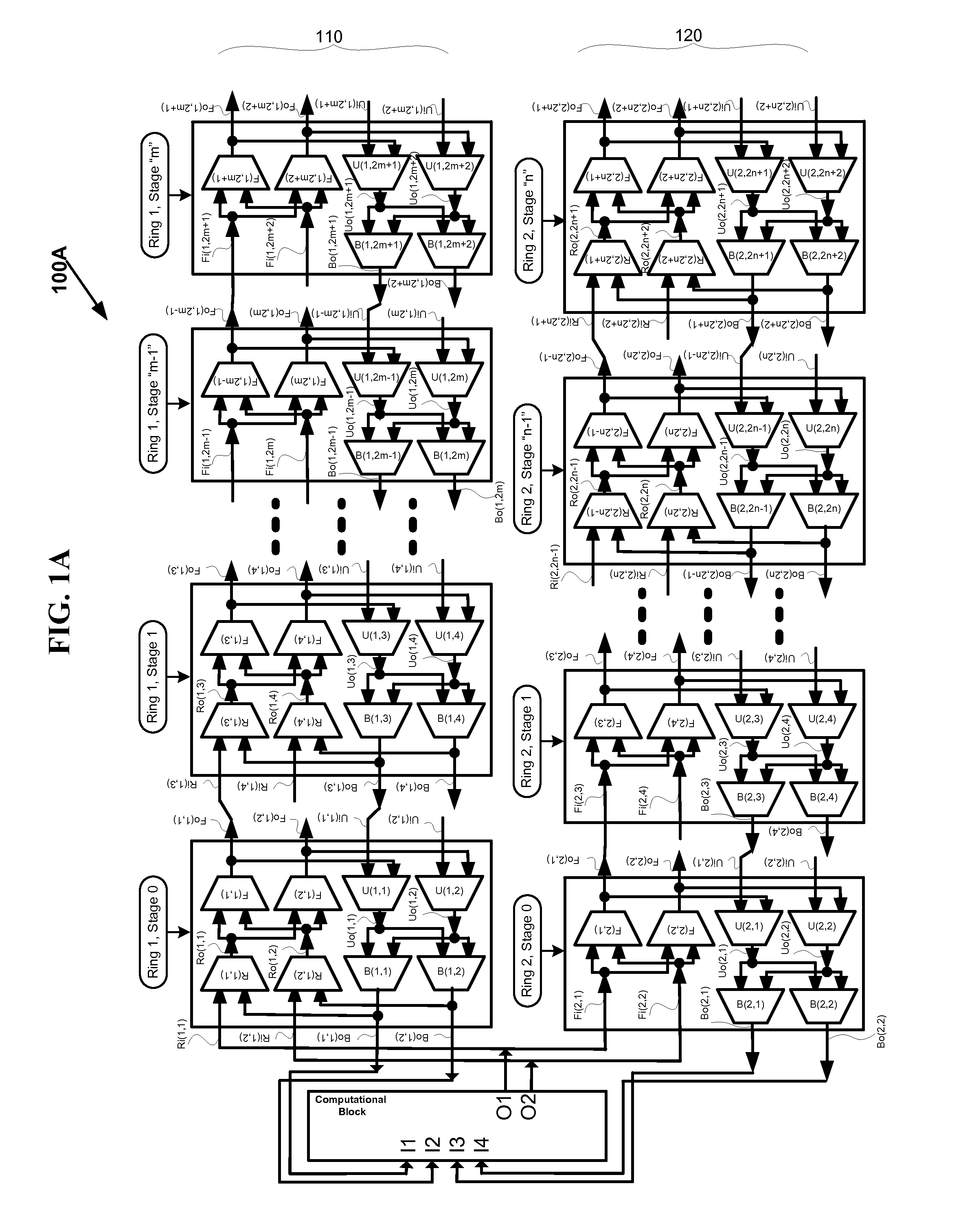

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

The use of redundant routes to increase the yield and reliability of a VLSI layout

ActiveUS20060265684A1Increase redundancyReduce sensitivityCAD circuit designSoftware simulation/interpretation/emulationPathPingVlsi layout

Disclosed is a method and system for inserting redundant paths into an integrated circuit. Particularly, the invention provides a method for identifying a single via in a first path connecting two elements, determining if an alternate route is available for connecting the two elements (other than a redundant via), and for inserting a second path into the available alternate route. The combination of the first and second paths provides greater redundancy than inserting a redundant via alone. More importantly, such redundant paths provide for redundancy when congestion prevents a redundant via from being inserted adjacent to the single via. An embodiment of the method further comprises removing the single via and any redundant wire segments, if all of the additional vias used to form the second path can be made redundant.

Owner:GLOBALFOUNDRIES US INC

VLSI layouts of fully connected generalized networks

ActiveUS8269523B2Low pour pointReduce signal delaySolid-state devicesComputer aided designCross-linkMulti link

Owner:KONDA VENKAT

VLSI layouts of fully connected generalized networks

ActiveUS20110037498A1Low pour pointReduce signal delaySolid-state devicesComputer aided designCross-linkMulti link

In accordance with the invention, VLSI layouts of generalized multi-stage networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts presented are applicable to generalized multi-stage networks V(N1, N2, d, s), generalized folded multi-stage networks Vfold(N1, N2, d, s), generalized butterfly fat tree networks Vbft(N1, N2, d, s), generalized multi-link multi-stage networks Vmlink(N1, N2, d, s), generalized folded multi-link multi-stage networks Vfold-mlink(N1, N2, d, s), generalized multi-link butterfly fat tree networks Vmlink-bft(N1, N2, d, s), and generalized hypercube networks Vhcube(N1, N2, d, s) for s=1, 2, 3 or any number in general. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA VENKAT

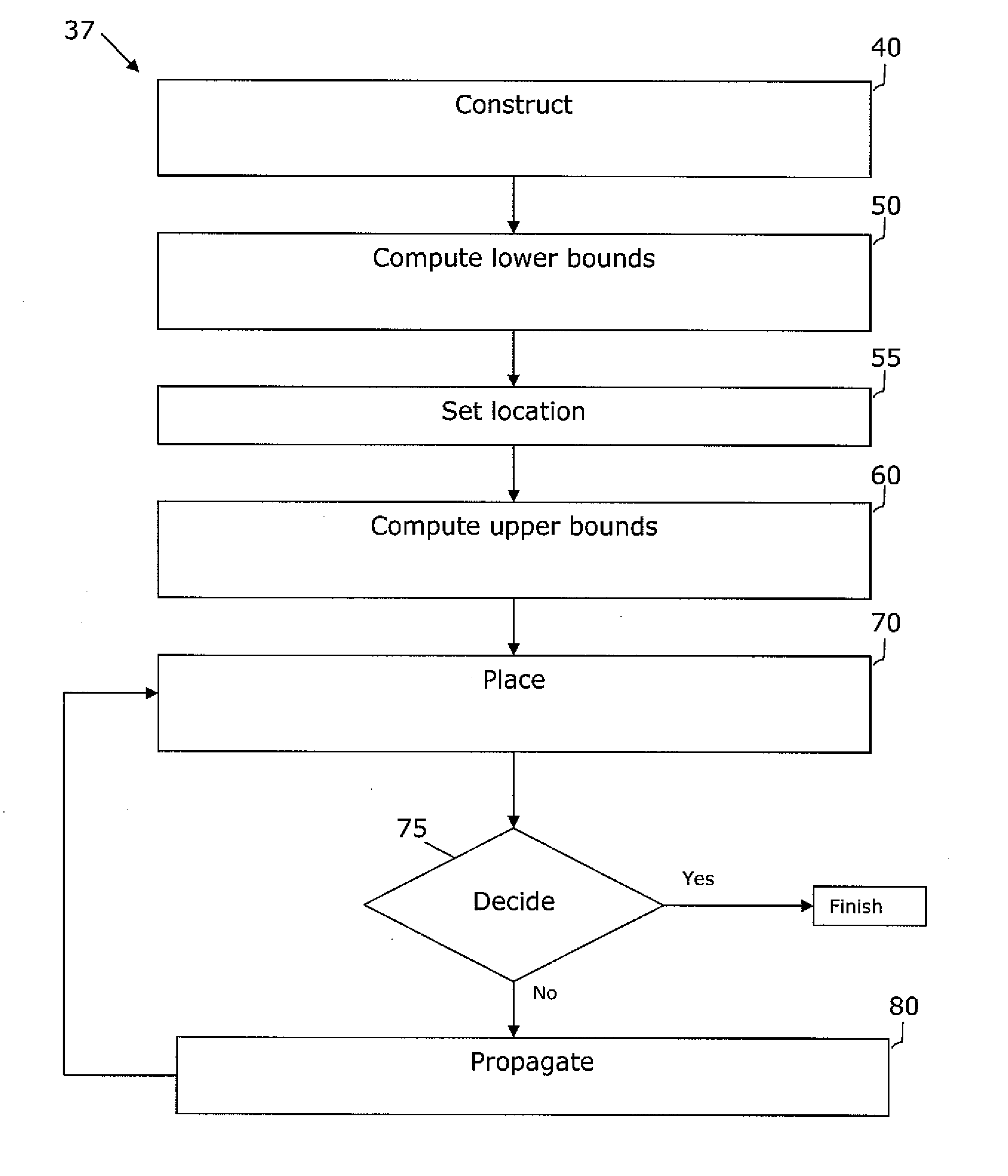

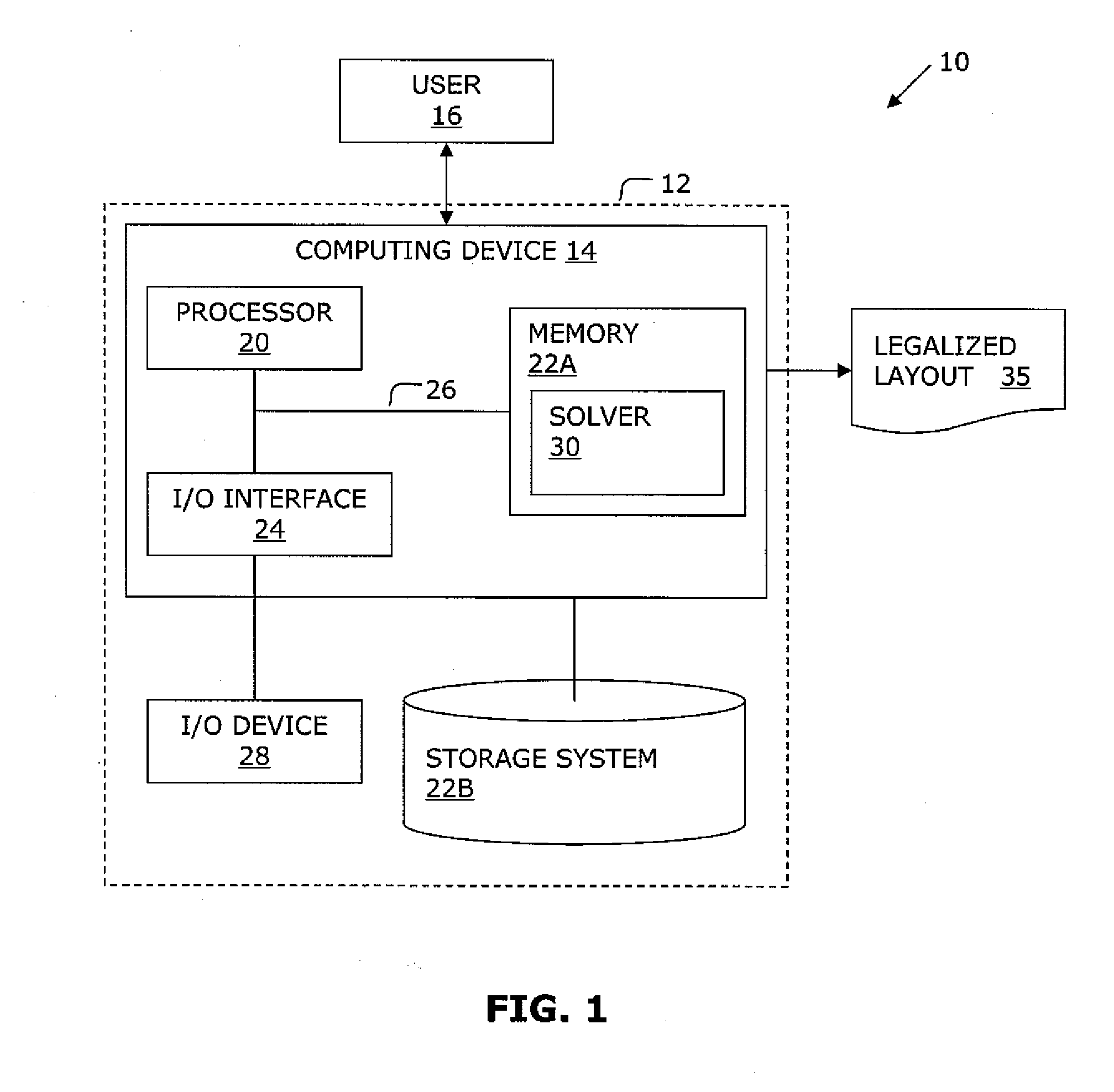

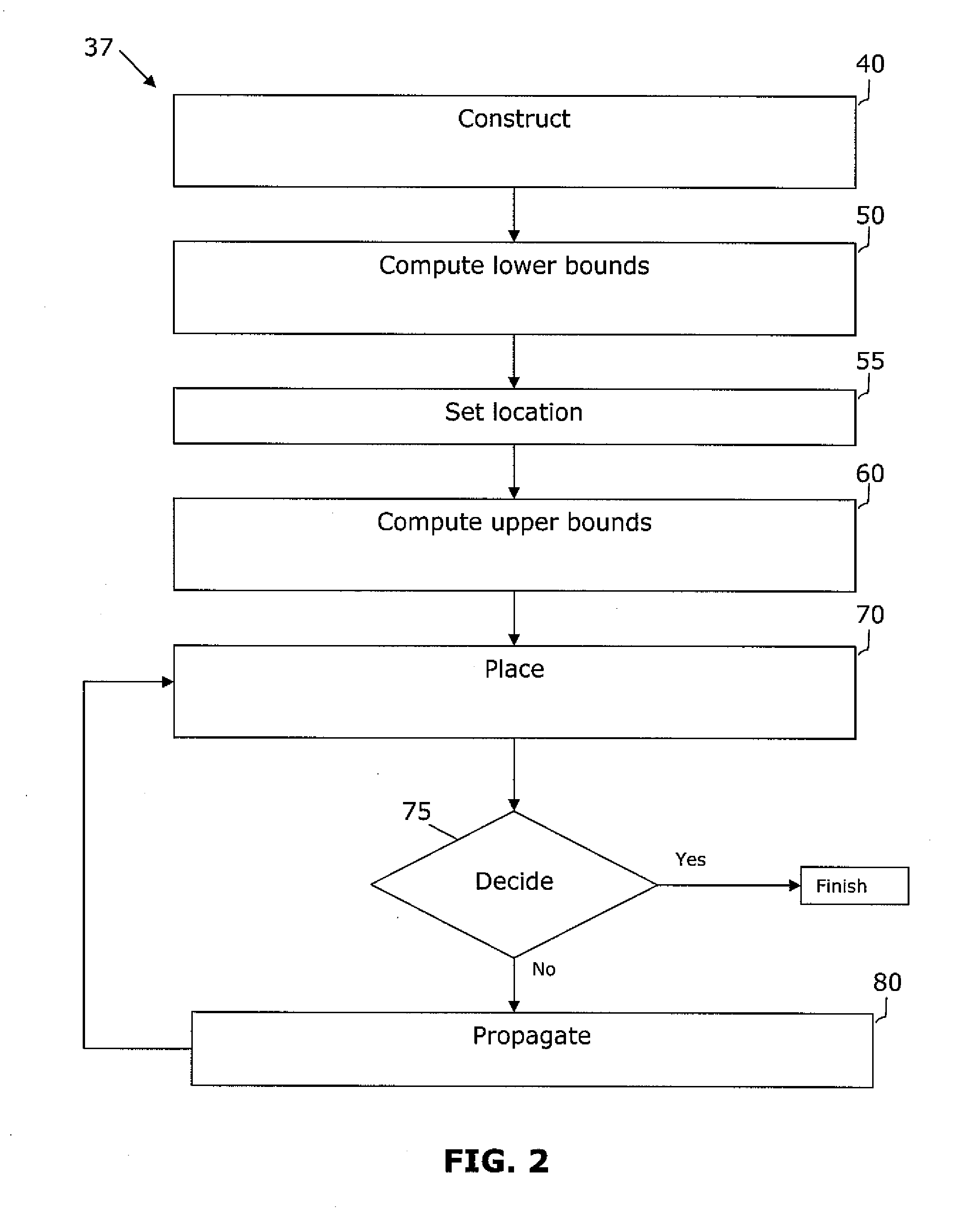

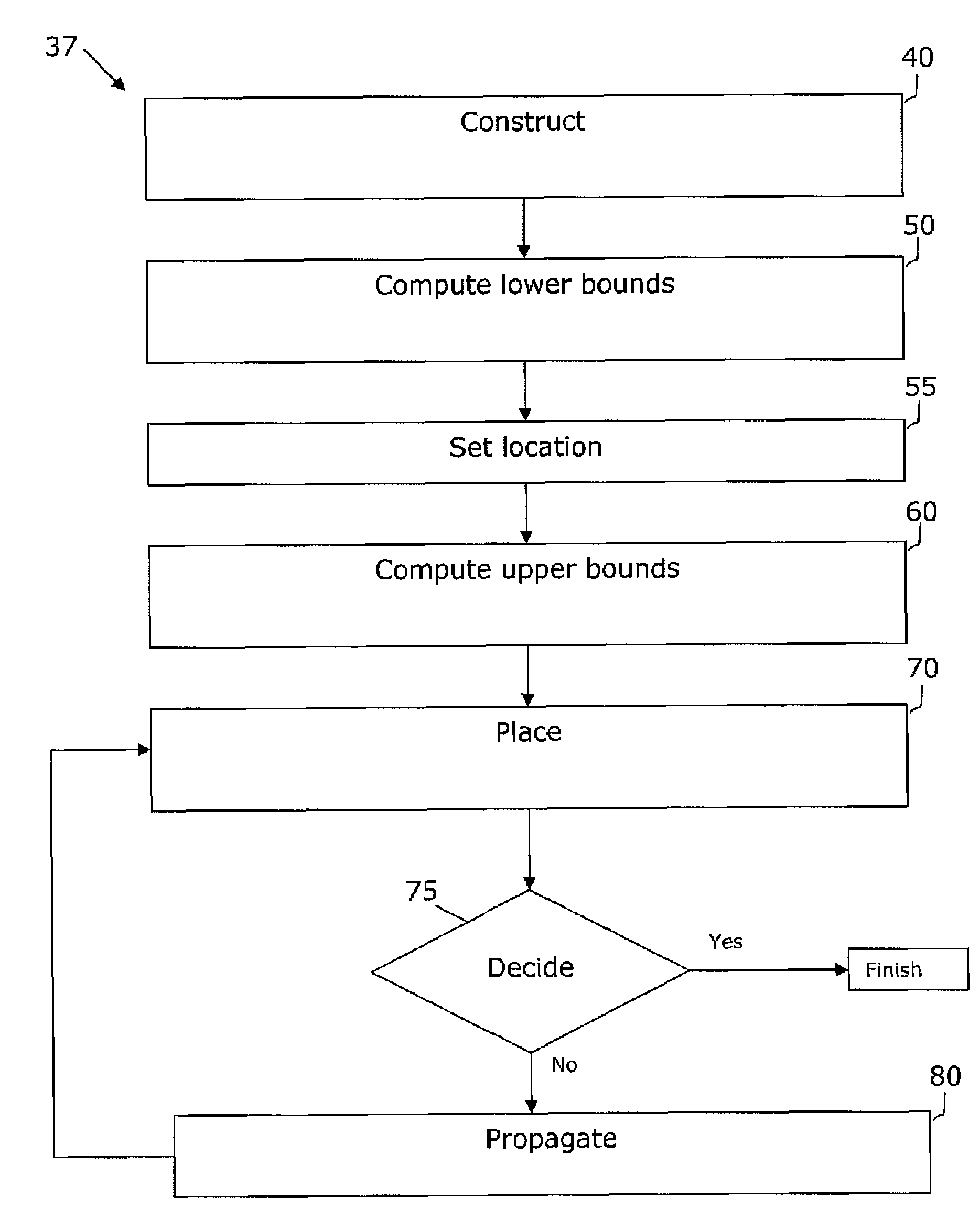

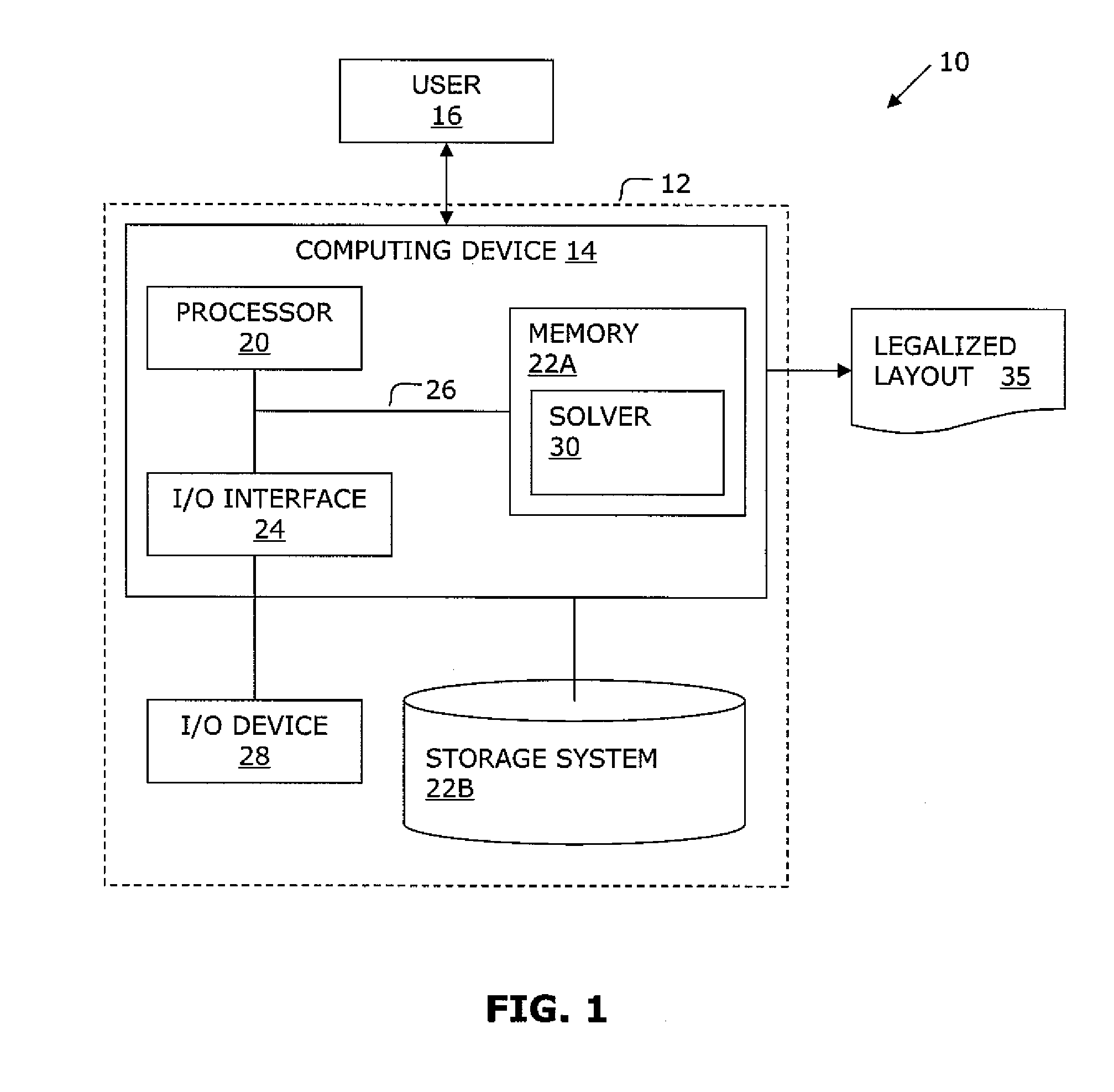

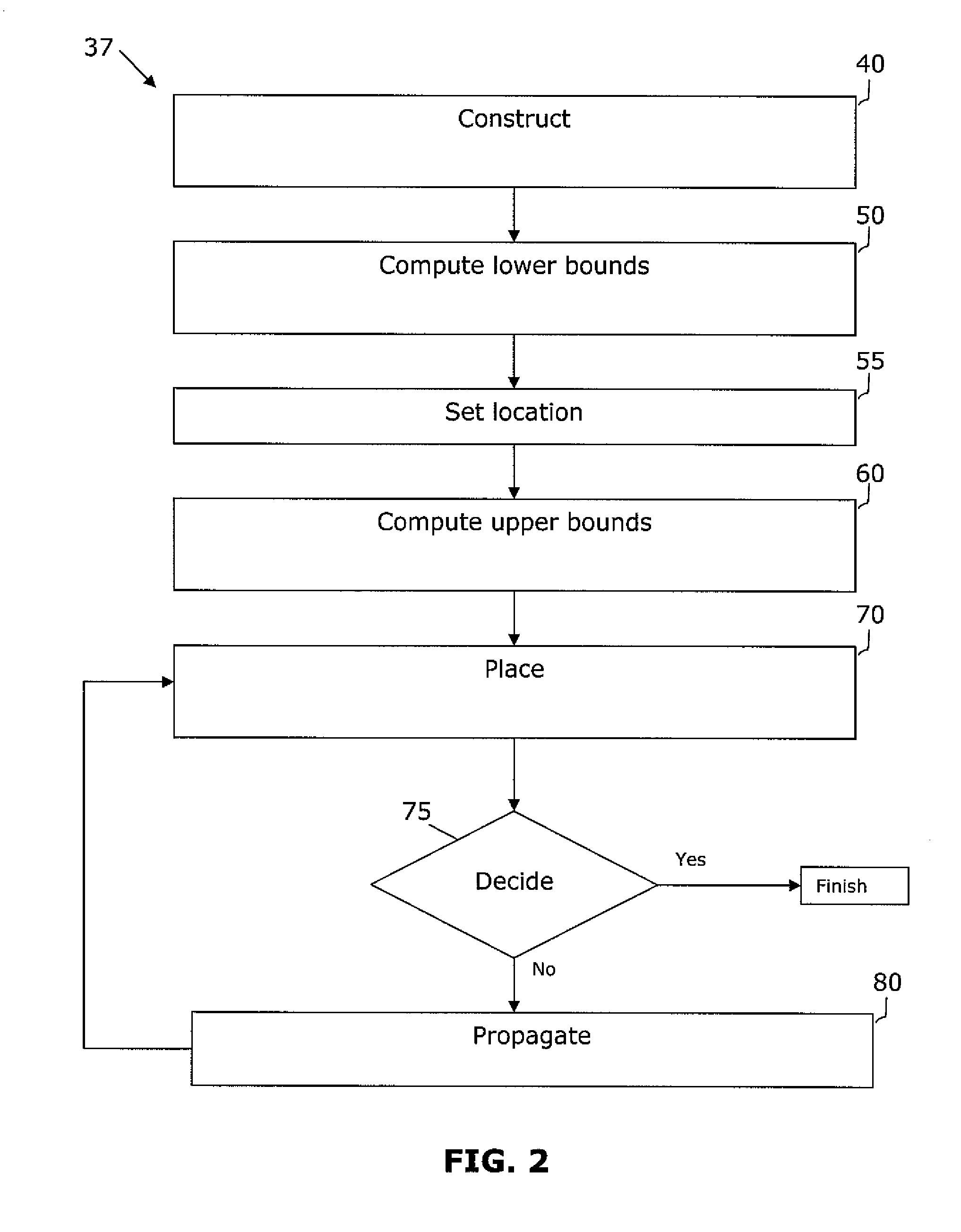

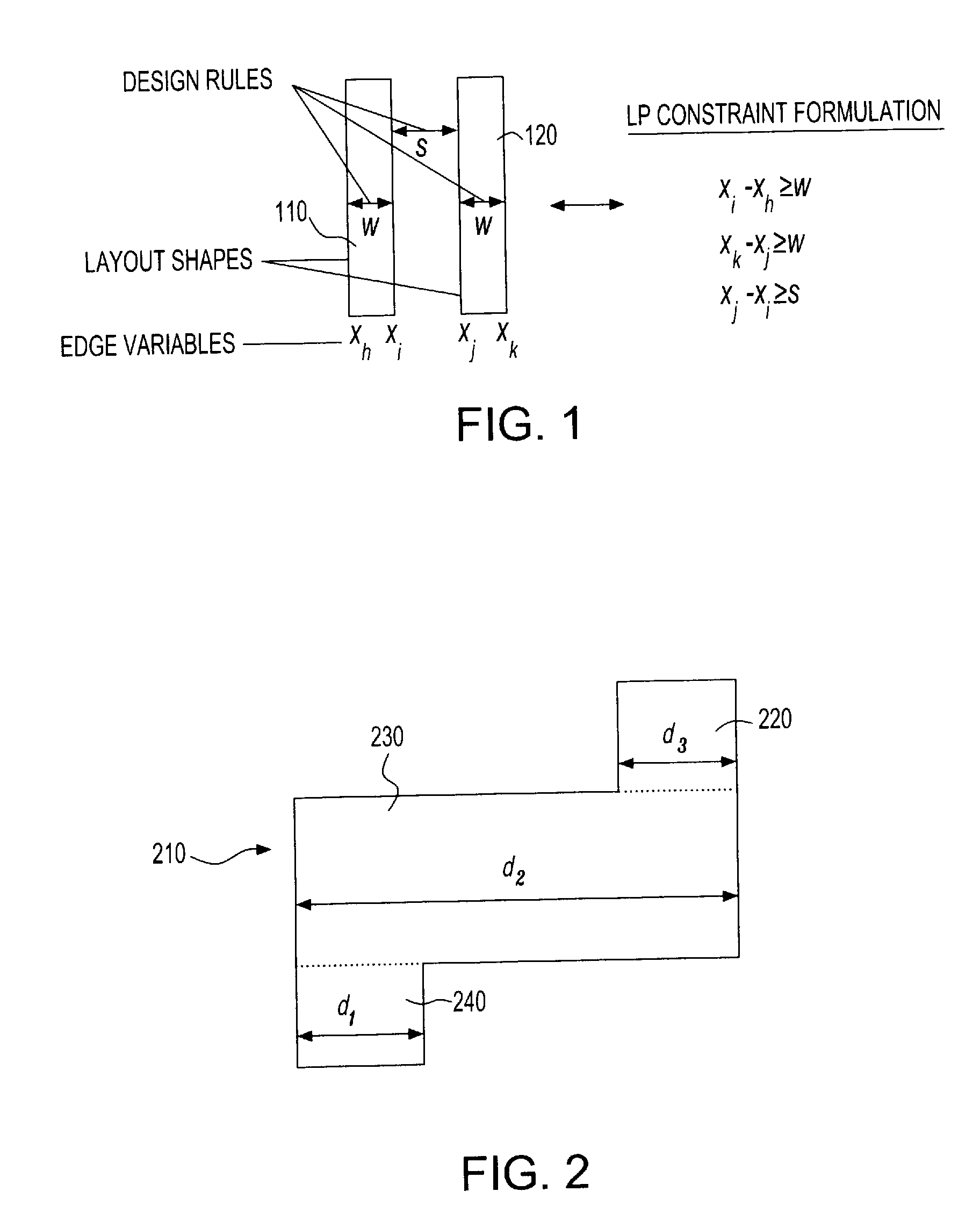

VLSI artwork legalization for hierarchical designs with multiple grid constraints

A system and method are disclosed for legalizing a flat or hierarchical VLSI layout to meet multiple grid constraints and conventional ground rules. Given a set of ground rules with multiple grid constraints and a VLSI layout (either hierarchical or flat) which is layout-versus-schematic (LVS) correct but may not be ground rule correct, the system and method provide a legalized layout which meets the multiple grid constraints while maintaining LVS correctness and fixing the ground rule errors as much as possible with minimum layout perturbation from the input design. The system and method support multiple grid pitch constraints for hierarchical design, and provide for LVS correctness to be maintained while an on-grid solution possibly with some spacing violations.

Owner:GLOBALFOUNDRIES US INC

VLSI Layouts of Fully Connected Generalized and Pyramid Networks with Locality Exploitation

ActiveUS20120269190A1Low pour pointFull connectivityMultiplex system selection arrangementsGeometric CADCross-linkMulti link

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

VLSI layouts of fully connected generalized and pyramid networks with locality exploitation

ActiveUS9529958B2Low pour pointReduce signal delayCircuit switching systemsCAD circuit designCross-linkMulti link

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation. The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

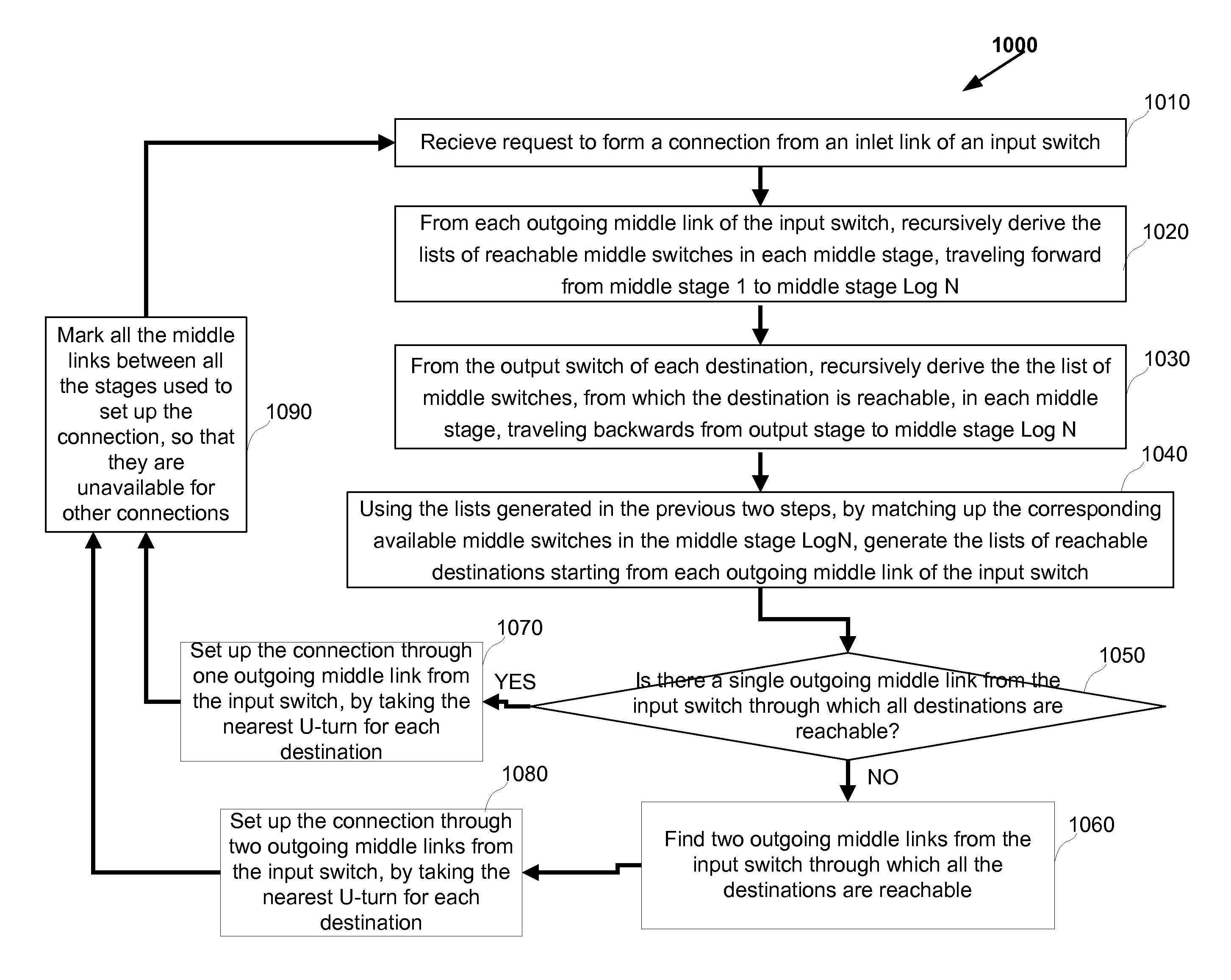

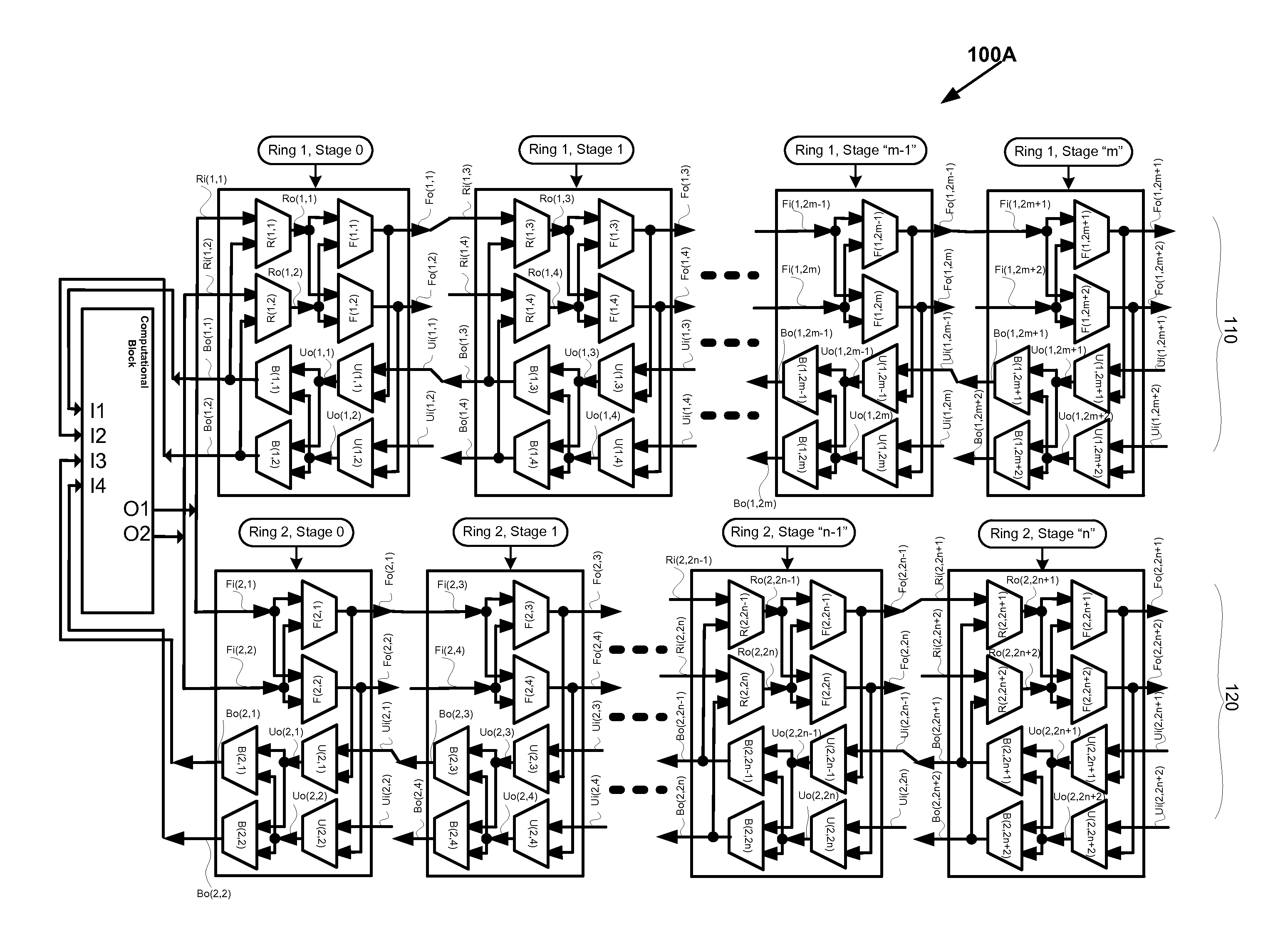

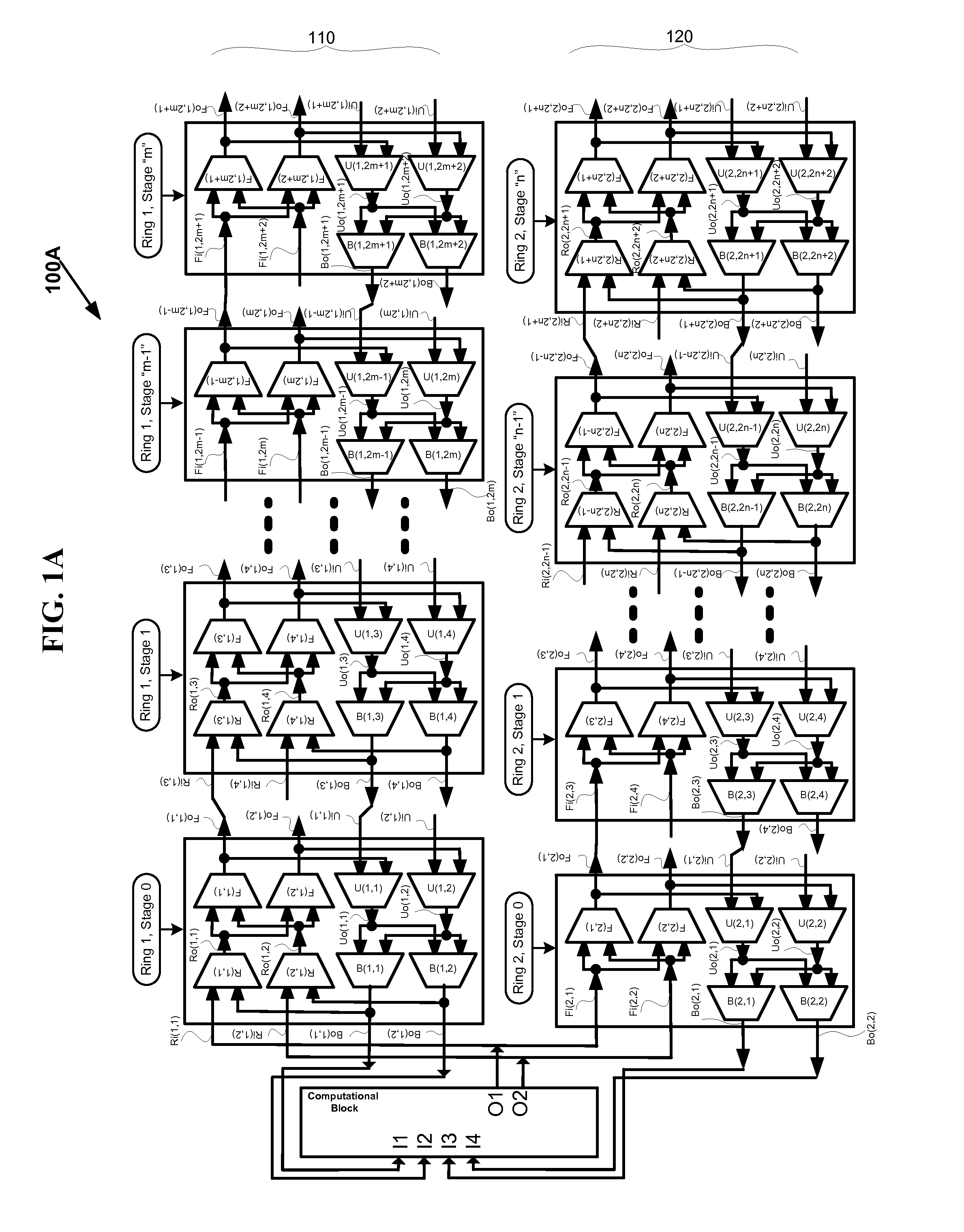

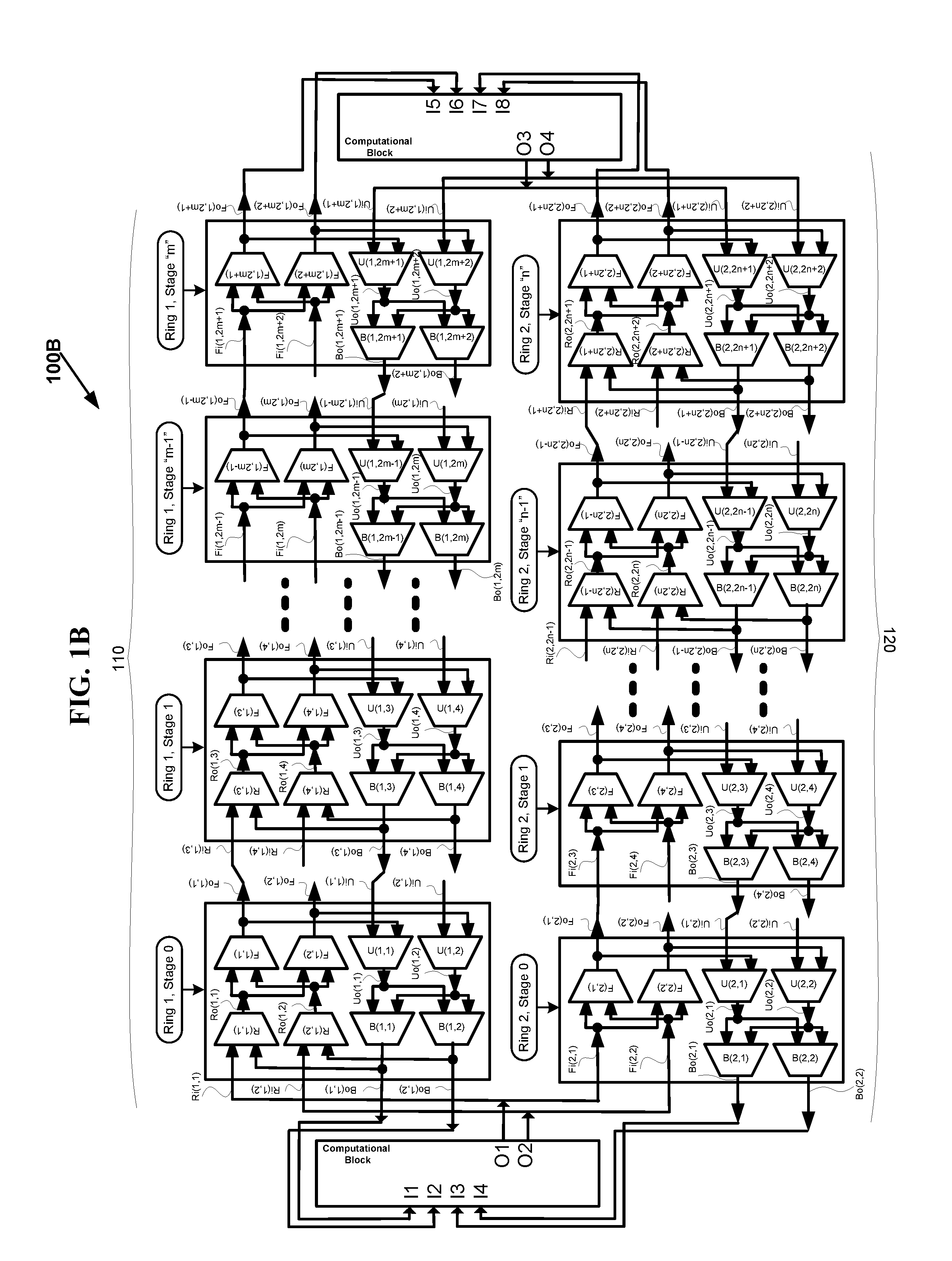

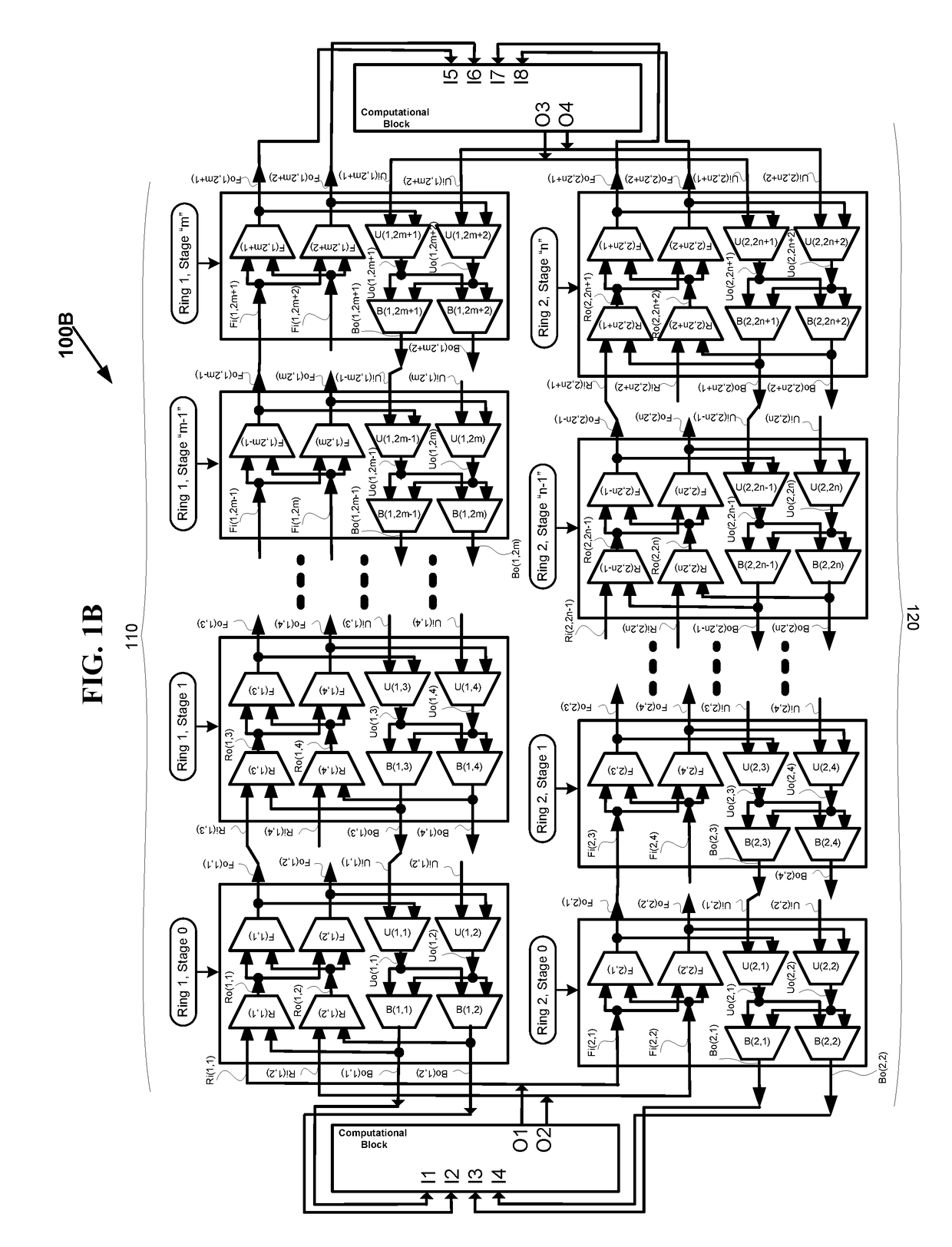

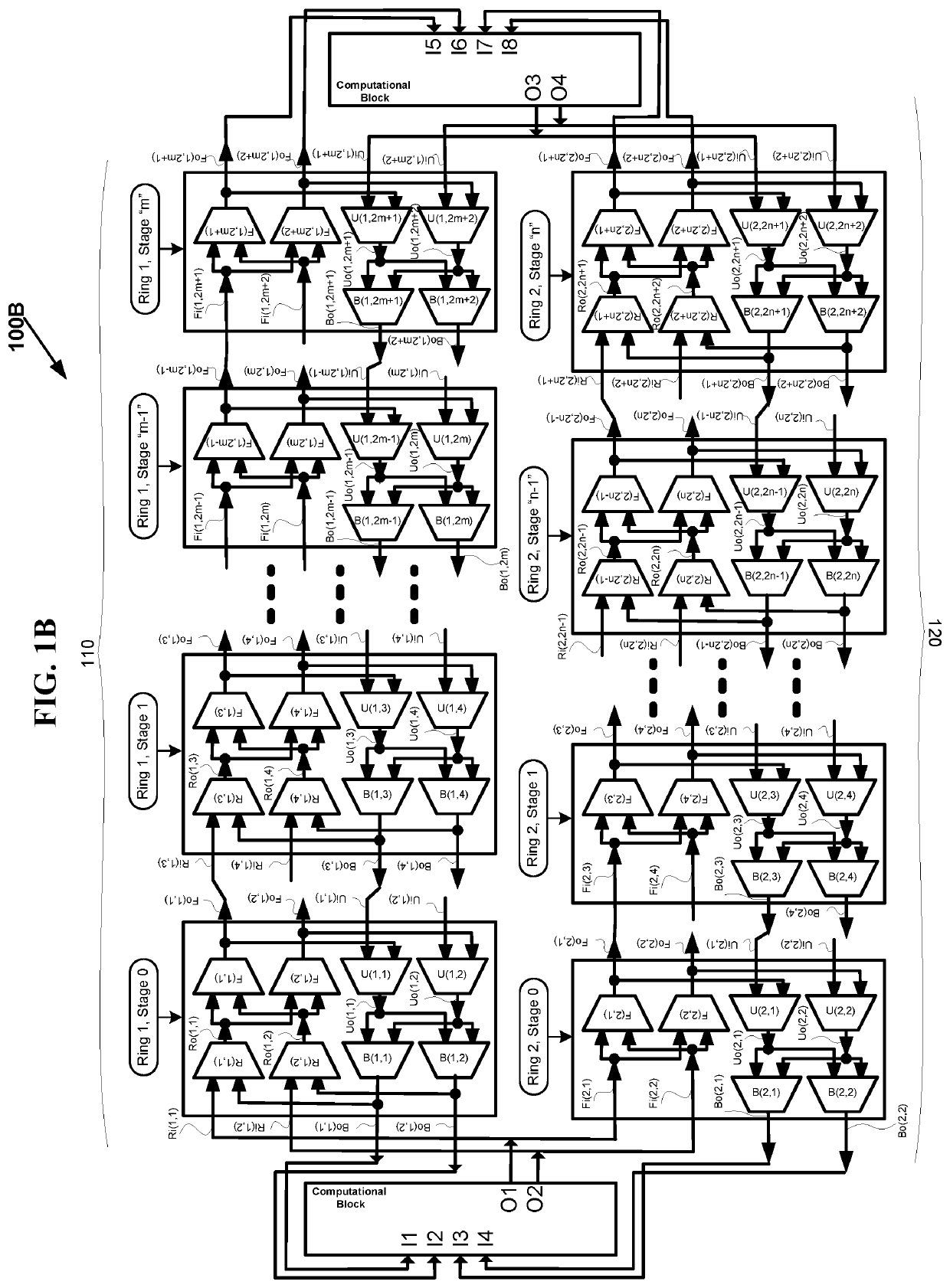

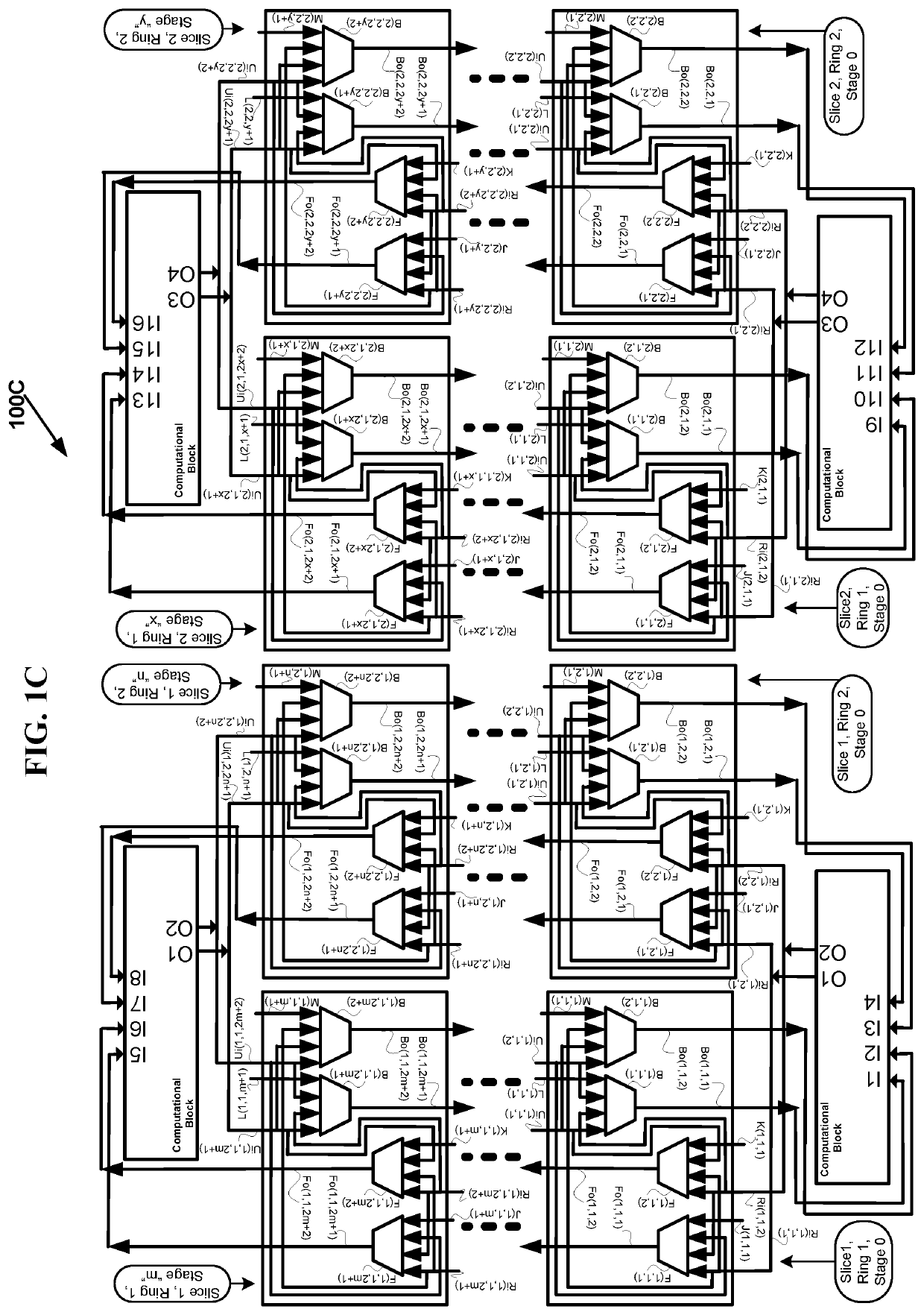

Fast scheduling and optmization of multi-stage hierarchical networks

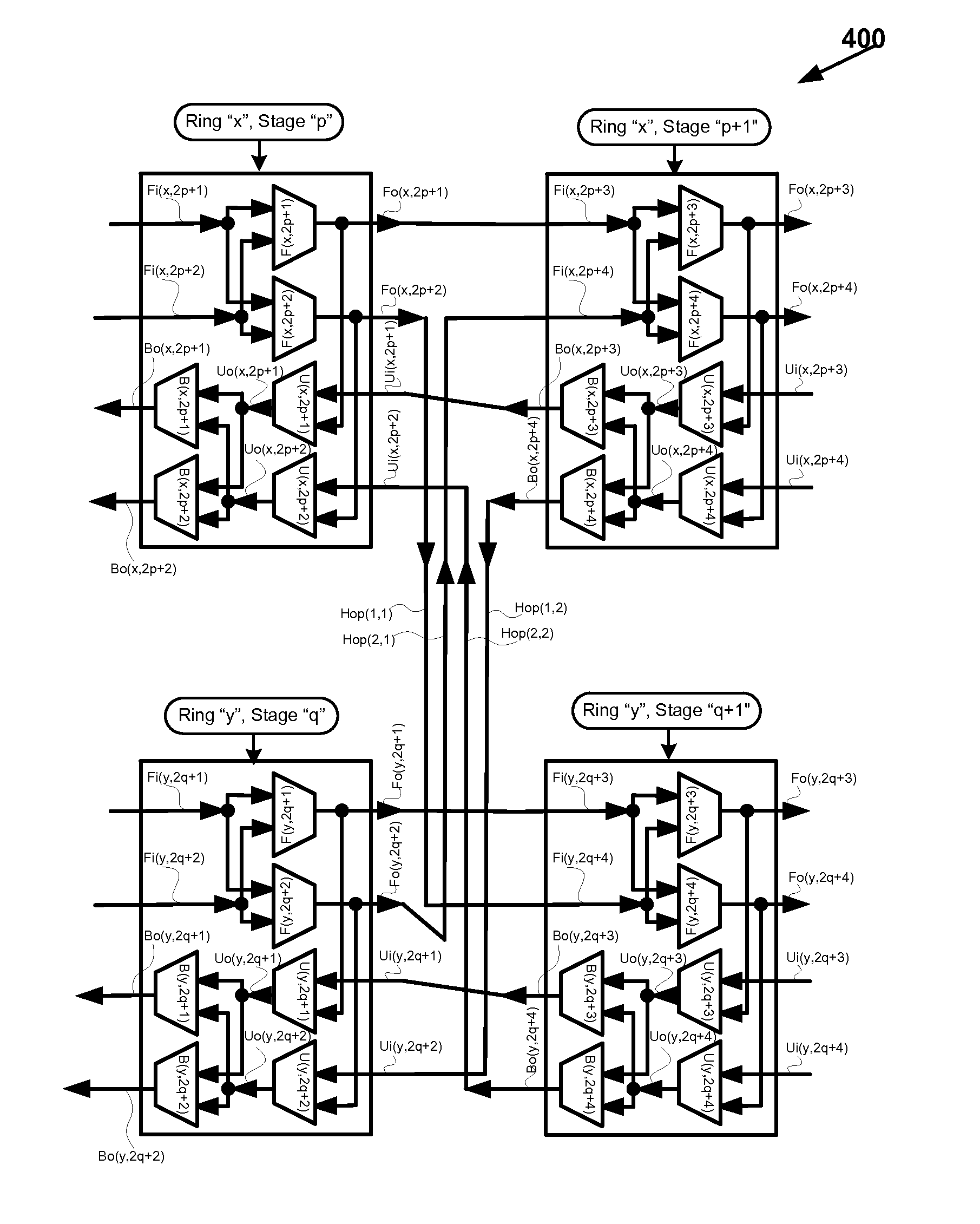

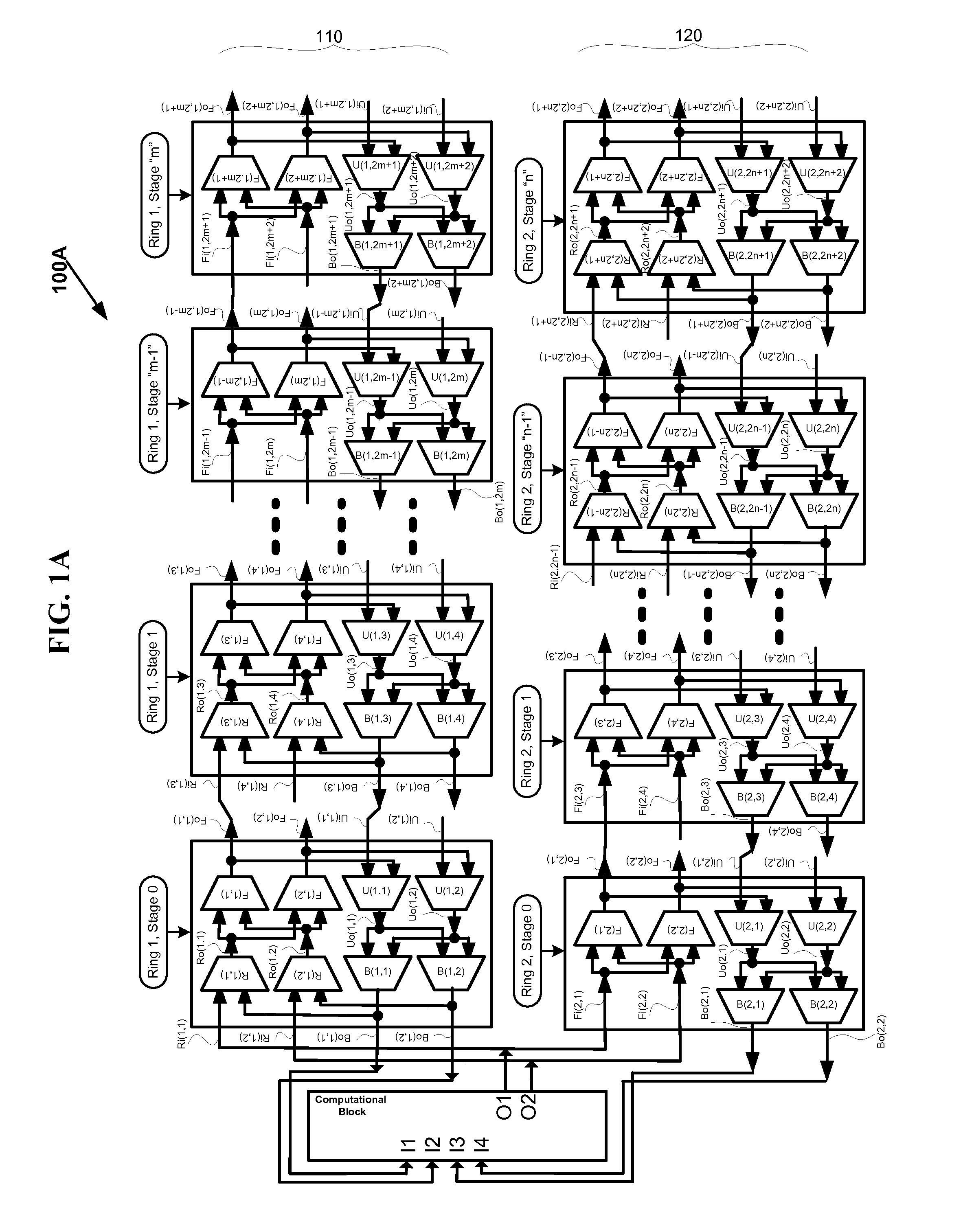

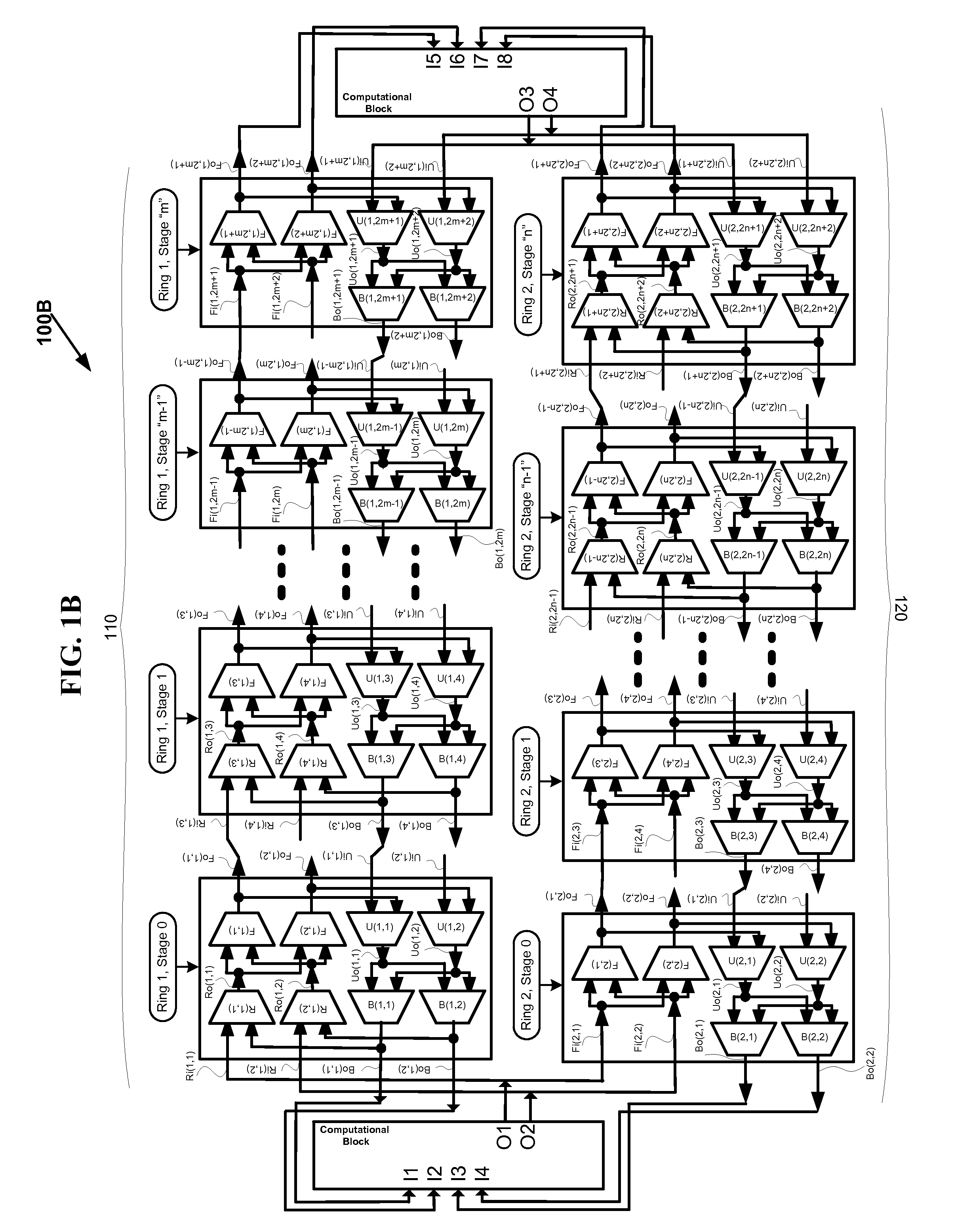

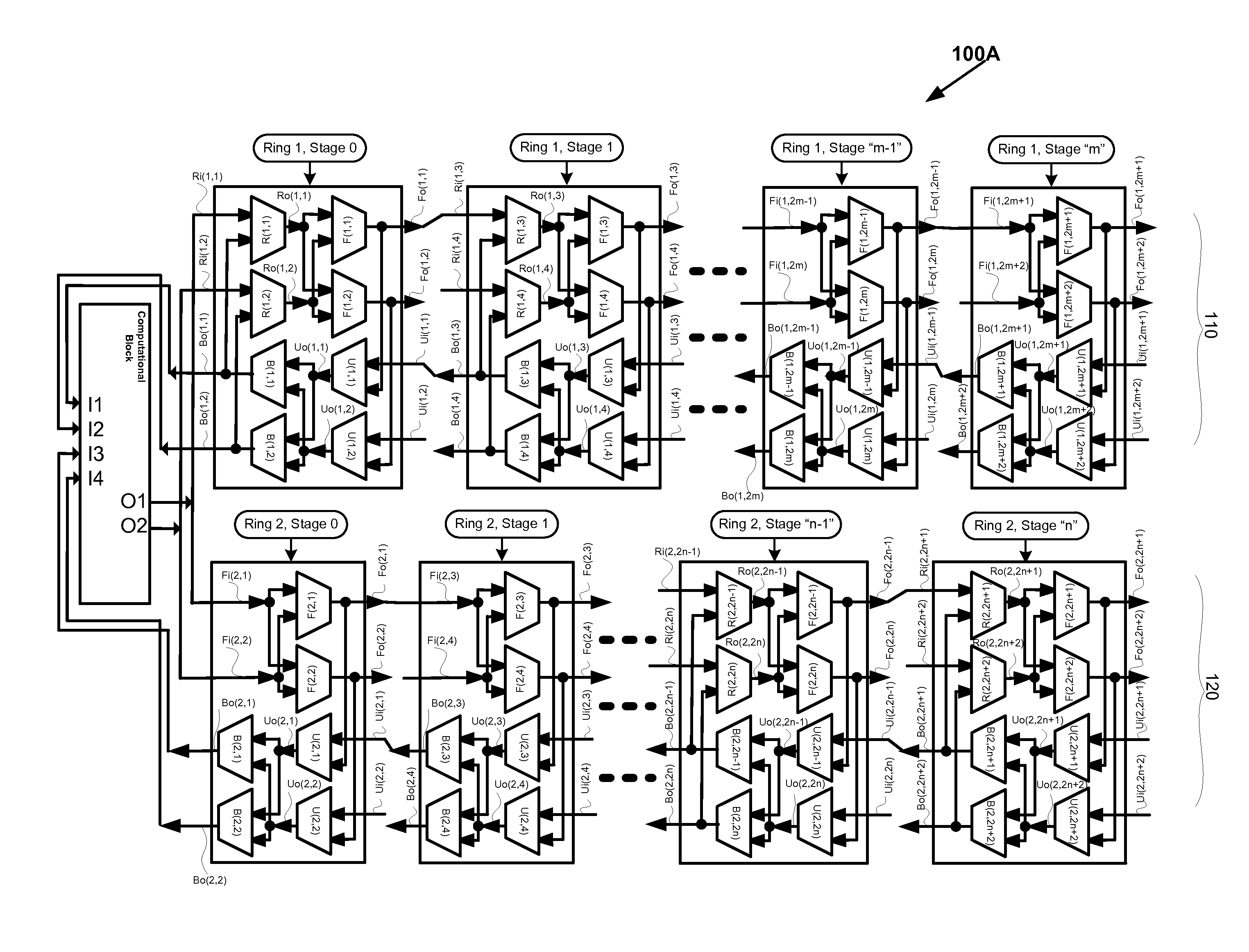

ActiveUS20150049768A1Quick dispatchHigh routabilityData switching by path configurationCross-linkVlsi layout

Significantly optimized multi-stage networks with scheduling methods for faster scheduling of connections, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several slices of rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ multi-drop links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA TECH

VLSI artwork legalization for hierarchical designs with multiple grid constraints

ActiveUS7437691B2Geometric CADComputation using non-denominational number representationGraphicsLayout Versus Schematic

A system and method are disclosed for legalizing a flat or hierarchical VLSI layout to meet multiple grid constraints and conventional ground rules. Given a set of ground rules with multiple grid constraints and a VLSI layout (either hierarchical or flat) which is layout-versus-schematic (LVS) correct but may not be ground rule correct, the system and method provide a legalized layout which meets the multiple grid constraints while maintaining LVS correctness and fixing the ground rule errors as much as possible with minimum layout perturbation from the input design. The system and method support multiple grid pitch constraints for hierarchical design, and provide for LVS correctness to be maintained while an on-grid solution possibly with some spacing violations.

Owner:GLOBALFOUNDRIES U S INC

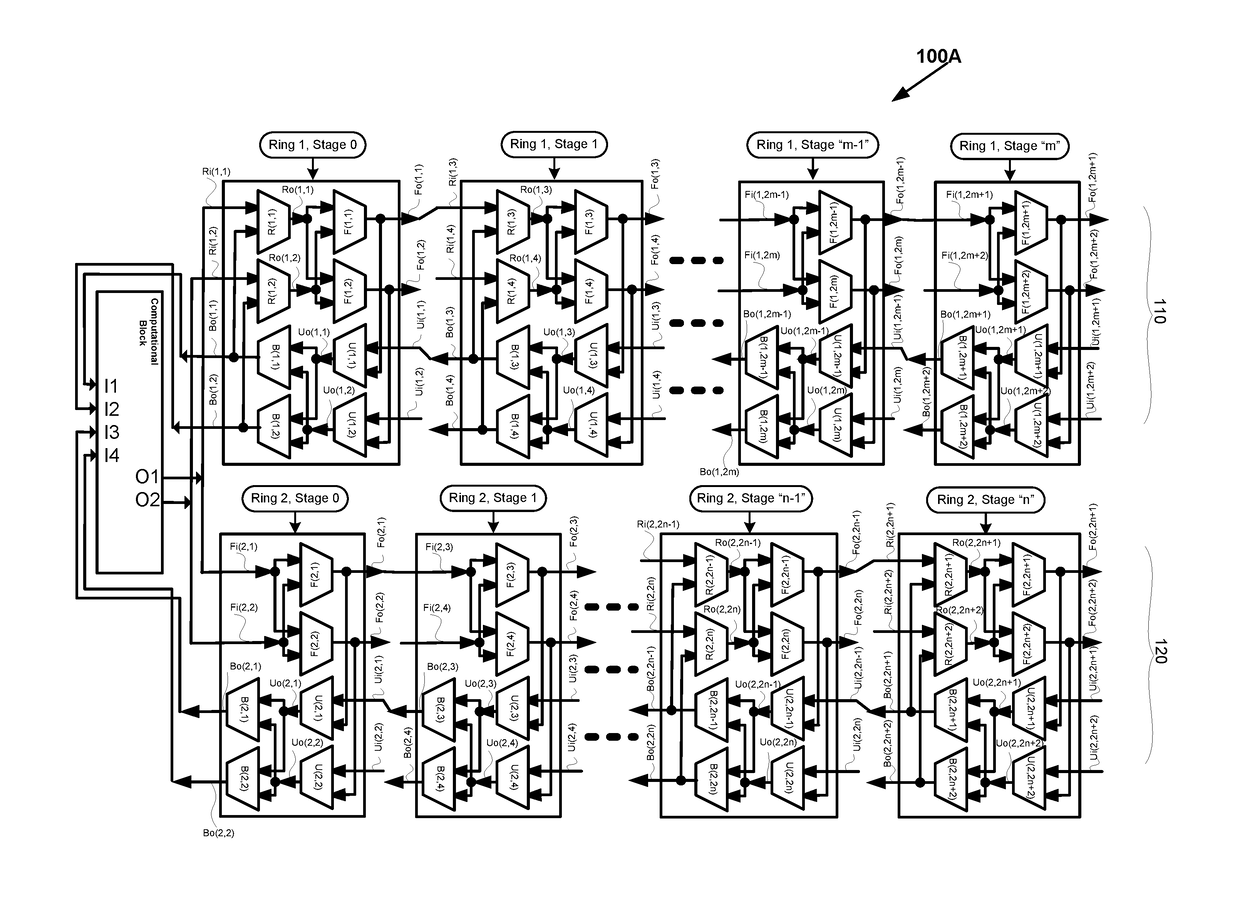

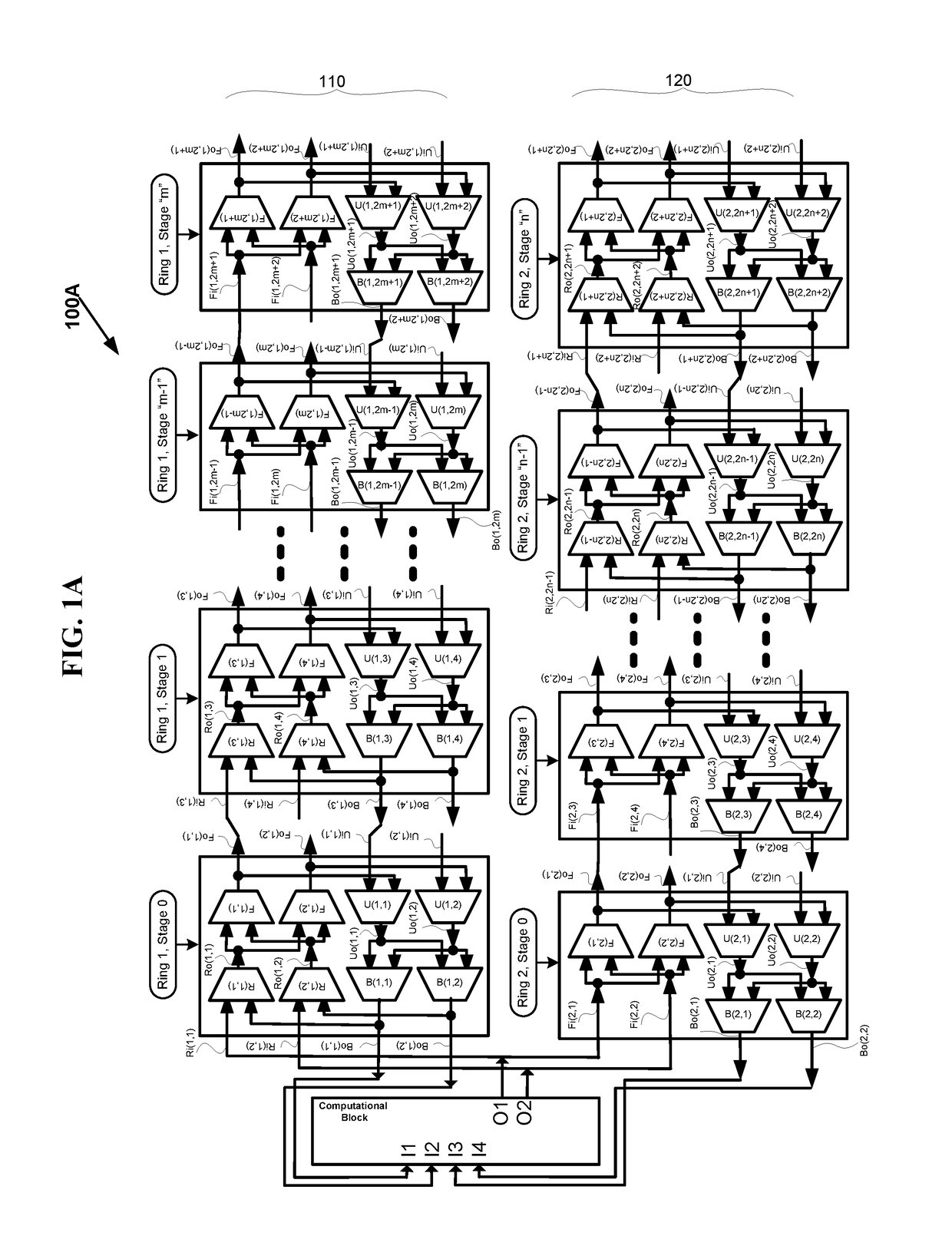

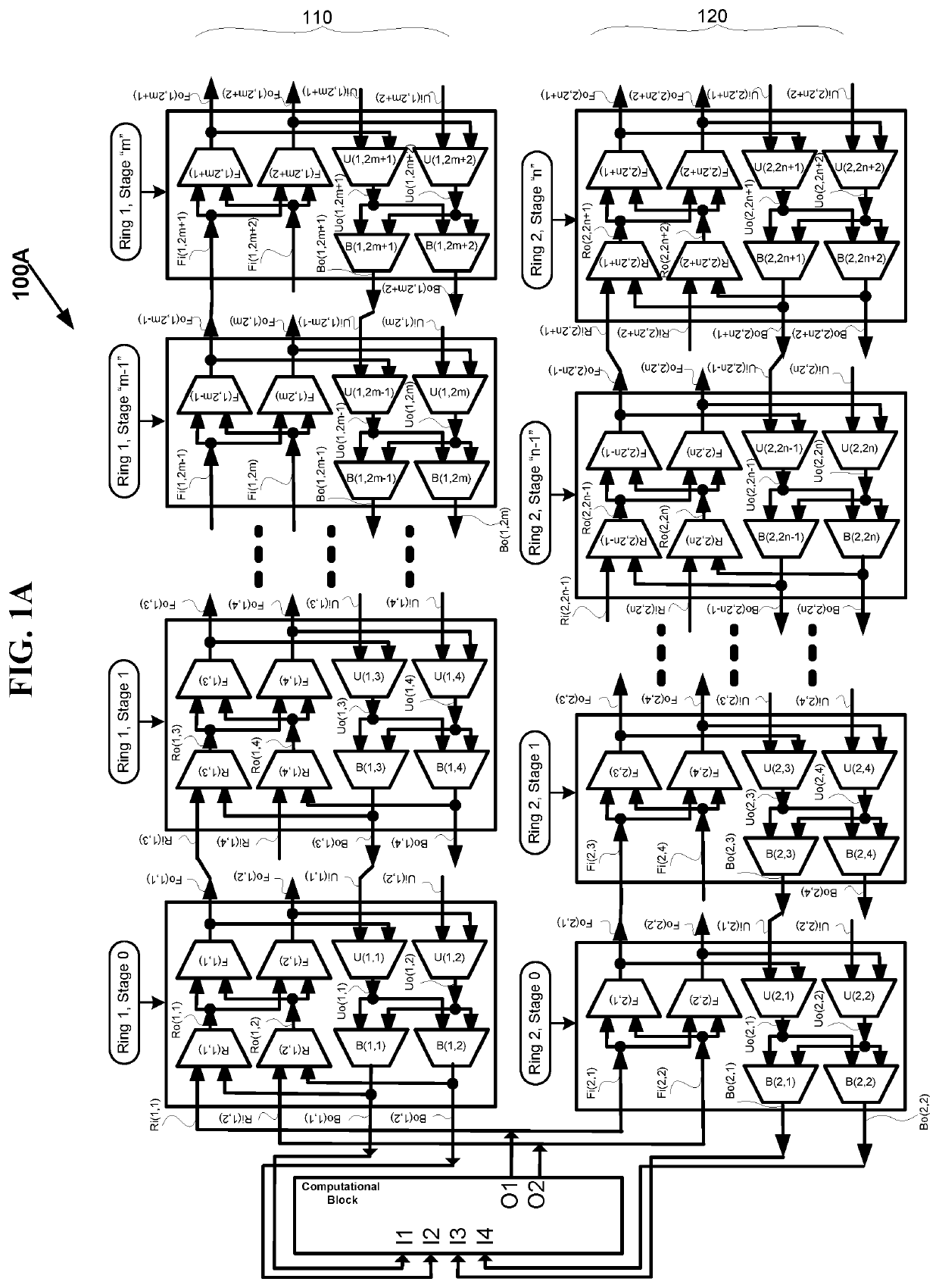

Optimization of multi-stage hierarchical networks for practical routing applications

ActiveUS20140313930A1High routabilityLow pour pointData switching by path configurationCross-linkVlsi layout

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

Fast scheduling and optmization of multi-stage hierarchical networks

Significantly optimized multi-stage networks with scheduling methods for faster scheduling of connections, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several slices of rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ multi-drop links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA TECH

Optimization of multi-stage hierarchical networks for practical routing applications

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

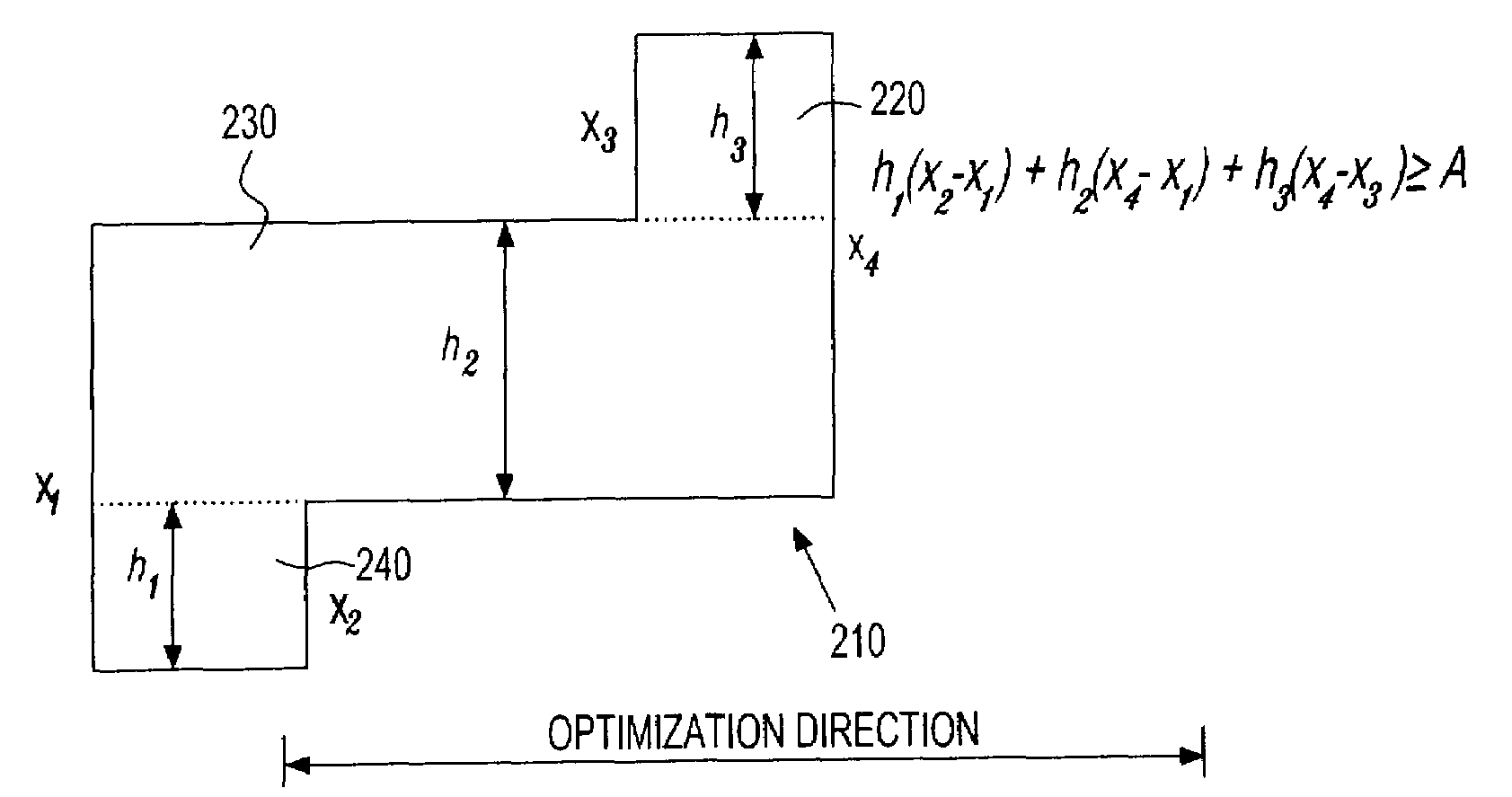

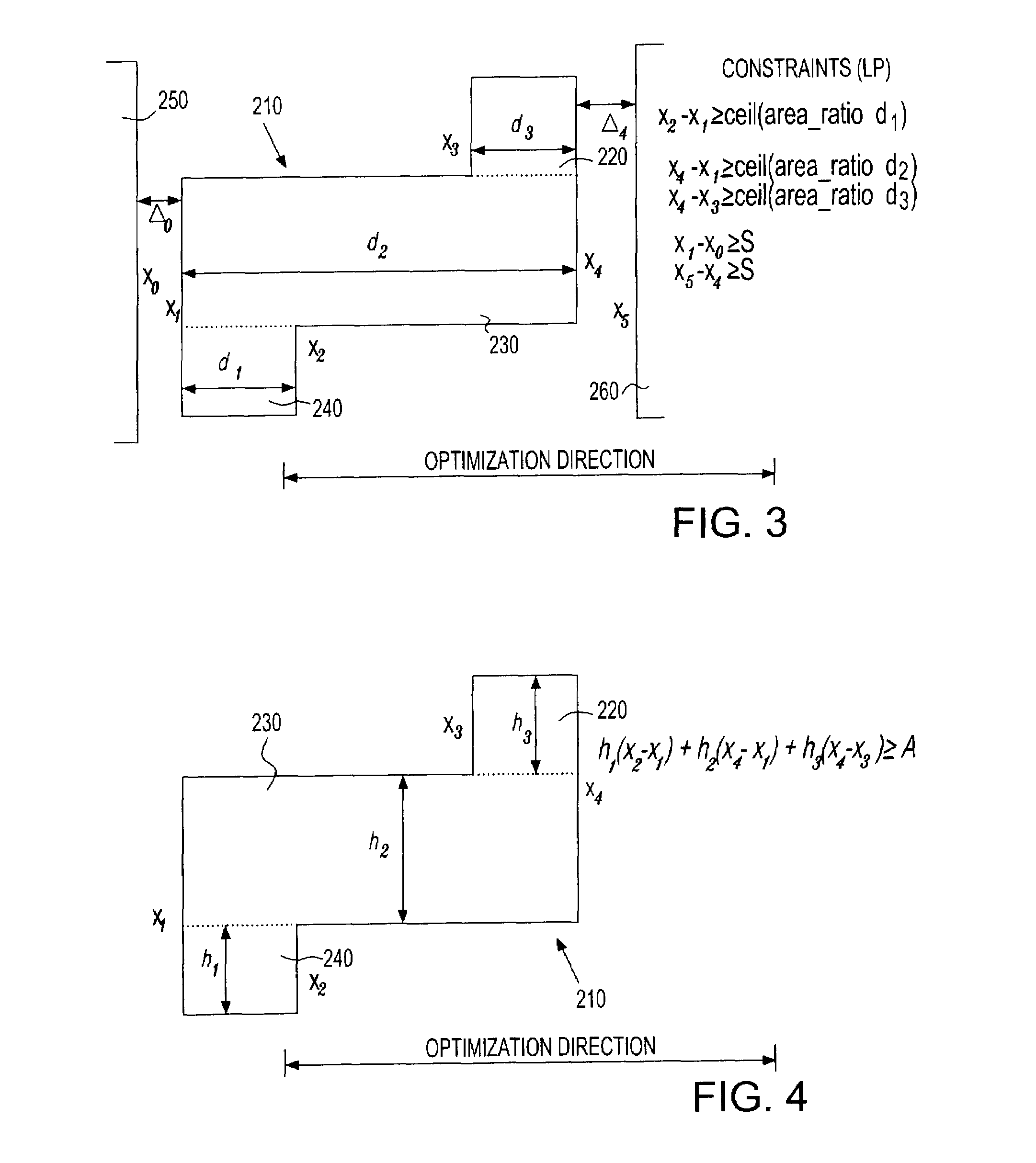

Polygonal area design rule correction method for VLSI layouts

InactiveUS20090037850A1Computer aided designSoftware simulation/interpretation/emulationVlsi layoutCorrection method

A method of polygonal area design rule correction for use in an electronic design automation tool for governing integrated circuit (IC) design layouts using one-dimensional (1-D) optimization, with steps of analyzing IC design layout data to identify violating polygons, partitioning violating polygons into rectangles in a direction of optimization, formulating an area constraint for each violating polygon to formulate a global linear programming (LP) problem that includes each constraint for each violating polygon and solving the global LP problem to obtain a real-valued solution. A next LP problem is created for each area constraint, and solved. The creating a next and solving the next LP problem and solving are repeated until the last “next LP problem” is solved using constraints and objectives representing sums or differences of no more than two optimization variables.

Owner:IBM CORP

VLSI Layouts of Fully Connected Generalized and Pyramid Networks with Locality Exploitation

ActiveUS20150046895A1Low pour pointFull connectivityCircuit switching systemsCAD circuit designCross-linkMulti link

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

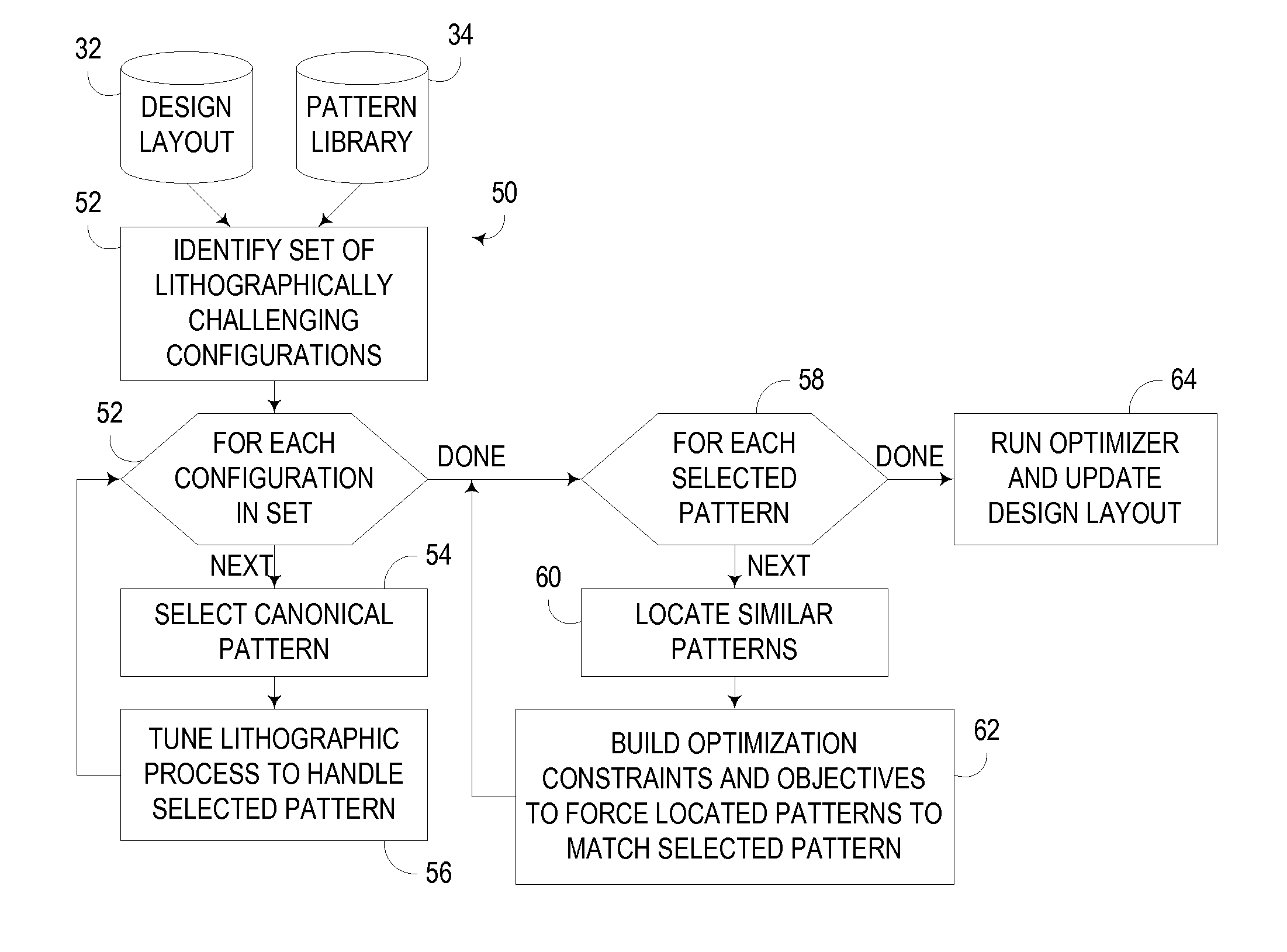

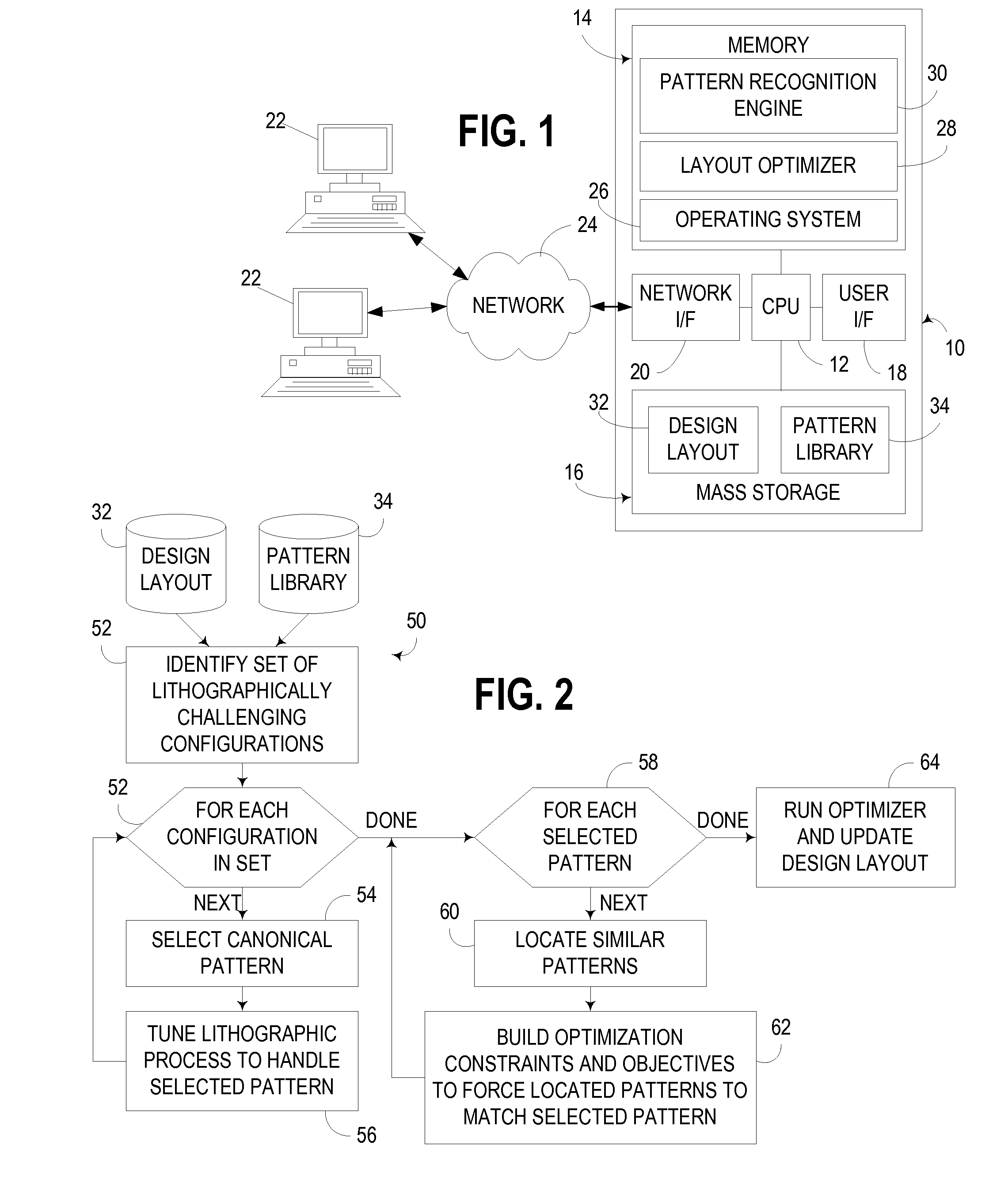

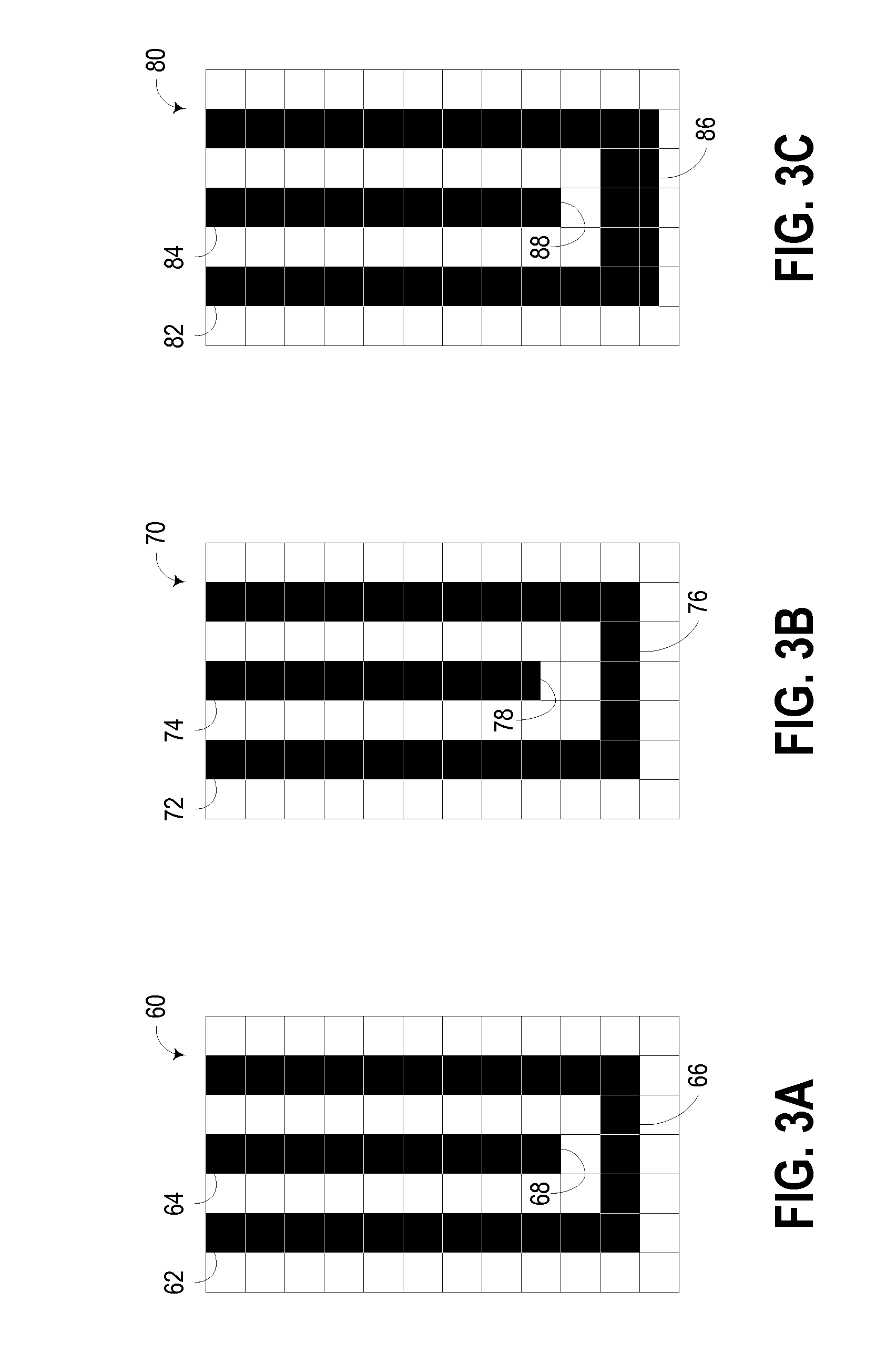

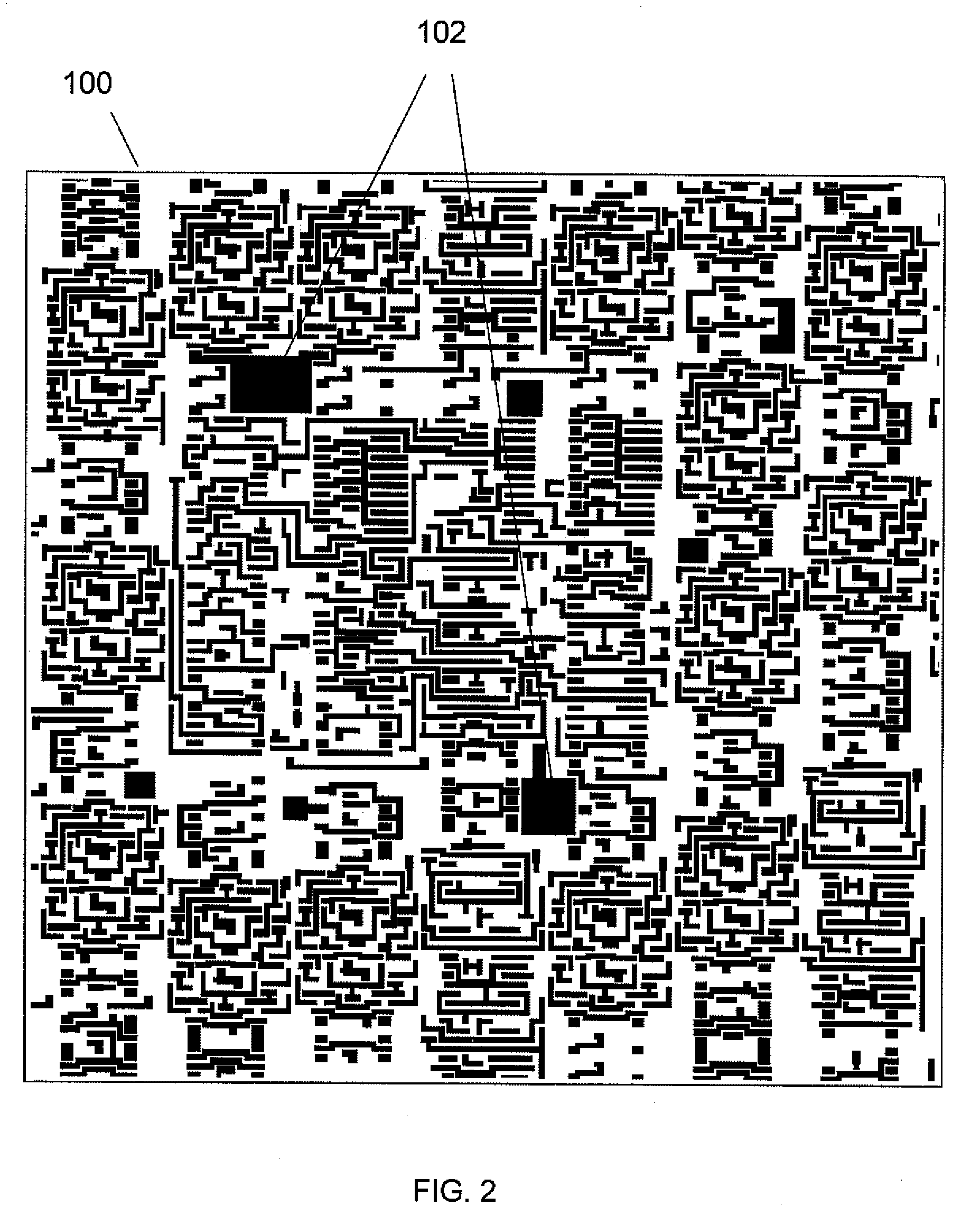

Automated optimization of VLSI layouts for regularity

InactiveUS20080155482A1Improve lithographic fidelityReducing pattern space of patternComputer aided designTotal factory controlEngineeringVlsi layout

VLSI lithographic fidelity is improved via reducing the pattern space of difficult patterns or structures in a design layout for an integrated circuit design, and thereby increasing the regularity of the design, by converting patterns or structures that are similar but not identical to one another into a smaller set of canonical geometric configurations. By doing so, lithographic processing can be tuned to handle the smaller set of configurations more accurately and efficiently.

Owner:GLOBALFOUNDRIES INC

Optimization of multi-stage hierarchical networks for practical routing applications

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

Optimization of multi-stage hierarchical networks for practical routing applications

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA VENKAT

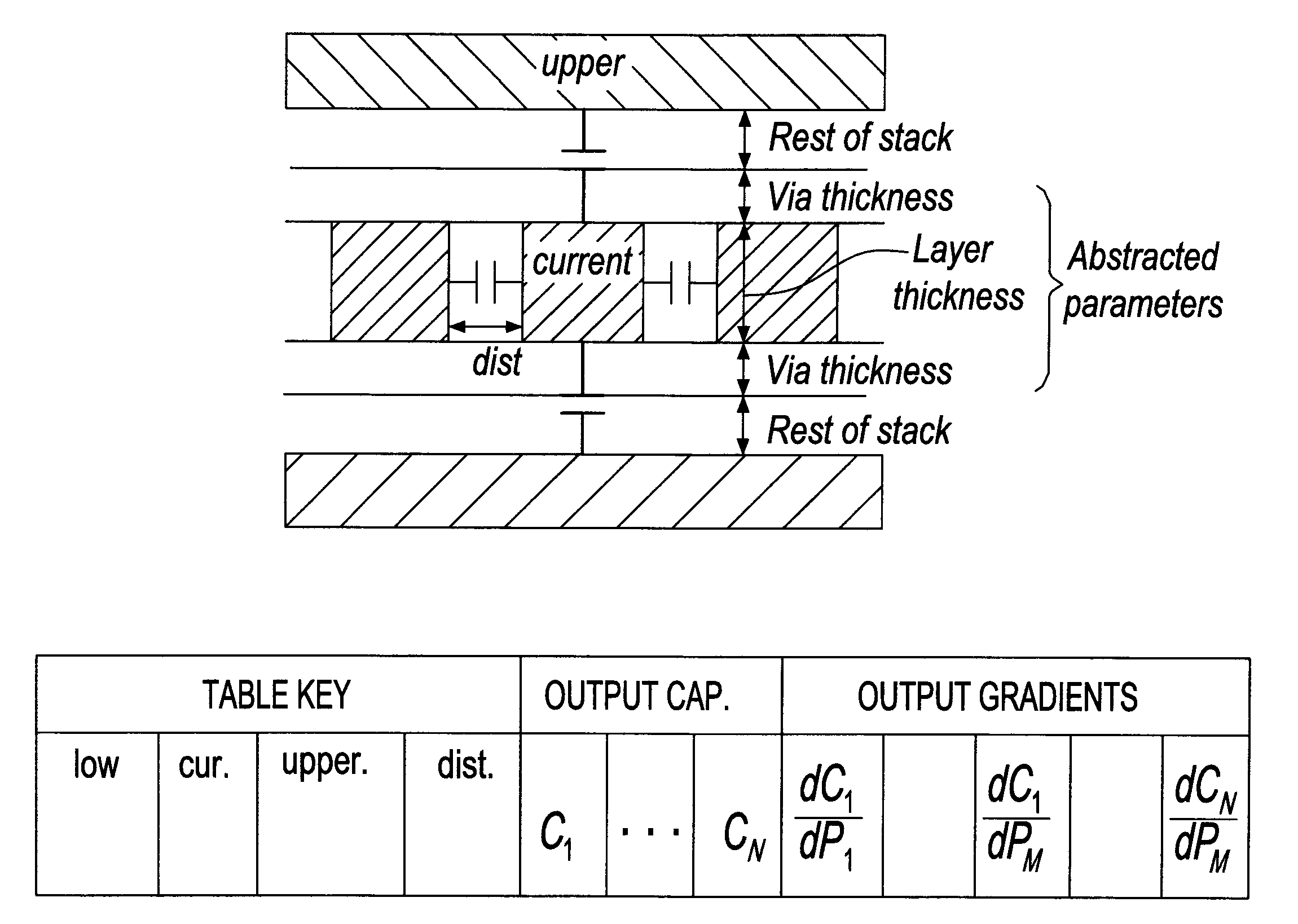

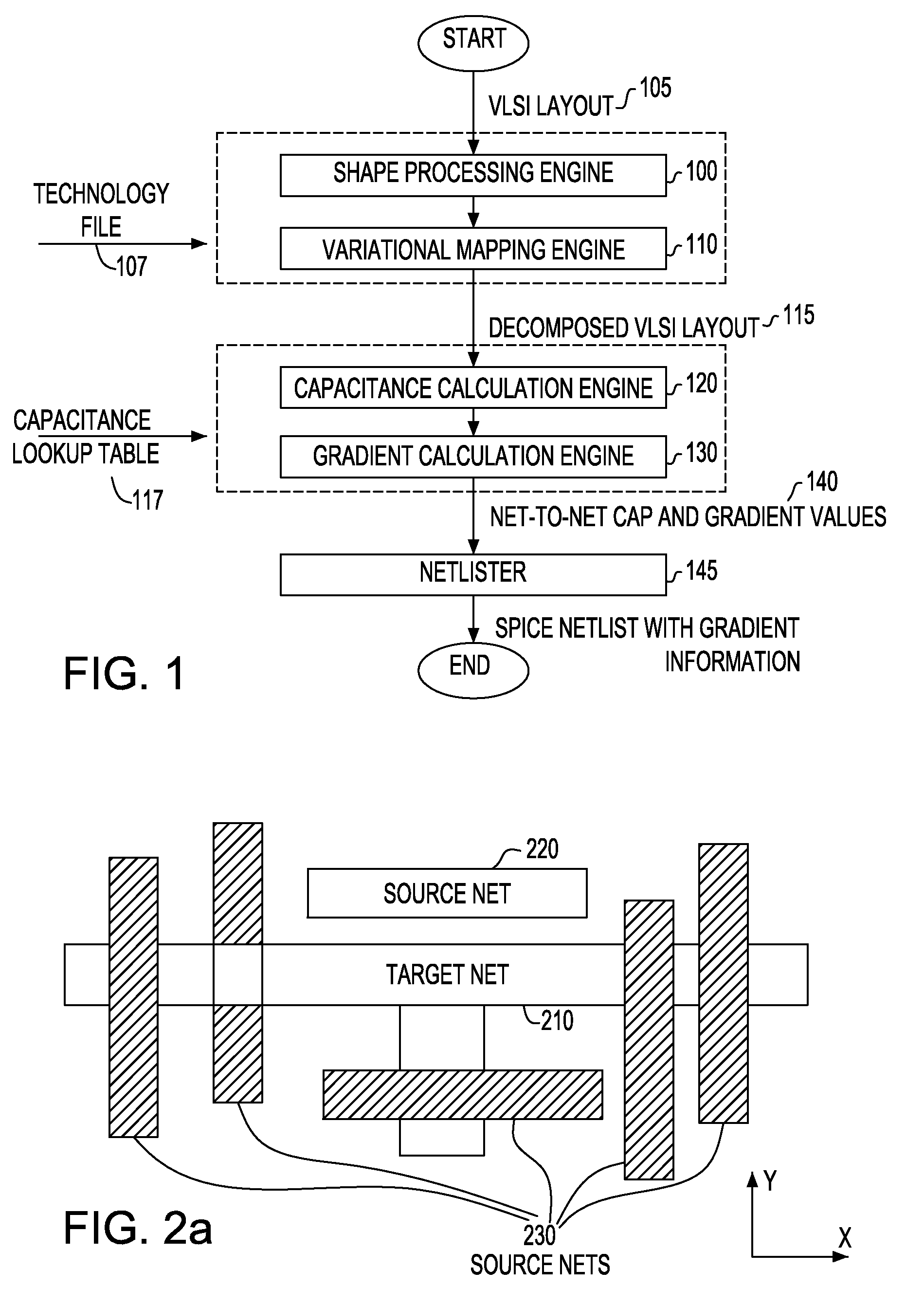

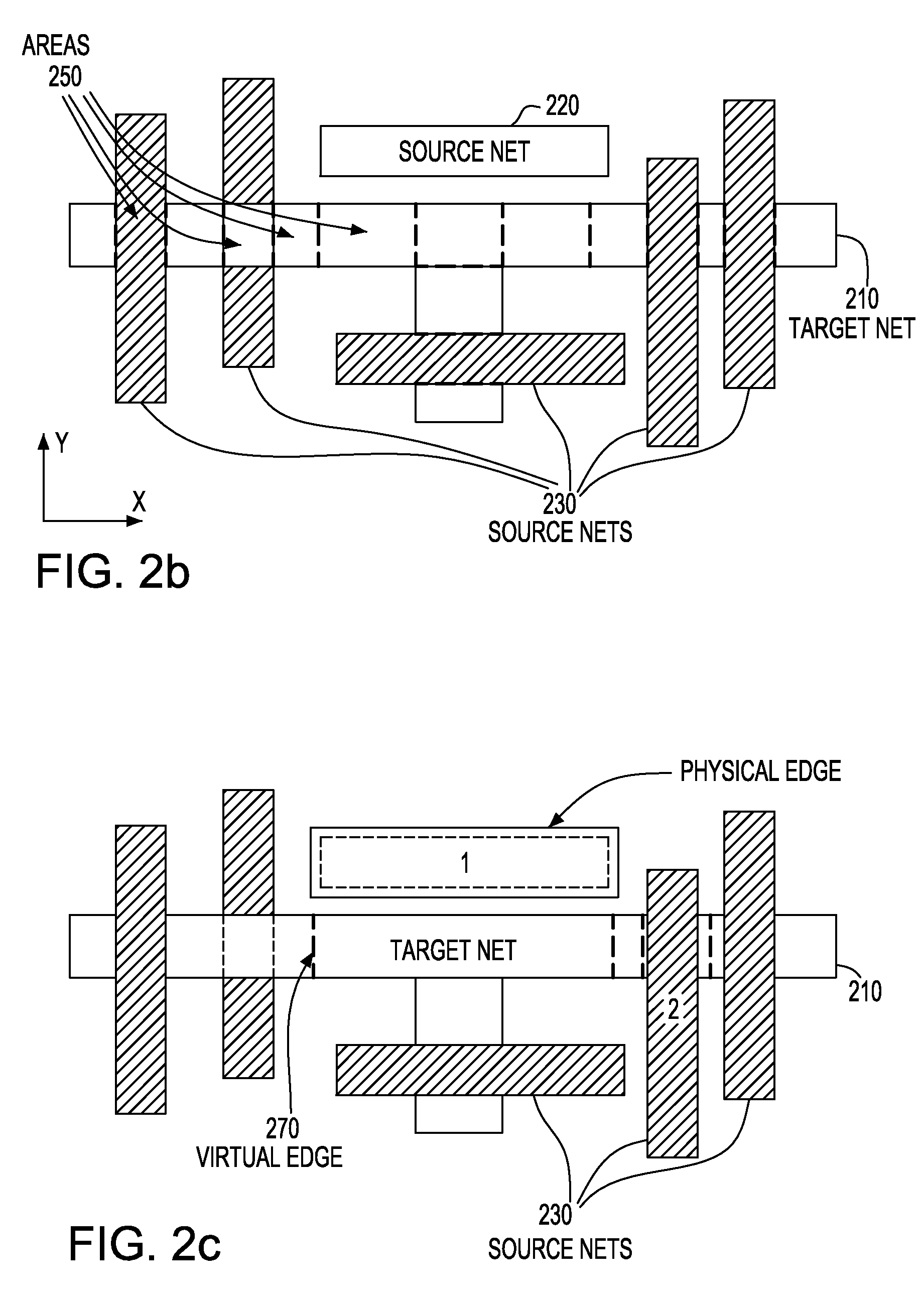

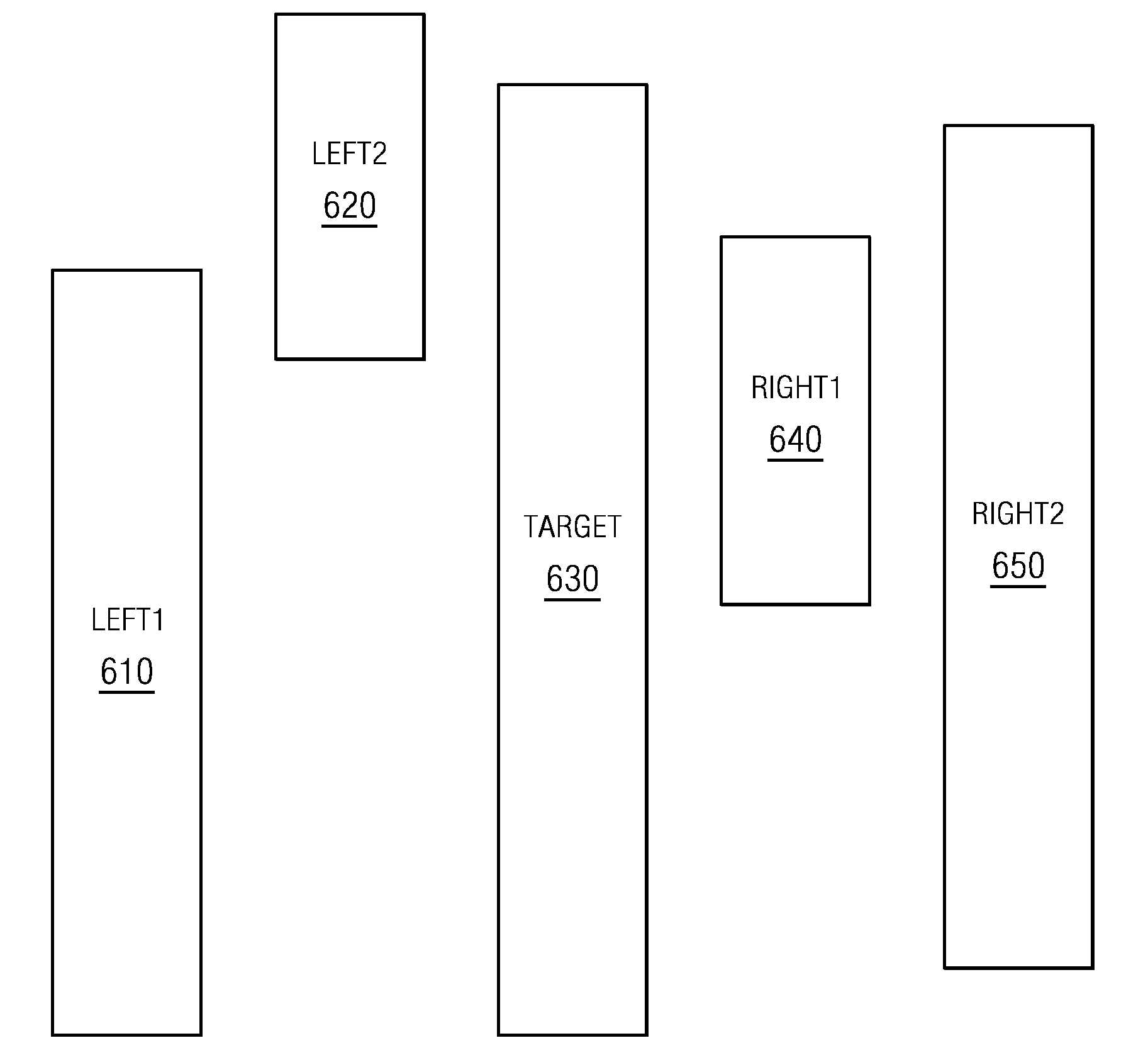

Method for calculating capacitance gradients in VLSI layouts using a shape processing engine

InactiveUS8239804B2Computer aided designSoftware simulation/interpretation/emulationCapacitanceAnalytical expressions

Computing the gradients of capacitances in an integrated circuit chip layout with respect to design and process parameters is described. Included is a shape processing engine in the form of a variational mapping engine and a capacitance calculation engine that includes a gradient calculation engine. The variational mapping engine translates physical parameter variations into variations on the edges of the elementary patterns to which the layout of the integrated circuit is decomposed. The gradient calculation engine computes capacitance gradients by combining information from two sources. The first source consists of pre-existing gradients in a capacitance lookup table. The second source consists of analytical expressions of capacitance correction factors.

Owner:GLOBALFOUNDRIES INC

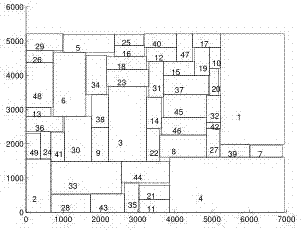

Accurate Approximation of Resistance in a Wire with Irregular Biasing and Determination of Interconnect Capacitances in VLSI Layouts in the Presence of Catastrophic Optical Proximity Correction

ActiveUS20100262940A1Reduce memoryReduce performance consumptionComputer aided designSoftware simulation/interpretation/emulationCapacitanceElectrical resistance and conductance

The Width Bias Calculator (WBC) calculates electrical values by effectively averaging the electrical values to either side of a target wire shape whereby values are approximated for design validation without a significant impact on performance or memory consumption.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

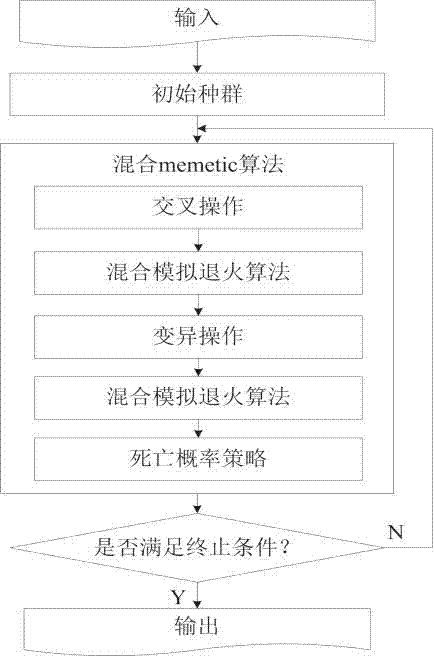

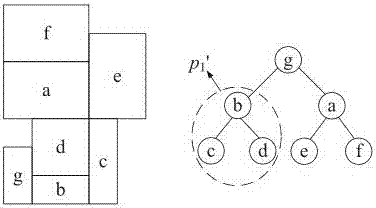

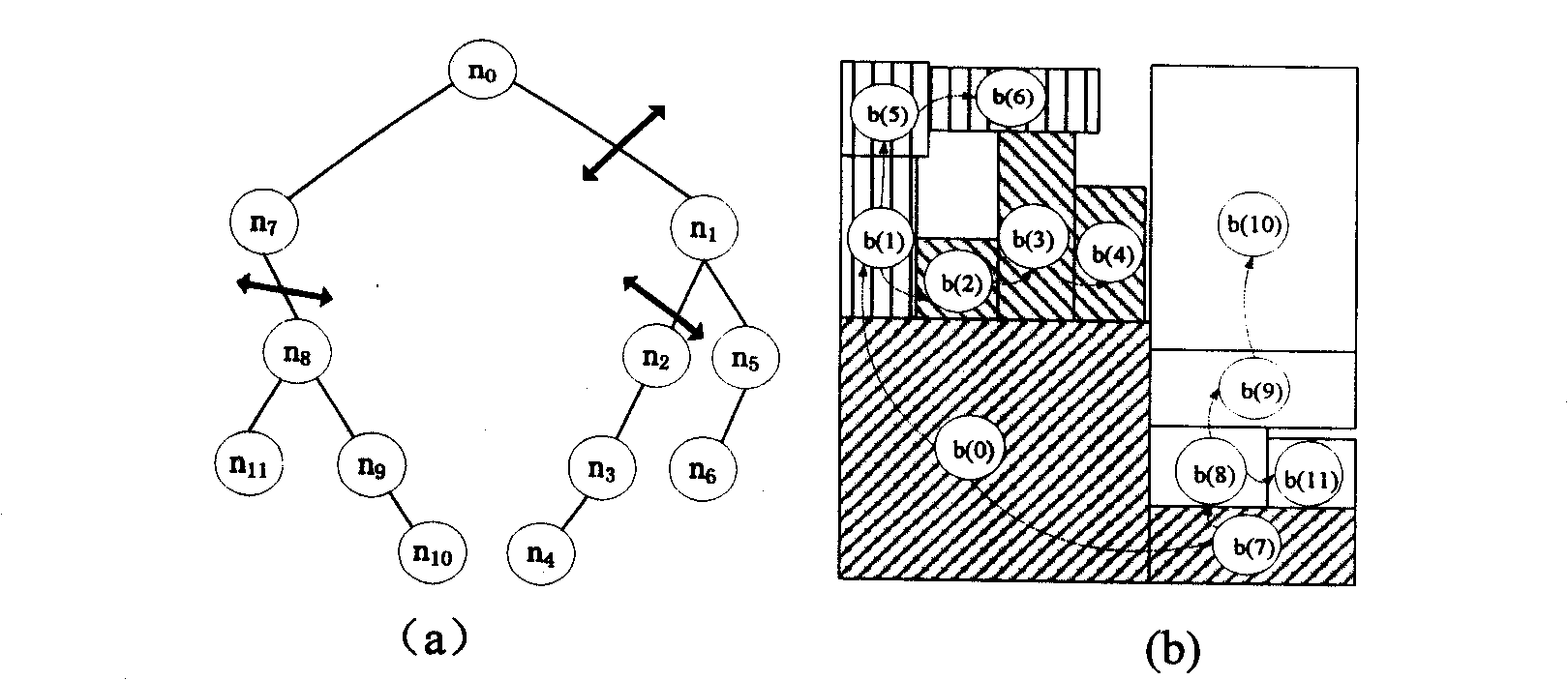

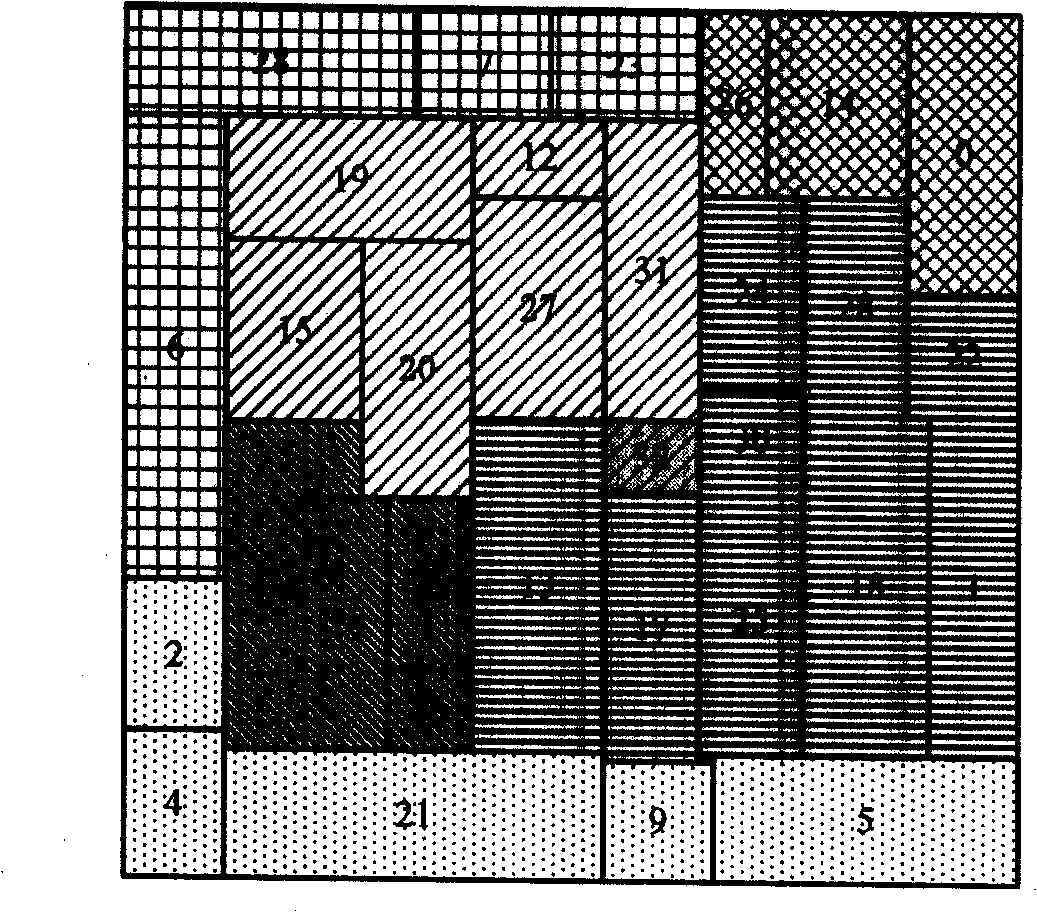

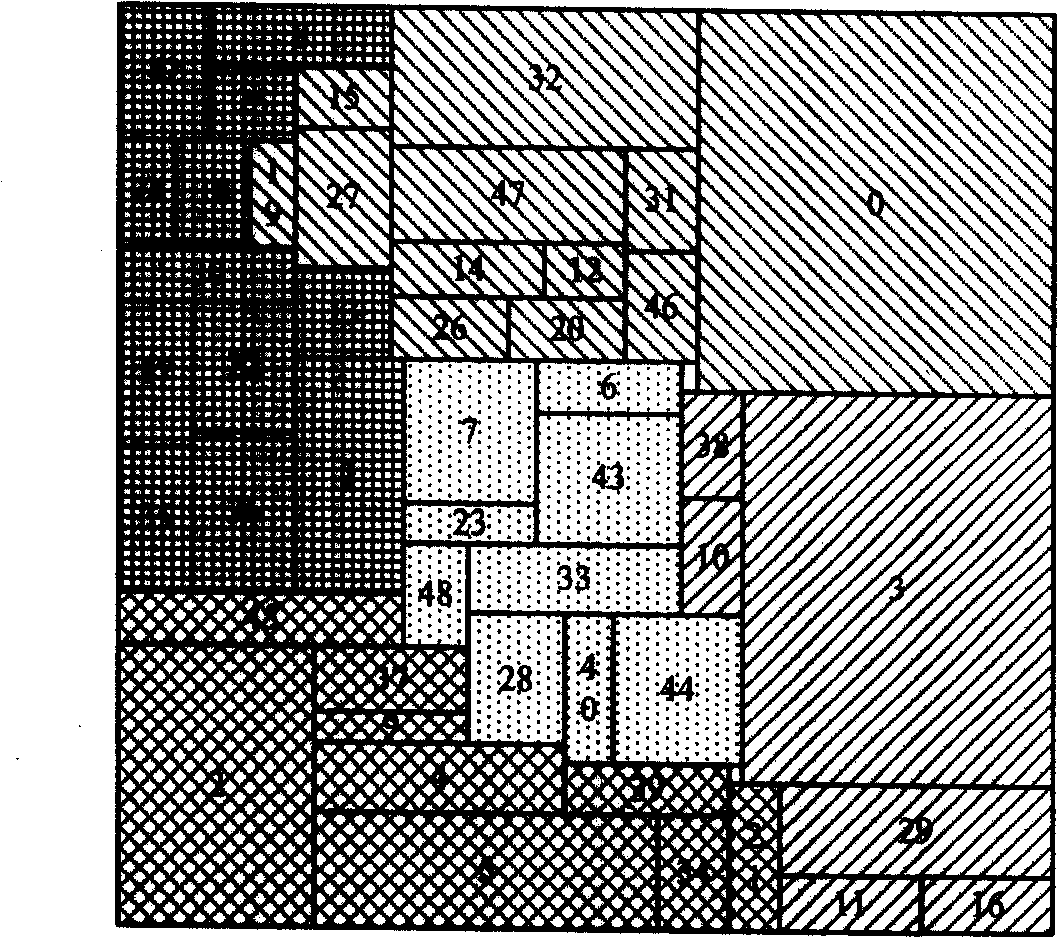

Design method used for solving VLSI (Very Large Scale Integration) Non-secondary-division layout planning

InactiveCN106971041AReduce search timeBalanced Global SearchSpecial data processing applicationsGenetic algorithmsLocal optimumLayout planning

The invention relates to a design method used for solving VLSI (Very Large Scale Integration) Non-secondary-division layout planning. The method comprises the following steps that: (1) in a global search stage, adopting a genetic operator operation to carry out global search, wherein the operator can effectively increase the type of solutions and a possibility for searching an optimal solution; (2) in a local search stage, circularly calling a hybrid simulated annealing algorithm, wherein the algorithm can effectively search the local optimal solution; and (3) in a balance global and local search stage, adopting a mortality probability strategy, wherein the mortality probability strategy reduces the size of a solution space so as to enable the global search and the local search to achieve certain balance. In the strategy, according to a natural rule, each individual in a population can not exist all the time or can not immediately die, on the basis of the rule, and each individual in the population is endowed with a practical age and a dynamic existence age. By use of the method provided by the invention, an efficient and practical layout planning result can be provided, and in addition, a planning result can meet existing VLSI layout planning design requirements.

Owner:FUZHOU UNIV

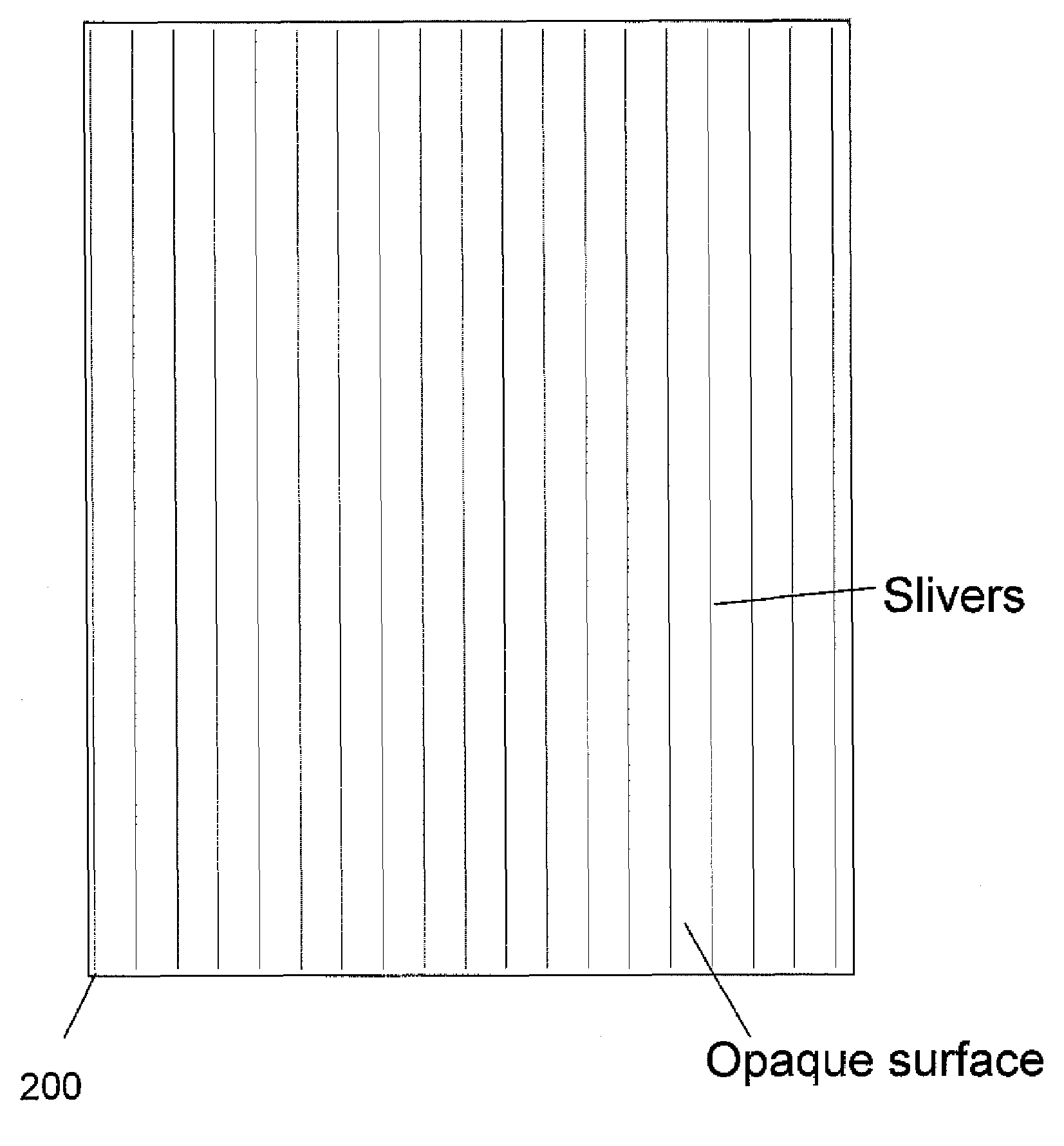

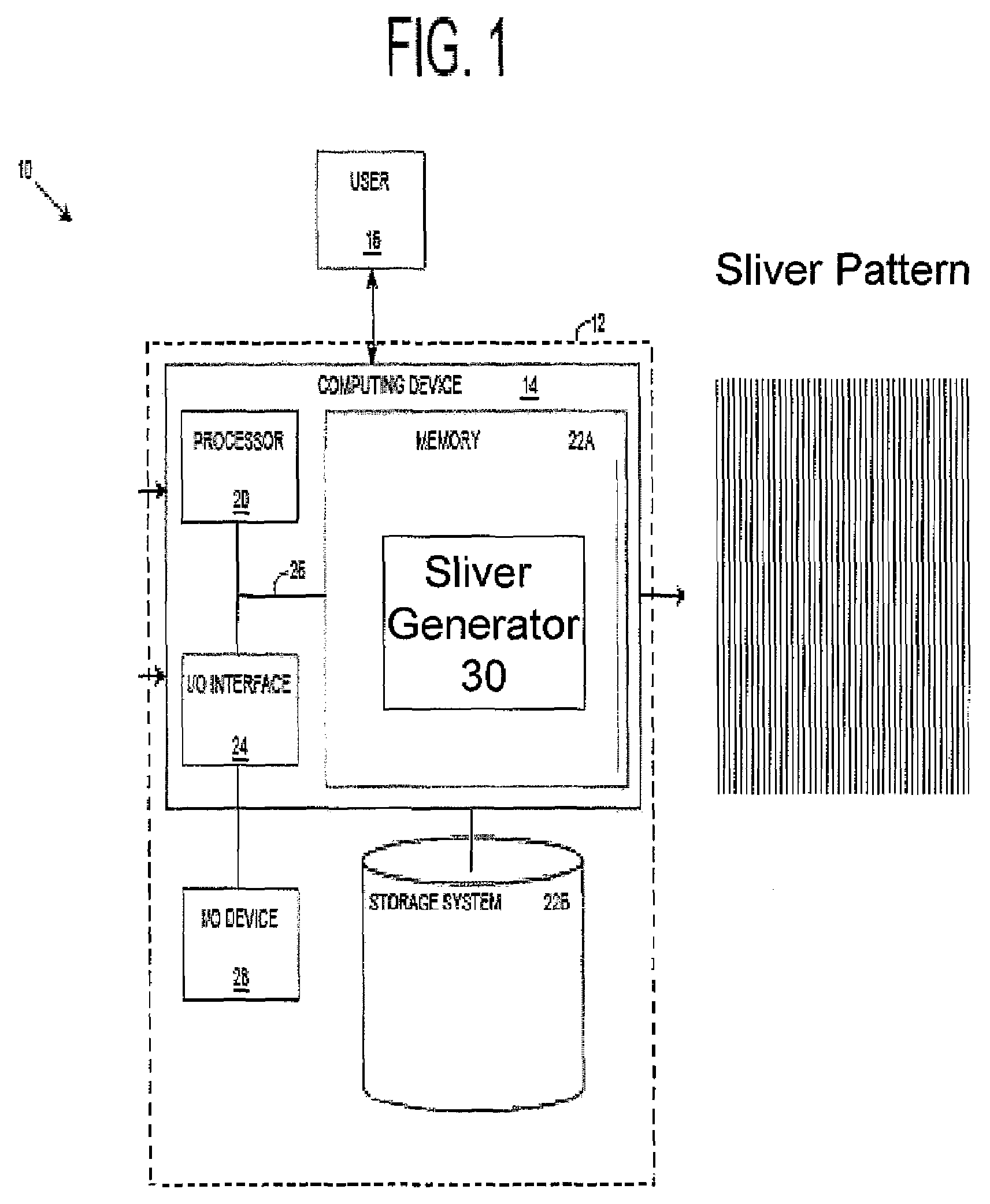

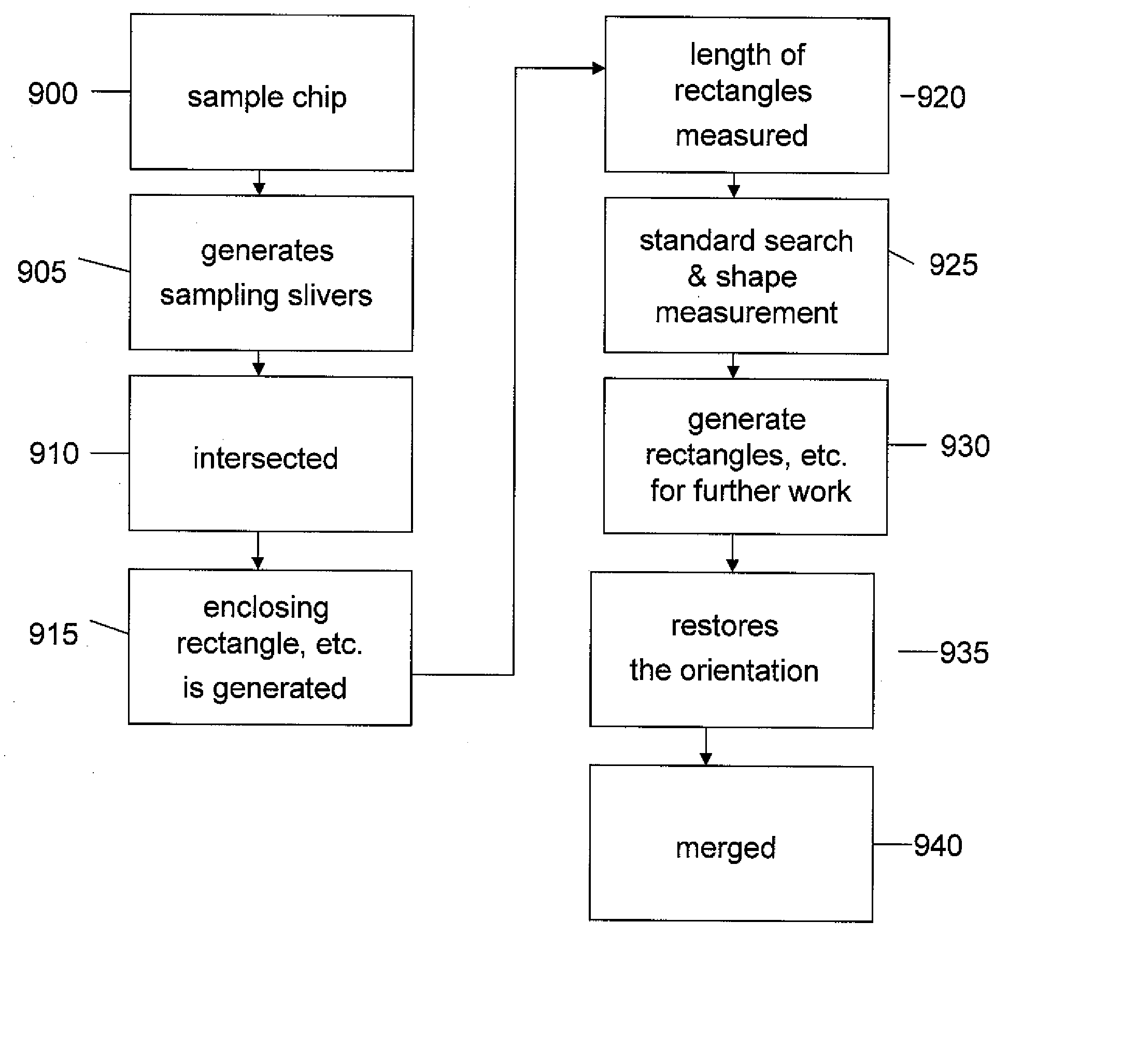

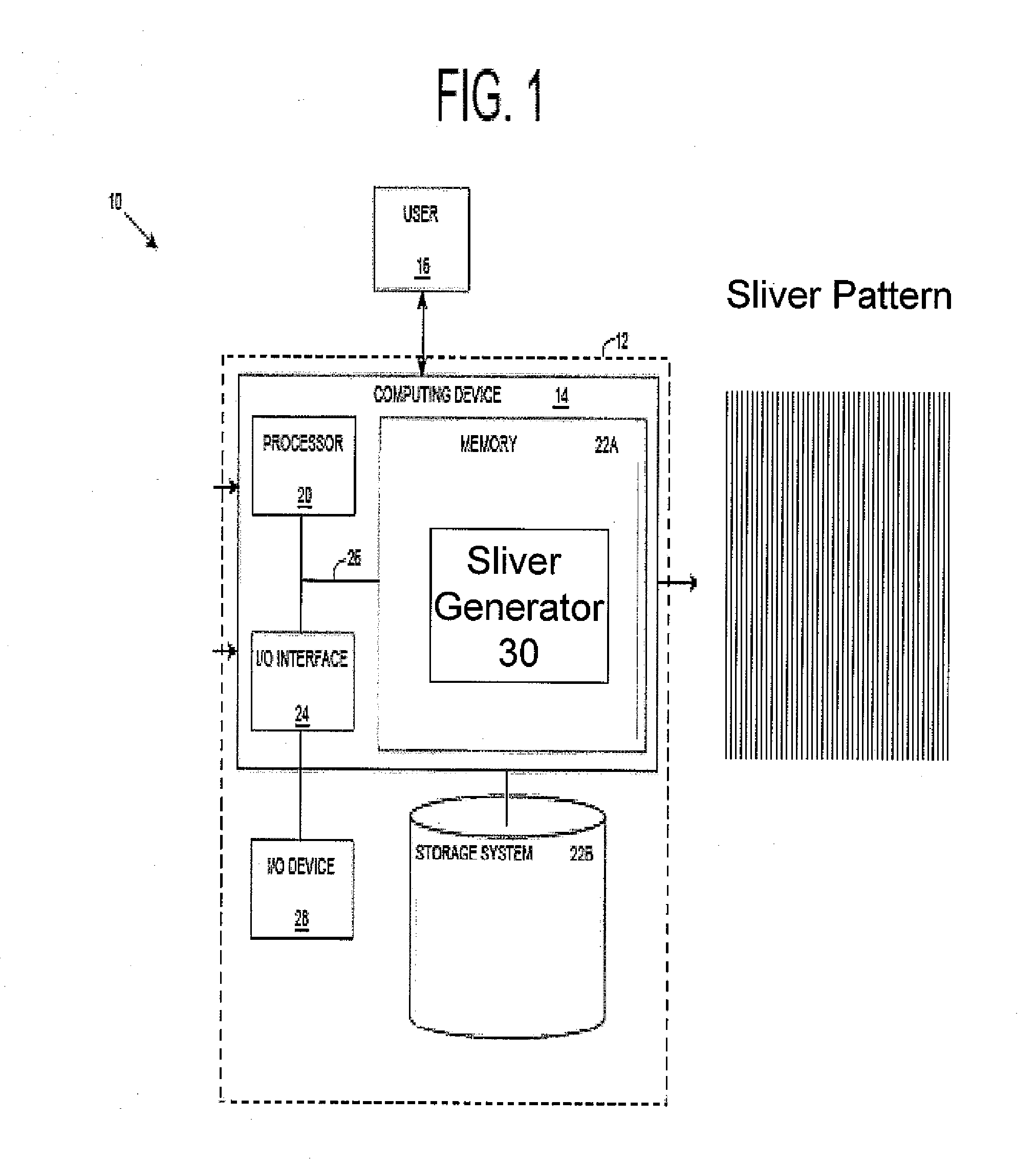

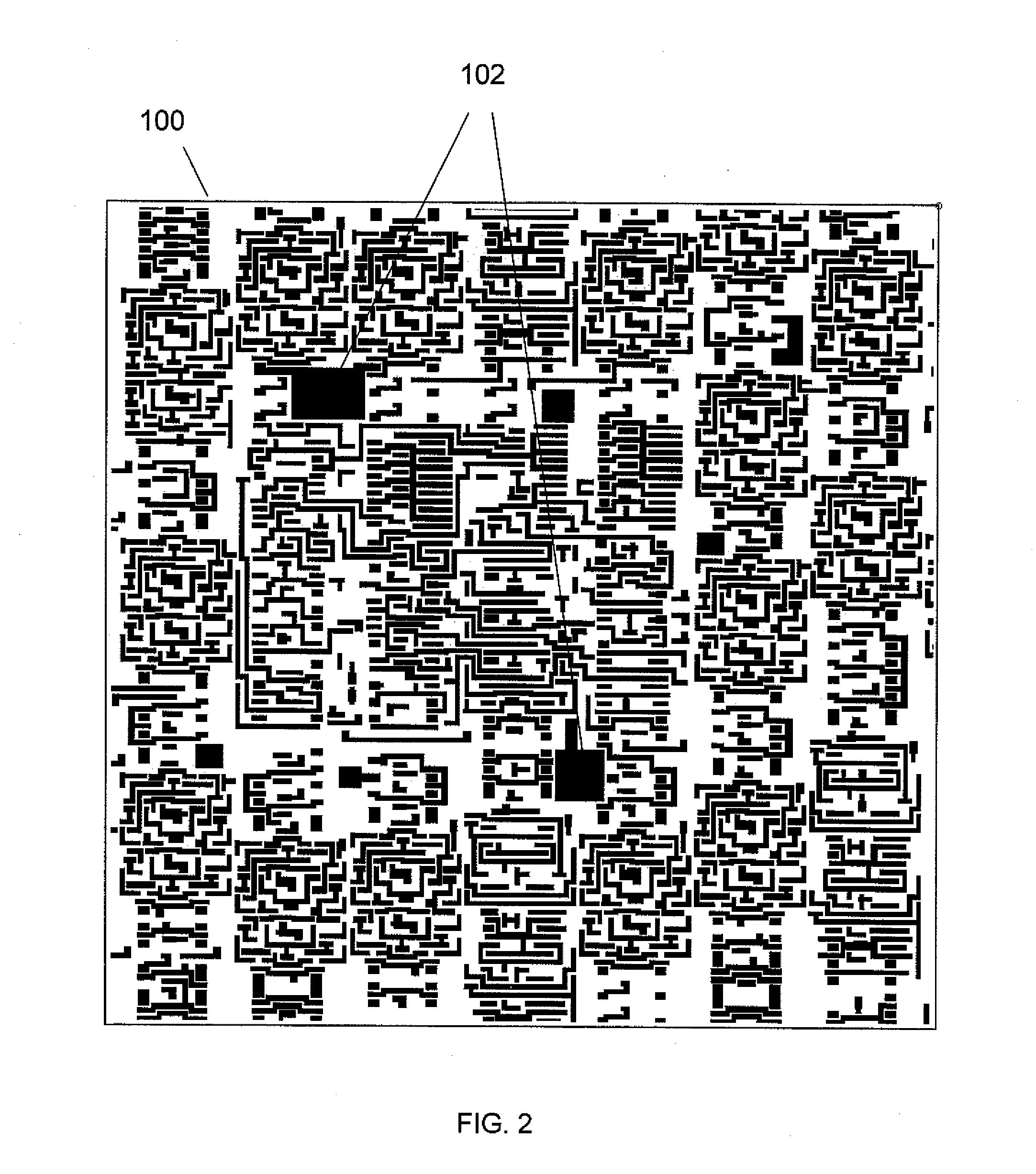

Method and apparatus of rapid determination of problematic areas in VLSI layout by oriented sliver sampling

A method and system for identifying problematic areas in a very large scale integrated (VLSI) layout. The method and system includes defining one or more sample area and overlaying the one or more sample area onto at least a portion of a layout having a plurality of structures. The method and system includes identifying at least one region of the layout in the sample area which has at least one structure which satisfies a predetermined value. In embodiments, the method and system can be implemented on a computer program product comprising a computer useable medium including a computer readable program.

Owner:INT BUSINESS MASCH CORP

AUTOMATIC MULTI-STAGE FABRIC GENERATION FOR FPGAs

Systems and methods to automatically generate various multi-stage pyramid network based fabrics, applicable to including Field programmable gate arrays, are disclosed. Significantly optimized multi-stage pyramid networks either partially connected or fully connected, useful in wide target applications, with VLSI layouts (or floor plans) substantially using horizontal and vertical links to route signals between inlet and outlet links of large scale sub-integrated circuit blocks and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks, (for example in an FPGA where the sub-integrated circuit blocks are Lookup Tables, or memory blocks, or DSP blocks) are disclosed. The optimized multi-stage networks in each block employ a plurality of slices of rings of stages of switches with different size multiplexer having inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side, or from right-hand side, or from both left-hand side and right-hand side, or through any incoming and outgoing links of any stage. The VLSI layouts exhibit spatial locality so that sub-integrated circuit blocks that are spatially nearer are connected with shorter hop wires.Fabrics are generated iteratively either manually or automatically by changing different parameters including such as number of slices, number of rings, number of stages, number of switches, number of multiplexers, the size of the multiplexers which may be in any switch, connections between stages of rings which may be between the same numbered stages (same level stages) or different numbered stages, single or multi-drop hop wires, hop wires of different hop lengths, hop wires outgoing to different directions, hop wires incoming from different directions, number of hop wires based on the number and type of inlet and outlet links of large scale sub-integrated circuit blocks. One or more parameters are changed in each iteration so that optimized fabrics are generated, at the end of iterations, to route a given set of benchmarks or designs having a specific connection requirements.

Owner:KONDA TECH

Method and apparatus of rapid determination of problematic areas in VLSI layout by oriented sliver sampling

A method and system for identifying problematic areas in a very large scale integrated (VLSI) layout. The method and system includes defining one or more sample area and overlaying the one or more sample area onto at least a portion of a layout having a plurality of structures. The method and system includes identifying at least one region of the layout in the sample area which has at least one structure which satisfies a predetermined value. In embodiments, the method and system can be implemented on a computer program product comprising a computer useable medium including a computer readable program.

Owner:IBM CORP

VLSI layout planning centralized constrain implementing method

InactiveCN101339571BSpecial data processing applicationsLinear programming algorithmComputer Aided Design

The invention belongs to a technical field of an integrated circuit computer aided design, in particular to the implementation method of centralized constraint in VLSI layout planning. The method is combined with B<*> -tree representation, simulated annealing algorithm and linear programming algorithm. The steps comprise that a constrained sub-tree is constructed according to constraint, each sub-tree is connected so as to form a permissible initial layout, and the simulated annealing algorithm is adopted to optimize such factors as areas, and the like; the constraint condition of linear programming is obtained from the initial layout, a linear programming matrix is constructed, a linear programming function is called for solving the linear programming matrix, compressing operation and soft module adjustment are carried out, and finally the result of optimizing the layout is obtained. The method is used for realizing the constraint that a plurality of modules need to be centralized and placed in a plane layout, and also is used for realizing the centralized constraint on the basis of a plurality of divisions or a whole division.

Owner:FUDAN UNIV

Fast scheduling and optimization of multi-stage hierarchical networks

Significantly optimized multi-stage networks including scheduling methods for faster scheduling of connections, useful in wide target applications, with VLSI layouts using only horizontal wires and vertical wires to route large scale partial multi-stage hierarchical networks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are disclosed. The optimized multi-stage networks in each block employ one or more slices of rings of stages of switches with inlet and outlet links of partial multi-stage hierarchical networks connecting to rings from either left-hand side or right-hand side; and employ hop wires or multi-drop hop wires wherein hop wires or multi-drop wires are connected from switches of stages of rings of slices of a first partial multi-stage hierarchical network to switches of stages of rings of slices of the first or a second partial multi-stage hierarchical network.

Owner:KONDA TECH

Optimization of multi-stage hierarchical networks for practical routing applications

ActiveUS11405331B1High routabilityLow pour pointData switching networksTelecommunicationsVlsi layout

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

Owner:KONDA TECH

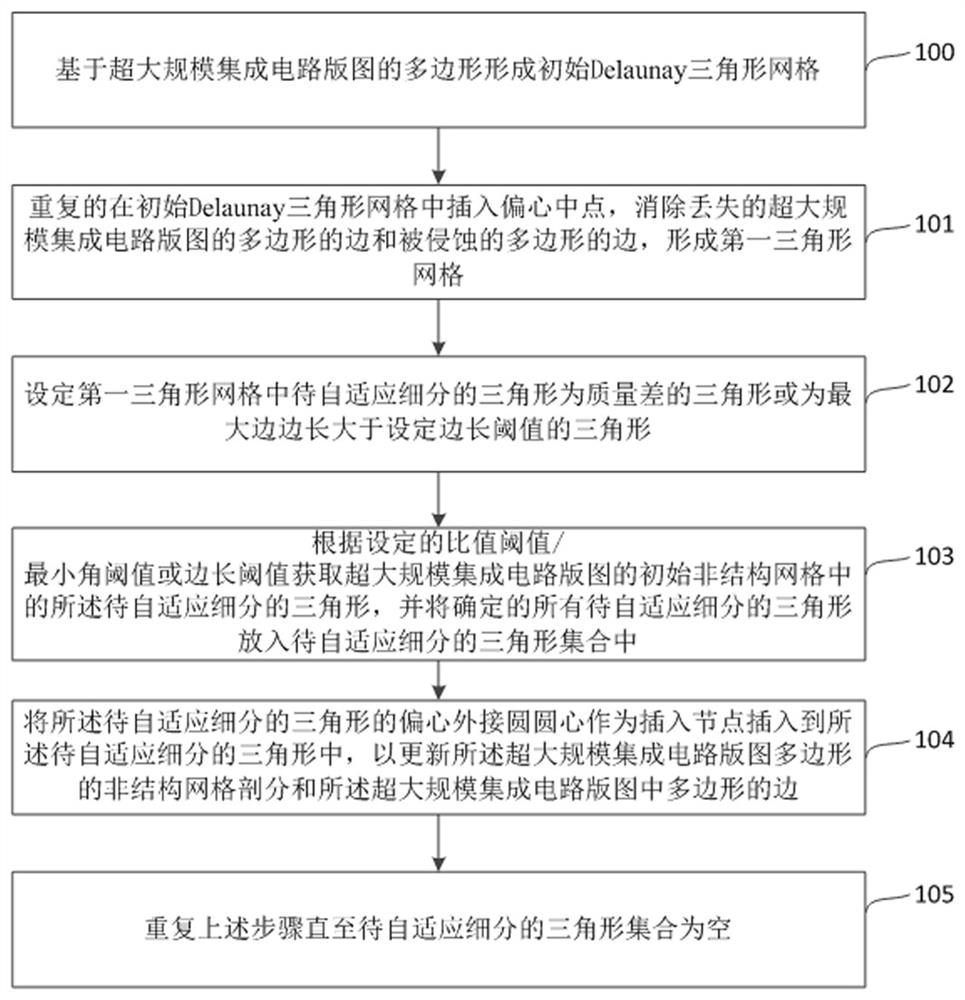

Method and system for self-adaptive subdivision of polygonal unstructured grid for integrated circuit layout

ActiveCN111767688BHigh precisionImprove efficiencyCAD circuit designSpecial data processing applicationsComputational scienceAlgorithm

The invention relates to a method and system for self-adaptive subdivision of a polygonal unstructured grid of an integrated circuit layout. The method includes sequentially inserting eccentric points into the existing mesh according to the lost and eroded polygon edges to recover the lost and eliminated eroded polygon edges, determining the triangles to be subdivided according to the set ratio / minimum angle threshold, in order Insert the center of the eccentric circle of the triangle to be subdivided into the existing mesh to eliminate the triangle to be subdivided. The above restores the lost and eliminated the eroded polygon edges and eliminates the triangle to be subdivided. Interleaved until the integrated circuit layout polygonal unstructured network There are no missing and eroded polygon edges and triangles to be subdivided in the grid, and finally form a new unstructured grid of VLSI layout to solve the redundancy caused by newly inserted nodes in the prior art While solving the problem of excessively dense local grids, it improves grid division accuracy and numerical calculation efficiency, and reduces calculation memory.

Owner:北京智芯仿真科技有限公司