Patents

Literature

322results about How to "Reduce signal delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

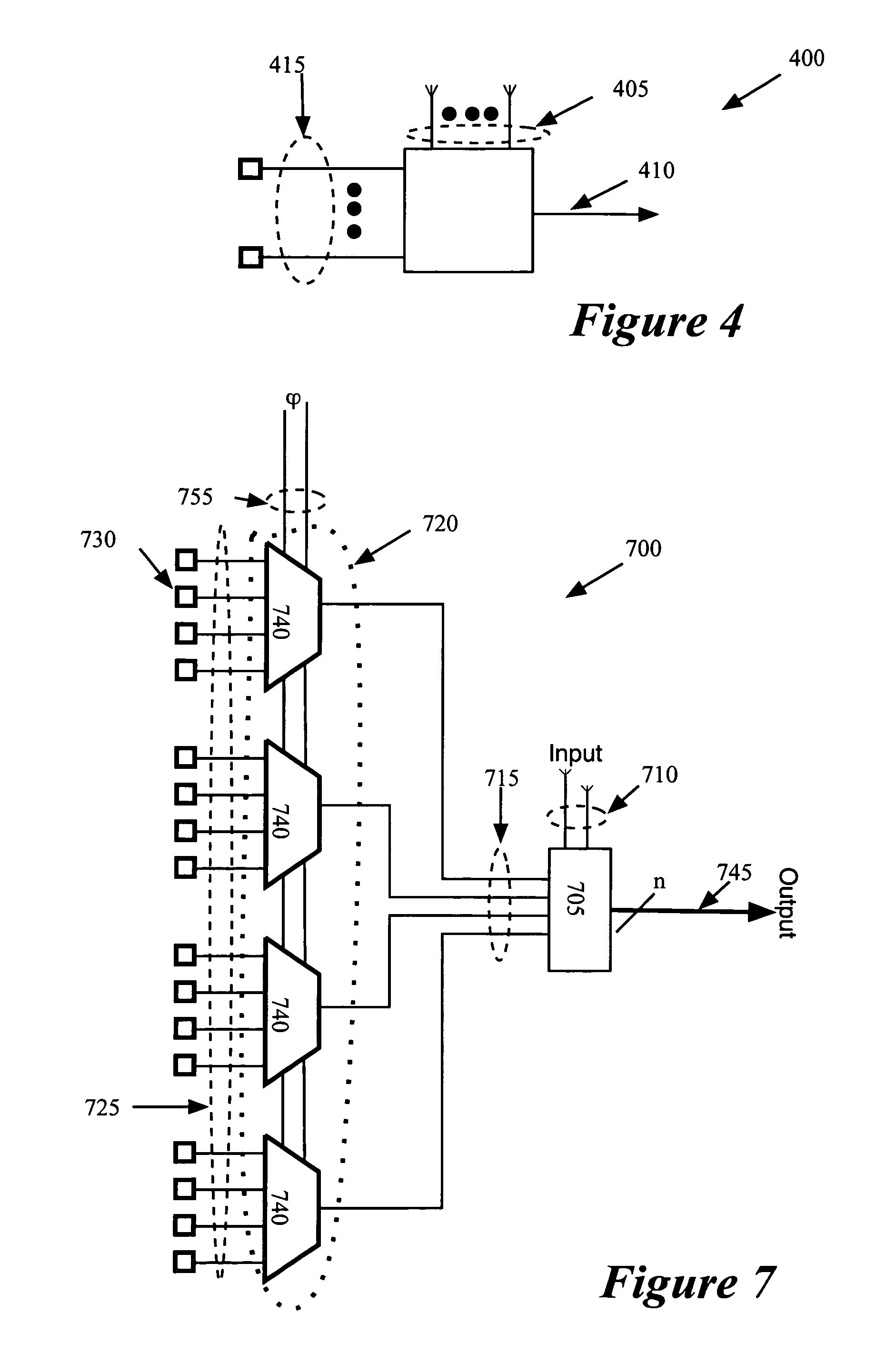

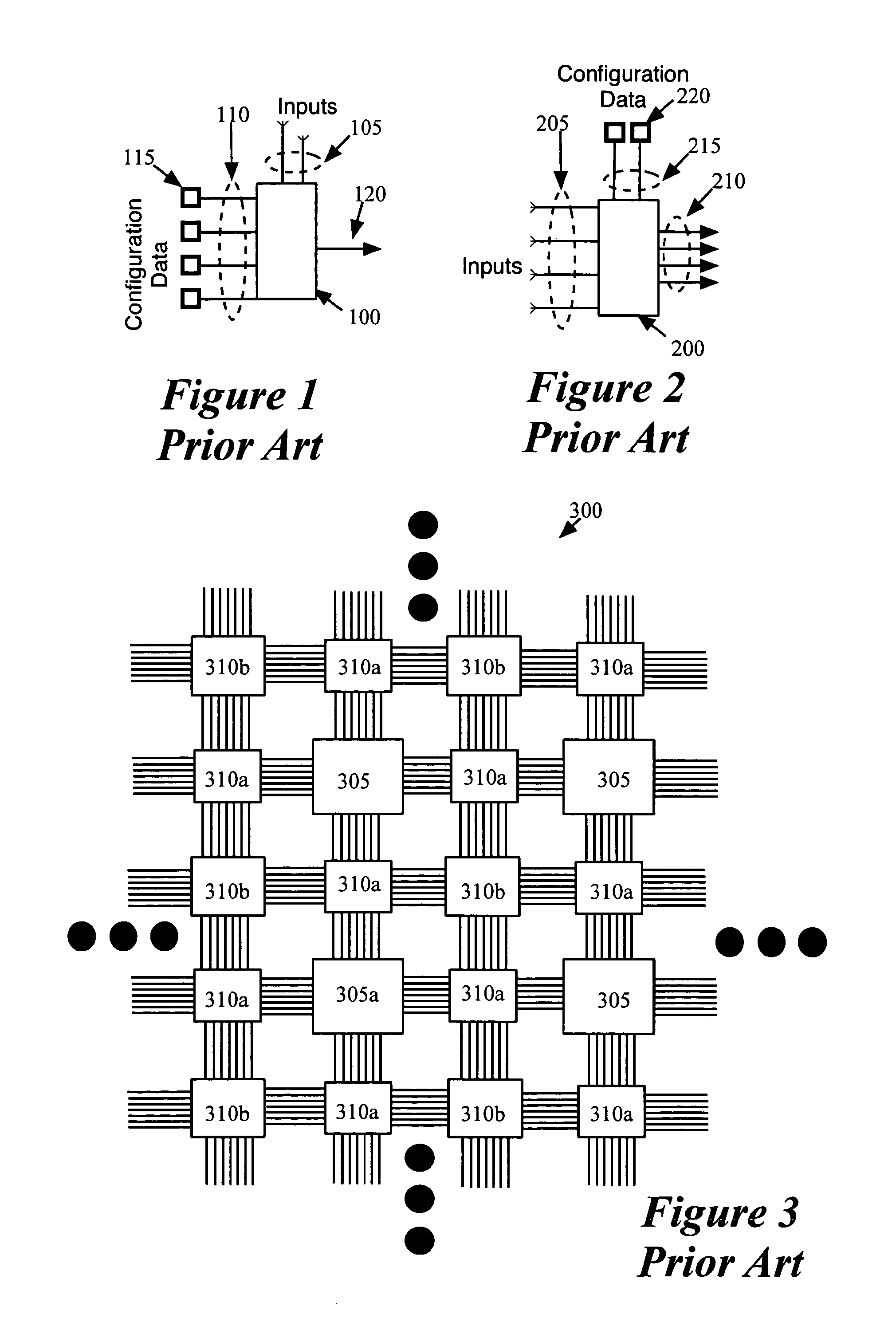

Reconfigurable processing

ActiveUS20070198971A1Reduce signal delayReduce areaEnergy efficient ICTSoftware engineeringPathPingComputer architecture

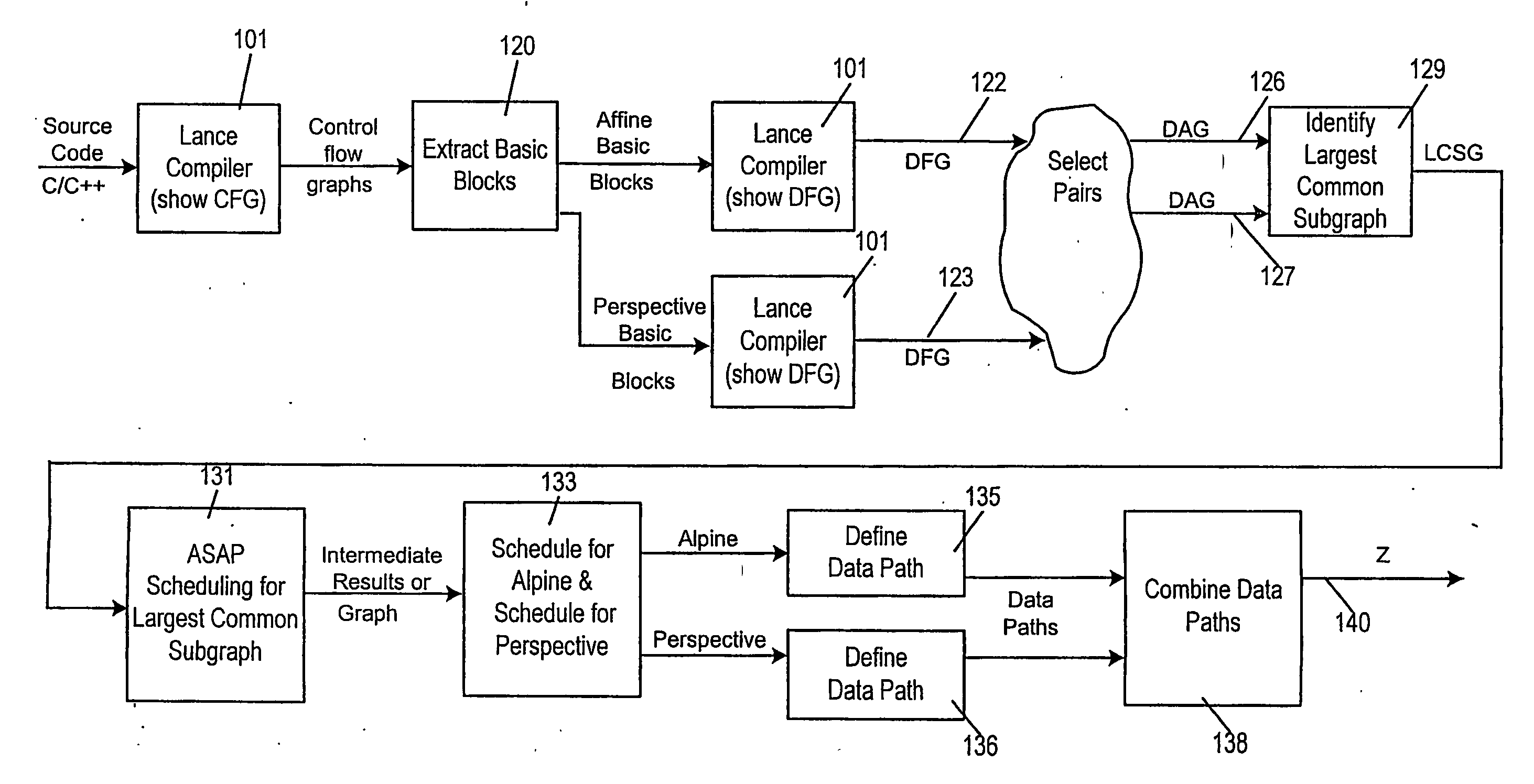

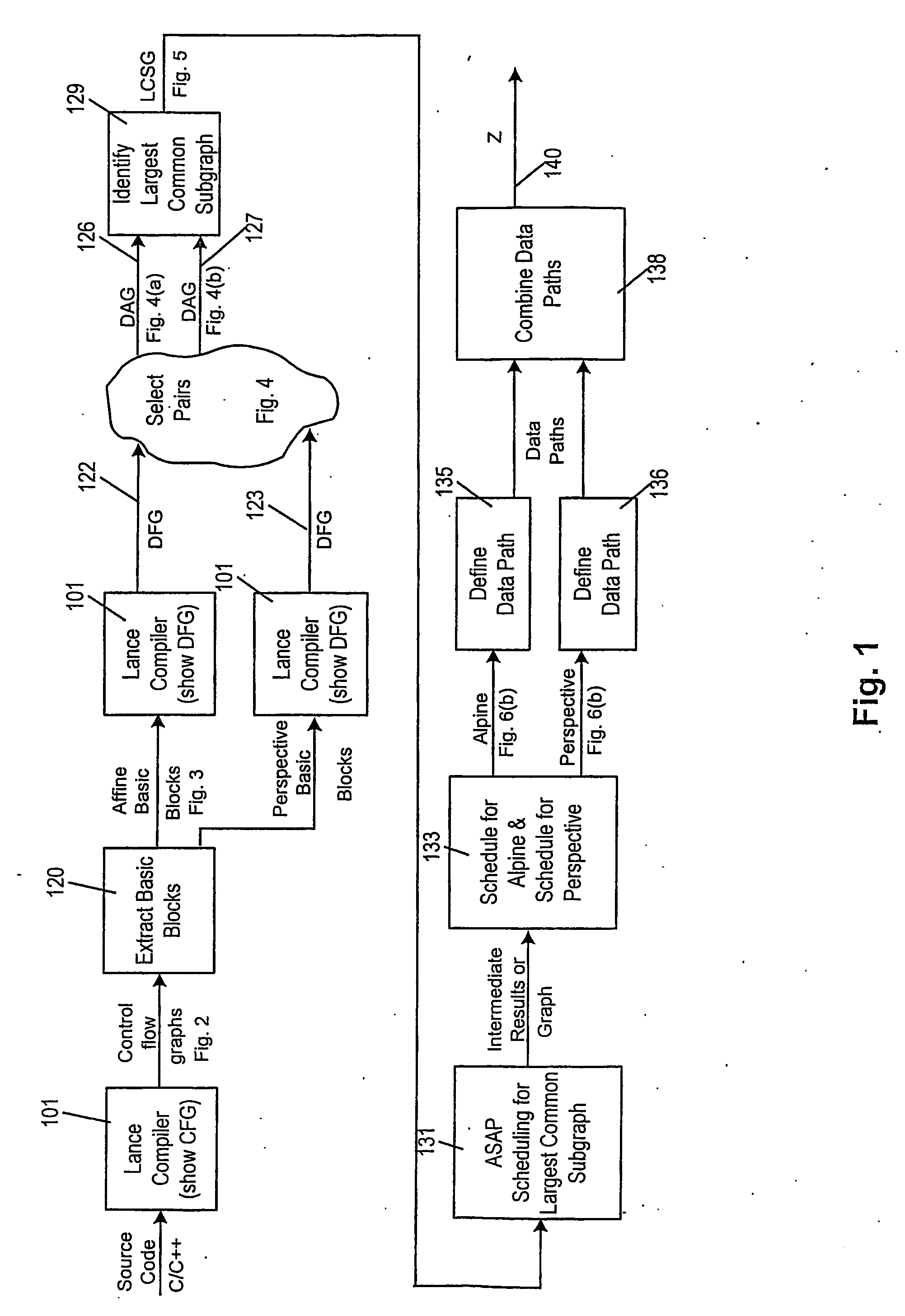

A method of producing a reconfigurable circuit device for running a computer program of moderate complexity such as multimedia processing. Code for the application is compiled into Control Flow Graphs representing distinct parts of the application to be run. From those Control Flow Graphs are extracted basic blocks. The basic blocks are converted to Data Flow Graphs by a compiler utility. From two or more Data Flow Graphs, a largest common subgraph is determined. The largest common subgraph is ASAP scheduled and substituted back into the Data Flow Graphs which also have been scheduled. The separate Data Flow Graphs containing the scheduled largest common subgraph are converted to data paths that are then combined to form code for operating the application. The largest common subgraph is effected in hardware that is shared among the parts of the application from which the Data Flow Graphs were developed. Scheduling of the overall code is effected for sequencing, providing fastest run times and the code is implemented in hardware by partitioning and placement of processing elements on a chip and design of the connective fabric for the design elements.

Owner:ARIZONA STATE UNIVERSITY

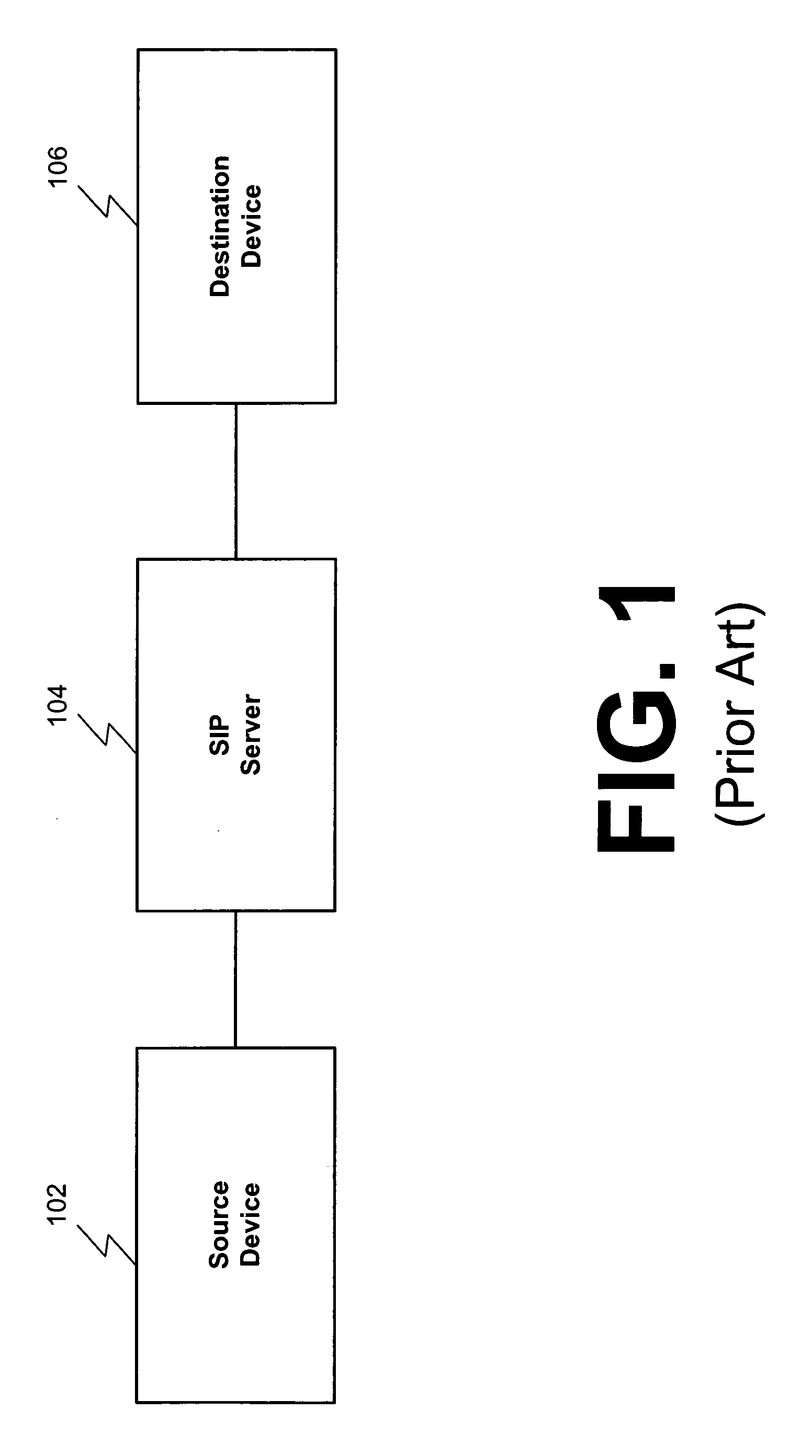

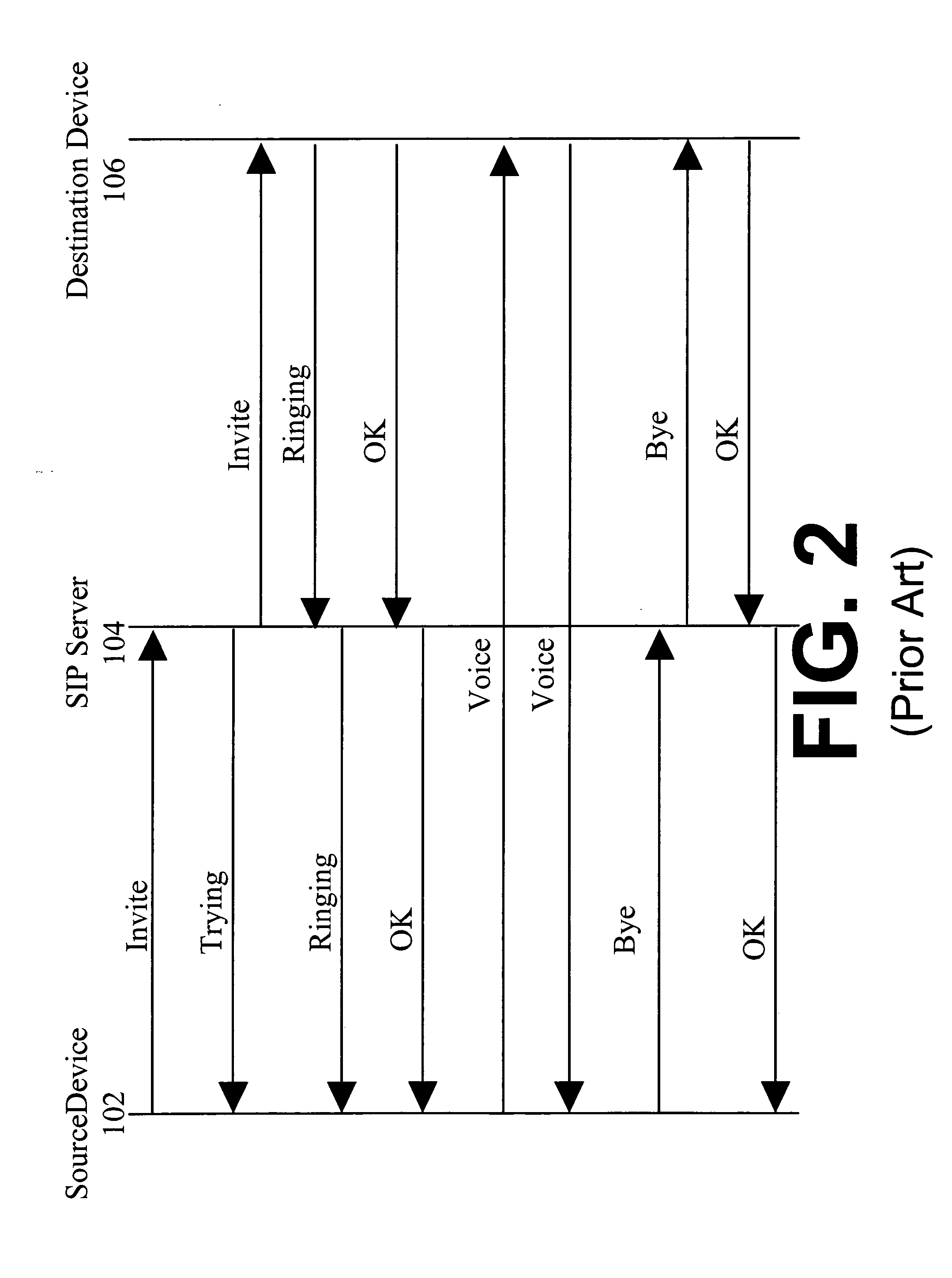

System and method for load balancing a communications network

InactiveUS20060069776A1Reduce signal delayFast communication speedMultiple digital computer combinationsTransmissionLoad SheddingRunning time

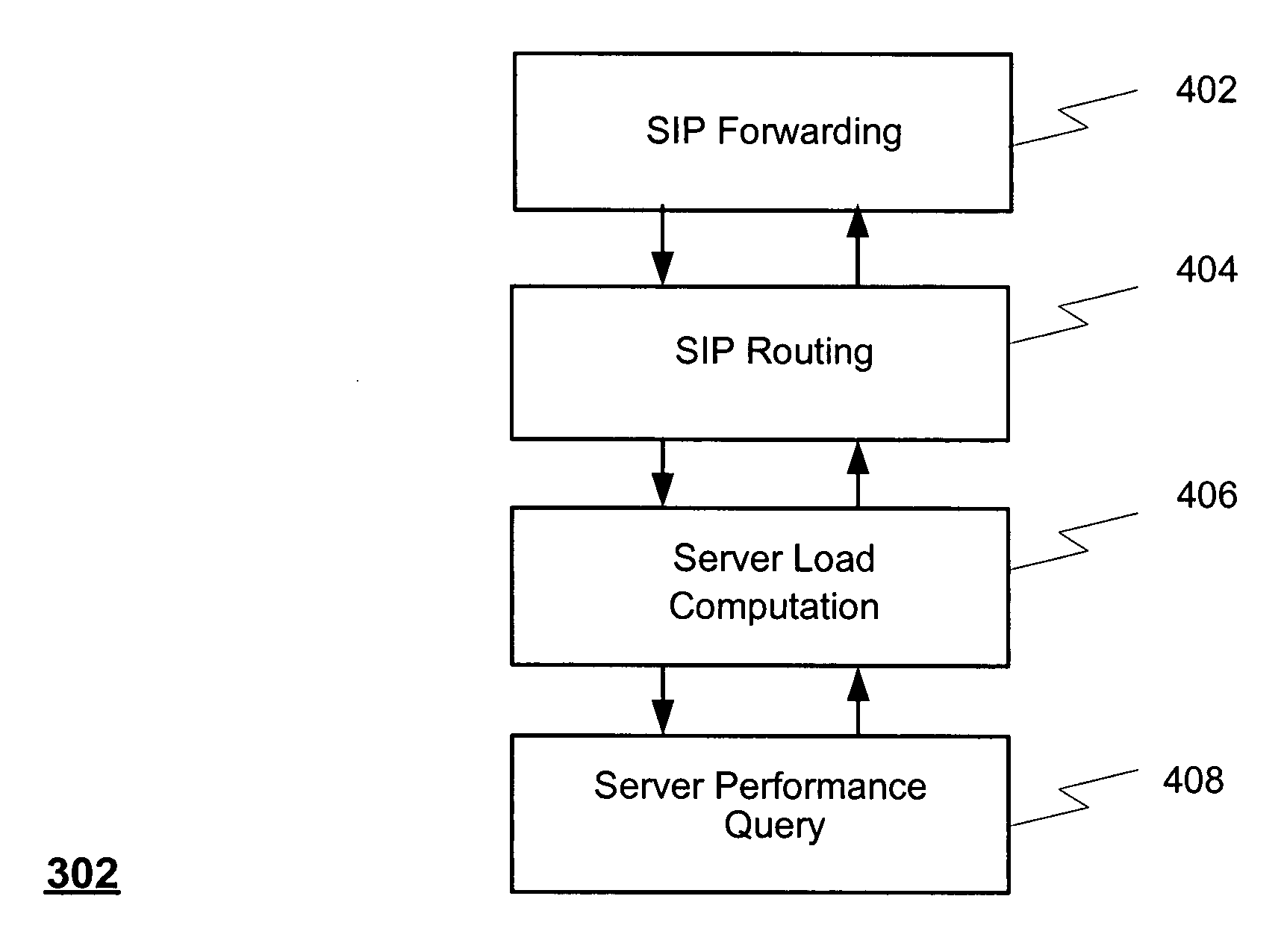

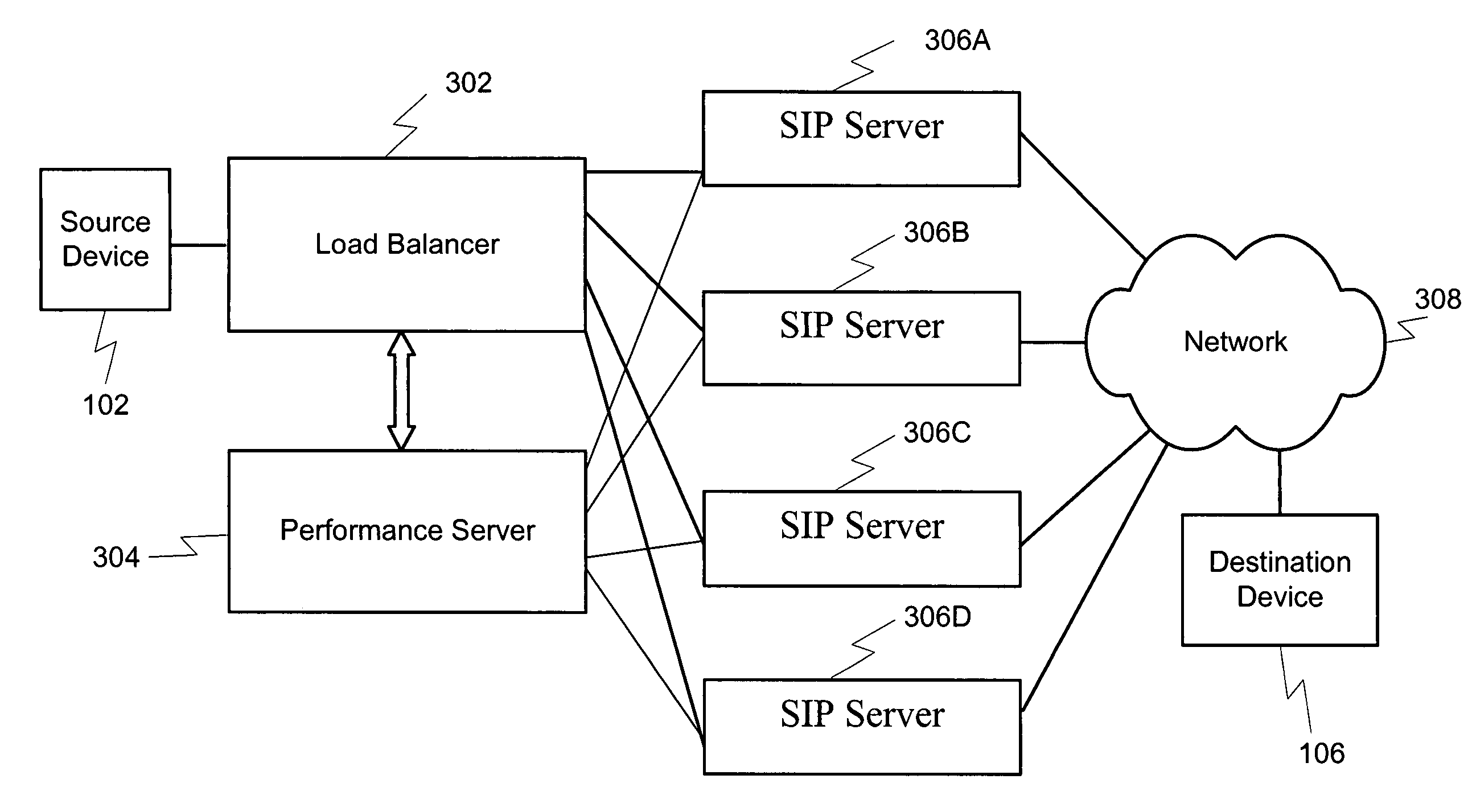

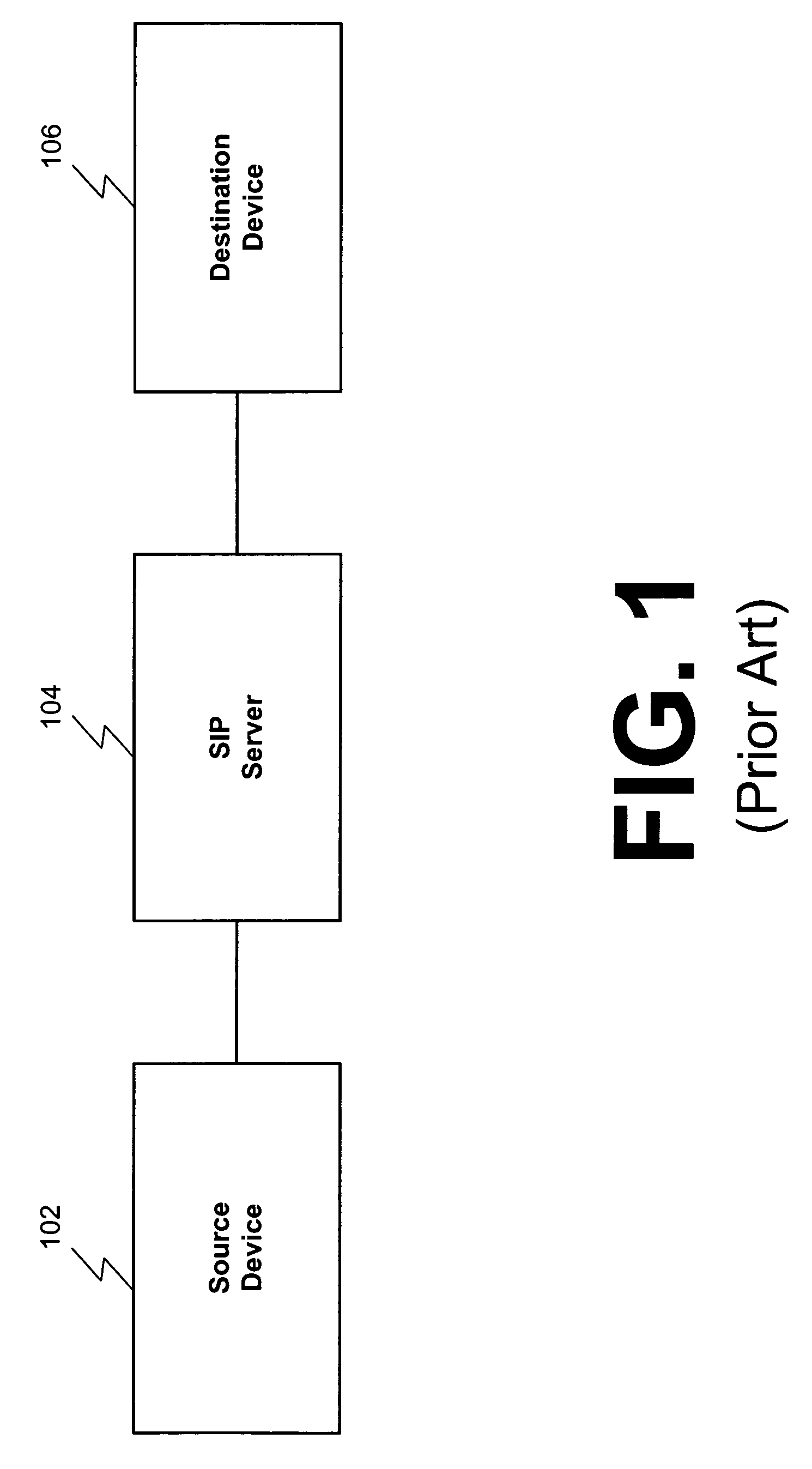

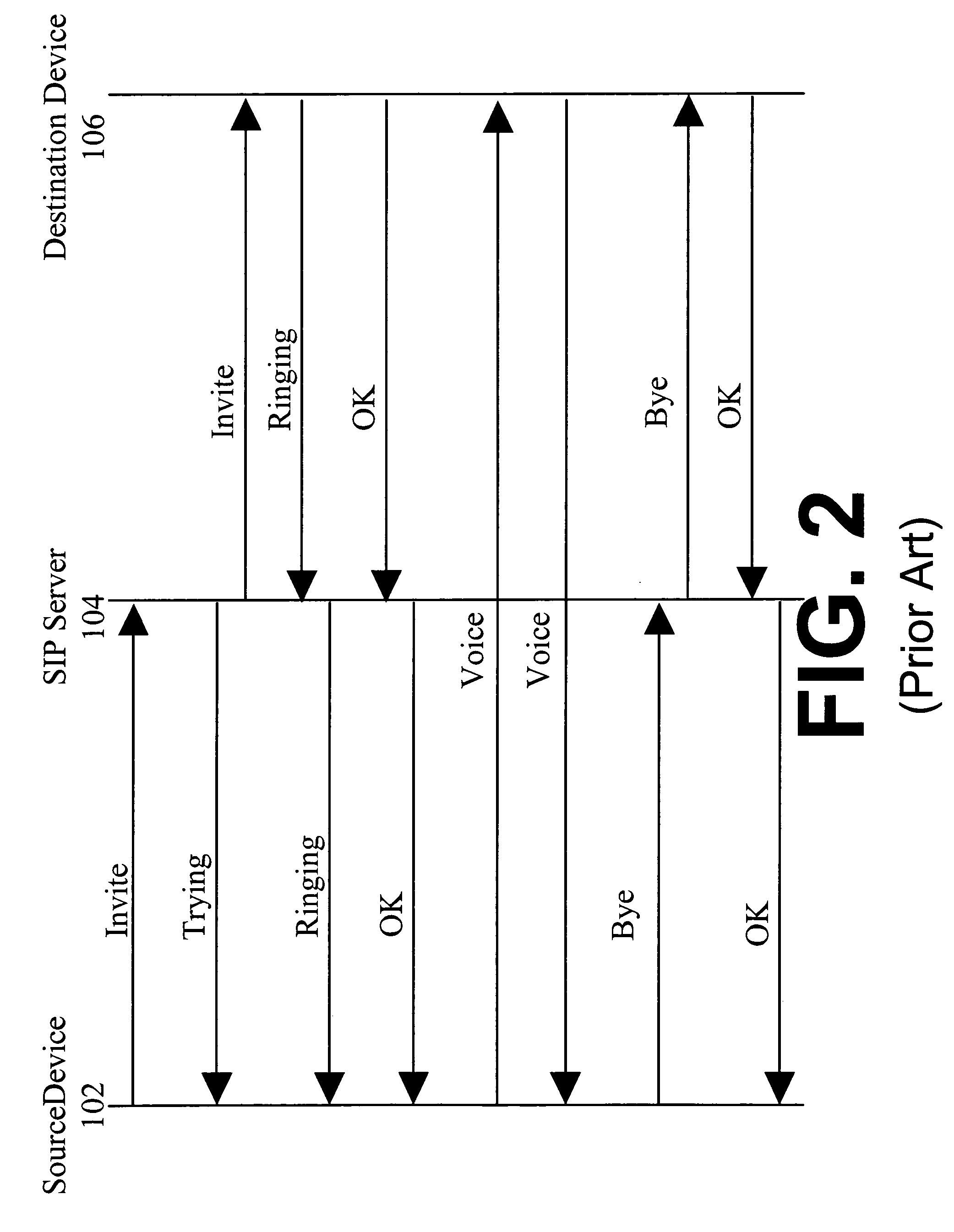

The invention relates to a system and method for load-balancing multiple servers in a communications network. Instead of using round robin or other predetermined scheme, SIP messages are forwarded to one of multiple SIP servers according to a performance score that is calculated from measured performance data. Advantageously, the disclosed system and method decreases signaling latency, improving overall communications speed. Moreover, where performance data indicates that a SIP server has failed, the performance score for the failed SIP server is zero, and the load balancer will not forward SIP messages to the failed SIP server. System uptime is also improved.

Owner:CISCO TECH INC

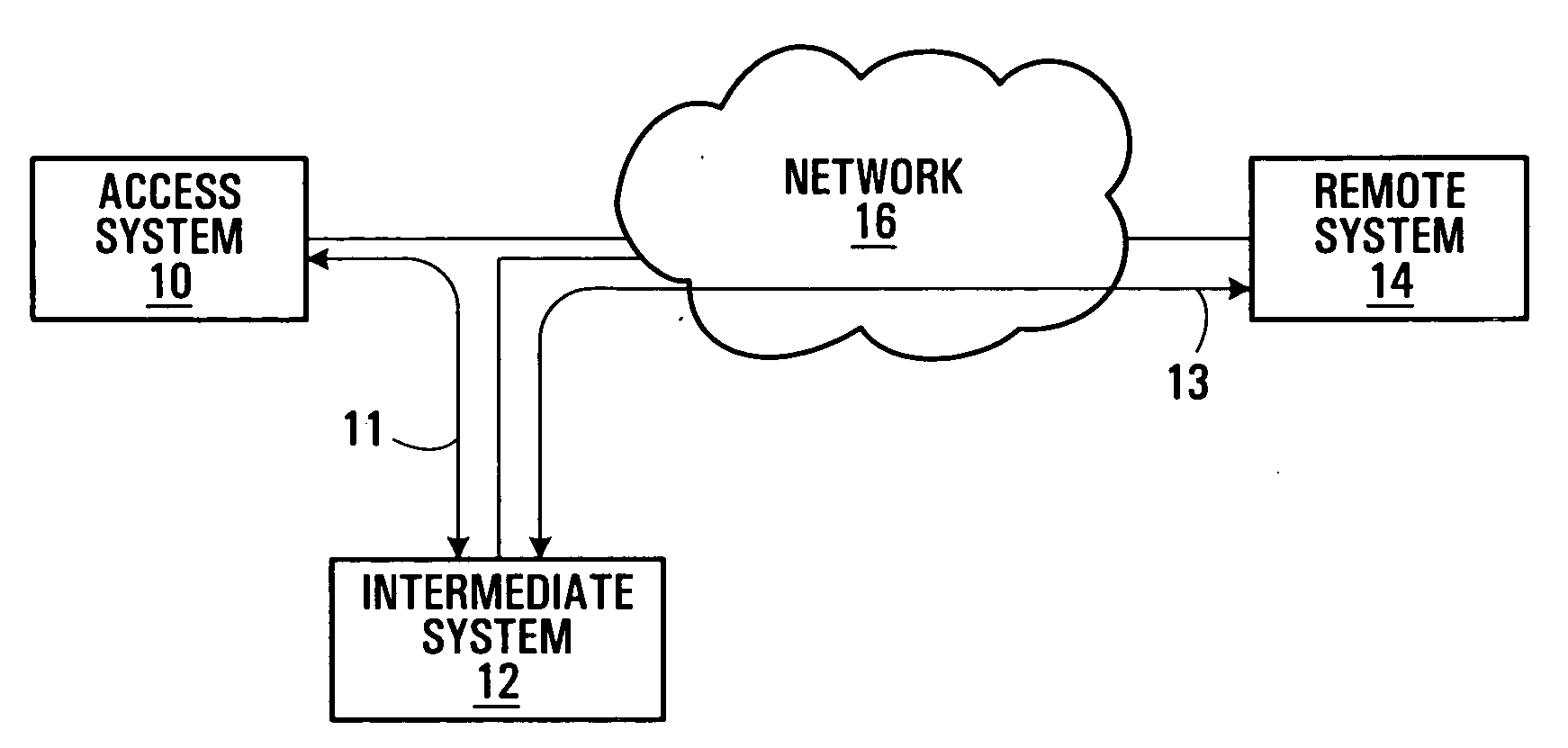

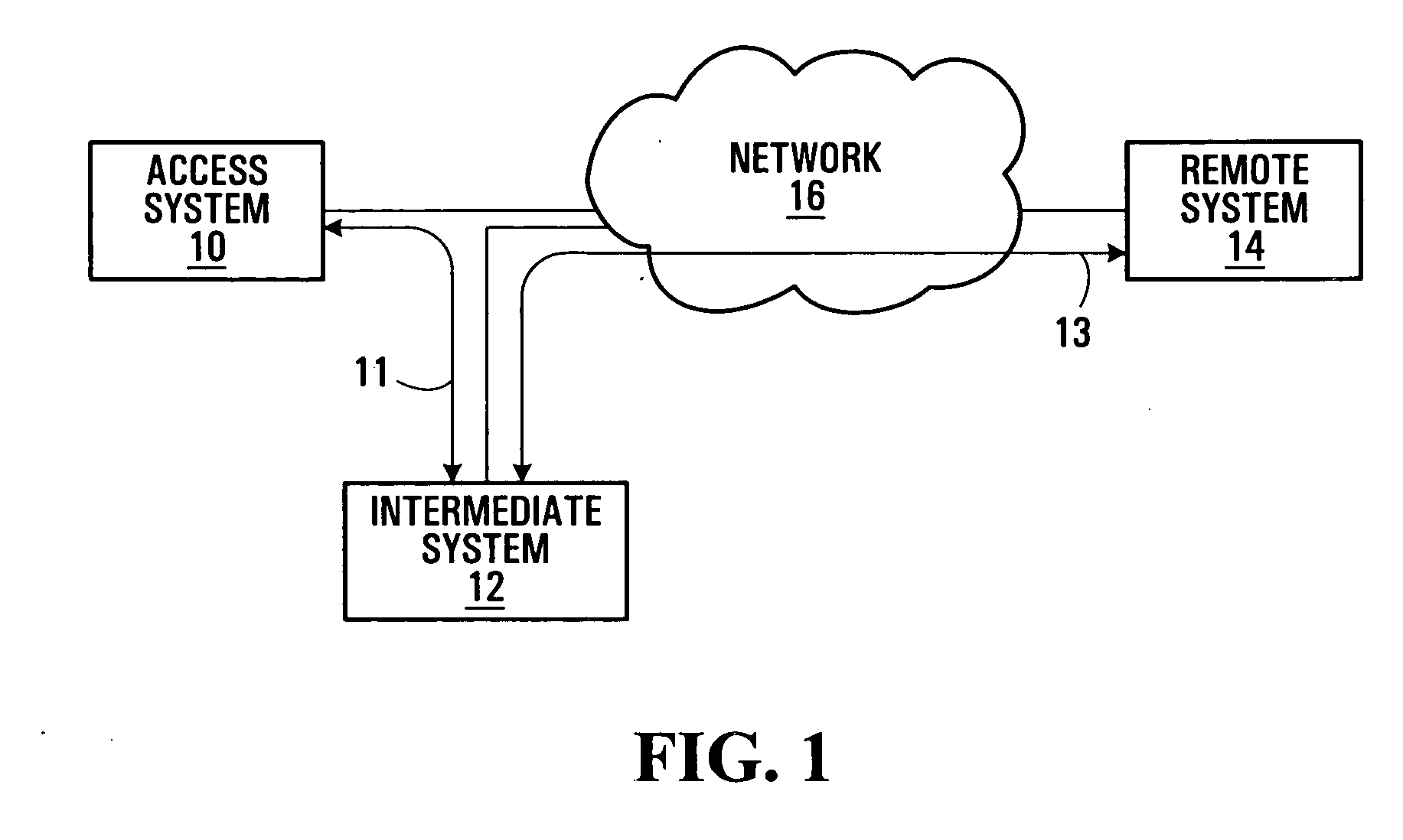

Secure communication methods and systems

InactiveUS20060020787A1Reduce signal delayMultiple digital computer combinationsWireless network protocolsSecure communicationSecurity association

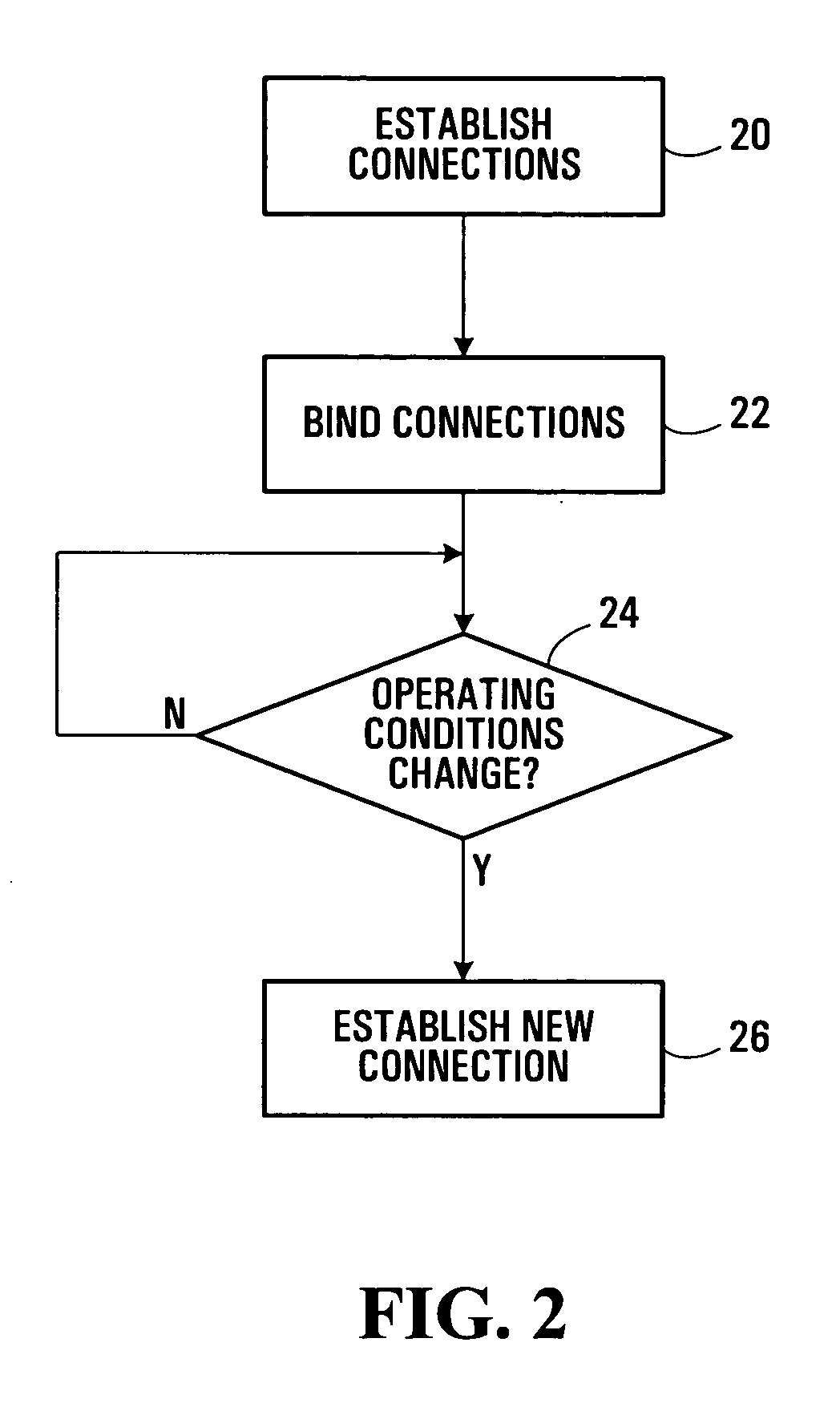

Methods and systems for secure communications are provided. Secure end-to-end connections are established as separate multiple secure connections, illustratively between a first system and an intermediate system and between a second system and an intermediate system. The multiple secure connections may be bound, by binding Internet Protocol Security Protocol (IPSec) Security Associations (SAs) for the multiple connections, for example, to establish the end-to-end connection. In the event of a change in operating conditions which would normally require the entire secure connection to be re-established, only one of the multiple secure connections which form the end-to-end connection is re-established. Separation of end-to-end connections in this manner may reduce processing resource requirements and latency normally associated with re-establishing secure connections.

Owner:RPX CORP

System and method for load balancing a communications network

InactiveUS7805517B2Reduce signal delayFast communication speedMultiple digital computer combinationsTransmissionLoad SheddingRunning time

Owner:CISCO TECH INC

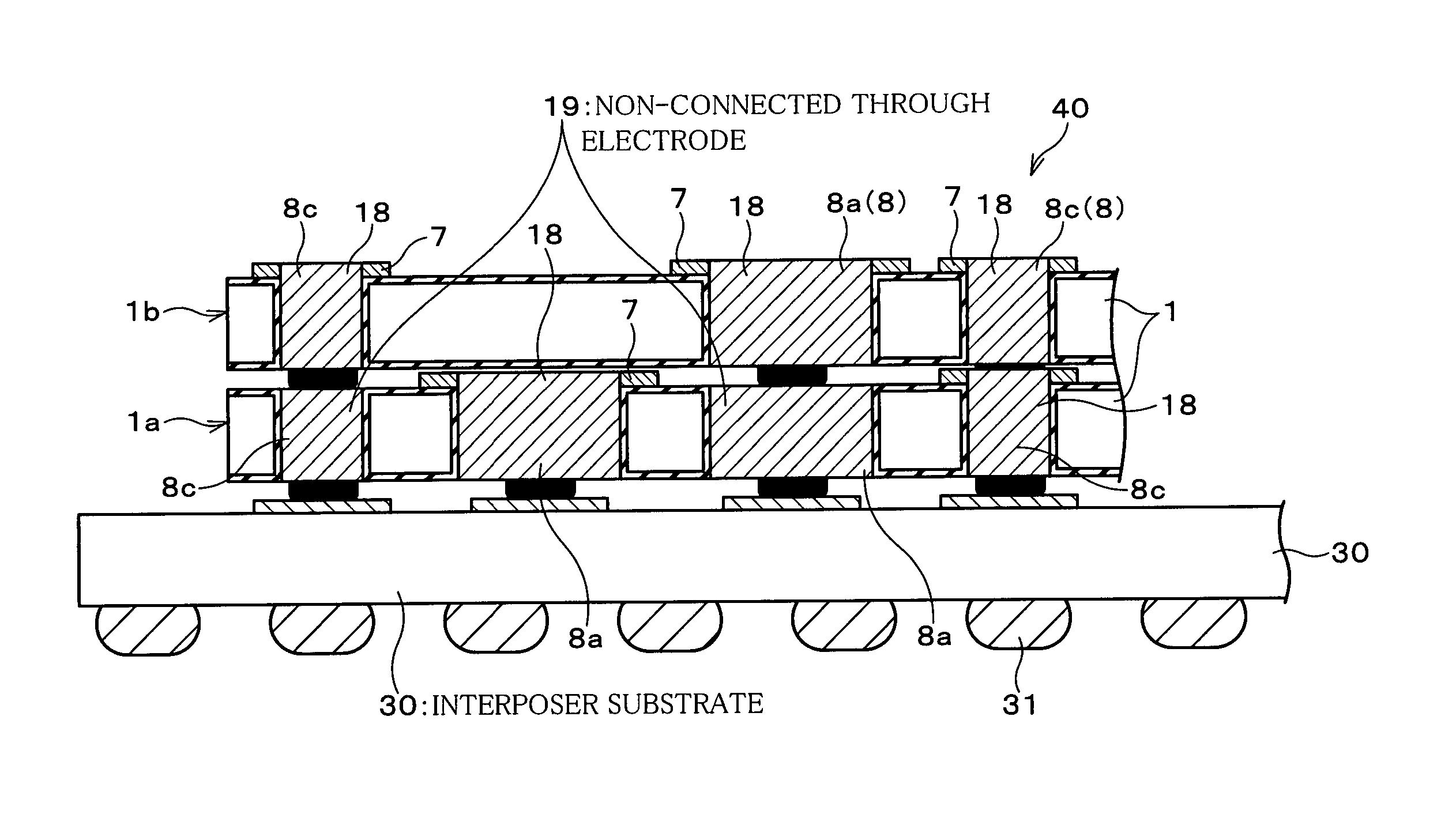

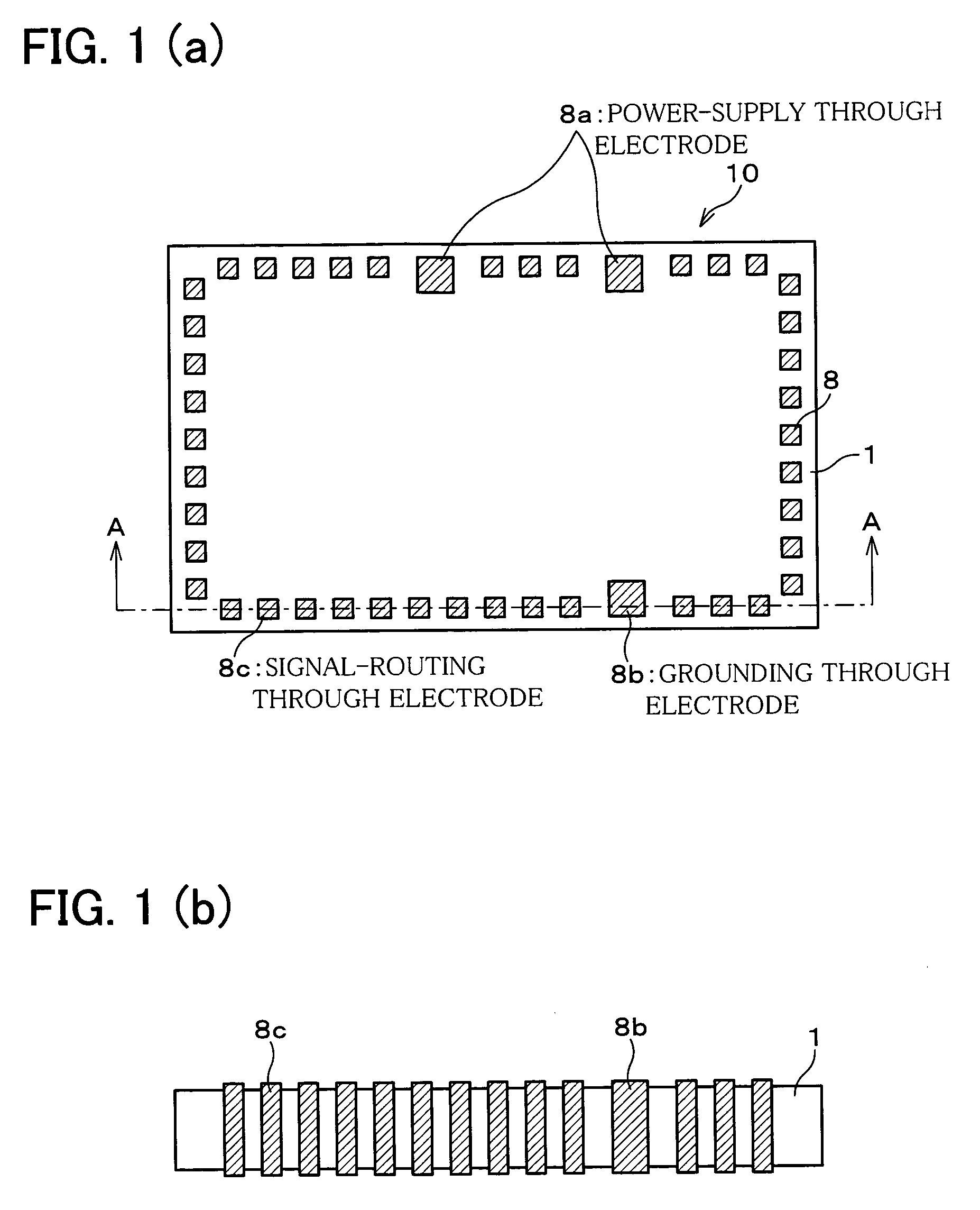

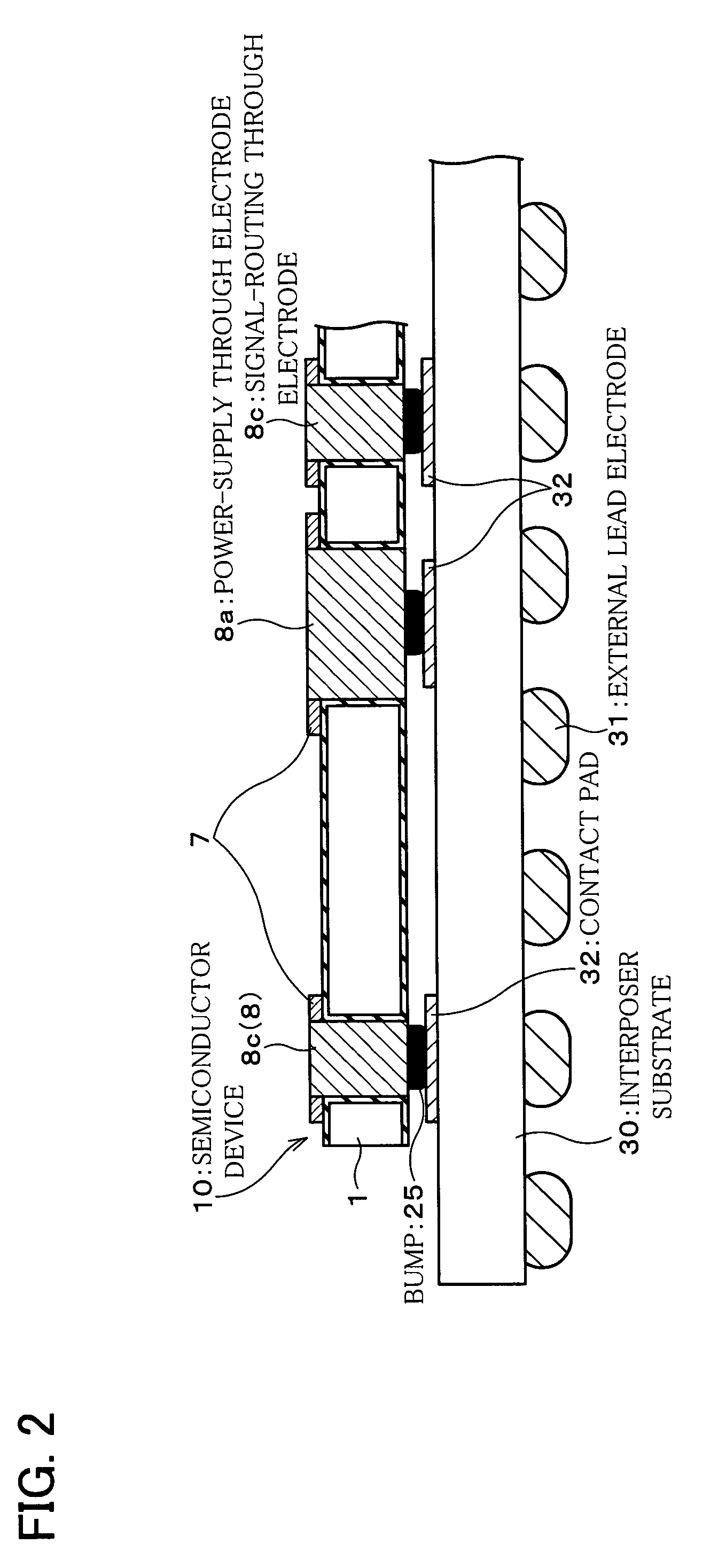

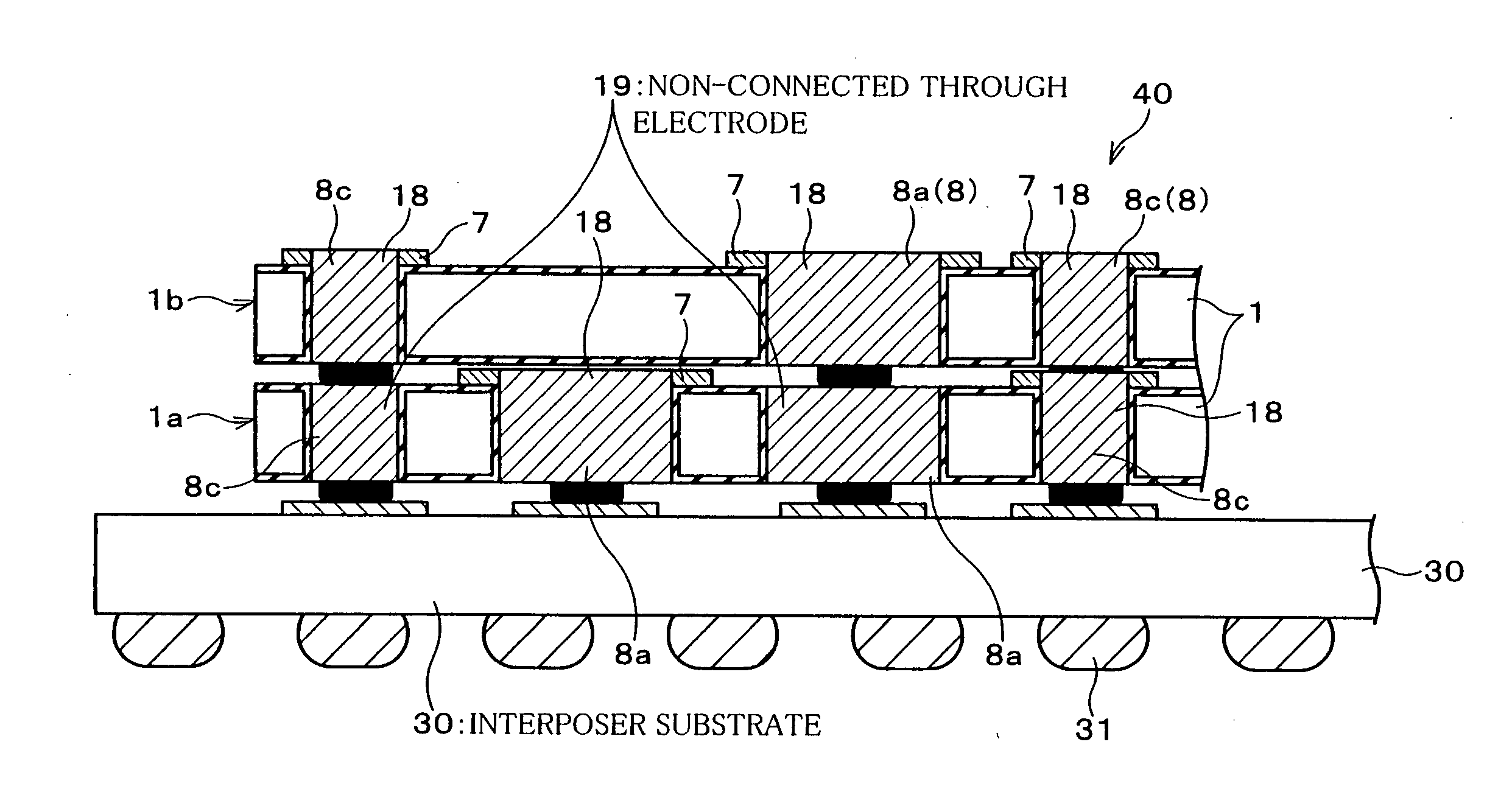

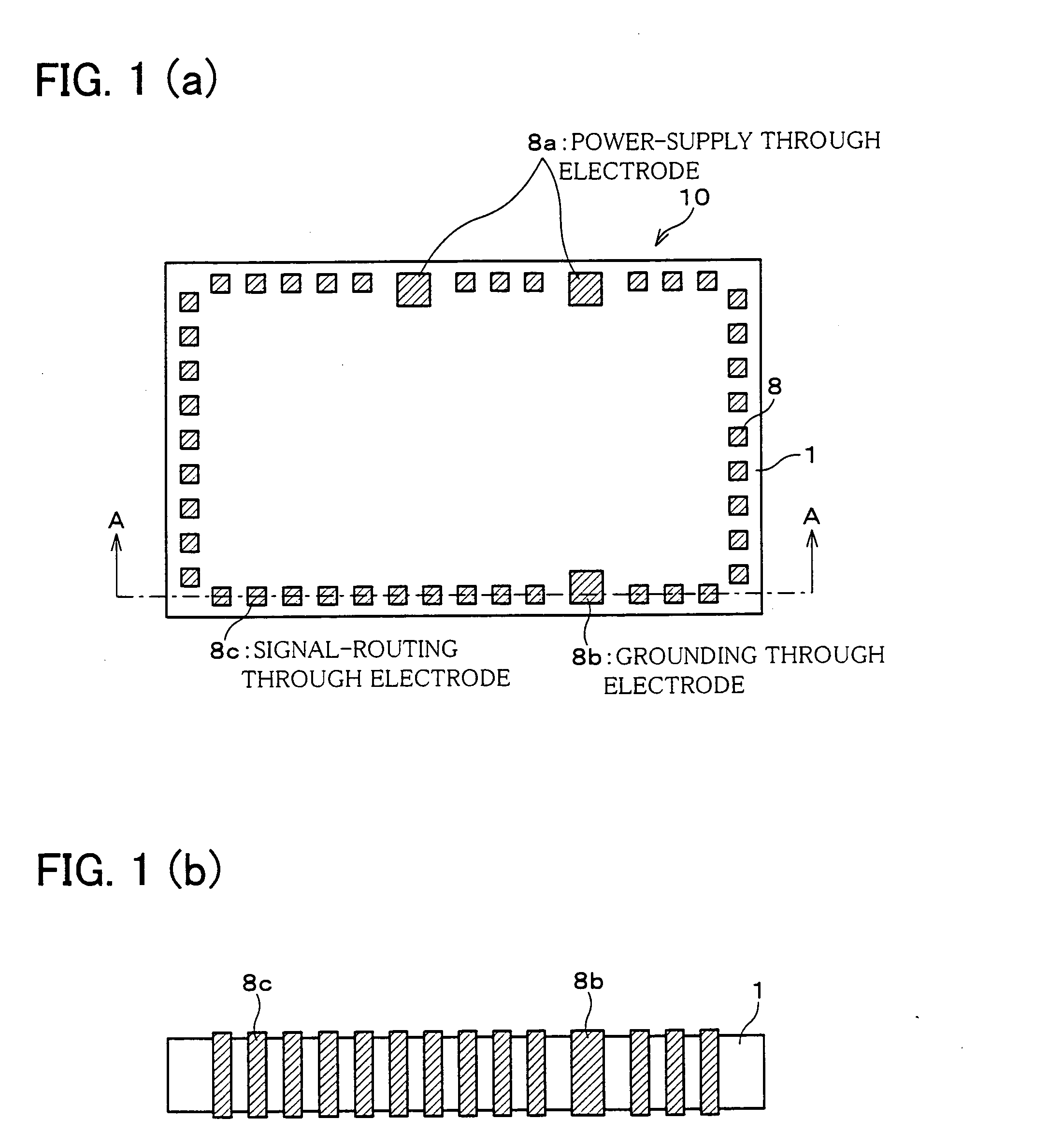

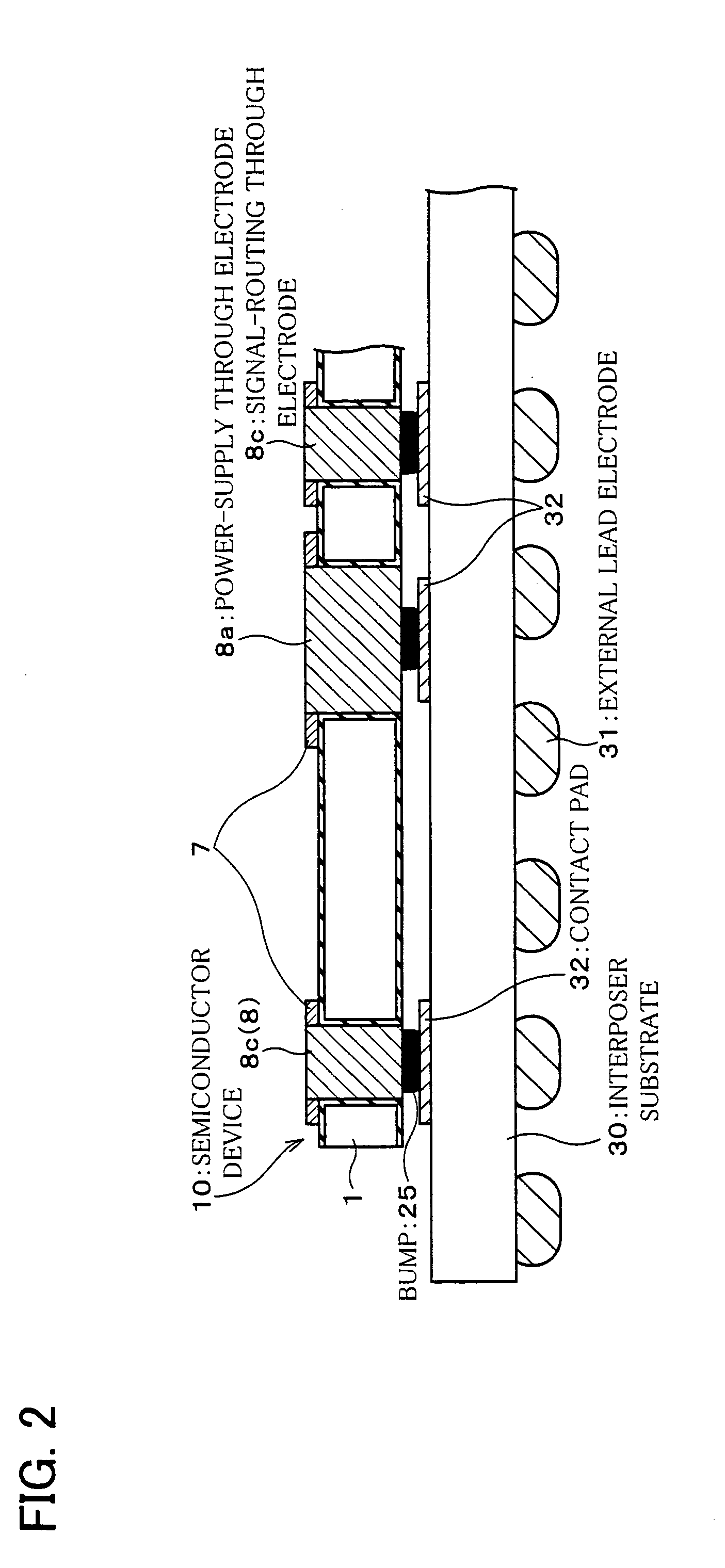

Semiconductor device and chip-stack semiconductor device

ActiveUS7115972B2Delayed deteriorationReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceSignal routing

A semiconductor device has multiple power-supply through electrodes, grounding through electrodes, and signal-routing through electrodes made through a semiconductor chip. The power-supply through electrodes, the grounding through electrodes, and the signal-routing through electrodes differ mutually in cross-sectional area. Hence, a semiconductor device and a chip-stack semiconductor device are provided which are capable of preventing the electrodes' resistance from developing excessive voltage drop, heat, delay, and loss, and also from varying from one electrode to the other.

Owner:SAMSUNG ELECTRONICS CO LTD

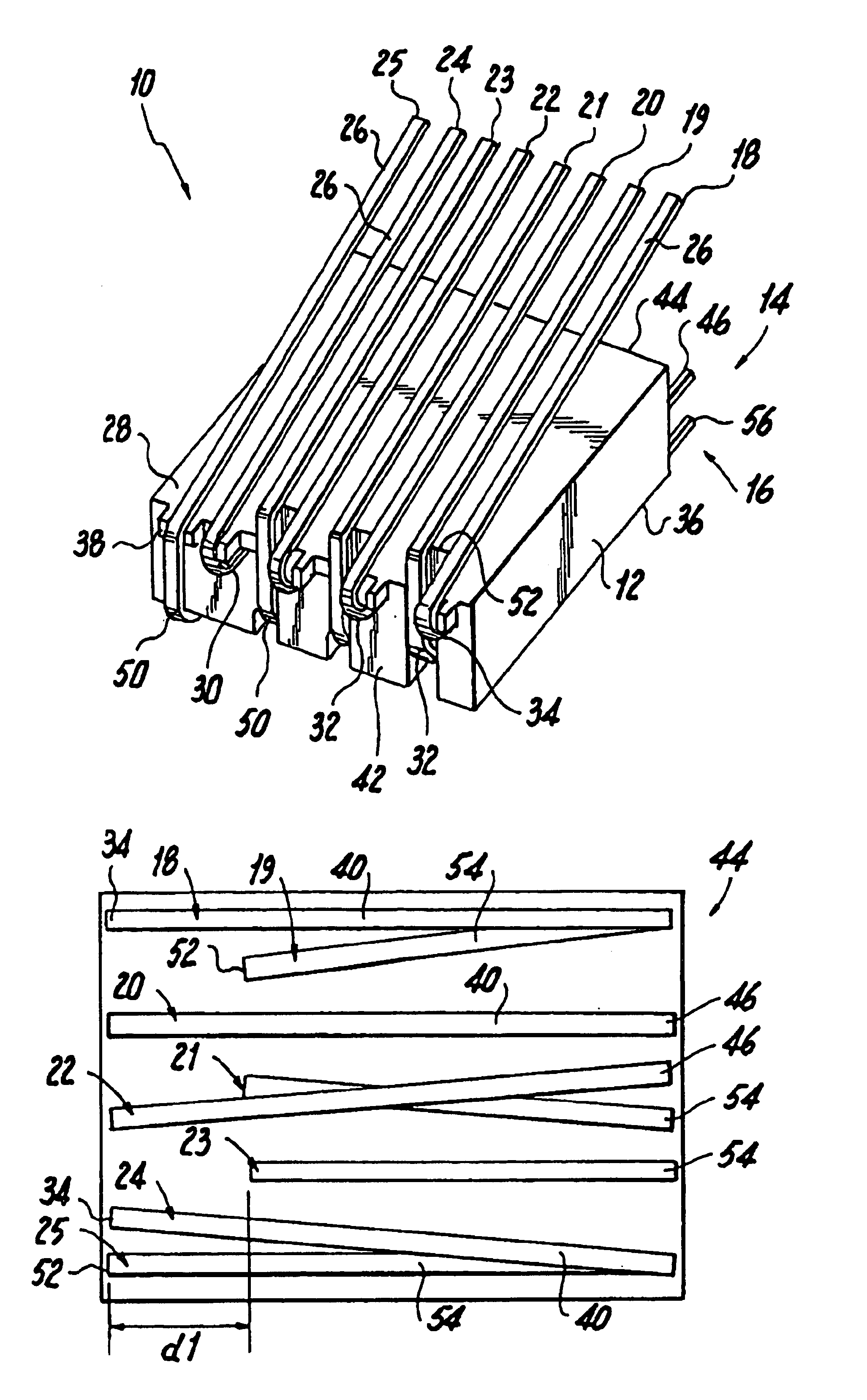

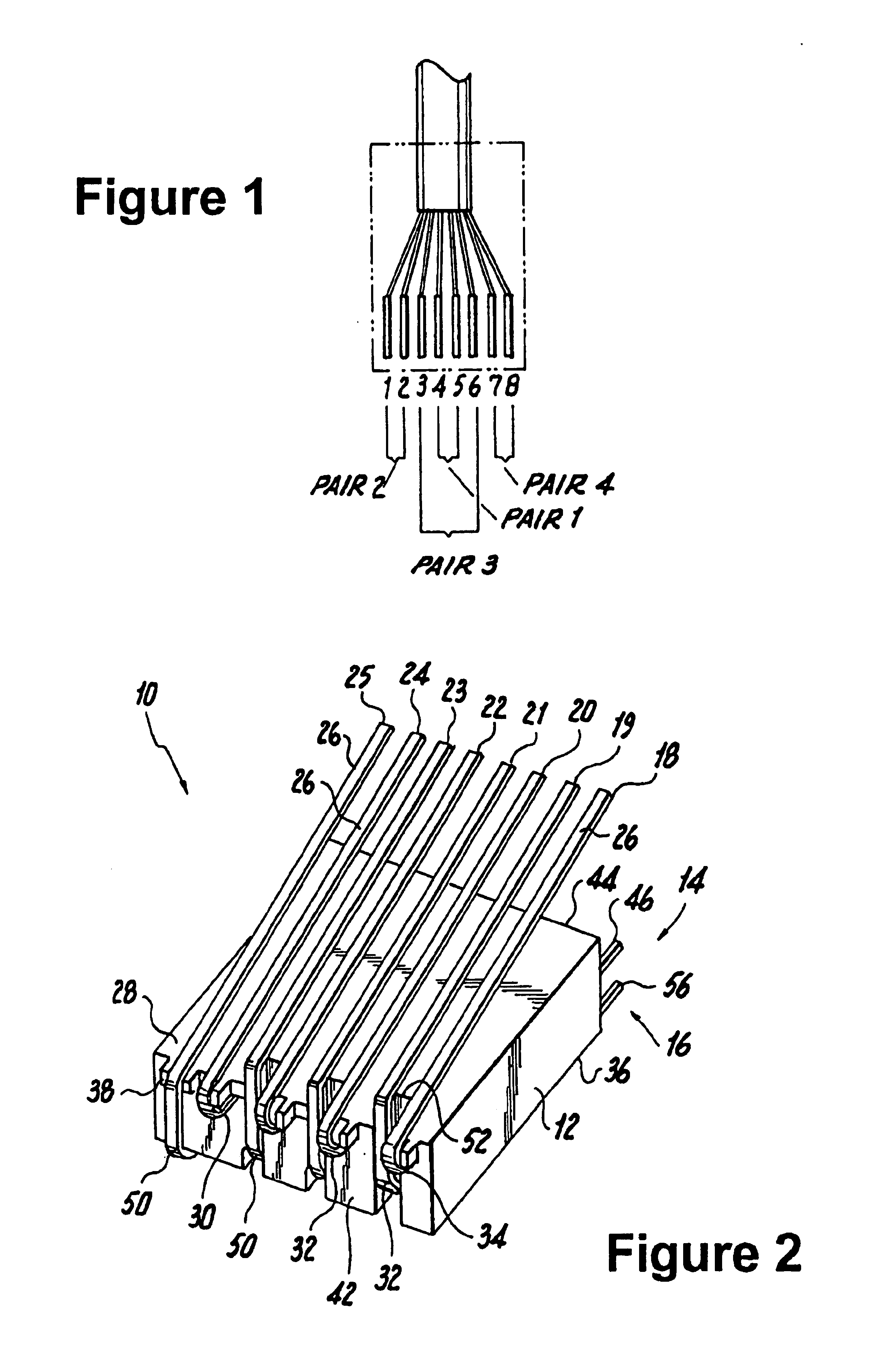

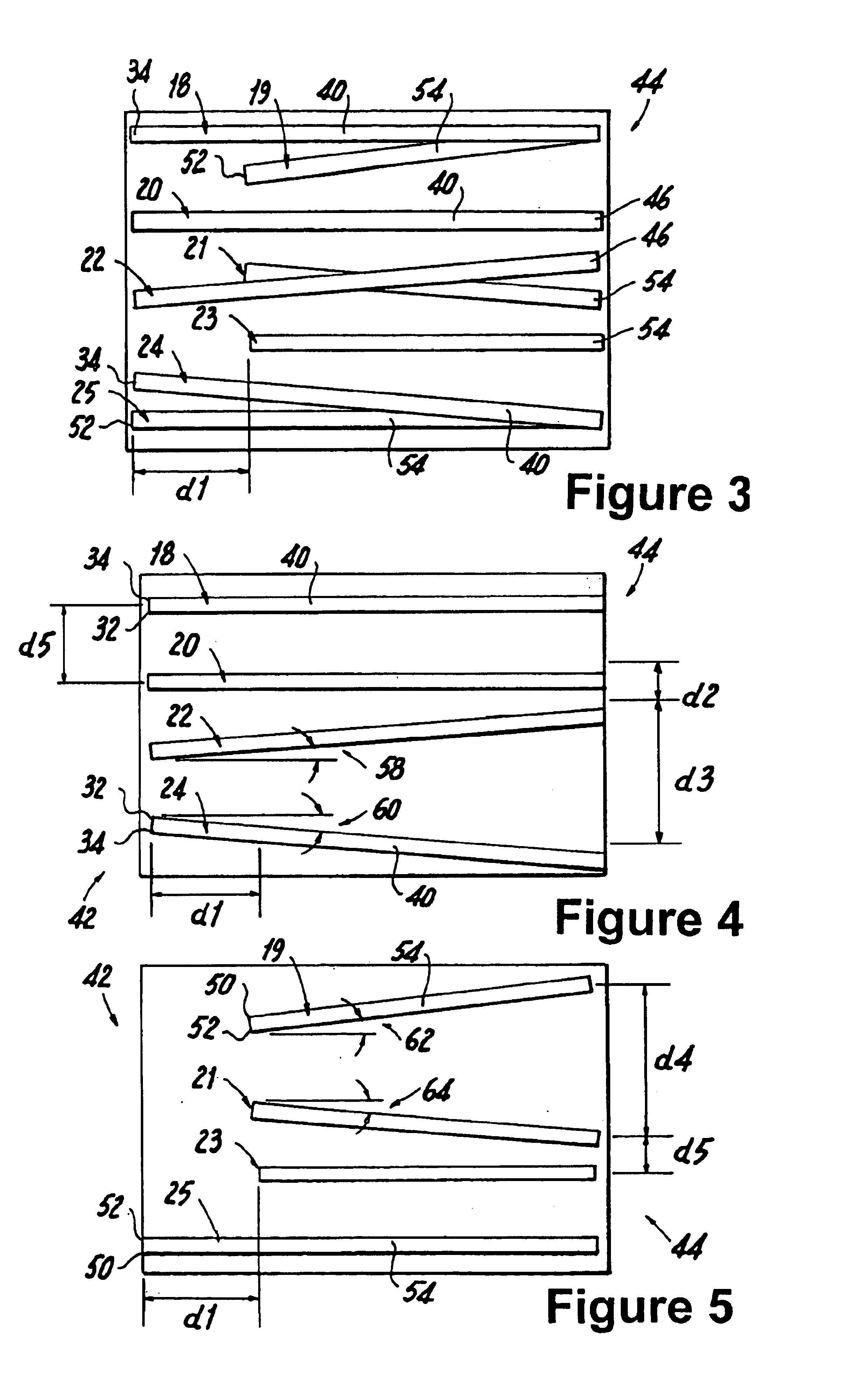

Low noise communication modular connector insert

InactiveUS6802743B2Reduce signal delayEasy to controlIncorrect coupling preventionTwo-part coupling devicesLow noiseElectricity

The present disclosure is related to a modular plug housing insert device that makes electrical contact to a telecommunication plug to complete an interface media connection. The positional relationship of the conductors in the modular plug housing insert device are arranged to form a capacitance, such that the Near-end Crosstalk (NEXT) and Far End Crosstalk (FEXT) are reduced without compromising impedance.

Owner:LEGRAND DPC LLC

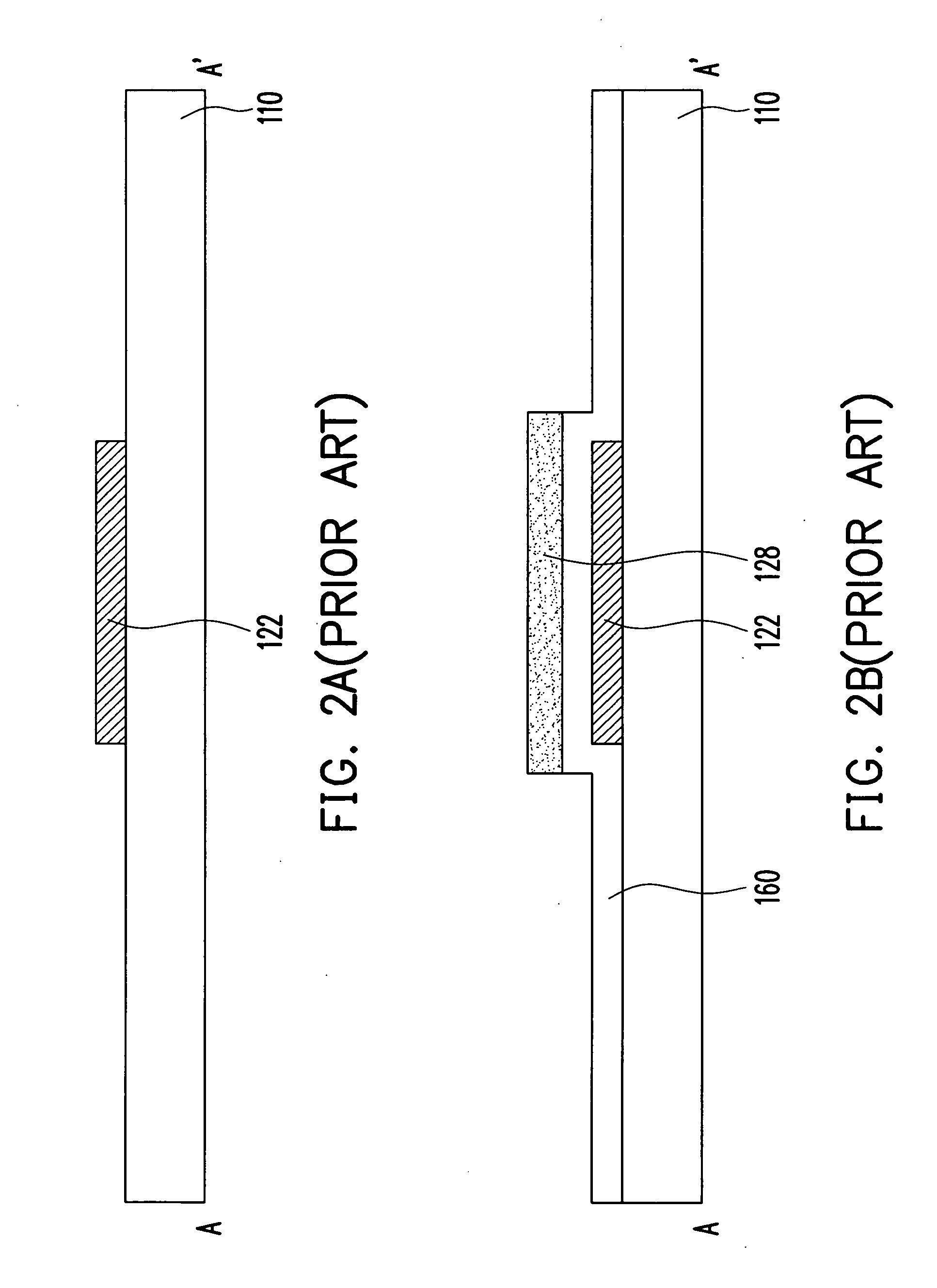

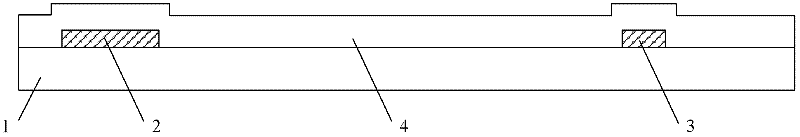

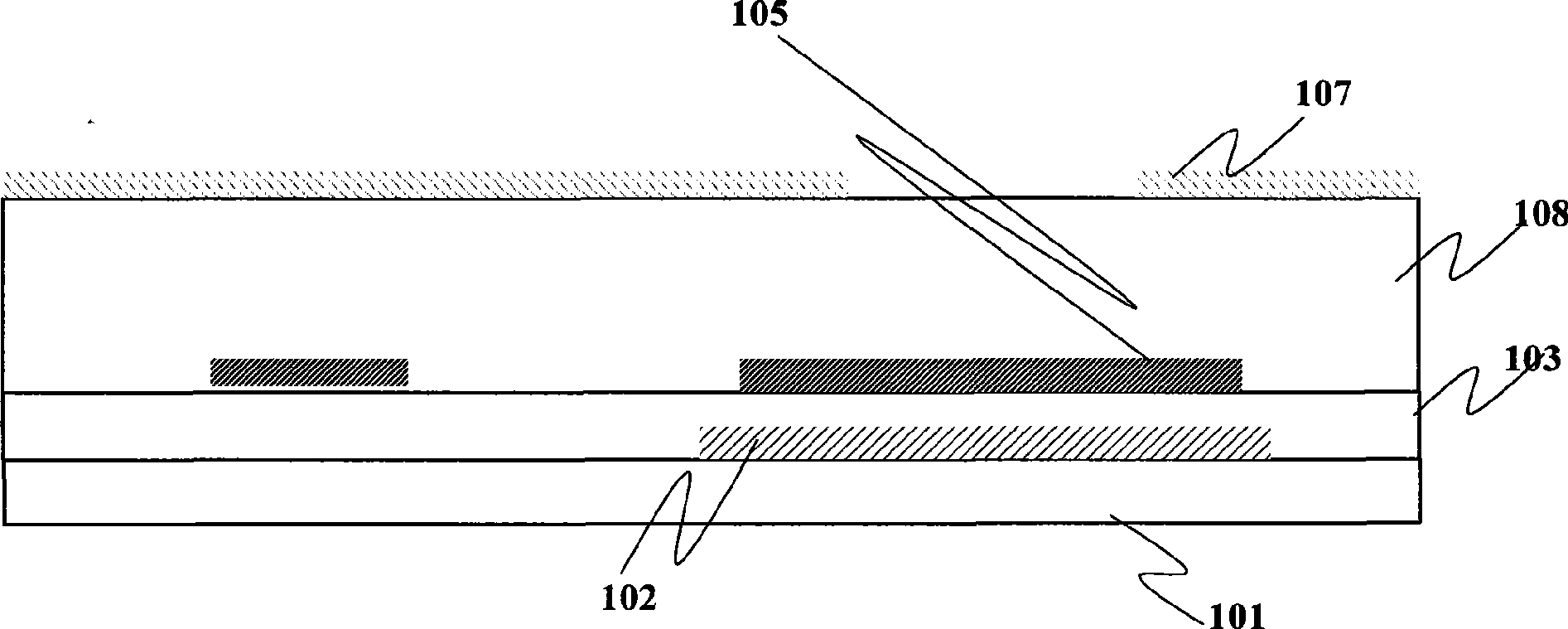

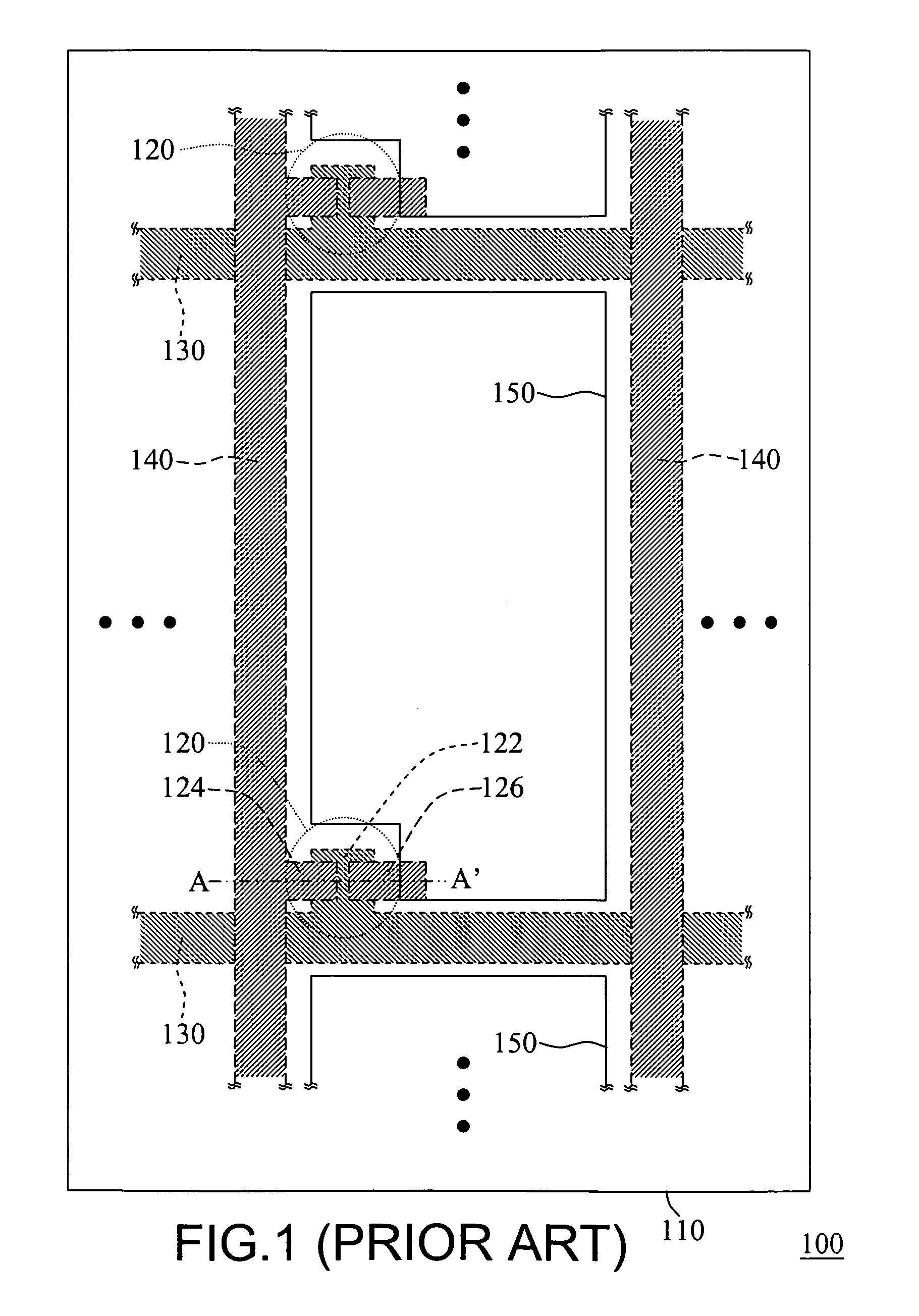

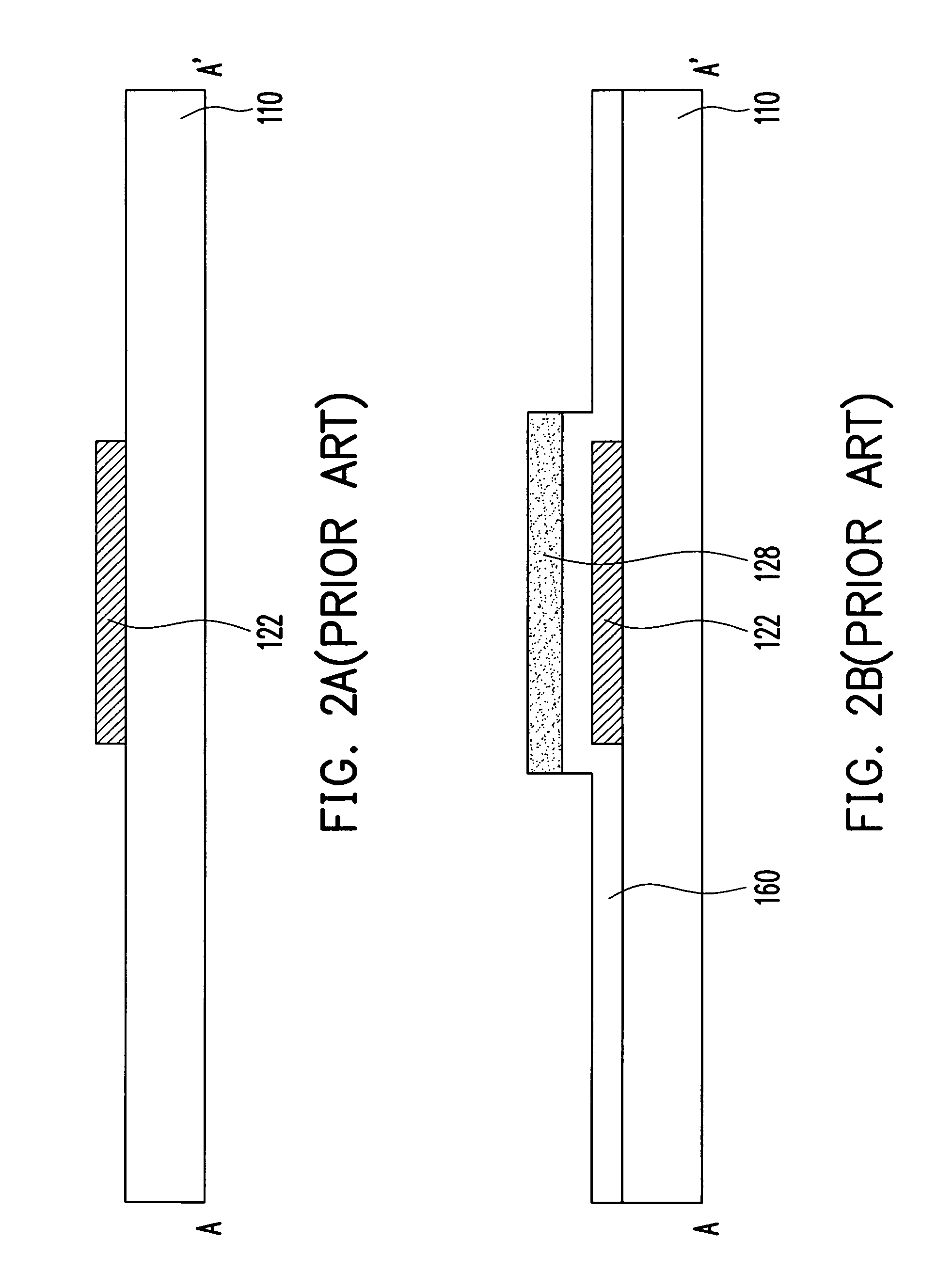

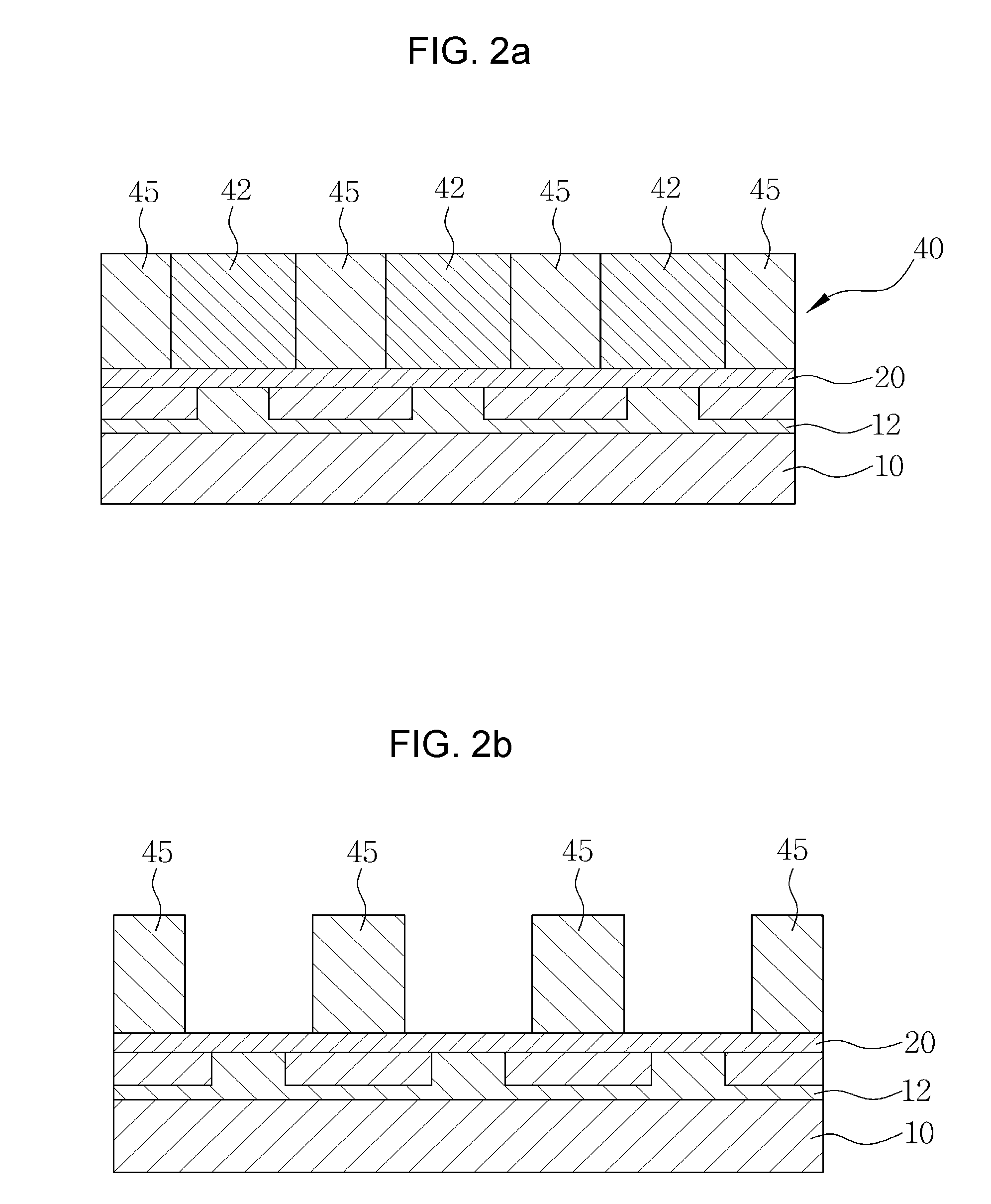

Method for fabricating pixel array substrate

A method for fabricating a pixel array substrate is provided. The method includes: forming a plurality of gate electrodes, a plurality of scan lines, a plurality of data line patterns and a plurality of pixel electrode patterns on a substrate; then forming a channel over each of the gate electrodes and a plurality of contact window openings for exposing the data line patterns; then forming a plurality of contact windows electrically connected with the data line patterns; and then forming a plurality of contacting portions which are electrically connected with the contact windows, a plurality of source electrodes which are electrically connected with the data line patterns, and a plurality of drain electrodes which are electrically connected with the pixel electrodes. The data line patterns at each column are electrically connecting with each other via the contacting portions and the contact windows so as to form a data line.

Owner:AU OPTRONICS CORP

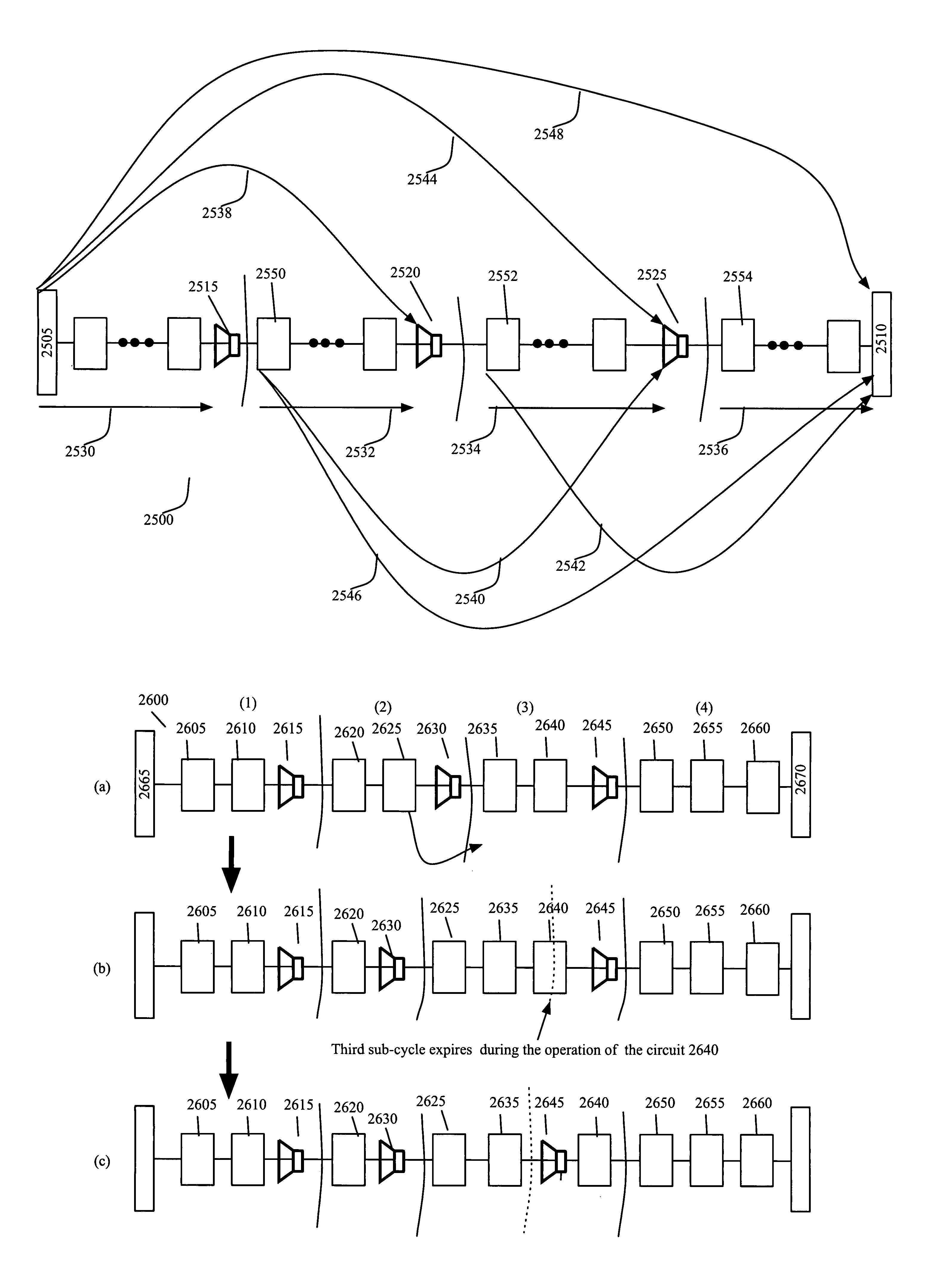

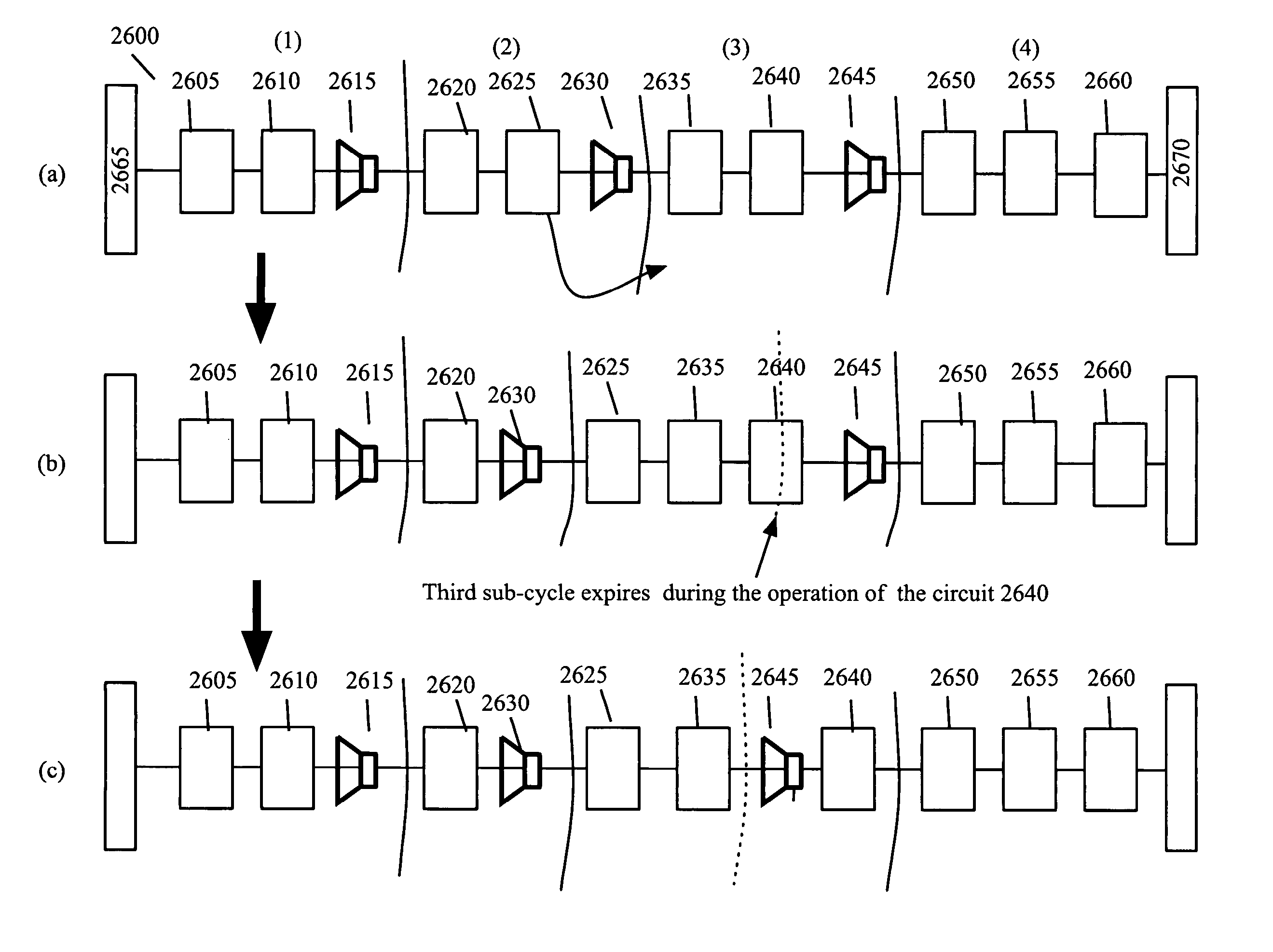

Operational time extension

InactiveUS7236009B1Reduce signal delaySolid-state devicesCAD circuit designIntegrated circuitEngineering

Some embodiments provide a reconfigurable integrated circuit (“IC”). This IC has several reconfigurable circuits, each having several configurations for several configuration cycles. The reconfigurable circuits include several time-extending reconfigurable circuits. During the operation of the IC, each particular time-extending reconfigurable circuit maintains at least one of its configurations over at least two contiguous cycles, in order to allow a signal to propagate through a signal path, which contains the particular time-extending circuit, within a desired amount of time.

Owner:ALTERA CORP

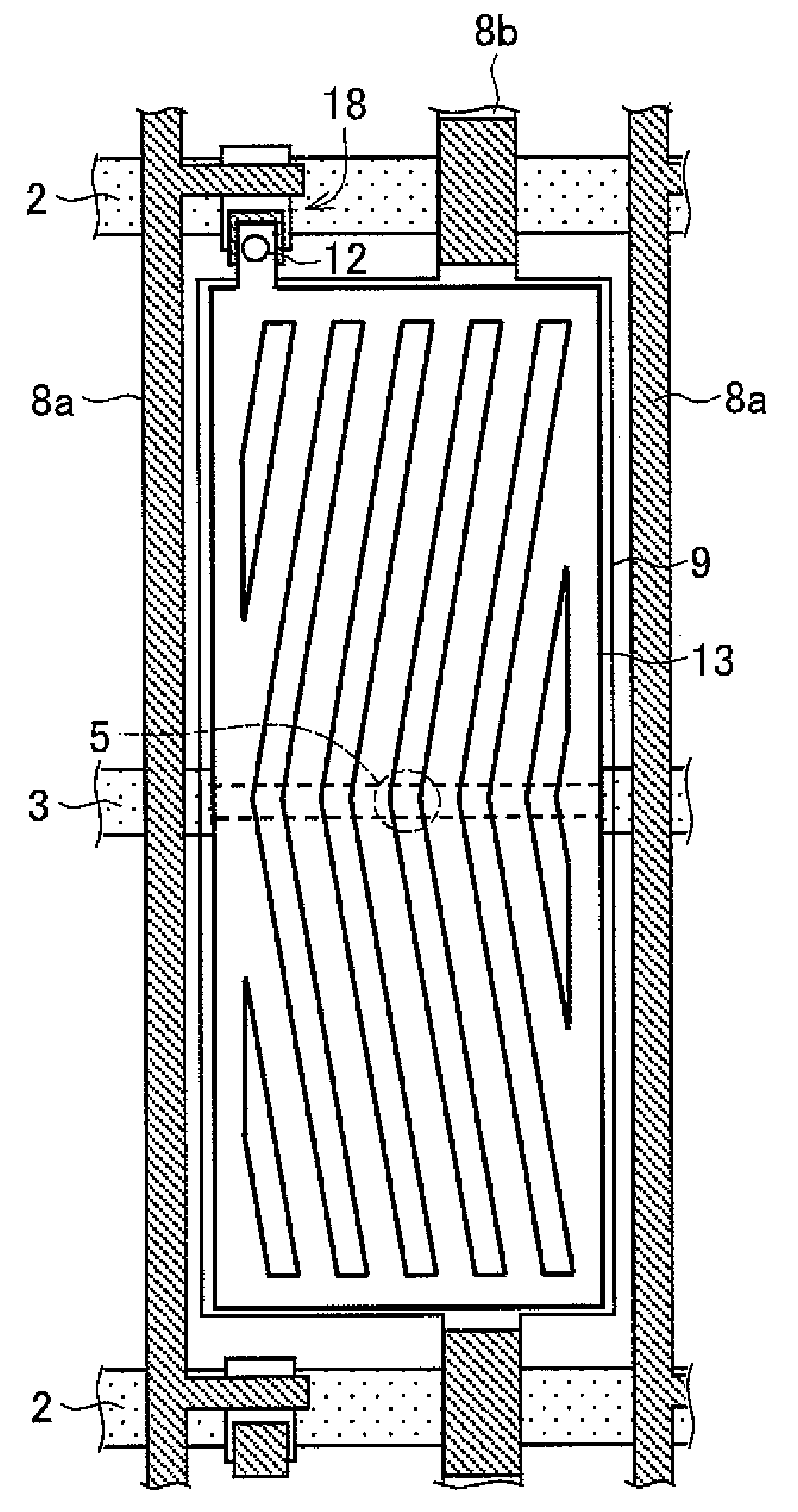

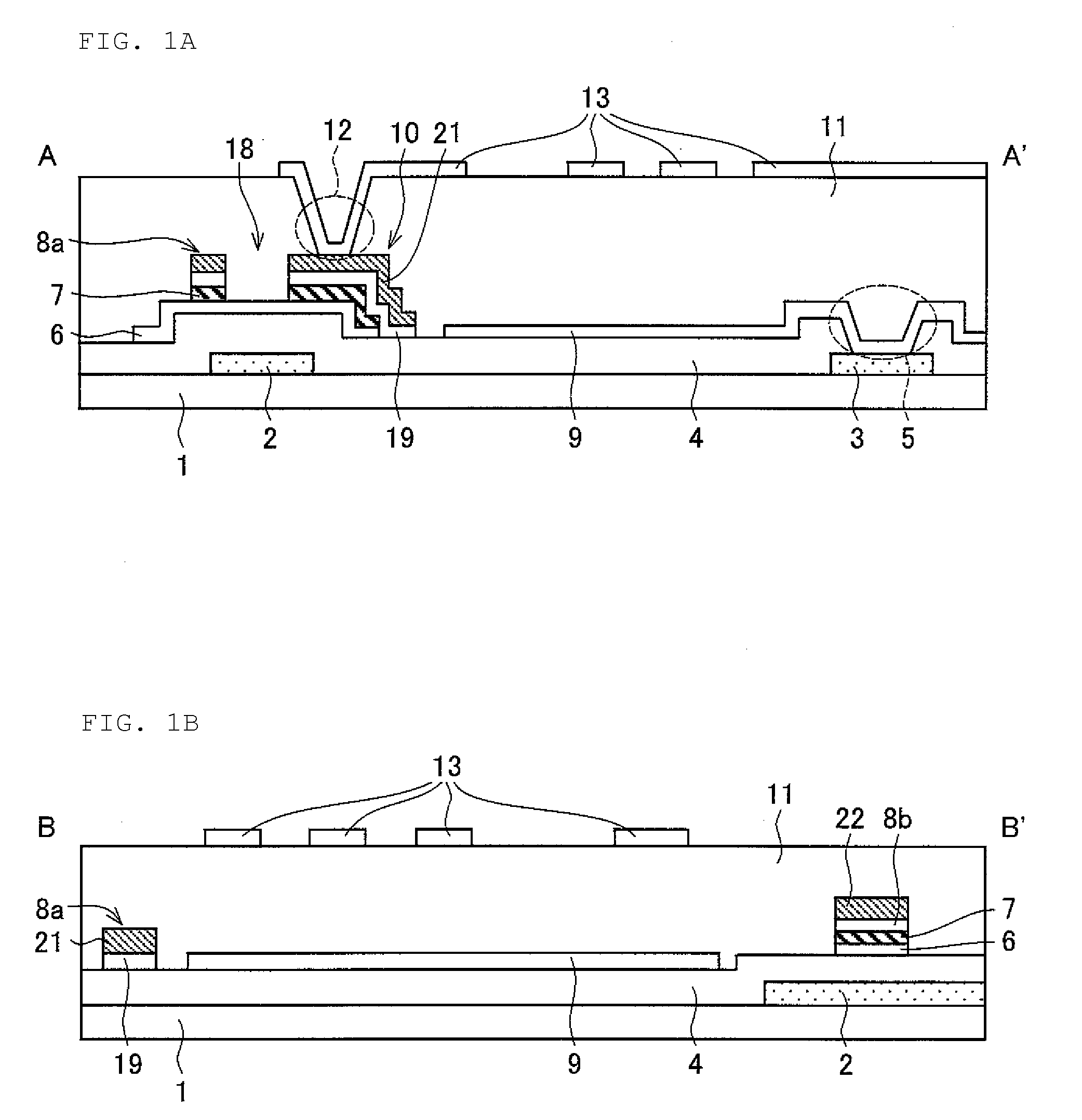

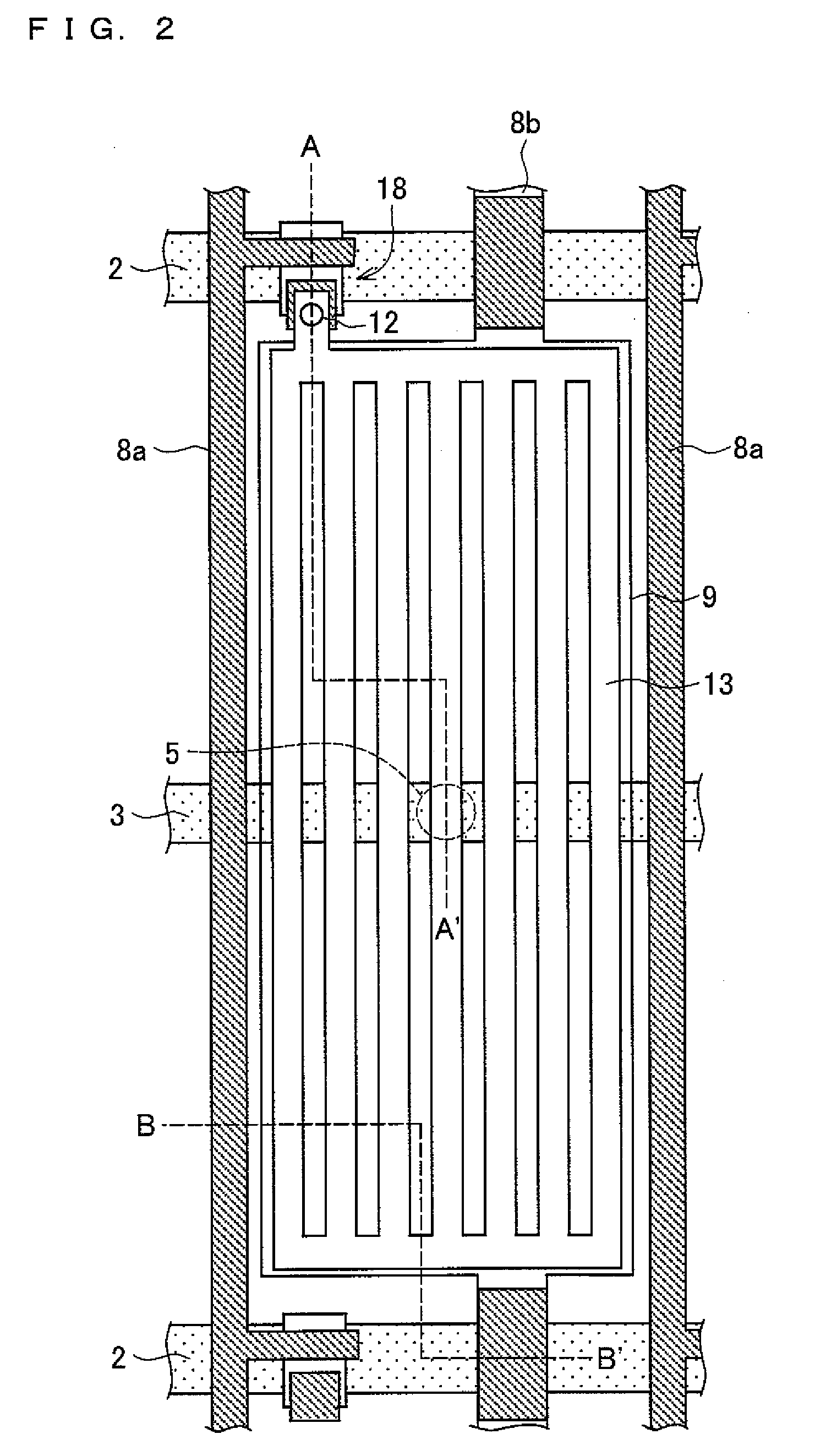

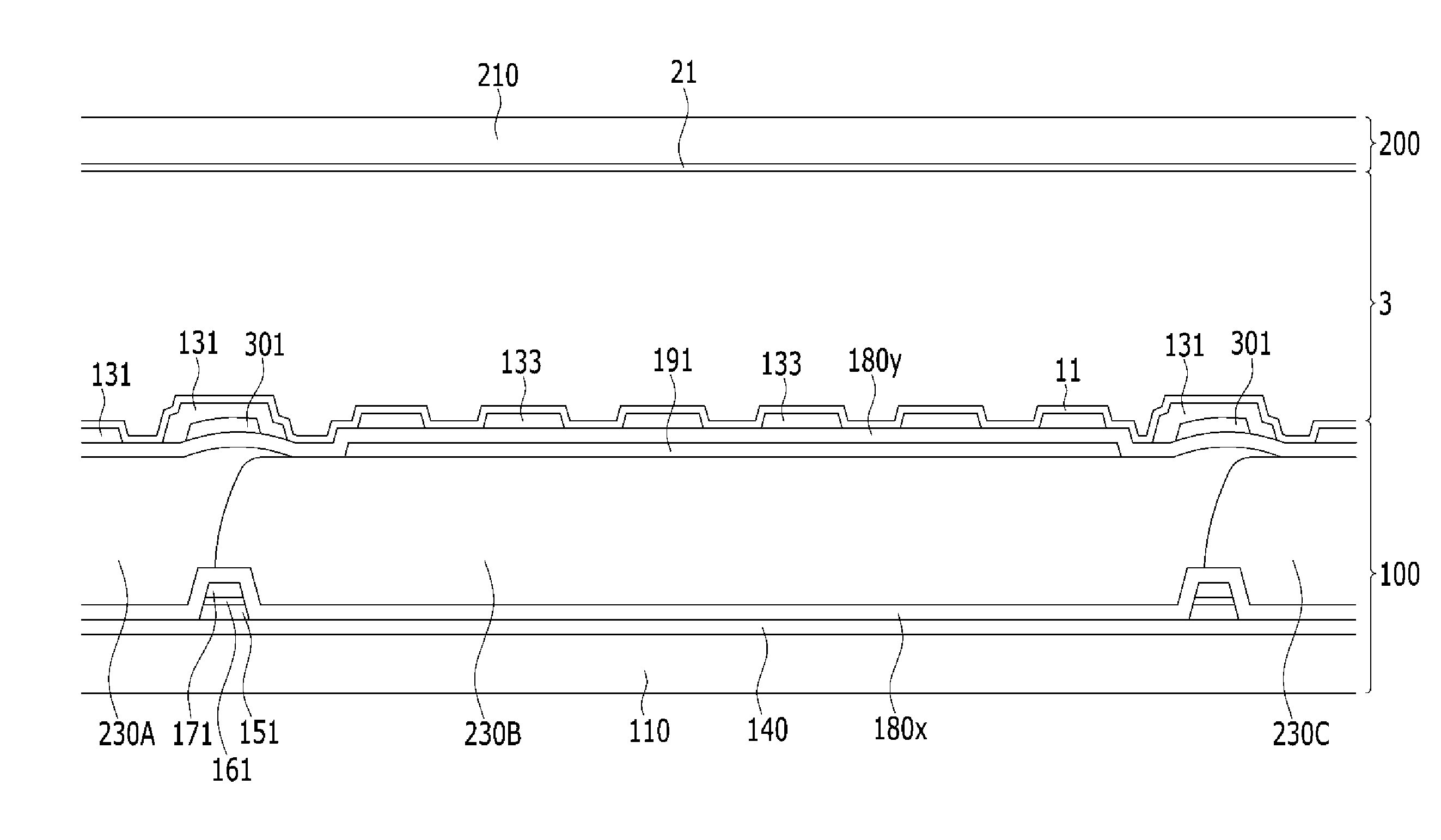

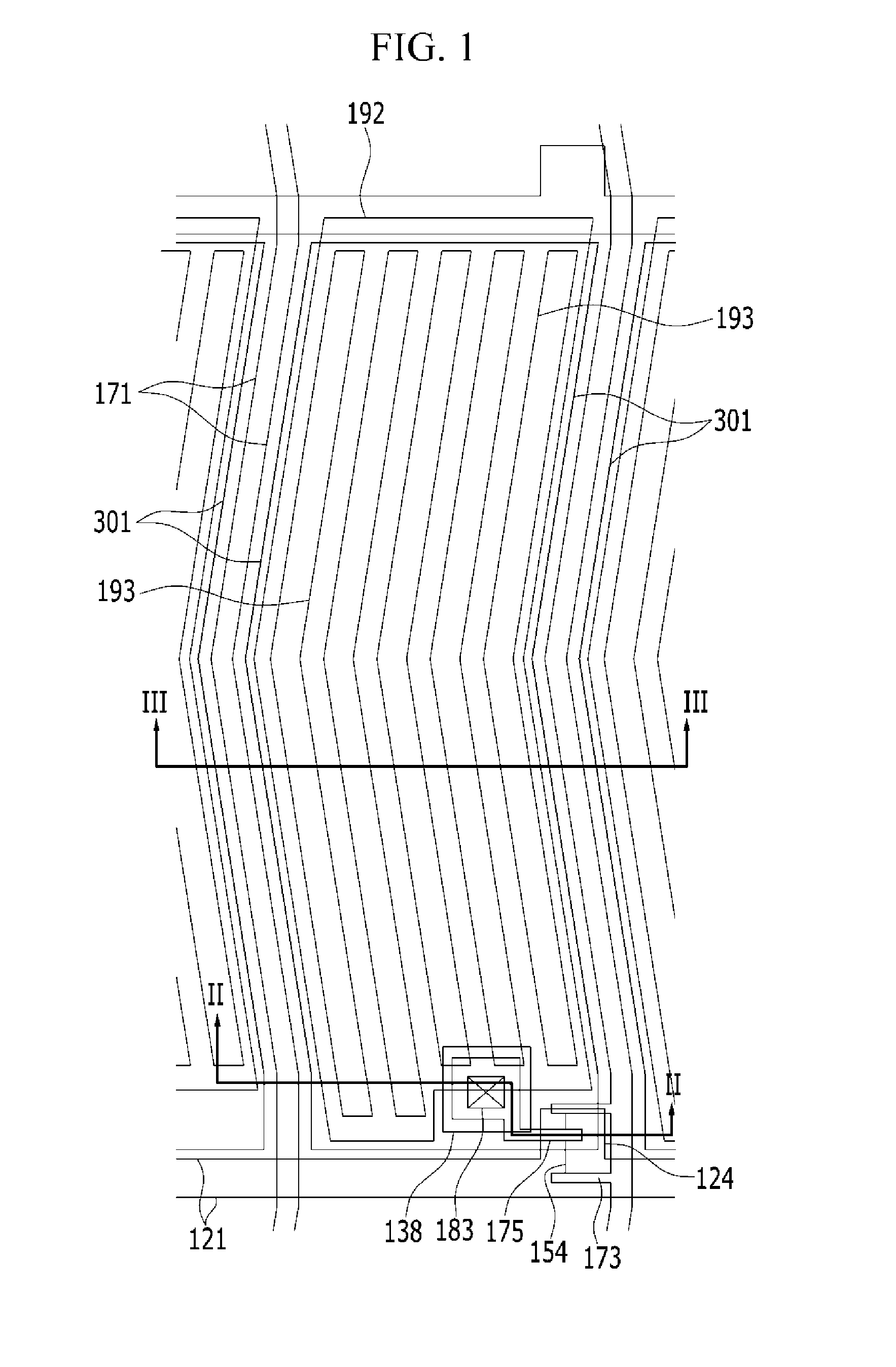

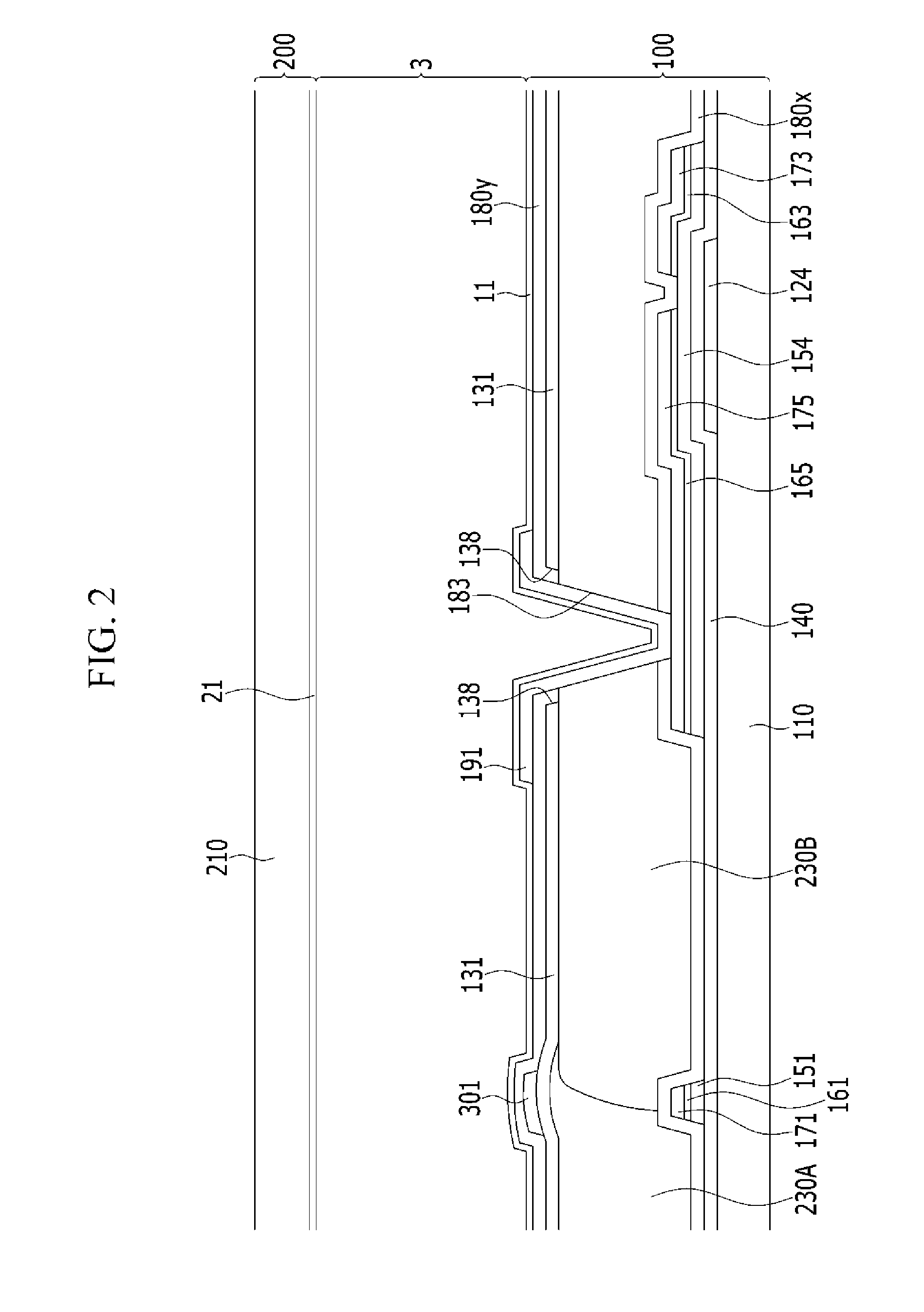

Active matrix substrate and liquid crystal display device provided with same

InactiveUS20090201455A1Reduce signal delaySolid-state devicesNon-linear opticsElectrical resistance and conductanceLiquid-crystal display

An active matrix substrate includes an insulating substrate, gate wires and source wires that intersect with each other on the insulating substrate, and TFTs provided at intersections of signal lines. The TFTs include gate electrodes, source electrodes and drain electrodes, respectively. A transparent conductive film, which is arranged to be used as a lower layer of the sources and the drains, is used as common electrodes for pixel areas surrounded by adjacent source wires, and also common electrode wires arranged to connect adjacent ones of the common electrodes parallel or substantially parallel to the source wires. This provides an active matrix substrate in which a signal delay caused by resistance and parasitic capacitance is reduced.

Owner:SHARP KK

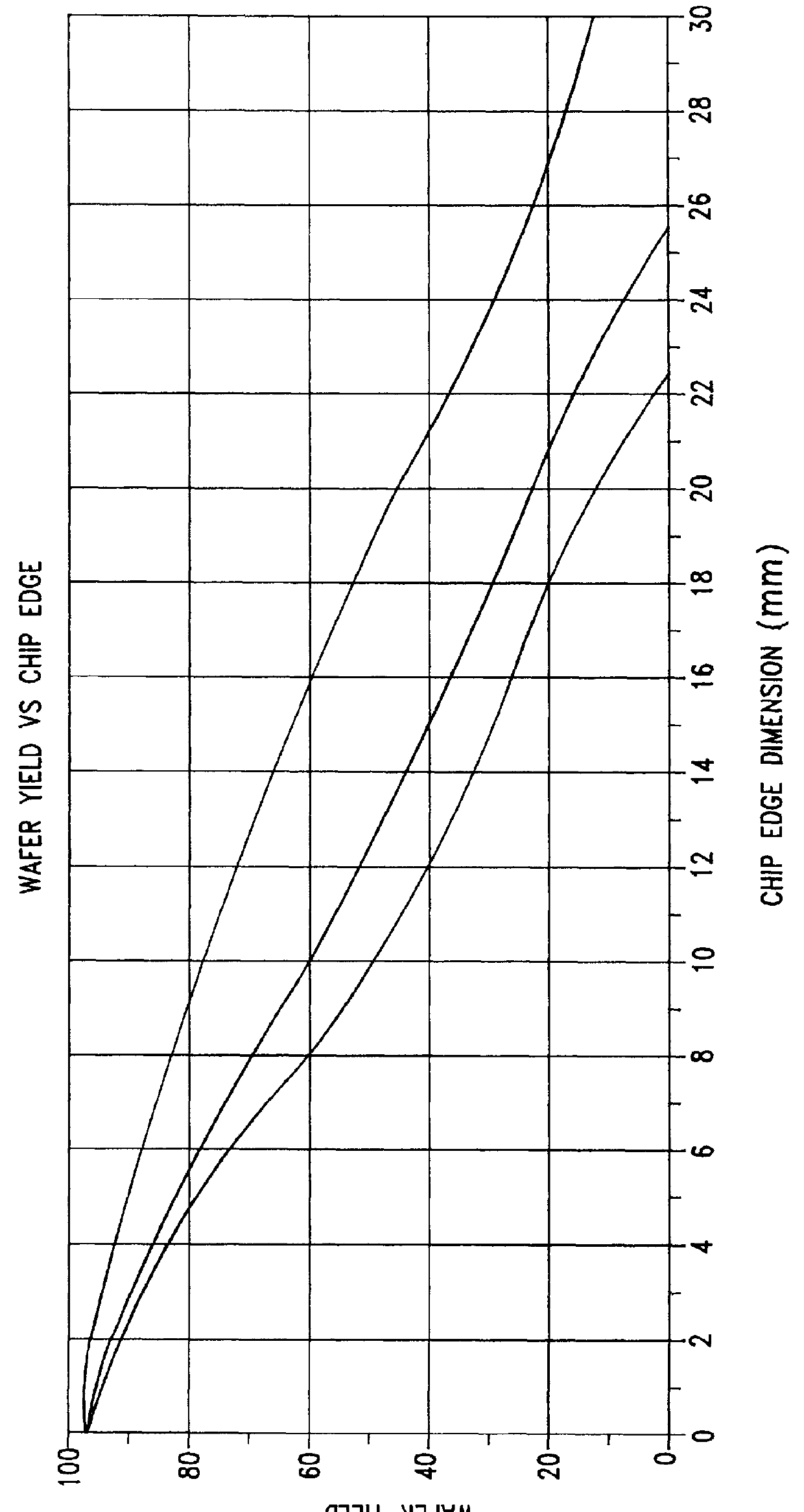

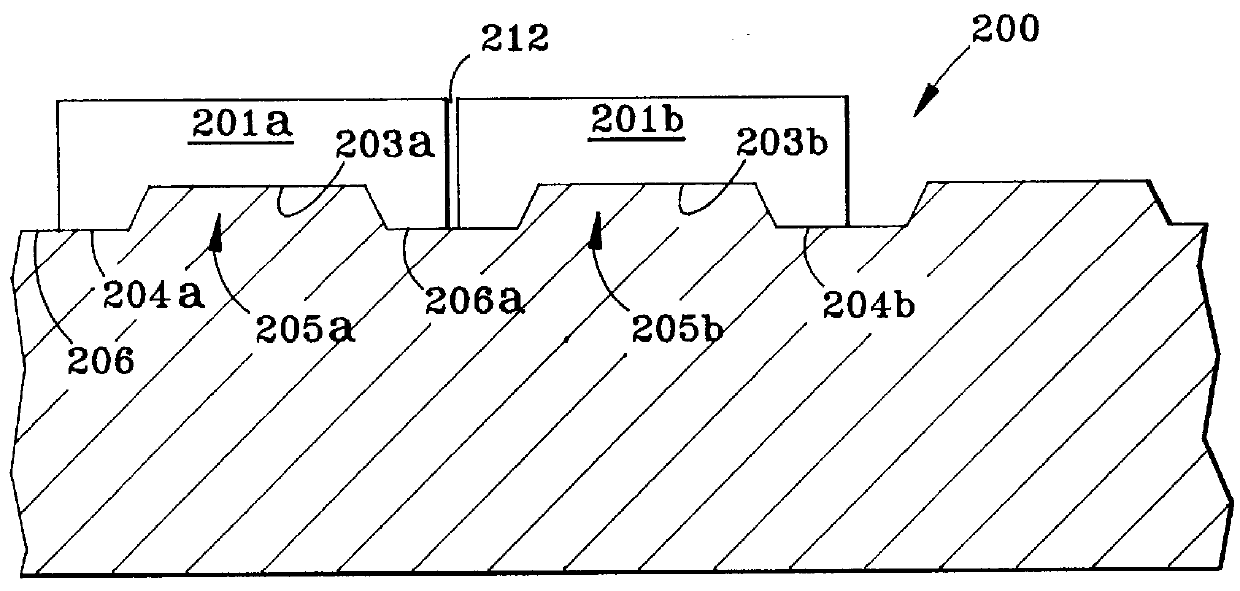

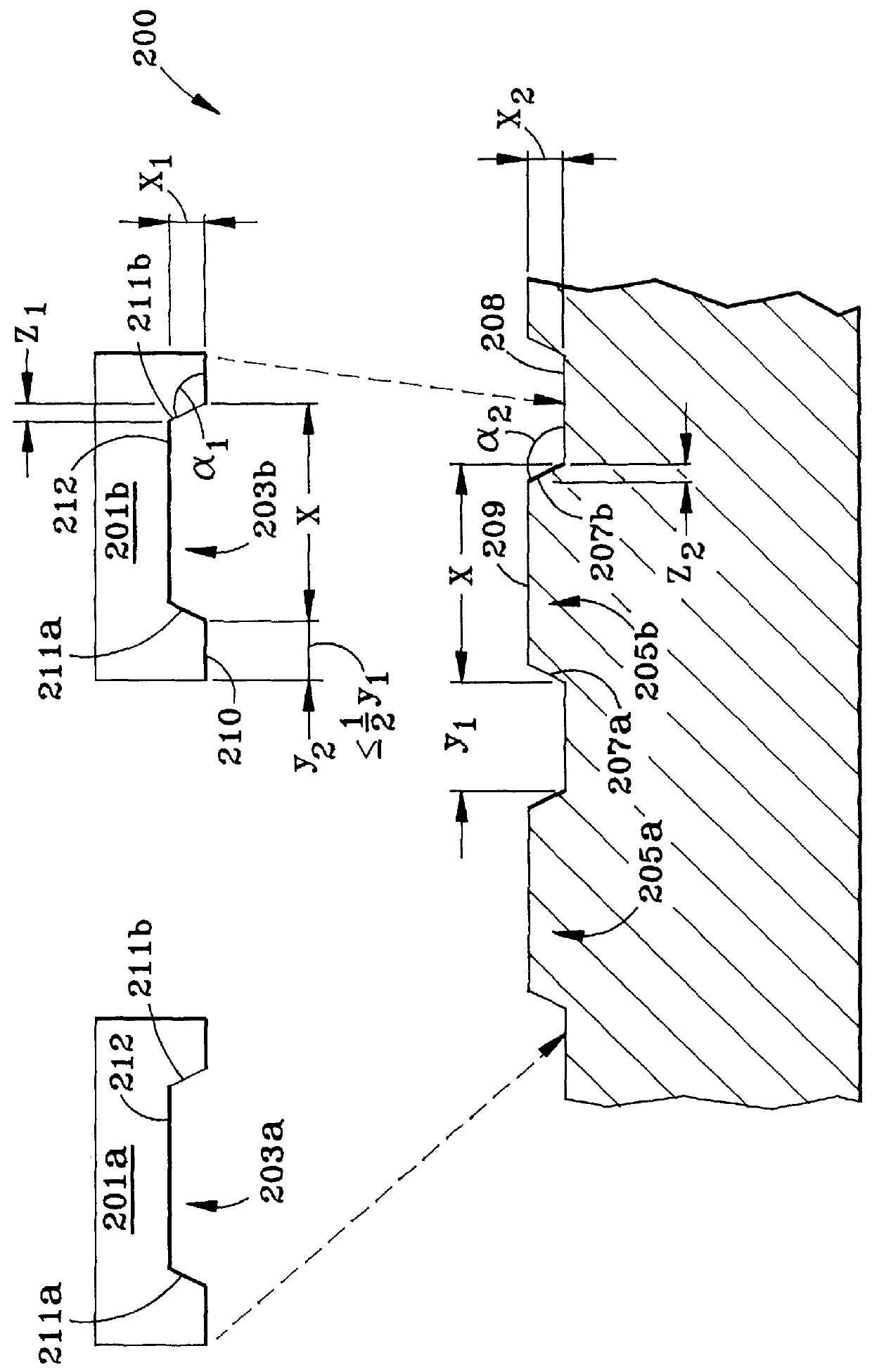

Method for fabricating a very dense chip package

InactiveUS6087199AConstant widthIncrease widthSemiconductor/solid-state device detailsSolid-state devicesIn planeTopography

A method for fabricating an integrated circuit package or arrangement includes providing a carrier having a surface topography of projections or recesses for supporting individual semiconductor circuit chips having conversely matching bottom surface topographies to permit self-aligned positioning of the chip on the carrier. Chips are provided such that top faces of neighboring chips lie substantially in planes separated by a distance of greater than 0.0 mu m. The carrier is arranged and dimensioned such that the neighboring chips are separated by a gap G or spacing in a range of 1 mu m<G< / =100 mu m. A metallic interconnect is provided over the top faces and the gap. Preferably, the interconnect has a gradual slope over the gap.

Owner:GOOGLE LLC

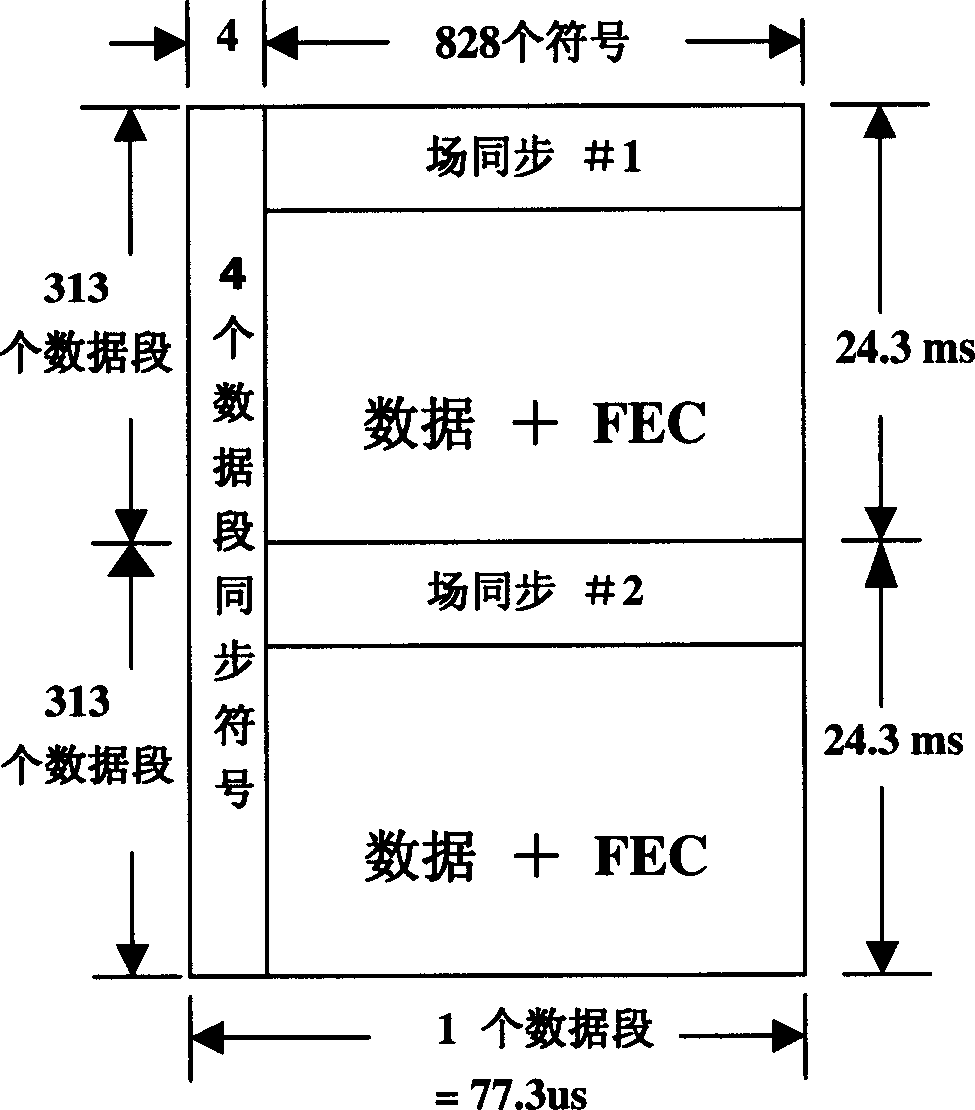

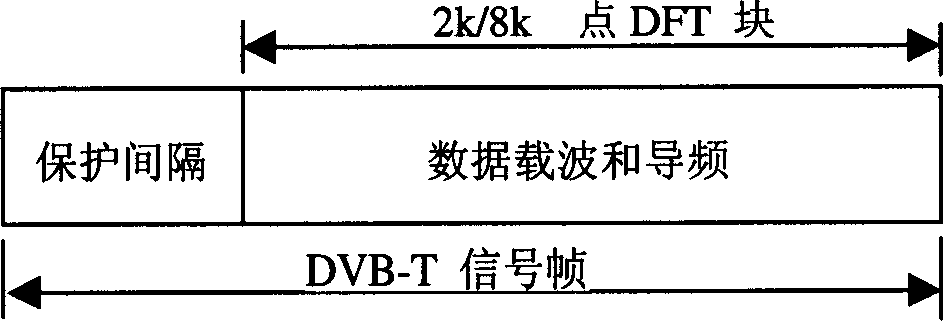

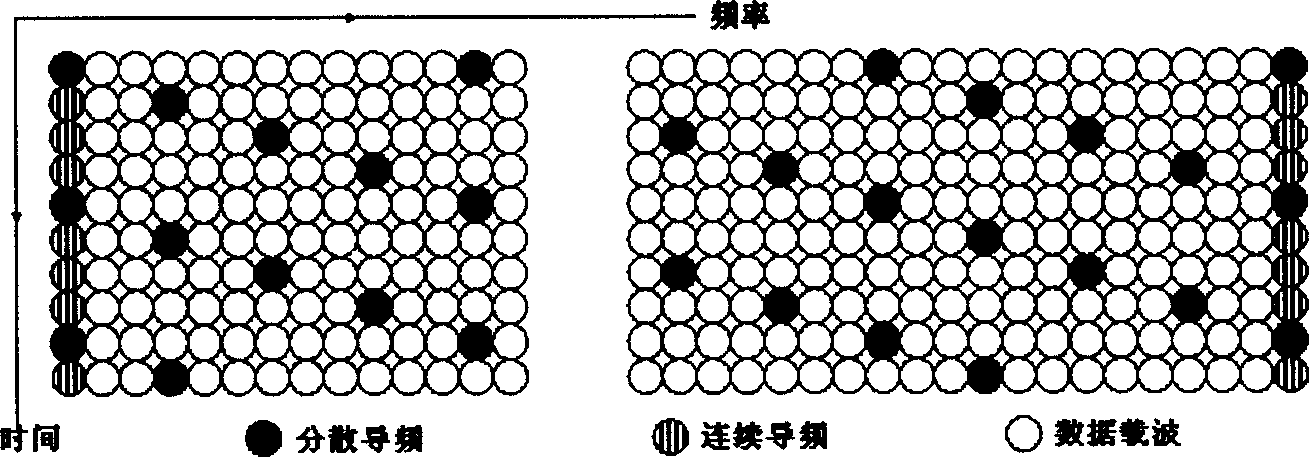

Time-frequency matrix two-dimensional channel dynamic allocation method in multimedia information transmission

InactiveCN1604509AFlexible allocationLow costMultiplex communicationMulti-frequency code systemsCarrier signalMultimedia information

It is a multimedia information transmission time frequency matrix two-dimensional sub-channel dynamic alignment method, which belongs to digit information transmission technique field and comprises the following steps: to generate two-dimensional time zone and frequency zone matrix TFM channel alignment pattern according to certain rules; to align the multimedia program code flow input to the relative TDS-OFDM signal frame and OFDM sub-carrier wave according to the alignment pattern; to insert TFMp matrix information into the head frame group of TDS-OFDM; finally to send the complete signal of TDS-OFDM.

Owner:TSINGHUA UNIV

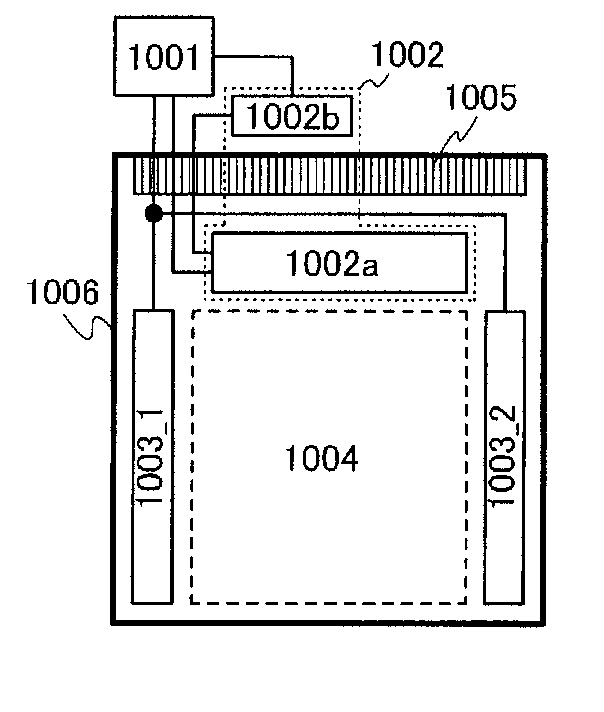

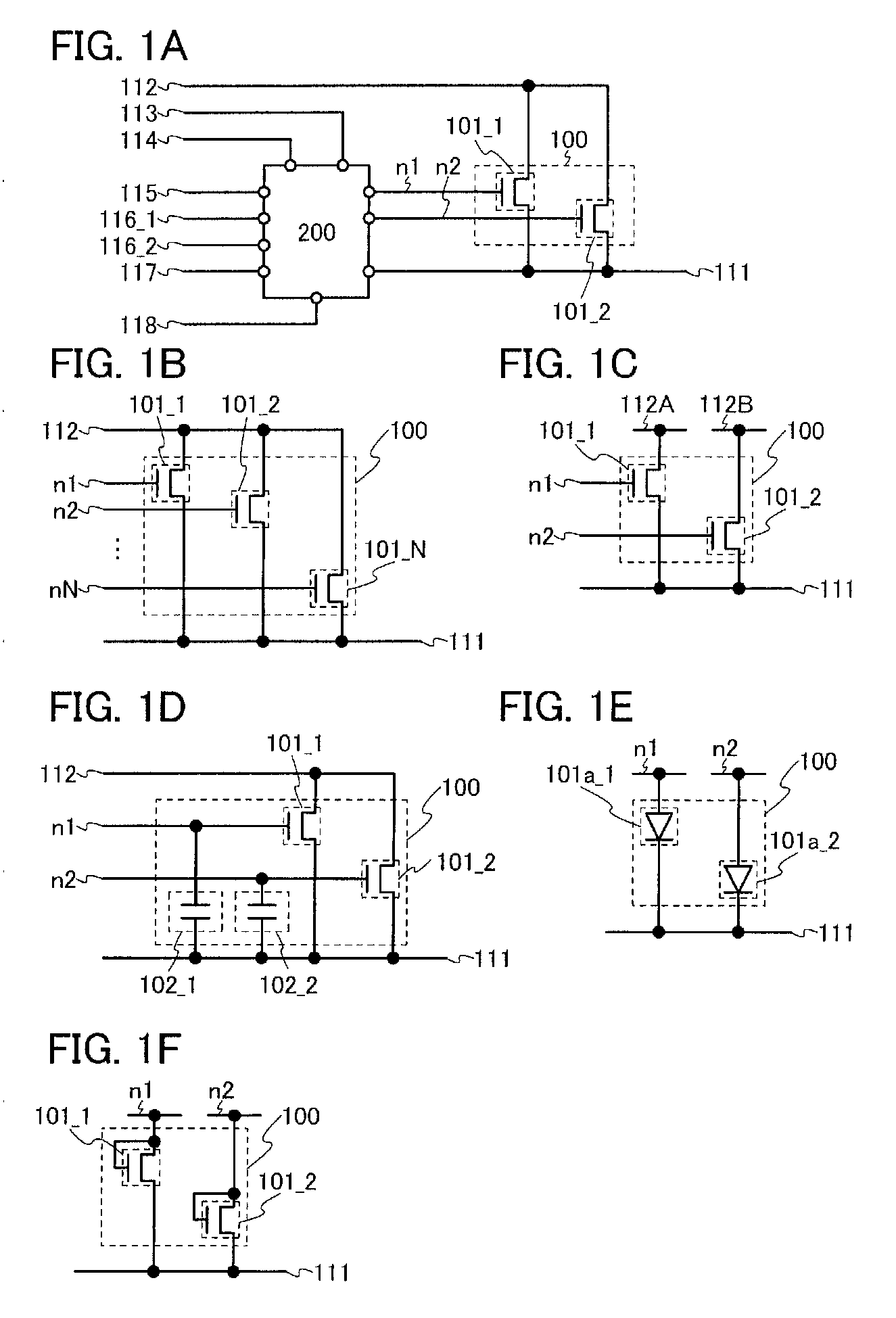

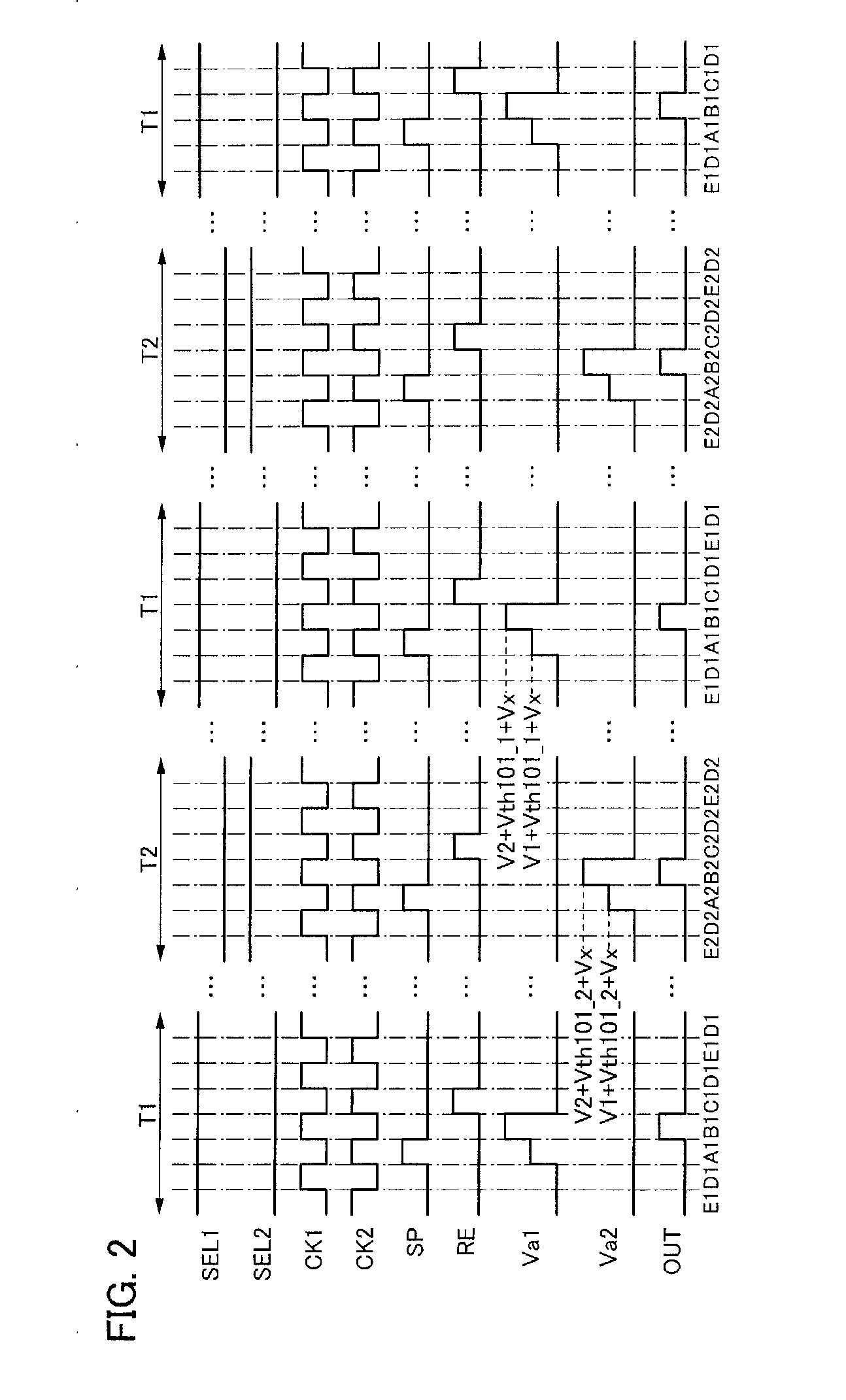

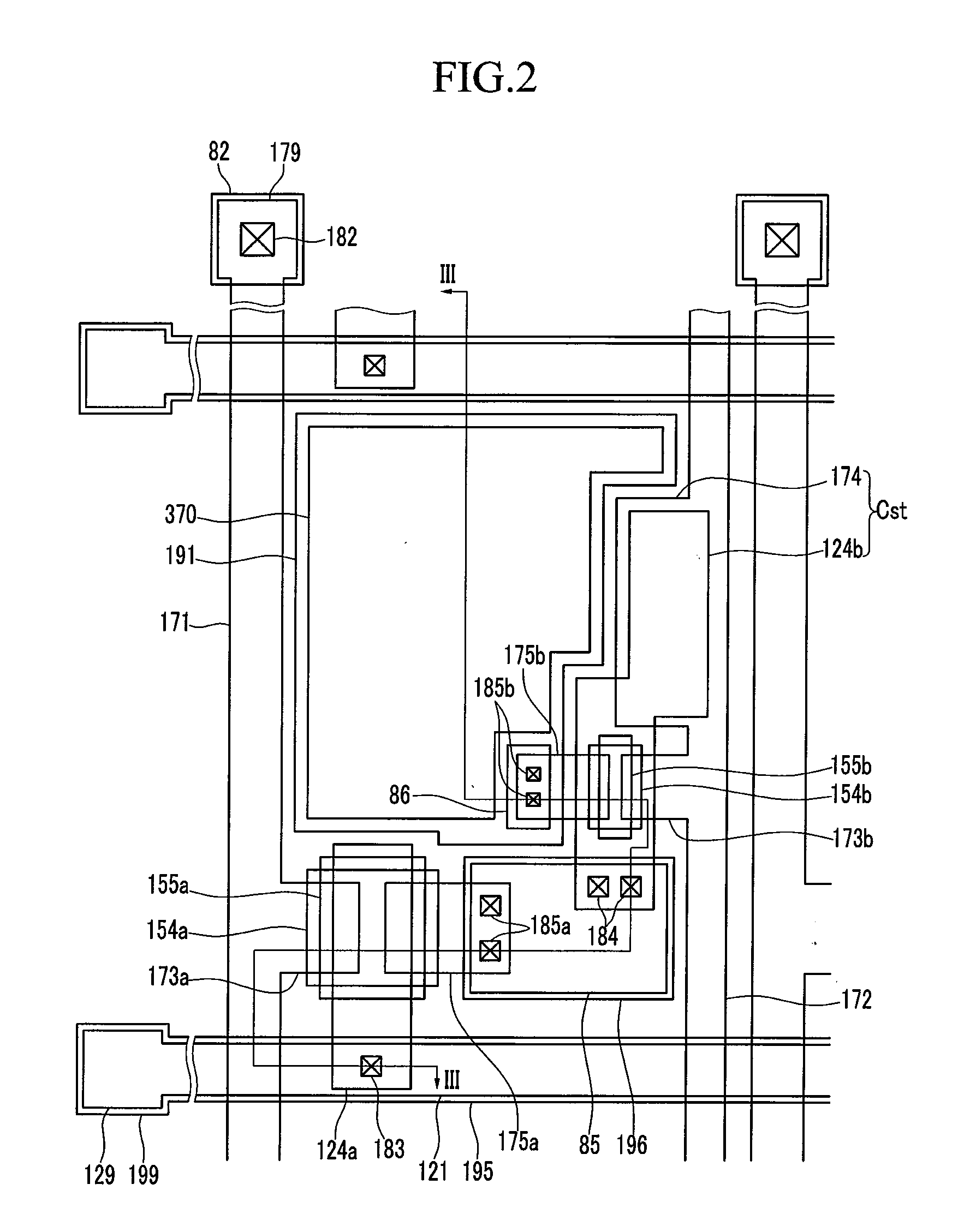

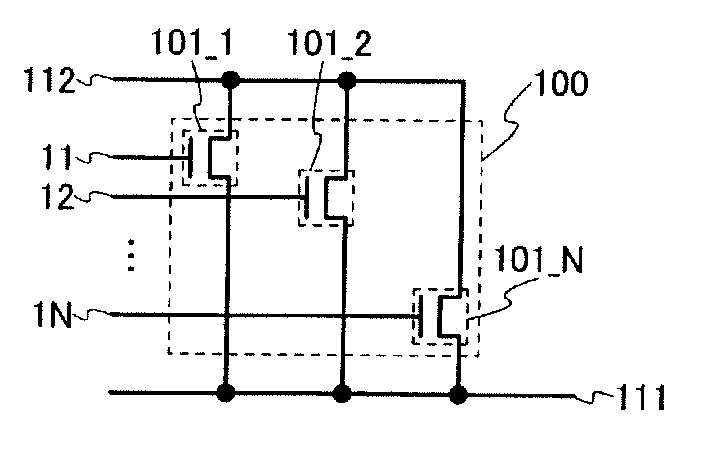

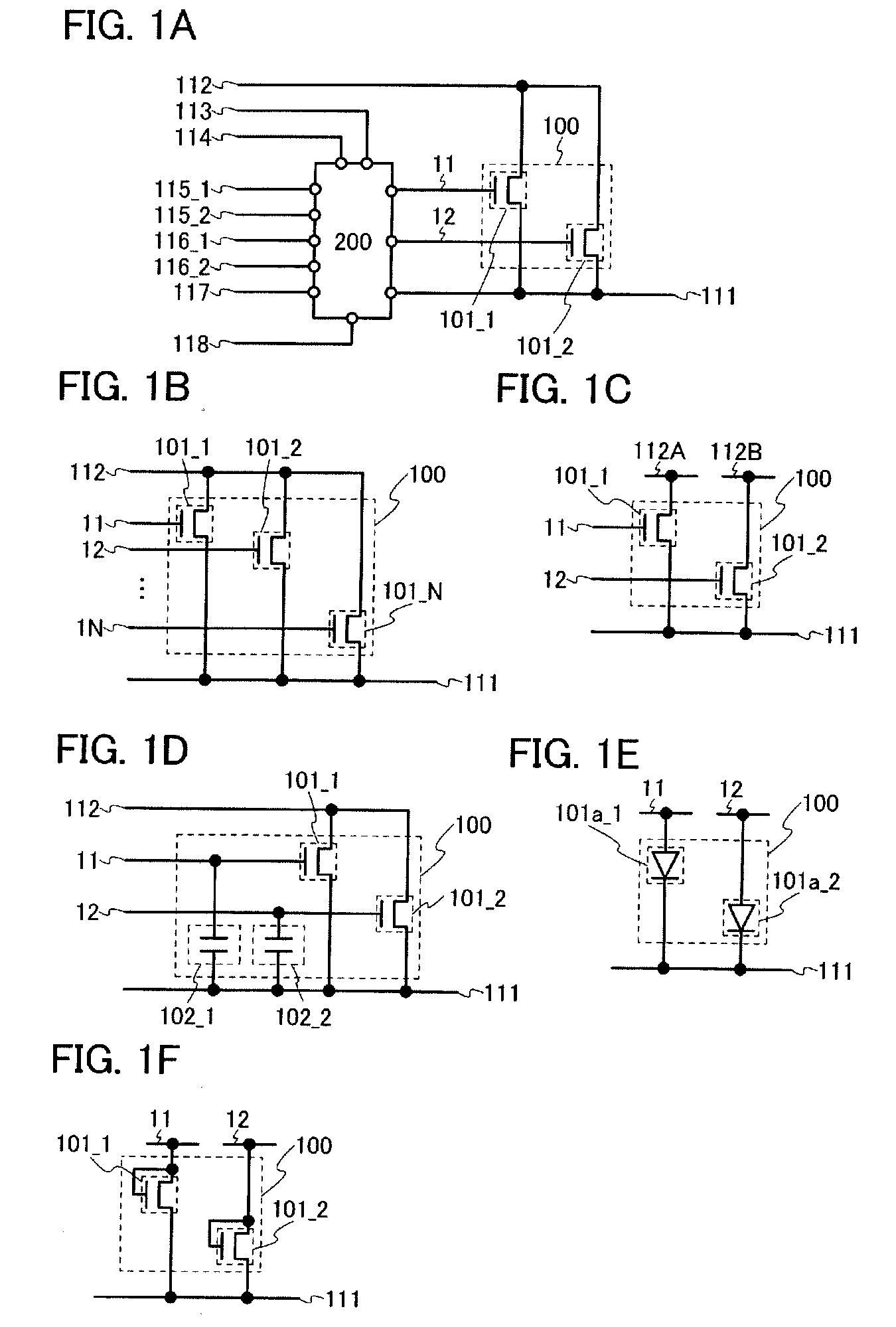

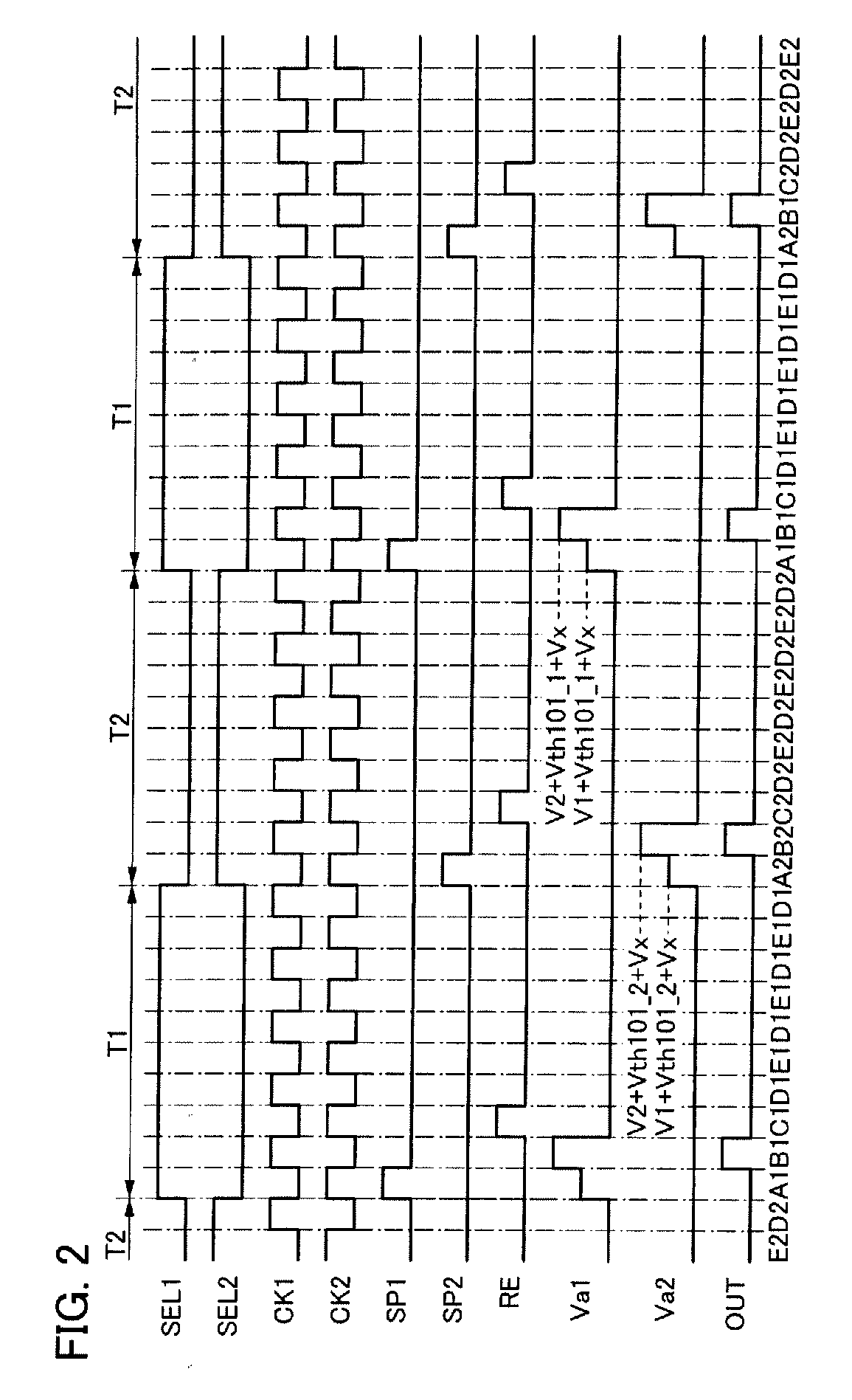

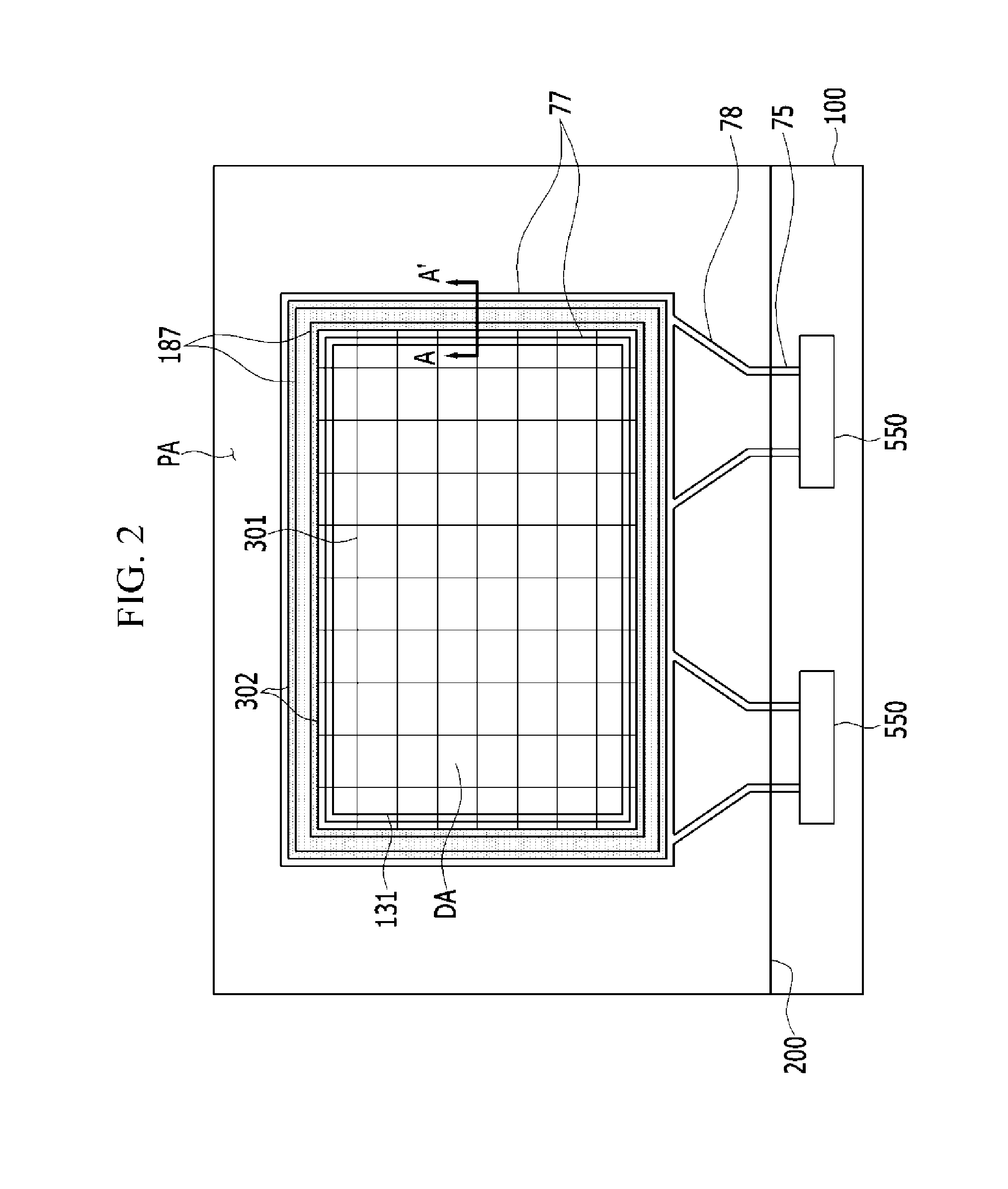

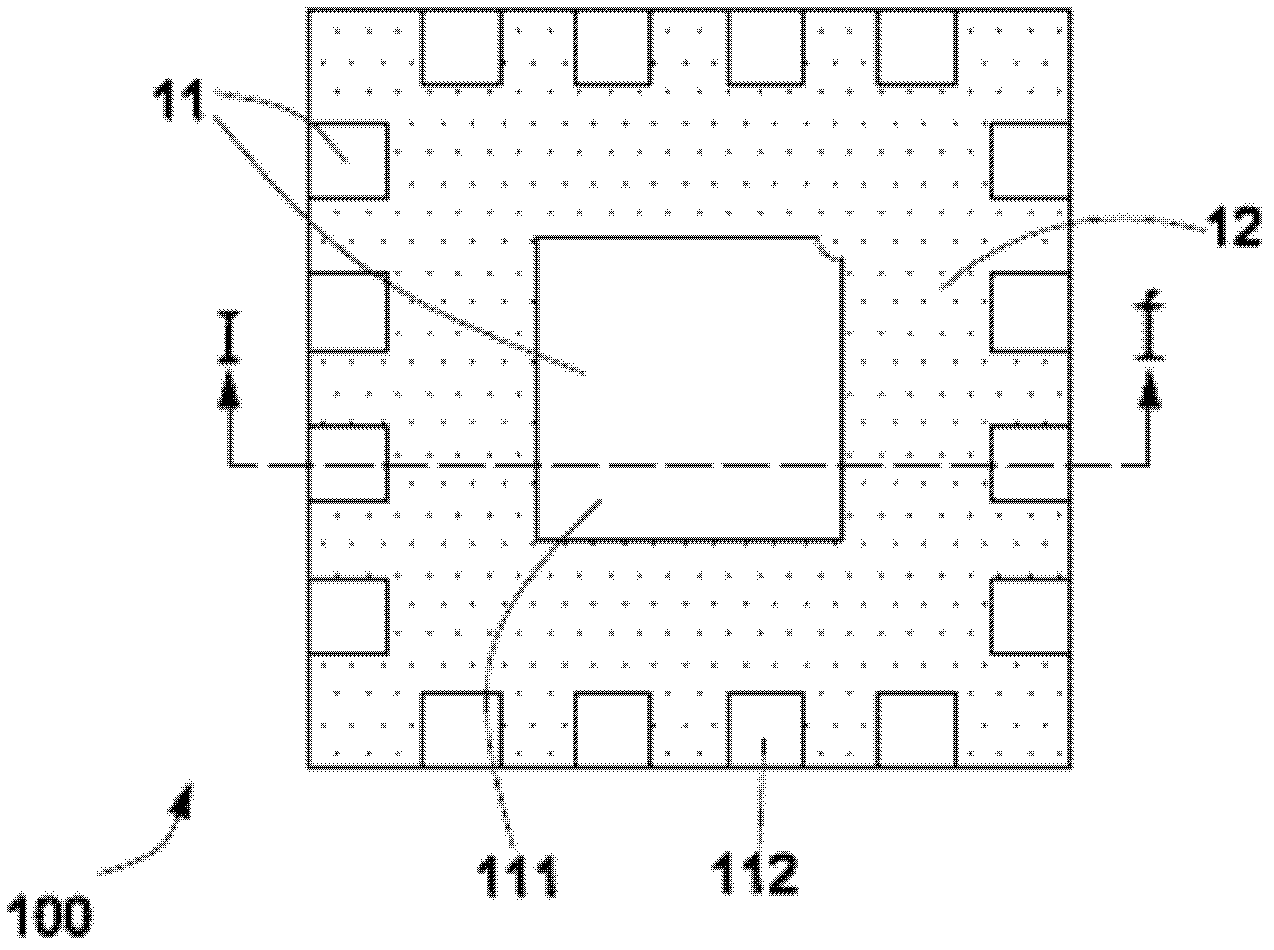

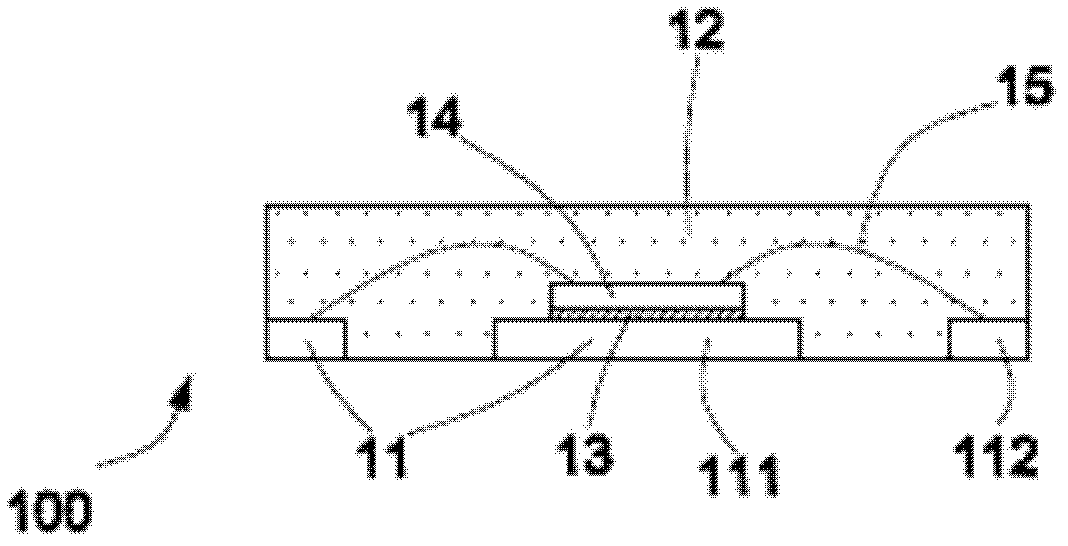

Liquid Crystal Display Device and Electronic Device Including the Same

ActiveUS20100245307A1Prevent degradationChannel width reductionSolid-state devicesCathode-ray tube indicatorsDriver circuitLiquid-crystal display

A driver circuit includes a circuit 200, a transistor 101—1, and a transistor 101—2. A signal is selectively input from the circuit 200 to a gate of the transistor 101—1 and the transistor 101—2, so that the transistor 1011 and the transistor 101—2 are controlled to be on or off. The transistor 101—1 and the transistor 101—2 are turned on or off; thus, the wiring 112 and the wiring 111 become conducting or non-conducting.

Owner:SEMICON ENERGY LAB CO LTD

Operational time extension

InactiveUS7587698B1Reduce signal delaySolid-state devicesCAD circuit designTime extensionEngineering

Some embodiments provide a reconfigurable integrated circuit (“IC”). This IC has several reconfigurable circuits, each having several configurations for several configuration cycles. The reconfigurable circuits include several time-extending reconfigurable circuits. During the operation of the IC, each particular time-extending reconfigurable circuit maintains at least one of its configurations over at least two contiguous cycles, in order to allow a signal to propagate through a signal path, which contains the particular time-extending circuit, within a desired amount of time.

Owner:ALTERA CORP

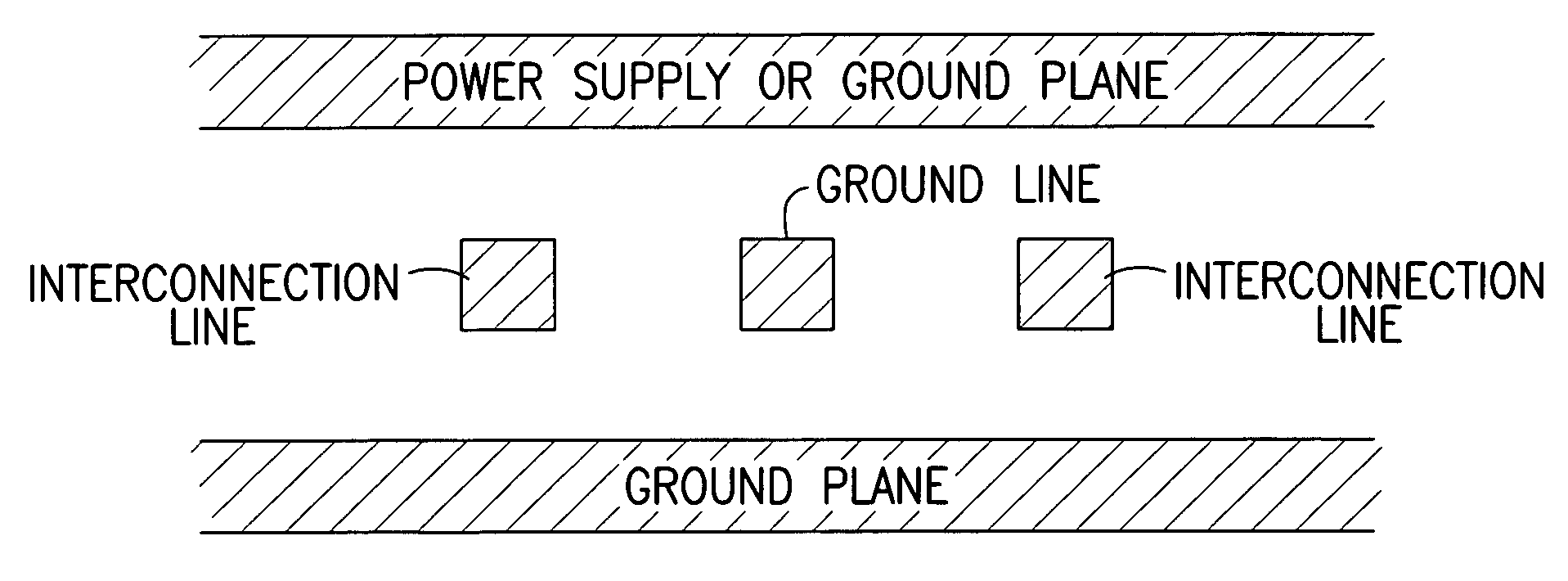

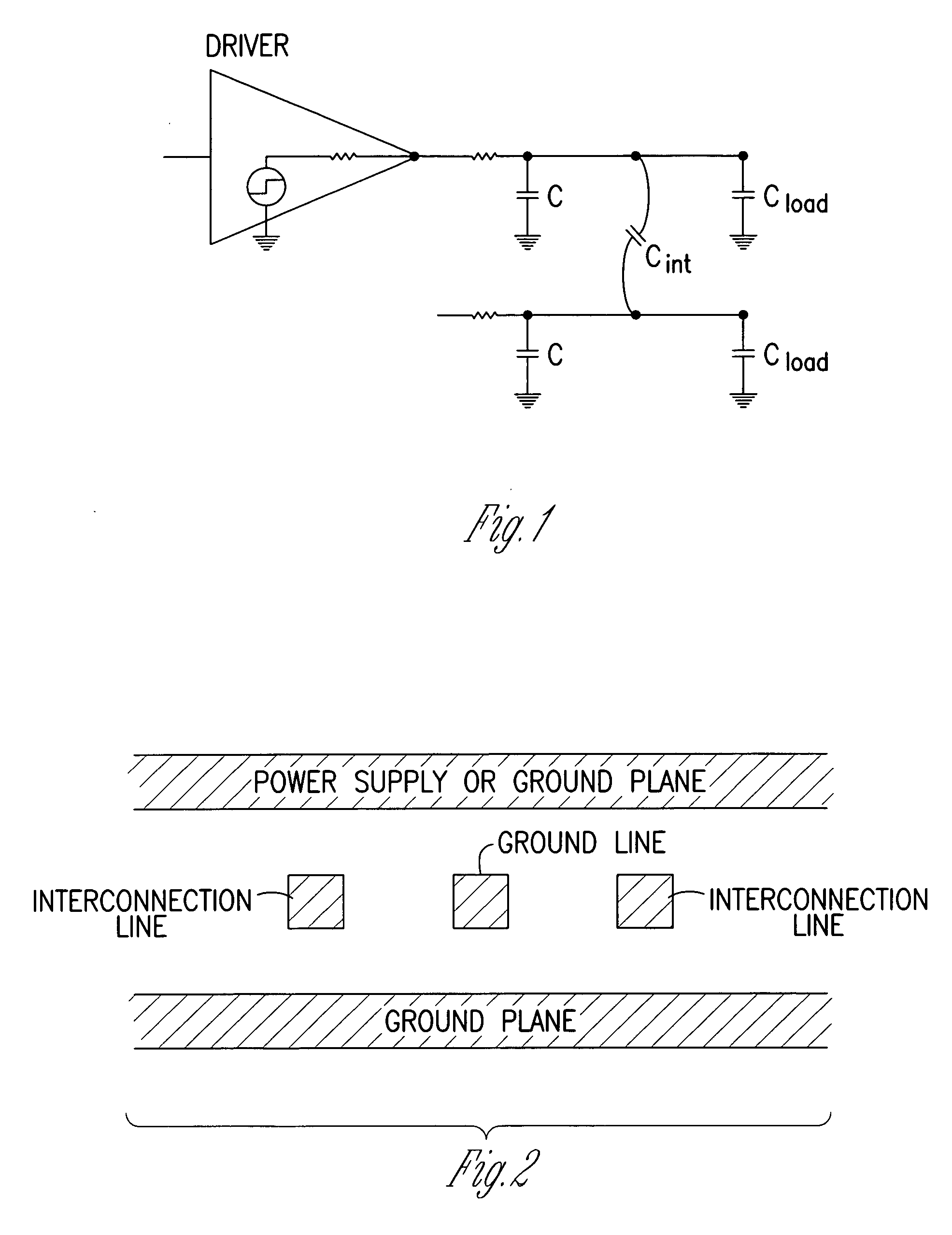

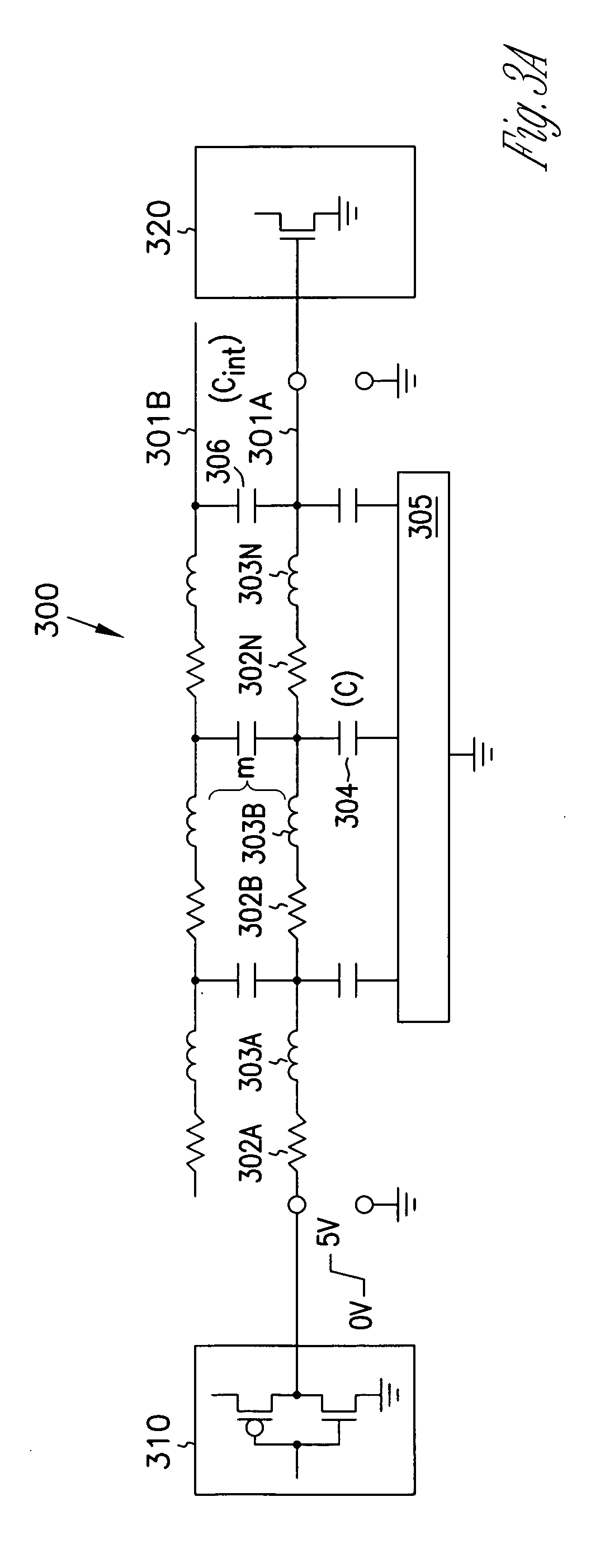

Capacitive techniques to reduce noise in high speed interconnections

InactiveUS20050023650A1Reduce noiseReduce signal delaySemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

Improved methods and structures are provided using capacitive techniques to reduce noise in high speed interconnections, such as in CMOS integrated circuits. The present invention offers an improved signal to noise ration. The present invention provides for the fabrication of improved transmission lines for silicon-based integrated circuits using conventional CMOS fabrication techniques. Embodiments of a method for forming transmission lines in an integrated circuit include forming a first layer of electrically conductive material on a substrate. The method includes forming a first layer of insulating material on the first layer of the electrically conductive material. The first layer has a thickness of less than 1.0 micrometers (μm). A transmission line is formed on the first layer of insulating material. The transmission line has a thickness and a width of approximately 1.0 micrometers. A second layer of insulating material is formed on the transmission line. And, a second layer of electrically conductive material is formed on the second layer of insulating material.

Owner:MICRON TECH INC

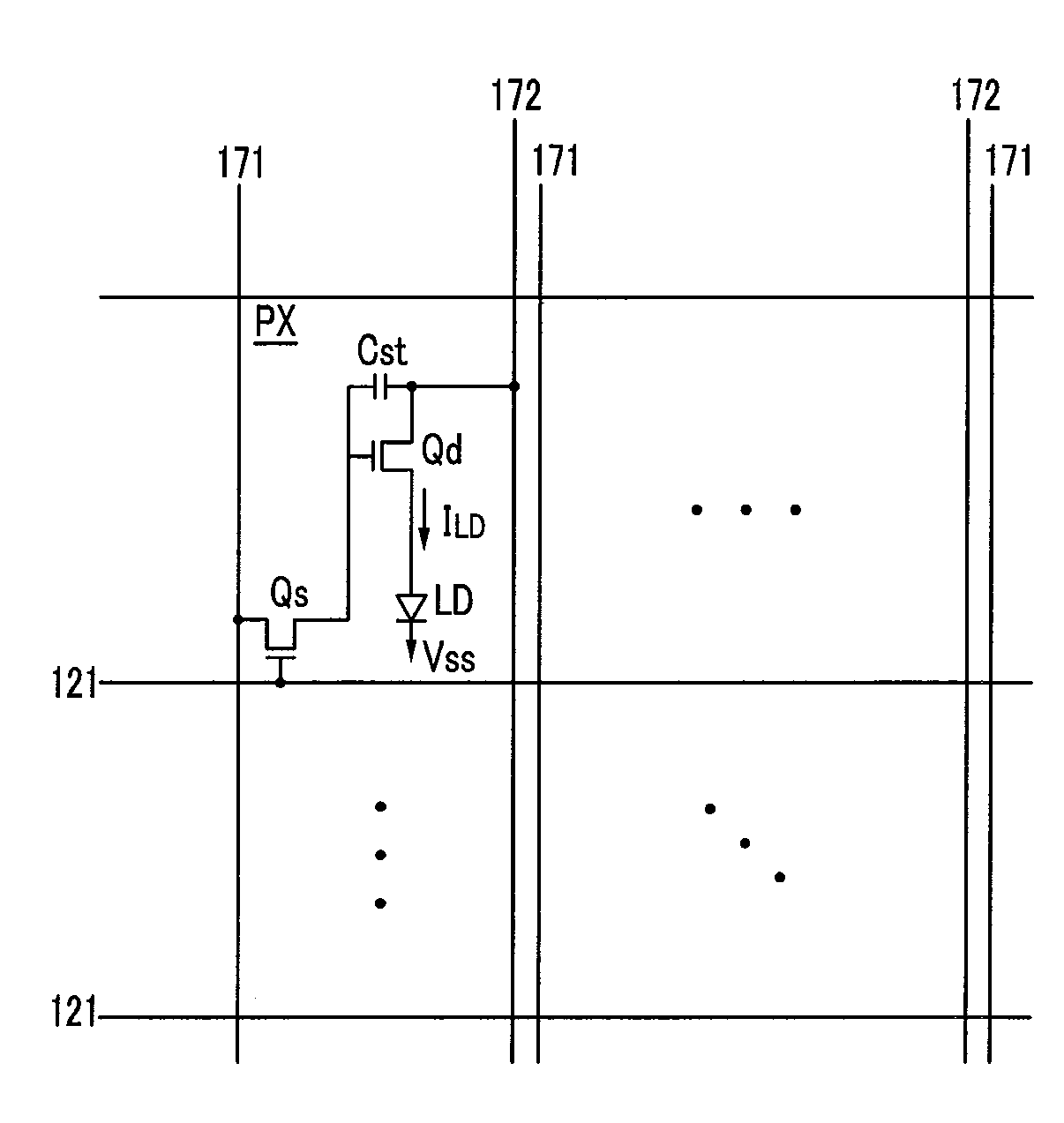

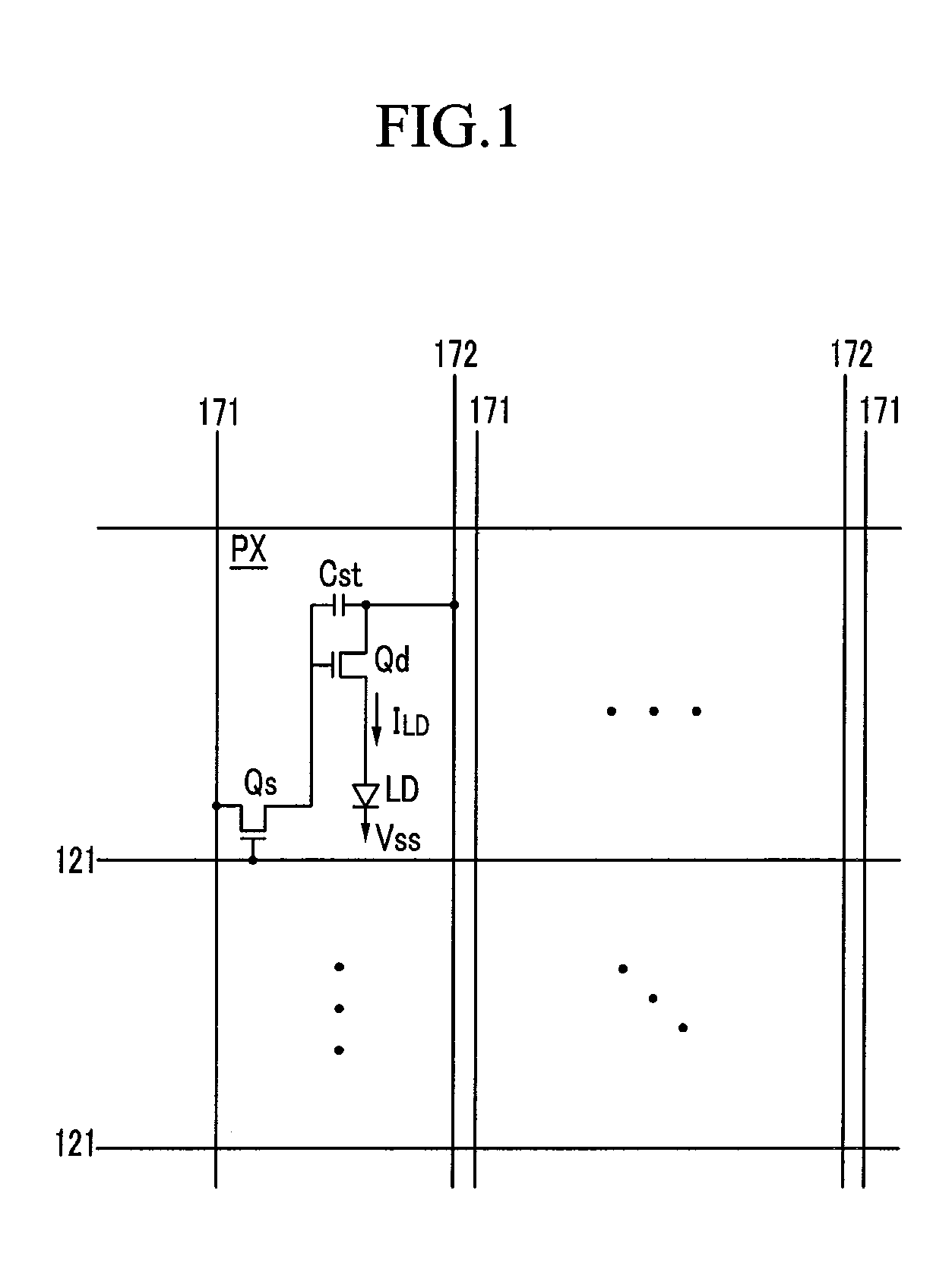

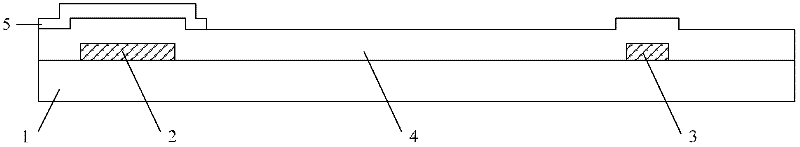

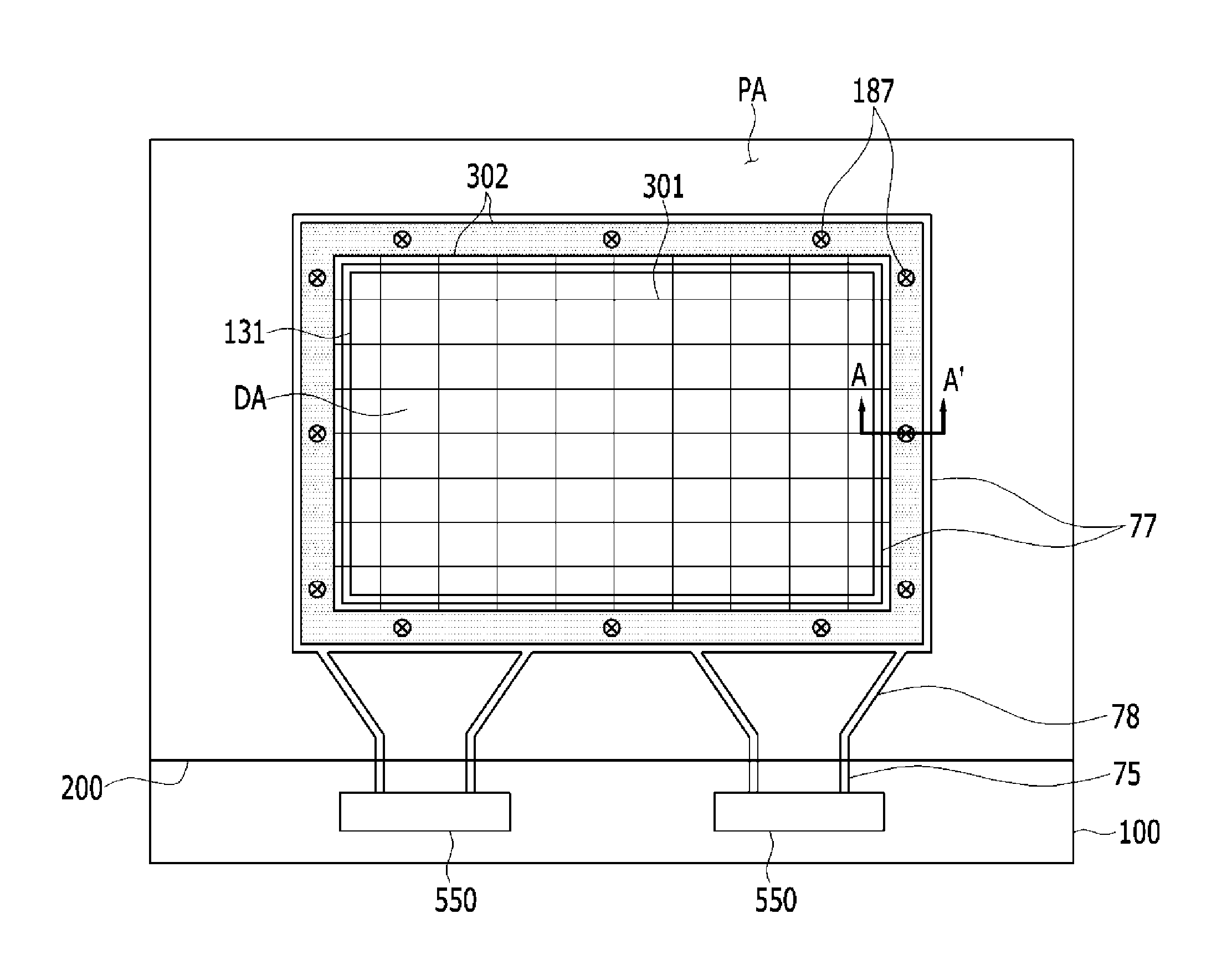

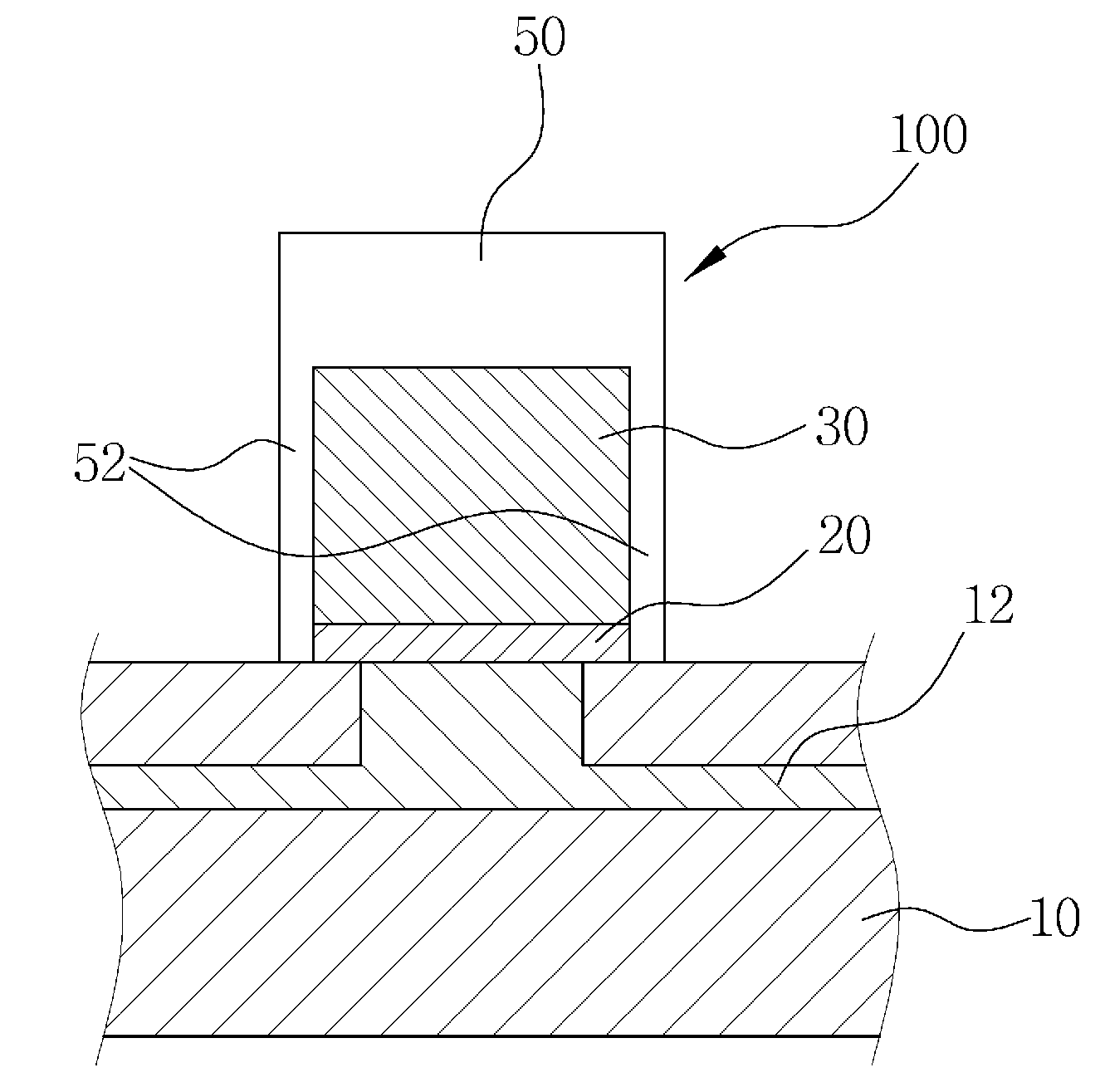

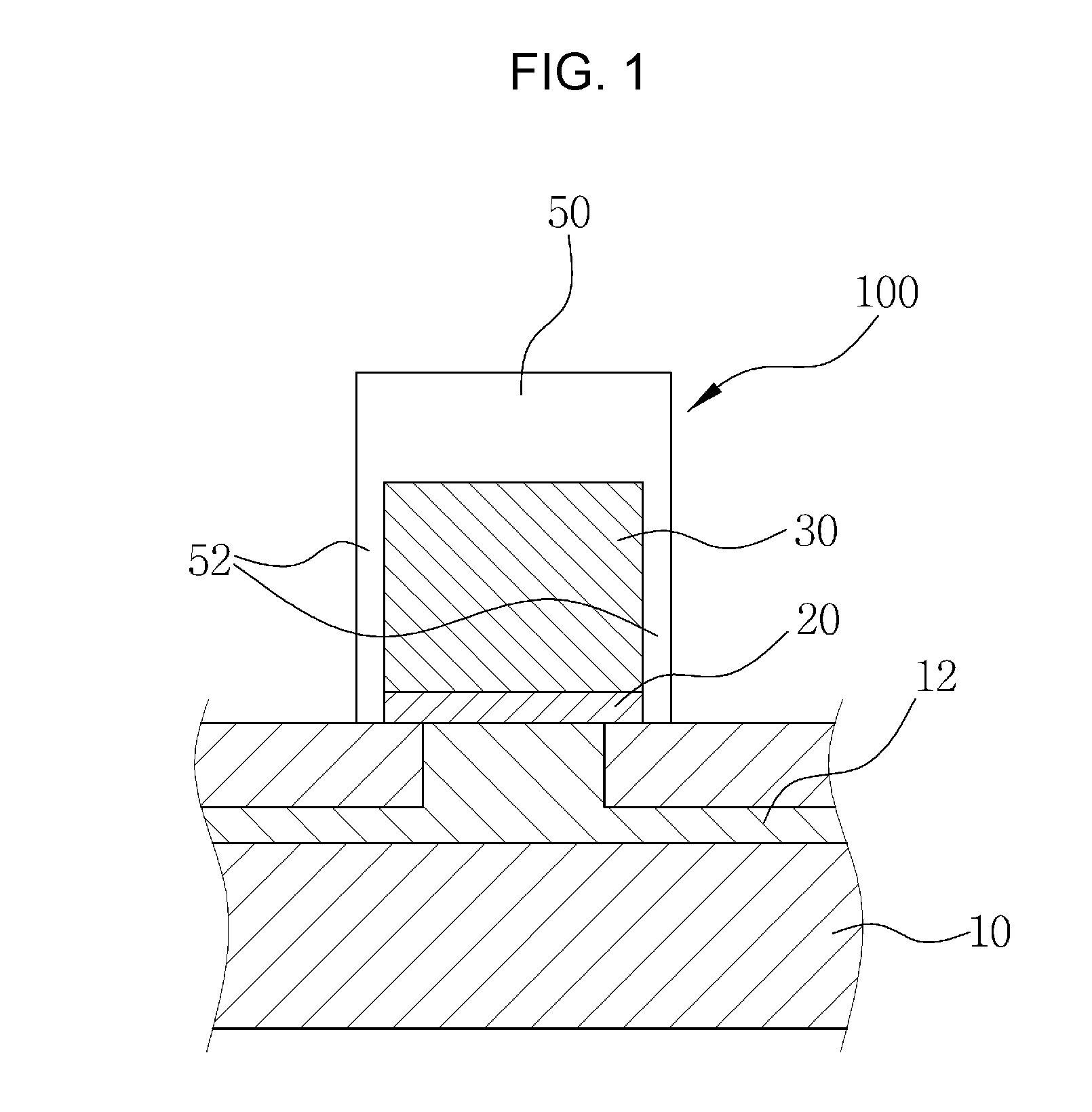

Organic light emitting diode display and method for manufacturing the same

ActiveUS20090121982A1Reduce signal delayImprove characteristicDischarge tube luminescnet screensStatic indicating devicesEngineeringData lines

An organic light emitting device according to one or more embodiments includes a gate line, a data line intersecting the gate line, a switching thin film transistor connected to the gate line and the data line, a driving thin film transistor connected to the switching thin film transistor, and a light emitting diode (LED) connected to the driving thin film transistor. The switching thin film transistor includes a control electrode connected to the gate line, a crystalline semiconductor overlapping the control electrode, and an input electrode and an output electrode are spaced apart from each other on the crystalline semiconductor, wherein the control electrode and the gate line are respectively disposed under and on the crystalline semiconductor and include different materials.

Owner:SAMSUNG DISPLAY CO LTD

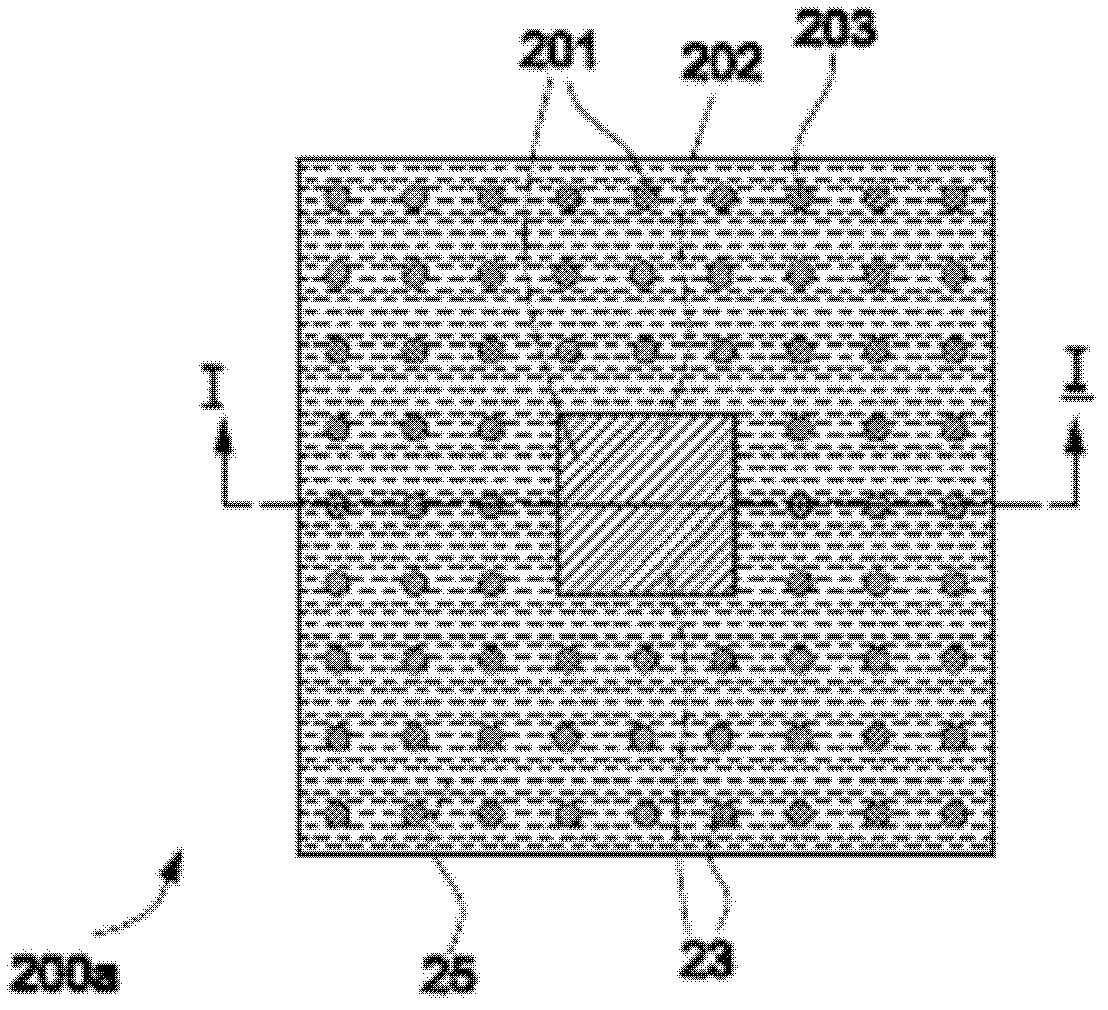

Semiconductor Device and Electronic Device Including Semiconductor Device

ActiveUS20100246750A1Suppress characteristicImprove the shortageTransistorStatic indicating devicesDriver circuitEngineering

It is an object to suppress deterioration in characteristics of a transistor in a driver cricuit. A driver circuit includes a first transistor, a second transistor including a gate and one of a source and a drain to which a second signal is inputted, a third transistor whose gate is electrically connected to one of a source and a drain of the first transistor and which controls whether a voltage state of an output signal is set or not by being turned on / off, and a fourth transistor whose gate is electrically connected to the other of the source and the drain of the second transistor and which controls whether a voltage state of an output signal is set or not by being turned on / off.

Owner:SEMICON ENERGY LAB CO LTD

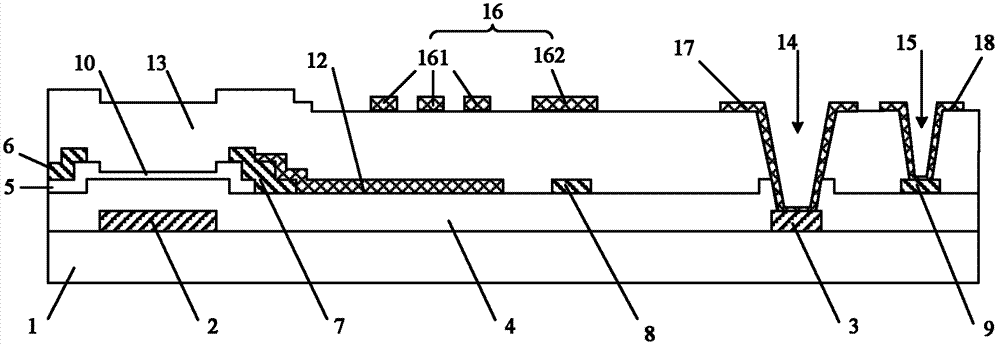

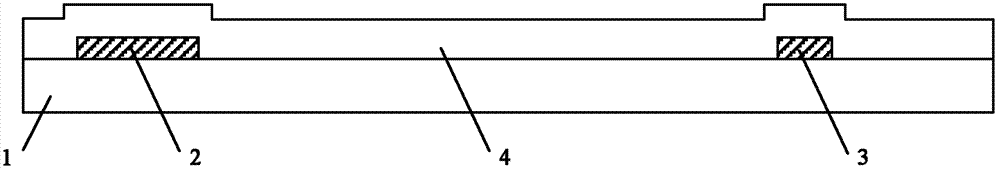

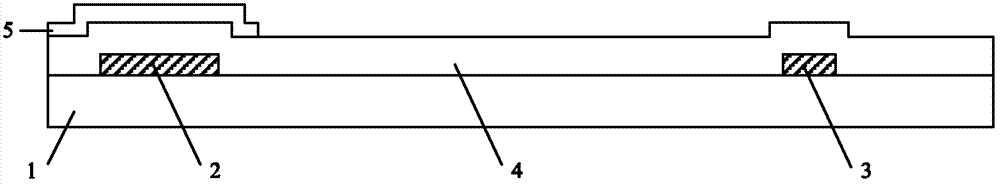

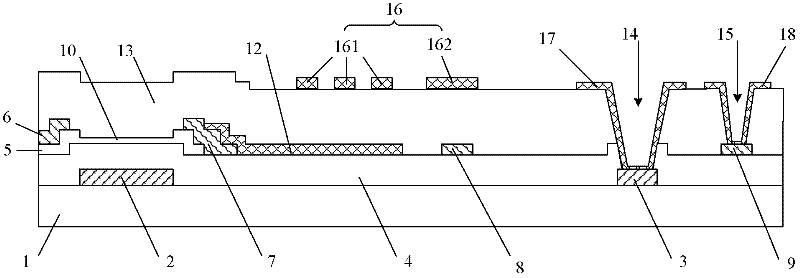

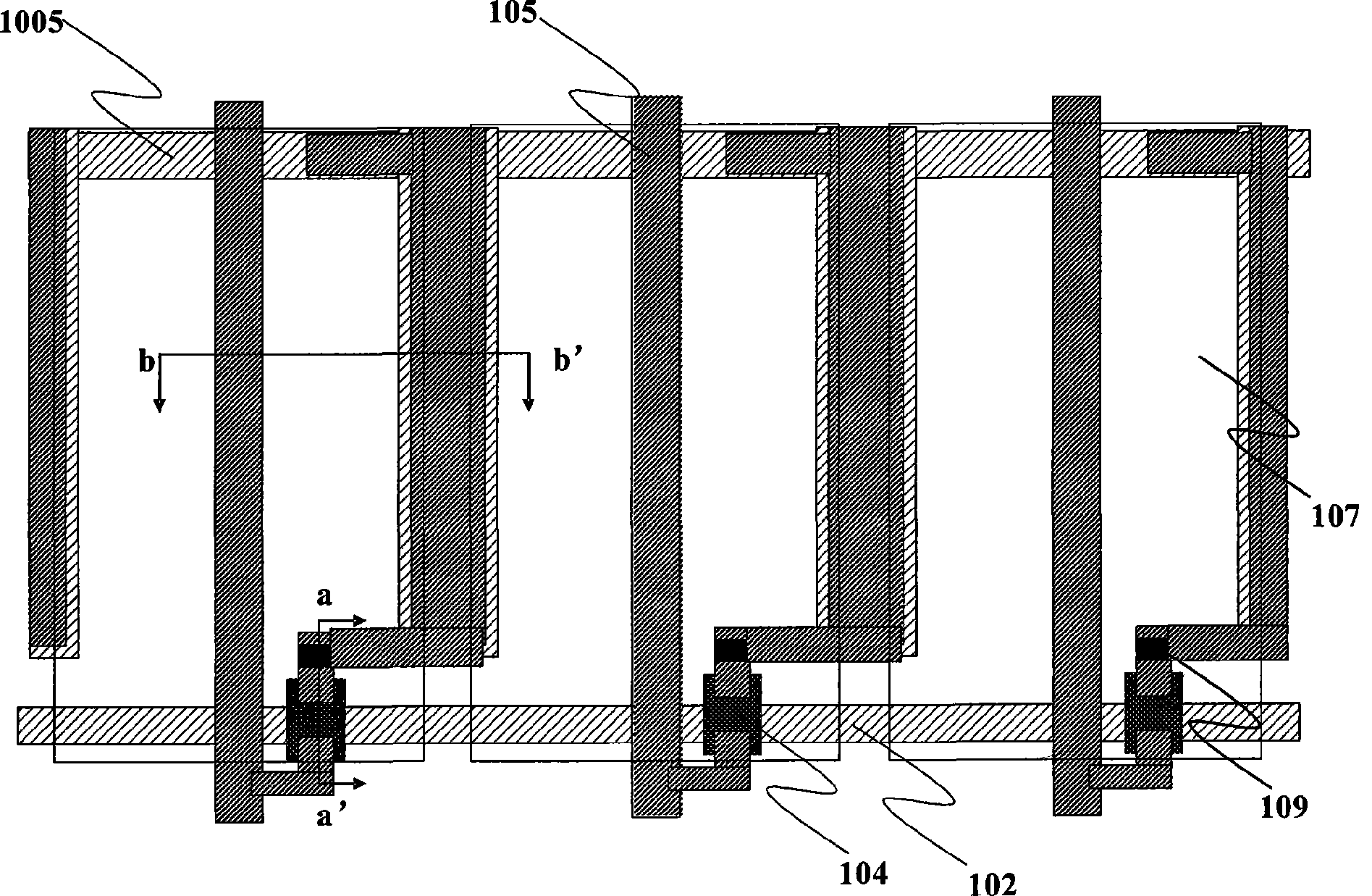

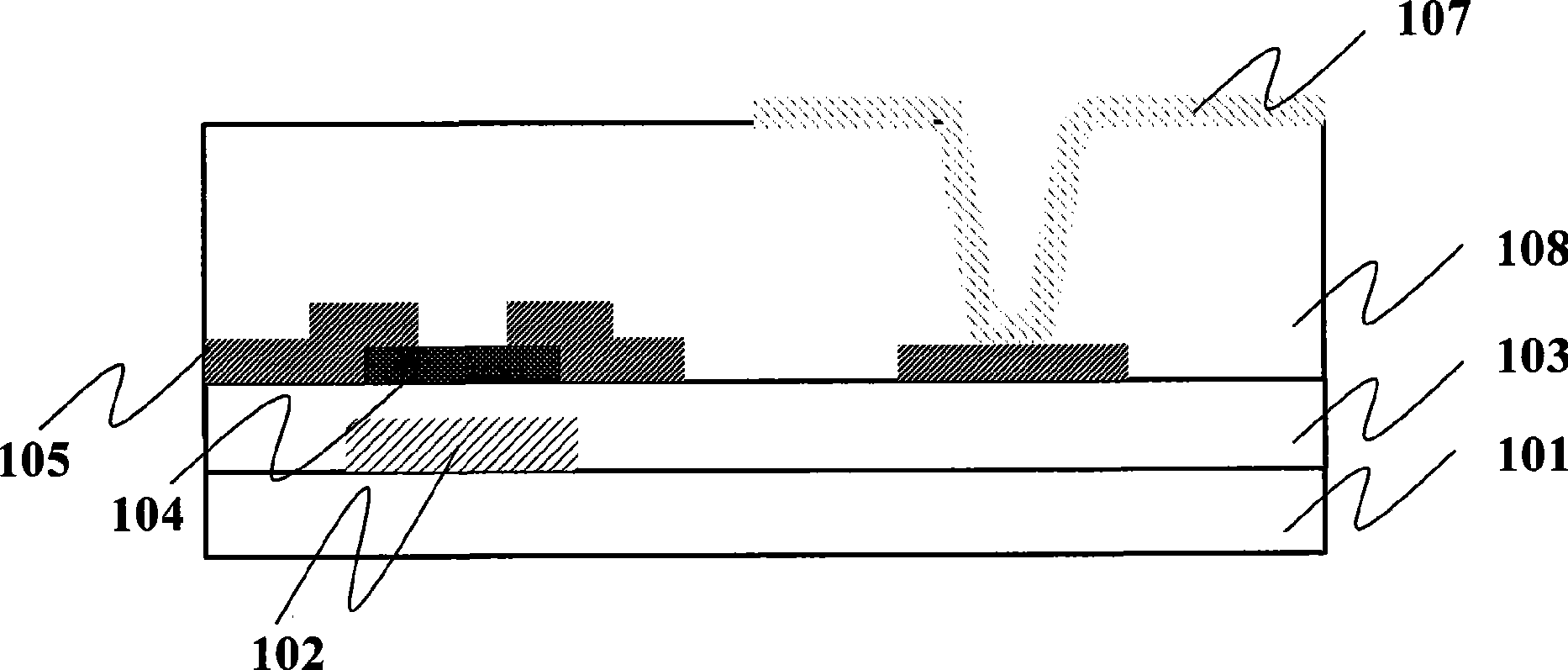

Manufacturing method of array substrate as well as array substrate and display device

InactiveCN102707523AReduce parasitic capacitanceReduce signal delaySemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayData lines

The invention provides a manufacturing method of an array substrate as well as the array substrate and a display device, belonging to the field of liquid crystal display. The array substrate comprises a display region and a non-display region, wherein the display region comprises a grid line, a data line and a plurality of pixel units located between the grid line and the data line; the non-display region comprises a grid welding disc and a data welding disc, wherein each pixel unit comprises a thin film transistor, a pixel electrode and a public electrode; the pixel electrode is connected with a drain electrode of the thin film transistor; the public electrode comprises a first public electrode located above the pixel electrode and a second public electrode located above the data line; a protection film is arranged between the layer on which the public electrode is located and the layer on which the pixel electrode is located; and organic insulating films are arranged between the pixel electrode and the data line, and between the thin film transistor and the protection film. According to the invention, the signal delay on the data line in the array substrate can be reduced.

Owner:BOE TECH GRP CO LTD +1

Manufacture method of array substrate, array substrate and display device

InactiveCN102645808AReduce parasitic capacitanceReduce signal delaySemiconductor/solid-state device manufacturingNon-linear opticsEngineeringData lines

The invention provides a manufacture method of an array substrate, the array substrate and a display device. A display region of the array substrate comprises a gate line, a data line and a plurality of pixel units. A non-display region comprises a gate bonding pad and a data bonding pad. Each of the pixel units comprises a thin film transistor, a pixel electrode and a common electrode. The pixel electrode is connected to a drain electrode of the thin film transistor. The common electrode comprises a first common electrode arranged above the pixel electrode and a second common electrode arranged above the data line. A protective film is arranged between a common electrode layer and a pixel electrode layer. An inorganic insulating film and an organic insulating film are arranged between the pixel electrode and the data line and between the thin film transistor and the protective film, respectively. The inorganic insulating film is formed above the data line, a source and the drain of the thin film transistor, and a semiconductor layer of a channel region, and the organic insulating film is arranged above the inorganic insulating film. The invention can reduce signal delay on the data line, and prevent generation of leakage current in the thin film transistor at a high temperature.

Owner:BOE TECH GRP CO LTD +1

Display device

ActiveUS20140184964A1Reduce display defectsIncrease freedomStatic indicating devicesNon-linear opticsDisplay deviceEngineering

A display device including: a substrate including a display area in which pixels are positioned and a peripheral area around the display area; a common electrode and a pixel electrode that are positioned on the display area and overlapping with each other, with a first insulating layer disposed therebetween; a common voltage line positioned on or below the common electrode and contacting the common electrode; an edge common voltage line connected with the common voltage line and formed along an edge of the display area; and a first common voltage transfer line contacting the edge common voltage line in the peripheral area and configured to transfer a common voltage to the common voltage line.

Owner:SAMSUNG DISPLAY CO LTD

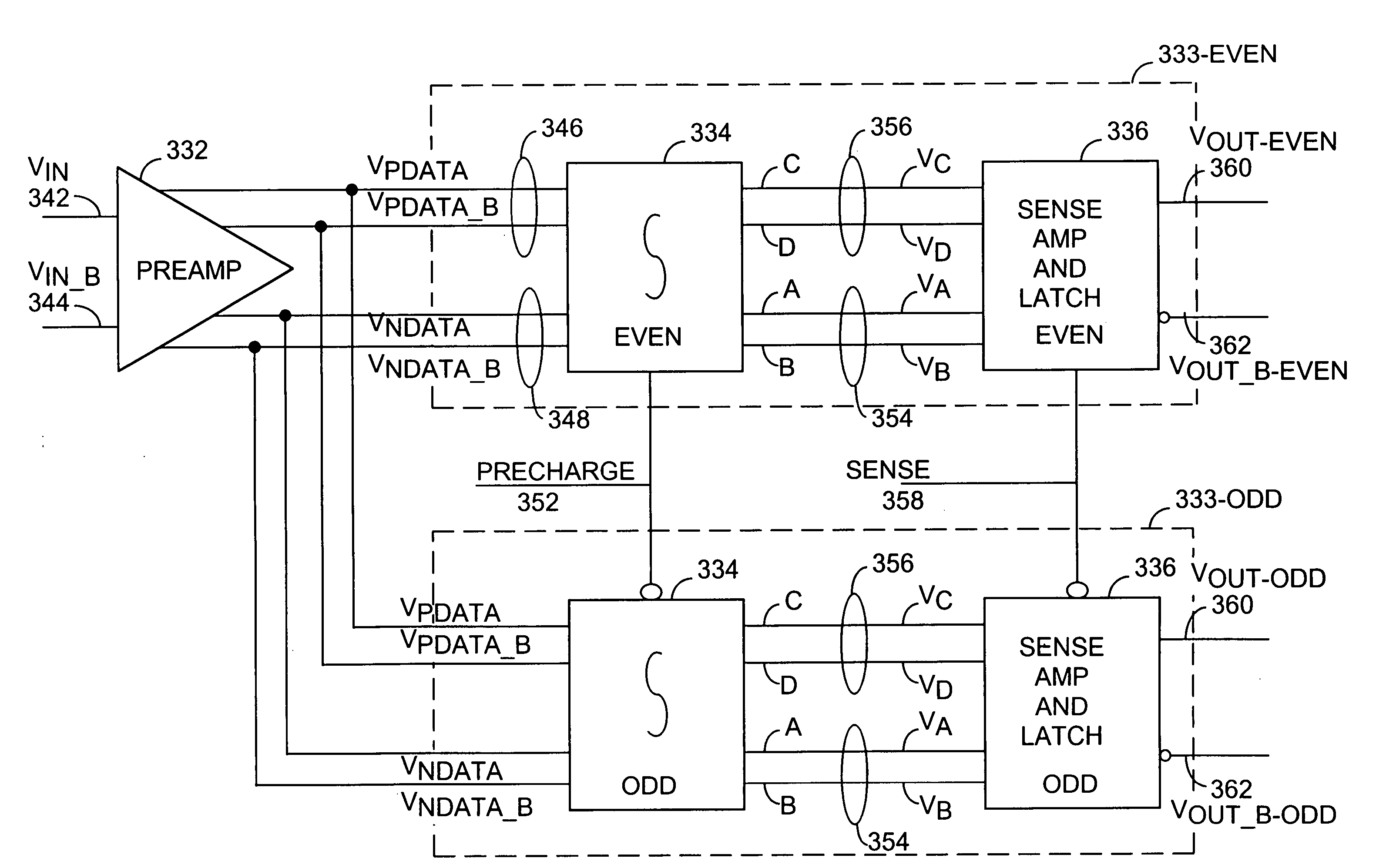

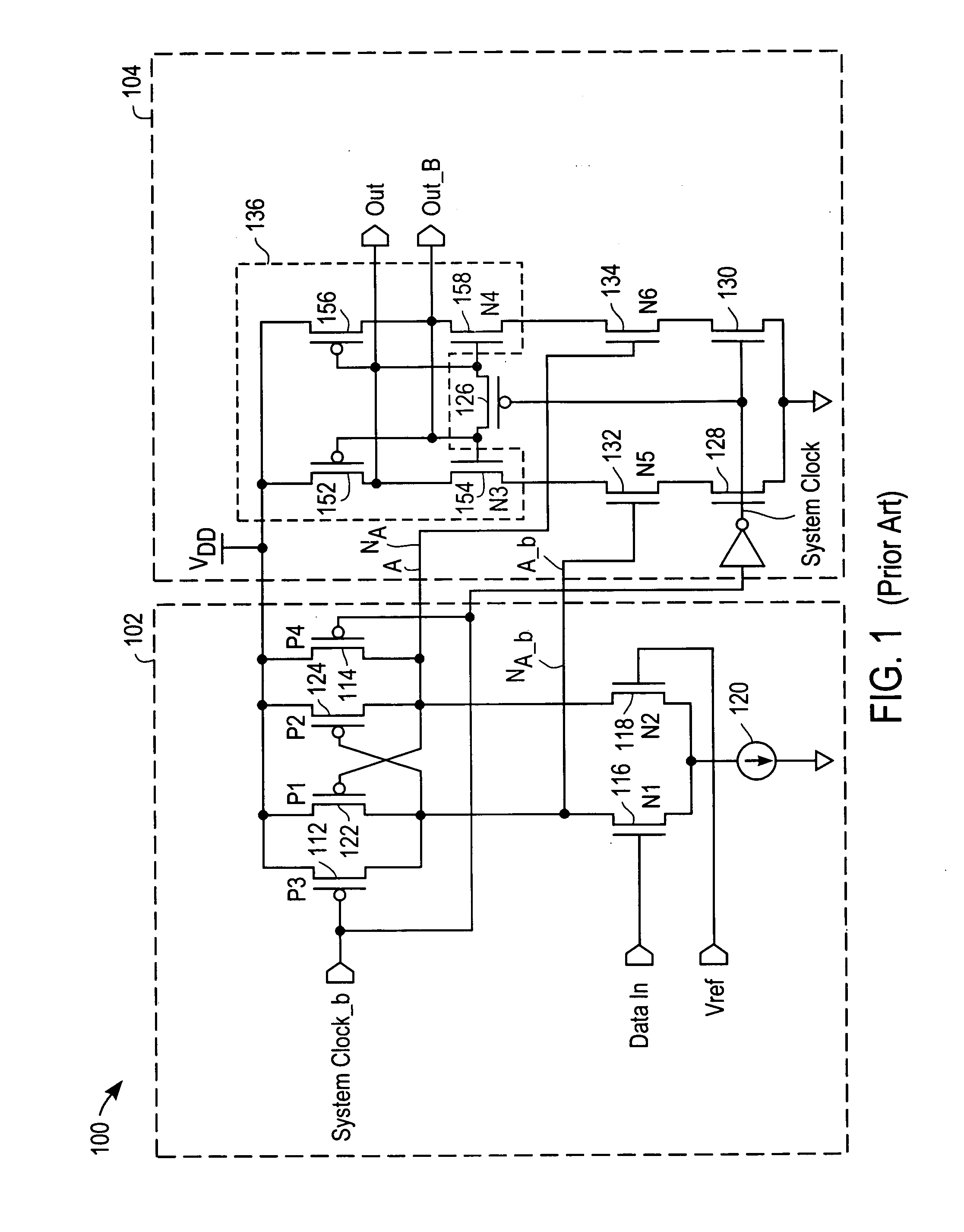

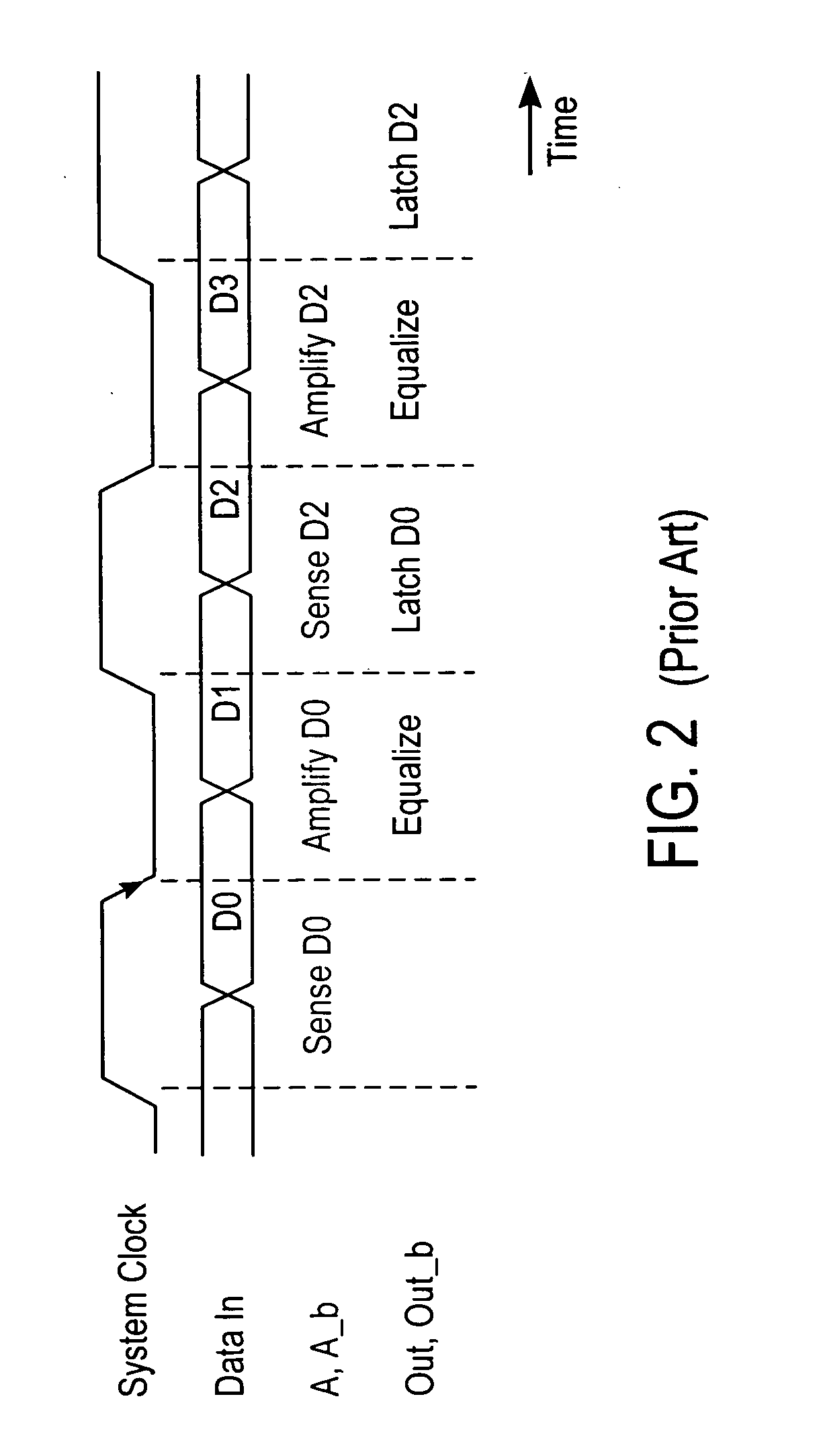

Method and apparatus for receiving high speed signals with low latency

InactiveUS20060061405A1Reduce signal delayDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

Liquid crystal display

ActiveUS20130077008A1Increase the aperture ratioReduce signal delayNon-linear opticsLiquid-crystal displayEngineering

A liquid crystal display in which the common voltage line is disposed directly on or directly under the common electrode directly contacts the common electrode such that a signal delay of the common voltage line may be reduced and simultaneously a reduction in the aperture ratio of the liquid crystal display may be prevented.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

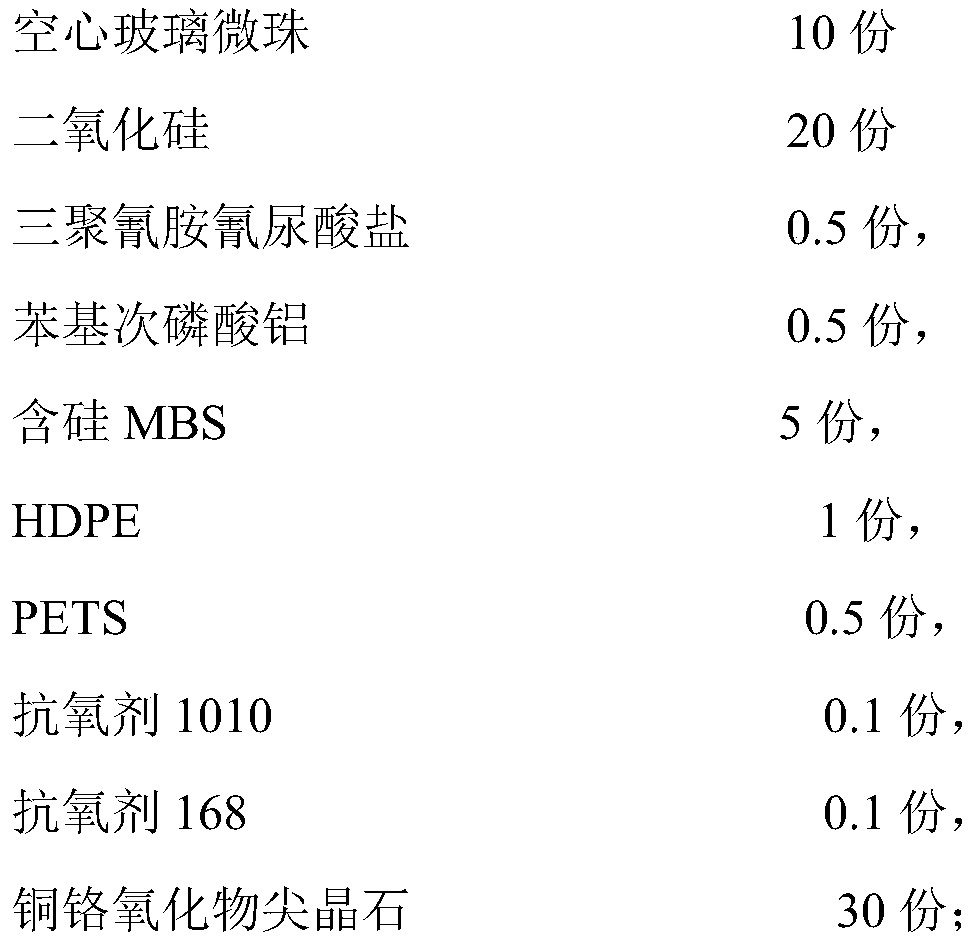

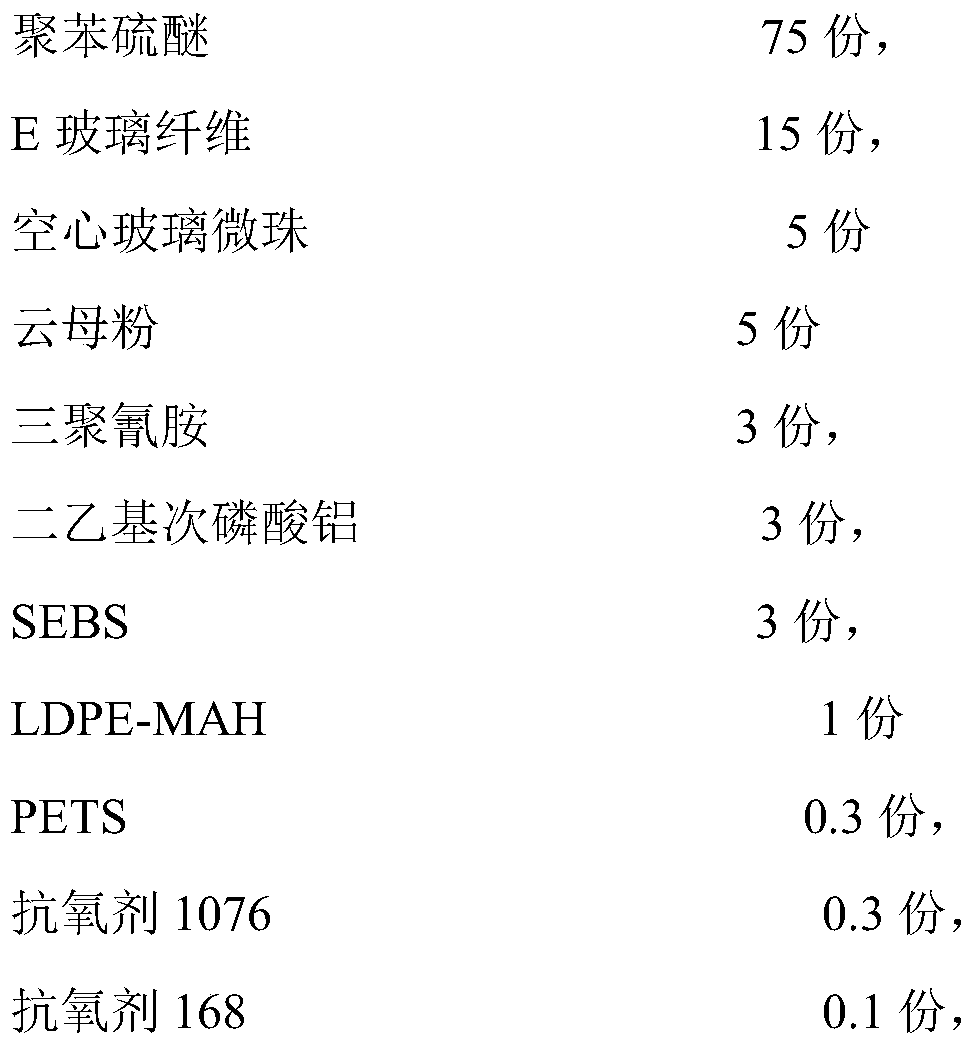

Low-dielectric laser direct structuring composite material suitable for 5G communication and preparation method thereof

ActiveCN110655792ALow dielectric constantHigh heat distortion temperatureChemical platingFire retardant

The invention relates to a low-dielectric laser direct structuring composite material suitable for 5G communication. The composite material is composed of the following components in parts by weight:52 to 86 parts of base resin, 0 to 30 parts of glass fibers, 10 to 30 parts of a filling agent, 1 to 9 parts of a flame retardant, 4 to 15 parts of a toughening agent, 0.1 to 1 part of a lubricating agent, 0.2 to 1 part of an antioxidant and 10 to 30 parts of a laser sensitive additive. A preparation method of the composite material comprises the steps that a twin-screw extruder is used for processing, the melt extrusion temperature is 250-380 DEG C, and the screw rotating speed is 150-300 rpm / min. The composite material has low dielectric property, so that improvement of the transmission speed of 5G communication millimeter wave signals is facilitated, the signal delay is reduced, and the signal loss is reduced; the composite material has the LDS processing capacity, can be rapidly prepared in a small size and a large number, can be subjected to batch laser etching and chemical plating to form a metal connecting circuit, and is an optimal solution of a 5G plastic antenna oscillator material.

Owner:中广核高新核材科技(苏州)有限公司

Package and manufacture method for thermal enhanced quad flat no-lead flip chip

InactiveCN102543907AImprove thermal conductivityImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesFilling materialsHeat conducting

The invention discloses a packaging and manufacturing method for a thermal enhanced quad flat no-lead flip chip. A thermal enhanced quad flat no-lead flip chip package piece structure comprises a lead framework, a first metal material layer, a second metal material layer, IC chips with convex points, an insulating filler material, a sticking material, radiating fins, heat conducting spacers and a plastic package material, wherein the lead framework comprises a chip carrier and a plurality of pins arranged in multiple circles around the chip carrier; the first metal material layer and the second metal material layer are respectively configured on the upper surface and the lower surface of the lead framework; the IC chips with the convex points are invertedly welded and configured at the position of the first metal material on the upper surface of the lead framework; the insulating filler material is configured below the stepped structure of the lead framework; the heat conducting spacers are configured between the IC chips and the chip carrier through the sticking material; and the radiating fins are configured on the edgeless surfaces of the IC chips through the sticking material and wrapped by the plastic package material to form a package piece. The QFN (Quad Flat No-lead) package piece structure provided by the invention has the advantages of high reliability, low cost and high I / O (Input / Output) density.

Owner:BEIJING UNIV OF TECH

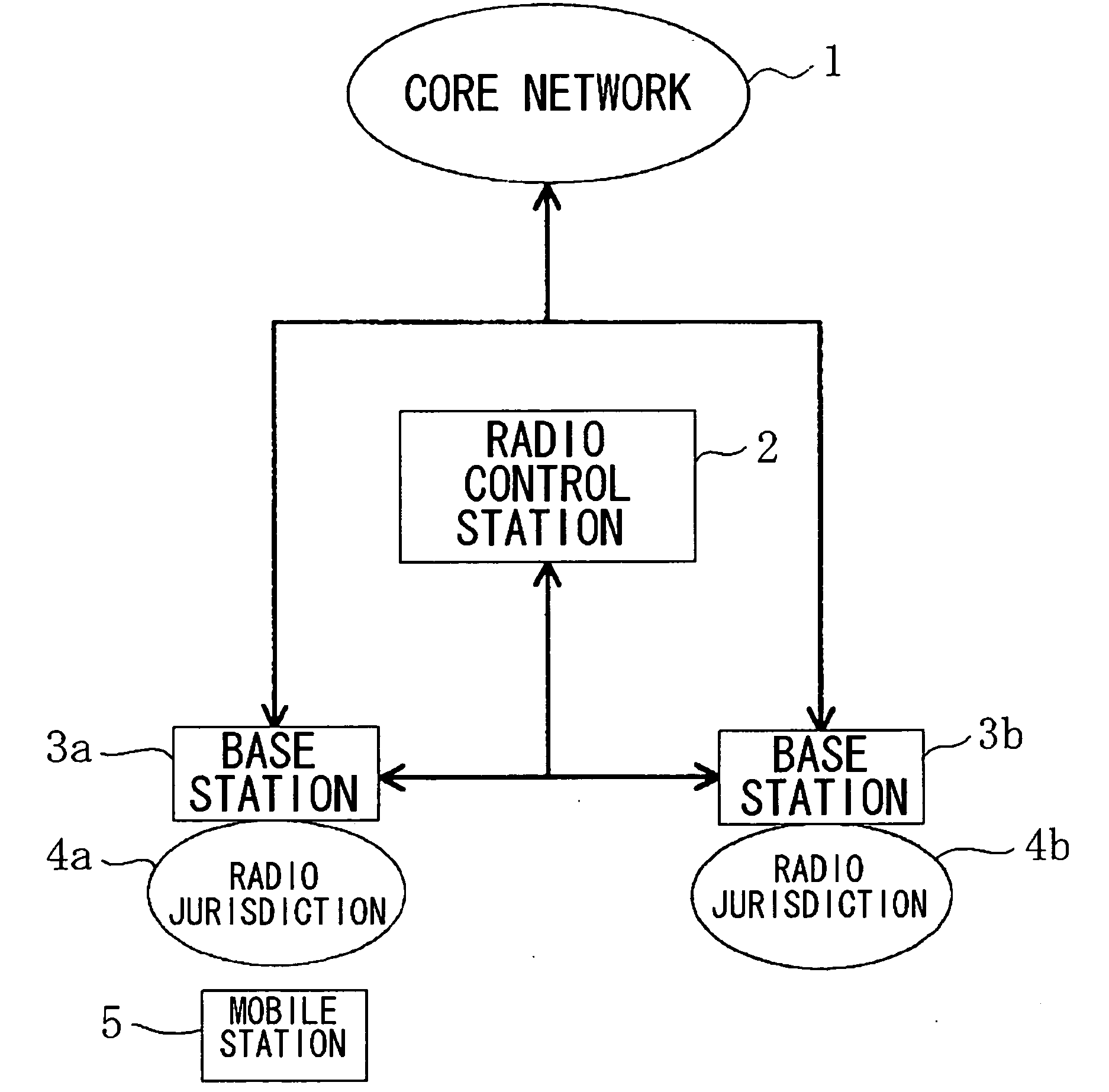

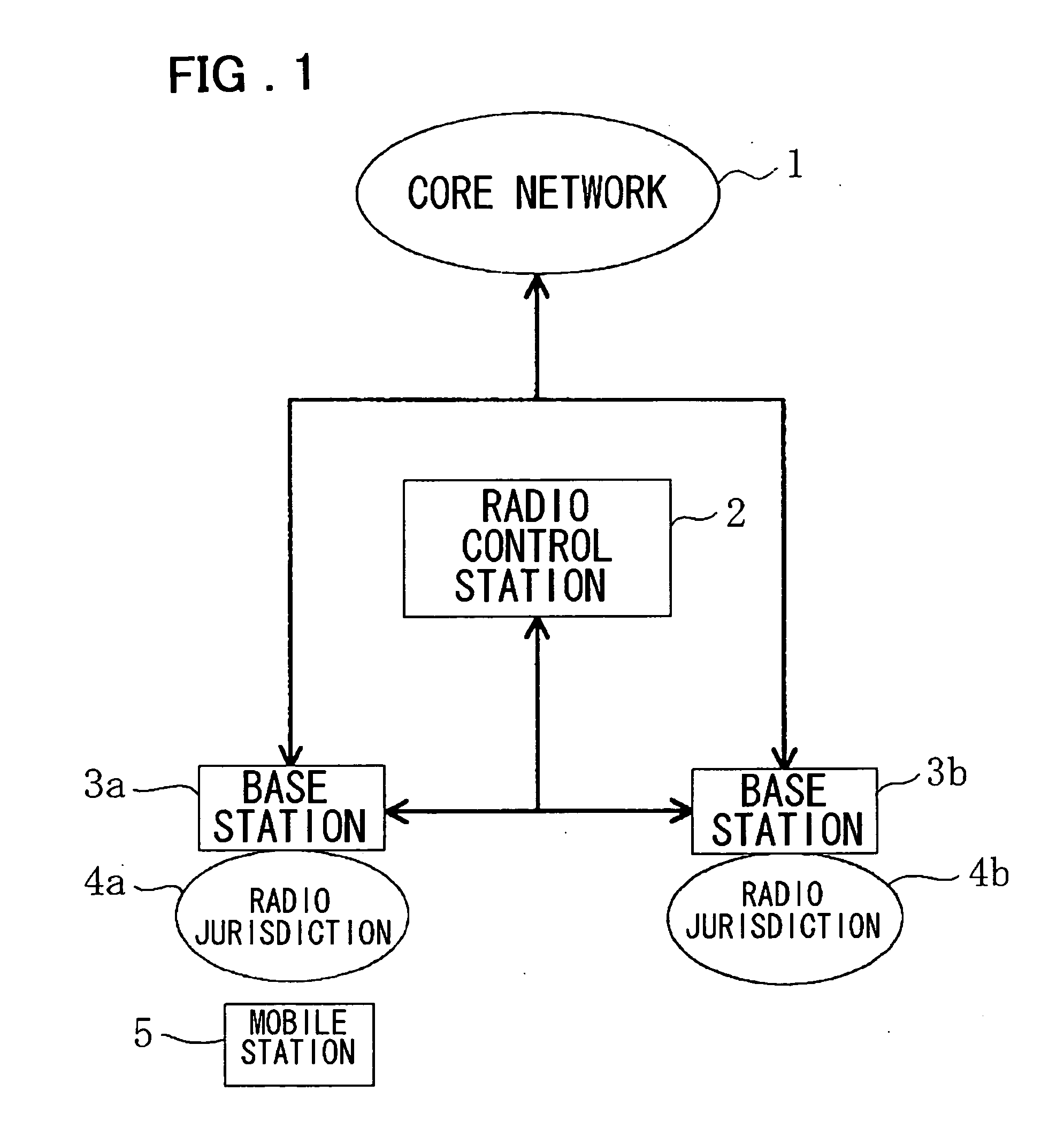

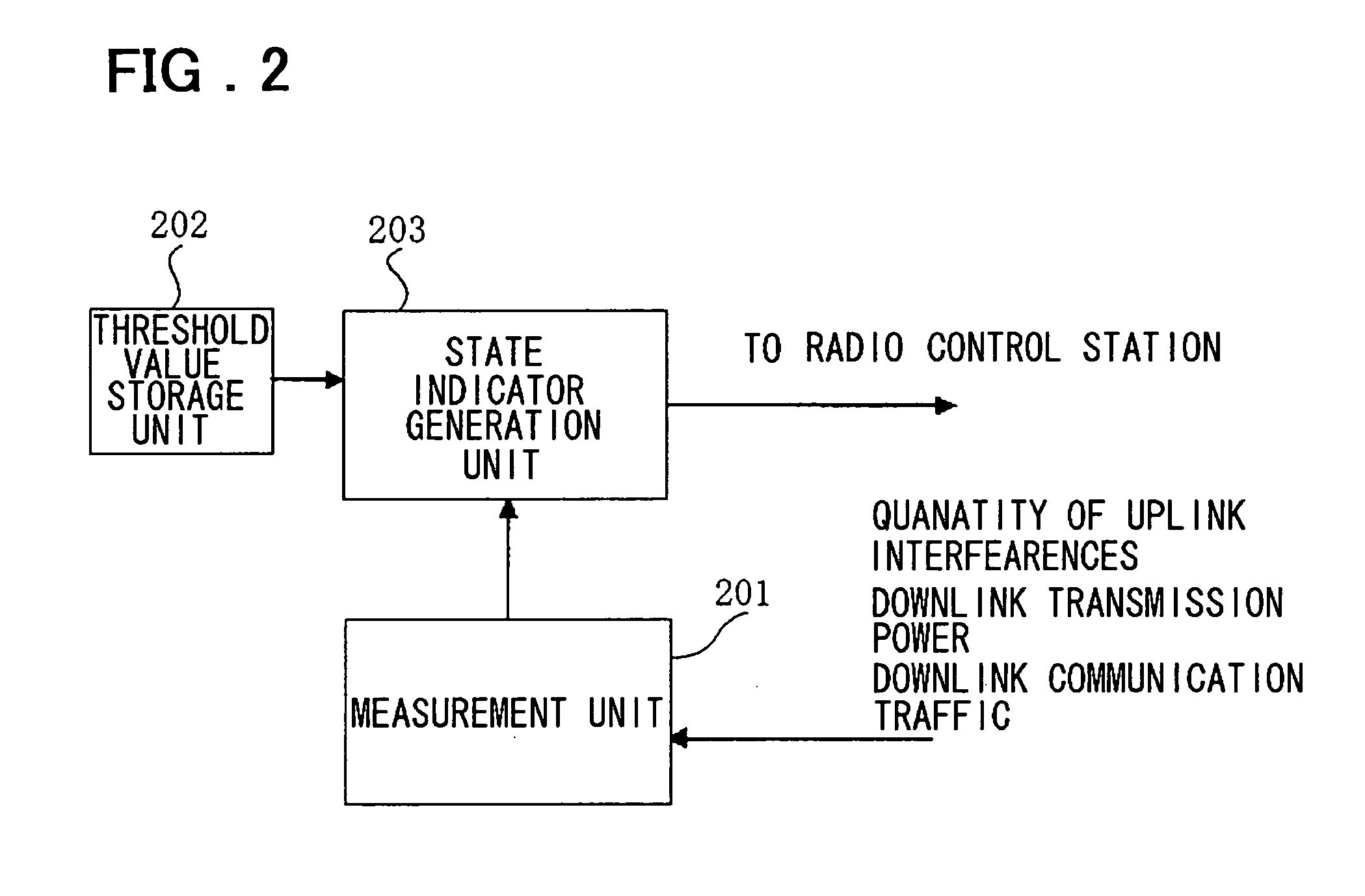

Mobile communication system and access control method

InactiveUS20070037581A1Reduce processing loadReduce signal delayNetwork traffic/resource managementRadio/inductive link selection arrangementsCommunications systemControl signal

A mobile communication system includes a mobile station (5) connected to a core network (1) through a communication line intervened by a base station (3a), and a radio control station (2) configured for controlling the setting of a radio link for the mobile station (5) in the base station (3a). The base station (3a) monitors the congested state of the communication line, generates a state indicator indicating the congested state / non-congested state of the communication line, based on the results of monitoring, and transmits the state indicator generated to the radio control station (2). The radio control station (2) recognizes the current state of the communication line based on the state indicator received from the base station (3a). When the radio control station (2) recognizes that the communication line is in the congested state and receives a line connection request from the mobile station (5), the control station (2) transmits a control signal for refusing the line connection request received to the mobile station (5) without performing control for setting the radio link.

Owner:NEC CORP

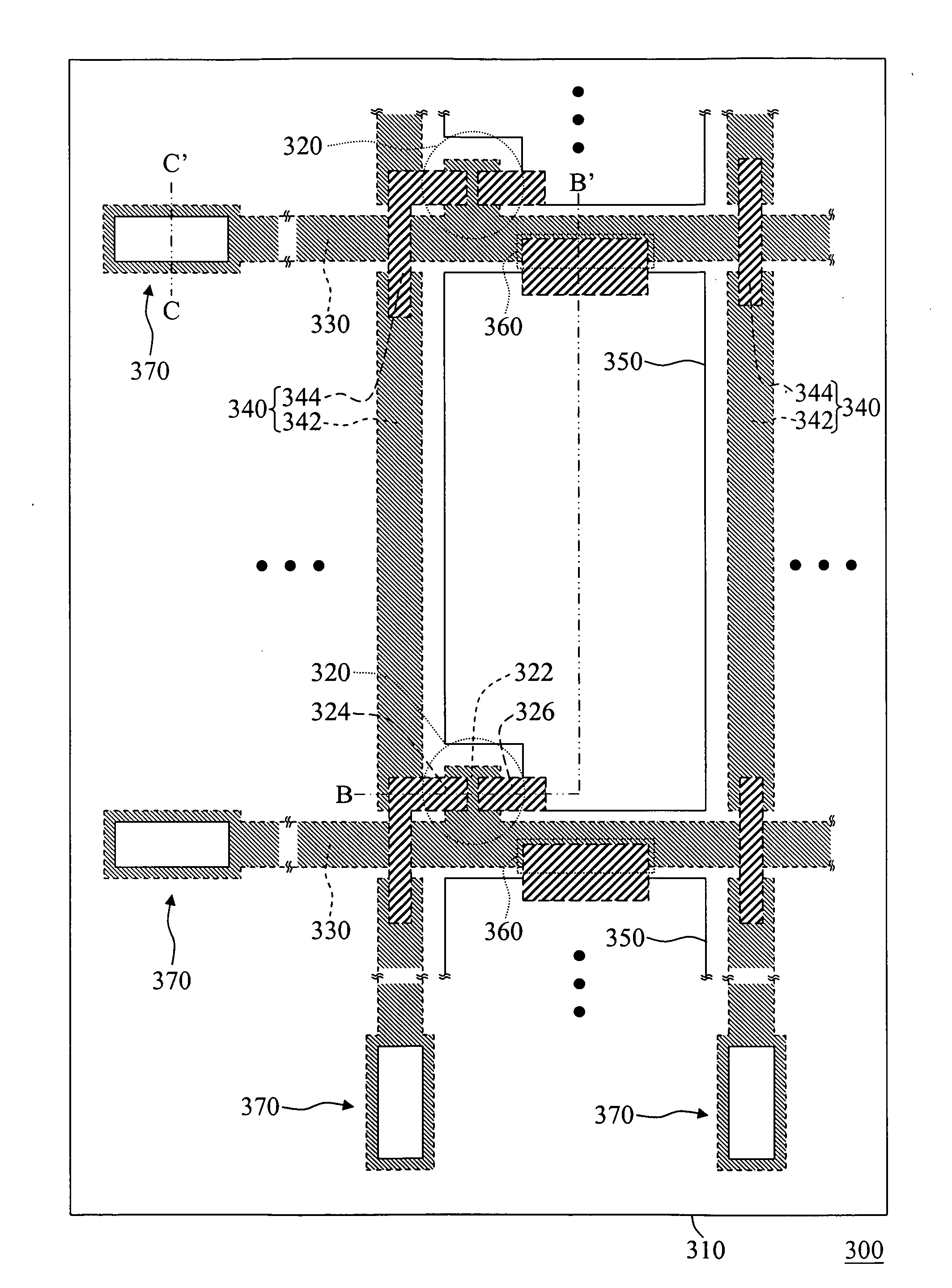

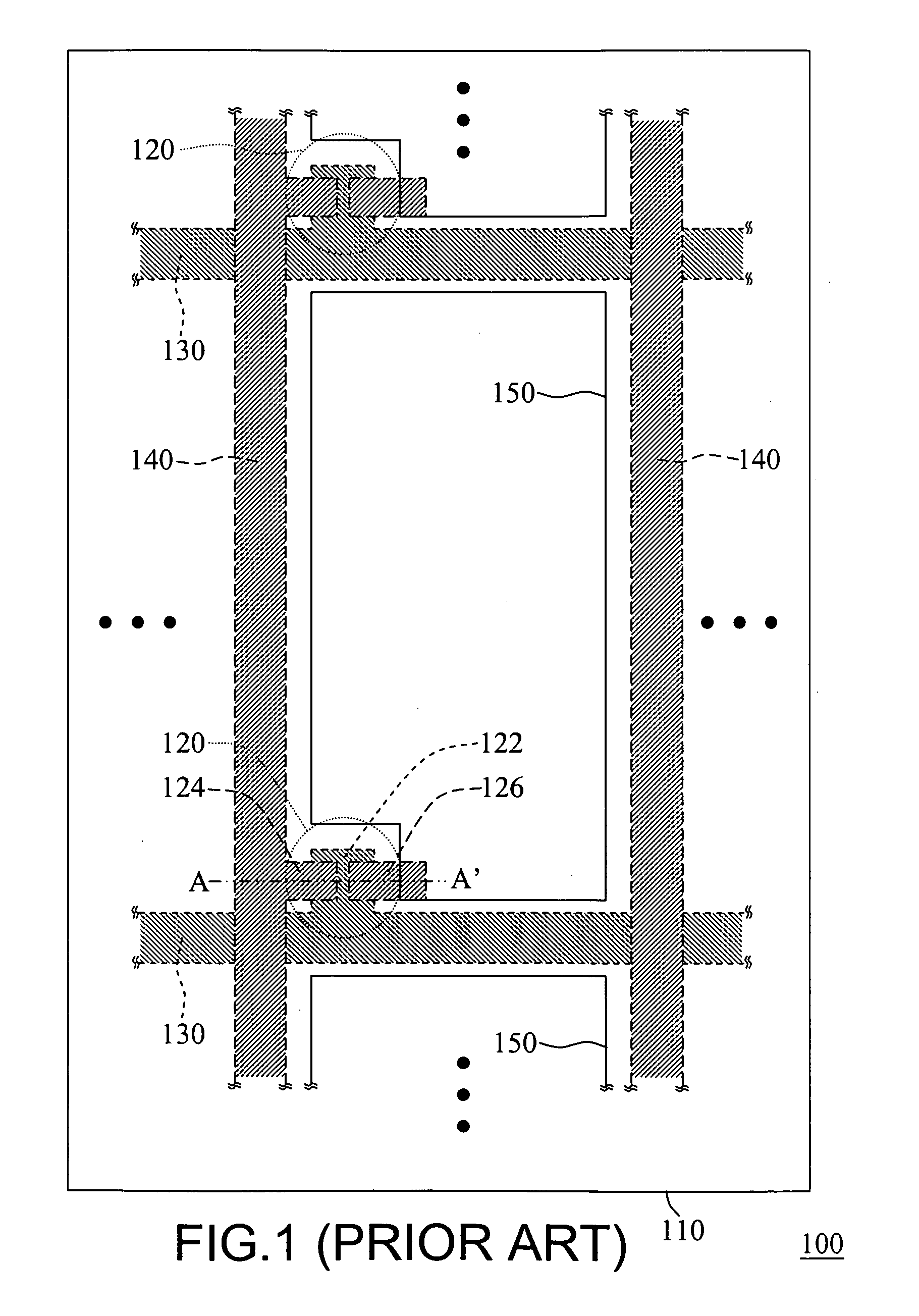

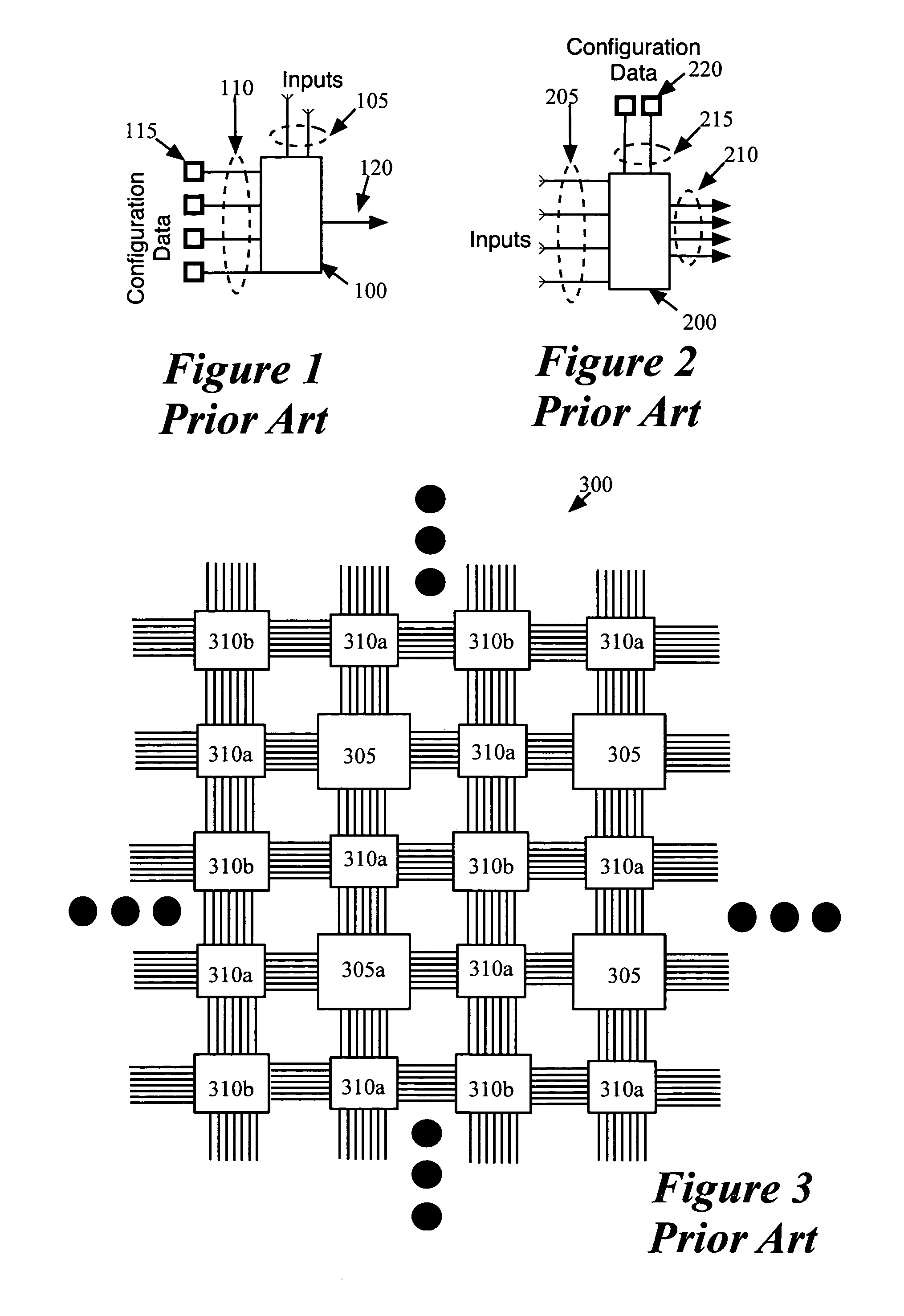

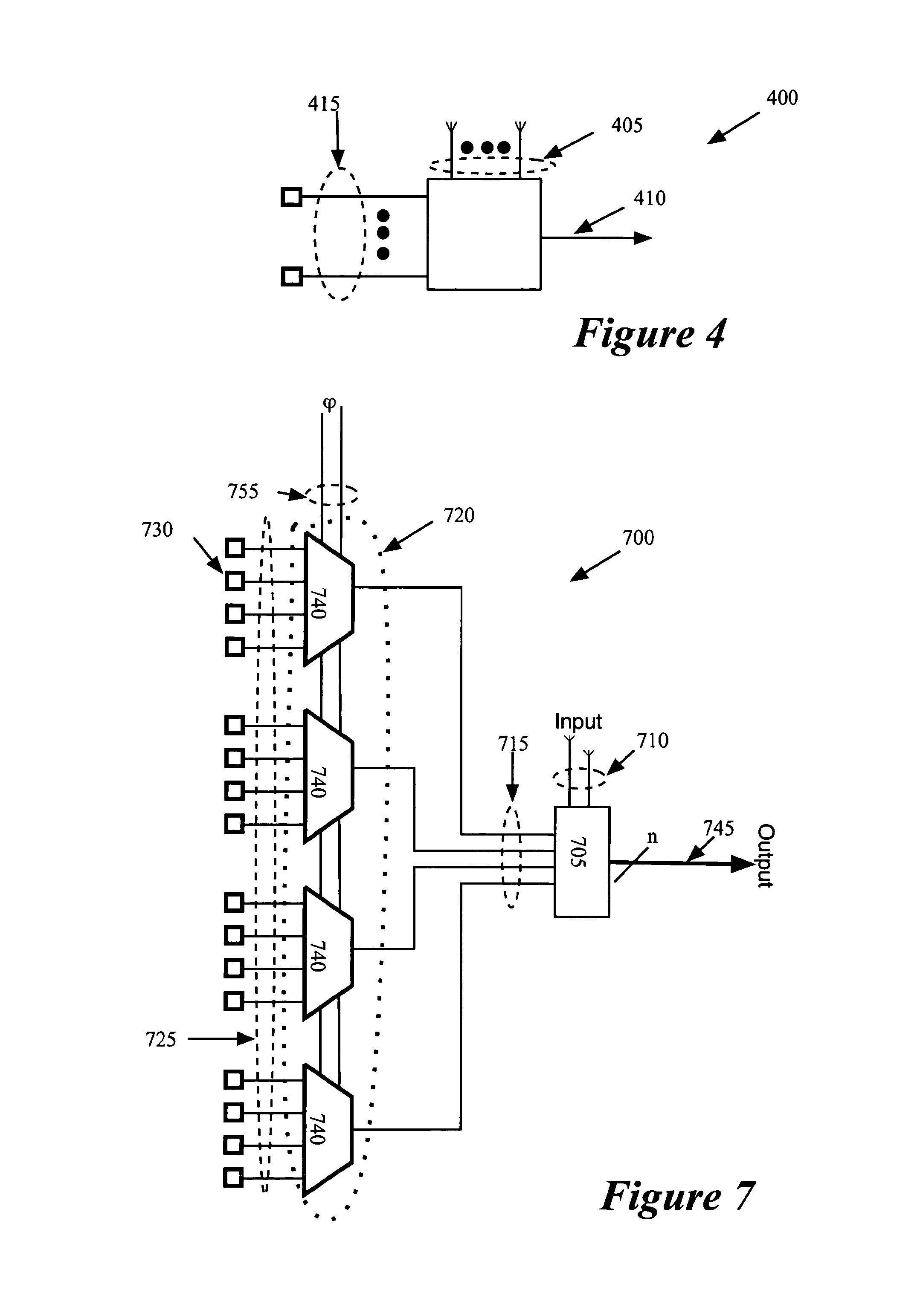

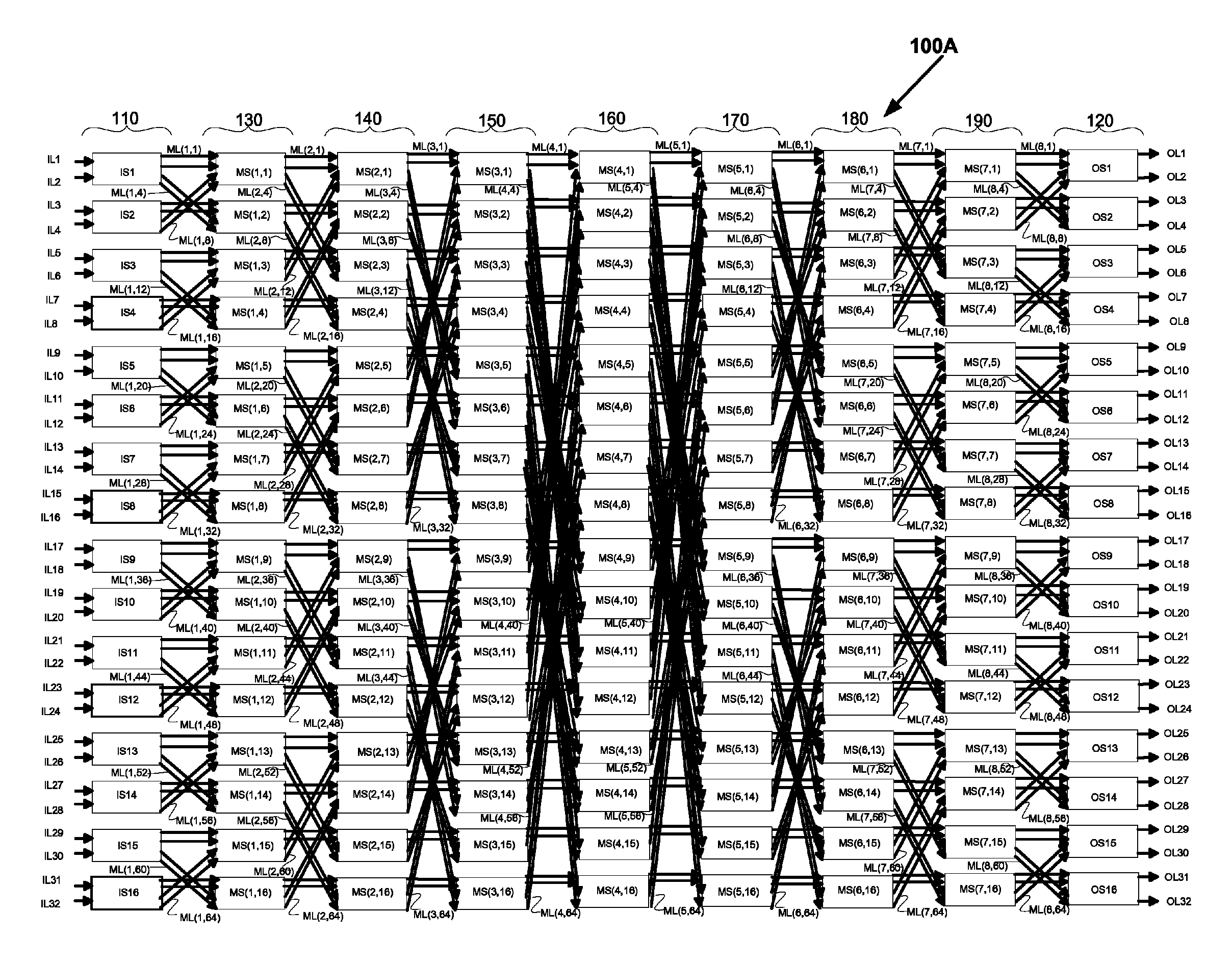

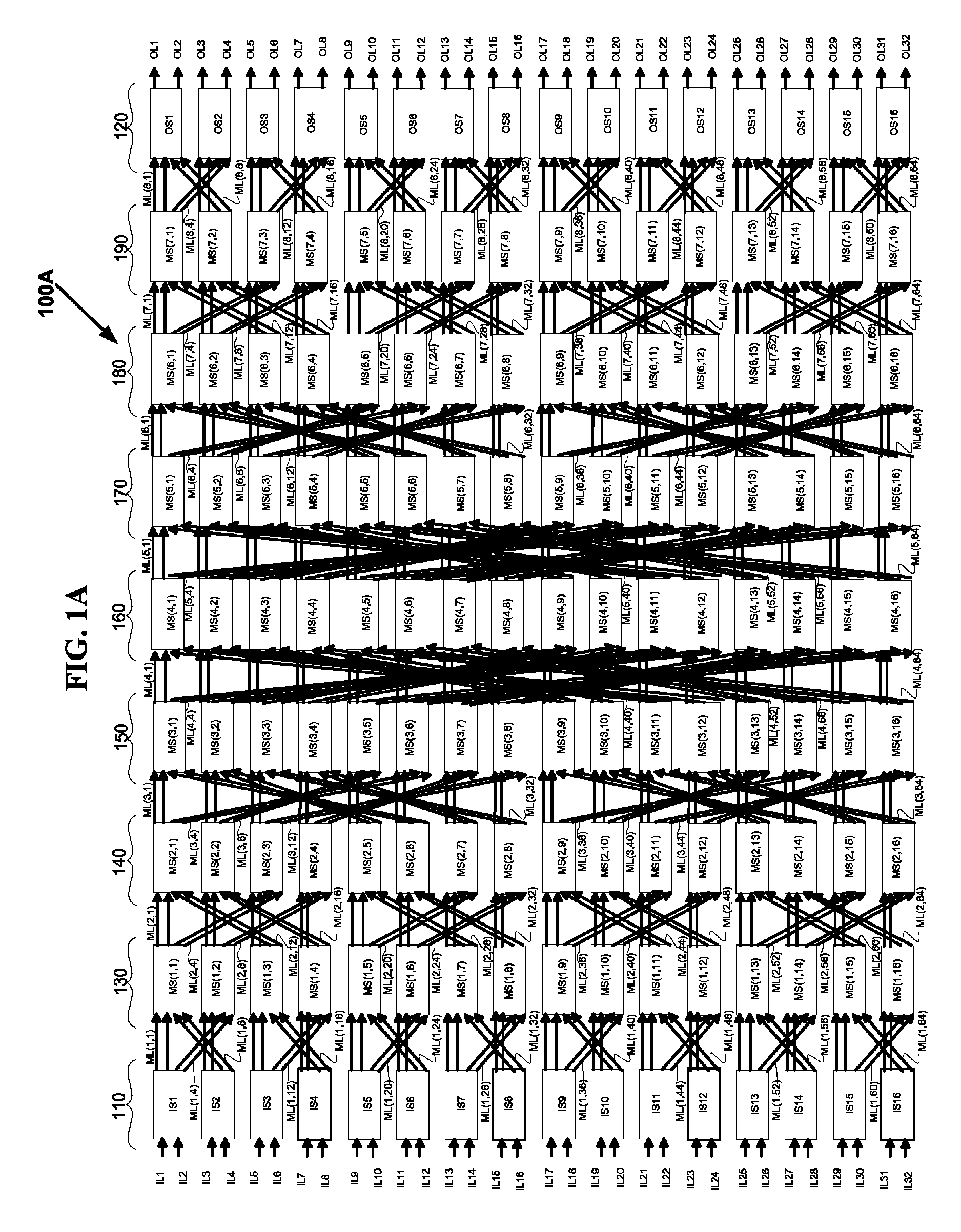

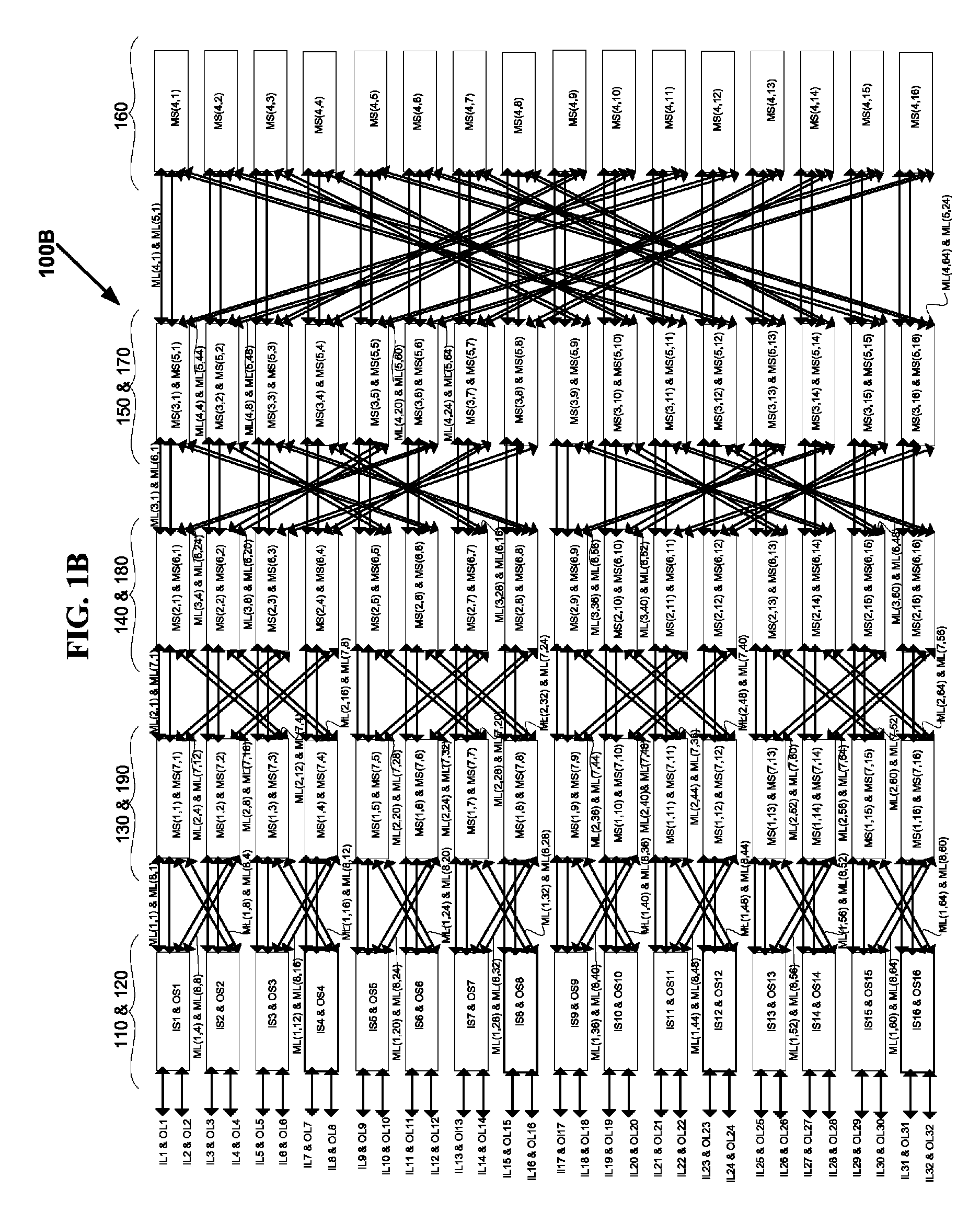

VLSI layouts of fully connected generalized and pyramid networks with locality exploitation

ActiveUS8898611B2Low pour pointReduce signal delayMultiplex system selection arrangementsGeometric CADCross-linkMulti link

VLSI layouts of generalized multi-stage and pyramid networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links with spacial locality exploitation. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. Furthermore the shuffle exchange links are employed between different sub-integrated circuit blocks so that spacially nearer sub-integrated circuit blocks are connected with shorter links compared to the shuffle exchange links between spacially farther sub-integrated circuit blocks. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.The VLSI layouts with spacial locality exploitation presented are applicable to generalized multi-stage and pyramid networks, generalized folded multi-stage and pyramid networks, generalized butterfly fat tree and pyramid networks, generalized multi-link multi-stage and pyramid networks, generalized folded multi-link multi-stage and pyramid networks, generalized multi-link butterfly fat tree and pyramid networks, generalized hypercube networks, and generalized cube connected cycles networks for speedup of s≧1. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

Owner:KONDA TECH

LCD device and method for producing the same

InactiveCN101430463AImprove efficiencyIncrease opening ratioStatic indicating devicesSemiconductor/solid-state device detailsCapacitanceOrganic film

The invention relates to a liquid crystal display device and a manufacture method thereof. The liquid crystal display device comprises a glass basic board as well as a grid scanning line layer, an insulating layer, a data line layer, a memory capacitance and a pixel electrode layer which are formed on the glass basic layer in sequence; wherein, the insulating layer is formed by overlapping an inorganic film and an organic film or an inorganic film with low specific inductive capacity or an organic film with low specific inductive capacity. The liquid crystal display device and a manufacture method thereof can improve the aperture opening ratio thereof, and reduce the signal delay of the data line or the grid scanning line.

Owner:SHANGHAI SVA LIQUID CRYSTAL DISPLAY

Semiconductor device and chip-stack semiconductor device

InactiveUS20060231928A1Delayed deteriorationReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesSignal routingElectrical resistance and conductance

A semiconductor device has multiple power-supply through electrodes, grounding through electrodes, and signal-routing through electrodes made through a semiconductor chip. The power-supply through electrodes, the grounding through electrodes, and the signal-routing through electrodes differ mutually in cross-sectional area. Hence, a semiconductor device and a chip-stack semiconductor device are provided which are capable of preventing the electrodes' resistance from developing excessive voltage drop, heat, delay, and loss, and also from varying from one electrode to the other.

Owner:SAMSUNG ELECTRONICS CO LTD

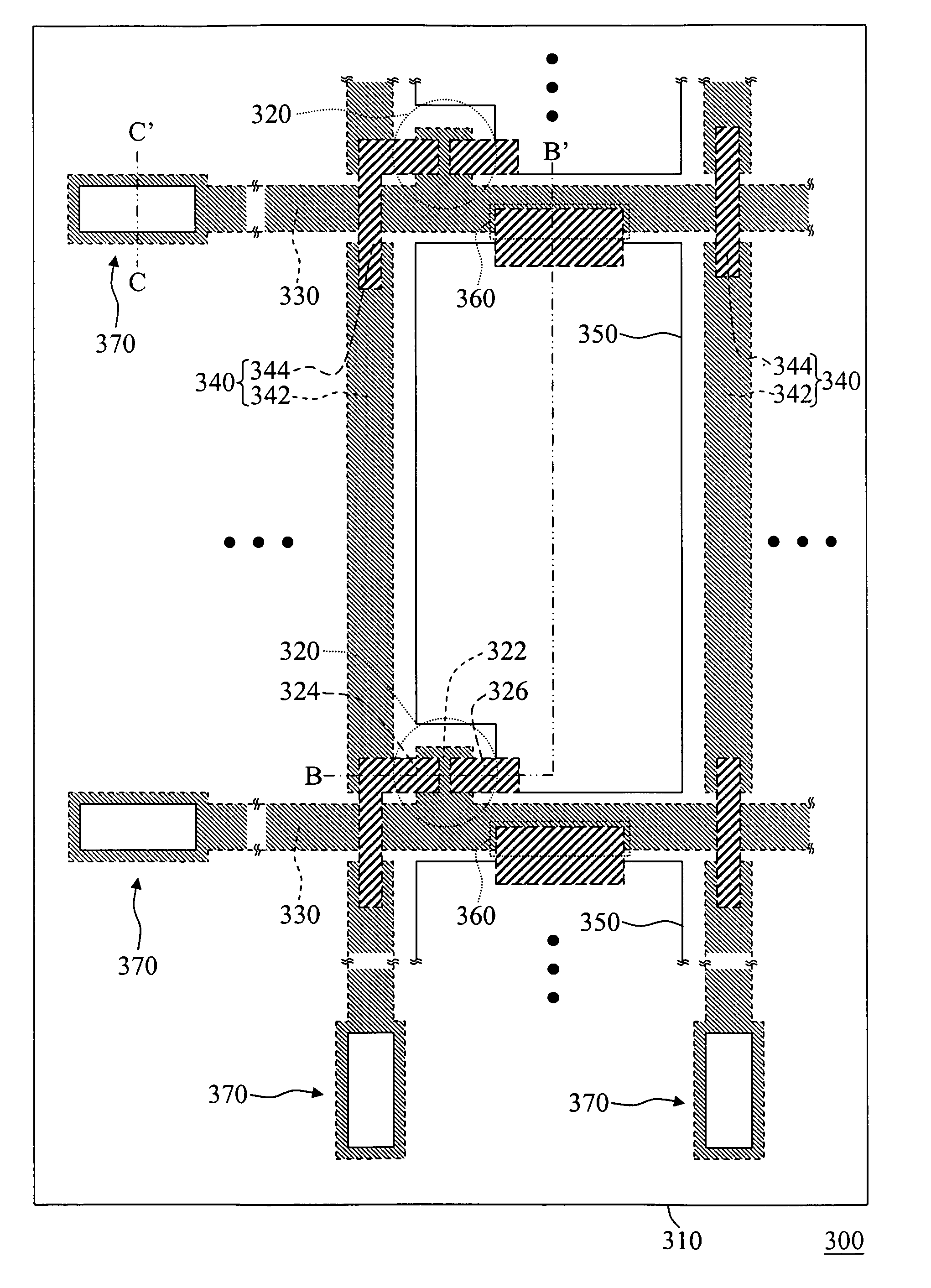

Method for fabricating pixel array substrate

A method for fabricating a pixel array substrate is provided. The method includes: forming a plurality of gate electrodes, a plurality of scan lines, a plurality of data line patterns and a plurality of pixel electrode patterns on a substrate; then forming a channel over each of the gate electrodes and a plurality of contact window openings for exposing the data line patterns; then forming a plurality of contact windows electrically connected with the data line patterns; and then forming a plurality of contacting portions which are electrically connected with the contact windows, a plurality of source electrodes which are electrically connected with the data line patterns, and a plurality of drain electrodes which are electrically connected with the pixel electrodes. The data line patterns at each column are electrically connecting with each other via the contacting portions and the contact windows so as to form a data line.

Owner:AU OPTRONICS CORP

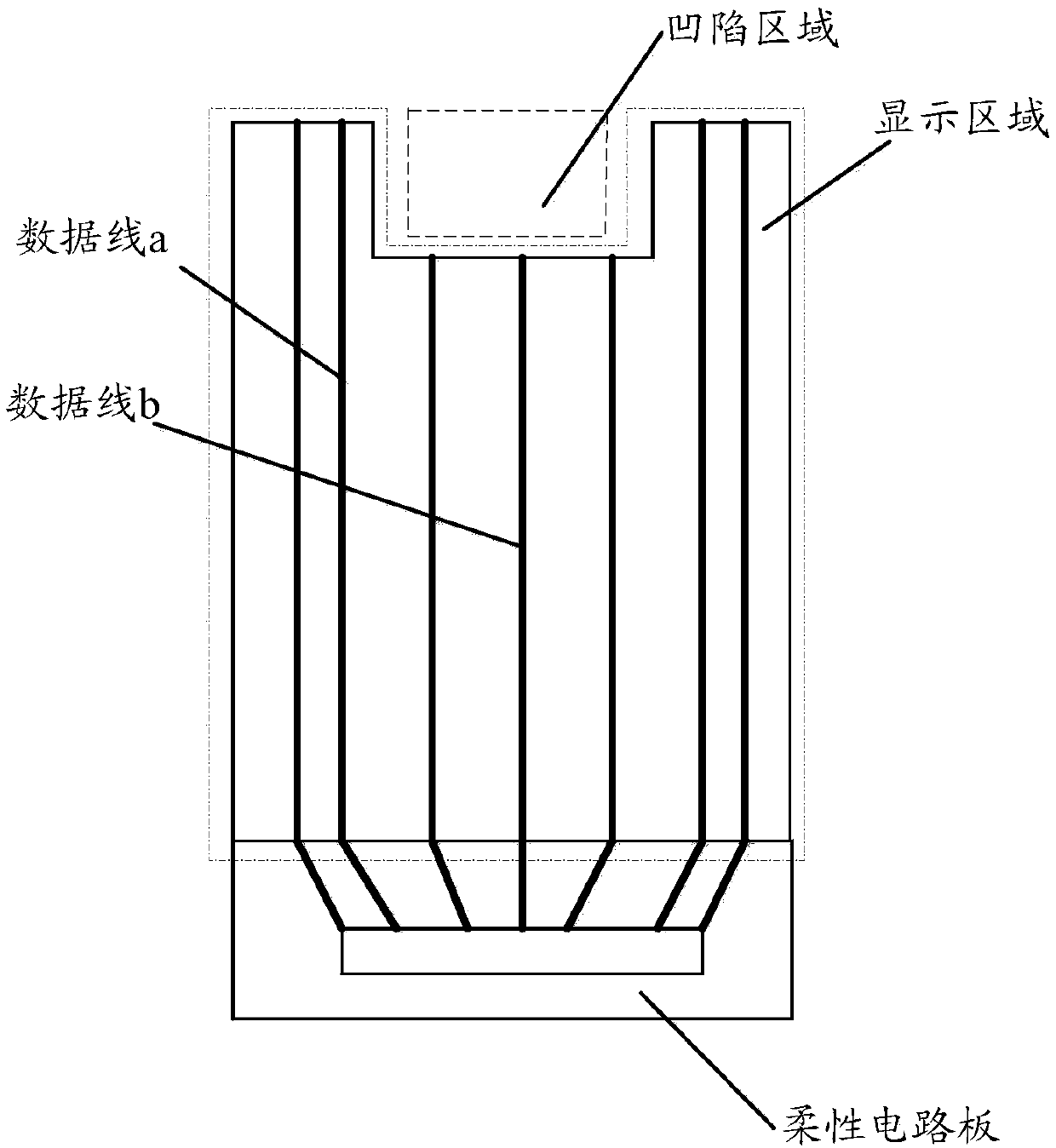

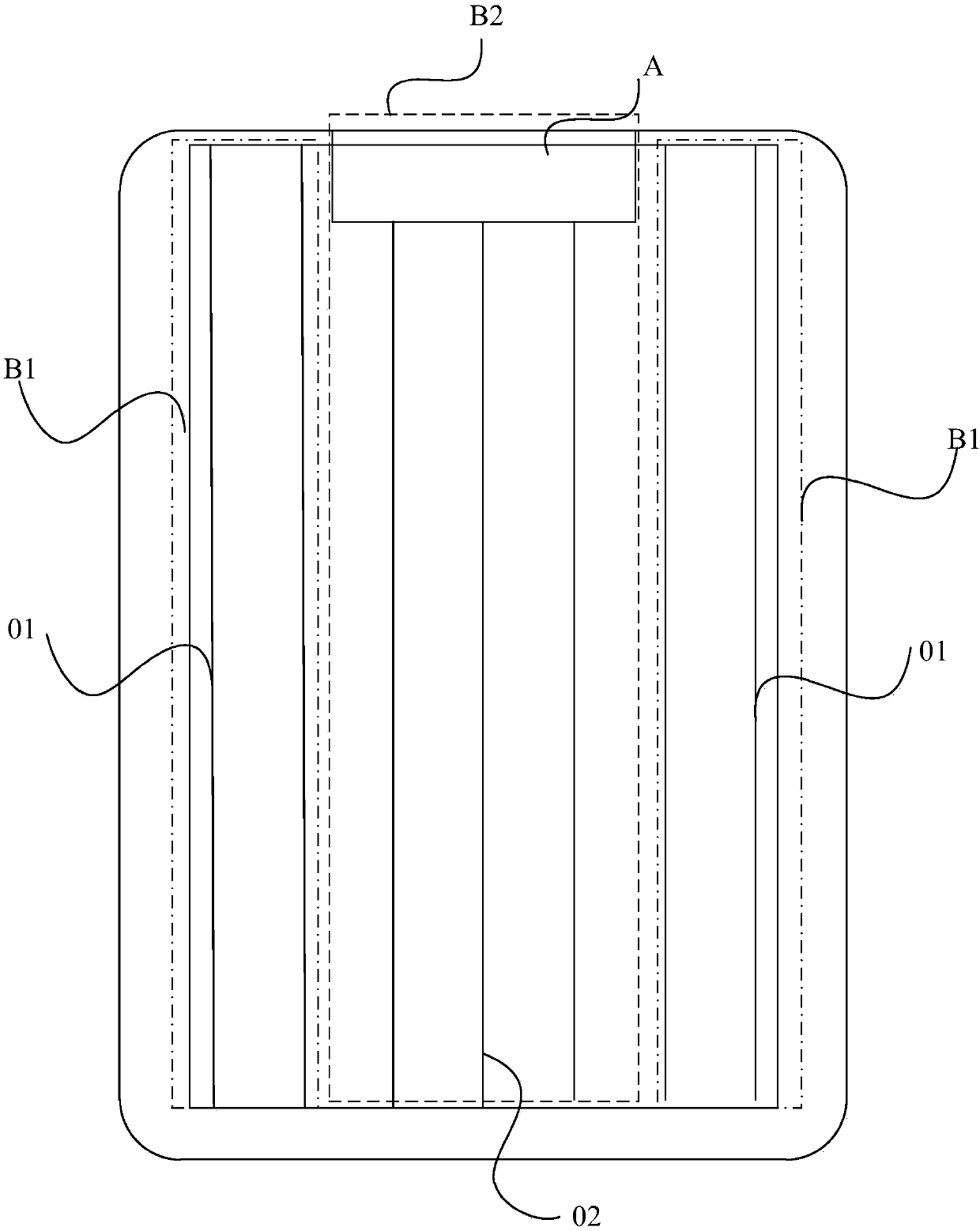

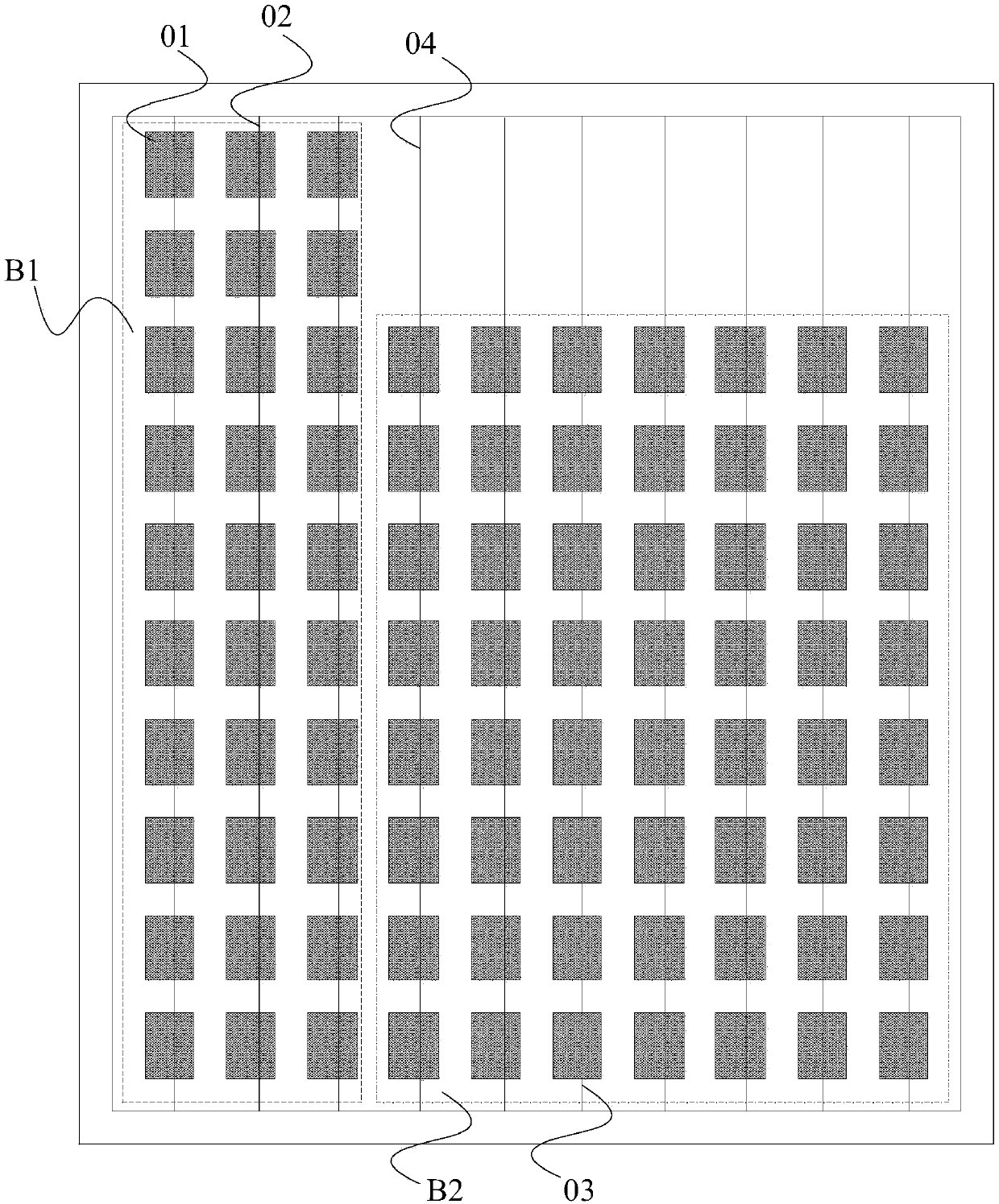

Display panel and display apparatus

ActiveCN107680995AMake up for the length differenceImprove loadingSolid-state devicesSemiconductor devicesElectricityTime delays

The invention discloses a display panel and a display apparatus. A display region of the display panel comprises multiple columns of pixels; the display region is divided into a second display regionand a first display region; the number of the pixels in one column in the second display region is less than that of the pixels in one column in the first display region; first data lines connected with the pixels in each column are arranged in the first display region; second data lines connected with the pixels in each column are arranged in the second display region; in the column direction, the length of the first data lines is longer than that of the second data lines; and the display panel also comprises third data lines which are in one-to-one correspondence to the second data lines andare electrically connected therewith. By virtue of addition of the third data lines electrically connected with the second data lines in the embodiment, the length difference between the first data lines and the second data lines is overcome; and in signal transmission, the loading of the first data lines and the second data lines can be improved, and the signal time delay between the first datalines and the second data lines can be lowered.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

Copper pillar tin bump on semiconductor chip and method of forming the same

InactiveUS20090127708A1High-density packagingHigh densitySemiconductor/solid-state device detailsSolid-state devicesResistSemiconductor chip

Copper pillar tin bump on semiconductor chip comprises a copper layer composed on chip and a tin layer entirely wrapping whole outer surface of said copper layer. A method for forming of the copper pillar tin bump on semiconductor chip comprises: composing the first copper layer on said chip; applying photoresist to said first copper layer, exposing and developing a part of said photoresist, composing the copper pillar layer at the developed part of photoresist, composing the upper tin layer, removing said photoresist, removing said the first copper layer except disposing place of copper pillar layer, composing side tin layer. The minute pattern makes it possible to form a high density packaging by reducing a pitch of copper pillar tin bump. Signal delay can be reduced by low electric resistance, and underfill can be easily soaked.

Owner:HWABEAK ENG