Patents

Literature

3567 results about "Transfer line" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A transfer line is a manufacturing system which consists of a predetermined sequence of machines connected by an automated material handling system and designed for working on a very small family of parts. Parts can be moved singularly because there’s no need for batching when carrying parts between process stations (as opposed to a job shop for example). The line can synchronous, meaning that all parts advance with the same speed, or asynchronous, meaning buffers exist between stations where parts wait to be processed. Not all transfer lines must geometrically be straight lines, for example circular solutions have been developed which make use rotary tables, however using buffers becomes almost impossible.

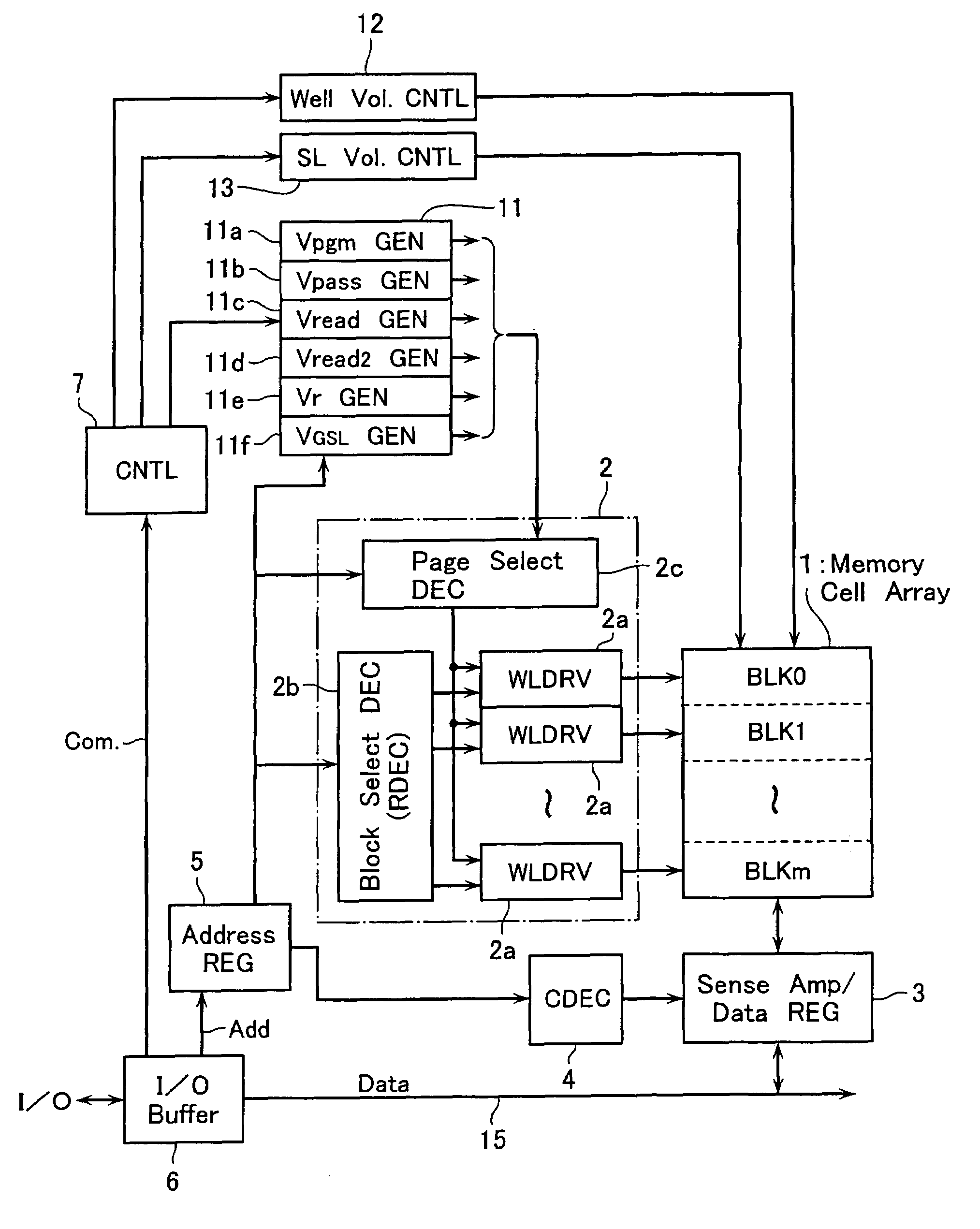

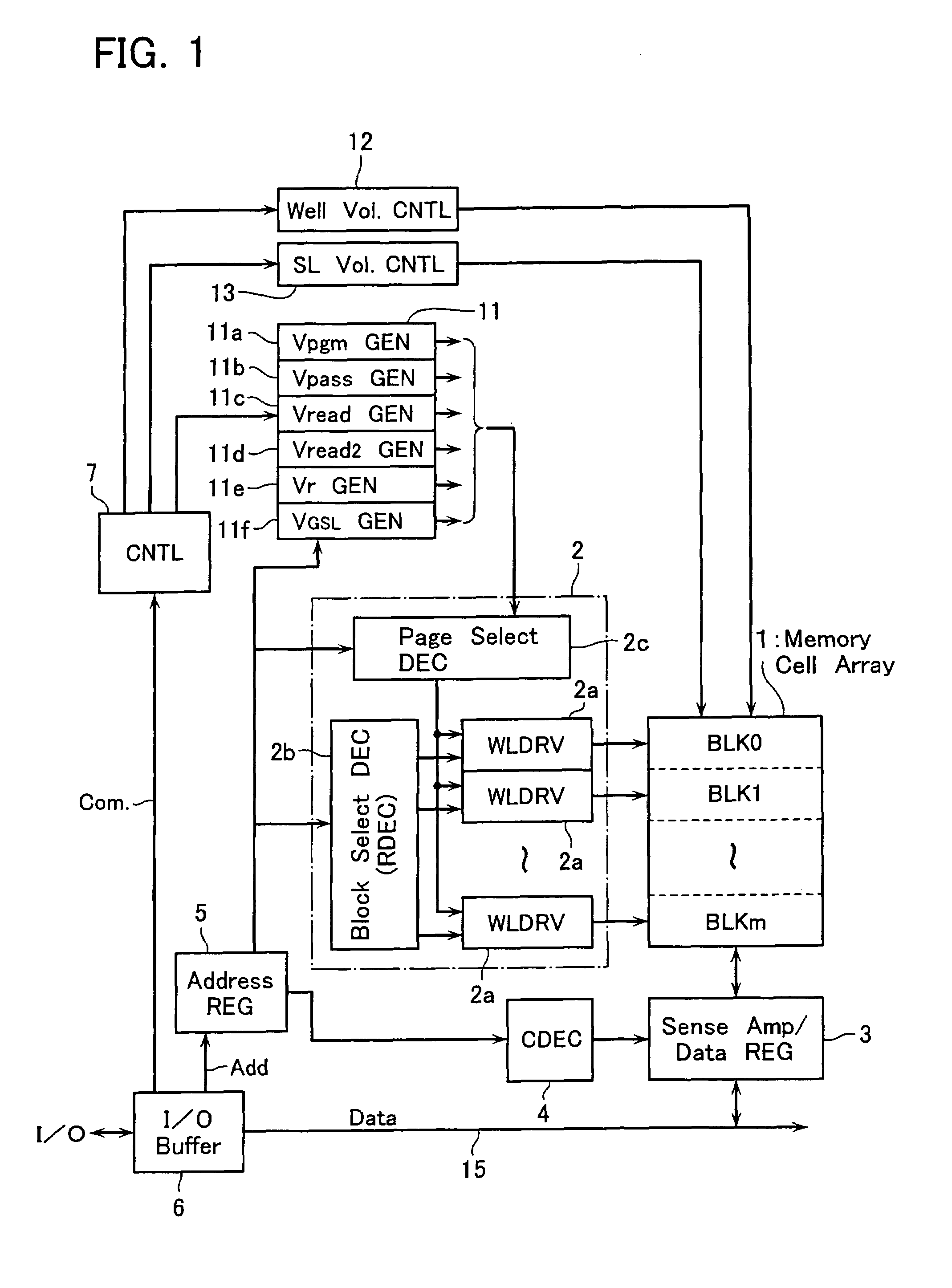

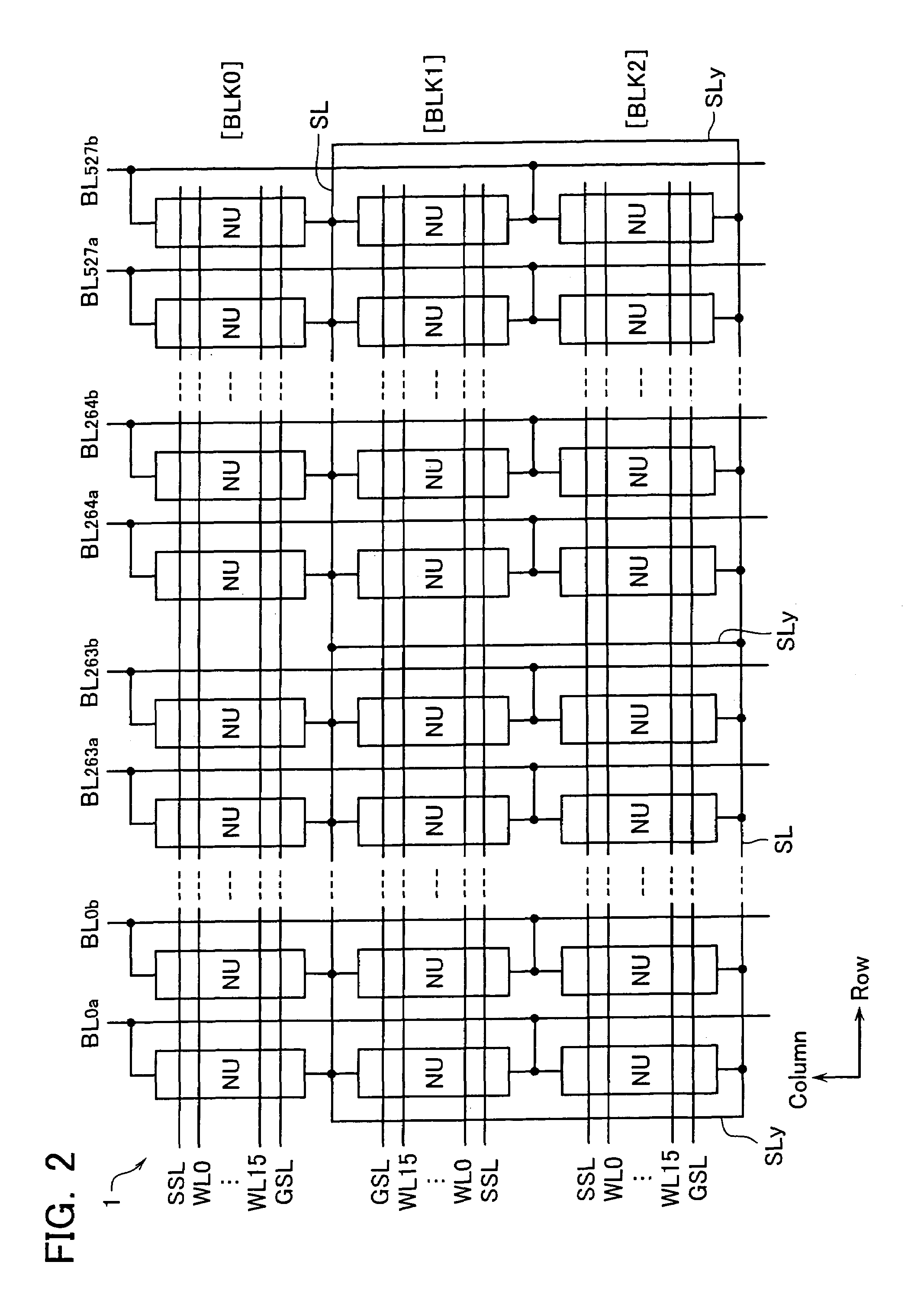

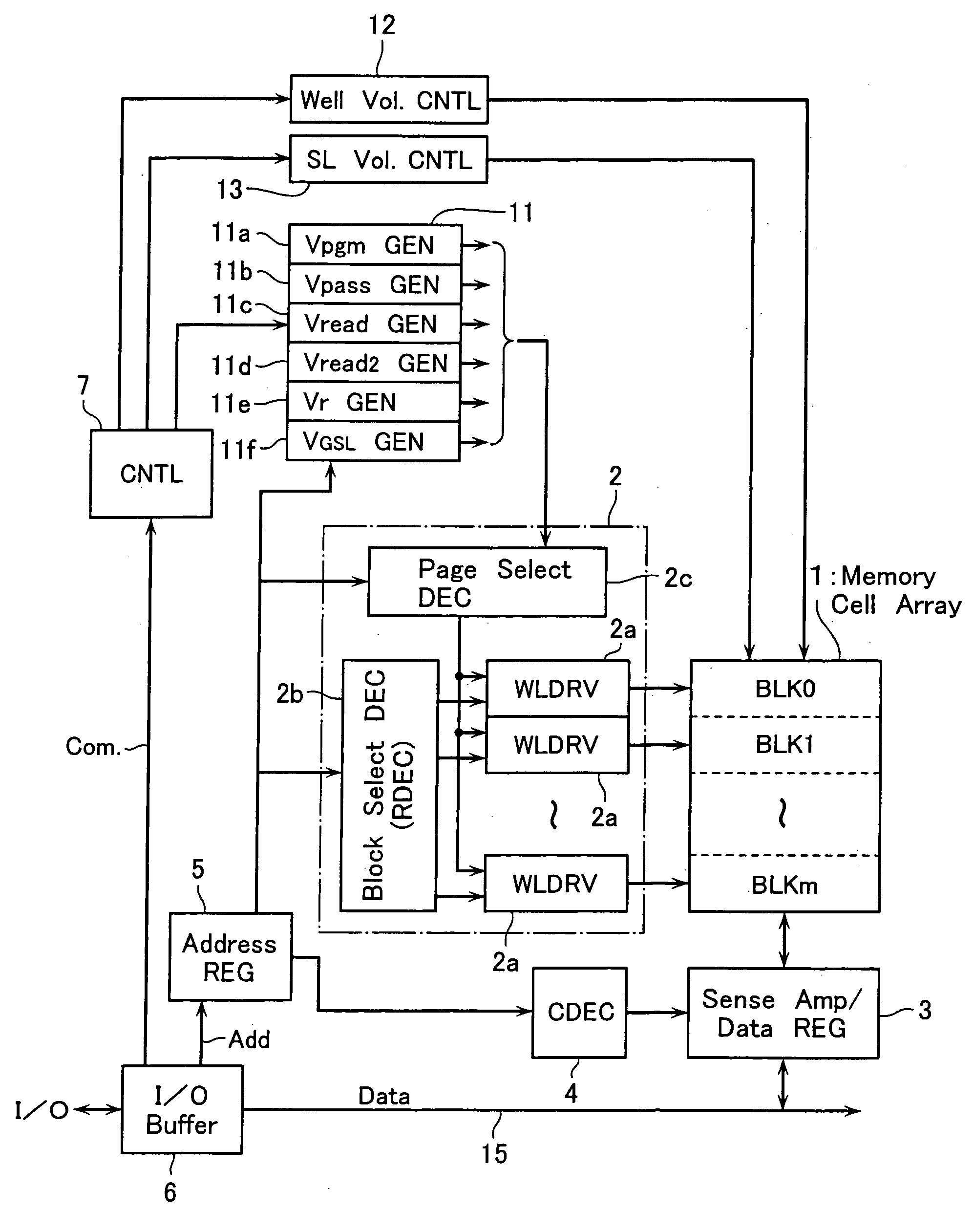

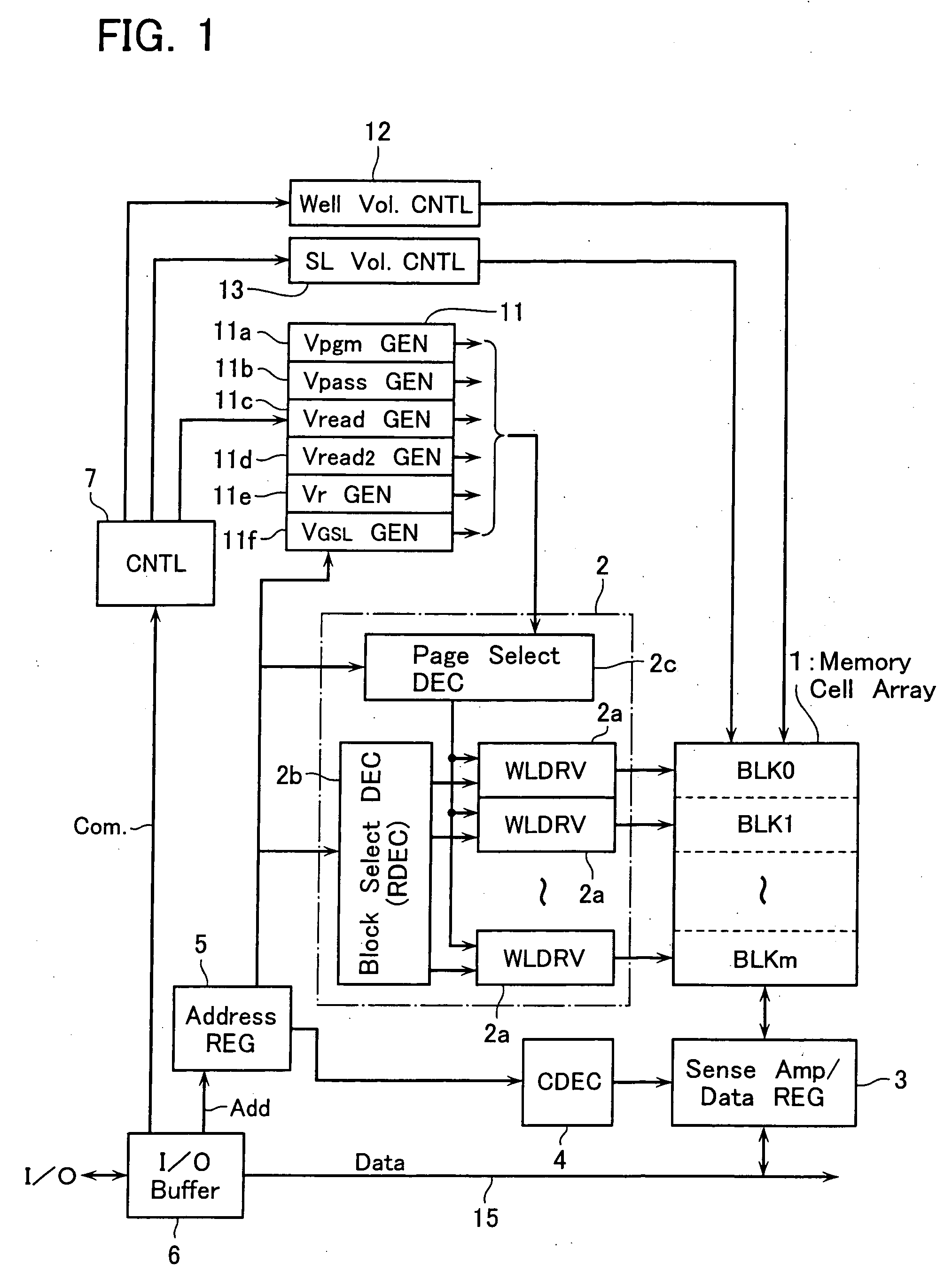

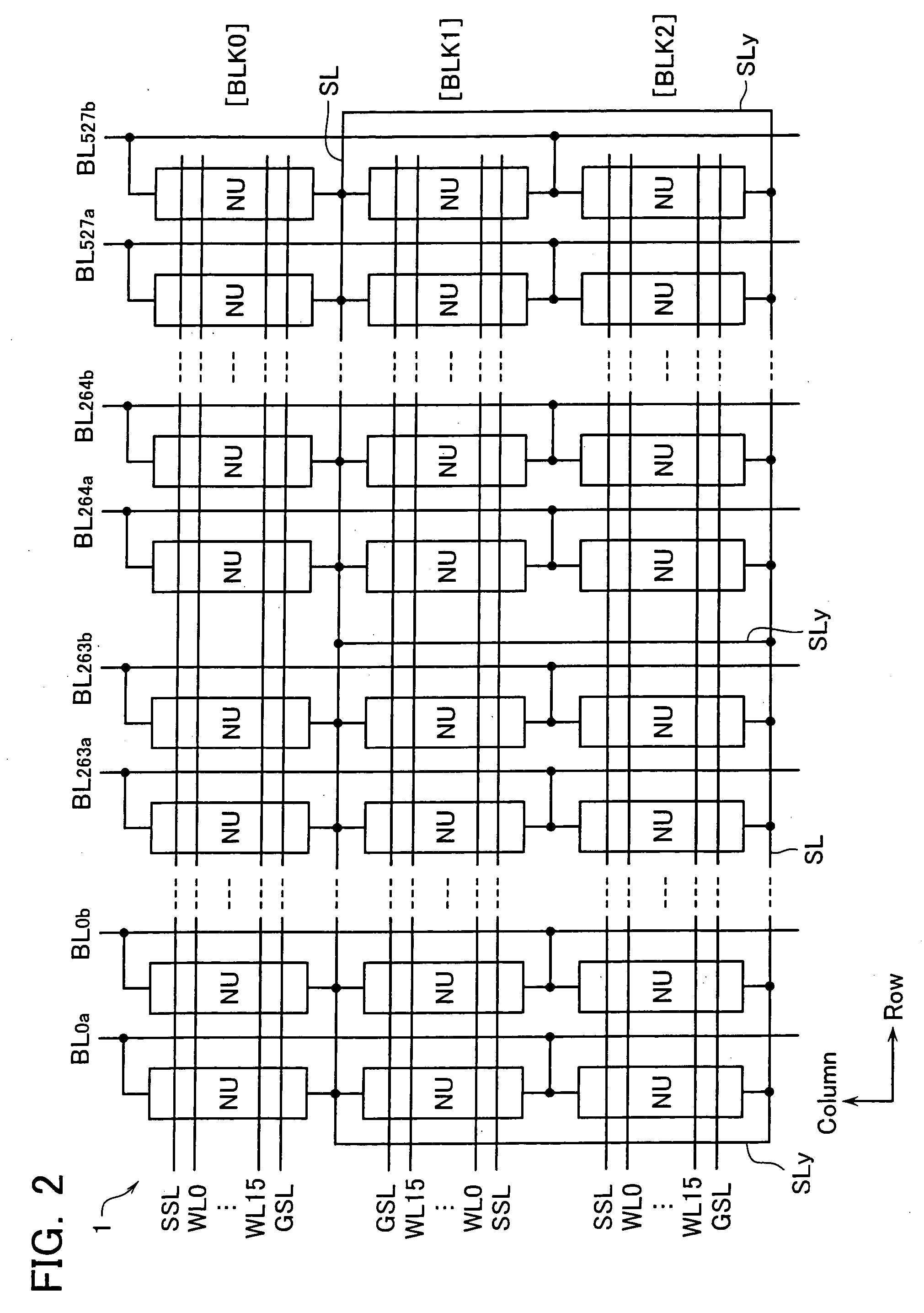

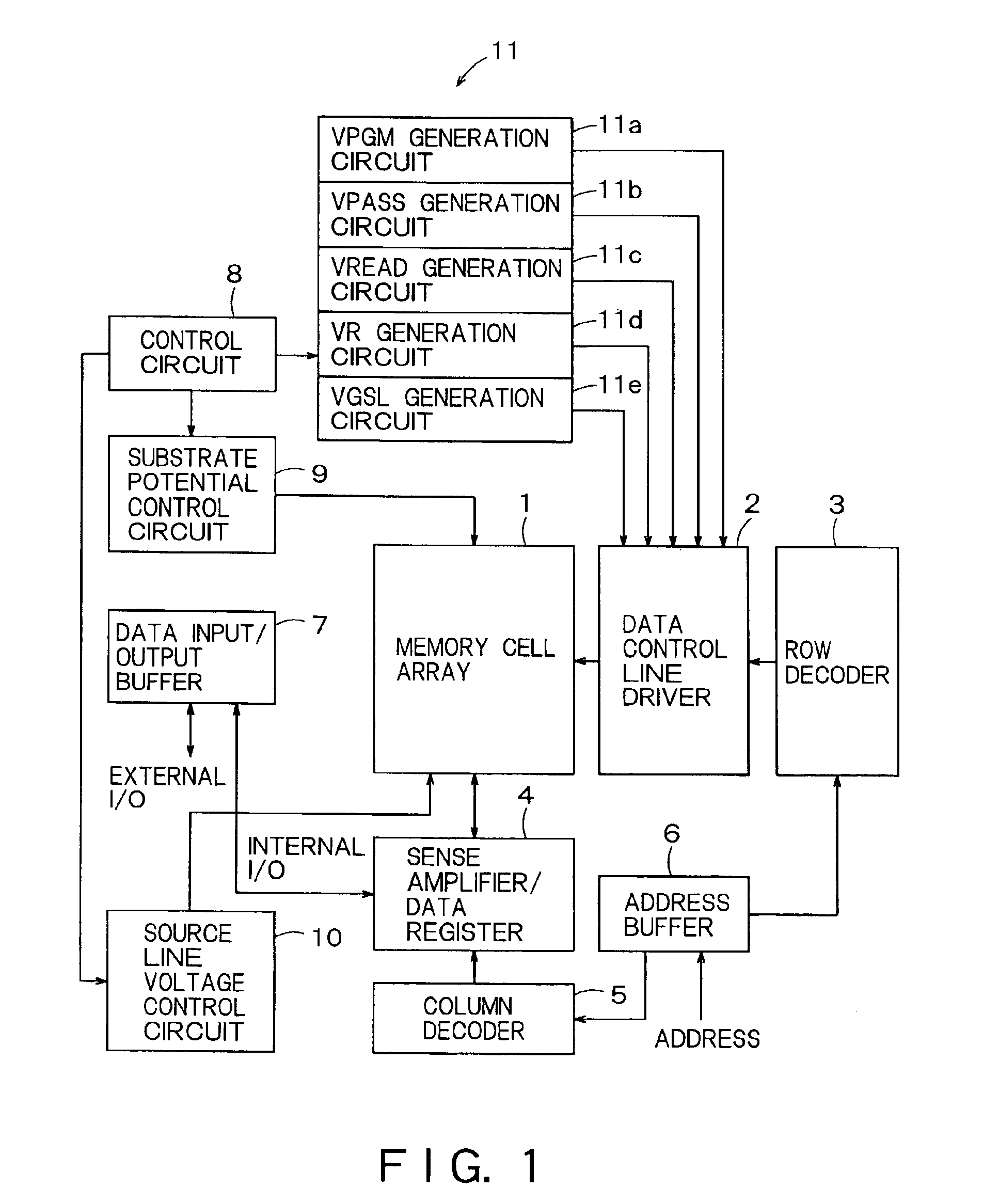

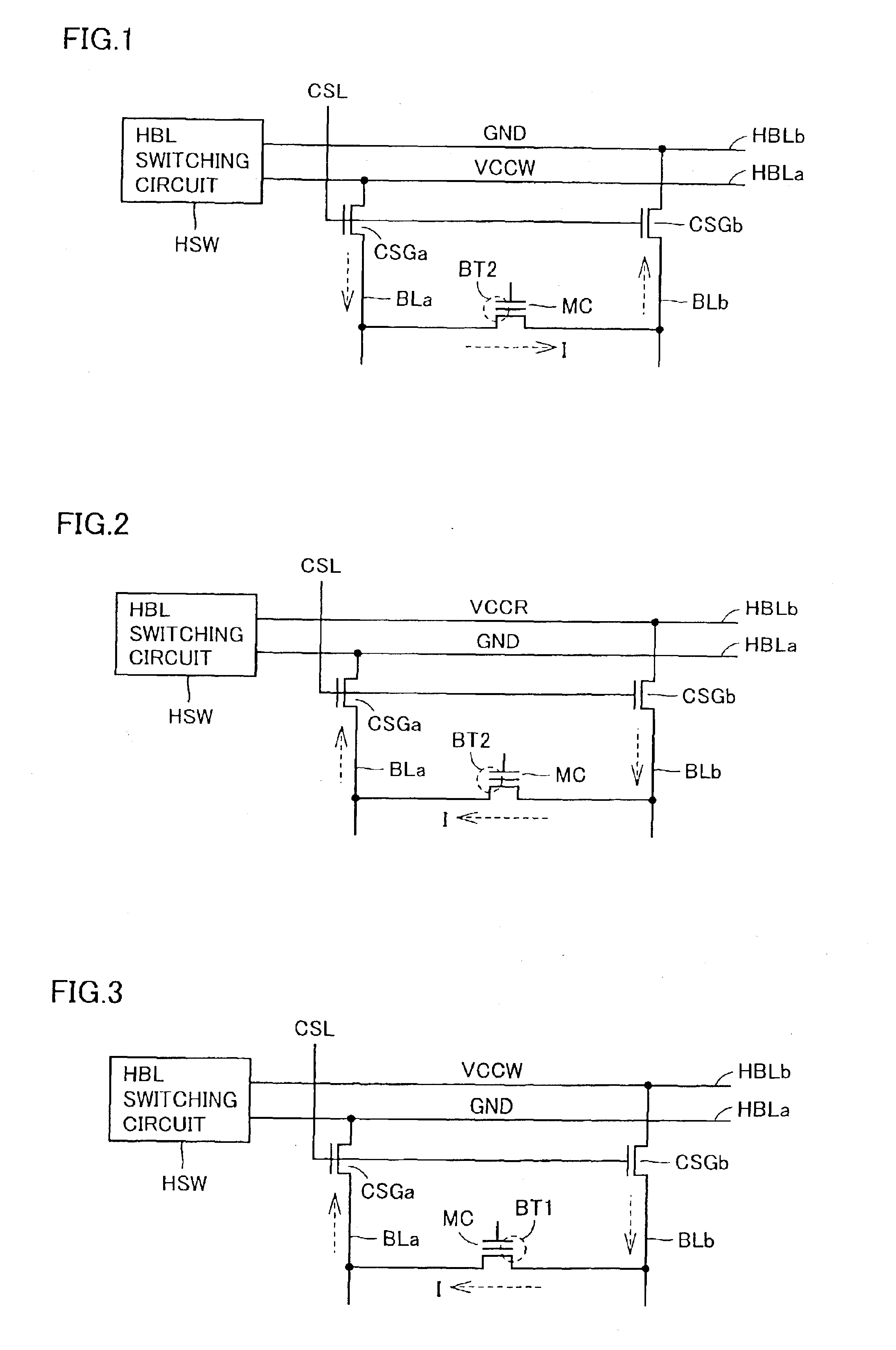

Semiconductor memory device

A semiconductor memory device includes a memory cell unit with a plurality of electrically rewritable memory cells connected in series, two ends thereof being coupled to a data transfer line and a reference potential line via select transistors, respectively, wherein the device has a data read mode defined as to detect a read current flowing between the data transfer line and the reference potential line, and judge data of a selected memory cell in the memory cell unit under the condition of: applying a read voltage to the selected memory cell, the read voltage being set to turn on or off the selected memory cell in accordance with data thereof; applying a pass voltage to remaining unselected memory cells, the pass voltage being set to turn on the remaining unselected memory cells without regard to data thereof; and making the select transistors on, and wherein in the data read mode, the more unselected memory cell or cells located on the source side of the selected memory cell, the higher the pass voltage applied to the unselected memory cell or cells located on the source side of the selected memory cell.

Owner:KK TOSHIBA

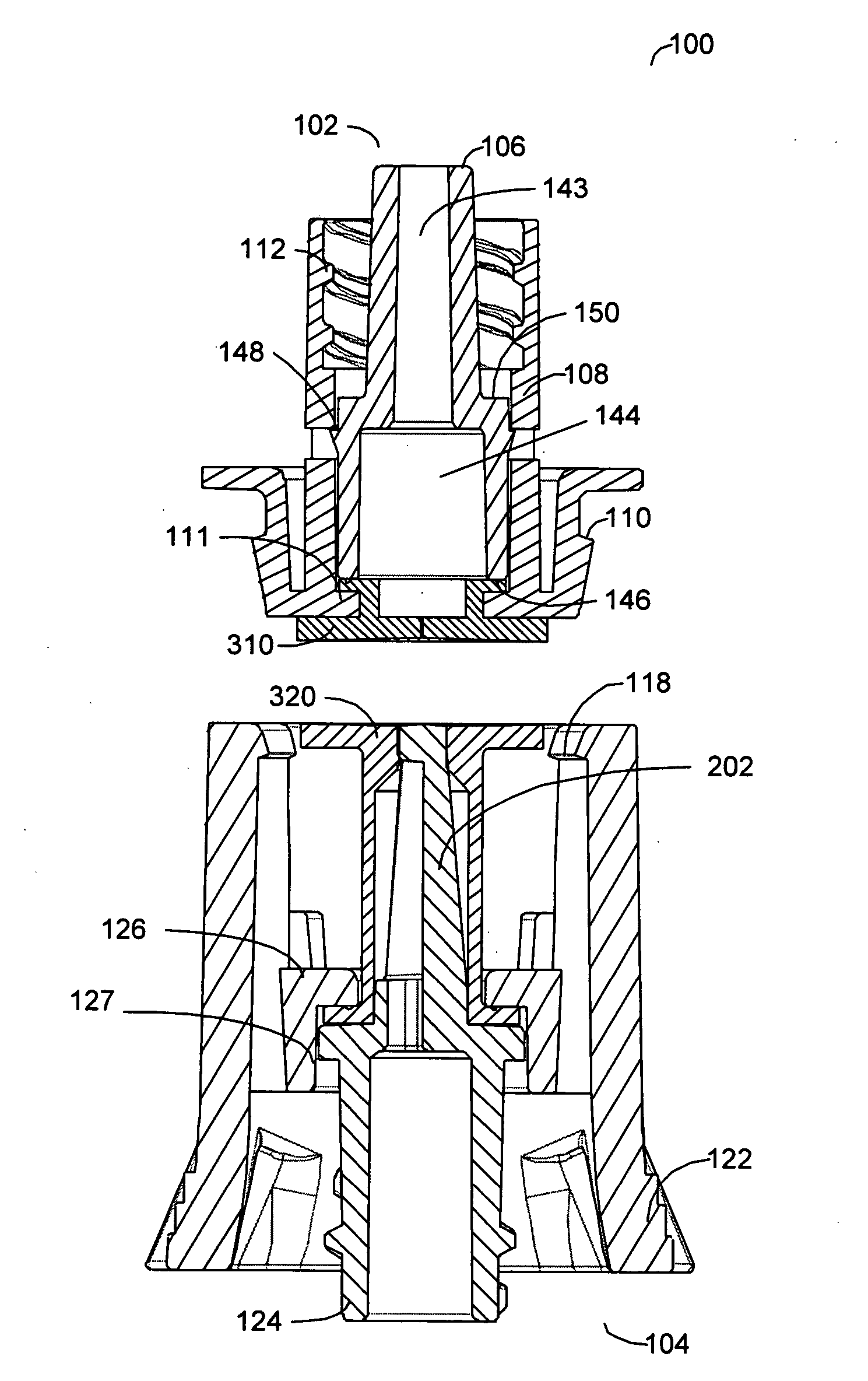

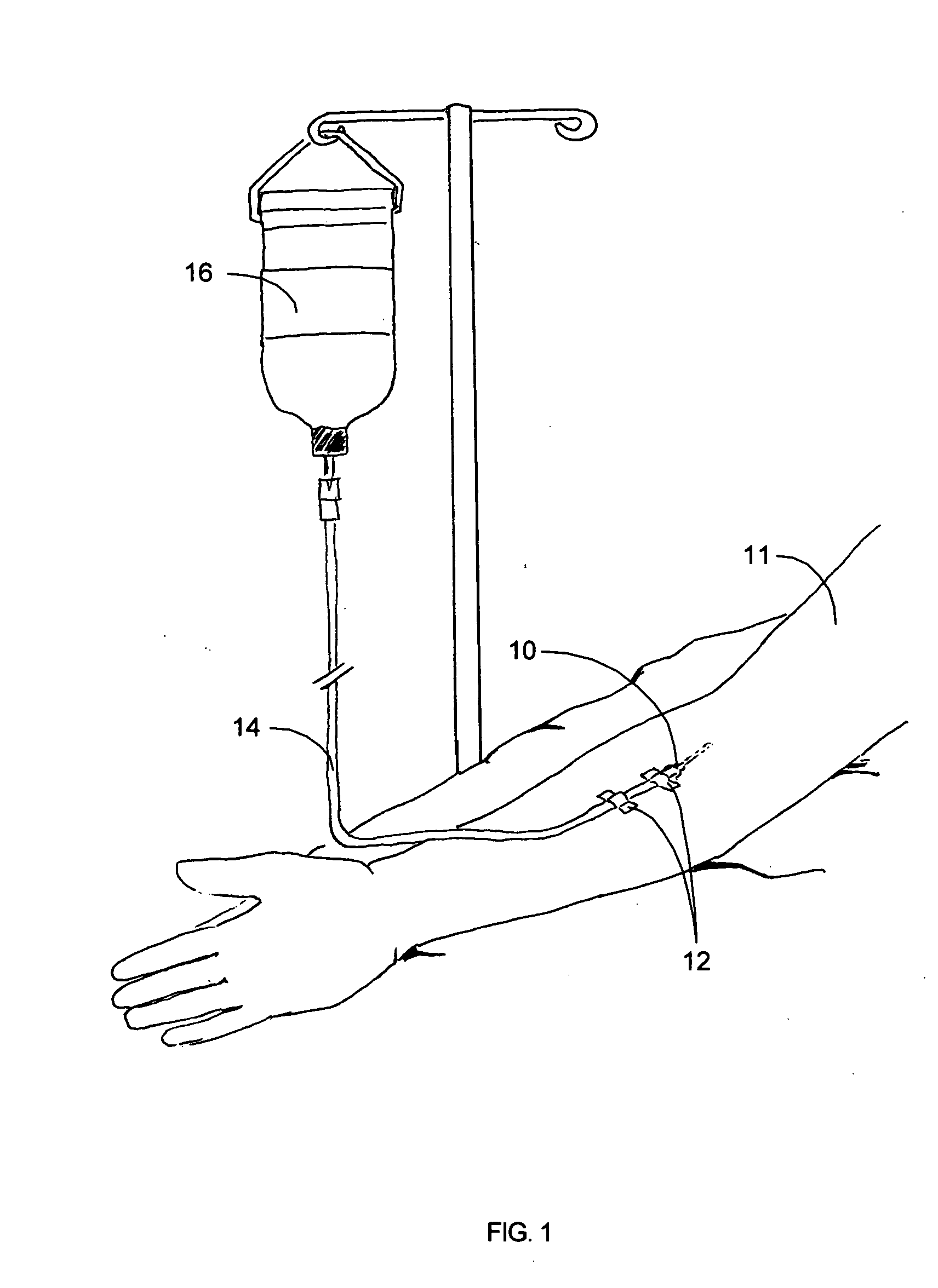

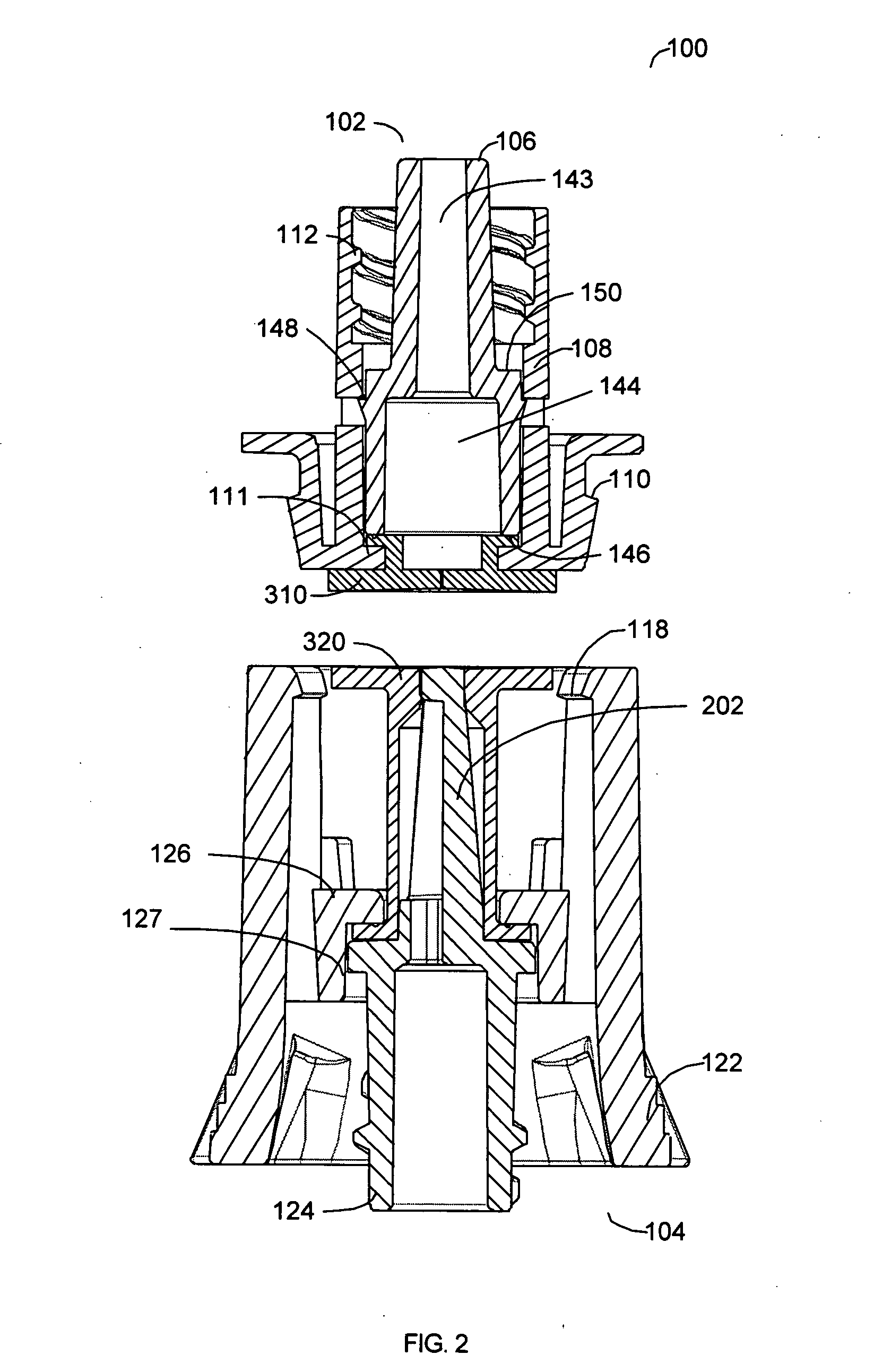

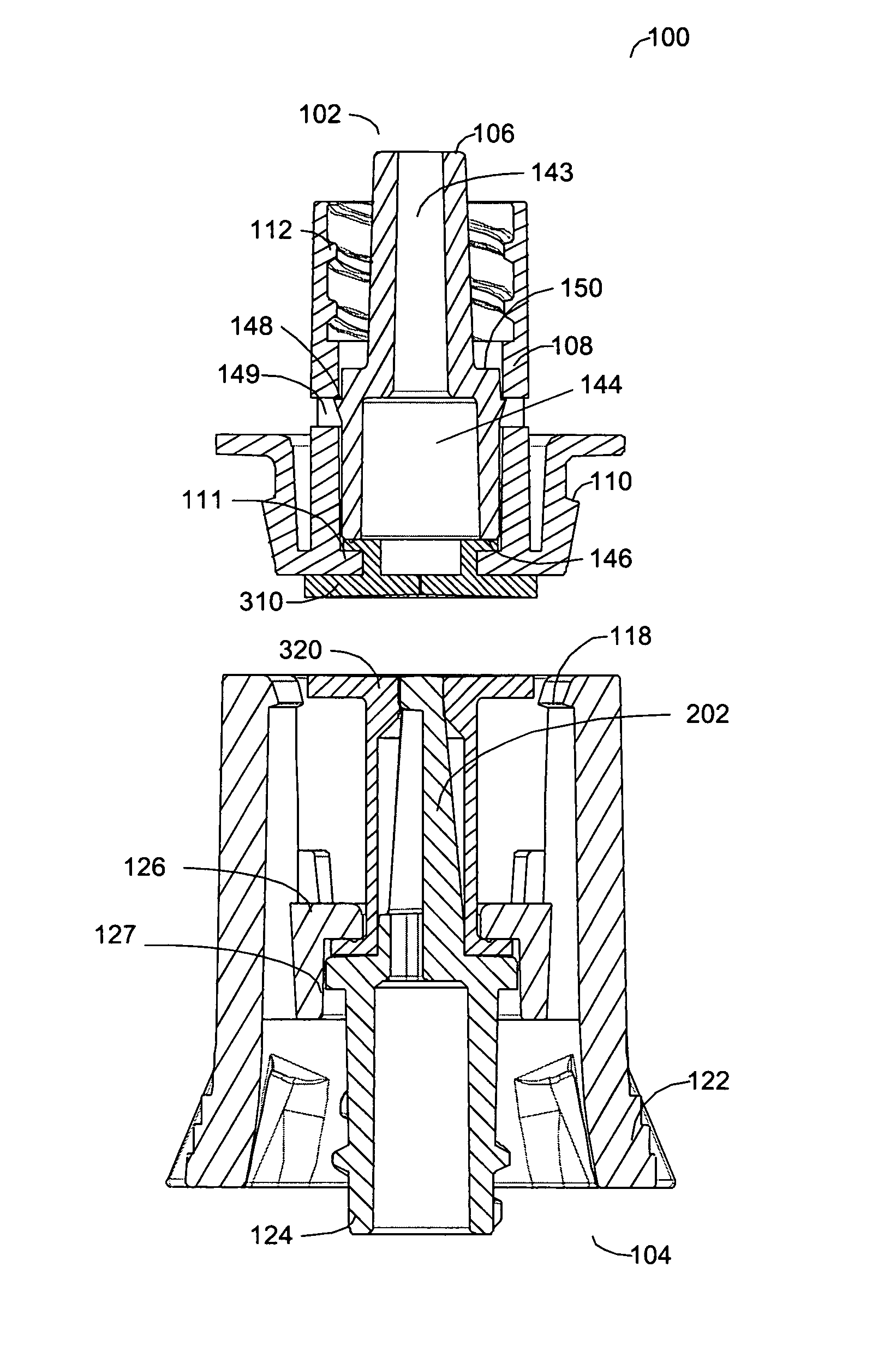

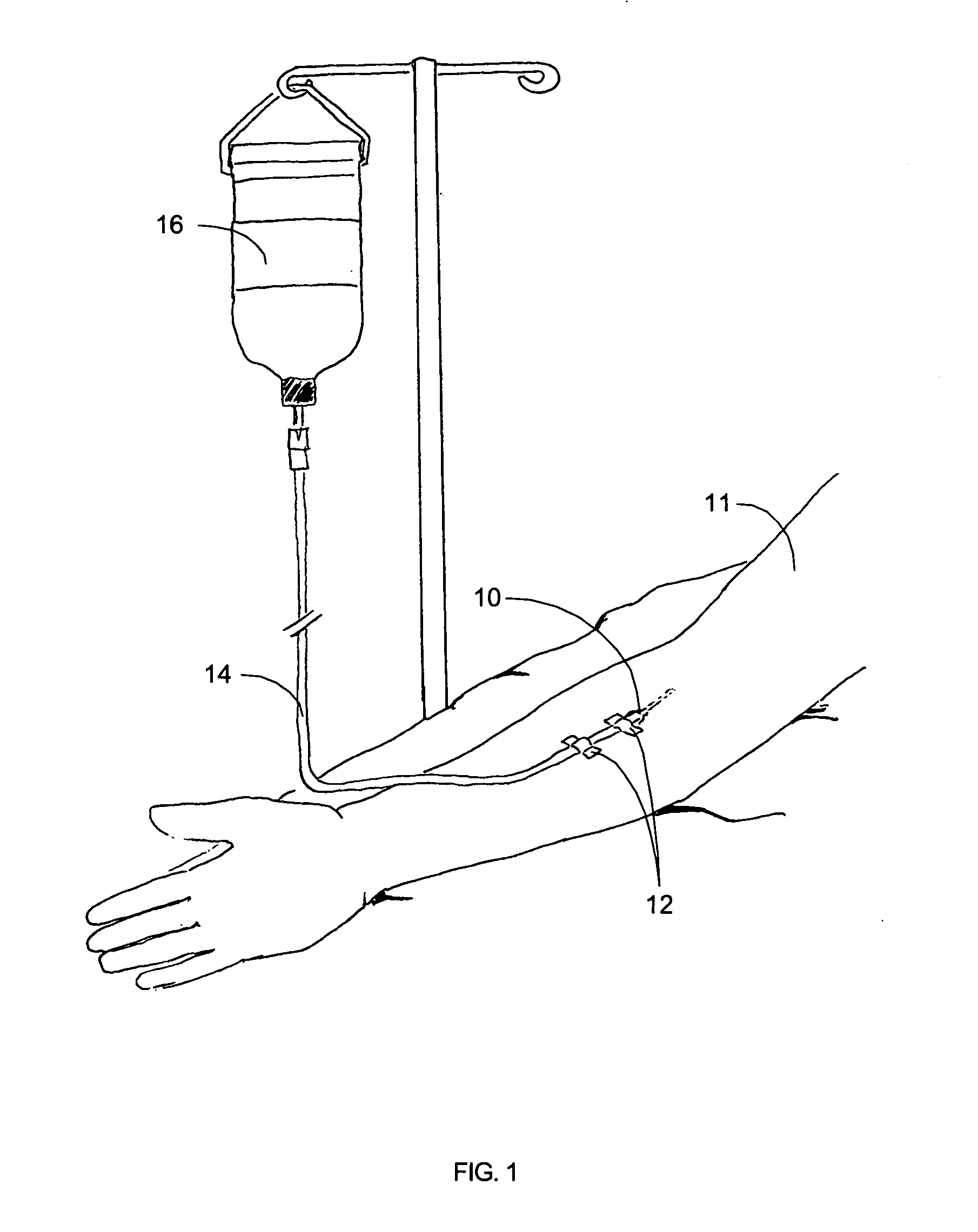

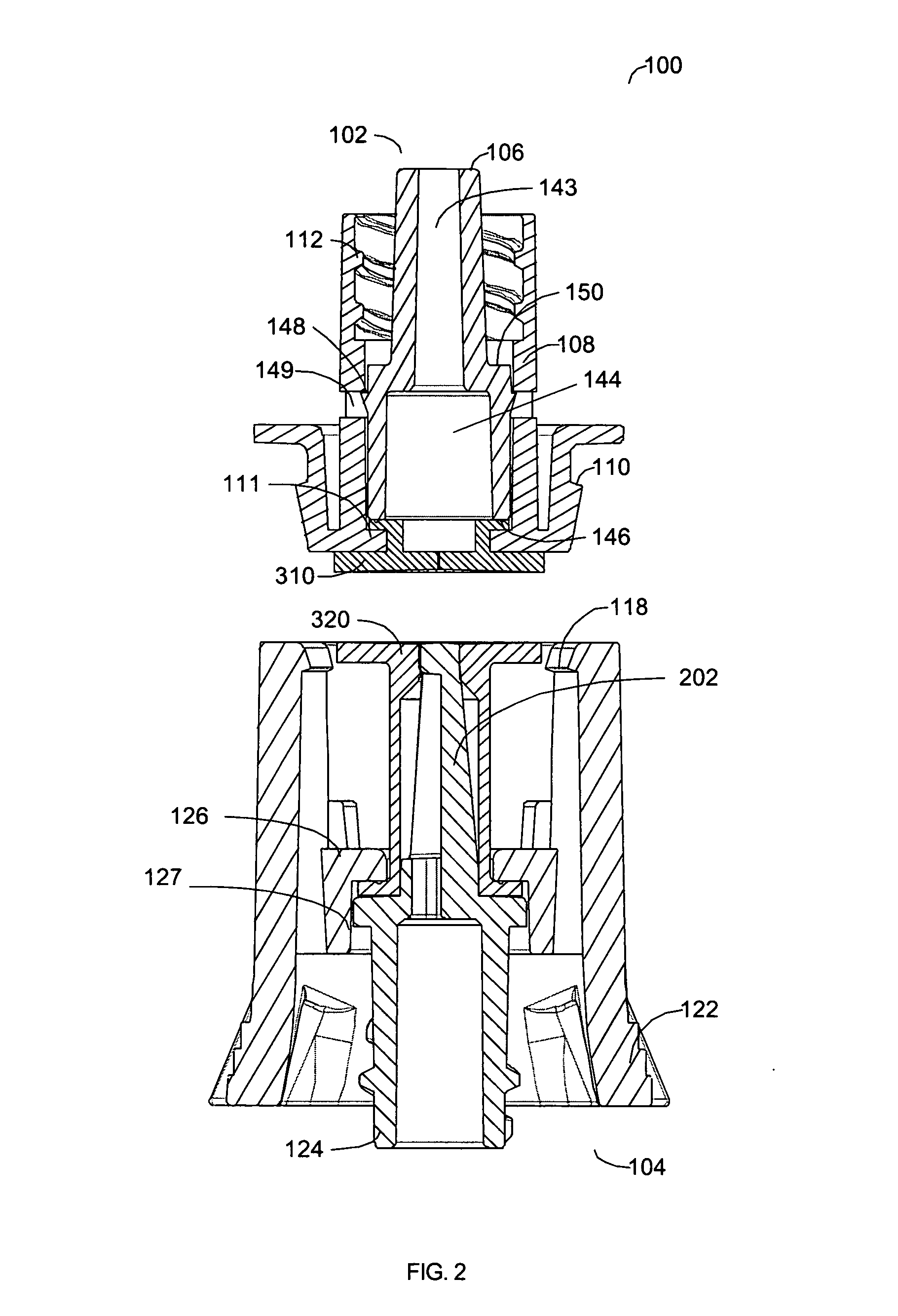

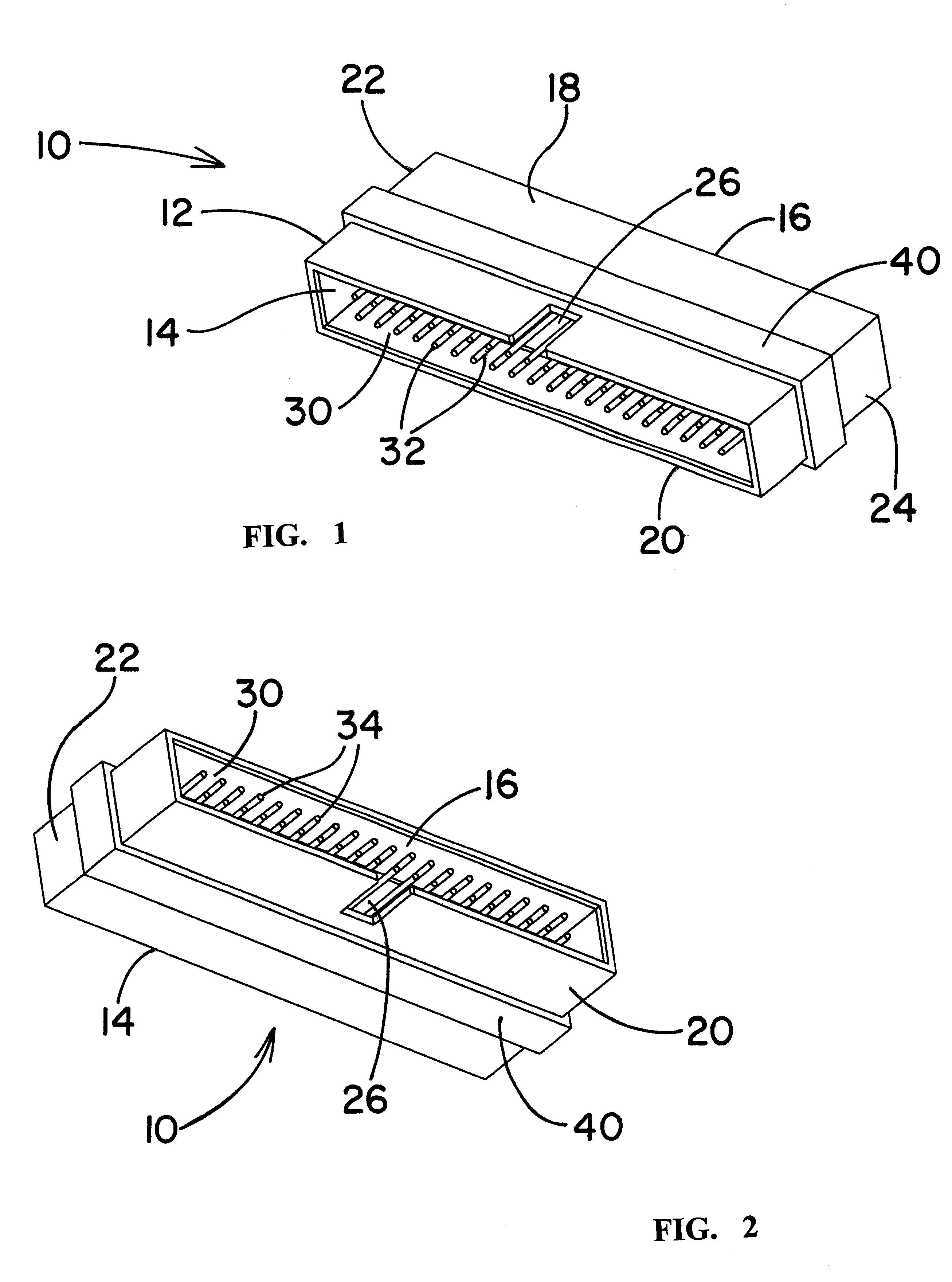

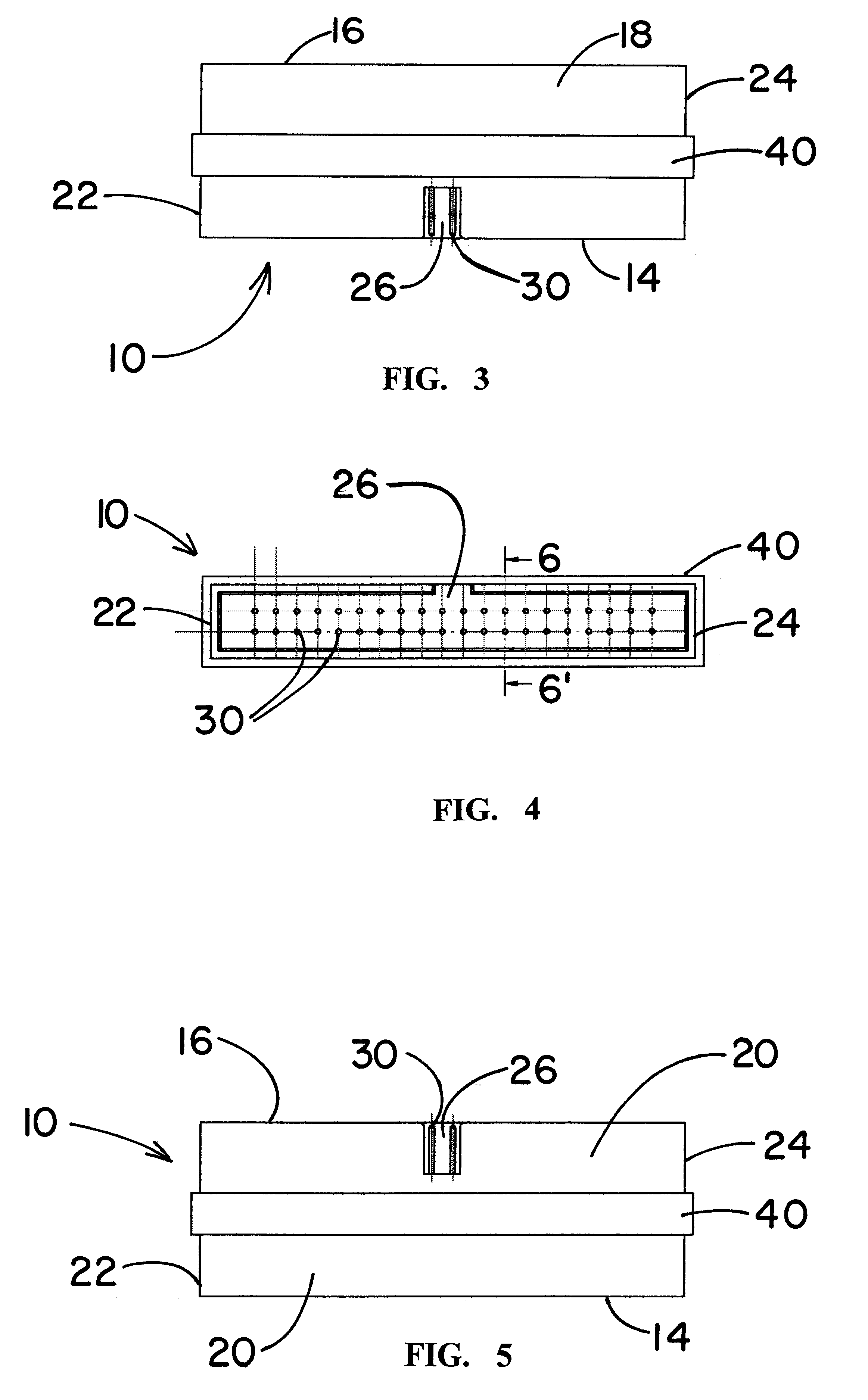

Reconnectable disconnect device for fluid transfer line

InactiveUS20060129109A1Avoid injuryEasy to disinfectIntravenous devicesValvesMedical productAxial force

An improved disconnect device suitable for use with an IV tube or other medical tubing device which can be either manually disconnected or automatically disconnected by the application of an axial force sufficiently low to prevent patient injury; which can be sterilely reattached after disconnection; which allows fluid flow in either direction; which shuts off fluid flow from both directions when disconnected; and which can be simply and inexpensively manufactured and assembled with techniques common to the injection molding, and medical products manufacturing industry.

Owner:SHAW SCOTT RANDALL +1

Reconnectable disconnect device for fluid transfer line

InactiveUS20050090805A1Simply and inexpensively manufacturedSimply and inexpensively and assembledCatheterTube connectorsMedical productAxial force

An improved disconnect device suitable for use with an IV tube or other medical tubing device which can be either manually disconnected or automatically disconnected by the application of an axial force sufficiently low to prevent patient injury; which can be sterilely reattached after disconnection; which allows fluid flow in either direction; which shuts off fluid flow from both directions when disconnected; and which can be simply and inexpensively manufactured and assembled with techniques common to the injection molding, and medical products manufacturing industry.

Owner:SHAW SCOTT RANDALL +1

Semiconductor memory device

A semiconductor memory device includes a memory cell unit with a plurality of electrically rewritable memory cells connected in series, two ends thereof being coupled to a data transfer line and a reference potential line via select transistors, respectively, wherein the device has a data read mode defined as to detect a read current flowing between the data transfer line and the reference potential line, and judge data of a selected memory cell in the memory cell unit under the condition of: applying a read voltage to the selected memory cell, the read voltage being set to turn on or off the selected memory cell in accordance with data thereof; applying a pass voltage to remaining unselected memory cells, the pass voltage being set to turn on the remaining unselected memory cells without regard to data thereof; and making the select transistors on, and wherein in the data read mode, the more unselected memory cell or cells located on the source side of the selected memory cell, the higher the pass voltage applied to the unselected memory cell or cells located on the source side of the selected memory cell.

Owner:KK TOSHIBA

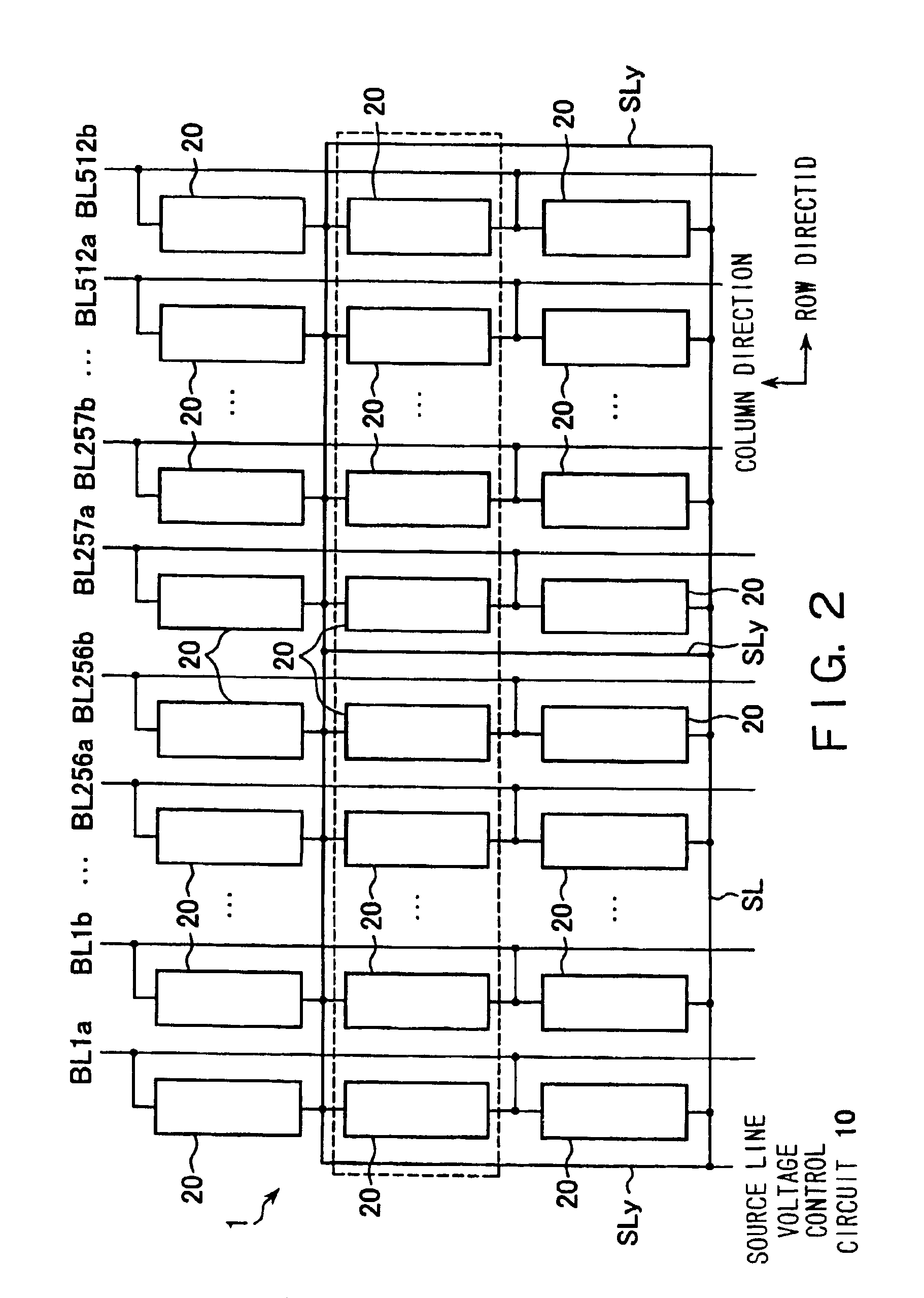

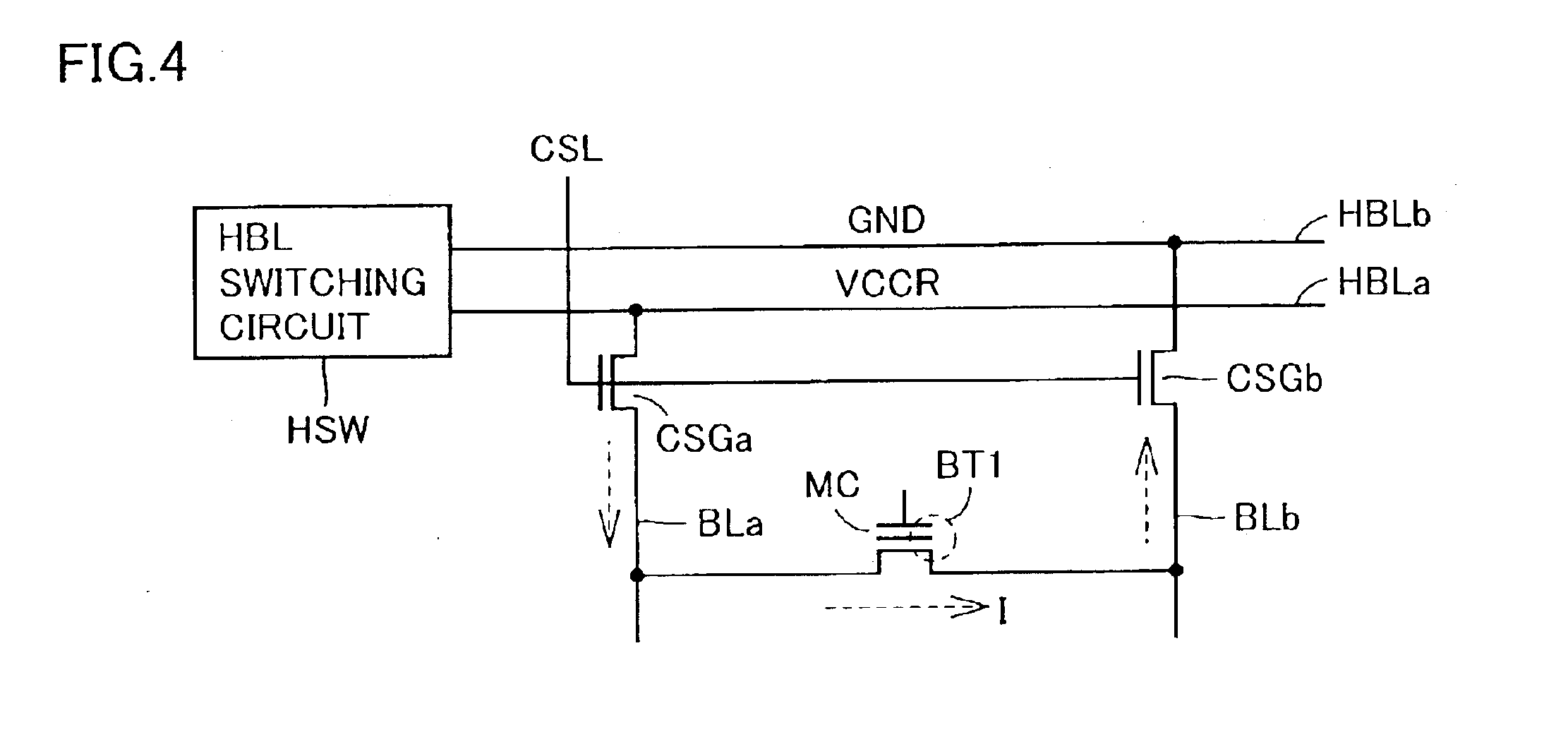

Semiconductor memory

A semiconductor memory including a memory cell unit, the memory cell unit comprising: a plurality of memory cells in which each conductance between current terminals changes according to held data, each having a plurality of current terminals connected in series between a first terminal and a second terminal, and each capable of electrically rewriting the data; a first select switching element electrically connecting said first terminal to a data transfer line; and a MISFET serving as a second select switching element connecting said second terminal to a reference potential line, wherein said semiconductor memory has a data read mode for forcing the first and second select switching elements of said memory cell unit into conduction, applying a read voltage for forcing a path between the current terminals into conduction or cut-off according to the data of a selected memory cell, to a control electrode of the selected memory cell, applying a pass voltage for forcing a path between the current terminals into conduction irrespectively of the data of each of the memory cells other than said selected memory cell, to the control electrode of each of the memory cells other than said selected memory cell, and detecting presence and absence or magnitude of a current between said data transfer line and said reference potential line, and in said data read mode, a conductance between current terminals of said MISFET is set lower than a conductance, in the case where the conductance between the current terminals is set to be the lowest, with regards to at least one of the memory cells other than said selected memory cell.

Owner:KIOXIA CORP

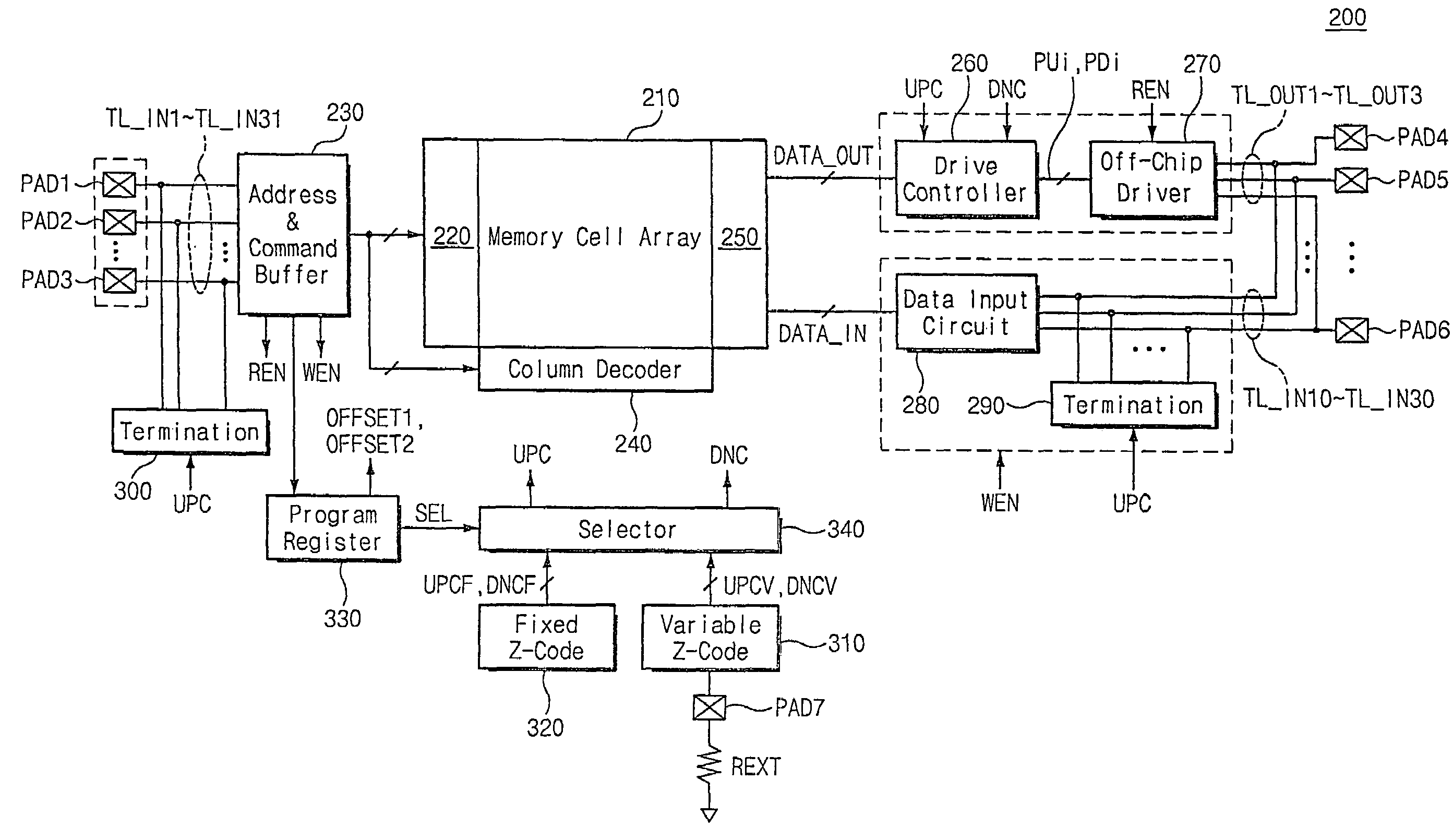

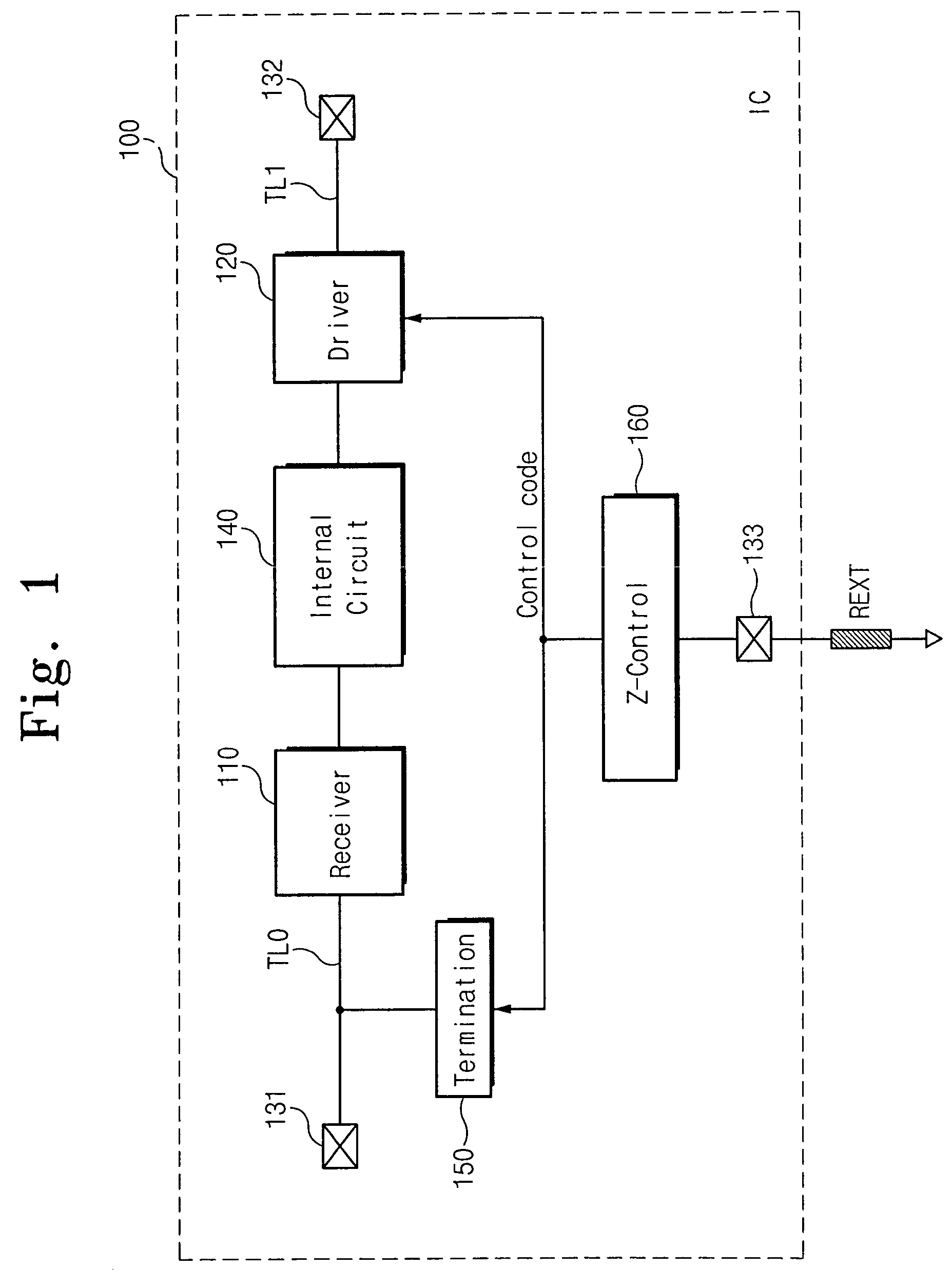

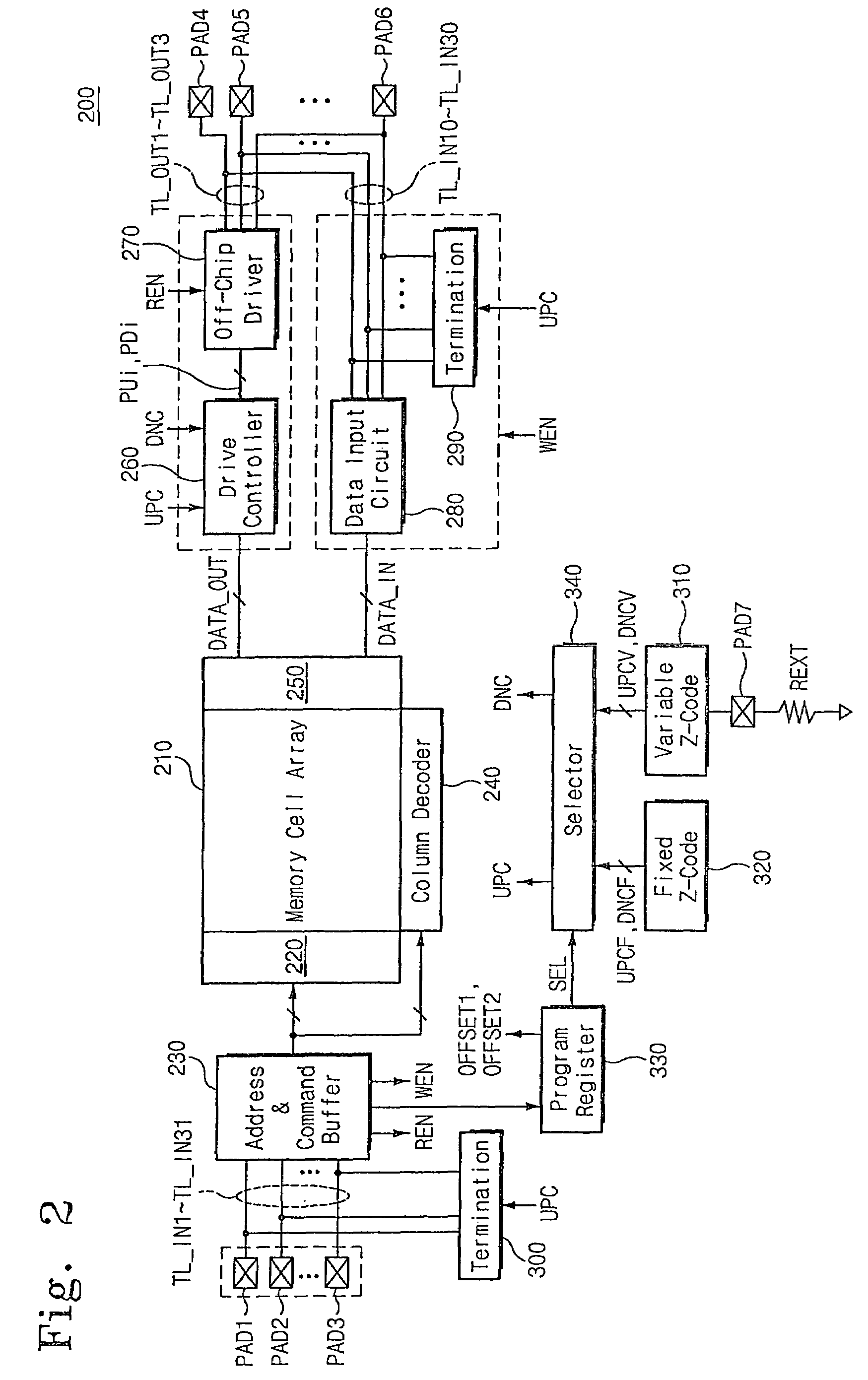

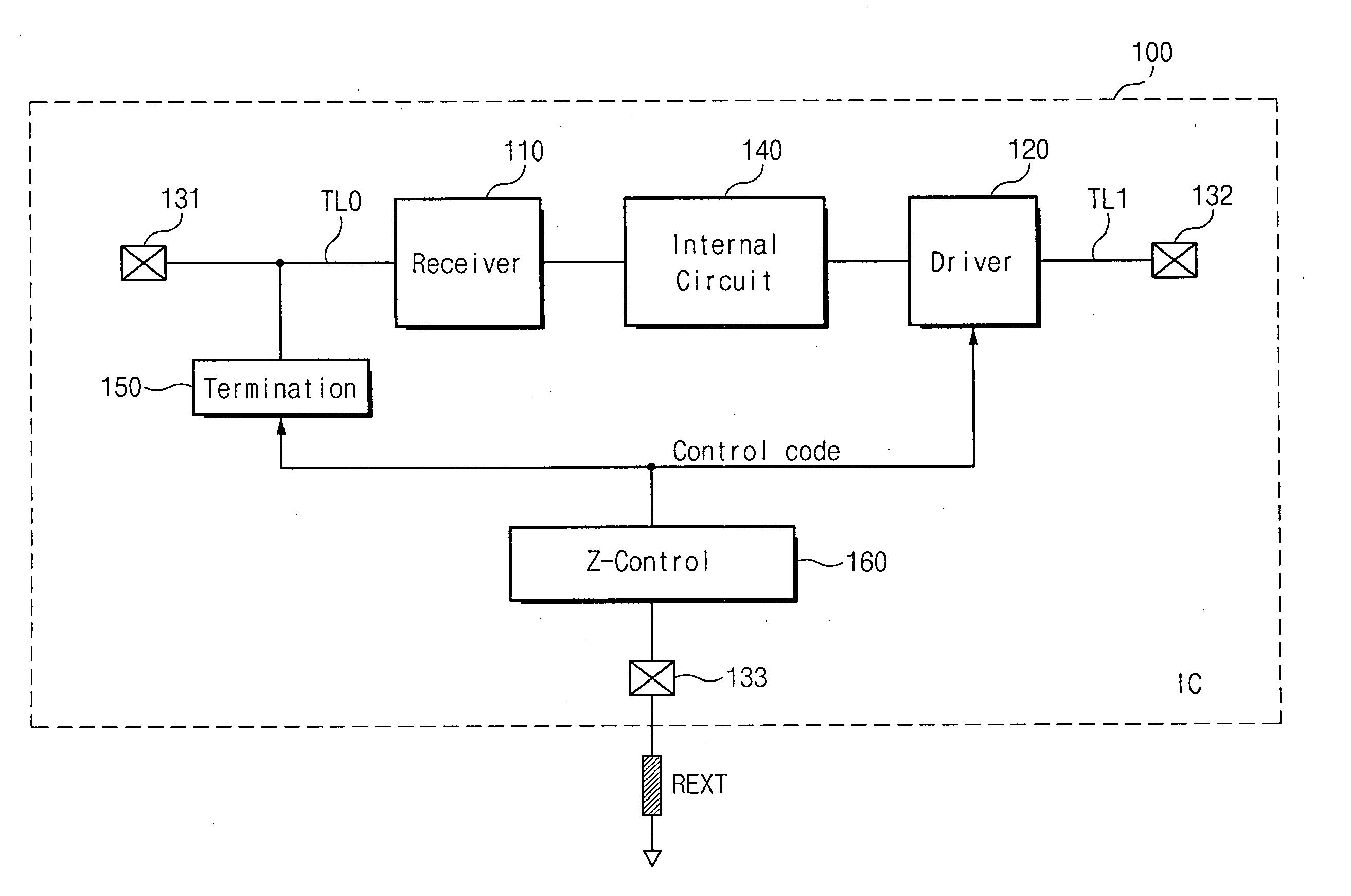

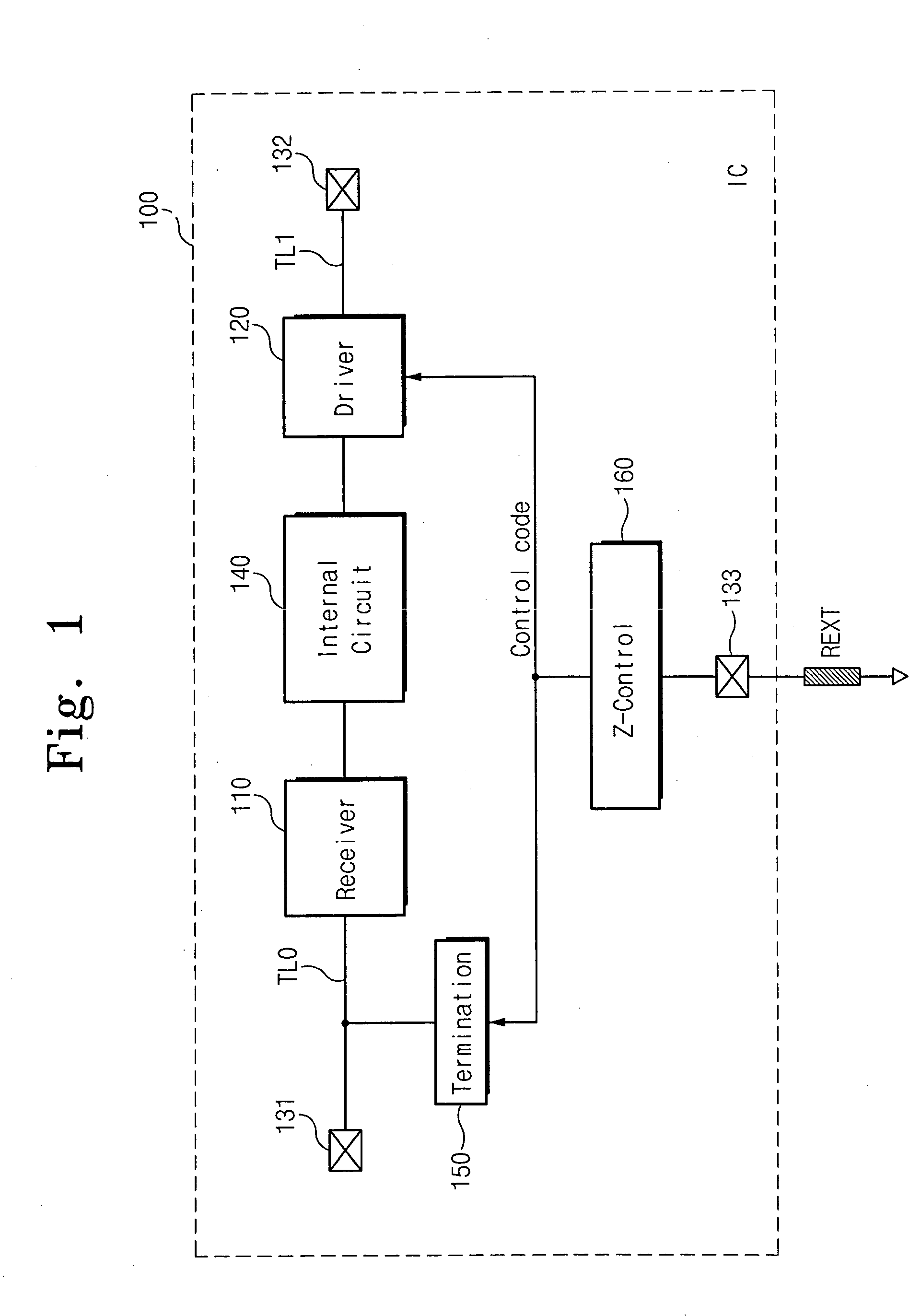

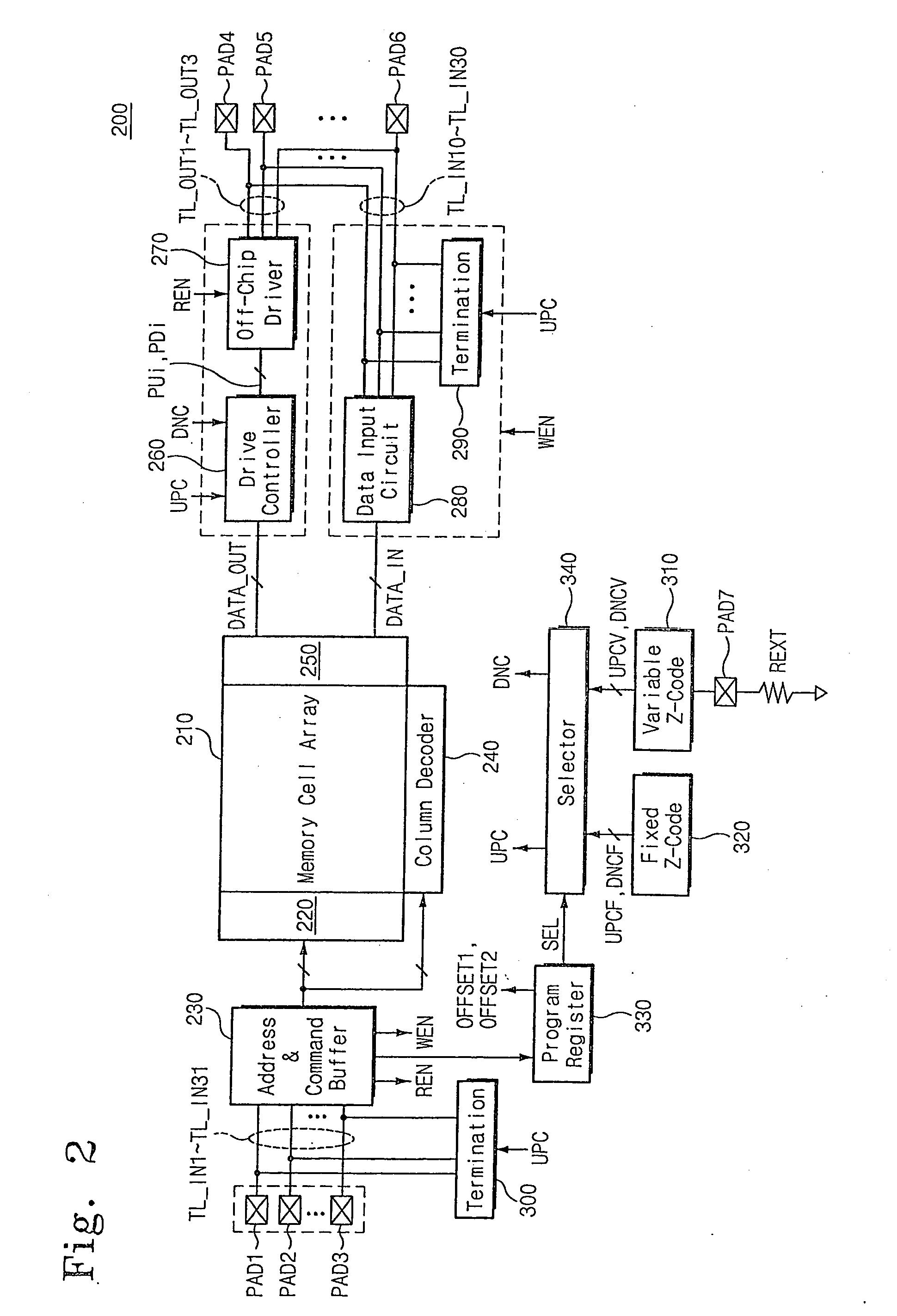

Semiconductor integrated circuit device capable of controlling impedance

ActiveUS7148721B2Input/output impedence modificationReliability increasing modificationsExternal referenceSemiconductor

A semiconductor integrated circuit device is connected to an external reference resistor, including an impedance control circuit for generating impedance control codes variable with impedances established by the external reference resistor. An input circuit receives an external signal through an input transfer line and forwards the external signal to an internal circuit. A termination circuit terminates the input transfer line in response to at least one of the impedance control code. An output circuit drives an output transfer line in accordance with an output signal. Impedance is variable with the control codes.

Owner:SAMSUNG ELECTRONICS CO LTD

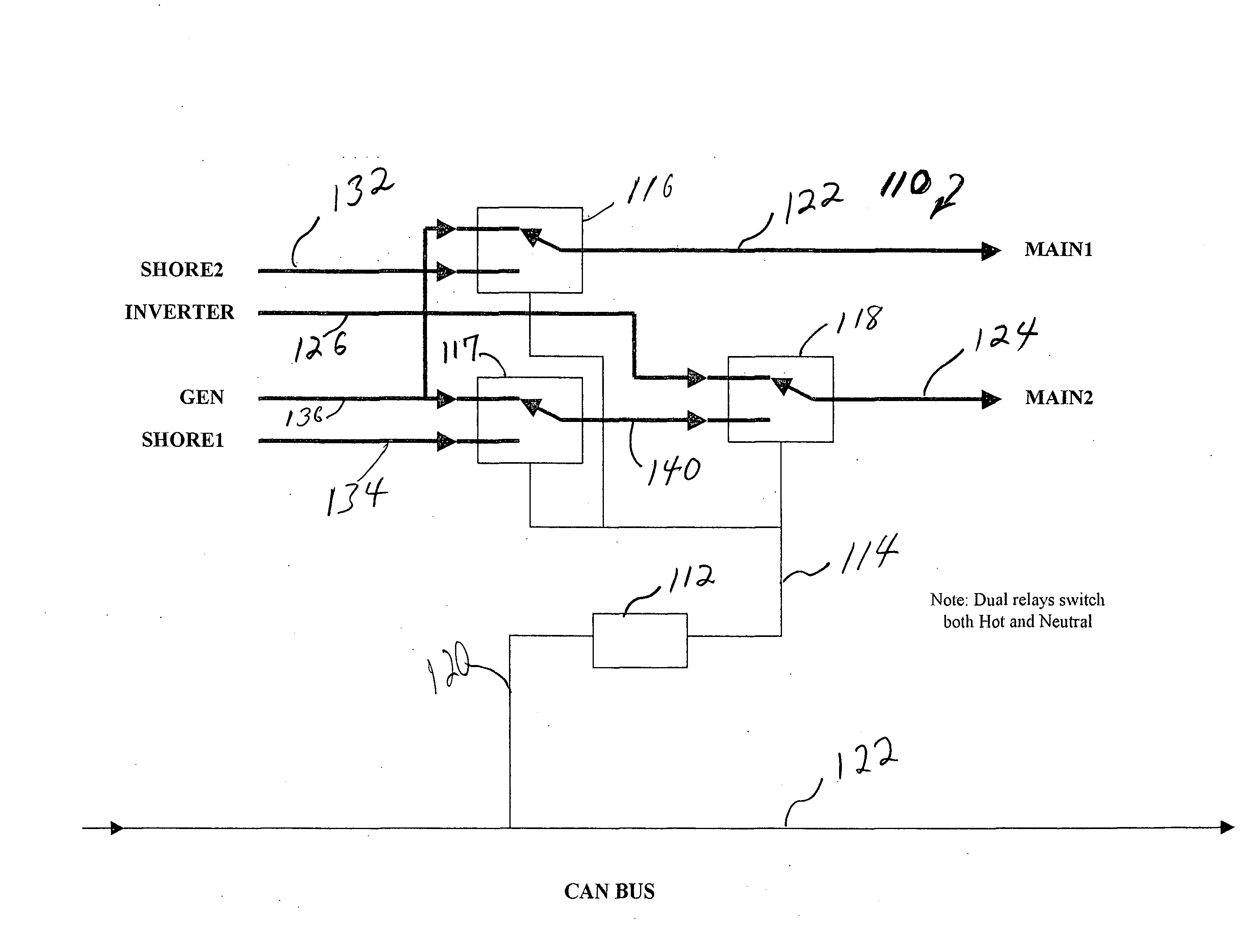

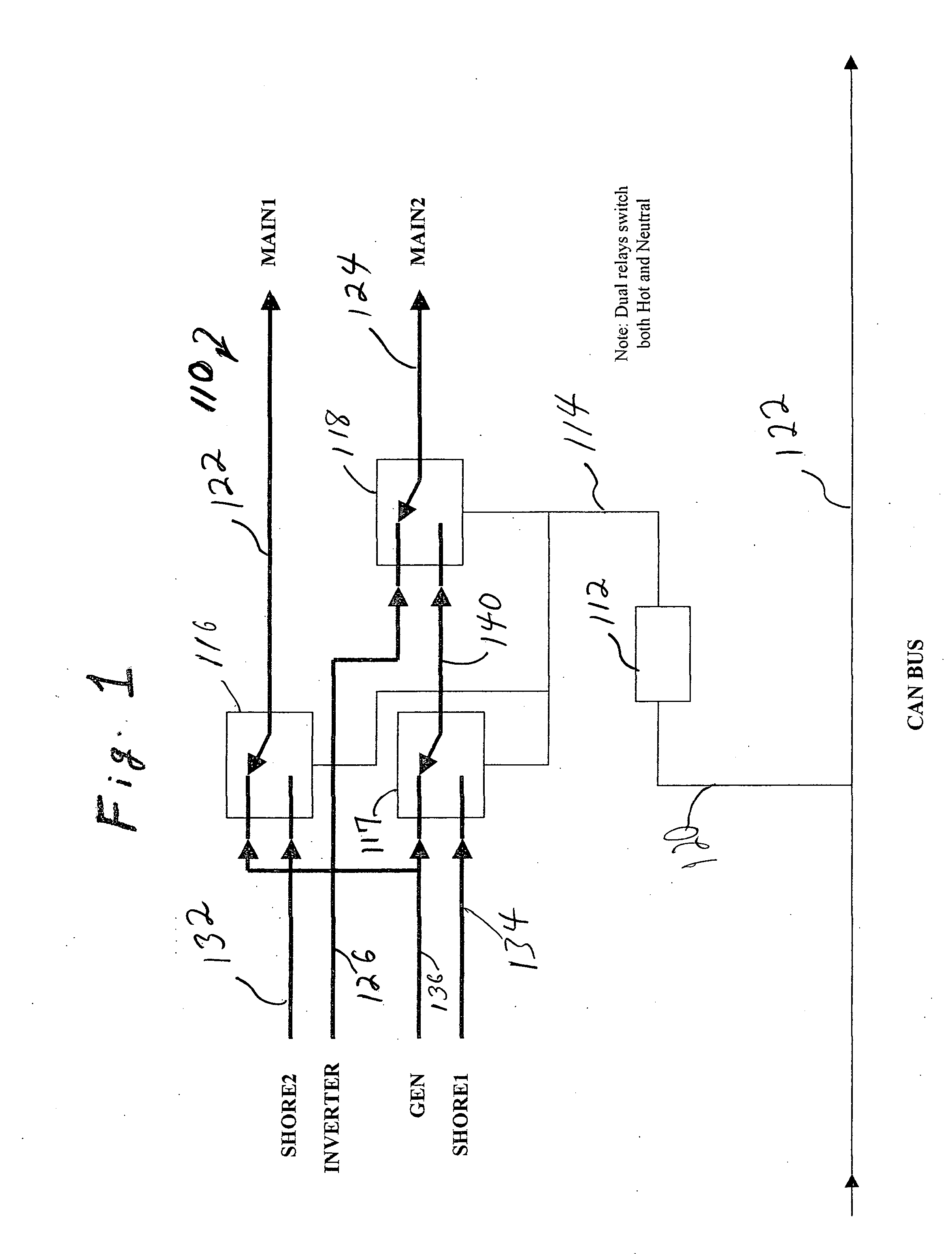

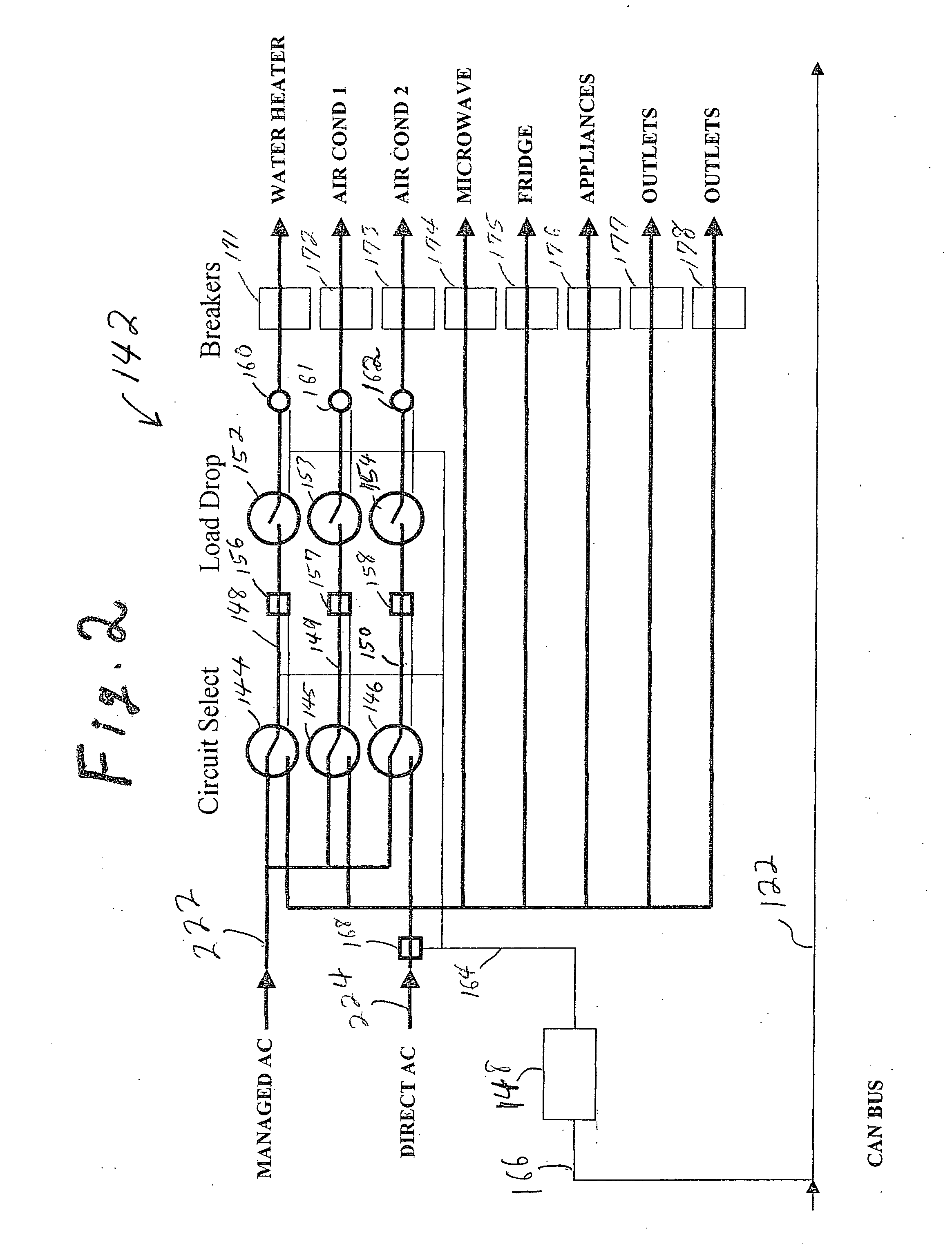

Power averaging and power load management system

InactiveUS20050141154A1Selective ac load connection arrangementsVehicle heating/cooling devicesElectric power transmissionDistribution control

A power and load management system for a recreational vehicle provides a power distribution panel comprising a distribution controller operative to generate distribution control signals including at least load signals corresponding to the power load demands on the power distribution panel and distribution relay control signals, and an automatic transfer switch (ATS). The ATS has multiple power inputs, each operative to be connected to one of multiple power sources, e.g., shore power, a battery bank, a generator, etc., and two power transfer lines to the power distribution switch. The ATS further comprises multiple relays, each controllable independently of the others by an ATS controller to connect a corresponding one of the power transfer lines to a selected one of the available power inputs to feed power to the power distribution panel. The ATS further has multiple sensors, each operative to generate a power availability signal to the ATS controller corresponding to the availability of power on a corresponding one of the power input lines. The ATS controller is operative to receive load signals from the distribution controller and power availability signals from the ATS sensors, and to generate the power transfer control signals to the ATS relays and ATS signals to the distribution controller corresponding to power availability. The power distribution panel further comprises independently controllable distribution relays to connect each of the power transfer lines to power load(s).

Owner:ATWOOD MOBILE PRODS

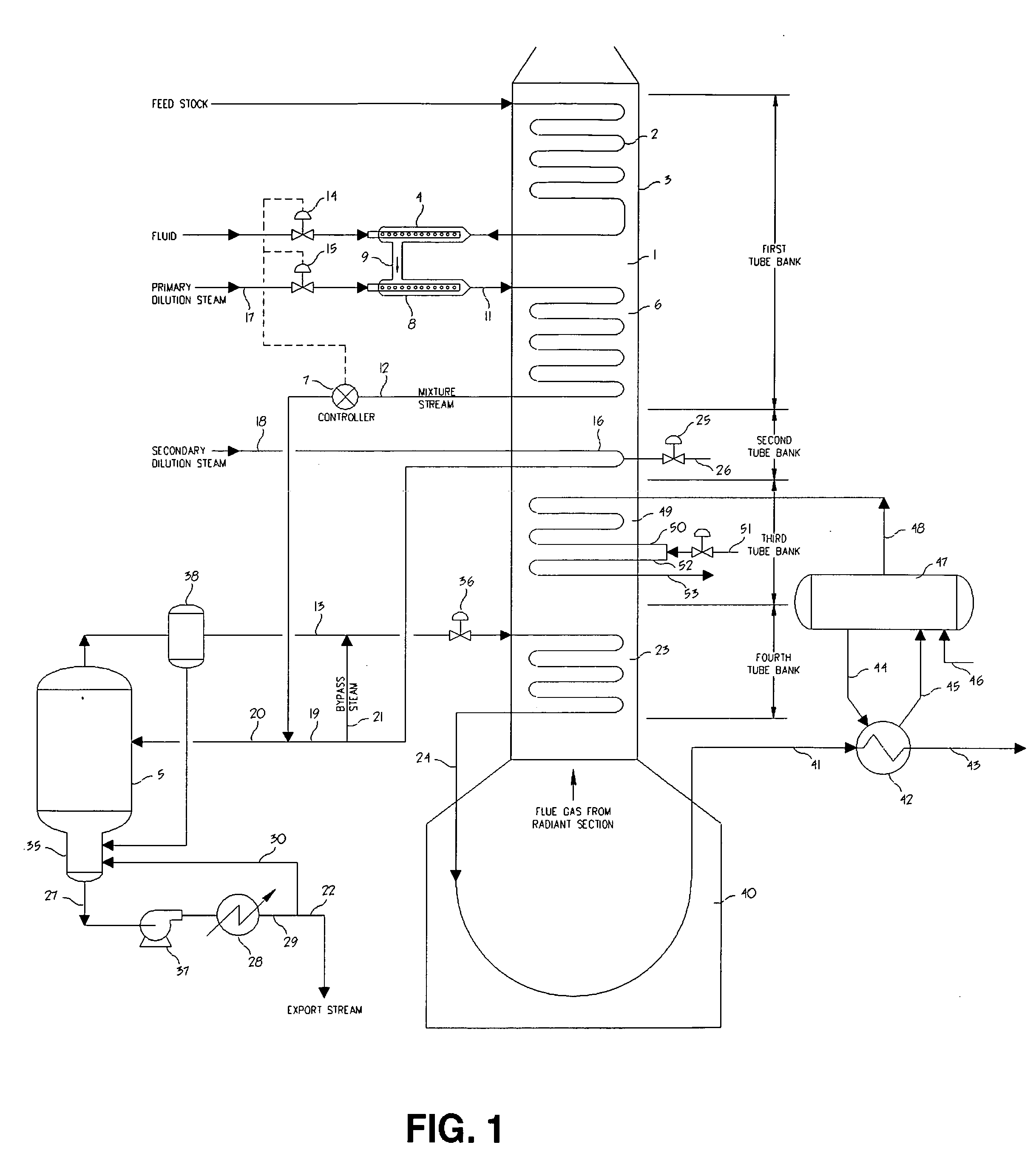

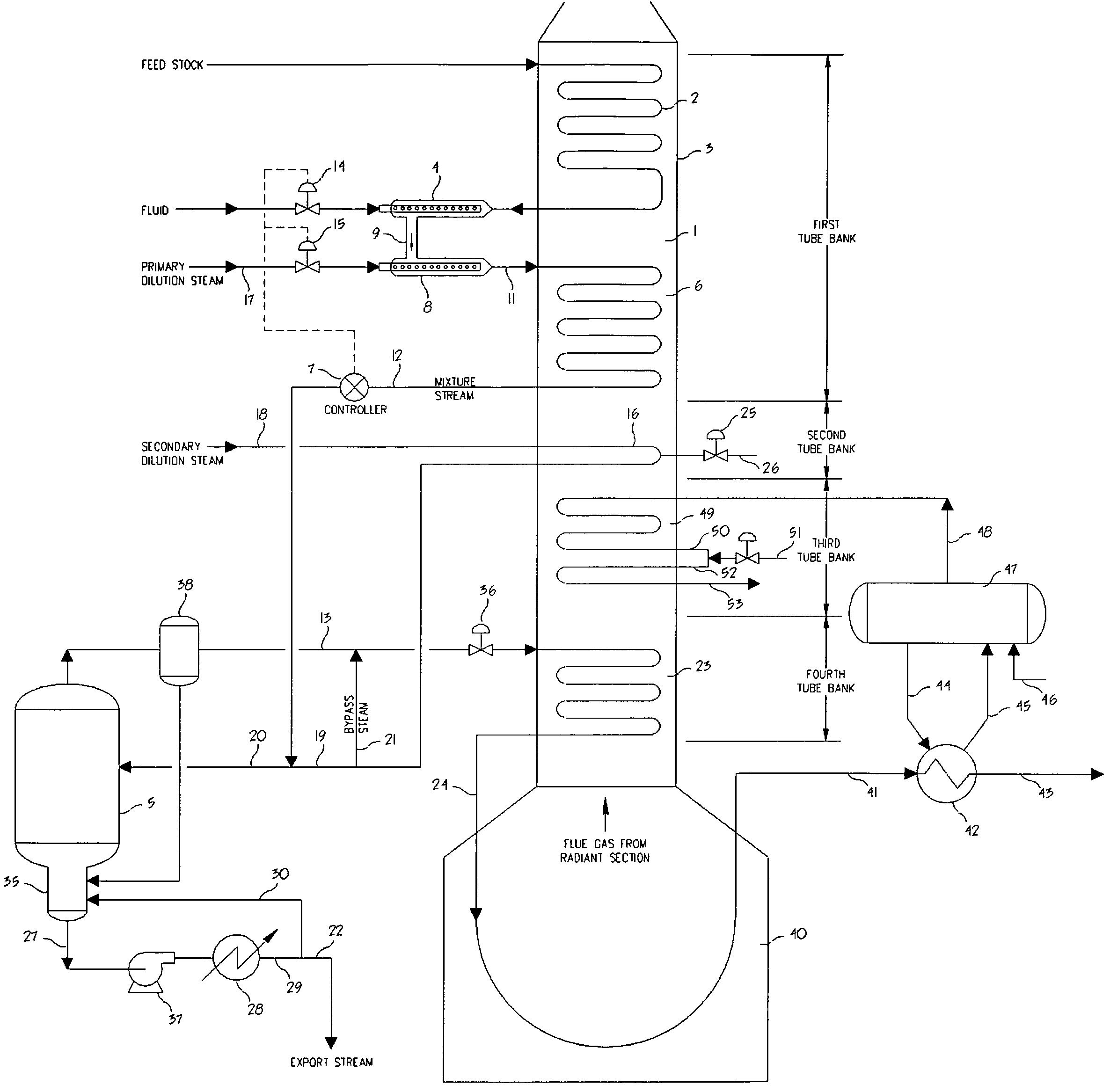

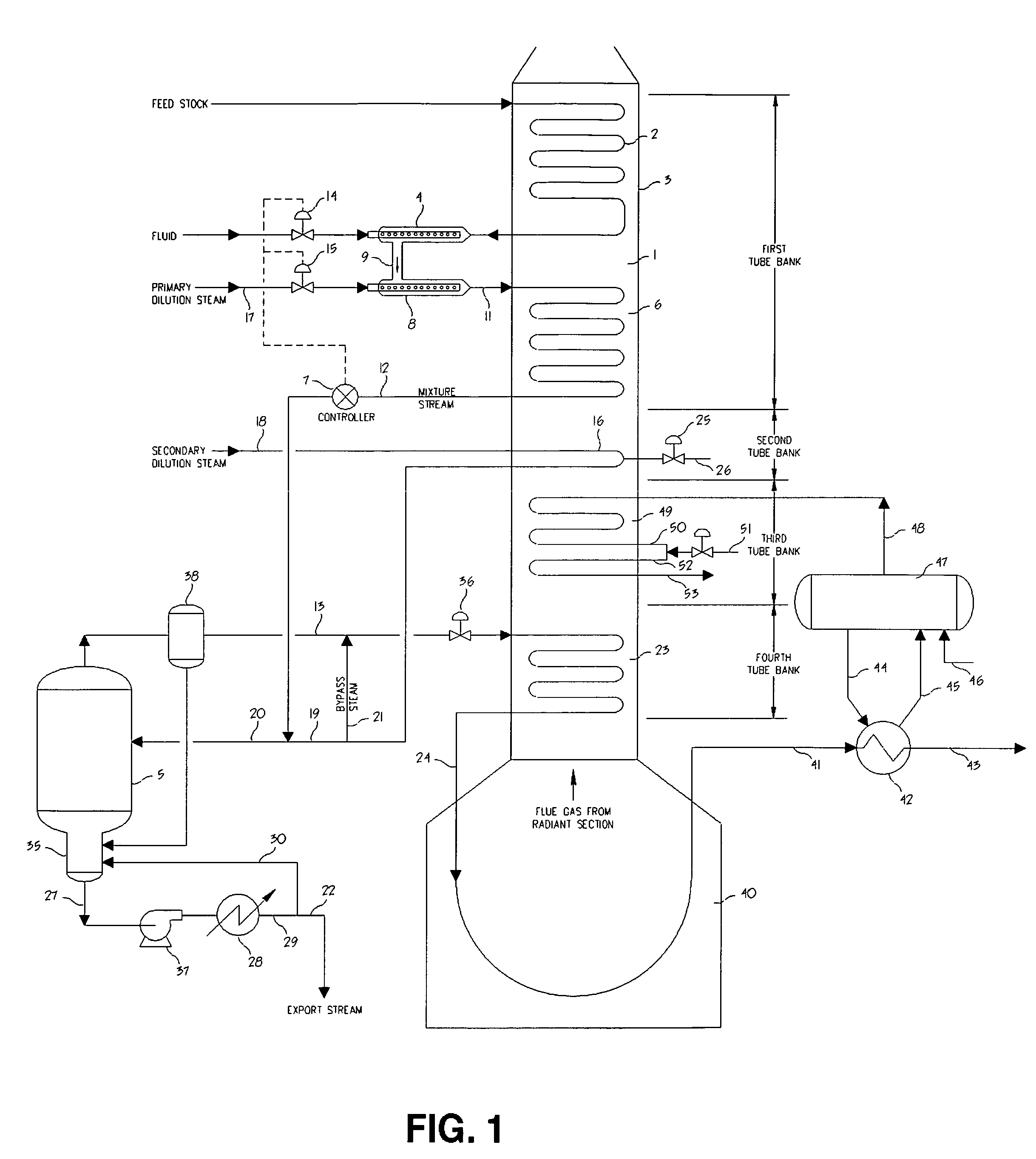

Process for steam cracking heavy hydrocarbon feedstocks

A process for cracking heavy hydrocarbon comprising heating the heavy hydrocarbon feedstock, mixing the heavy hydrocarbon feedstock with a fluid and / or a primary dilution steam stream to form a mixture, flashing the mixture to form a vapor phase and a liquid phase, separating and cracking the vapor phase, and cooling the product effluent in a transfer line exchanger, wherein the amount of the fluid and / or the primary dilution steam stream mixed with the heavy hydrocarbon feedstock is varied in accordance with at least one selected operating parameter of the process, such as the temperature of the flash stream before entering the flash / separator vessel.

Owner:EXXONMOBIL CHEM PAT INC

Process for steam cracking heavy hydrocarbon feedstocks

A process for cracking heavy hydrocarbon comprising heating the heavy hydrocarbon feedstock, mixing the heavy hydrocarbon feedstock with a fluid and / or a primary dilution steam stream to form a mixture, flashing the mixture to form a vapor phase and a liquid phase, separating and cracking the vapor phase, and cooling the product effluent in a transfer line exchanger, wherein the amount of the fluid and / or the primary dilution steam stream mixed with the heavy hydrocarbon feedstock is varied in accordance with at least one selected operating parameter of the process, such as the temperature of the flash stream before entering the flash / separator vessel.

Owner:EXXONMOBIL CHEM PAT INC

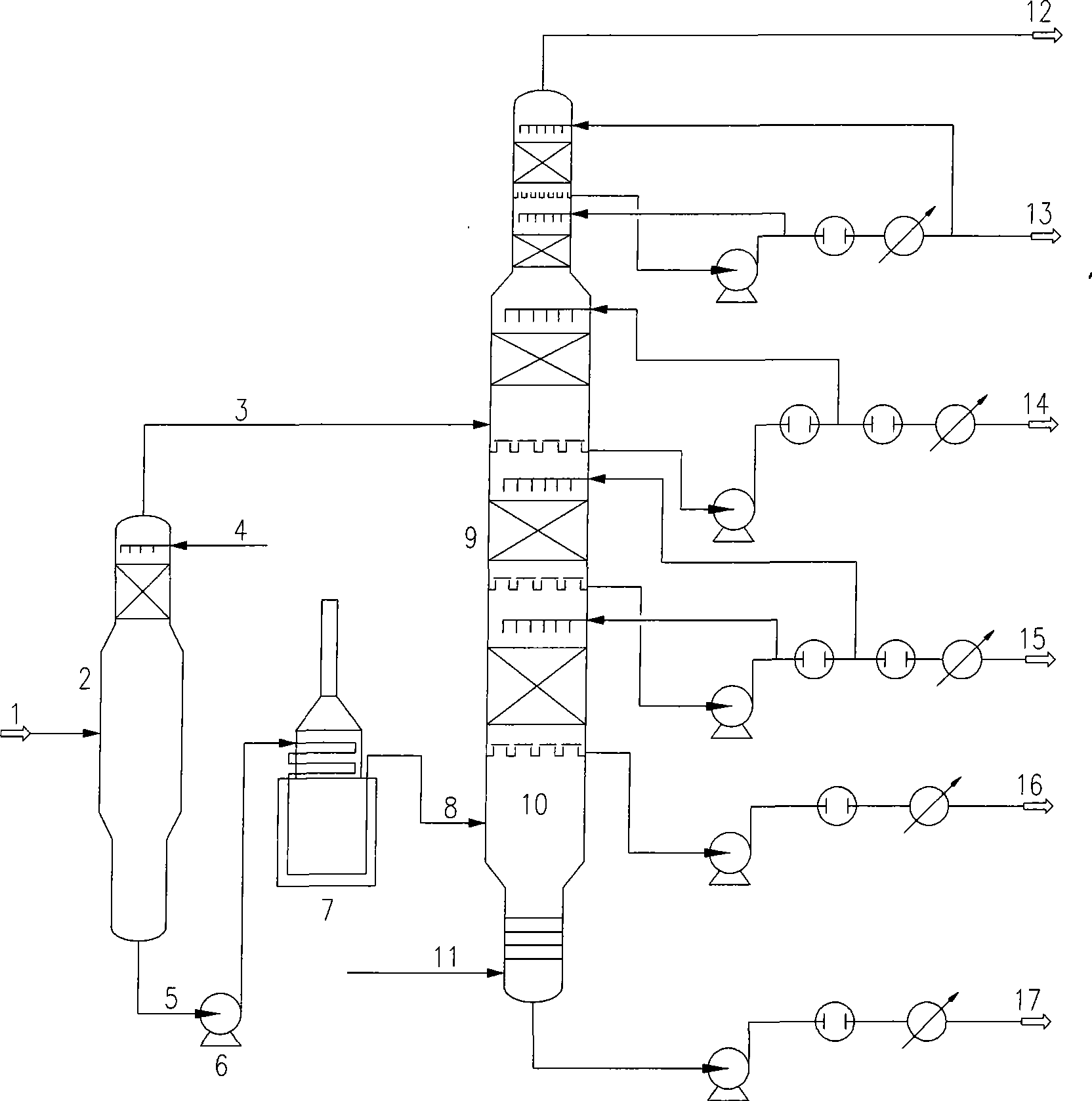

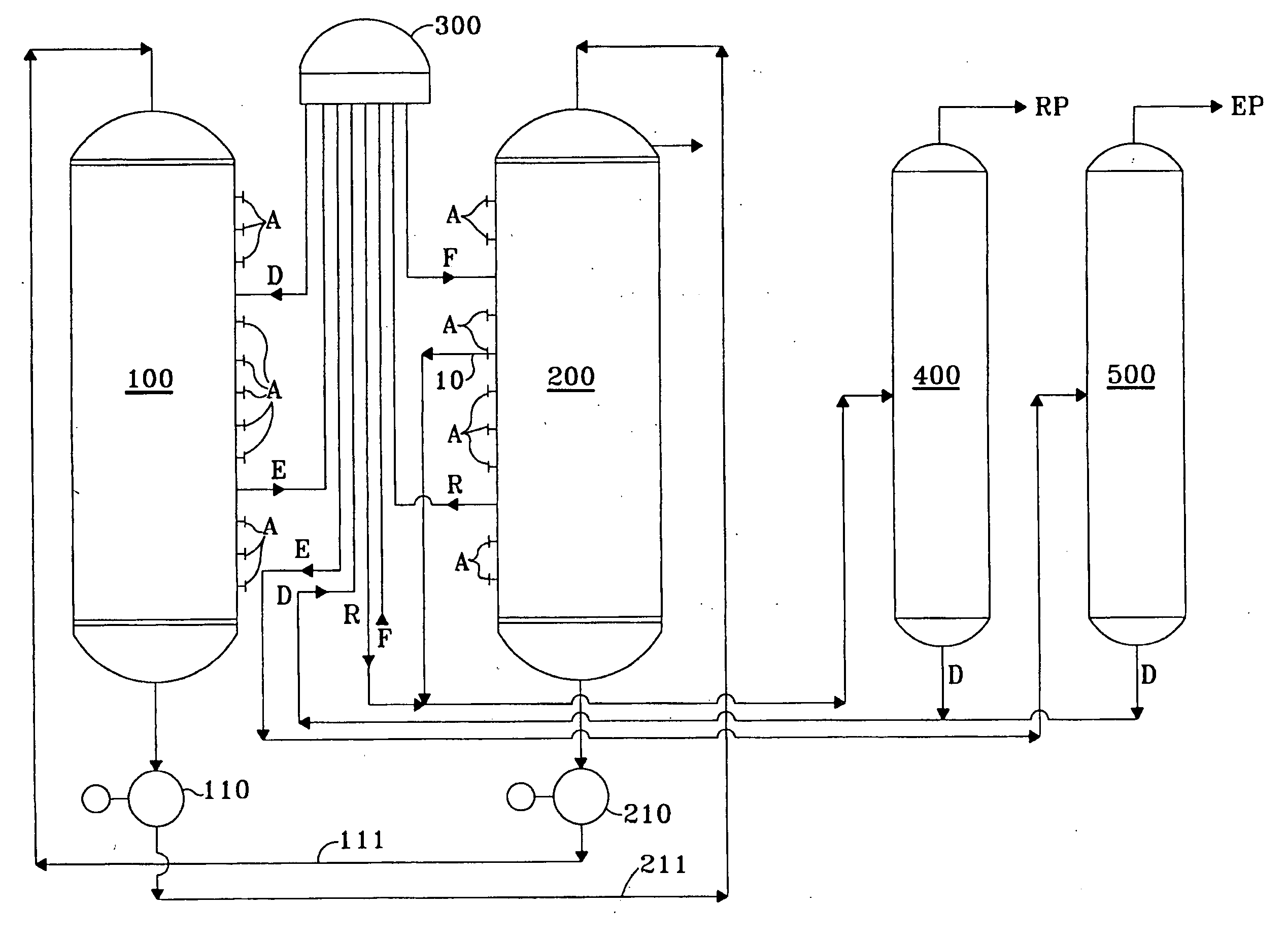

Atmospheric vacuum distillation method and apparatus with vacuum flash vaporizer

InactiveCN101376068AReduce the amount of feedEasy to handleVacuum distillation separationVacuum distillationVaporizationPulp and paper industry

The invention relates to an atmospheric and vacuum distillation device with a vacuum flash tower and a method thereof. The atmospheric and vacuum distillation device with a vacuum flash tower is characterized in that the vacuum flash tower arranged in front of a vacuum furnace is connected with the vacuum furnace and a vacuum tower through a pump and a pipeline. Constant bottom oil (1) is introduced into the vacuum flash tower (2)at first, and the operation pressure at the top part of the vacuum flash tower is higher than the operation pressure at the top part of the vacuum tower (9) by10 to 200mmHg; Flash cap gas (3) is introduced into the upper part or the lower part of an outlet for a side product which is similar to Flash cap gas fraction; flash bottom oil (5) is introduced into the vacuum furnace (7) through a flash bottom oil pump (6); when the flash bottom oil is heated to 350 to 430 degrees, air-liquid mixing vacuum tower feed material is obtained through partial vaporization and is introduced into a flash evaporation segment (10) of the vacuum tower through a transfer line (8); and products with different fractions are drawn from the side of the vacuum tower and vacuum residue is drawn from the bottom of the vacuum tower. Through adding the vacuum flash tower to improve the working process of the atmospheric and vacuum distillation device, the invention achieves the advantages of increasing treatment capacity, increasing vacuum distillation yield, and reducing energy consumption.

Owner:TIANJIN UNIV +2

Semiconductor integrated circuit device capable of controlling impedance

ActiveUS20050040845A1Input/output impedence modificationReliability increasing modificationsExternal referenceEngineering

A semiconductor integrated circuit device is connected to an external reference resistor, including an impedance control circuit for generating impedance control codes variable with impedances established by the external reference resistor. An input circuit receives an external signal through an input transfer line and forwards the external signal to an internal circuit. A termination circuit terminates the input transfer line in response to at least one of the impedance control code. An output circuit drives an output transfer line in accordance with an output signal. Impedance is variable with the control codes.

Owner:SAMSUNG ELECTRONICS CO LTD

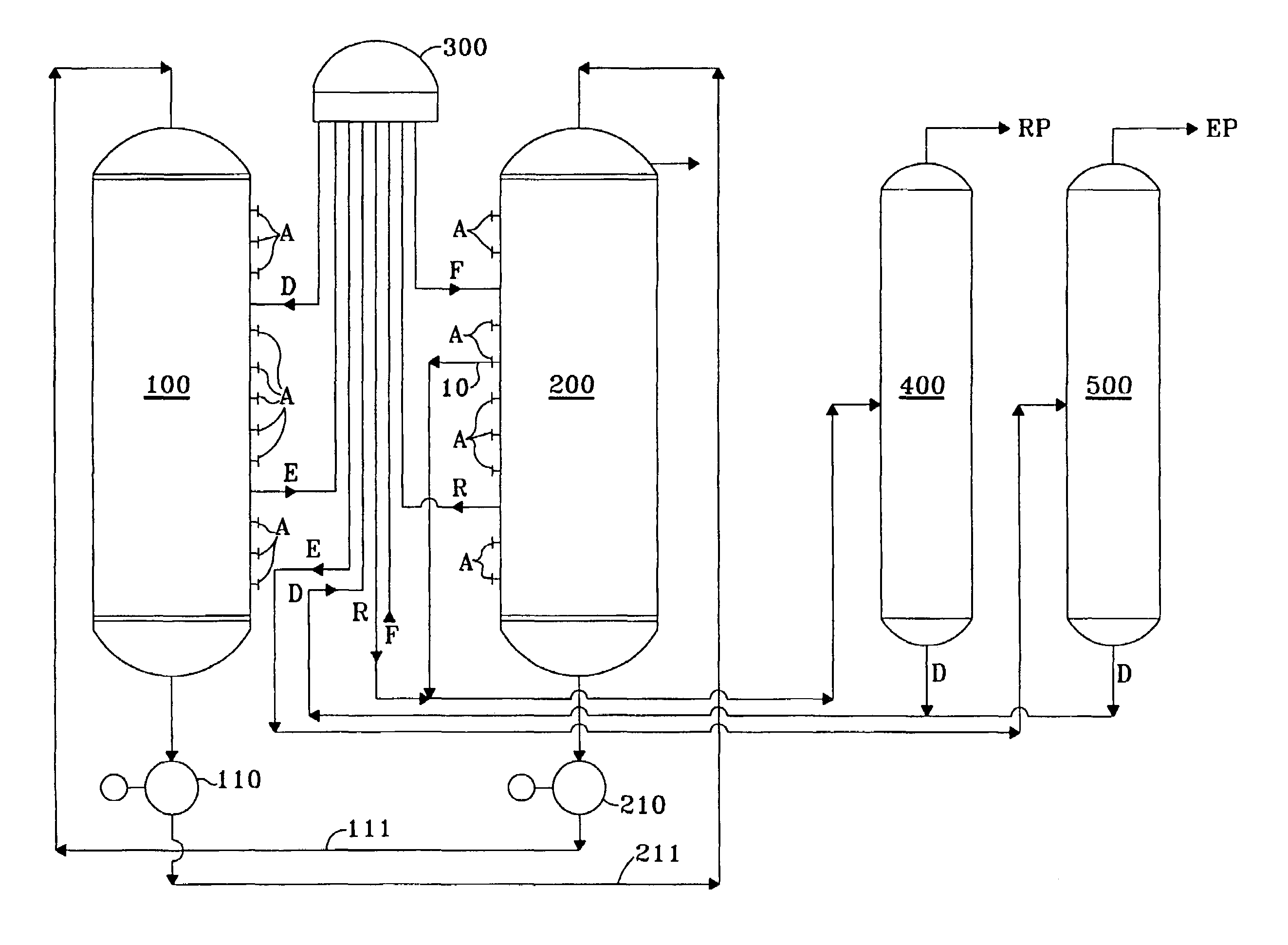

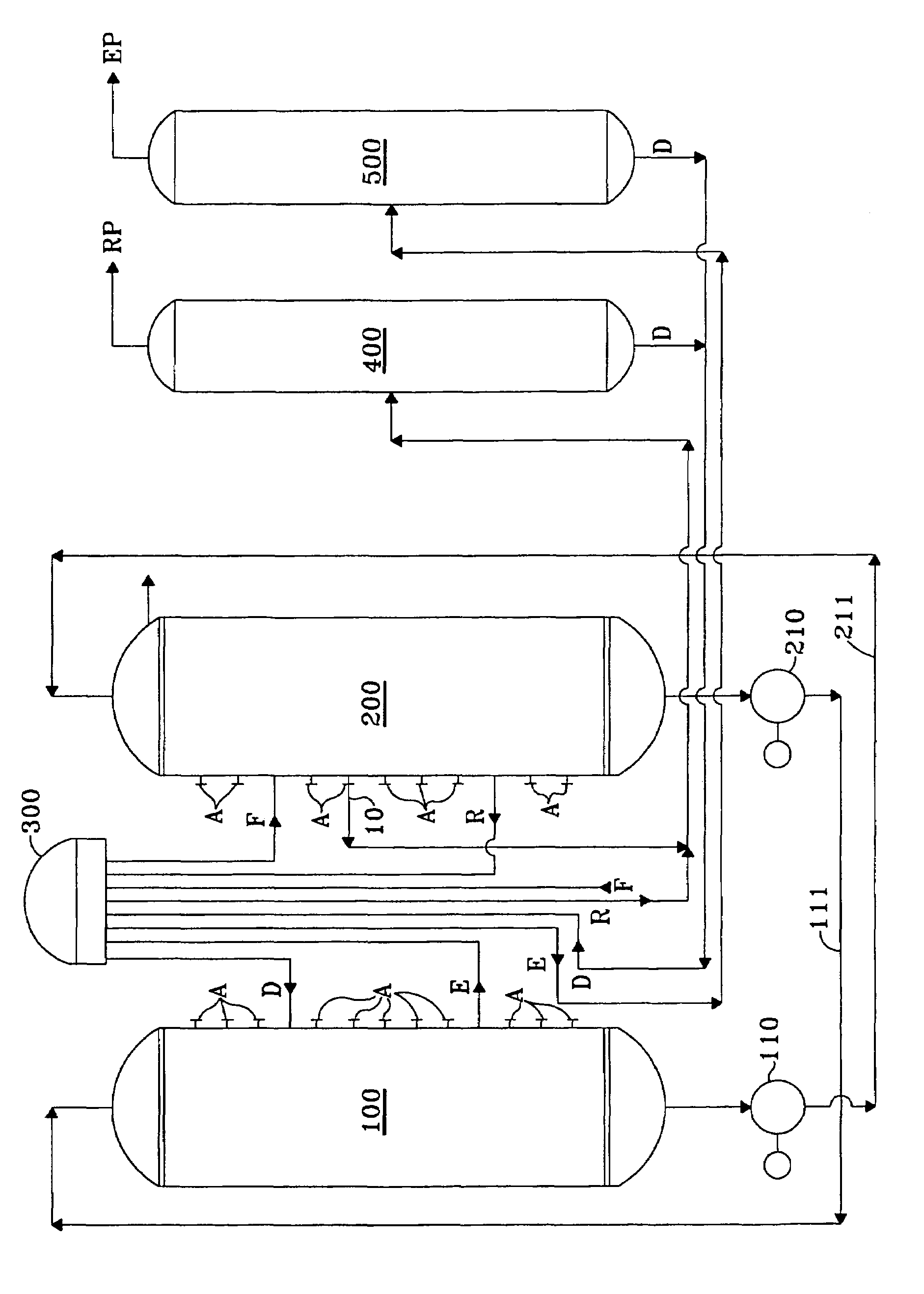

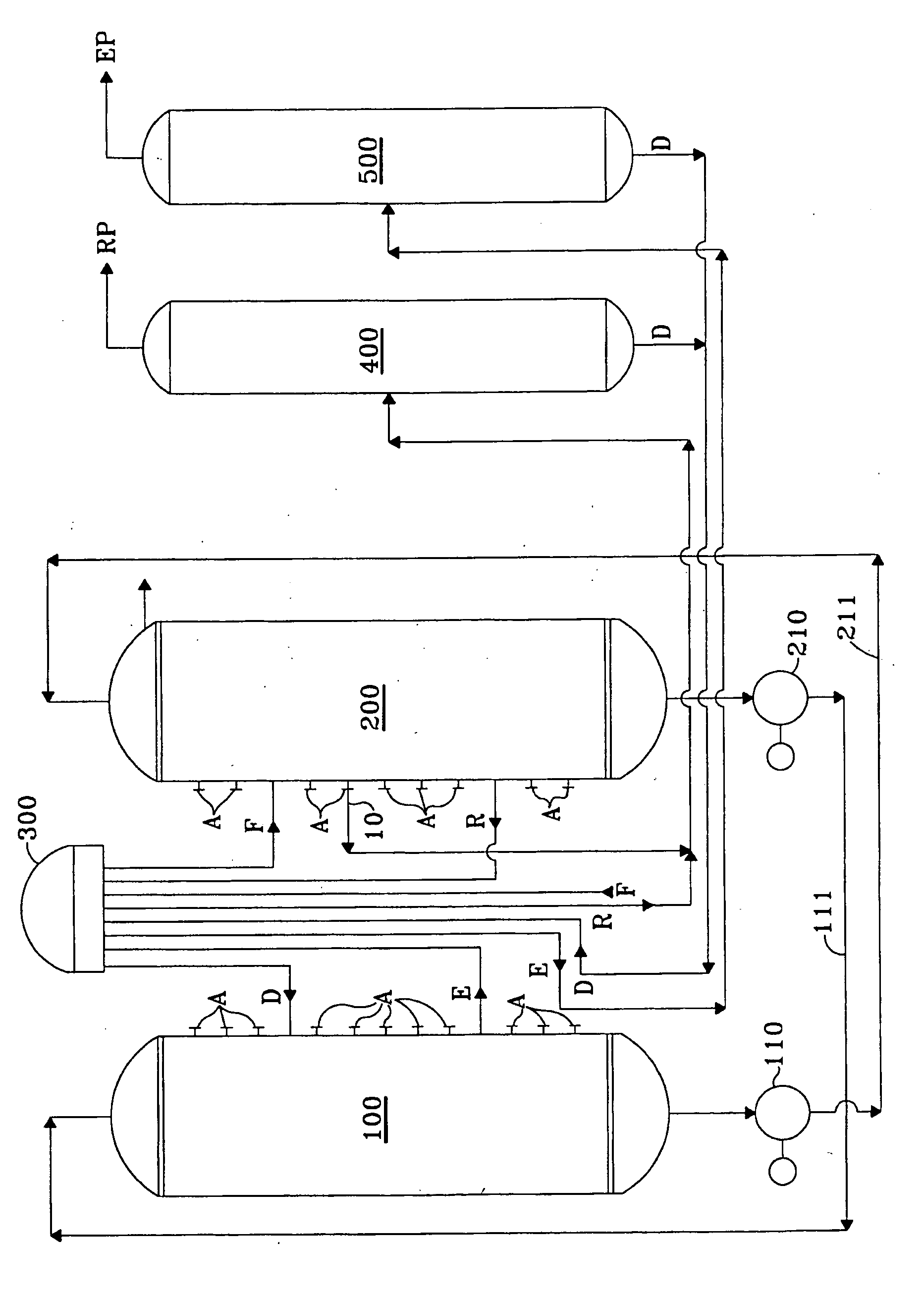

Product recovery from simulated-moving-bed adsorption

Product purity from or capacity of a simulated-moving-bed adsorptive separation process is increased by flushing the contents of the transfer line previously used to remove the raffinate stream away from the adsorbent chamber, preferably into the raffinate column used to separate desorbent from raffinate product. Preferably a stream from the adsorbent chamber at an intermediate point between the feed entry point and raffinate withdrawal is used as the flushing liquid. This flush step eliminates the passage of a quantity of the raffinate material into the adsorbent chamber in the transfer-line flush period or when the process conduit is subsequently used to charge the feed stream to the adsorbent chamber.

Owner:UOP LLC

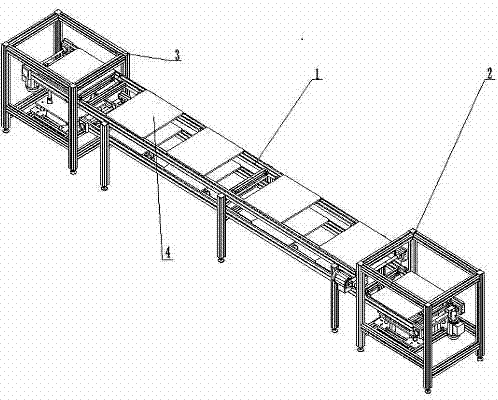

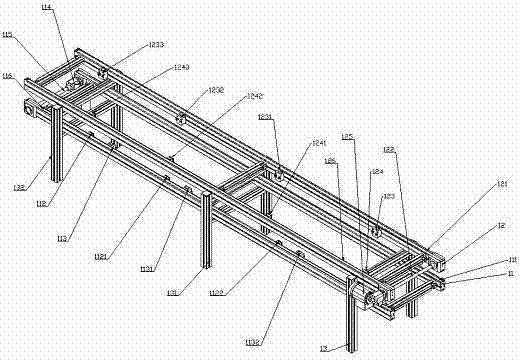

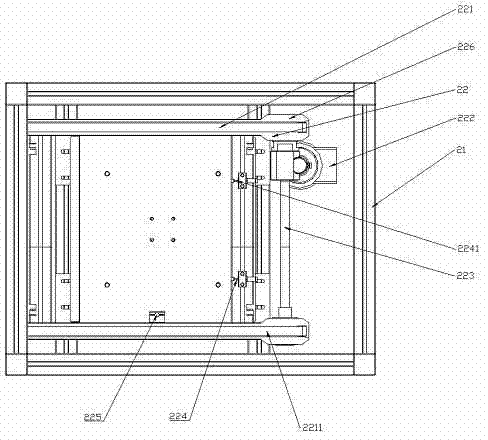

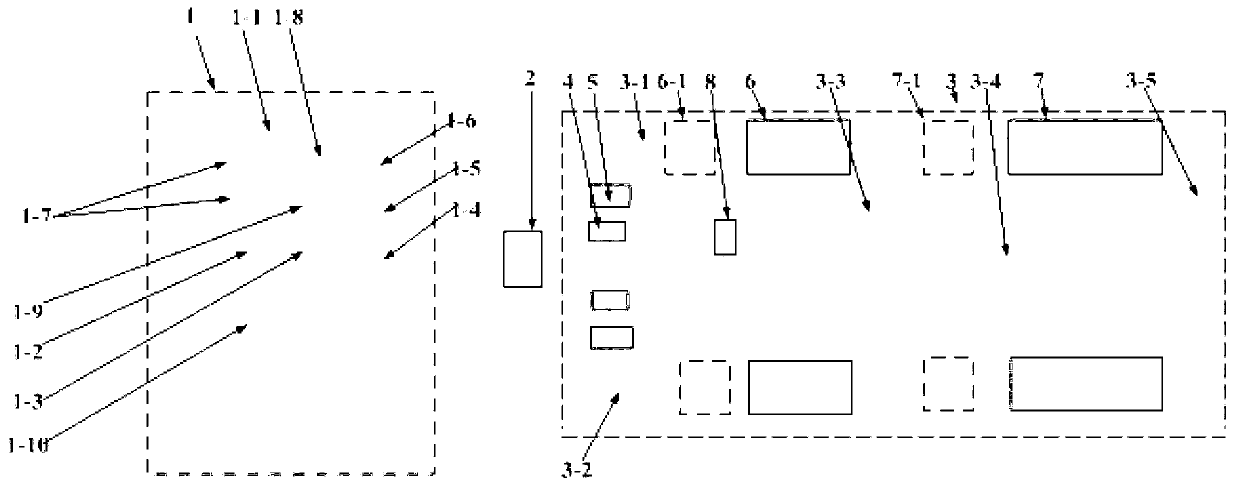

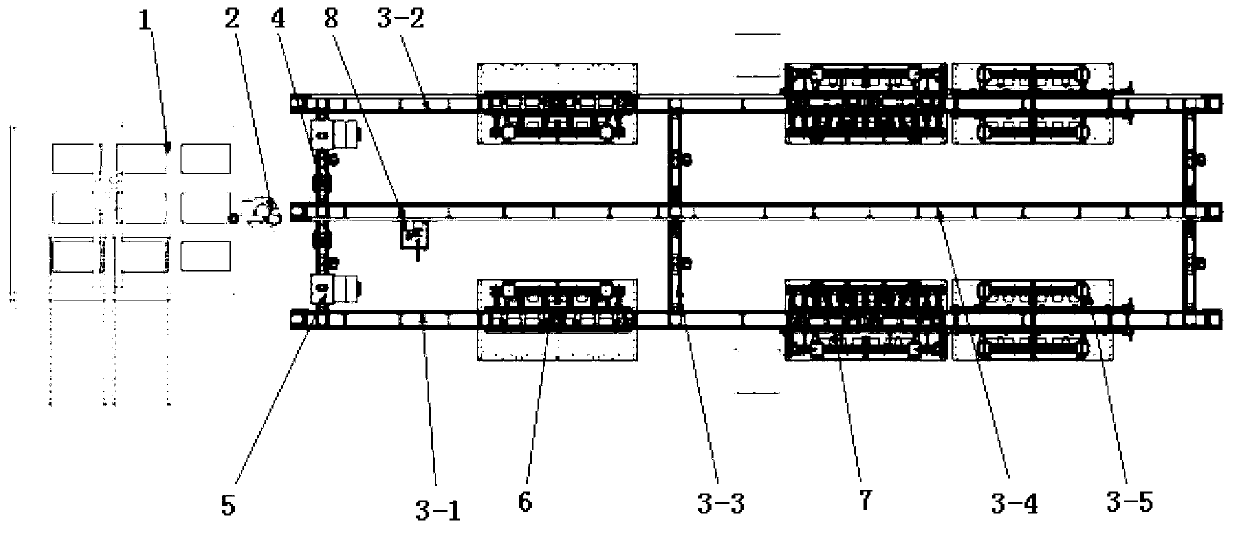

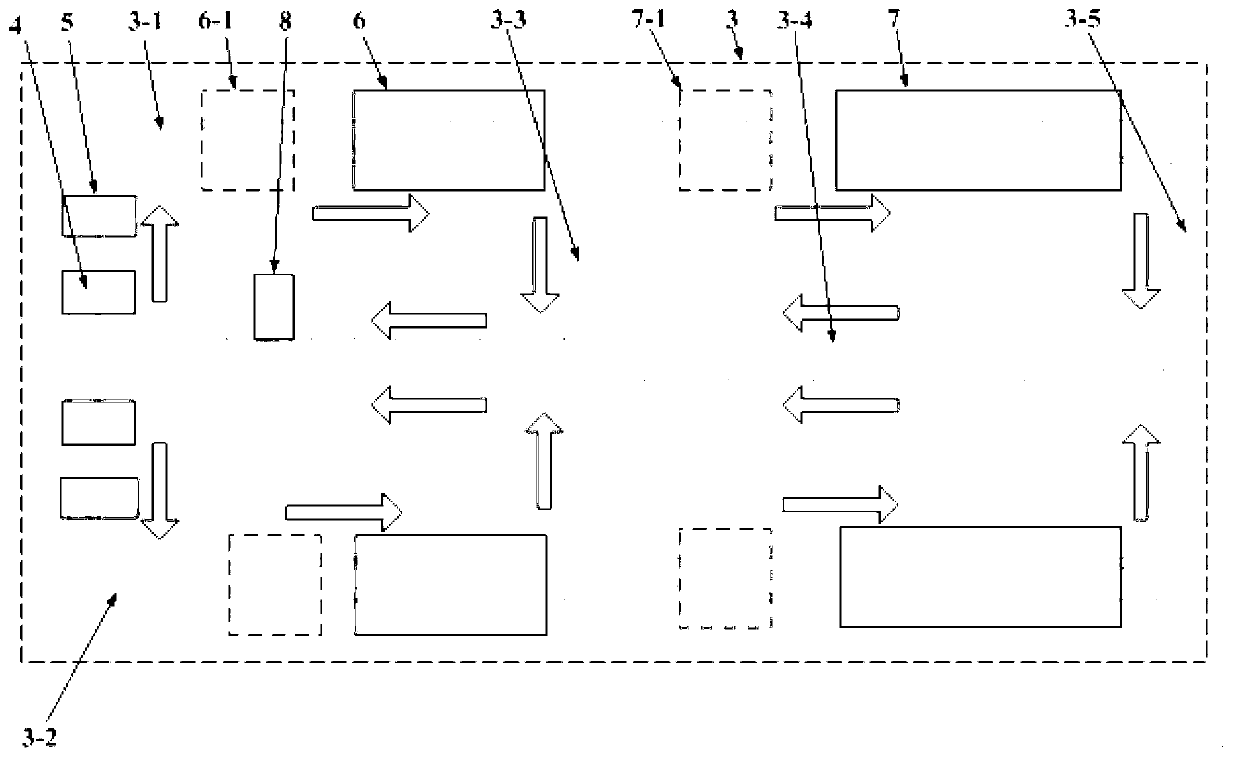

Method and conveying system for intelligently and circularly conveying products in vertical lift manner

InactiveCN104724455ARealize intelligenceFully automatedControl devices for conveyorsMechanical conveyorsProcess engineeringData management

The invention discloses a method and a conveying system for intelligently and circularly conveying products in a vertical lift manner. The method includes: subjecting product trays on a conveying line to reverse circular conveying between an upper tier and a lower tier, allowing vertical lift circular conveying at two ends of the double-tier conveying line, and setting RFID (radio frequency identification) passive reader-writers on the conveying line. The conveying system comprises the double-tier conveying line, lift conveyers mounted at two ends of the double-tier conveying line and a product tray assembly operating on the double-tier conveying line. The method and the conveying system have the advantages that products are under intelligent conveying control during conveying, multi-point operation with different spans is achieved for a production site, less space is used, conveying efficiency is high, input cost is low, the products can be subjected to data management during line production, the produced products are traceable, and automatic productivity of the whole process can be comprehensively improved.

Owner:KEN DAYSTAR SHANGHAI AUTOMATION SYST

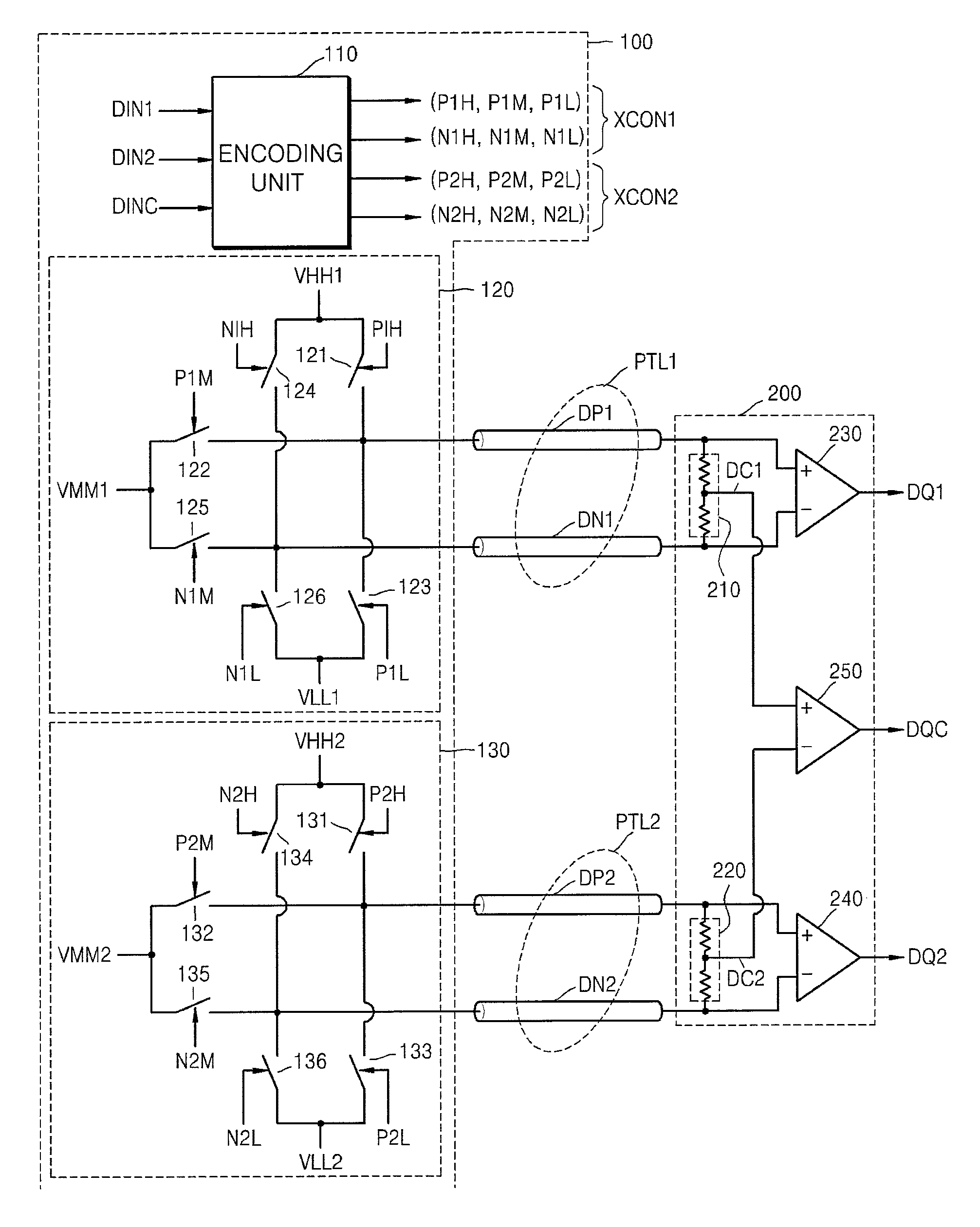

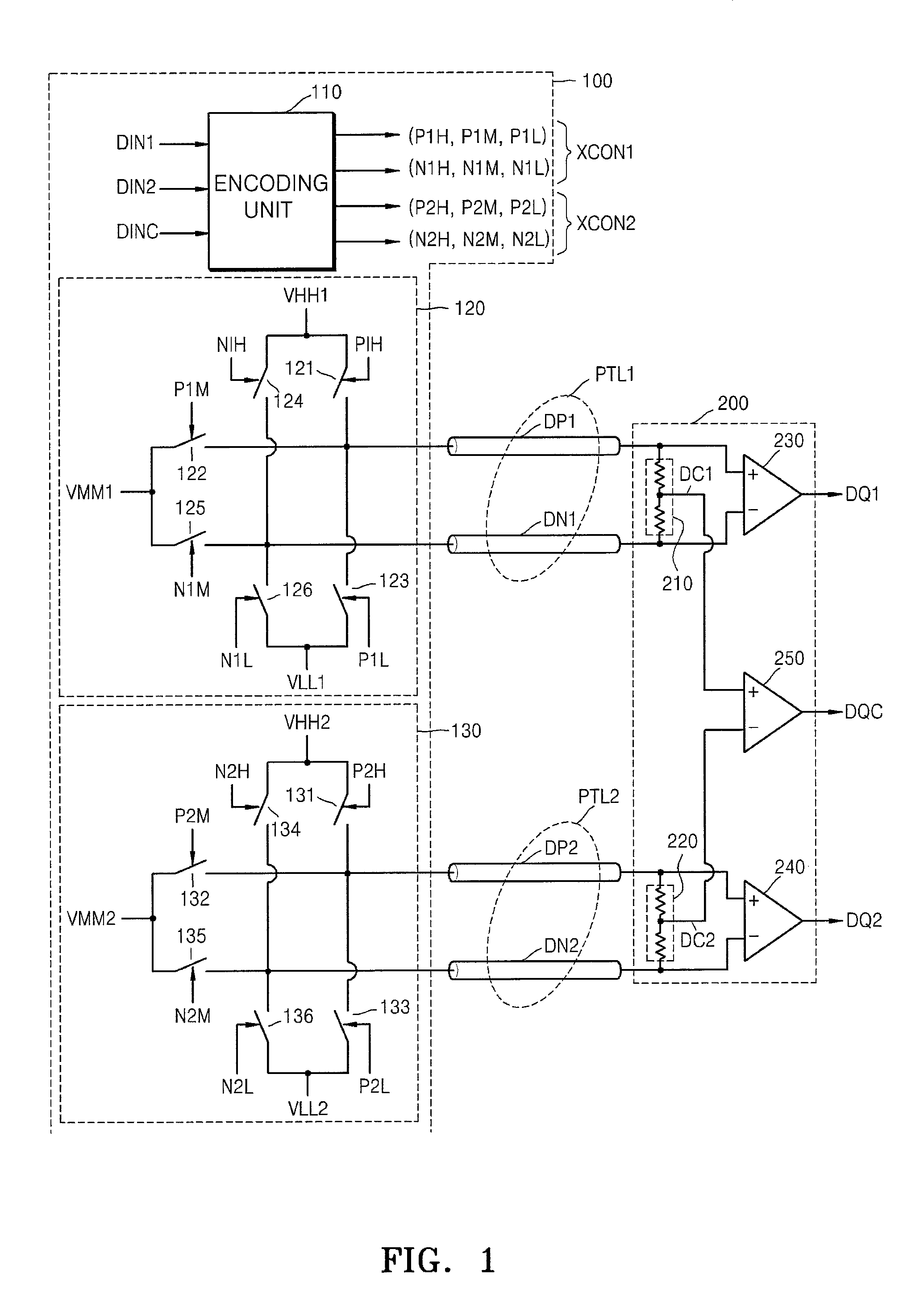

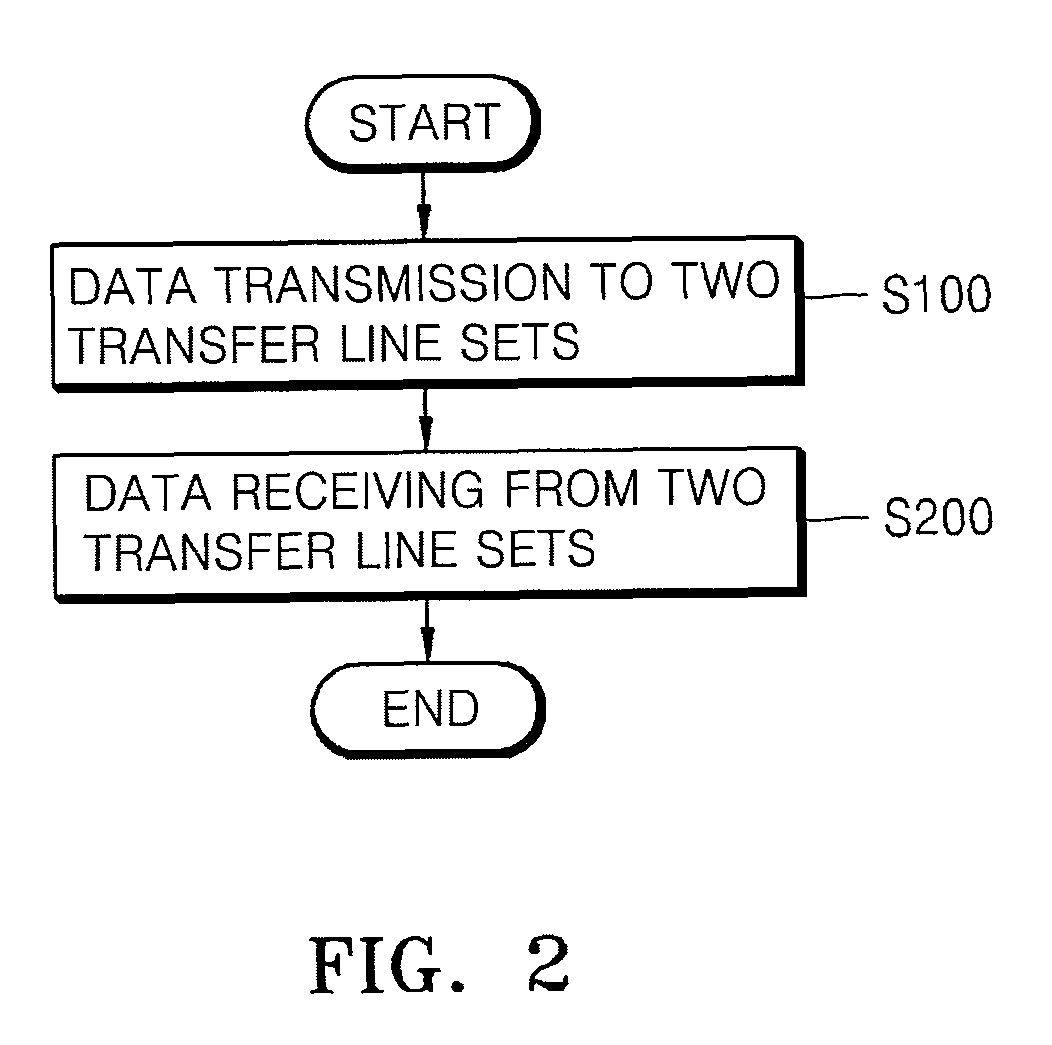

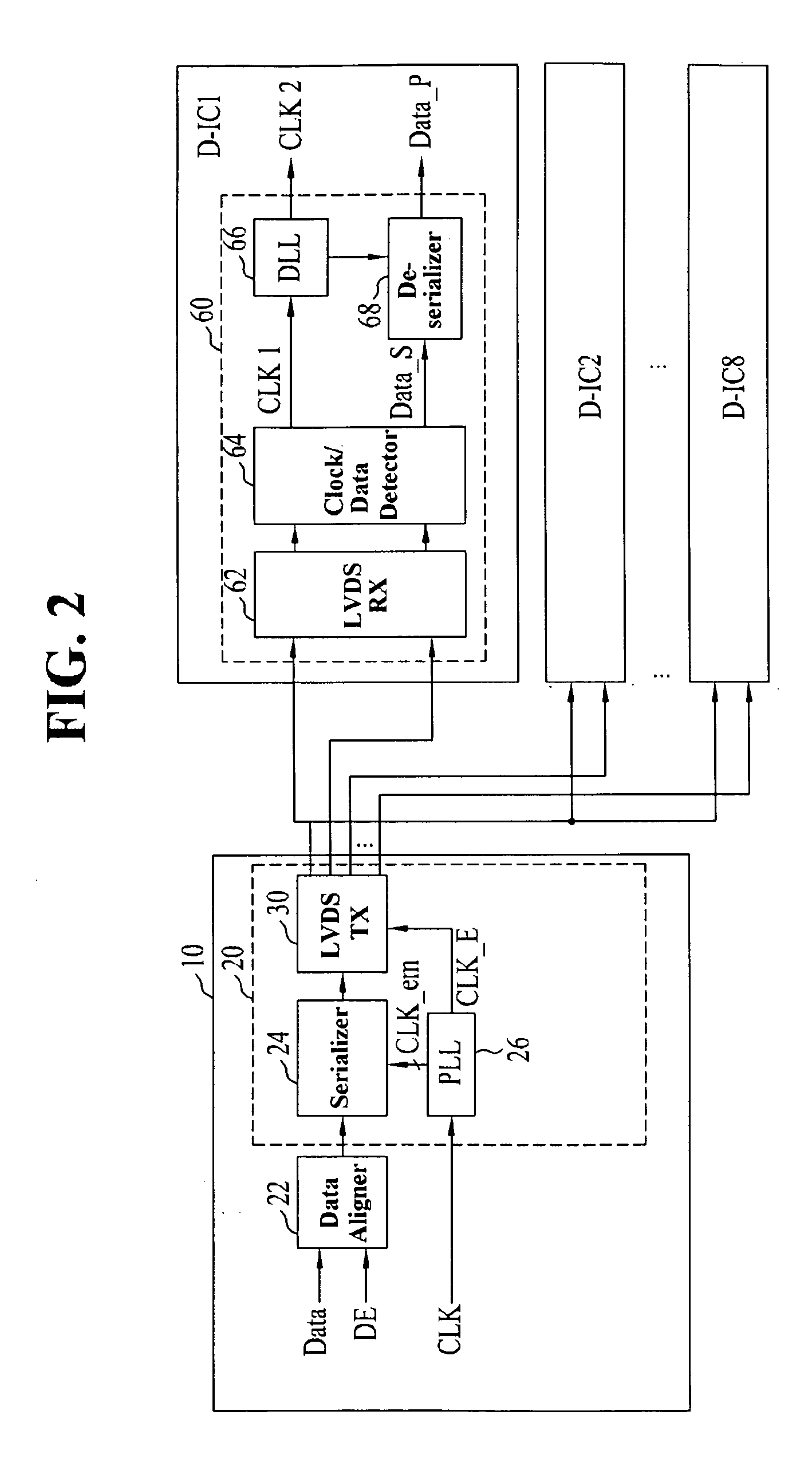

Differential data transferring system and method using three level voltages

ActiveUS8284848B2Improve efficiencyChannel dividing arrangementsTransmission line coupling arrangementsThree levelTransfer system

Owner:TLI

Methods for inhibiting hydrate blockage in oil and gas pipelines using amide compounds

A method and an amide composition used therein for inhibiting, retarding, mitigating, reducing, controlling and / or delaying formation of hydrocarbon hydrates or agglomerates of hydrates. The method may be applied to prevent or reduce or mitigate plugging of conduits, pipes, transfer lines, valves, and other places or equipment where hydrocarbon hydrate solids may form under the conditions. At least one amide compound is added into the process stream, where the compound may be mixed with another compound selected from amino alcohols, esters, quaternary ammonium, phosphonium or sulphonium salts, betaines, amine oxides, other amides, simple amine salts, and combinations thereof.

Owner:CLARIANT INT LTD

Automatic verification system of low-voltage current transformer

ActiveCN103344895AStrong targetingRealize multi-station sub-indicator verificationTesting dielectric strengthMaterial analysis by optical meansLow voltageControl engineering

The invention relates to an automatic verification system of a low-voltage current transformer in power industries. The automatic verification system comprises an input-output warehouse connection station, a grid-shaped frame type conveyor line and a feeding and blanking rotor which is connected with the input-output warehouse connection station and the grid-shaped frame type conveyor line, wherein the grid-shaped frame type conveyor line comprises a main verification conveyor line and a reserved verification conveyor line with up and down symmetrical structures, feeding and blanking station modules, appearance inspection station modules, insulation voltage-withstanding testing station modules and error verification station modules are sequentially arranged on the verification conveyor lines, middle return conveyor lines perpendicular to the verification conveyor lines are arranged between the insulation voltage-withstanding testing station modules and the error verification station modules, terminal return conveyor lines are arranged behind the error verification station modules, a conveyor line shared by the main verification conveyor line and the reserved verification conveyor line is a blanking conveyor line, and a labeling sorting station module is arranged at a part, which is close to the feeding and blanking station modules, of the blanking conveyor line; buffer areas are arranged between detection station modules on the verification conveyor lines.

Owner:河北海纳电测仪器股份有限公司

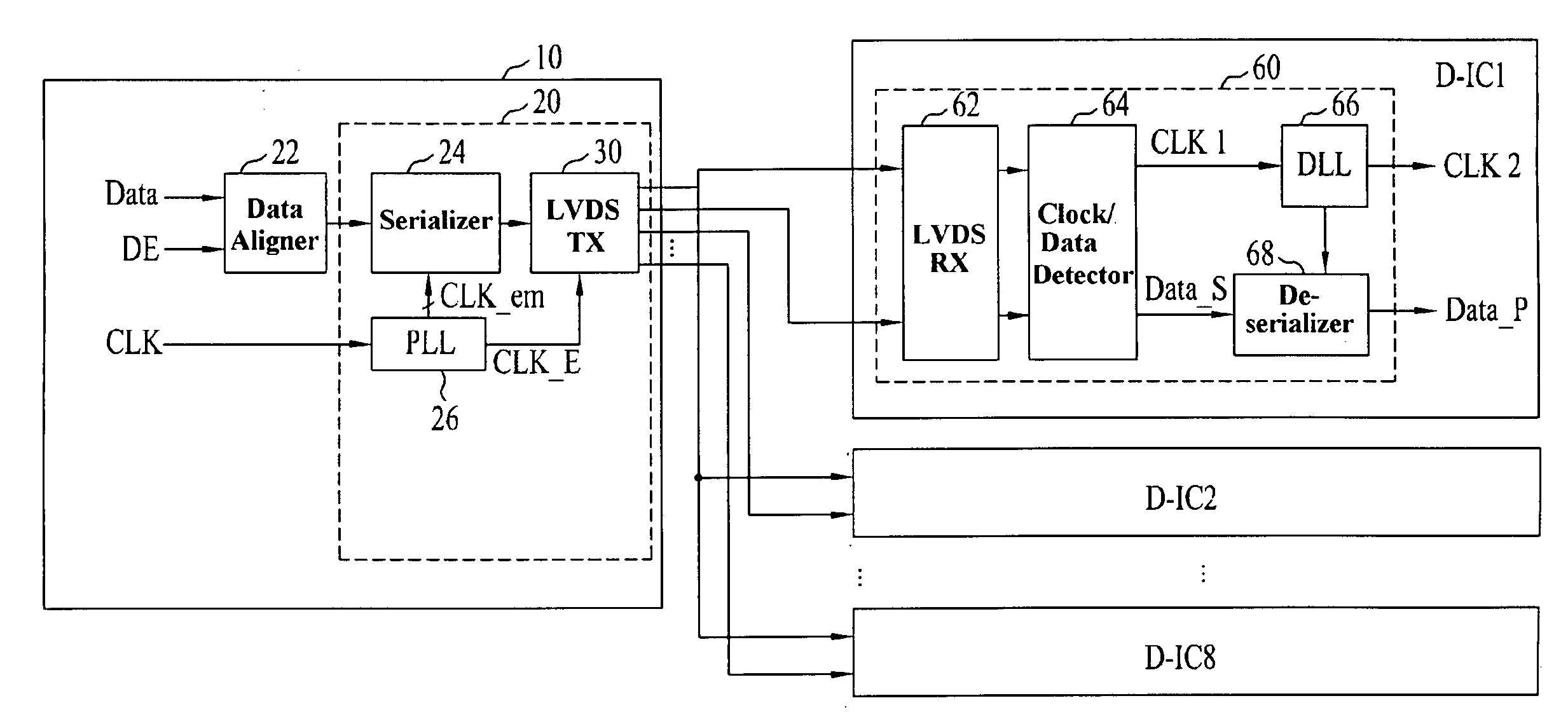

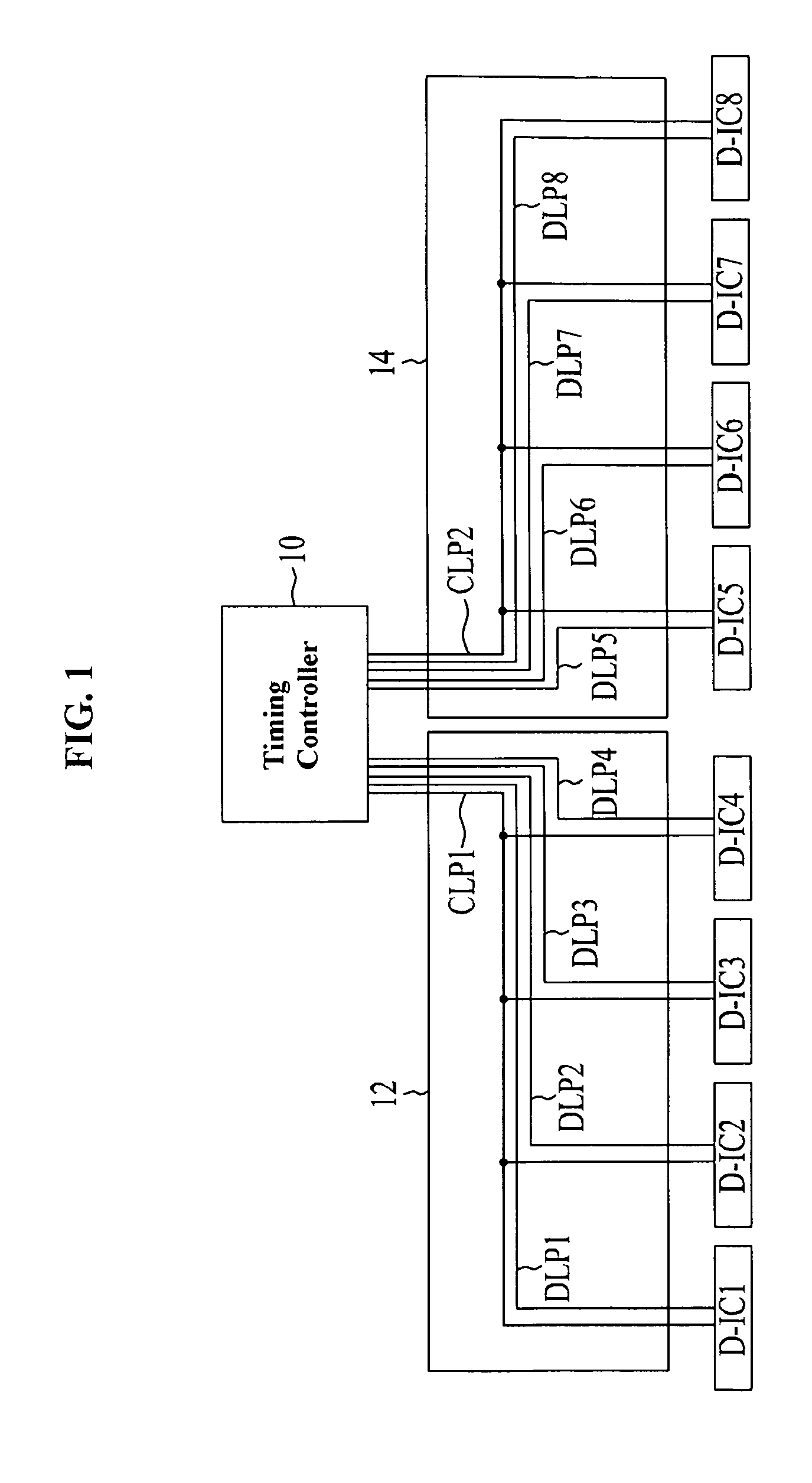

Apparatus and method for data interface of flat panel display device

ActiveUS20090167750A1Reduce in quantityAccurate data samplingCathode-ray tube indicatorsInput/output processes for data processingDigital dataFlat panel display

An apparatus and method for data interface of a flat panel display device, which is capable of transferring clocks in a state, in which the clocks are embedded in digital data, thereby reducing the number of transfer lines, is disclosed. The apparatus includes a transmitter unit built in a timing controller, to transmit transfer data with an embedding clock embedded between successive pieces of data, and a clock enable signal to indicate the embedding clock, and receiver units respectively built in a plurality of data integrated circuits connected to the timing controller, to separate and detect the embedding clock and the data from the transfer data, in response to the clock enable signal.

Owner:LG DISPLAY CO LTD

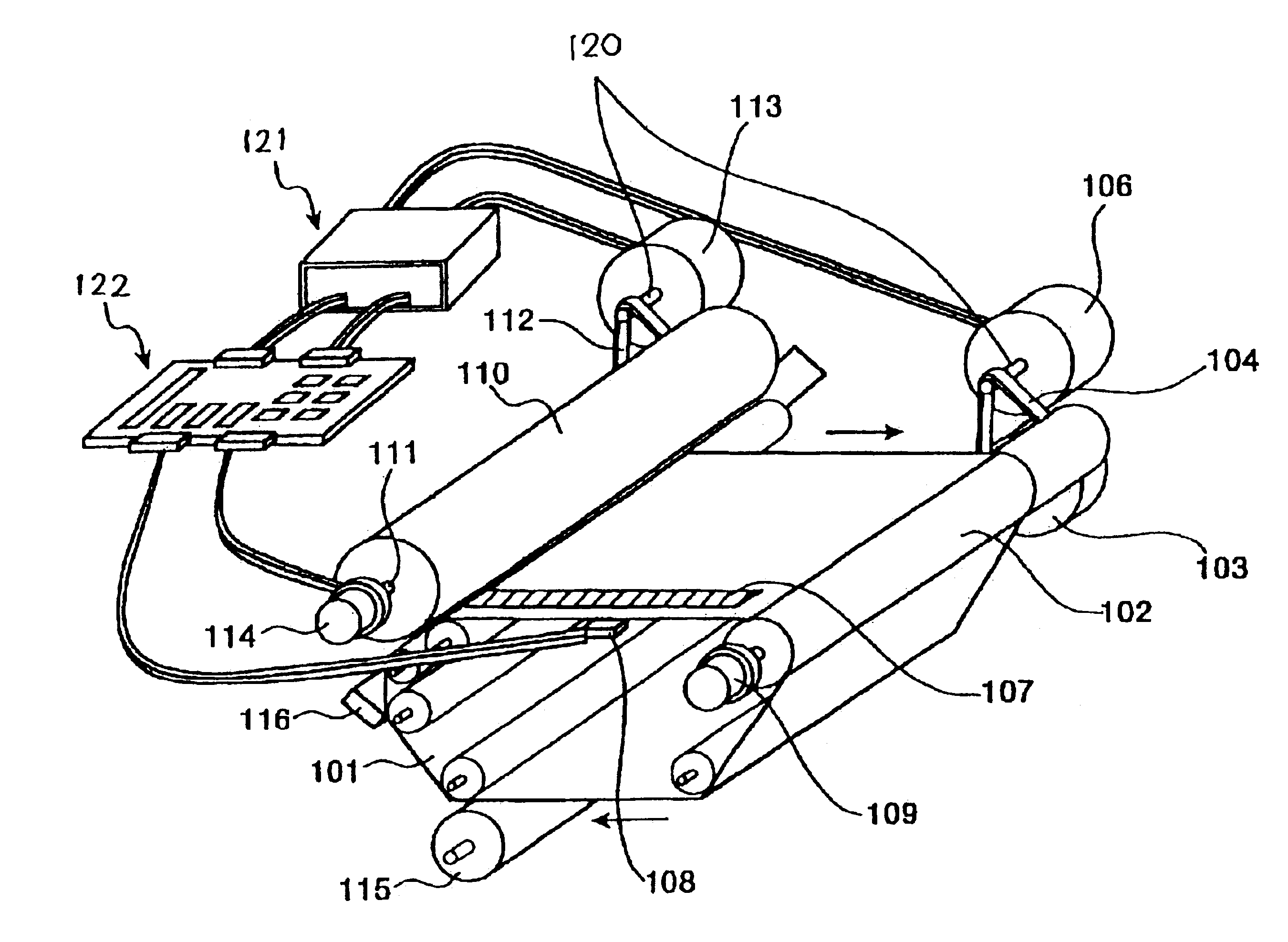

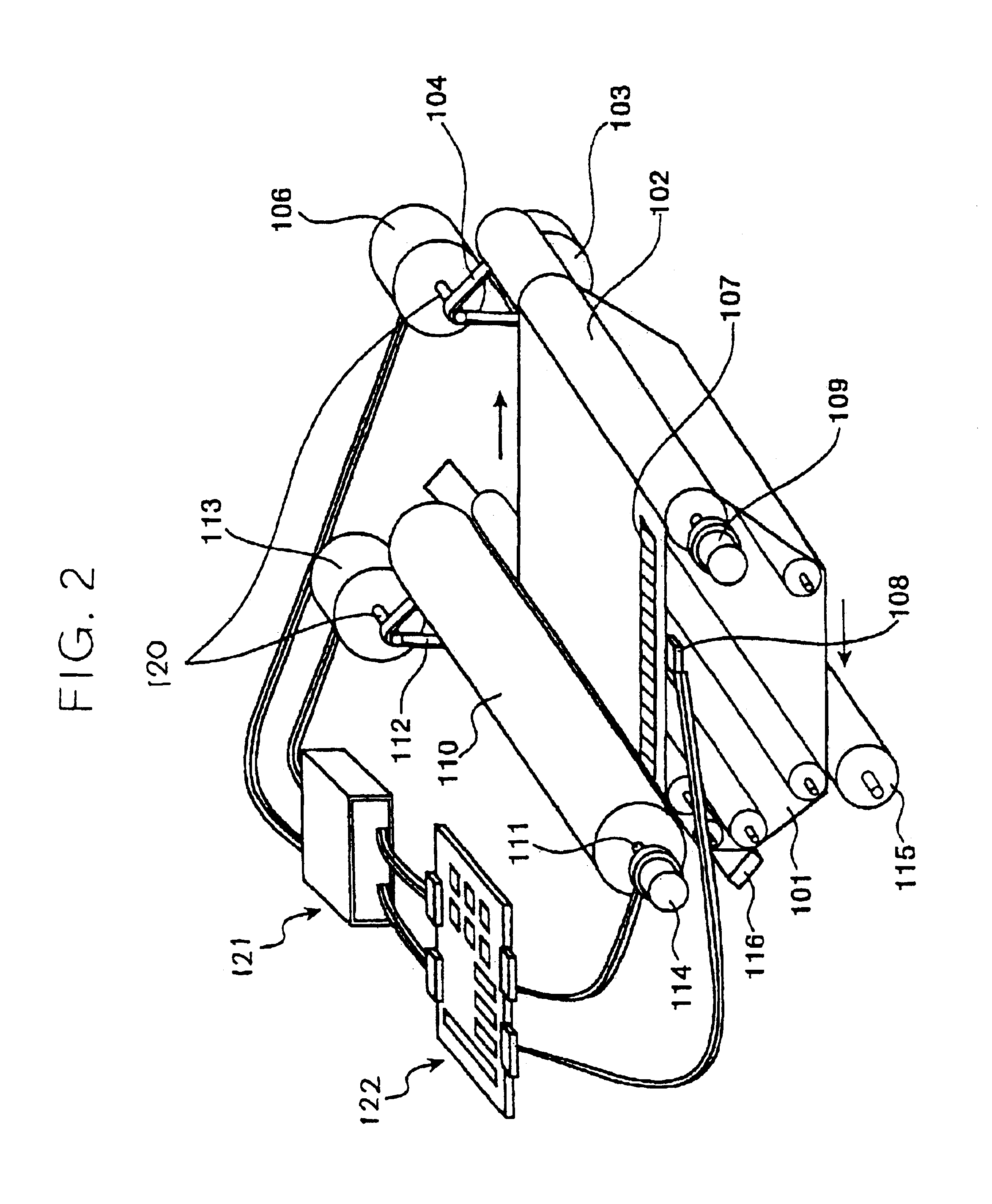

Belt moving device and image forming apparatus including the same

InactiveUS6925279B2Highly accurate position controlReduce bandingElectrographic process apparatusInformation controlDrive shaft

A belt moving device of the present invention includes a drive shaft for moving the belt and a drive transfer line for transferring the output torque of a motor to the drive shaft. A marker sensor senses a marker positioned on the belt to thereby determine the position of the belt in the direction of movement. A rotation condition sensor senses the rotation condition of the drive shaft. A first correction information generating circuit generates, based on the output of the marker sensor, correction information for correcting the position of the belt. A second correction information generating circuit generates, based on the output of the rotation condition sensor, correction information for correcting the rotation condition of the drive shaft. A controller controls the movement of the motor in accordance with the correction information output from the first and second correction information generating circuits.

Owner:RICOH KK

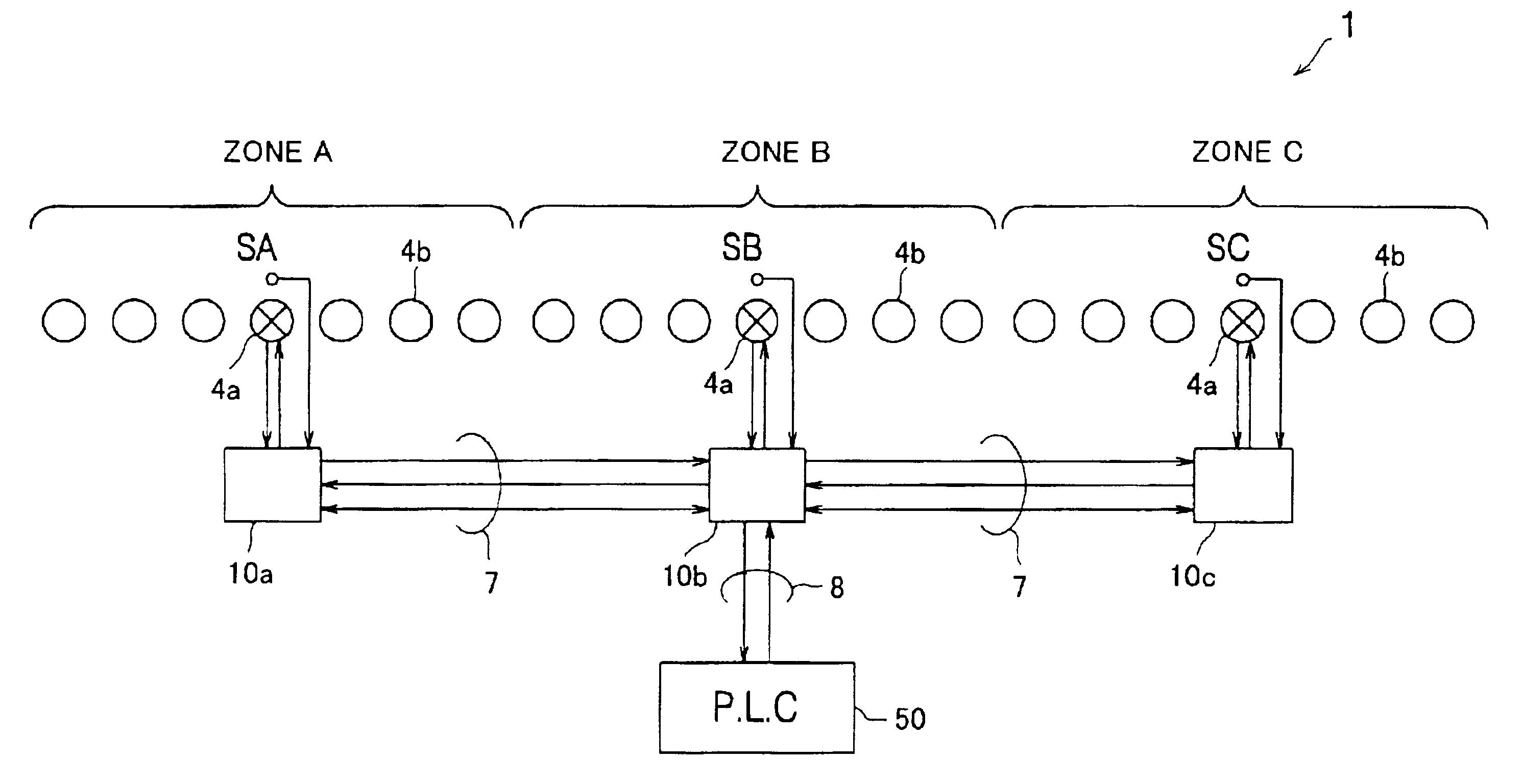

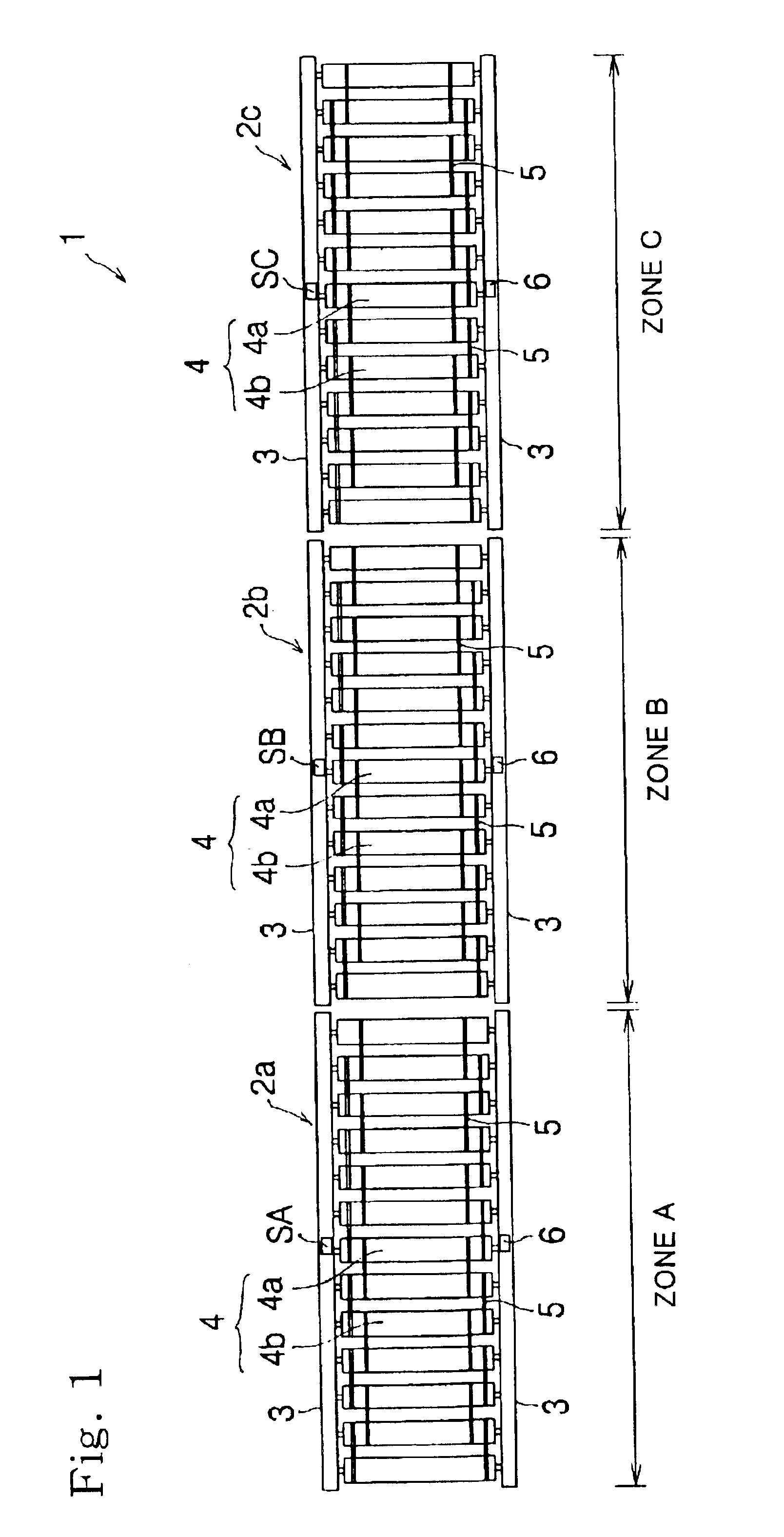

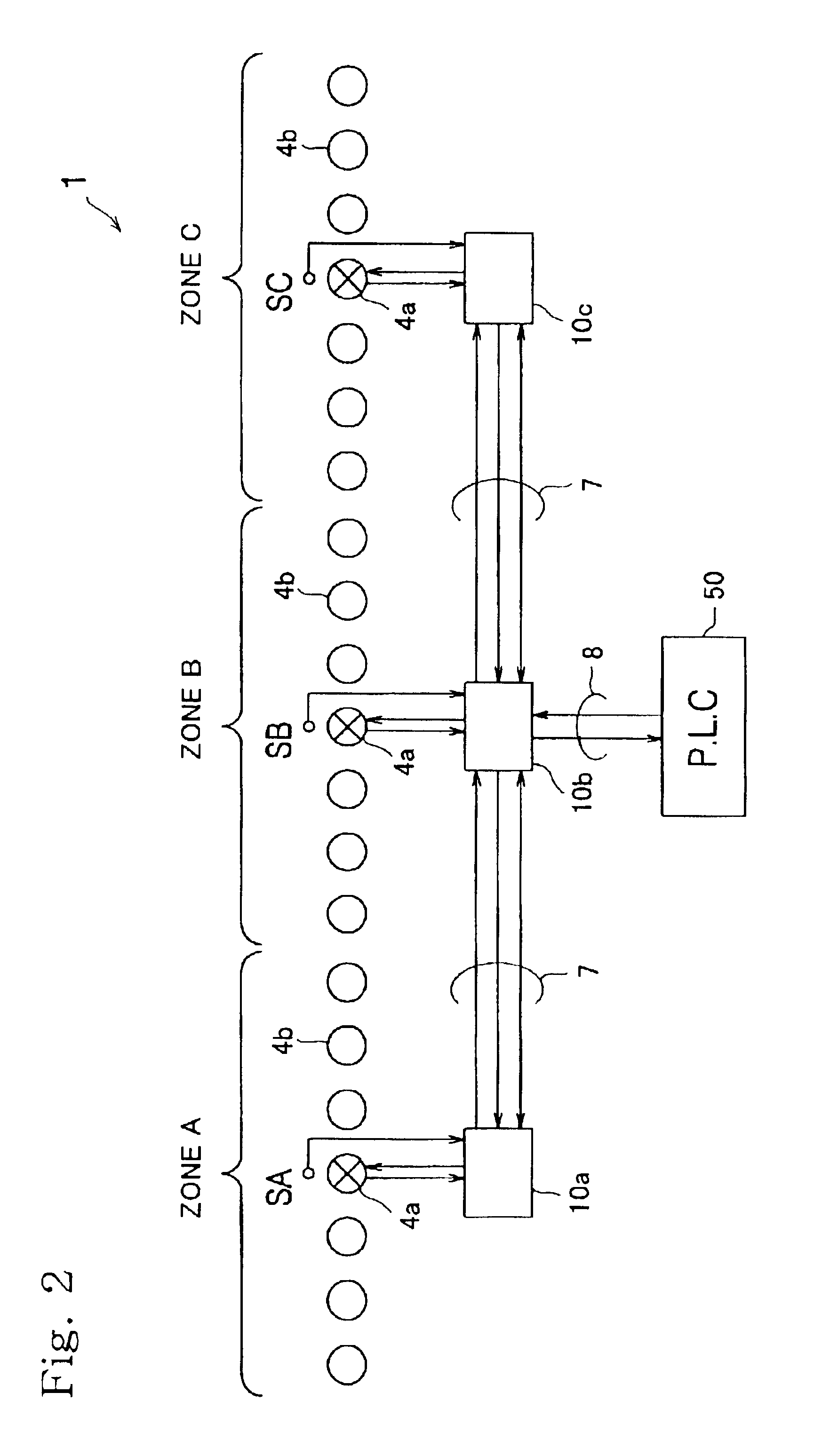

Zone controller

InactiveUS6843362B2Avoid collisionReduce power wasteControl devices for conveyorsMechanical conveyorsEngineeringTransfer line

A zone controller enabling flexible conveyance according to the use by simple change of setting. An aspect of the invention is a zone controller 10 for a particular zone picked from a plurality of zones for control into which a roller conveyor line 1 is divided and which are arrangeable in a row in the direction of conveyance, being capable of controlling operation of a driving roller 4a for conveyance provided in the particular zone, having a mode-setting means 14 capable of switching between a slug mode and a singulation mode. In the slug mode, operation of the driving roller is controlled so that articles in the zones are conveyed uniformly to downstream, maintaining the order of the articles in the conveying line. In the singulation mode, operation of the driving roller is controlled so that the articles are conveyed separately to downstream with a predetermined number of zones in which no article exists preserved between the zones in which the articles exist.

Owner:ITOH ELECTRIC COMPANY LIMITED

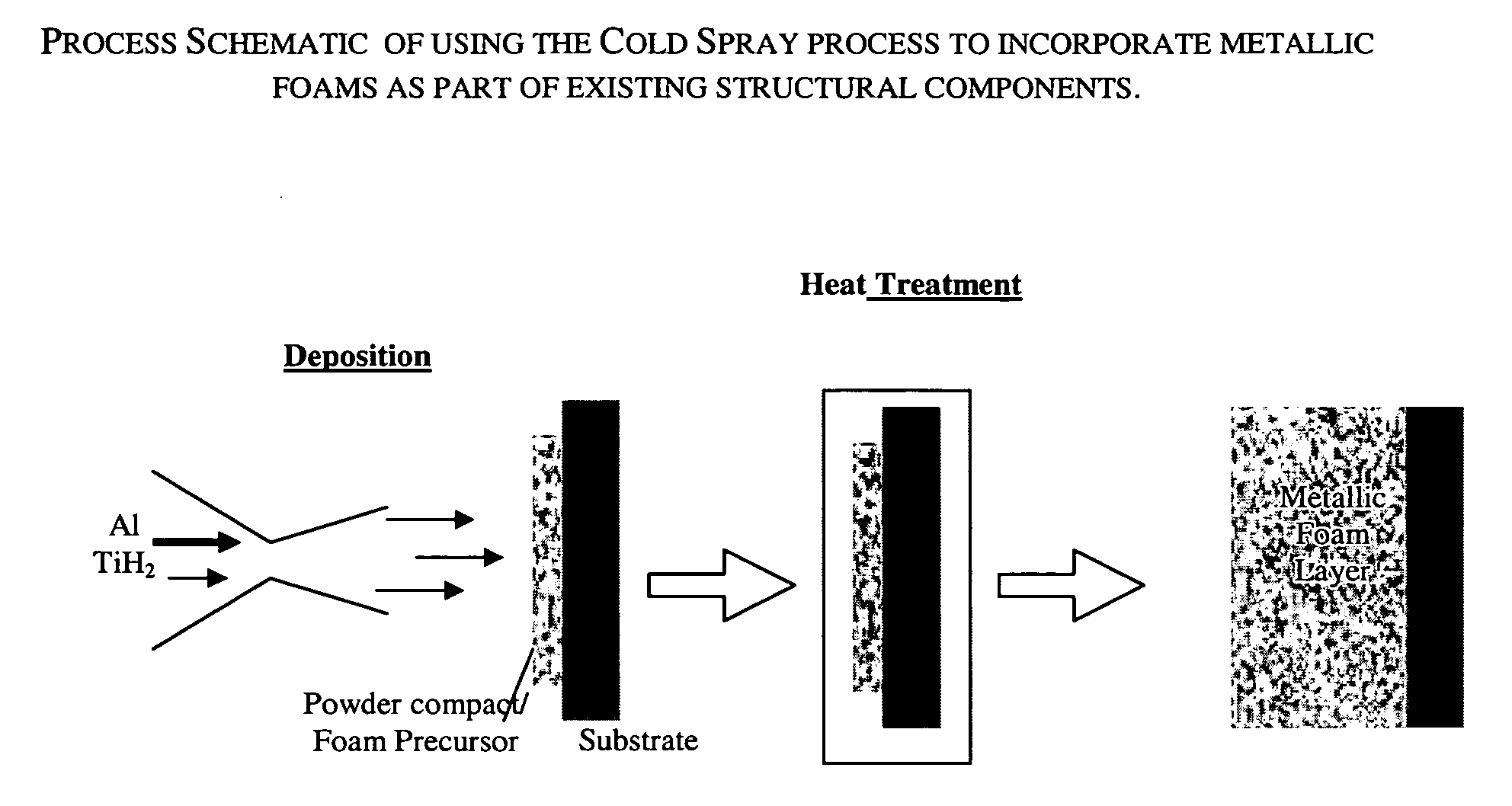

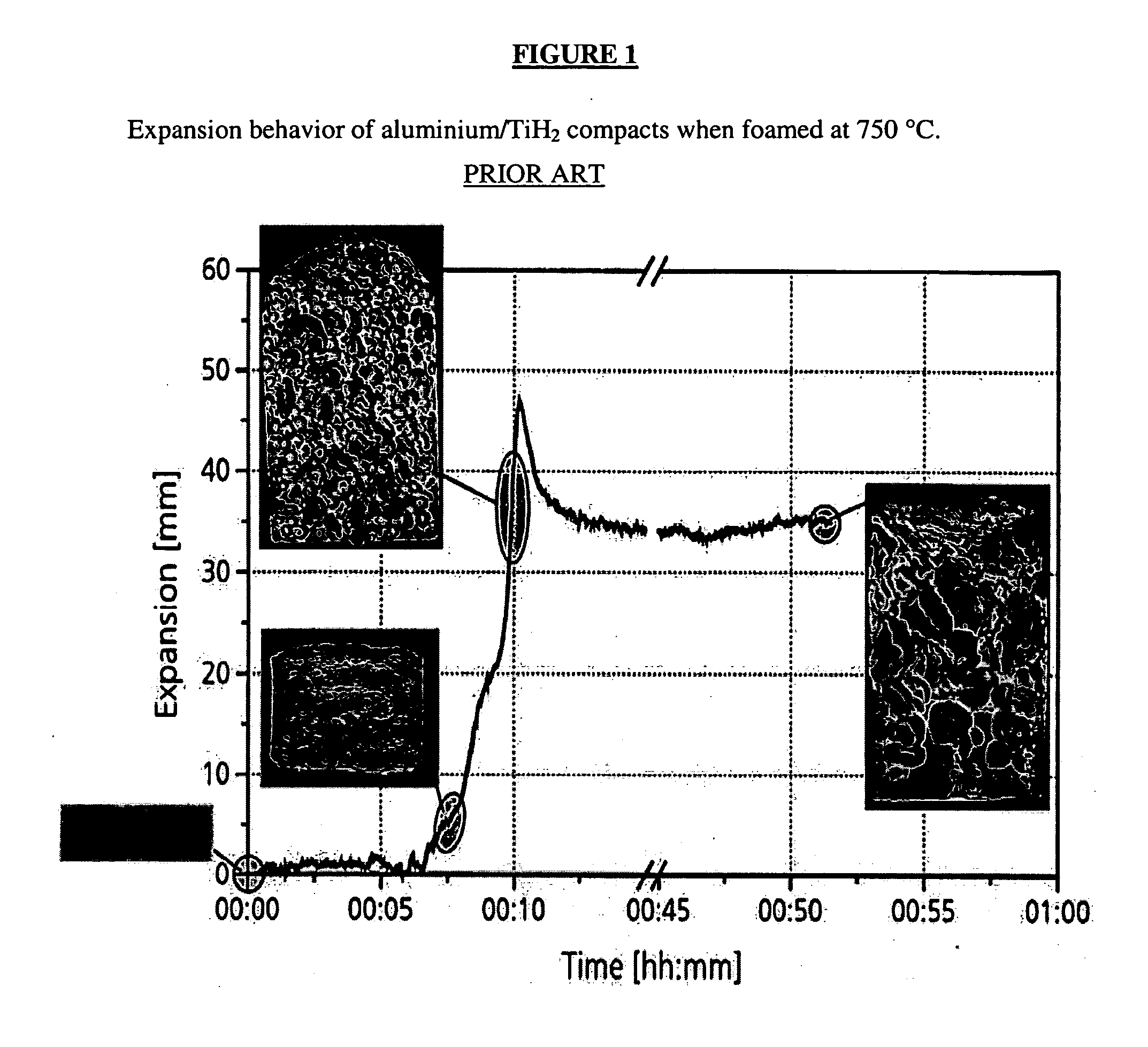

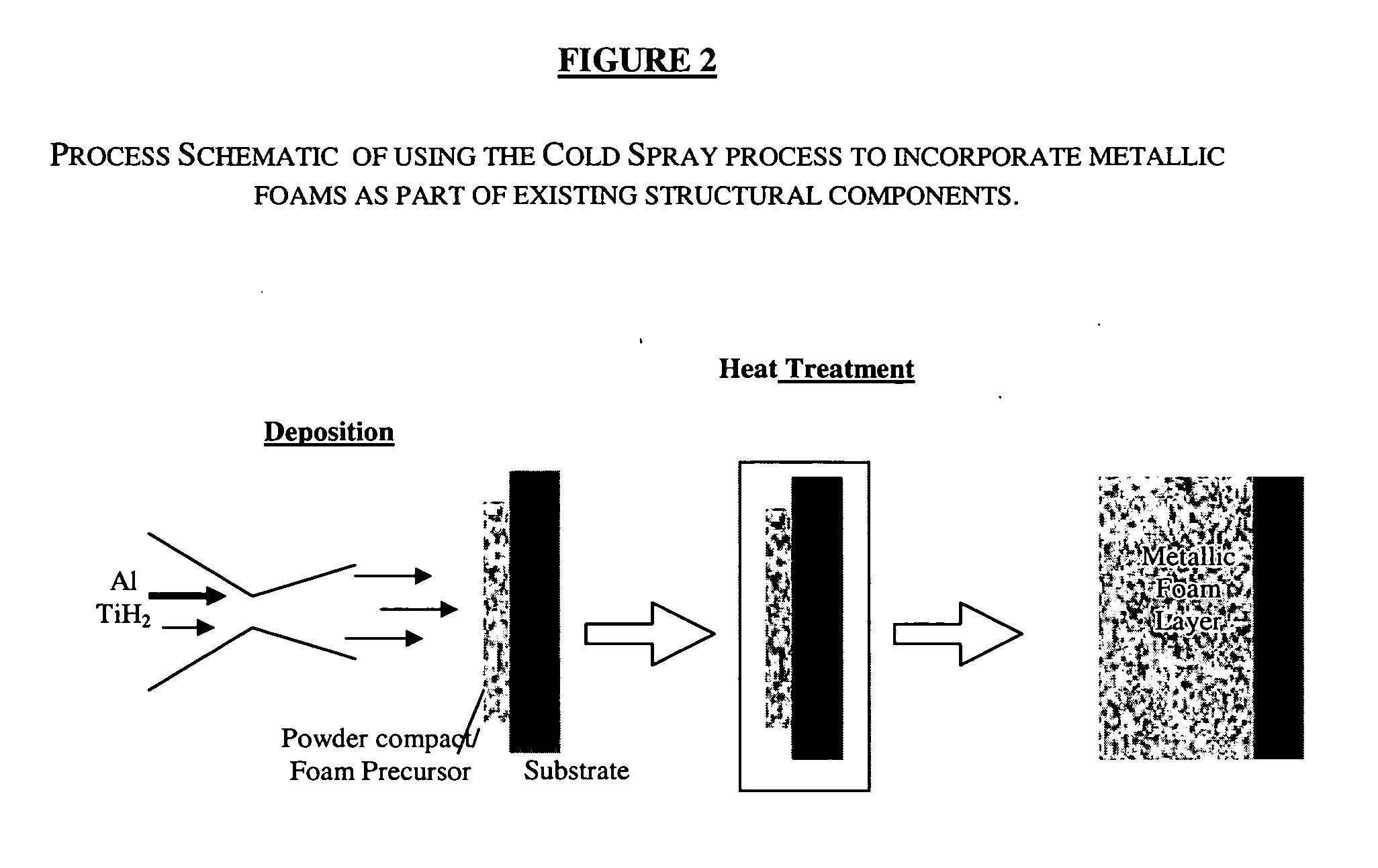

Method of forming metal foams by cold spray technique

The present invention relates to a method of forming metallic foams using cold spray processing. The method allows for the formation of metallic foams on existing substrates as a layer. The method includes the steps of providing a substrate for coating of a metallic foam; cold spraying a mixture of metal particles and a foaming agent onto the substrate to form a substrate coated with an unexpanded metallic layer; foam heat treating the substrate coated with an unexpanded metallic layer at a temperature above the decomposition temperature of the foaming agent for a time sufficient to form a heated substrate coated with an expanded metal foam layer; and cooling the heated substrate coated with an expanded metal foam layer to about ambient temperature to form a cooled substrate coated with an expanded metal foam layer. The method of forming metallic foams on substrates finds application in the oil, gas, and chemical industry by being an integral part of casings, pipelines, transfer lines, and other flow lines.

Owner:EXXON RES & ENG CO

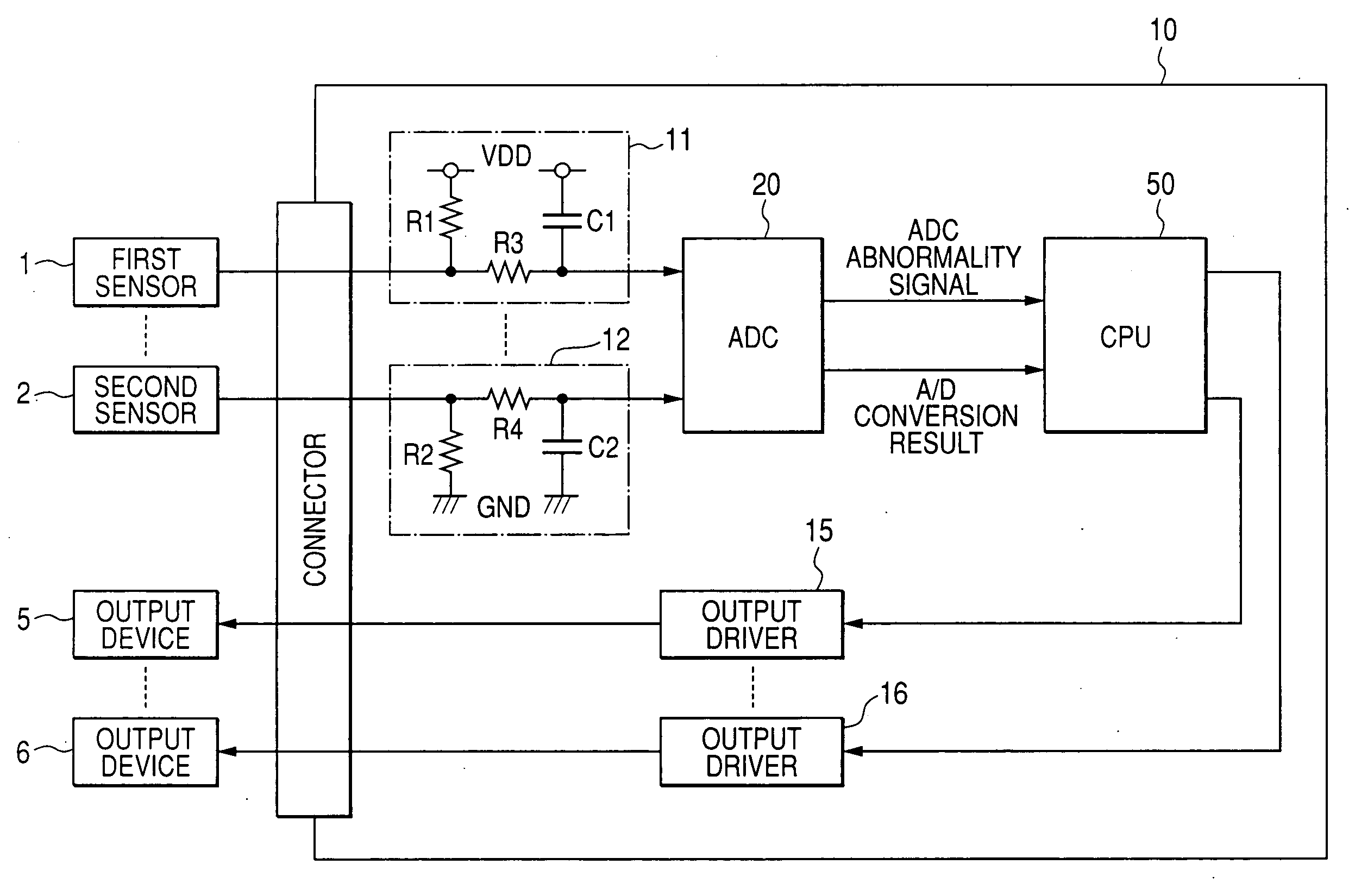

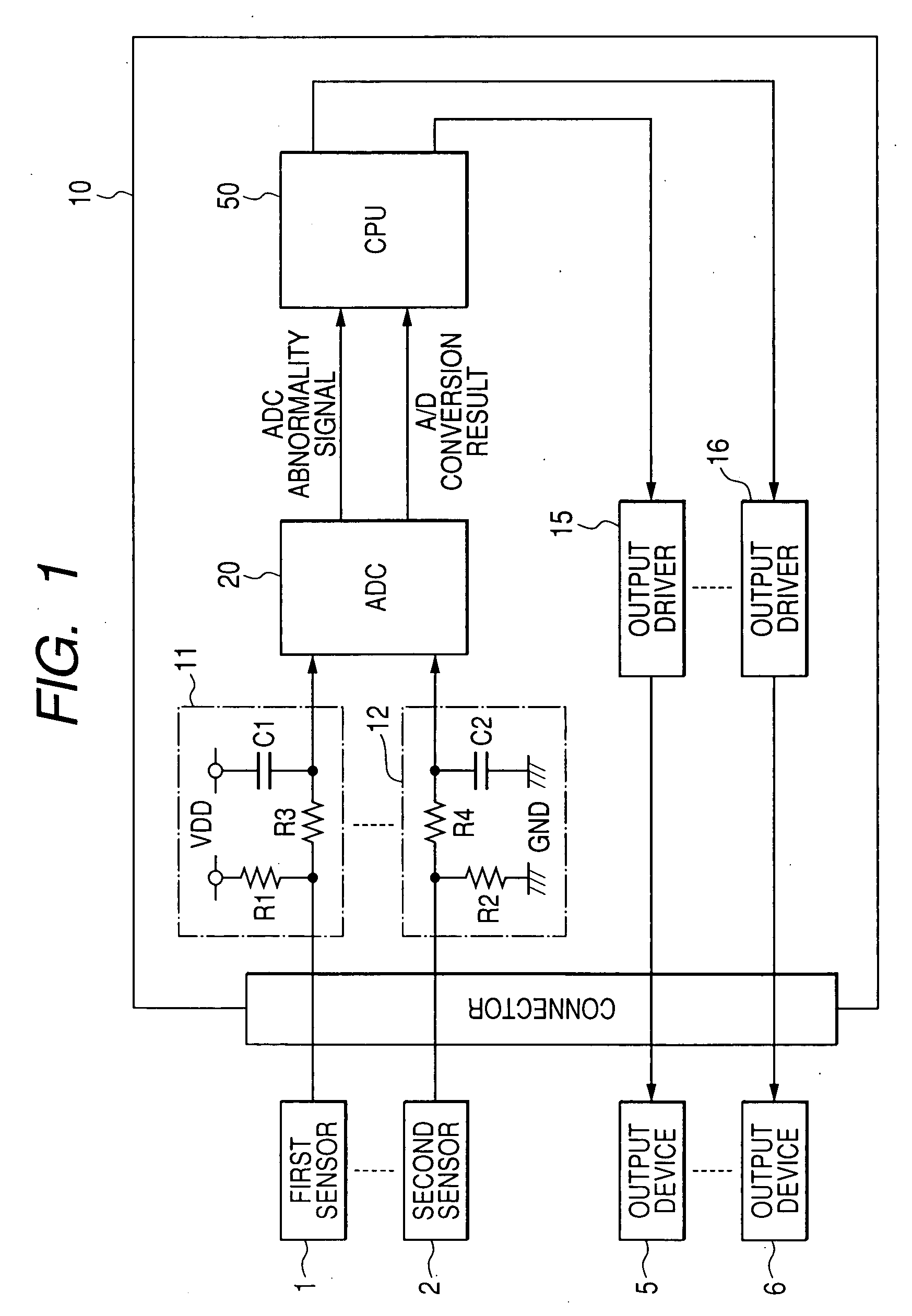

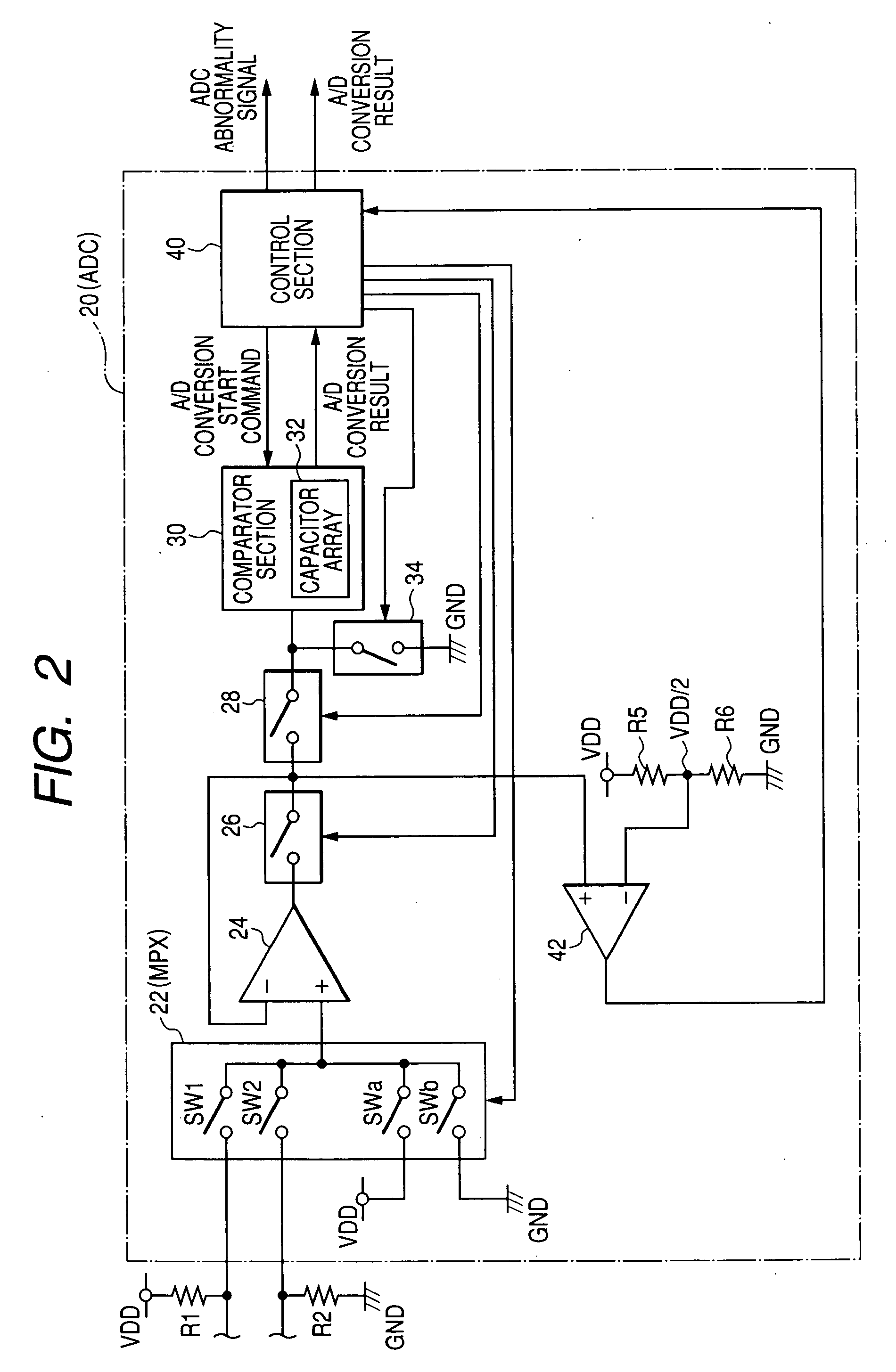

A/D converter device and electronic control apparatus including same

ActiveUS20070252744A1Perform operationElectric signal transmission systemsAnalogue-digital convertersMultiplexerA d converter

The A / D converter device includes a comparing section and an abnormality judging section. The comparing section compares a voltage of its signal transfer line connected between its input multiplexer and its A / D converting section through its sample-hold section with a predetermined abnormality judging voltage. The abnormality judging section is configured to apply a reference voltage to the signal transfer line in synchronization with an A / D conversion cycle thereof on condition that its A / D converting operation thereof is not interrupted, and to determine presence of abnormality in the A / D converter device if an comparison result of the comparing section does not match an expected value corresponding to the reference voltage.

Owner:DENSO CORP

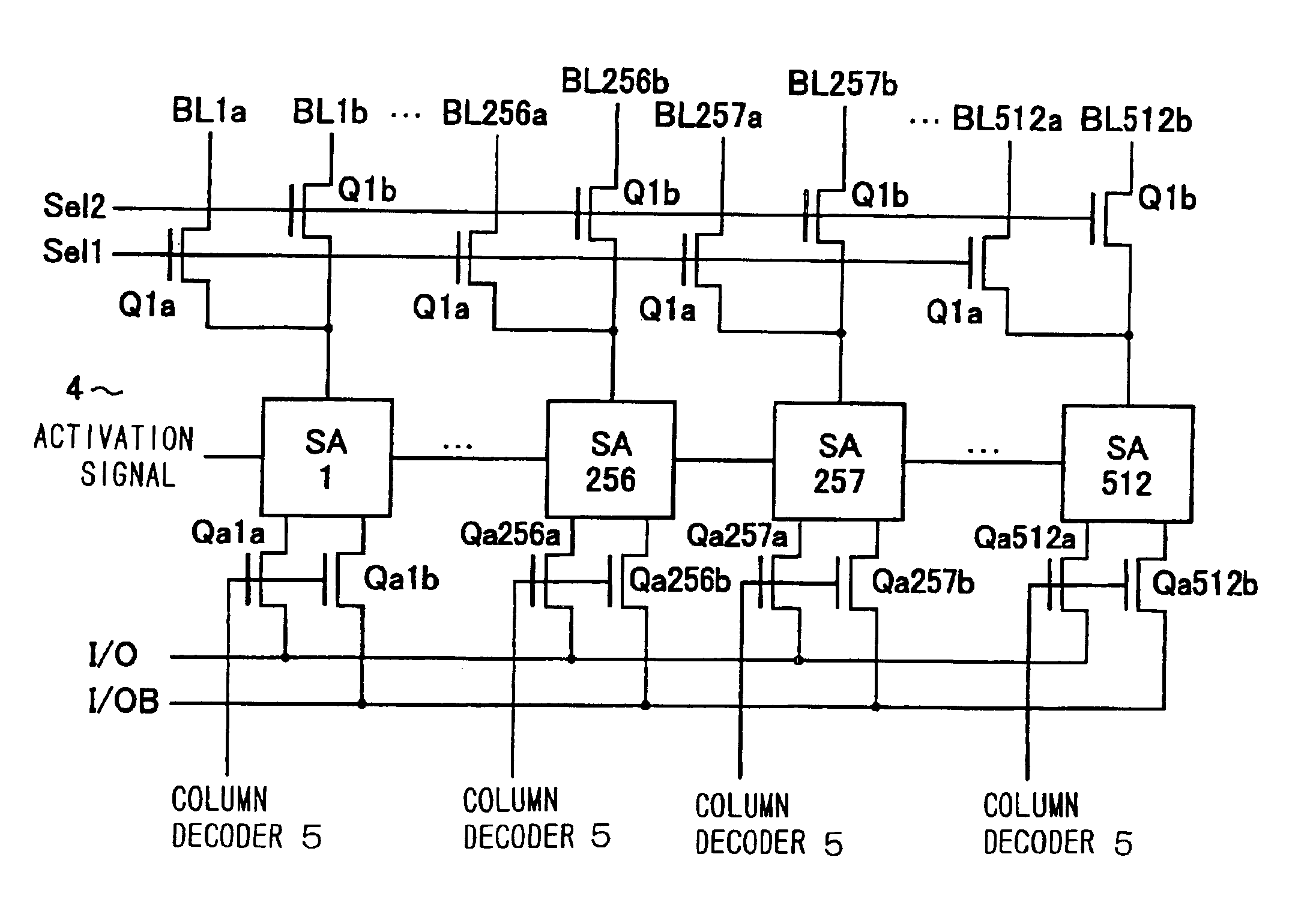

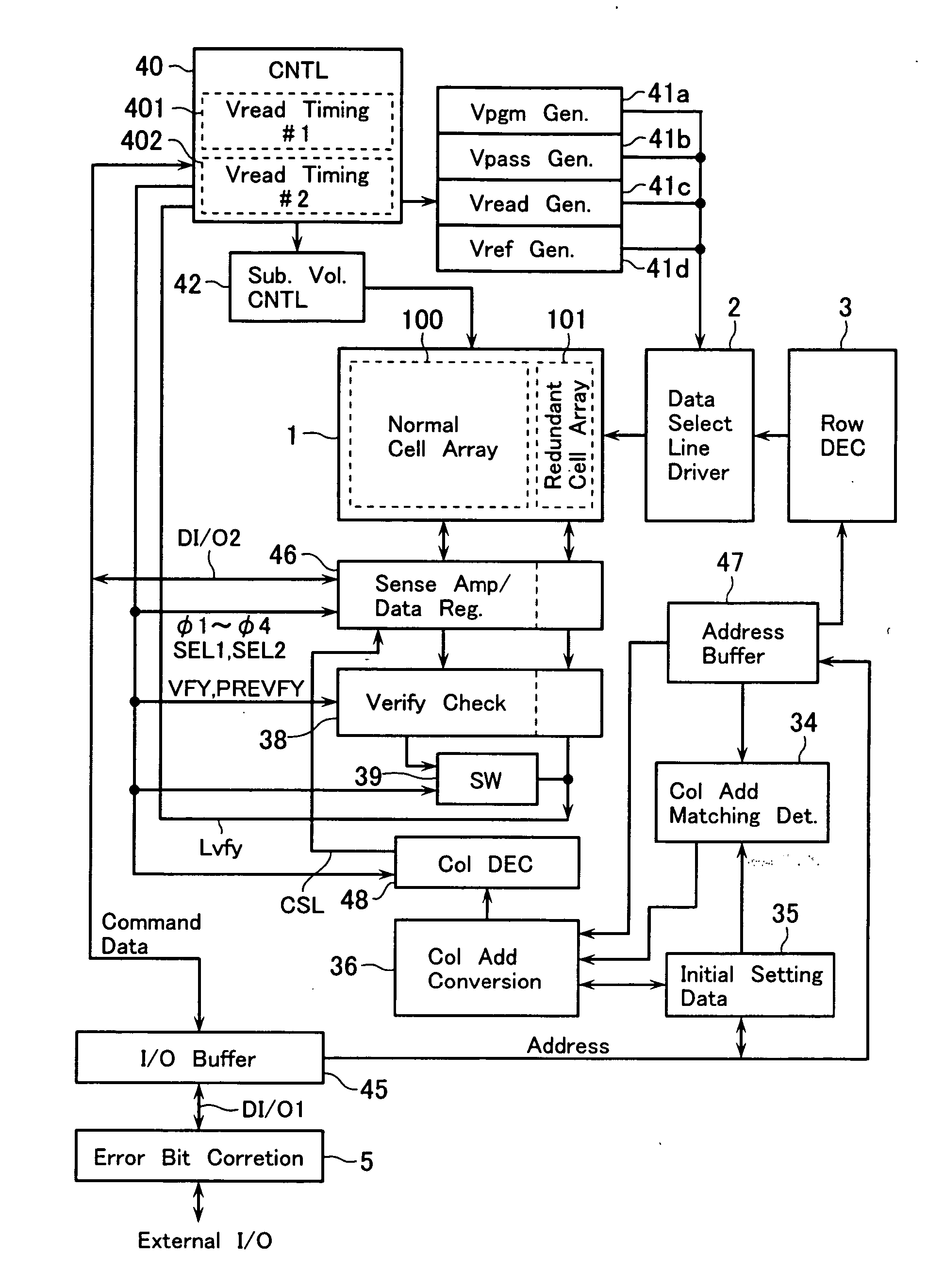

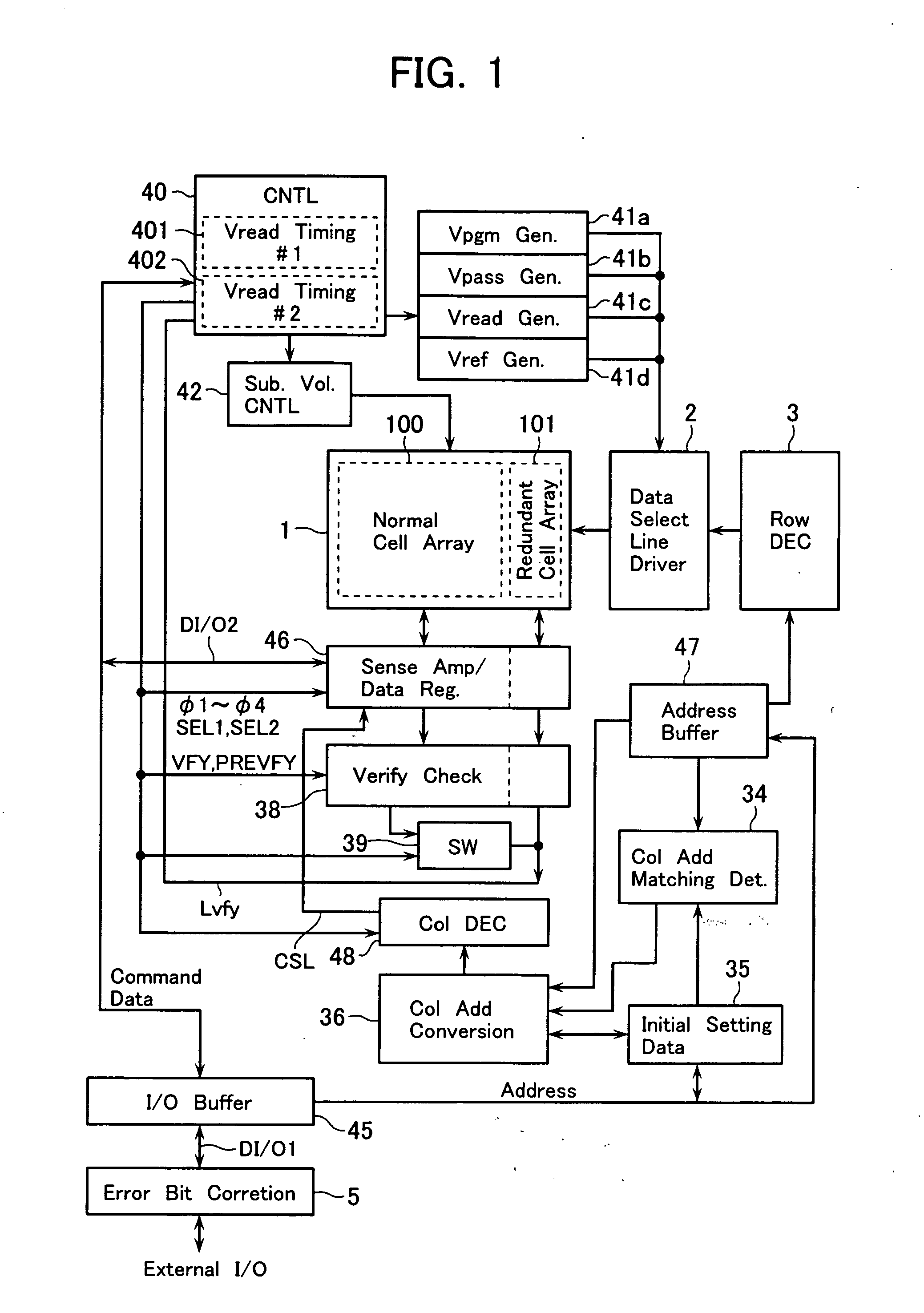

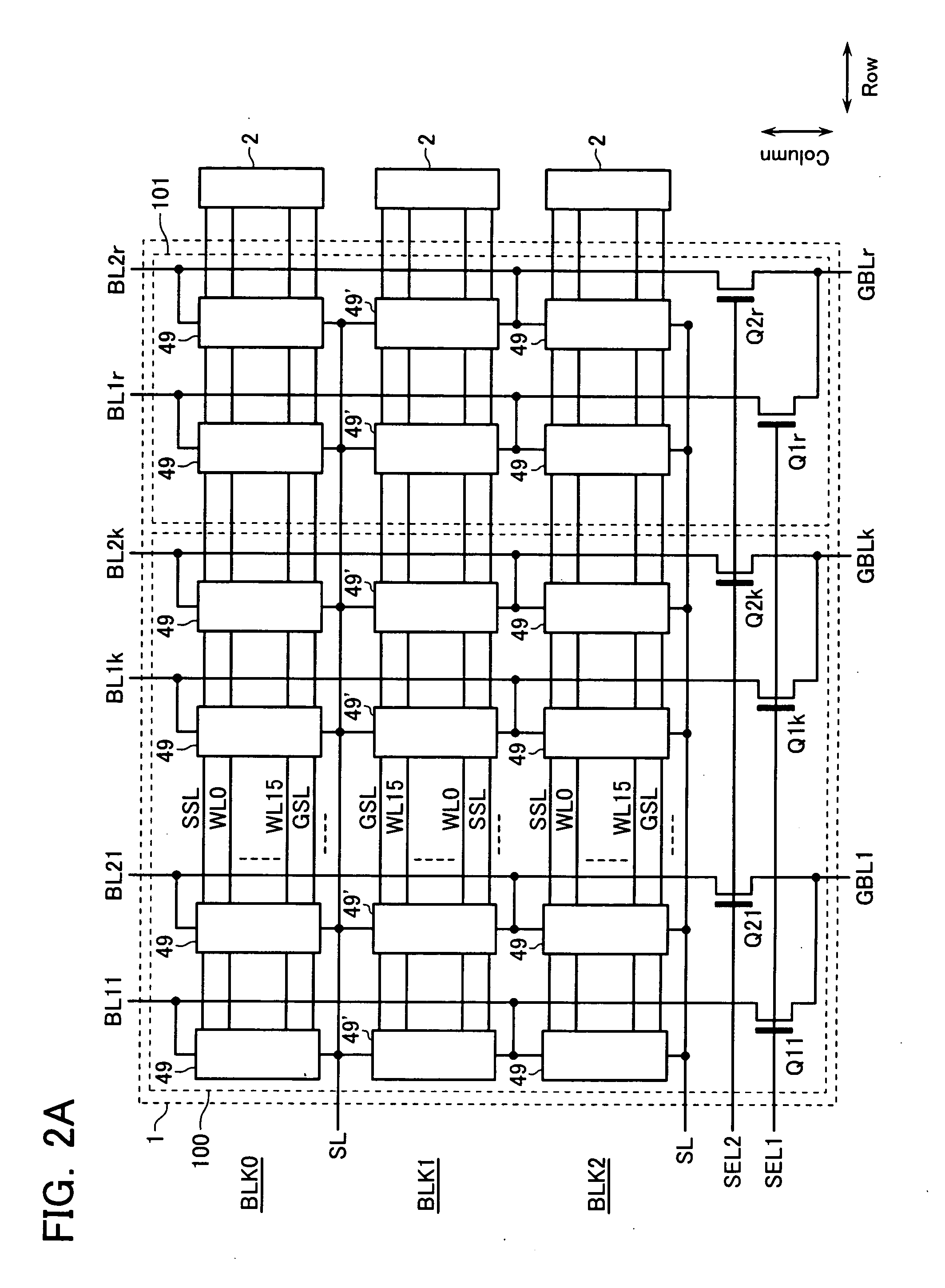

Semiconductor memory device

A semiconductor memory device includes: a memory cell array having a plurality of data select lines disposed in parallel with each other, a plurality of data transfer line disposed in parallel with each other to intersect the data select lines, and electrically rewritable memory cells laid out at cross portions between the data select lines and data transfer lines; a data select line driver for driving the data select lines of the memory cell array; a sense amplifier circuit connected to the data transfer lines of the memory cell array, for performing data read of memory cells selected by one of the data select lines; and a control circuit used for timing control of data read of the memory cell array, for outputting at least two types of timing signals as being different in accordance with a selected data area of the memory cell array.

Owner:KK TOSHIBA

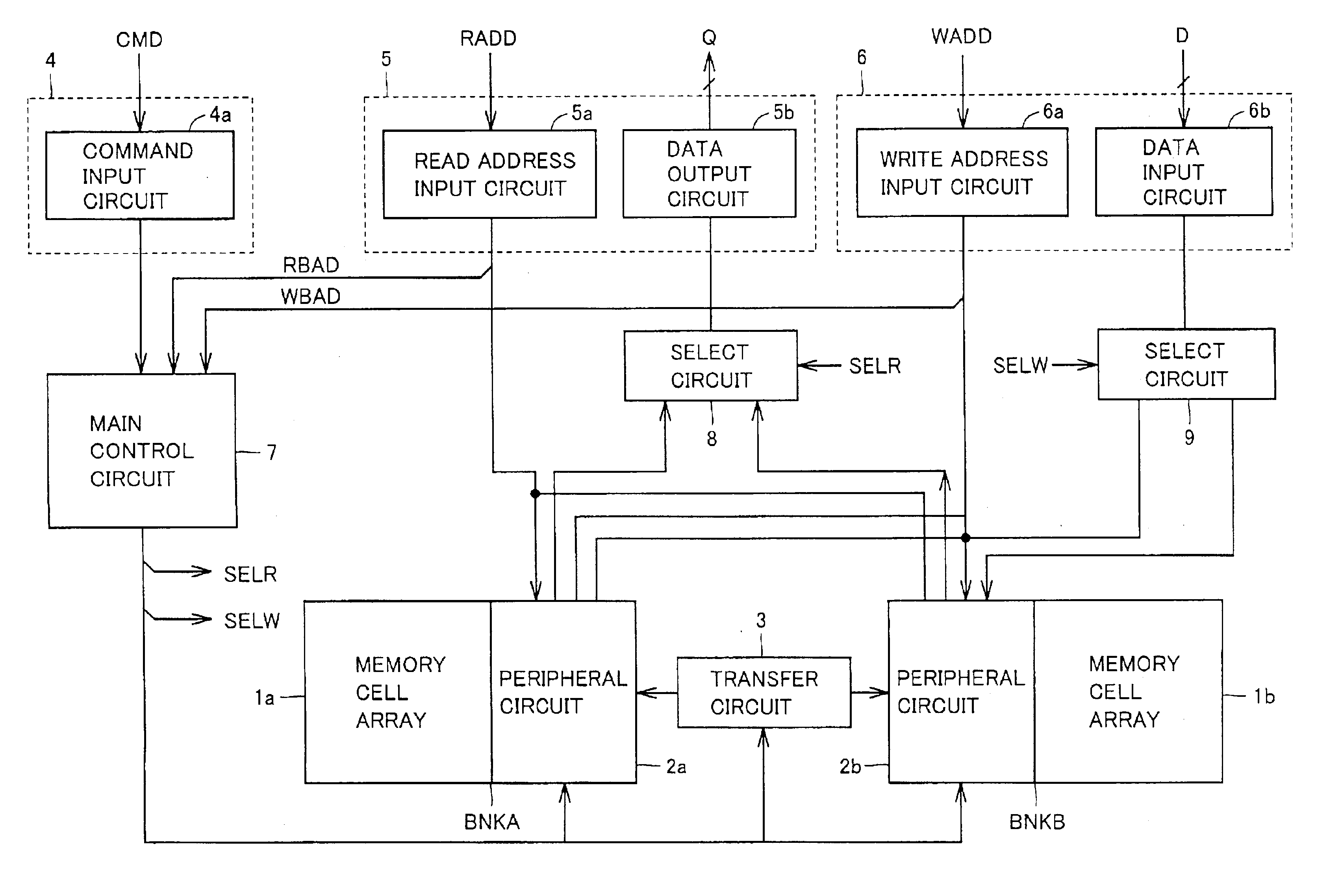

Nonvolatile semiconductor memory device allowing high speed data transfer

ActiveUS6922359B2Efficiently performing writing and reading of dataImprove data transfer efficiencyRead-only memoriesDigital storageParallel computingTransfer switch

Local buses for performing writing / reading of data are provided in correspondence to memory blocks each having a plurality of nonvolatile memory cells, and also circuits for performing writing / reading of data are provided in correspondence to the memory blocks. In addition, data transfer lines for bidirectionally transferring data are provided commonly to the memory blocks, and transfer switch gates for performing data transfer between the memory blocks are provided commonly to the memory blocks. The memory blocks are divided into banks, writing / reading of data on individual memory blocks are performed in units of banks, and parallel execution of writing and reading or of writing / reading and internal transfer is performed. Thus, it is possible to improve data transfer processing efficiency in a nonvolatile semiconductor device.

Owner:RENESAS ELECTRONICS CORP

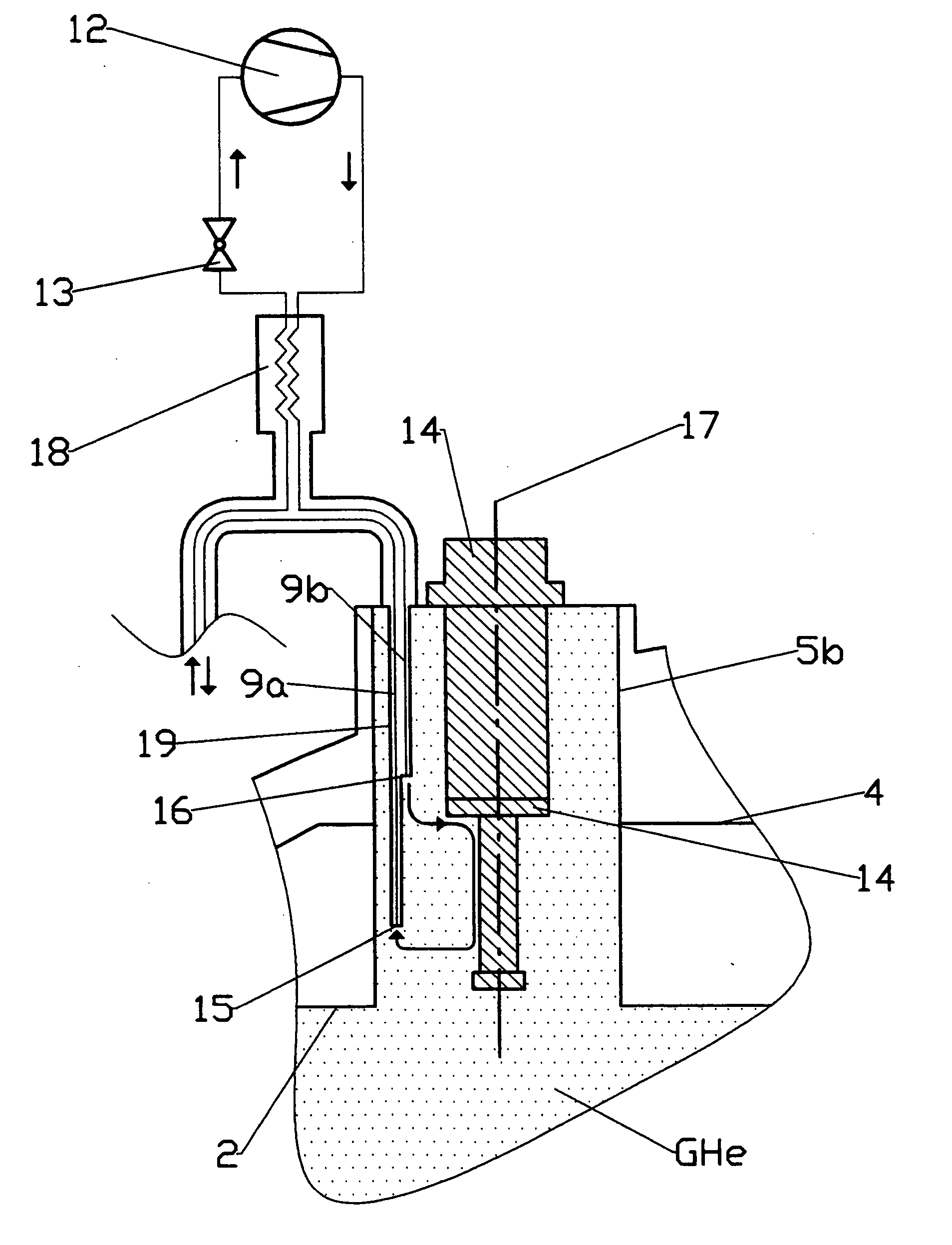

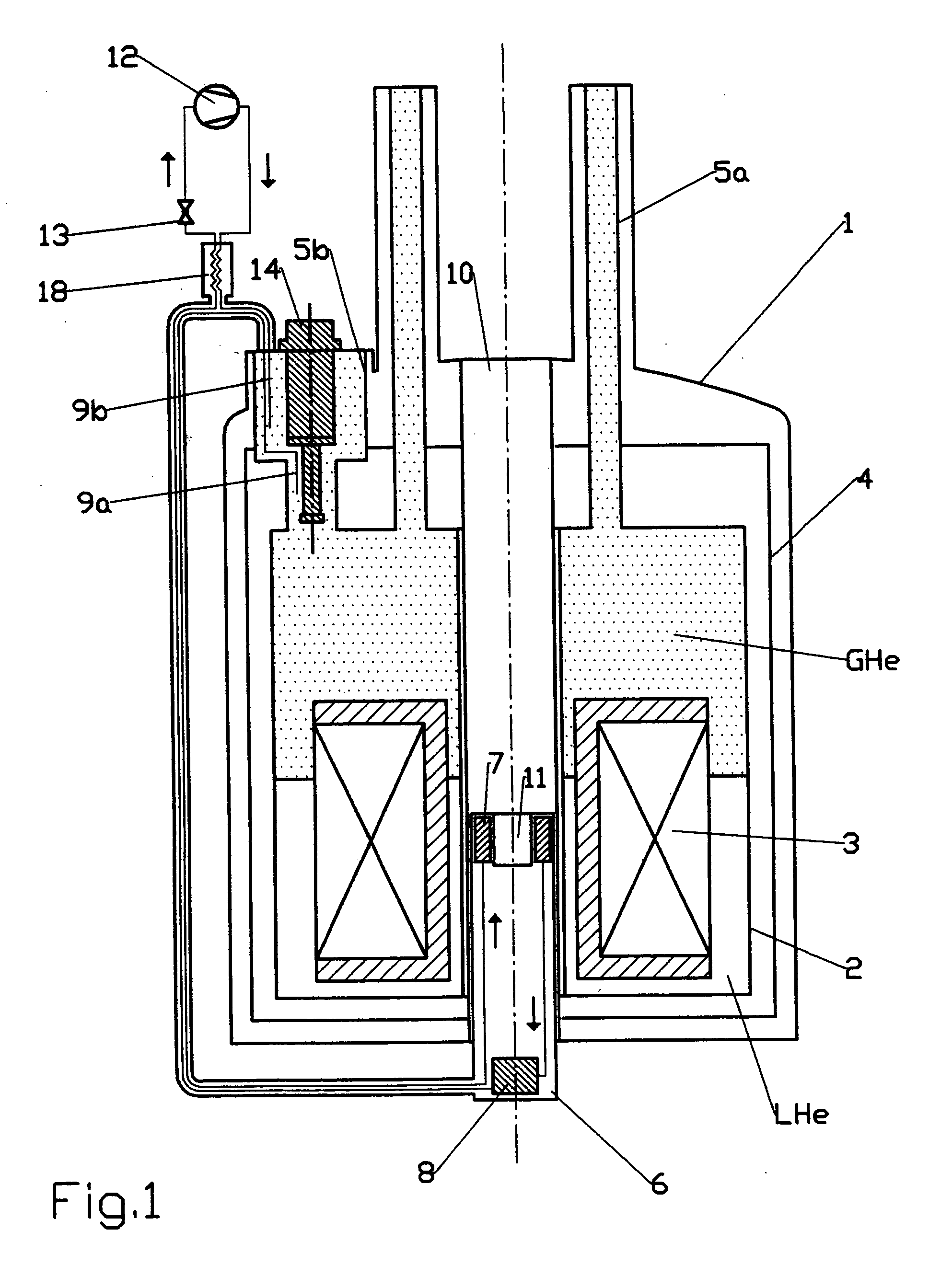

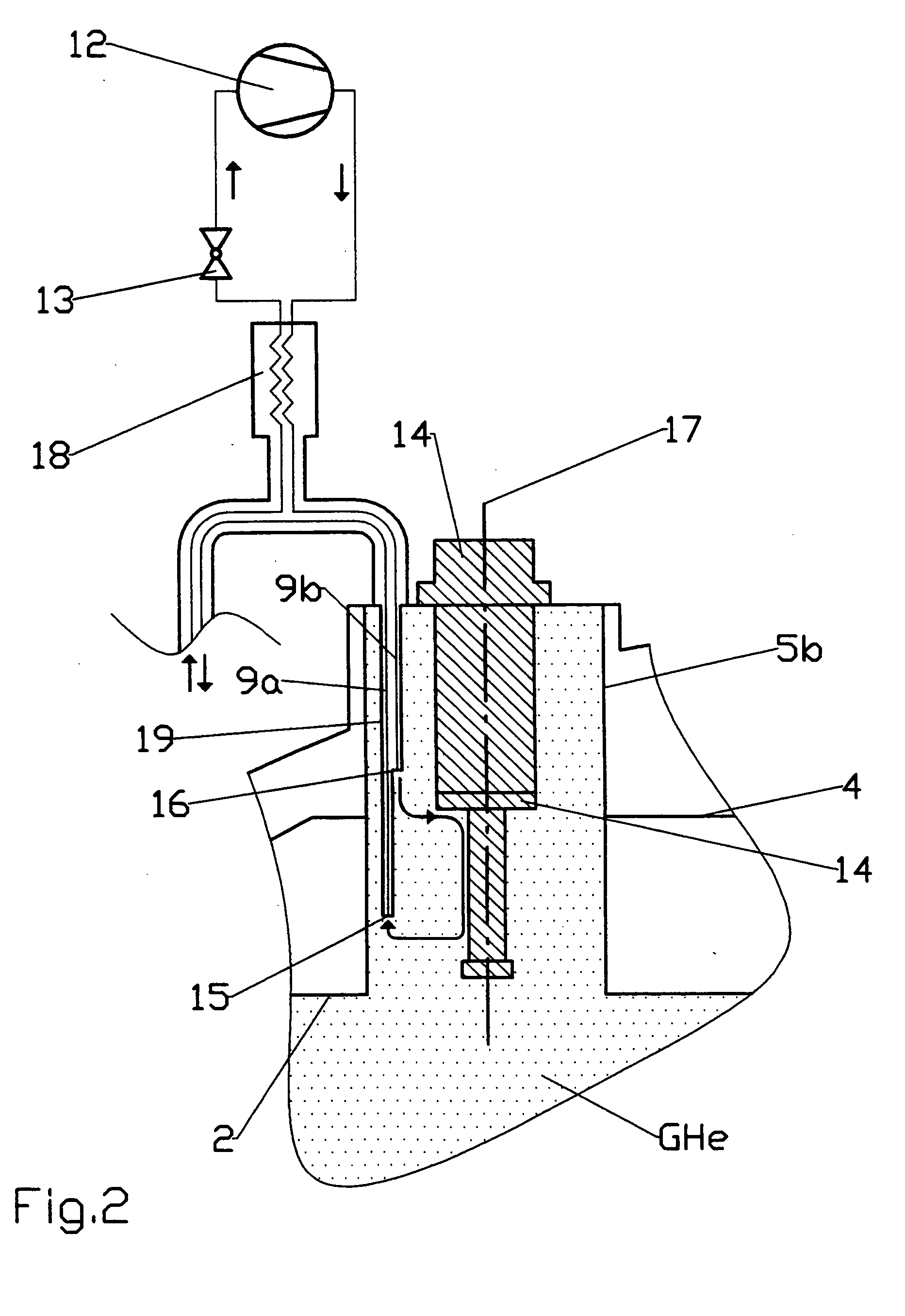

NMR spectrometer with common refrigerator for cooling an NMR probe head and cryostat

ActiveUS20060130493A1Optimum adjustment of performanceUtilization capacitySolidificationLiquefactionCryocoolerRefrigerated temperature

An NMR apparatus comprising a superconducting magnet coil system, in particular, an NMR spectrometer, with a cryostat which comprises an outer shell and a helium tank which contains the magnet coil system, and with an NMR probe head which is disposed in a room temperature bore of the cryostat and which contains a cooled RF resonator for receiving NMR signals from a sample to be examined and is cooled, together with the NMR probe head, by a cold head of a common, multi-stage, compressor-operated refrigerator, is characterized in that the cold head of the refrigerator is disposed in a neck tube, the upper end of which is connected to the outer shell of the cryostat and the lower end of which is connected to the helium tank in such a manner that the neck tube and the helium tank delimit a helium space, with at least one cooling circuit with thermally insulated transfer lines being provided between the helium space and the NMR probe head, wherein the cryogenic helium in the helium space is used as coolant for the cooling circuit. This produces an NMR apparatus which cools a plurality of elements at different temperature levels using only one single cryocooler to optimally utilize the cooling resources of the refrigerator.

Owner:BRUKER BIOSPIN

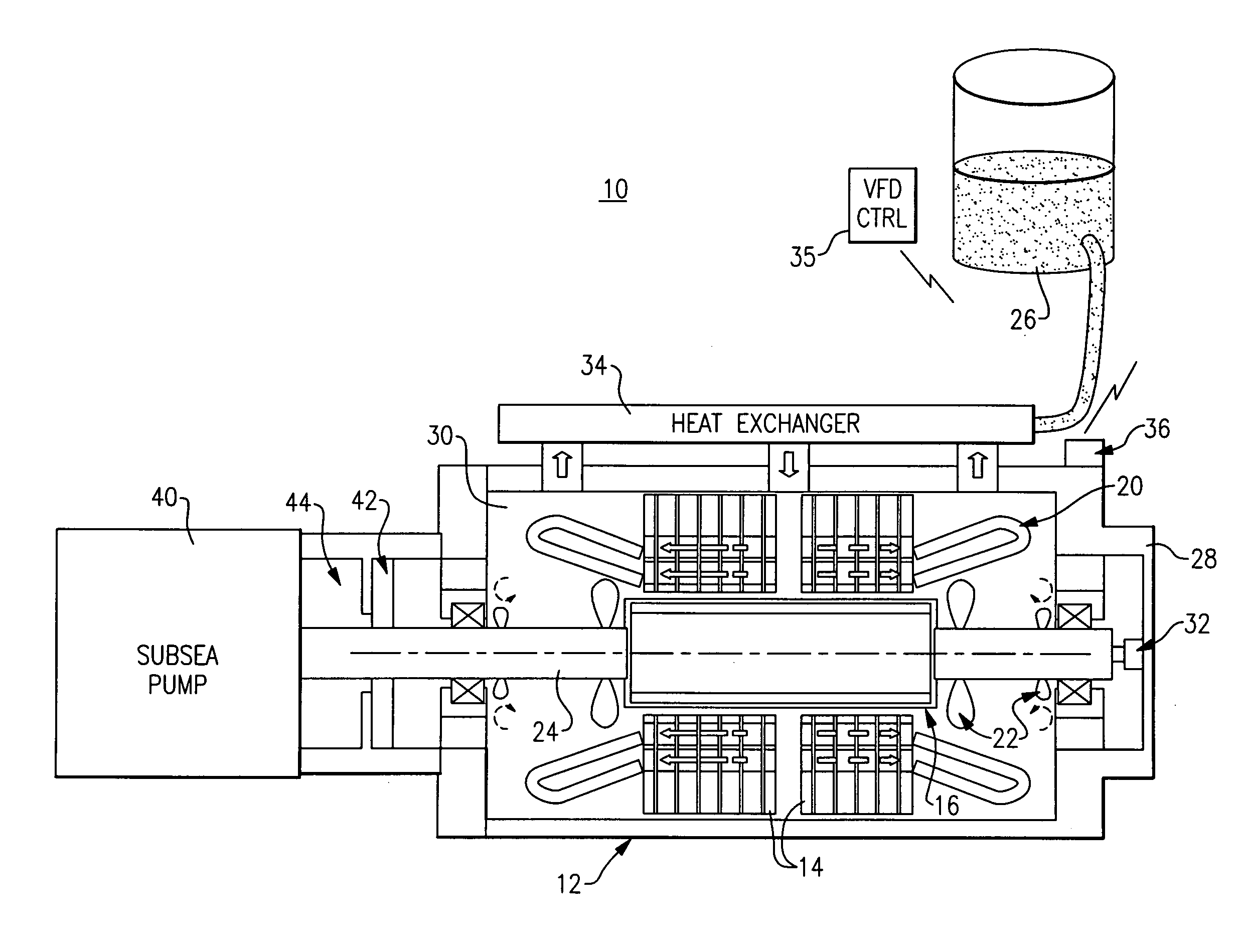

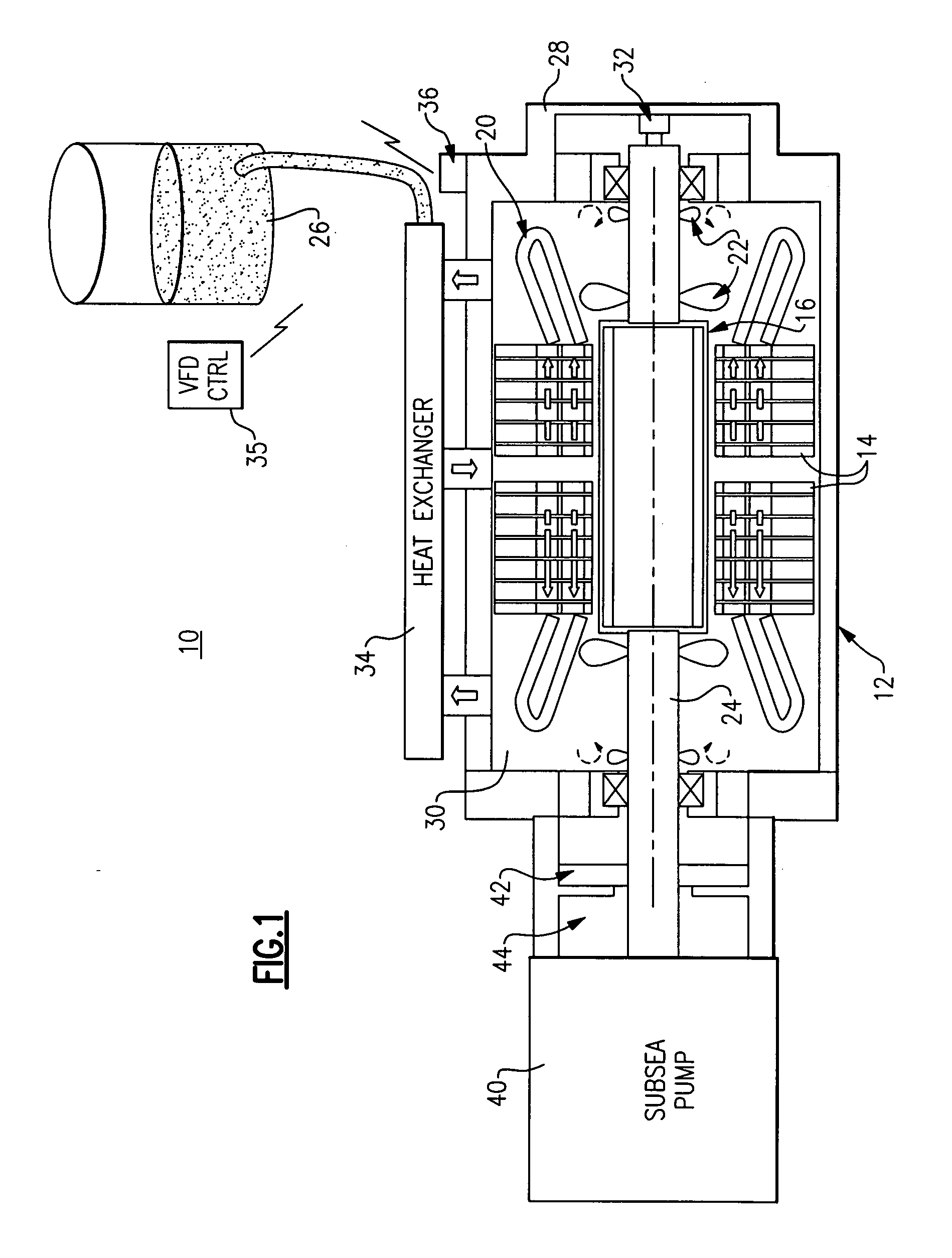

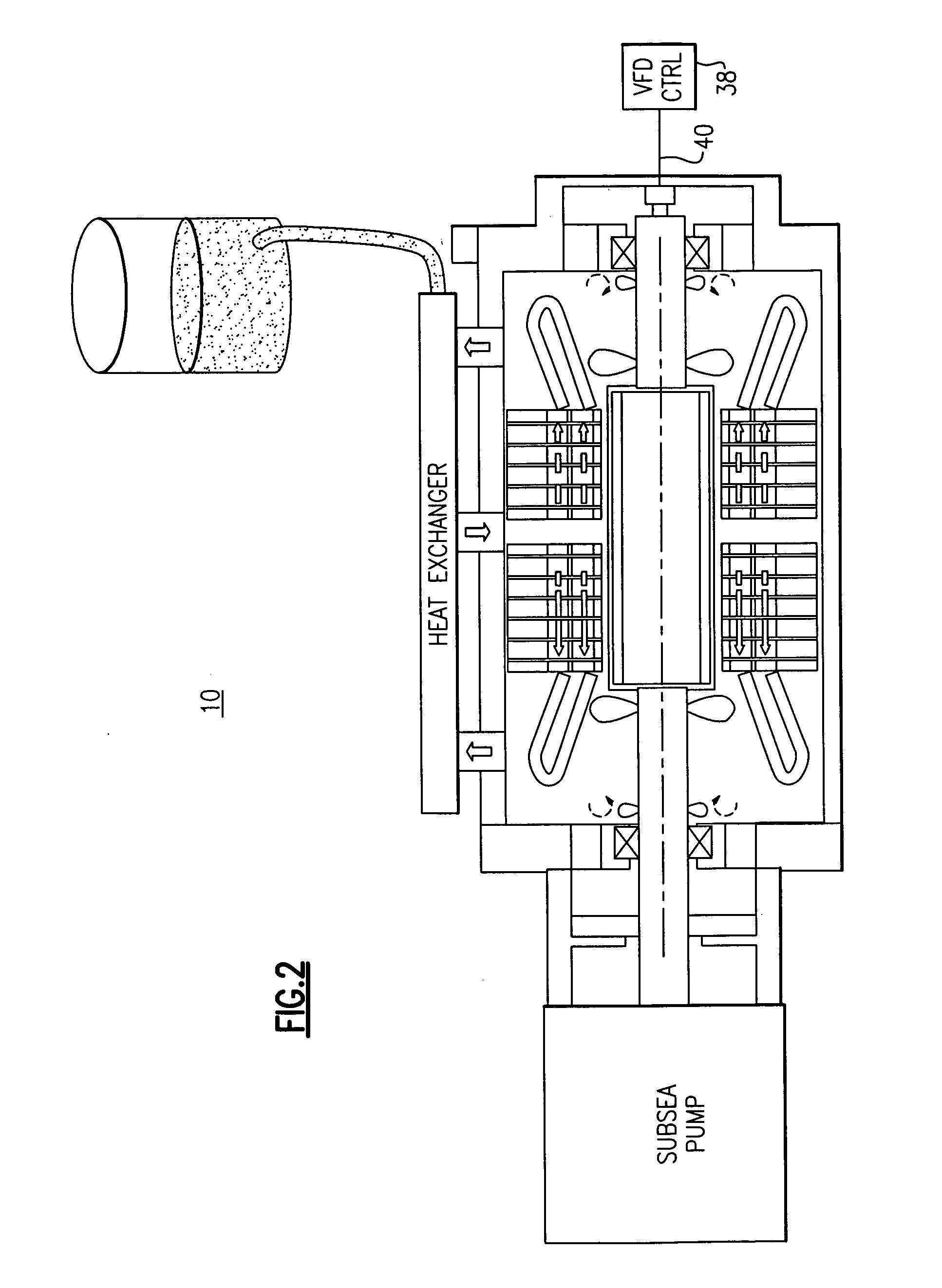

Permanent magnet motor for subsea pump drive

InactiveUS20090232664A1Avoid corrosionPositive displacement pump componentsPump controlPermanent magnet motorInconel

A subsea pump drive employs a permanent magnet (PM) motor to drive a subsea pump. The PM motor rotor in one embodiment is canned with a non-magnetic material such as inconel that can provide a desired level of corrosion protection. The PM motor provides a subsea pump drive that is smaller and more efficient, having a high power factor than a subsea pump drive utilizing a conventional induction motor. The PM motor subsea pump drive eliminates the necessity for a topside storage tank and associated fluid transfer lines when the motor rotor is cooled with processed fluid.

Owner:GENERAL ELECTRIC CO

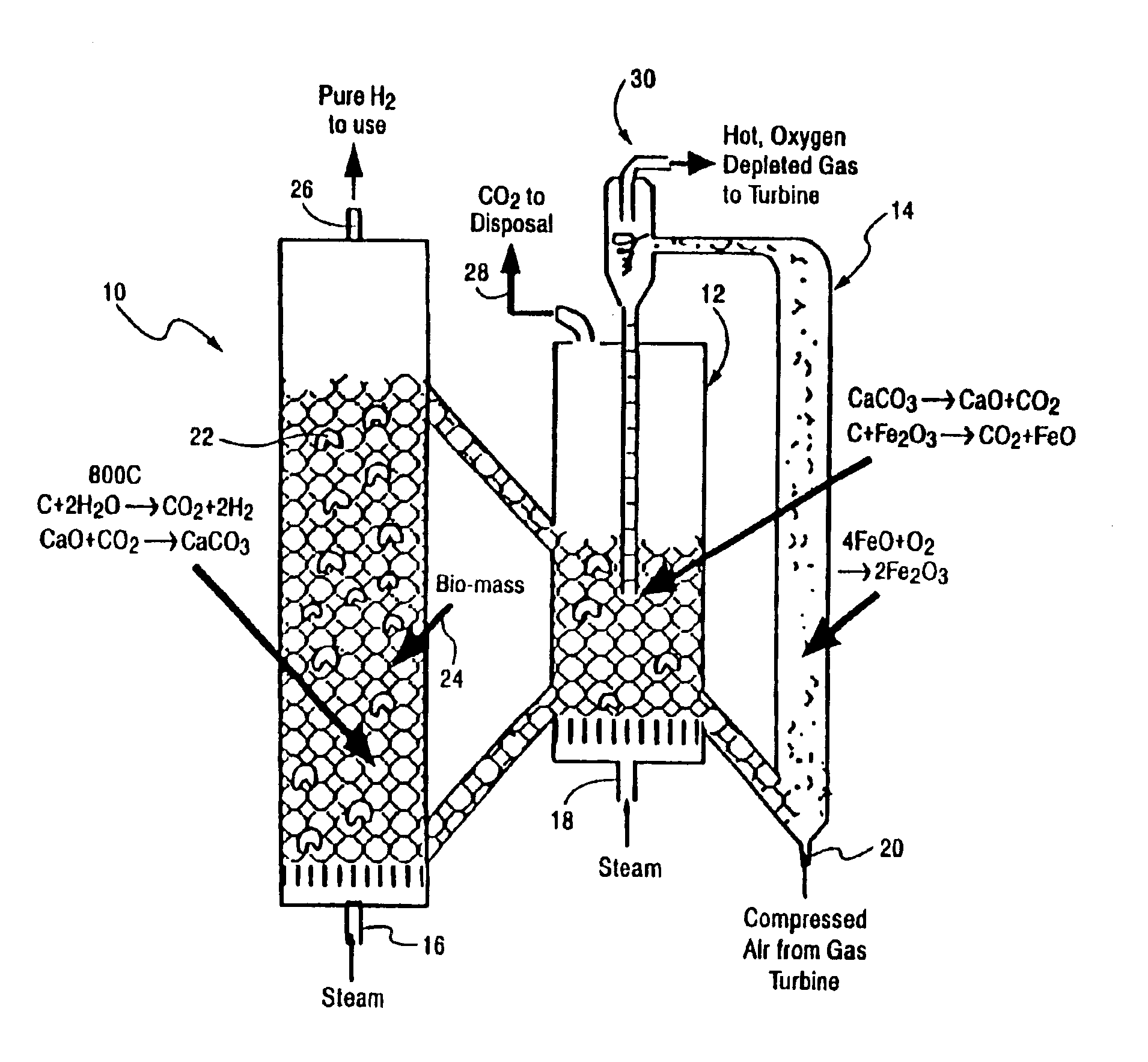

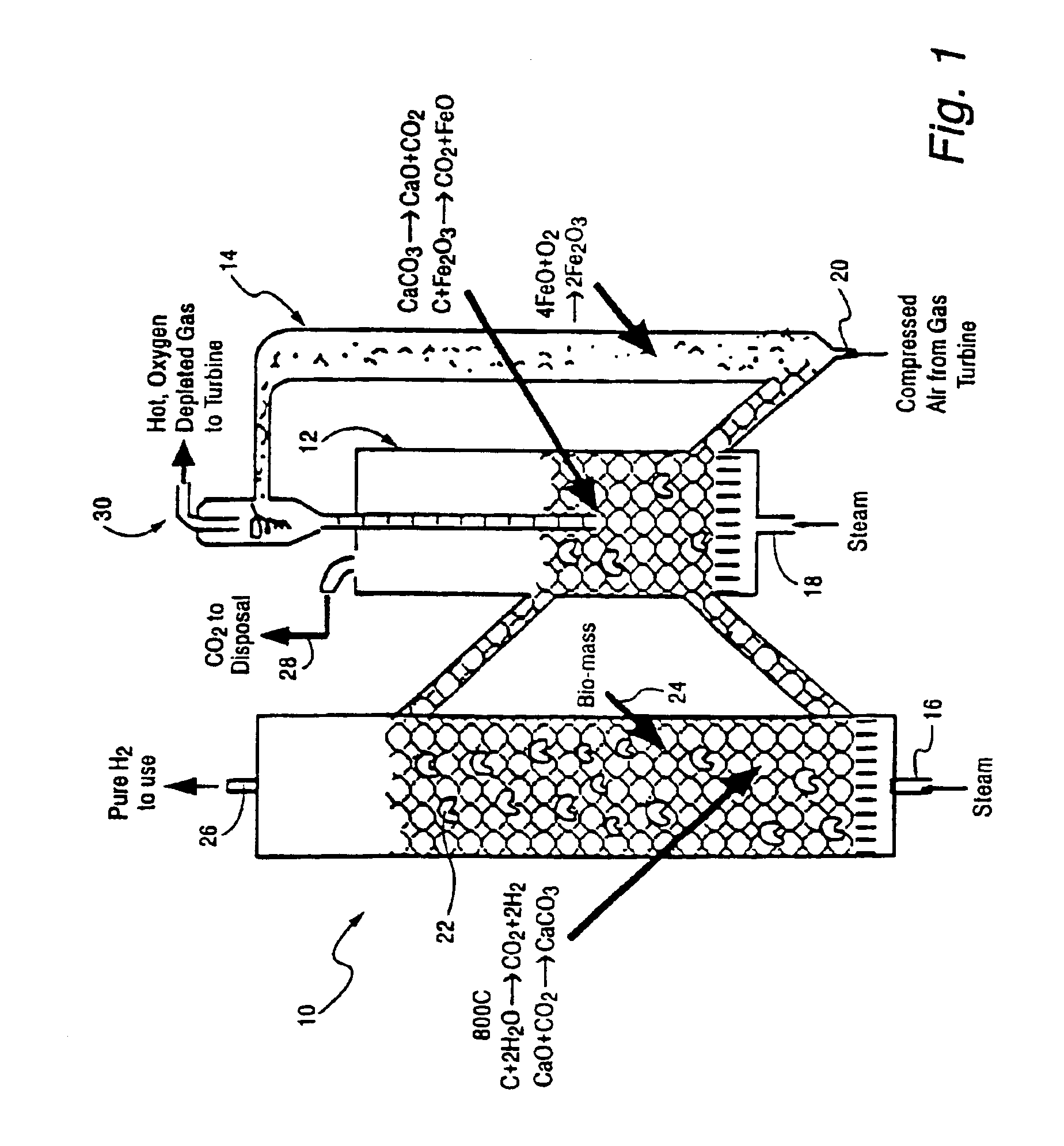

Apparatus for converting coal into fuel cell quality hydrogen and sequestration-ready carbon dioxide

An apparatus for burning coal to produce substantially pure hydrogen for use in fuel cells, together with “sequestration ready” carbon dioxide and a stream of oxygen depleted air for powering gas turbines. The apparatus includes two fluidized bed reactors and a third transfer line reactor. The first reactor is supplied with coal particles or “char” and fluidized with high temperature steam. The second reactor is fluidized with high temperature steam and the third reactor is fluidized by compressed air. Solids circulated among these three reactors include a mixture of materials containing coal, calcium compounds (present as CaO, CaCO3 and mixtures thereof) and iron compounds (present as FeO, Fe2O3 and mixtures thereof).

Owner:GENERAL ELECTRIC CO

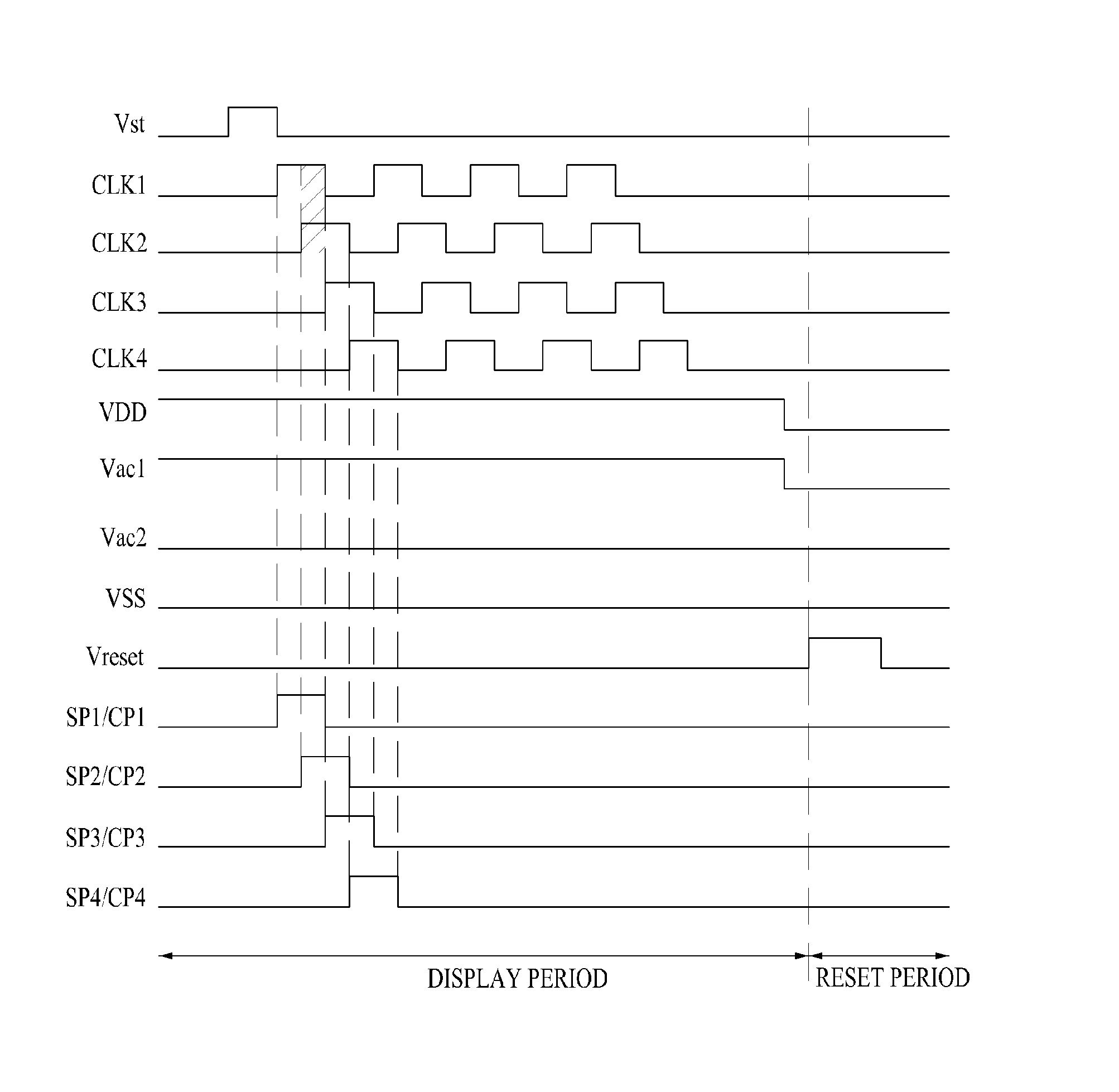

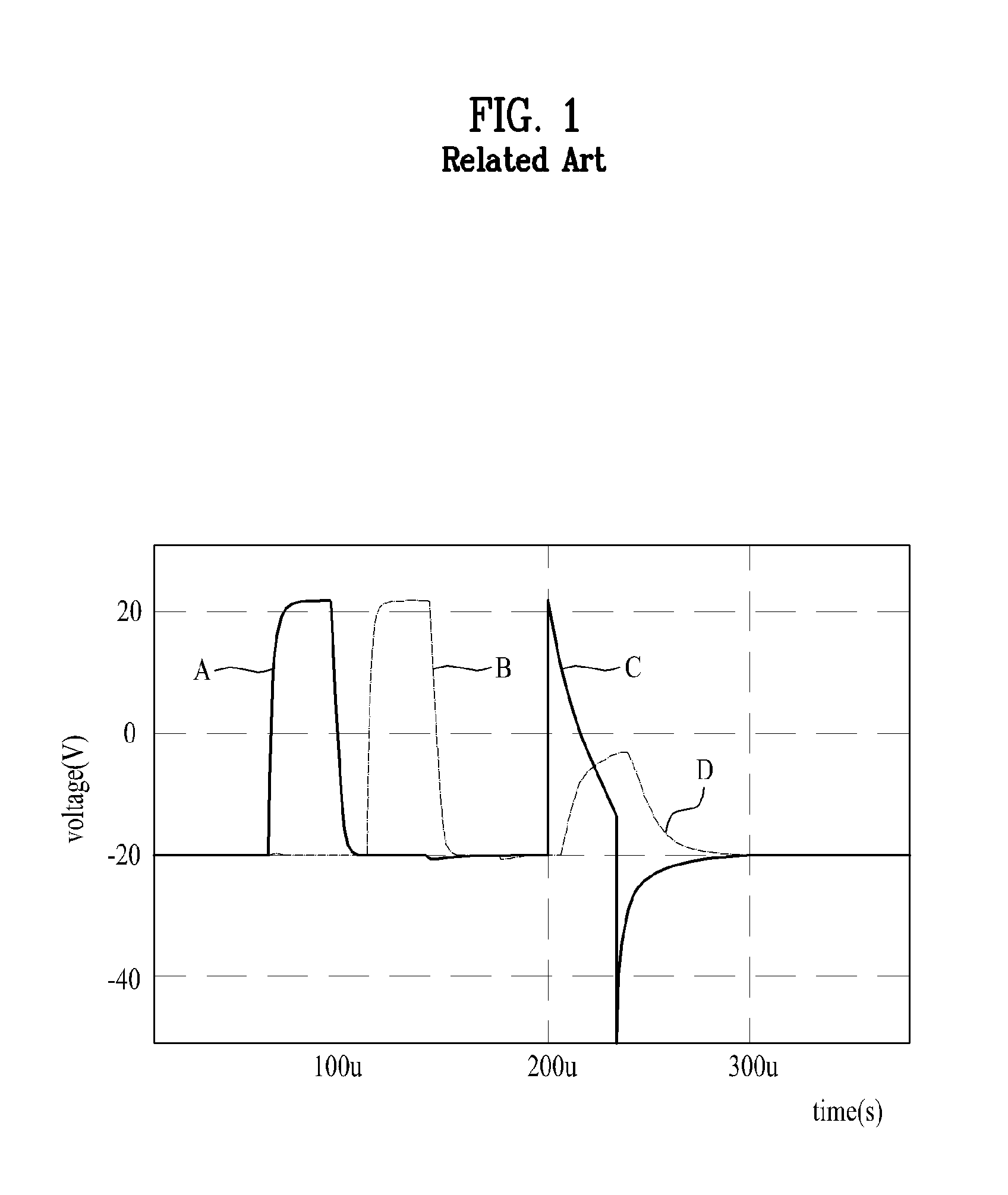

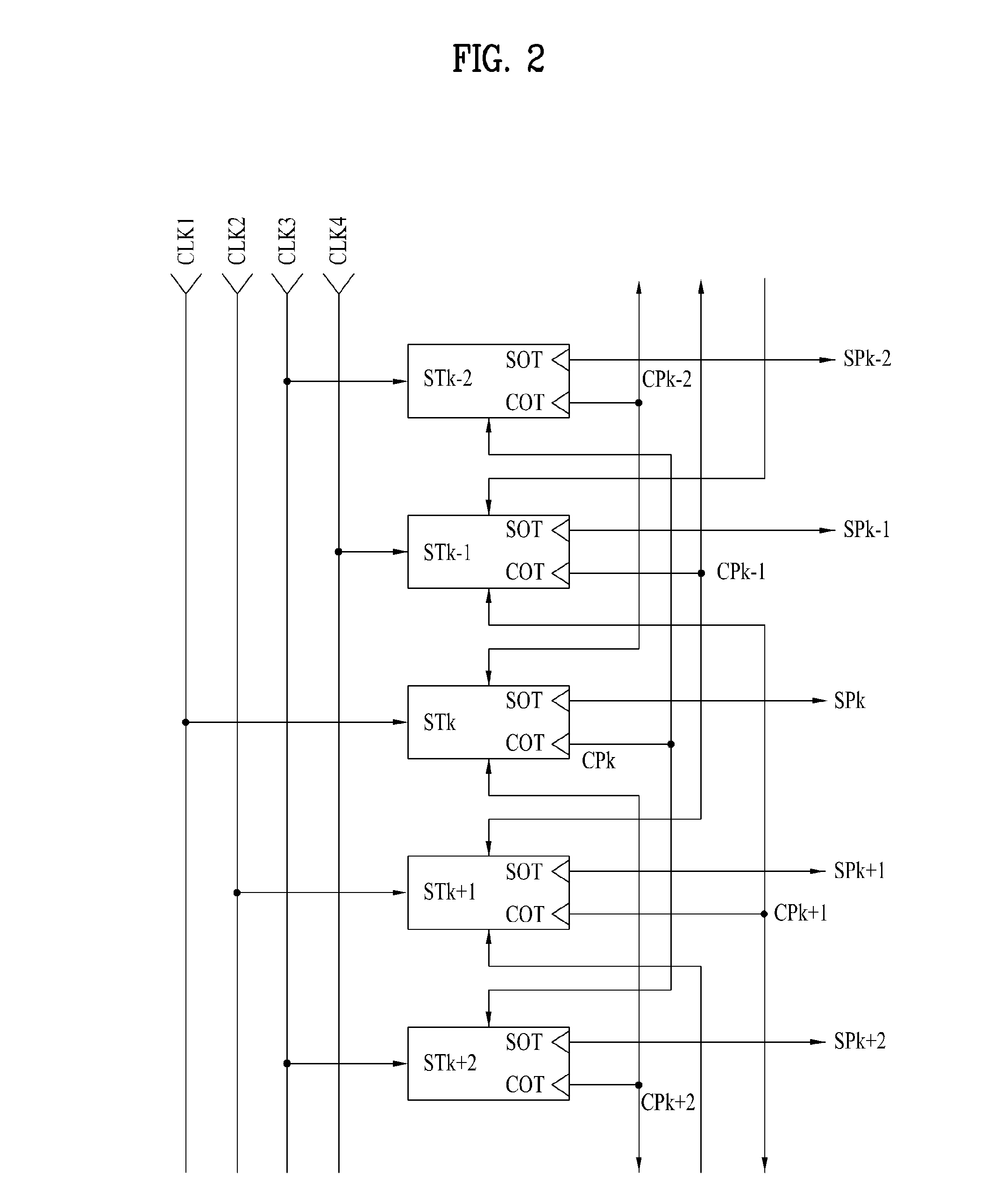

Shift register

ActiveUS20100214279A1Easy dischargeElectric analogue storesCathode-ray tube indicatorsShift registerEngineering

A shift register which is capable of minimizing a spike voltage is disclosed. The shift register includes a plurality of stages, each including a plurality of nodes, a scan pulse output unit controlled according to voltages at the nodes for outputting a scan pulse and supplying it to a corresponding gate line through a scan output terminal, a carry pulse output unit controlled according to the voltages at the nodes for outputting a carry pulse and supplying it to an upstream stage and a downstream stage through a carry output terminal, a node controller for controlling voltage states of the nodes in response to a carry pulse from the upstream stage and a carry pulse from the downstream stage, and a discharging unit connected to any one of a plurality of clock transfer lines and the scan output terminal for discharging a spike voltage of the scan output terminal.

Owner:E INK CORPORATION

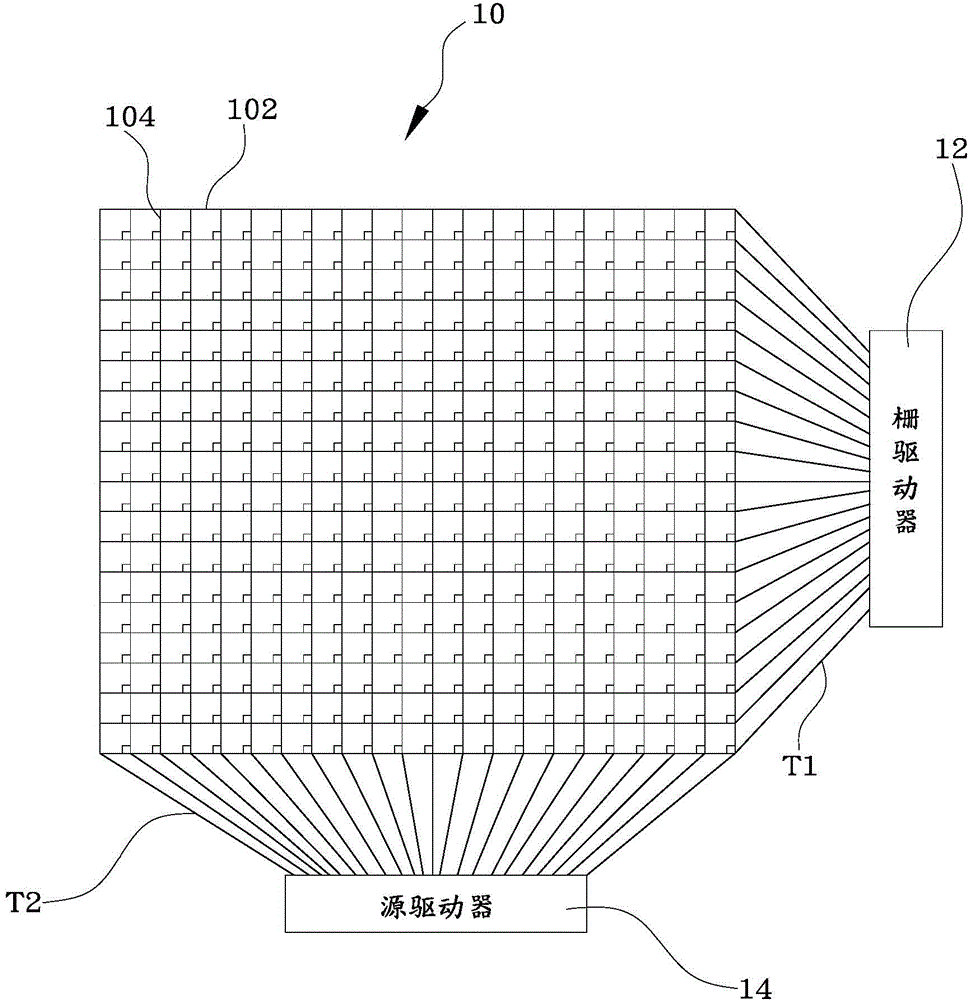

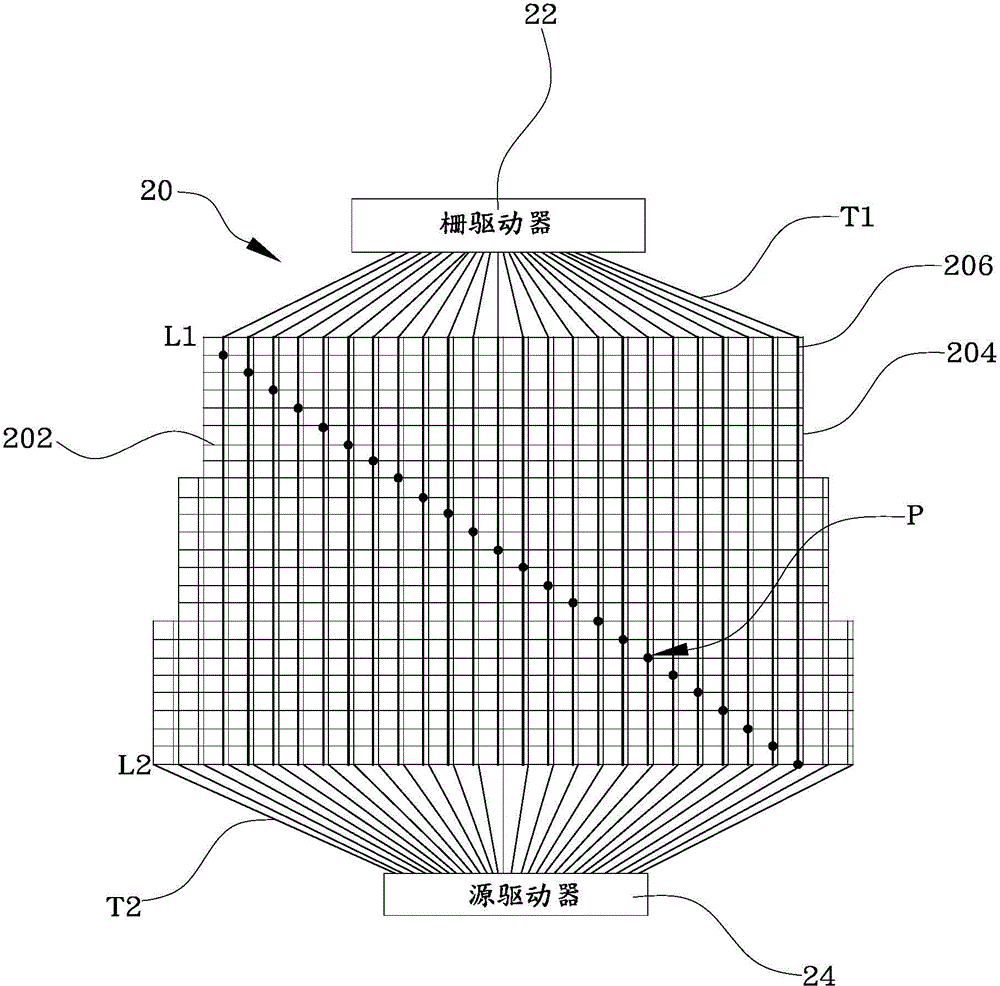

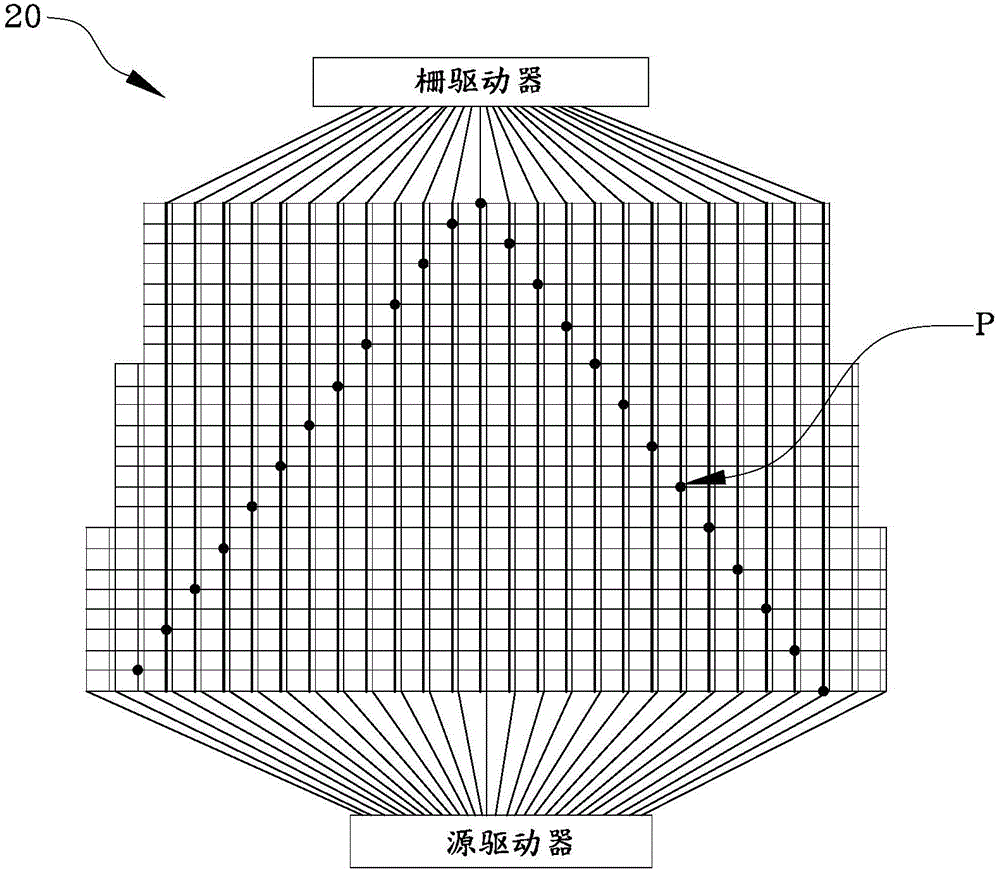

Liquid crystal display

InactiveCN104134429ARealize the display effectImprove narrow border effectStatic indicating devicesLiquid-crystal displayGate driver

The invention provides a liquid crystal display. The liquid crystal display comprises an effective display region, a gate driver and a source driver, wherein the effective display region comprises a plurality of gate lines, source lines and signal transfer lines arranged in a staggered mode, the gate lines are vertical to the source lines, and the signal transfer lines are vertical to the gate lines; the gate driver comprises a plurality of first terminals respectively electrically connected with the corresponding signal transfer lines; the source driver comprises a plurality of second terminals respectively electrically connected with the corresponding source lines; the gate driver and the source driver are respectively arranged at two parallel sides of the ladder-shaped effective display region; and the gate lines and the corresponding signal transfer lines are electrically conducted via a transfer pad to enable the gate lines to receive gate drive signals of the gate driver. Compared with the prior art, the gate driver and the source driver are arranged at two parallel sides, signal wiring does not need to occupy space at the left side and the right side of the panel, and effects of a narrow border can be further enhanced.

Owner:AU OPTRONICS CORP

Product recovery from simulated-moving-bed adsorption

Product purity from or capacity of a simulated-moving-bed adsorptive separation process is increased by flushing the contents of the transfer line previously used to remove the raffinate stream away from the adsorbent chamber, preferably into the raffinate column used to separate desorbent from raffinate product. Preferably a stream from the adsorbent chamber at an intermediate point between the feed entry point and raffinate withdrawal is used as the flushing liquid. This flush step eliminates the passage of a quantity of the raffinate material into the adsorbent chamber in the transfer-line flush period or when the process conduit is subsequently used to charge the feed stream to the adsorbent chamber.

Owner:UOP LLC

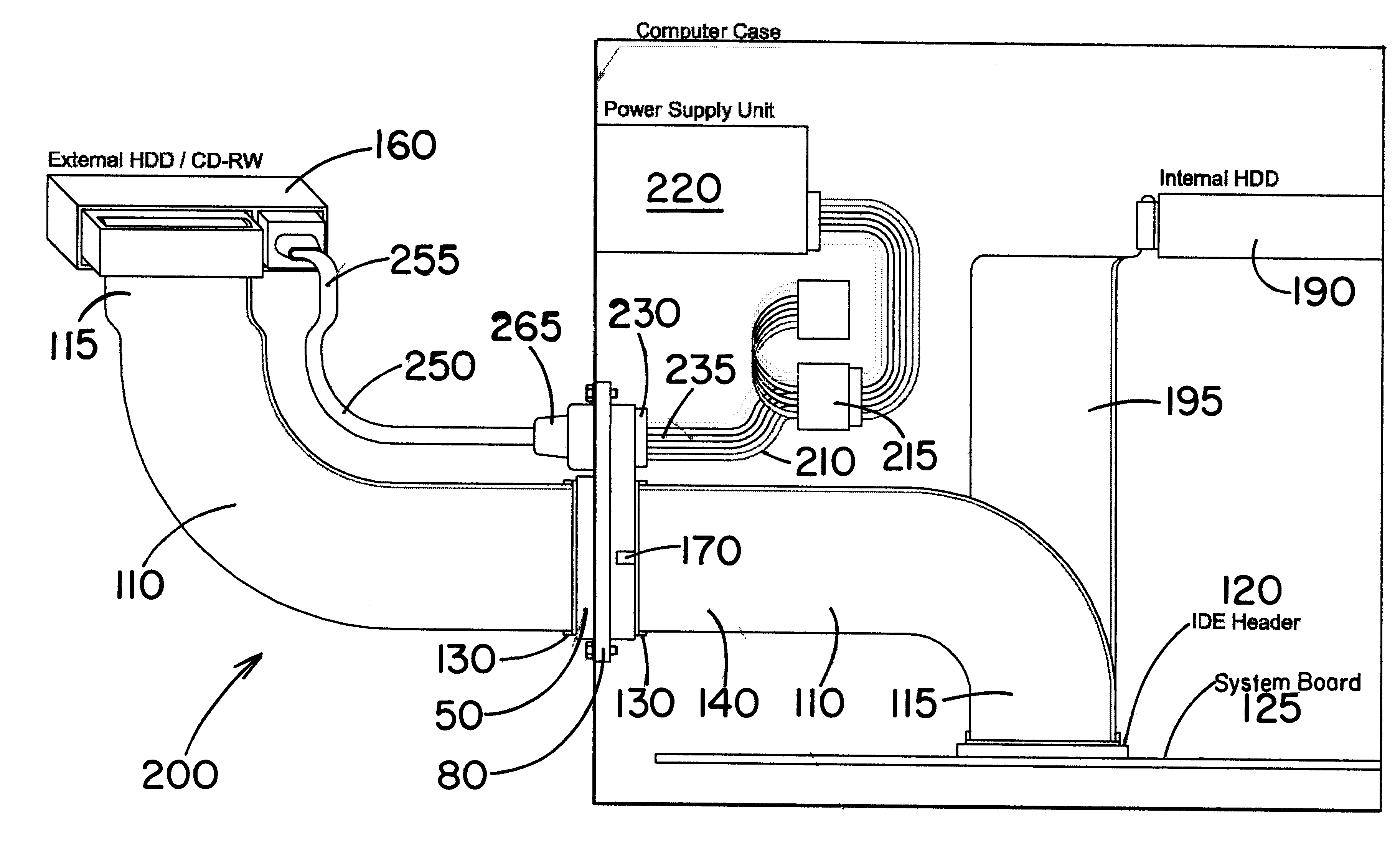

Mobile backup kit assembly

InactiveUS6361372B1Incorrect coupling preventionTwo-part coupling devicesHard disc driveElectric power

The present invention is directed to a connector and an assembly for connecting a computer having an internal hard drive with an external device for fast transmission of signals between devices. The connector provides for coupling two ATA signal transfer lines via two sets of signal transfer receptacles, with each receptacle set contained in a female connector of one signal transfer line. The connector also couples two electrical power lines to provide electrical power from the computer to the external device. A bracket secured to the connector positions the connector in an aperture of the computer case.

Owner:DAVID CHIANG