Patents

Literature

8030 results about "Shift register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital circuits, a shift register is a cascade of flip flops, sharing the same clock, in which the output of each flip-flop is connected to the "data" input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the "bit array" stored in it, "shifting in" the data present at its input and 'shifting out' the last bit in the array, at each transition of the clock input.

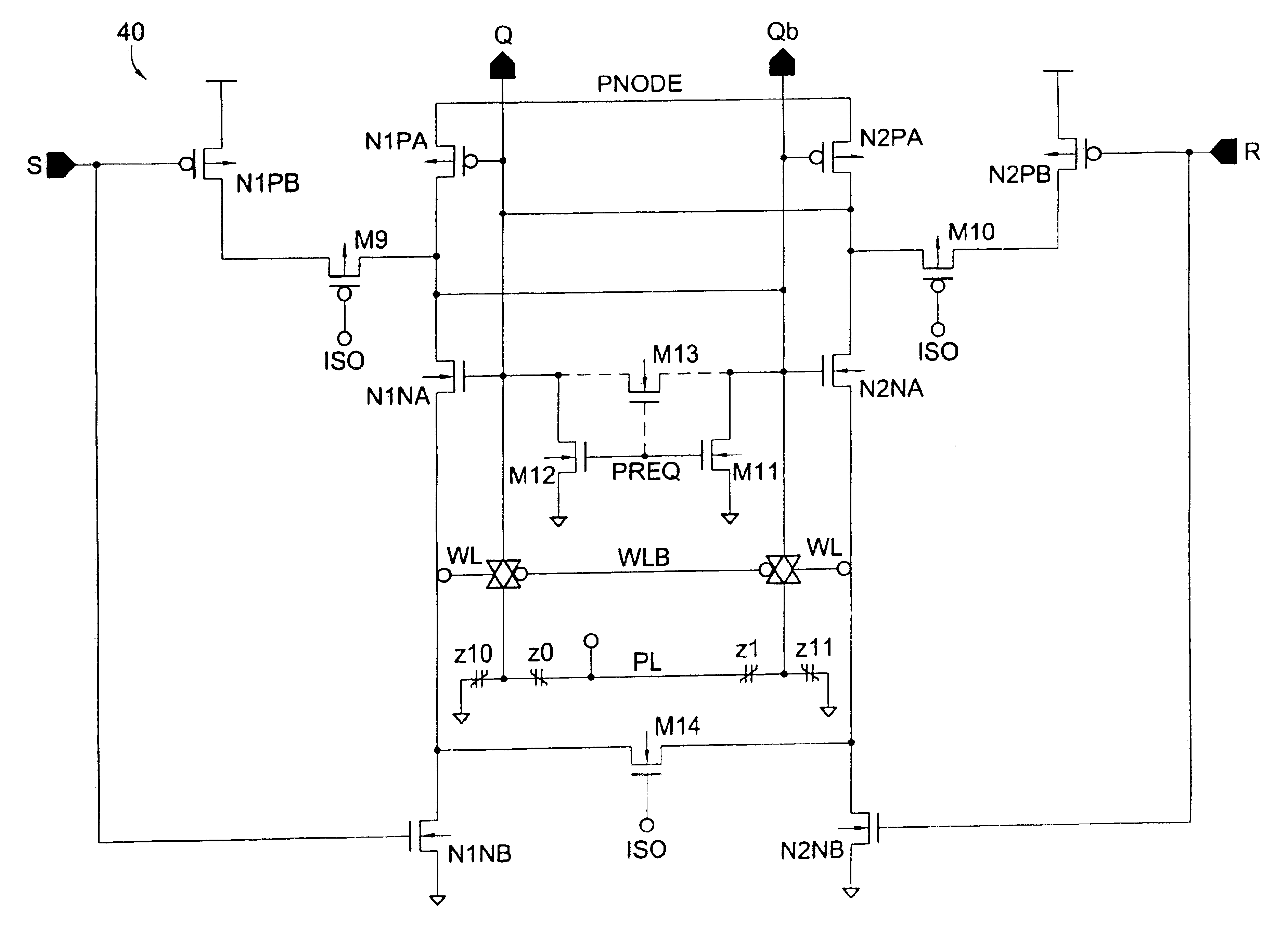

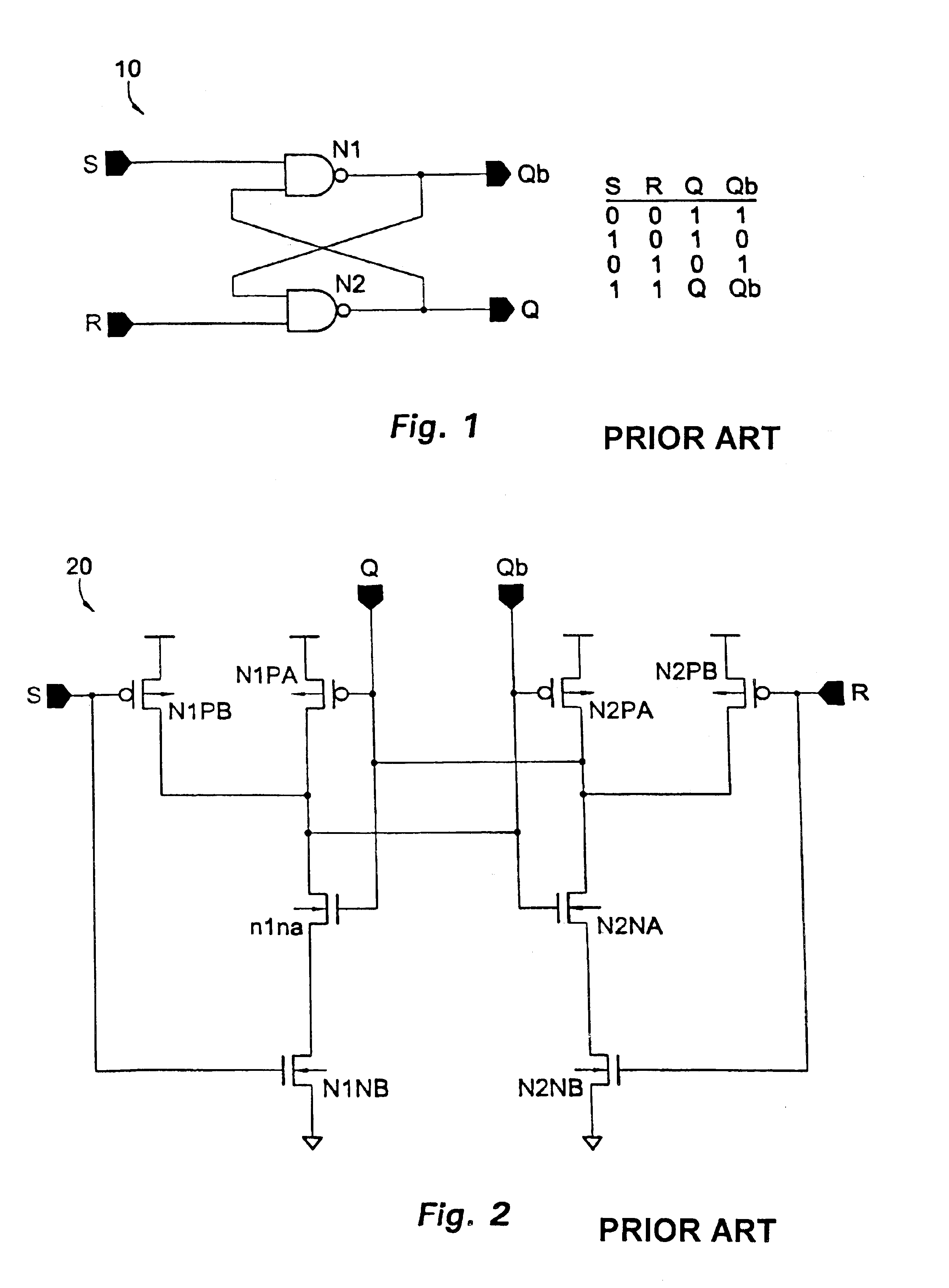

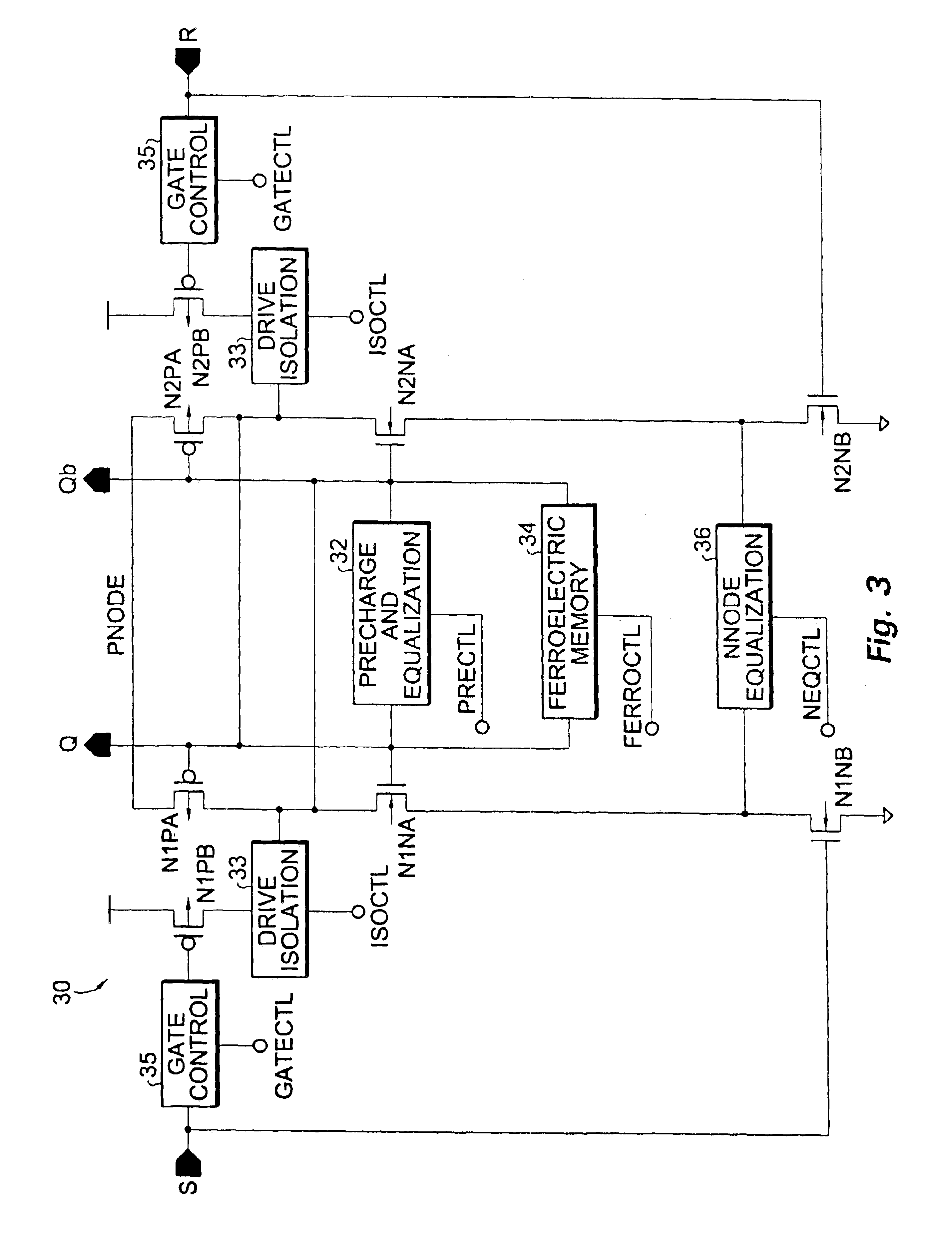

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

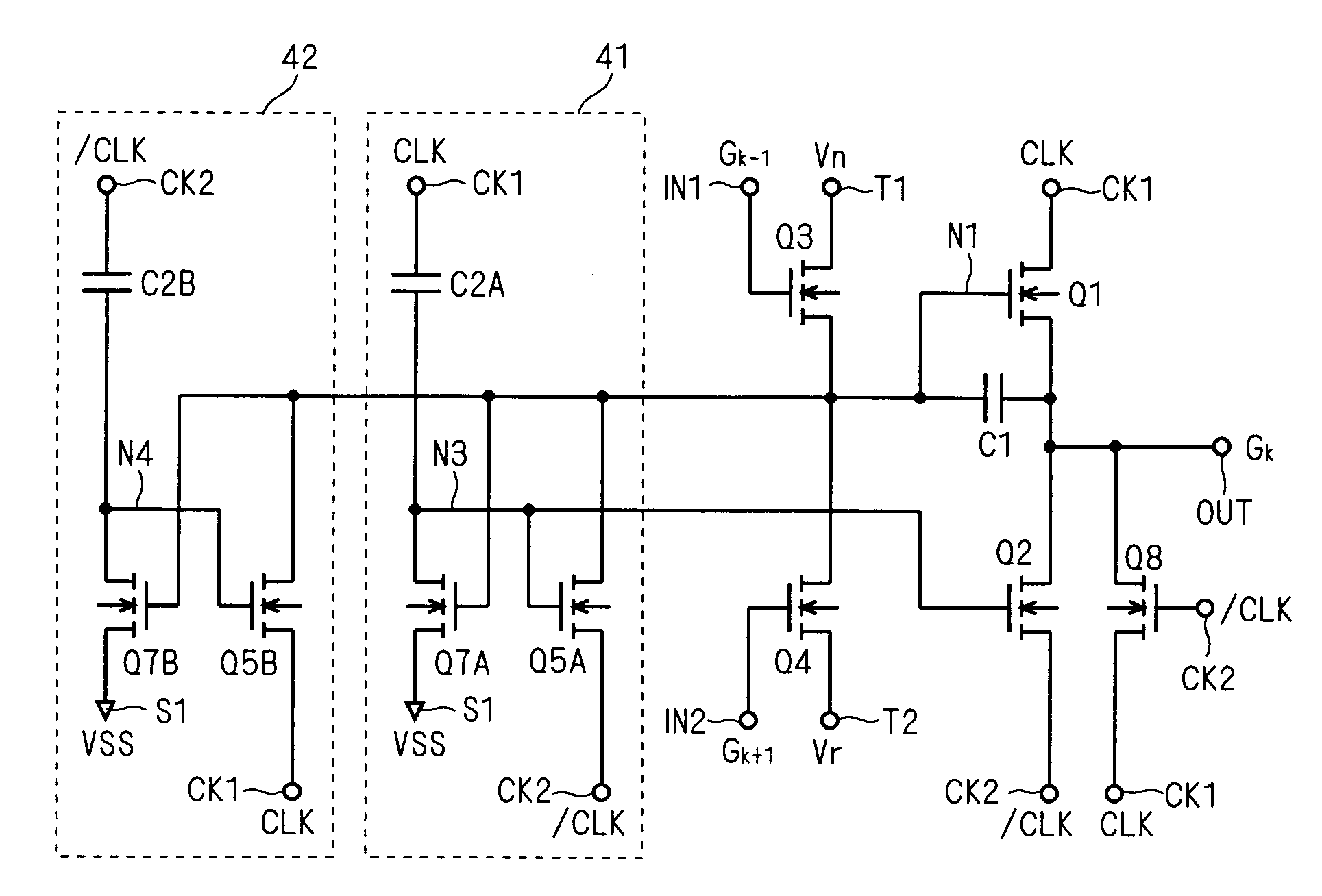

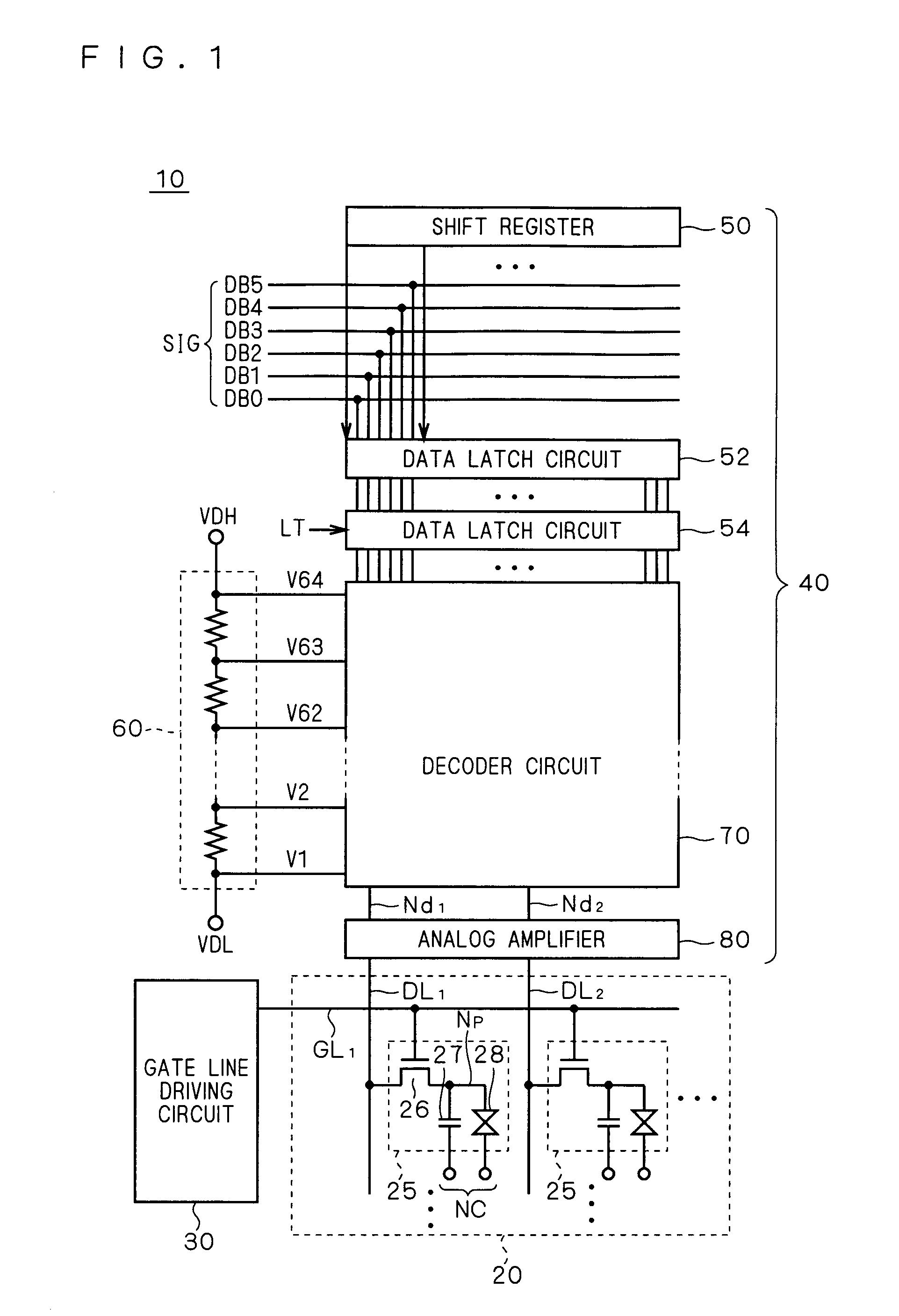

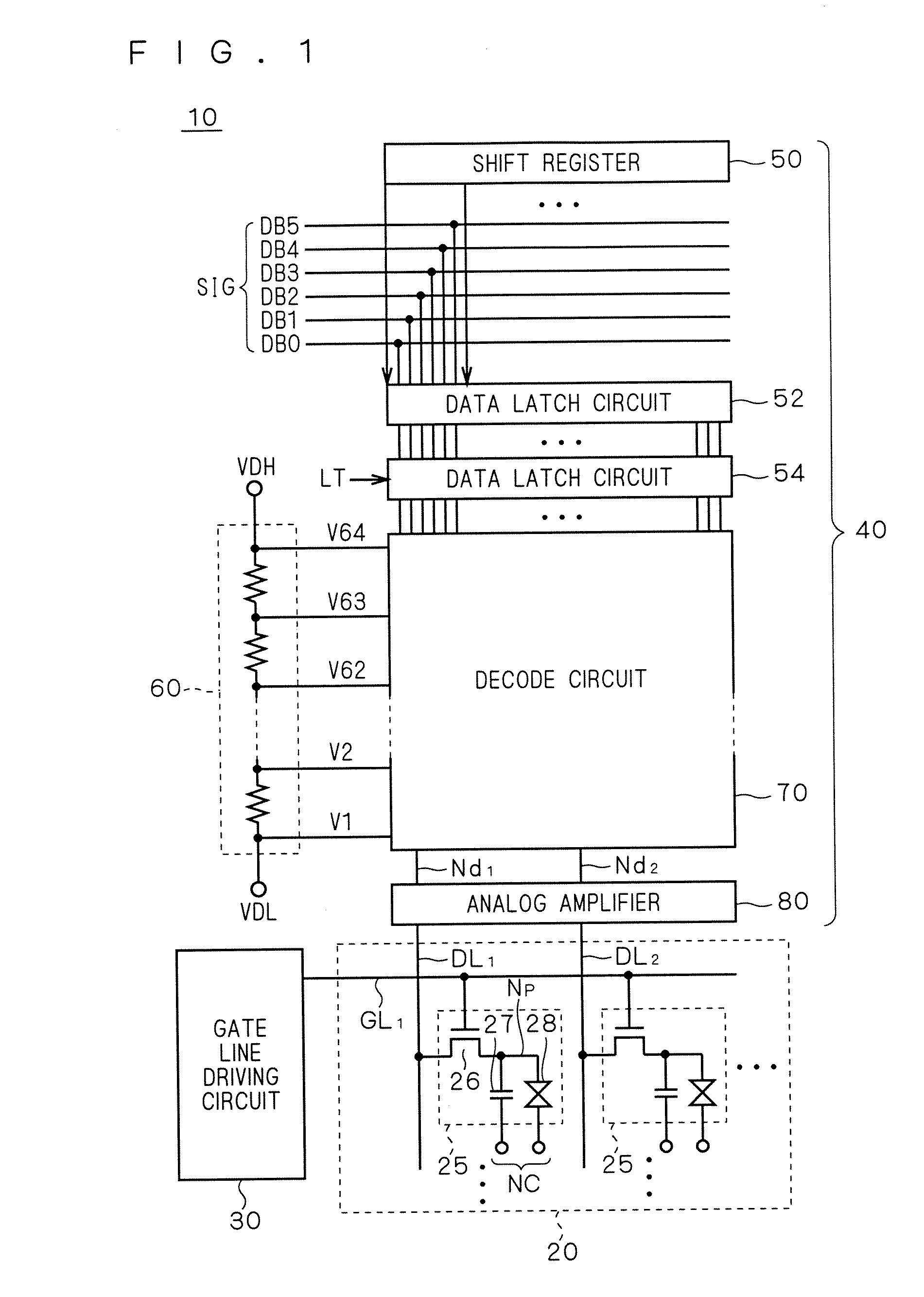

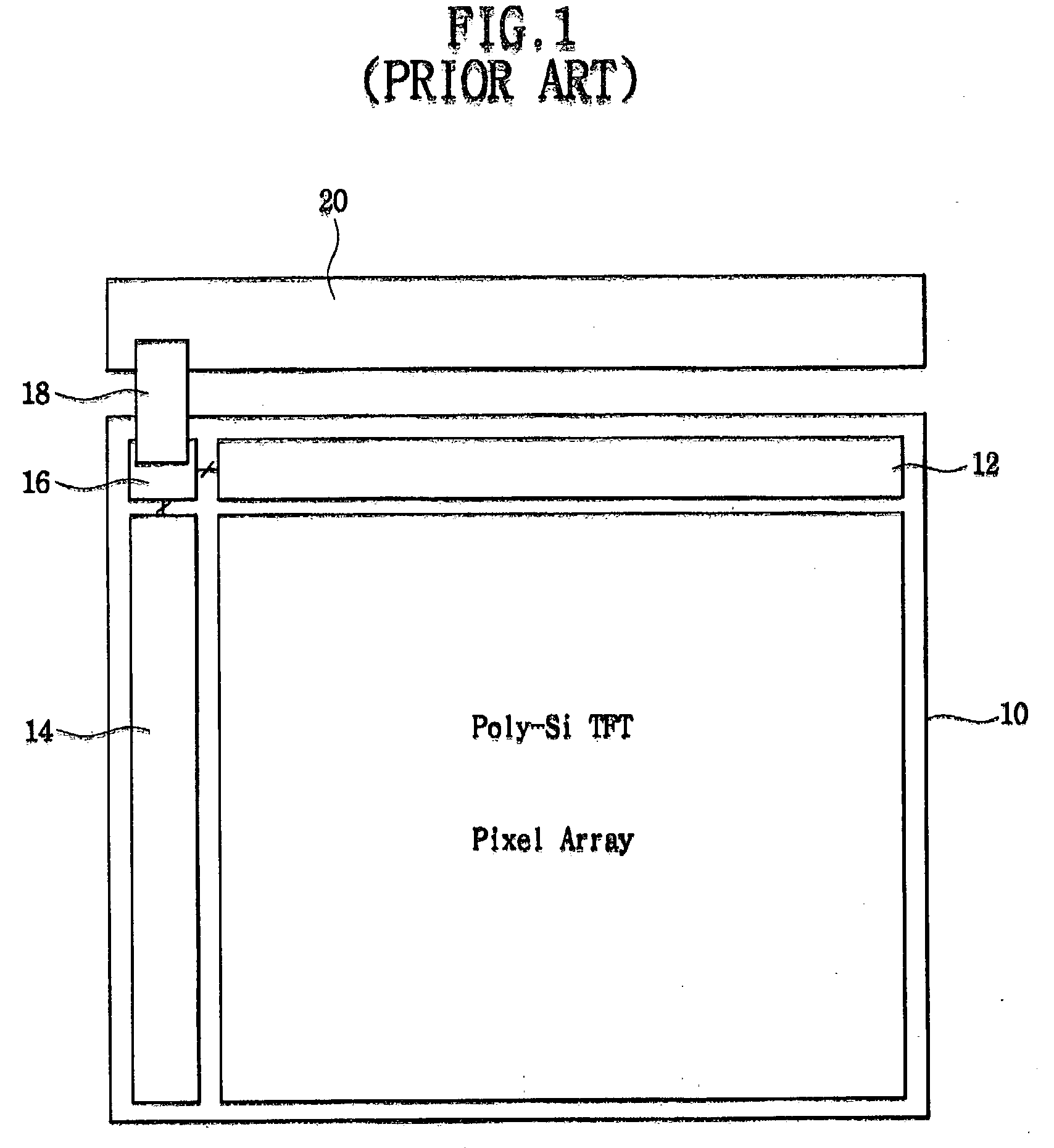

Shift register circuit and image display apparatus containing the same

InactiveUS20080219401A1Avoid failureReduced driving abilityStatic indicating devicesDigital storageShift registerProcessor register

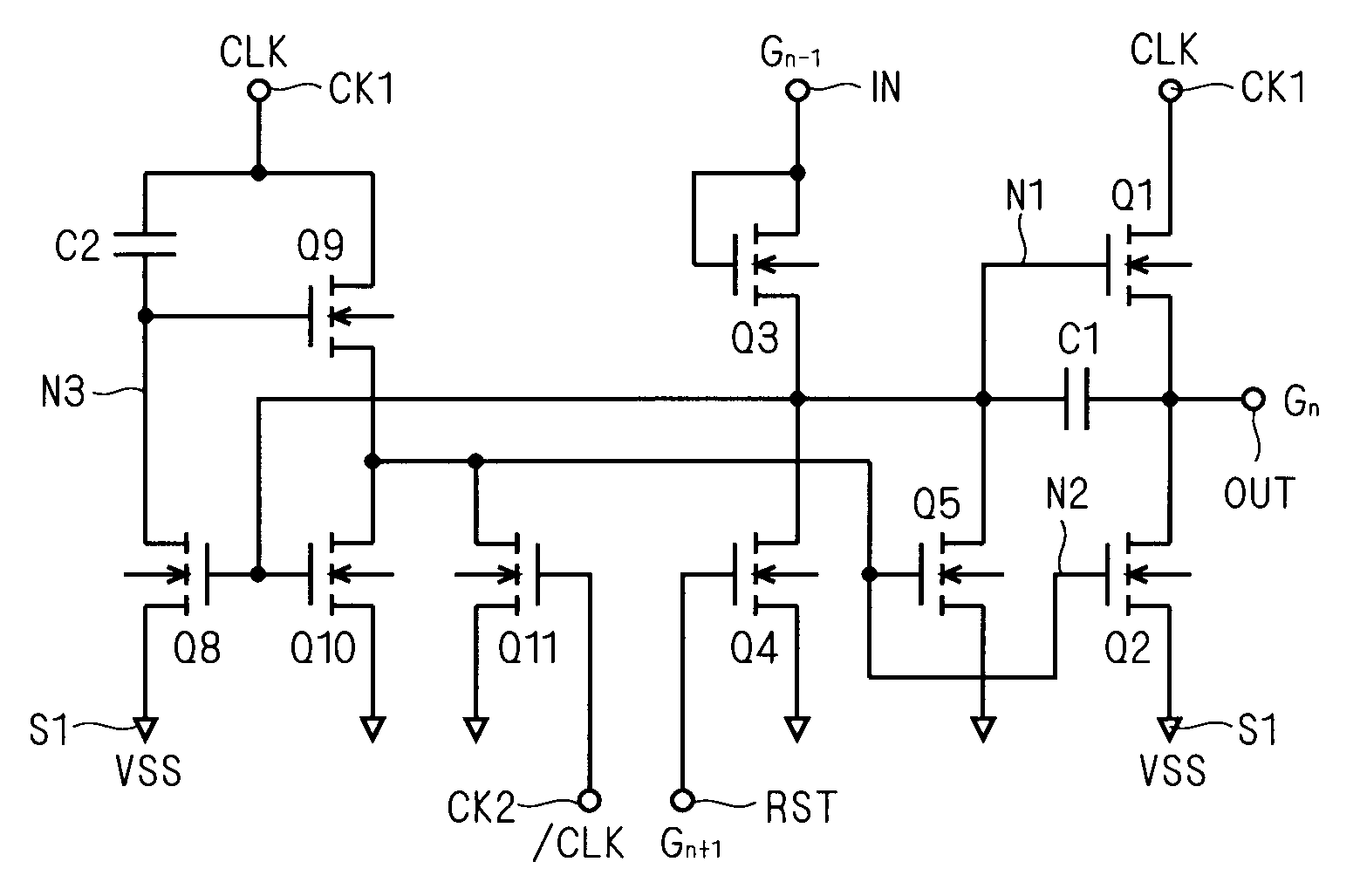

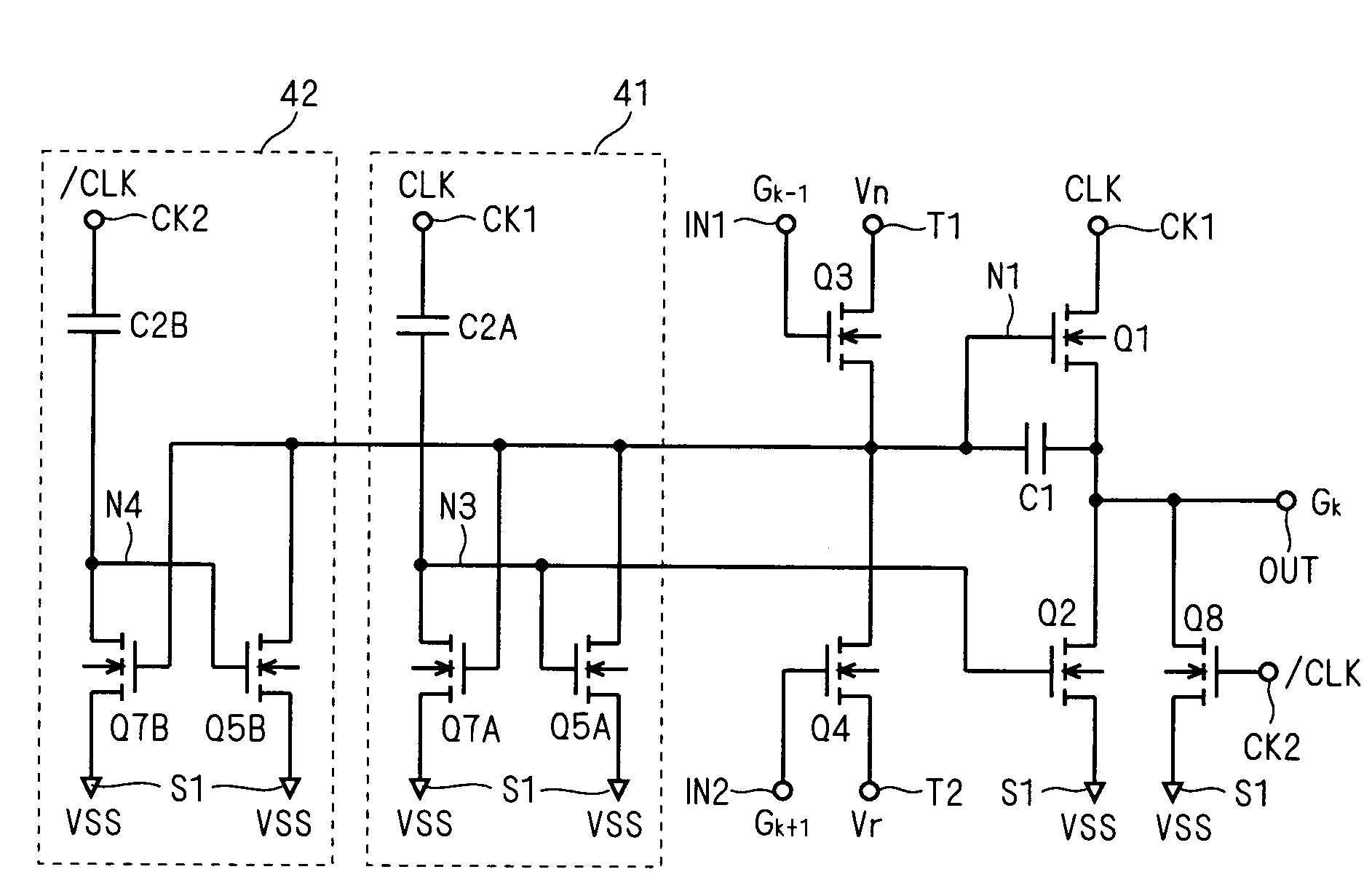

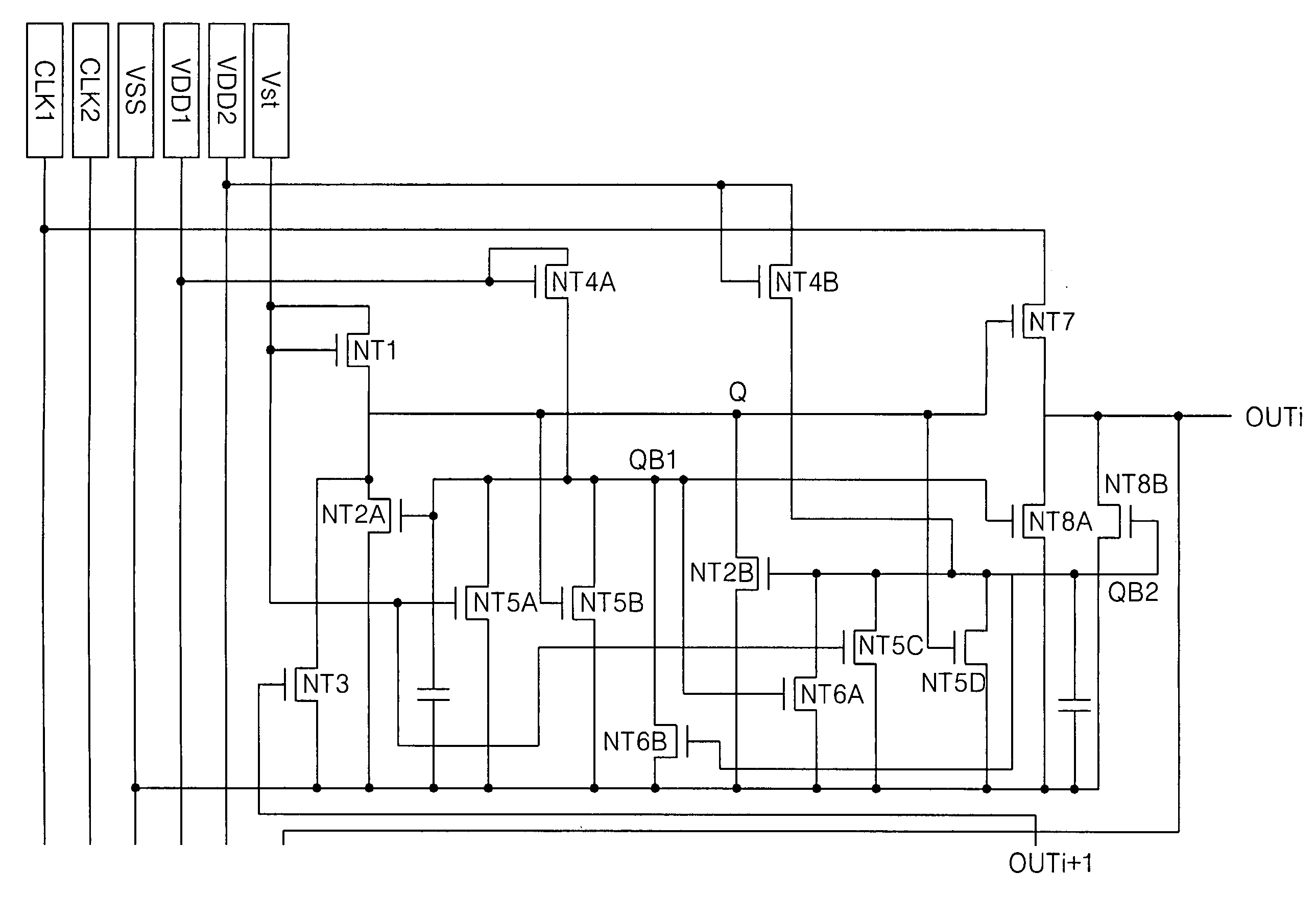

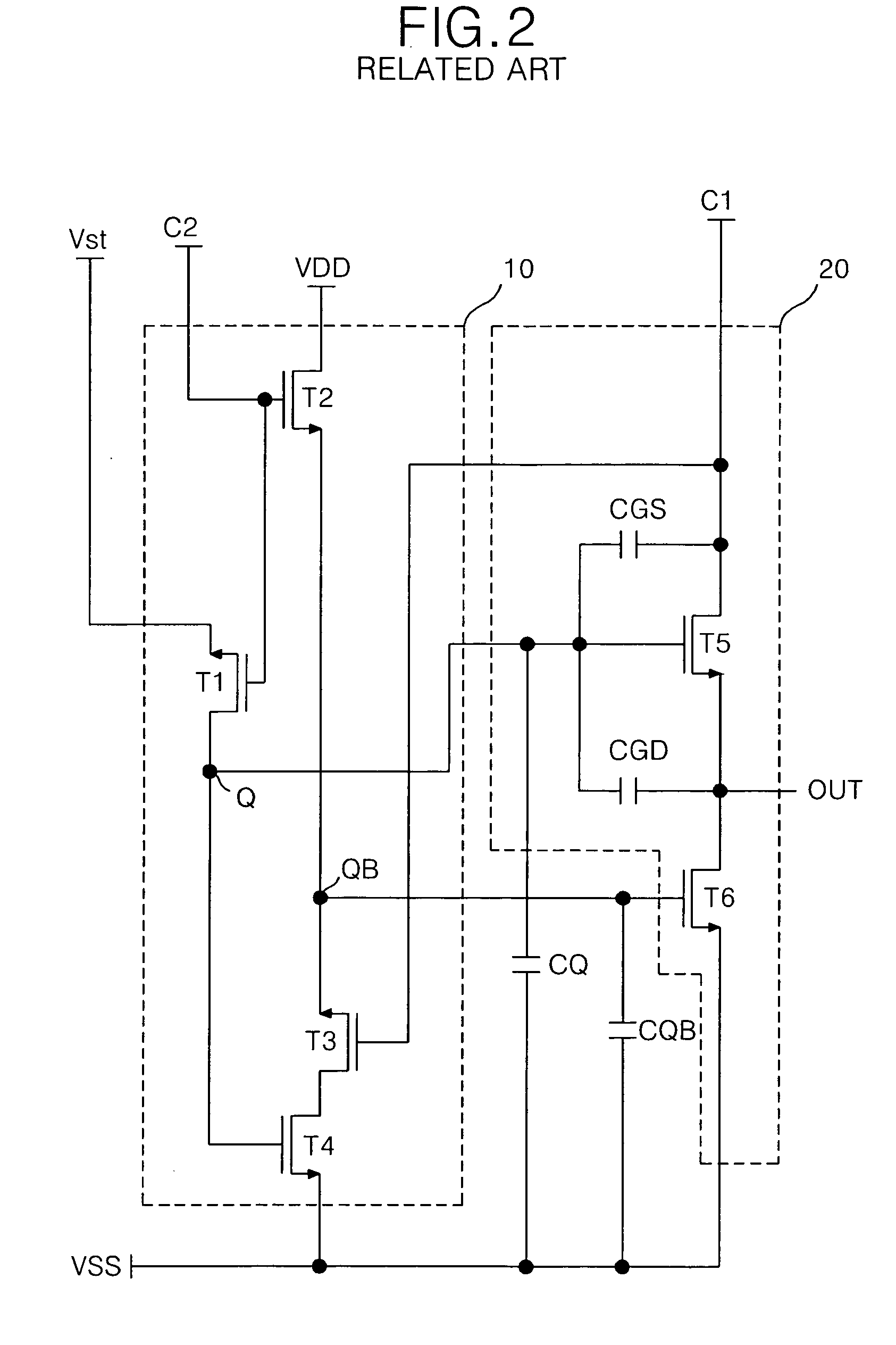

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:TRIVALE TECH LLC

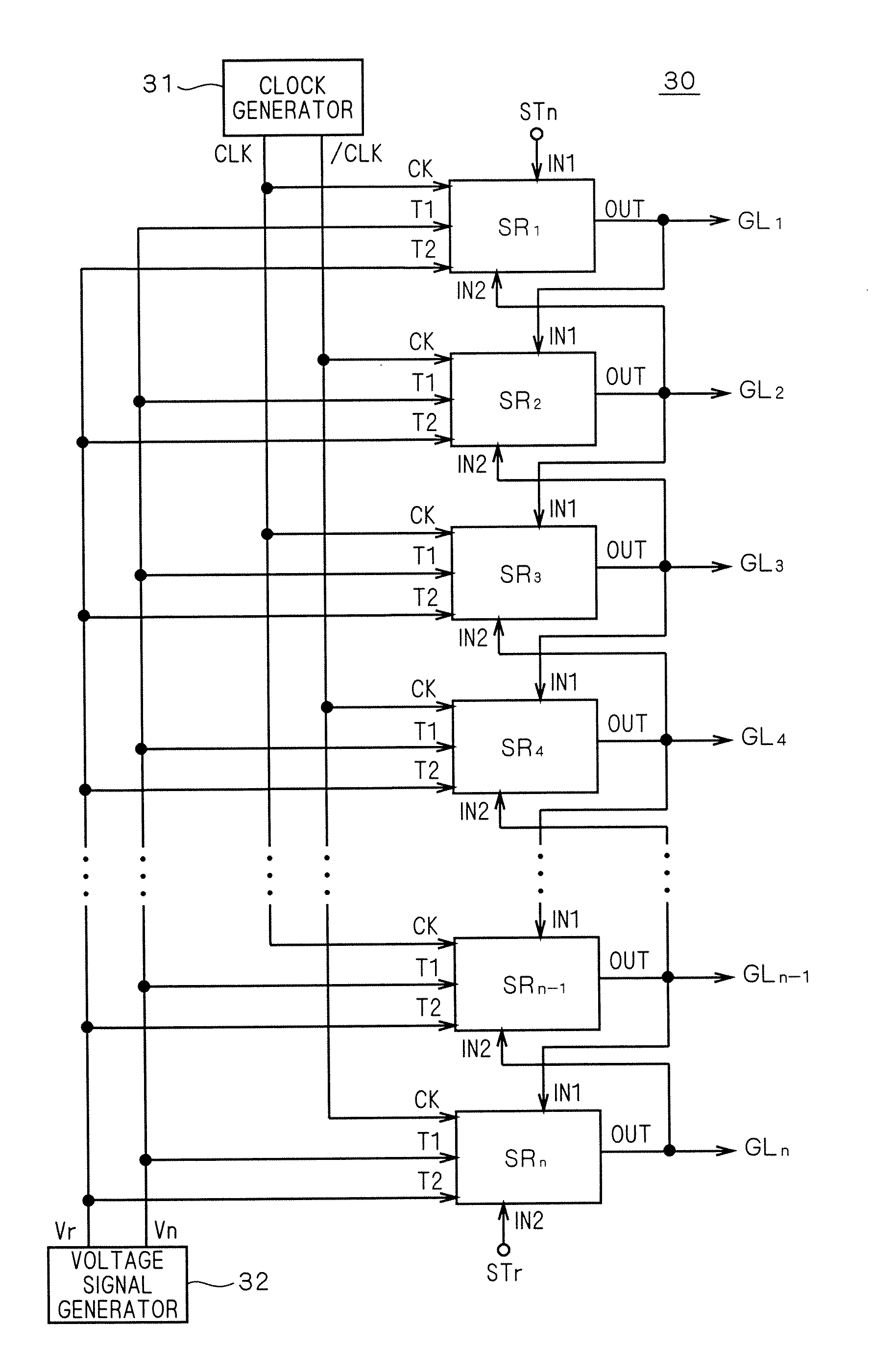

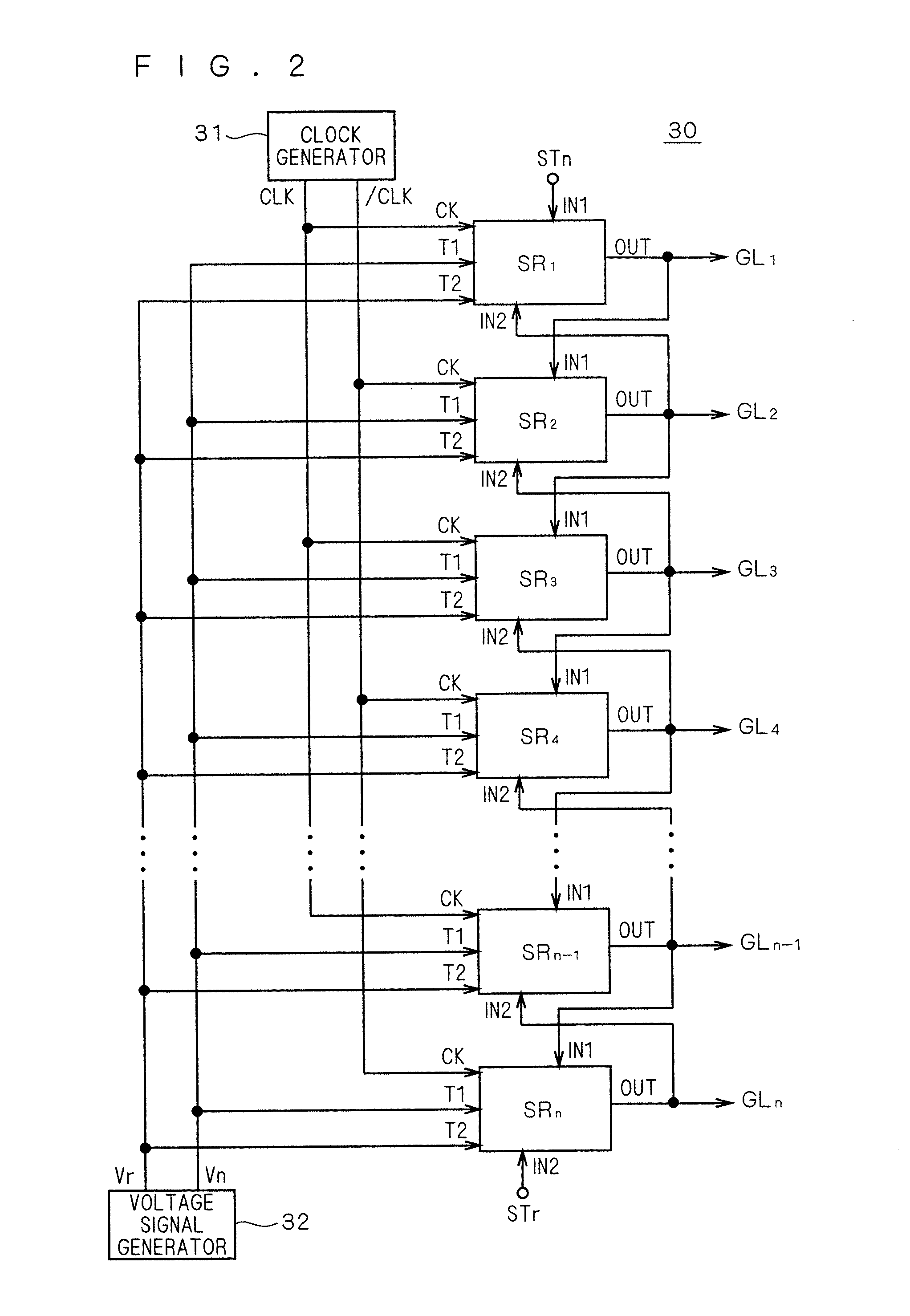

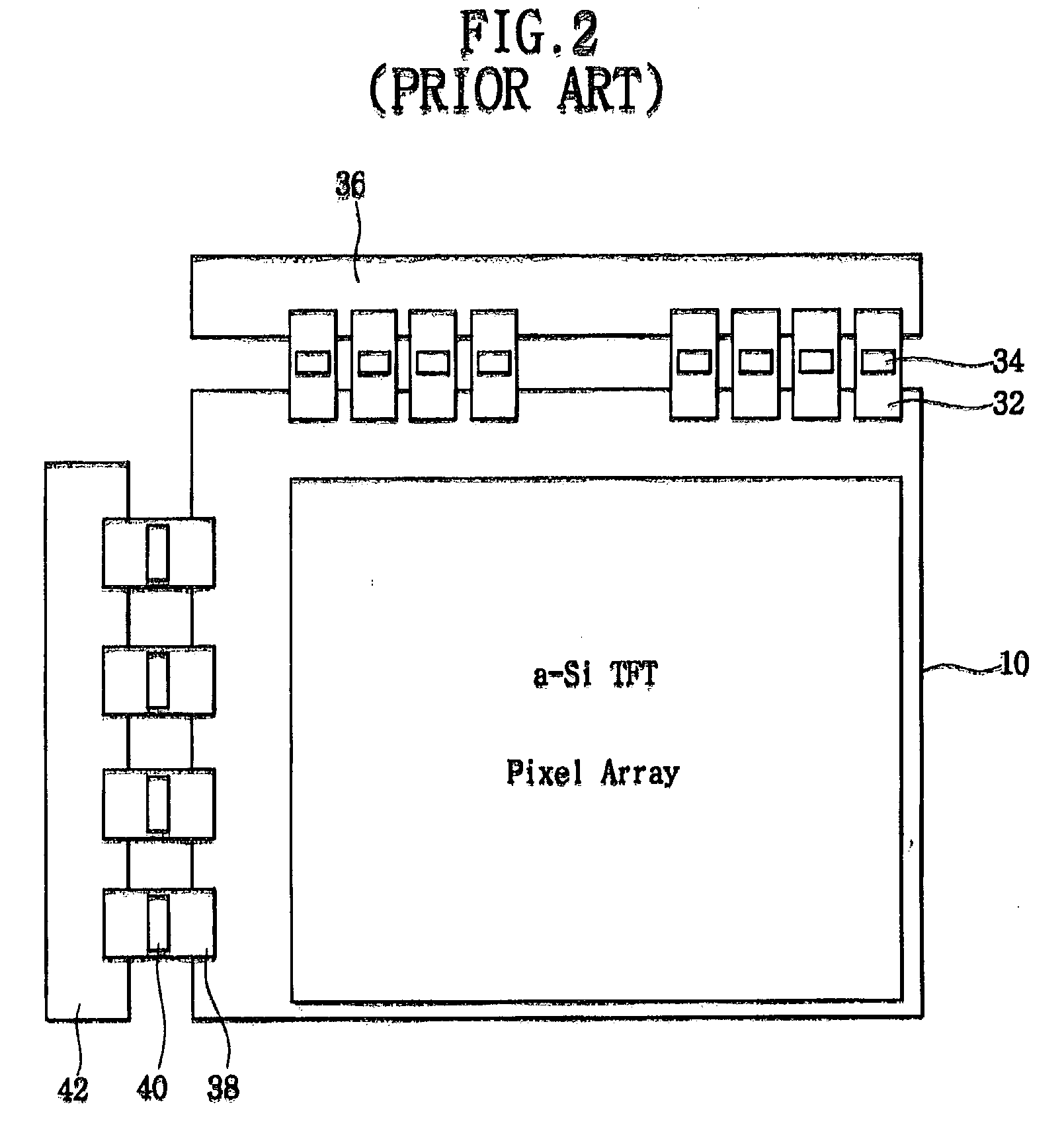

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

InactiveUS6845140B2InhibitionQuality improvementStatic indicating devicesDigital storageShift registerLiquid-crystal display

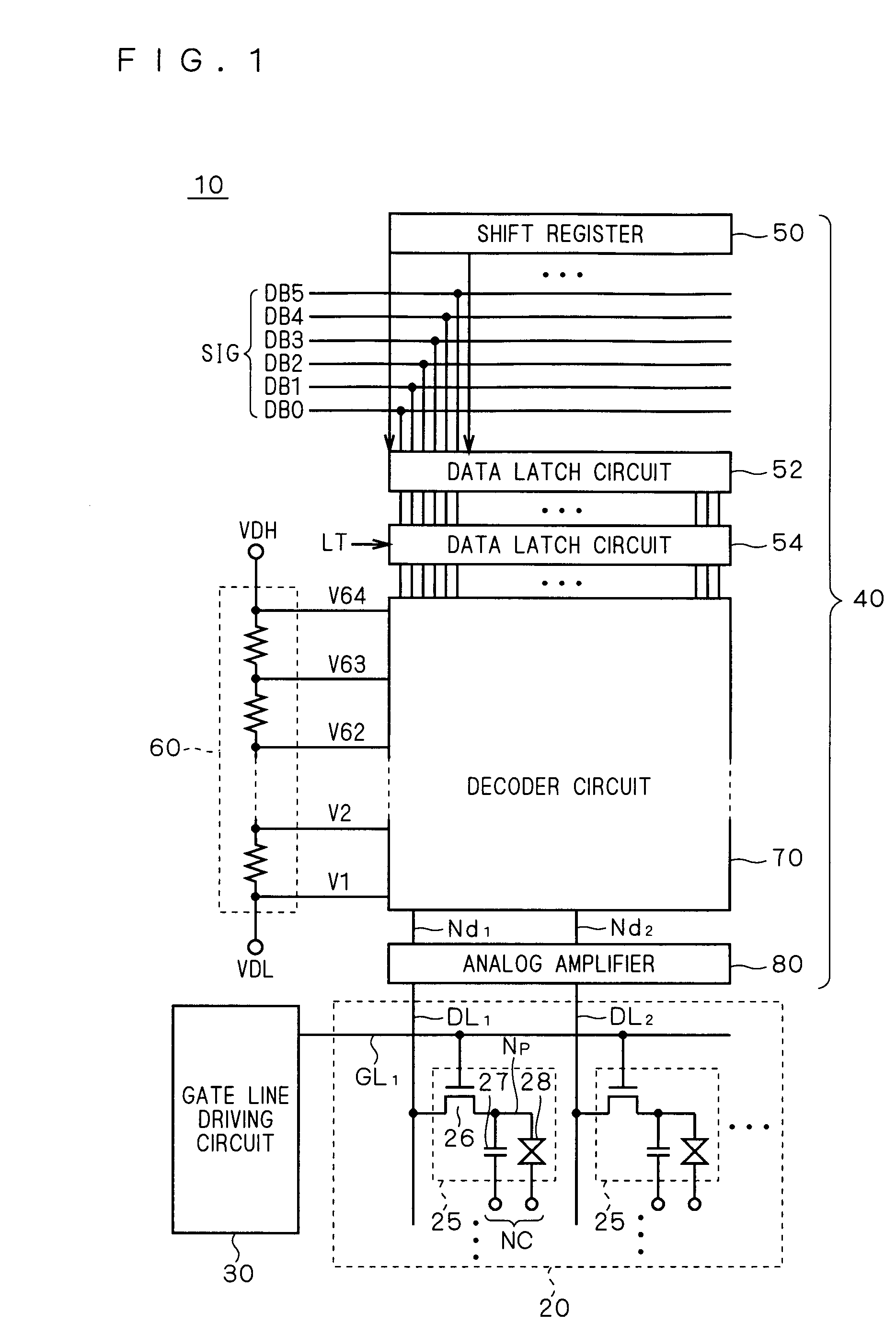

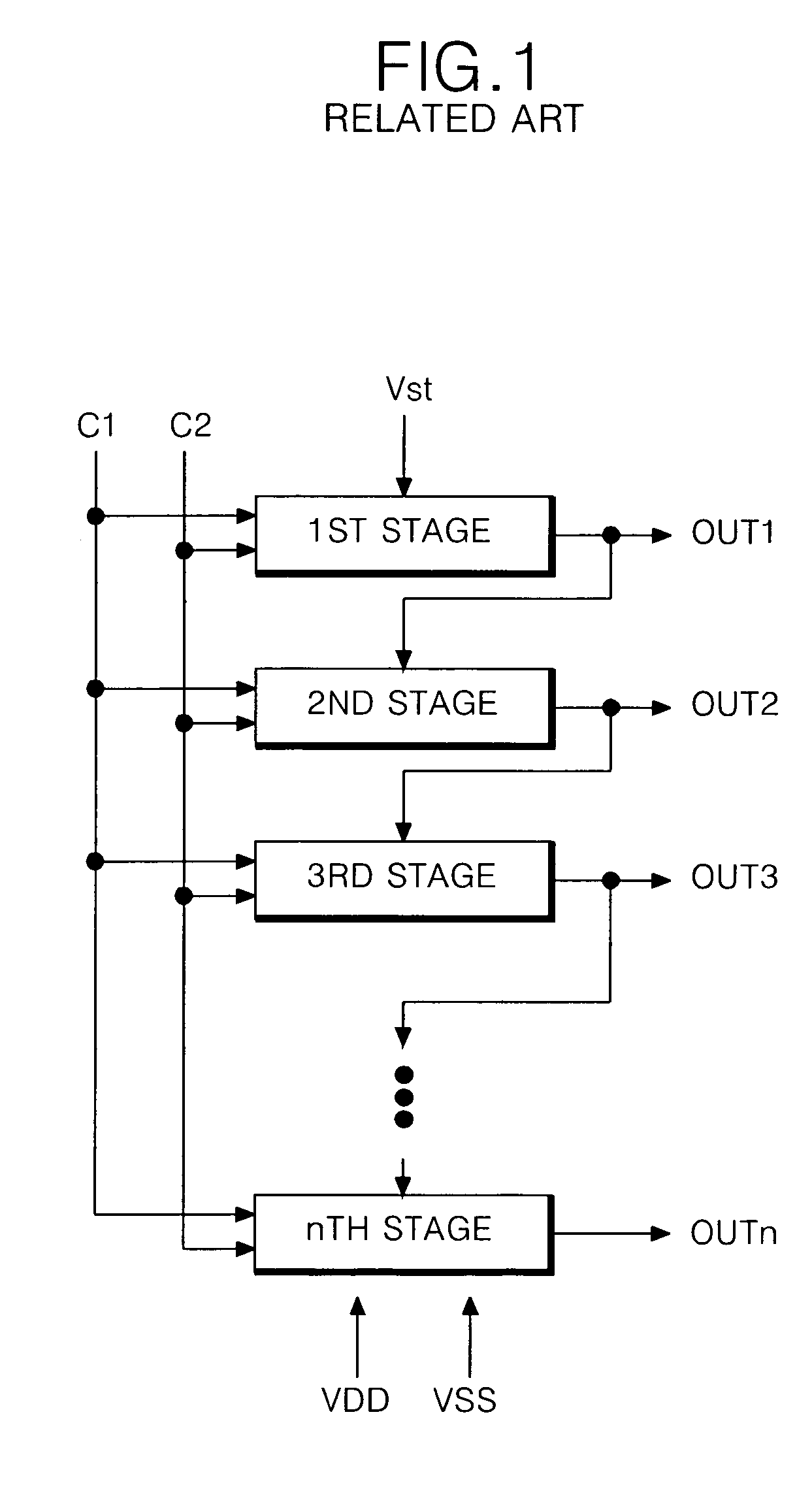

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages cascade-connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage Vona larger than the power voltage Von applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

Owner:SAMSUNG DISPLAY CO LTD

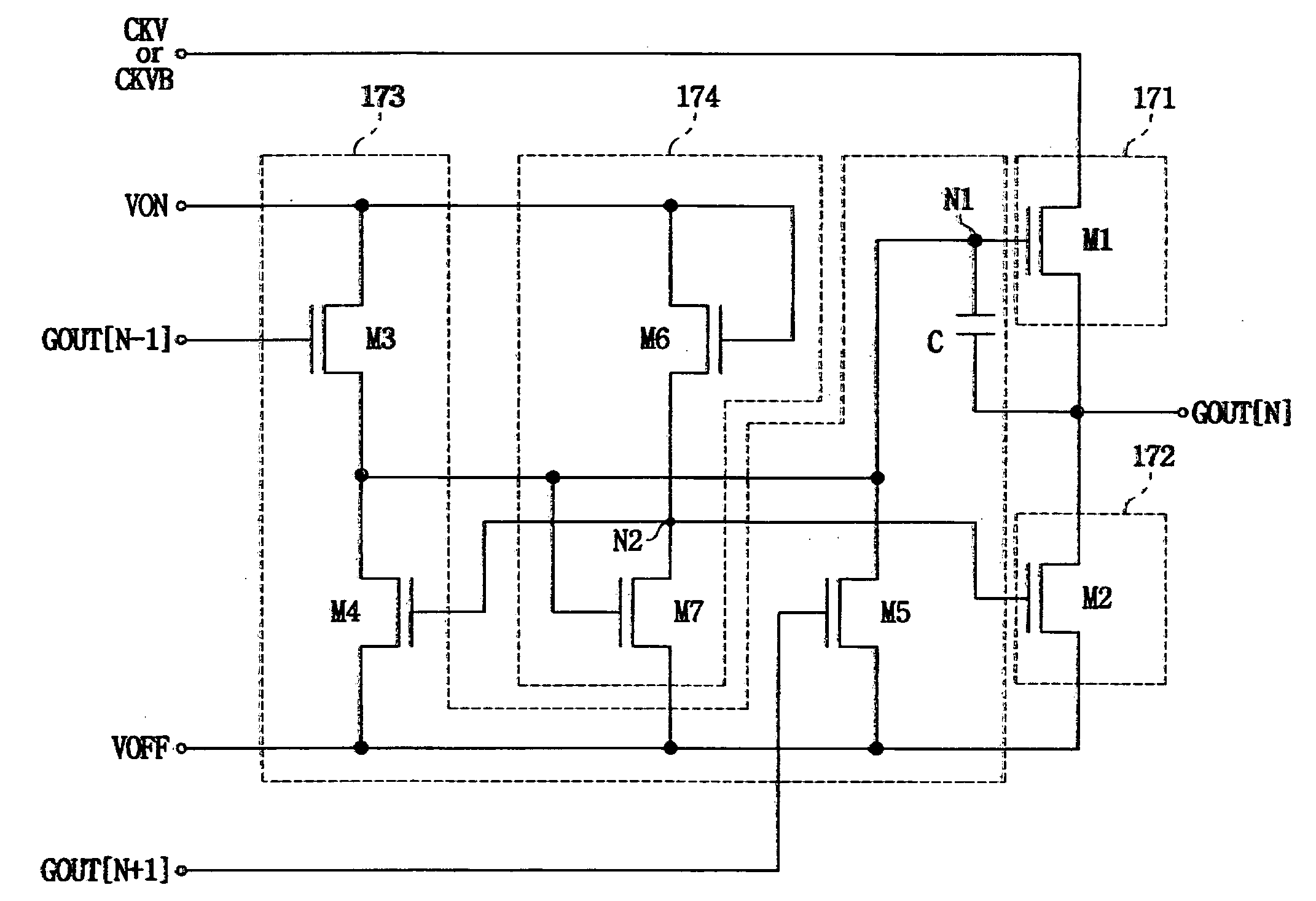

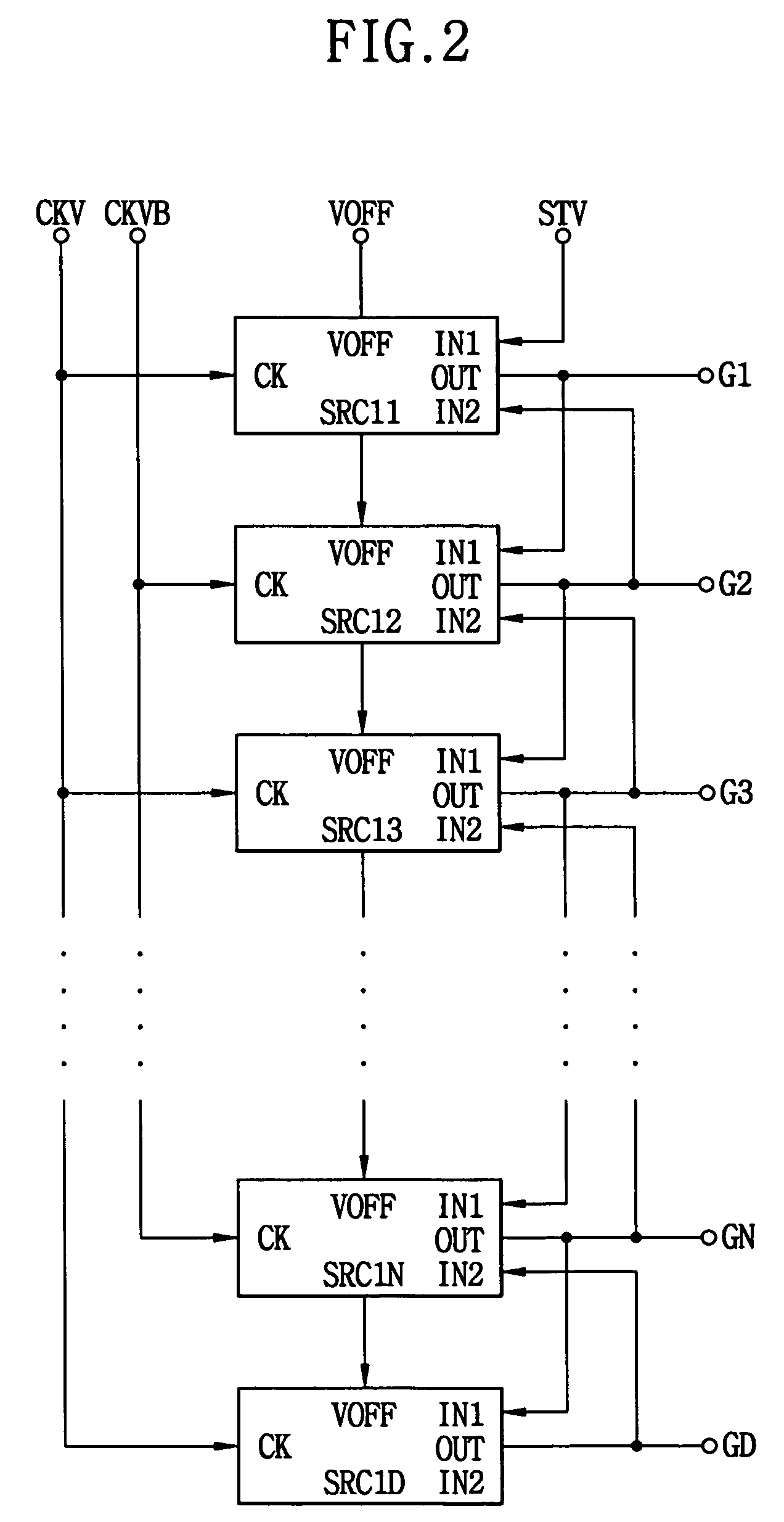

Shift register, display device having the same and method of driving the same

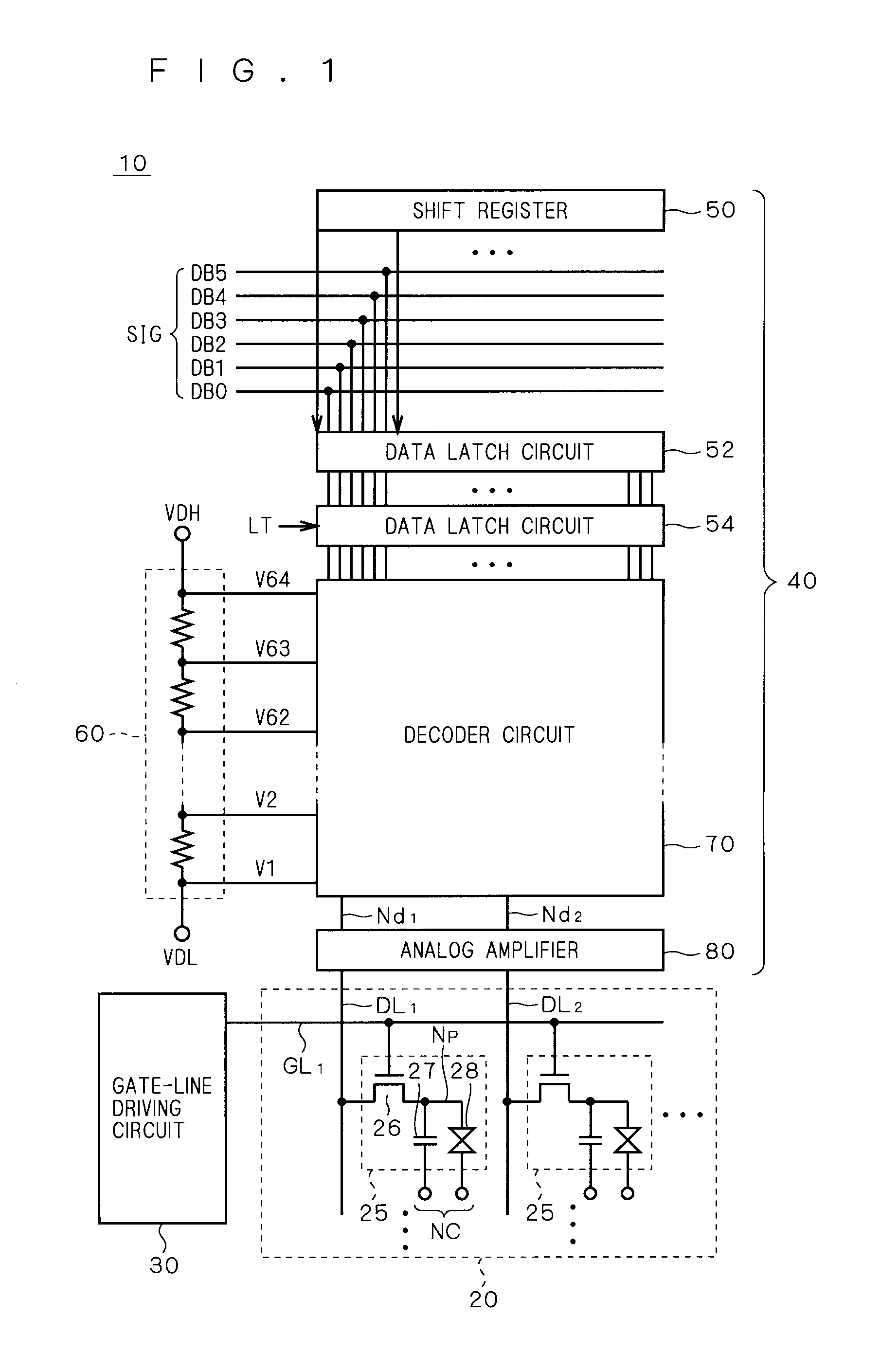

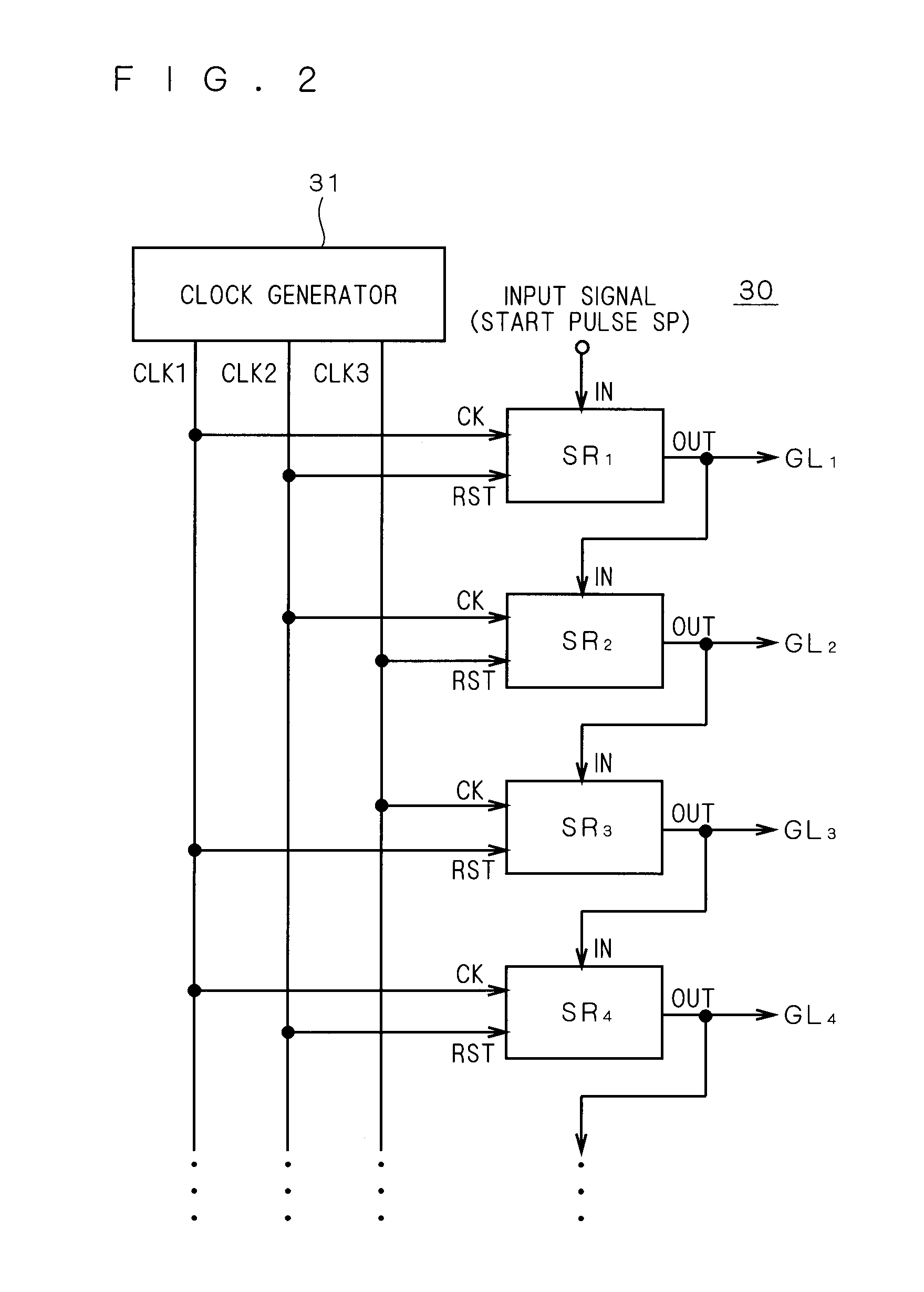

ActiveUS20060001637A1Improve reliabilitySize of display is limitedStatic indicating devicesDigital storageShift registerControl signal

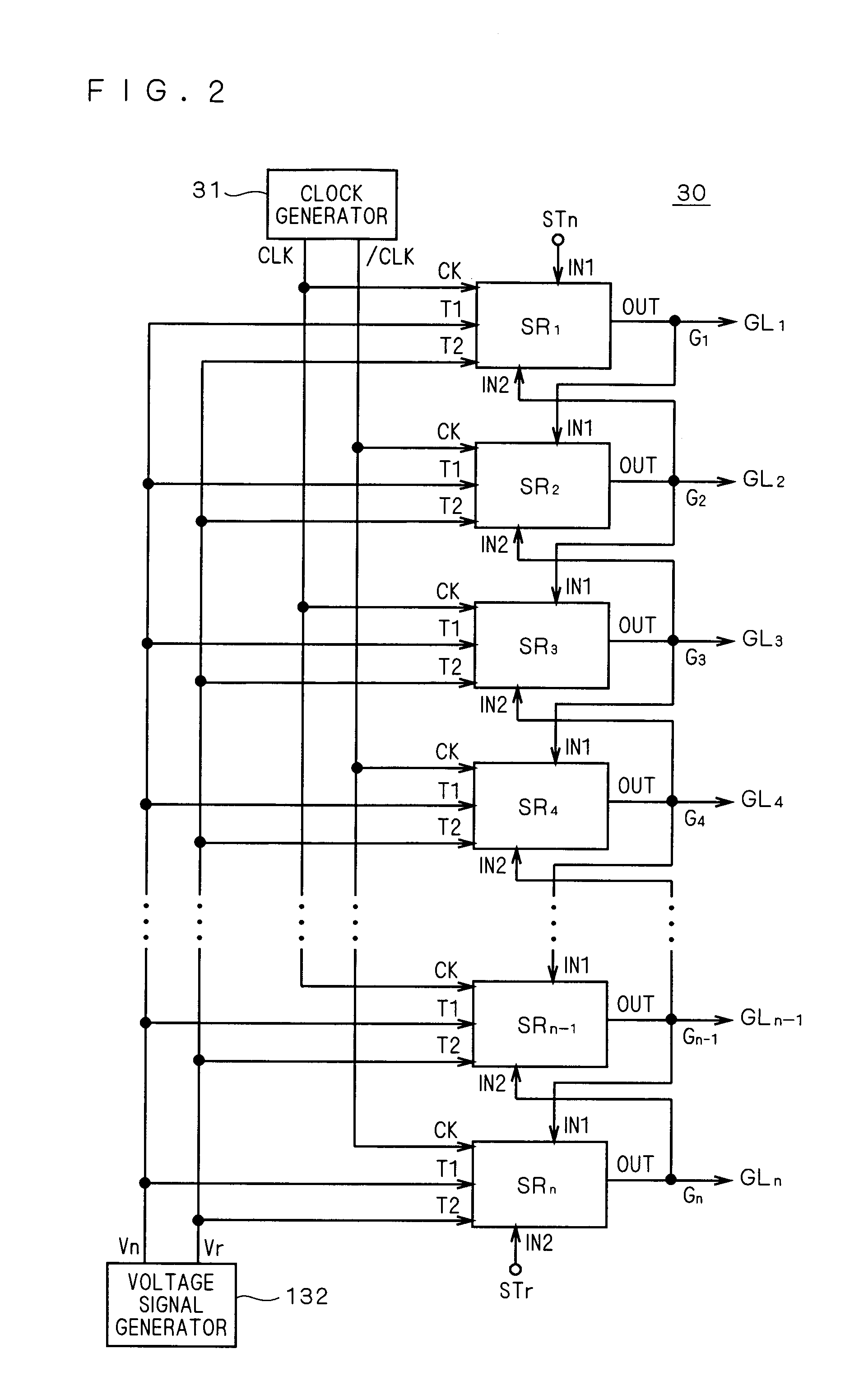

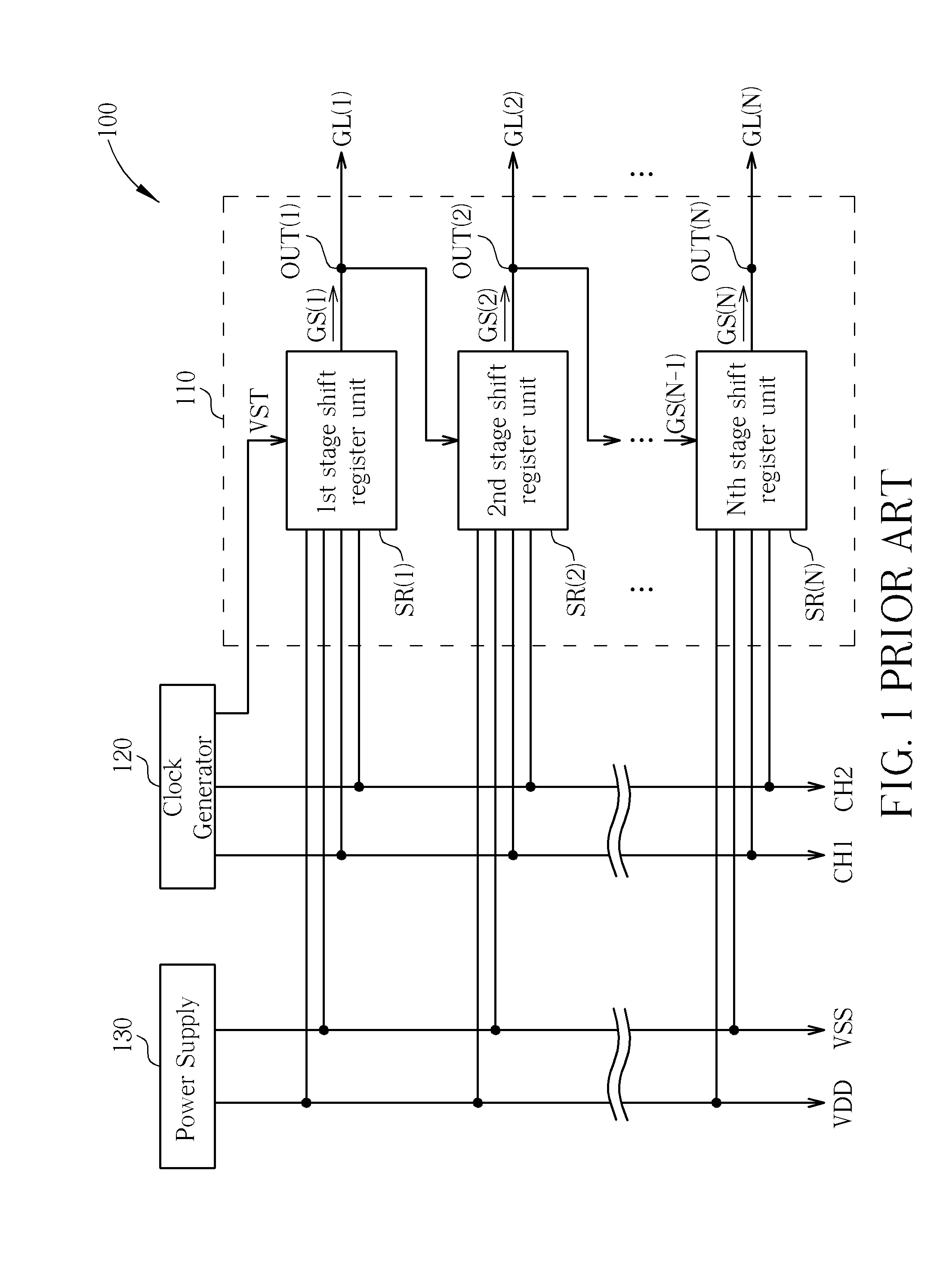

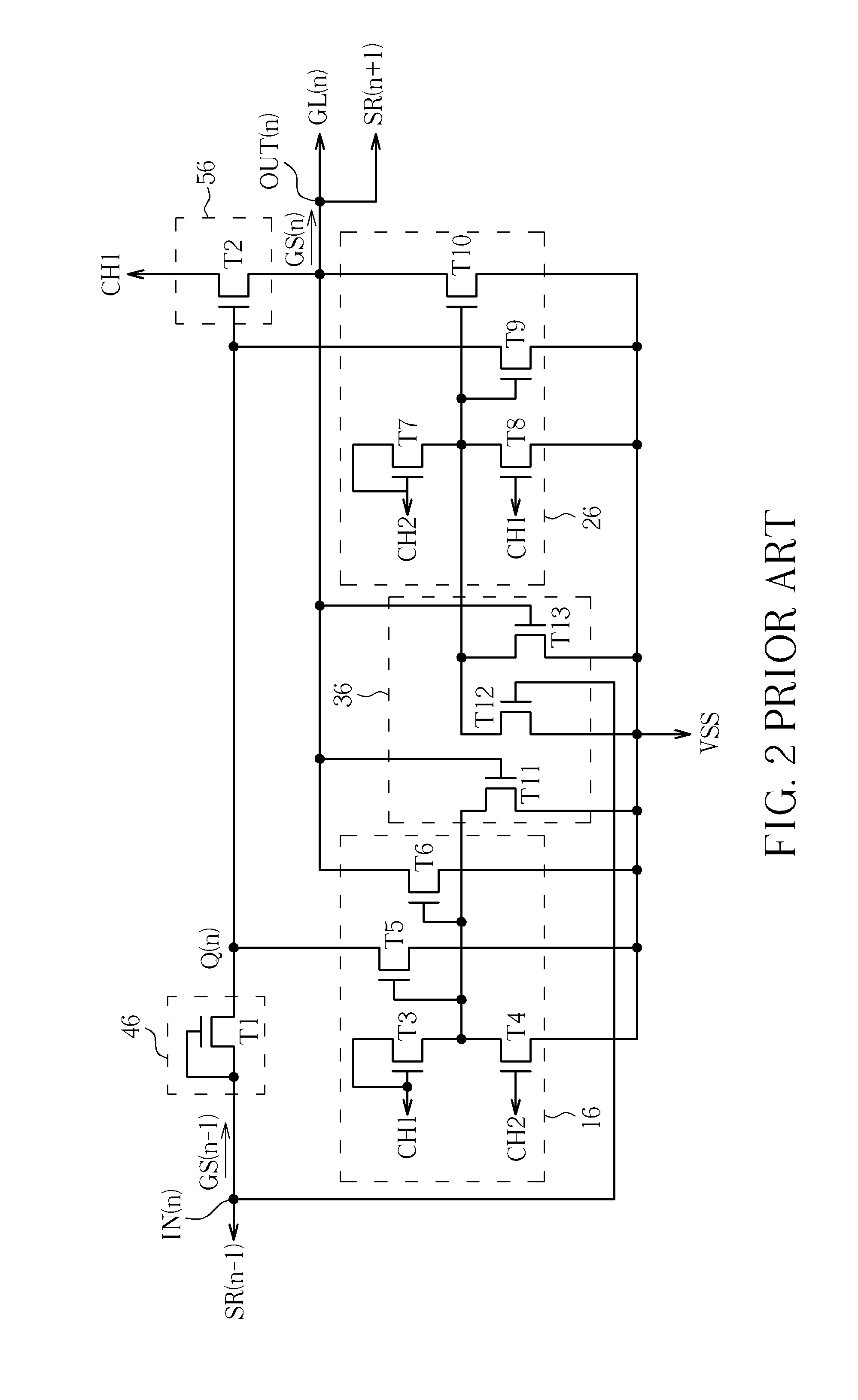

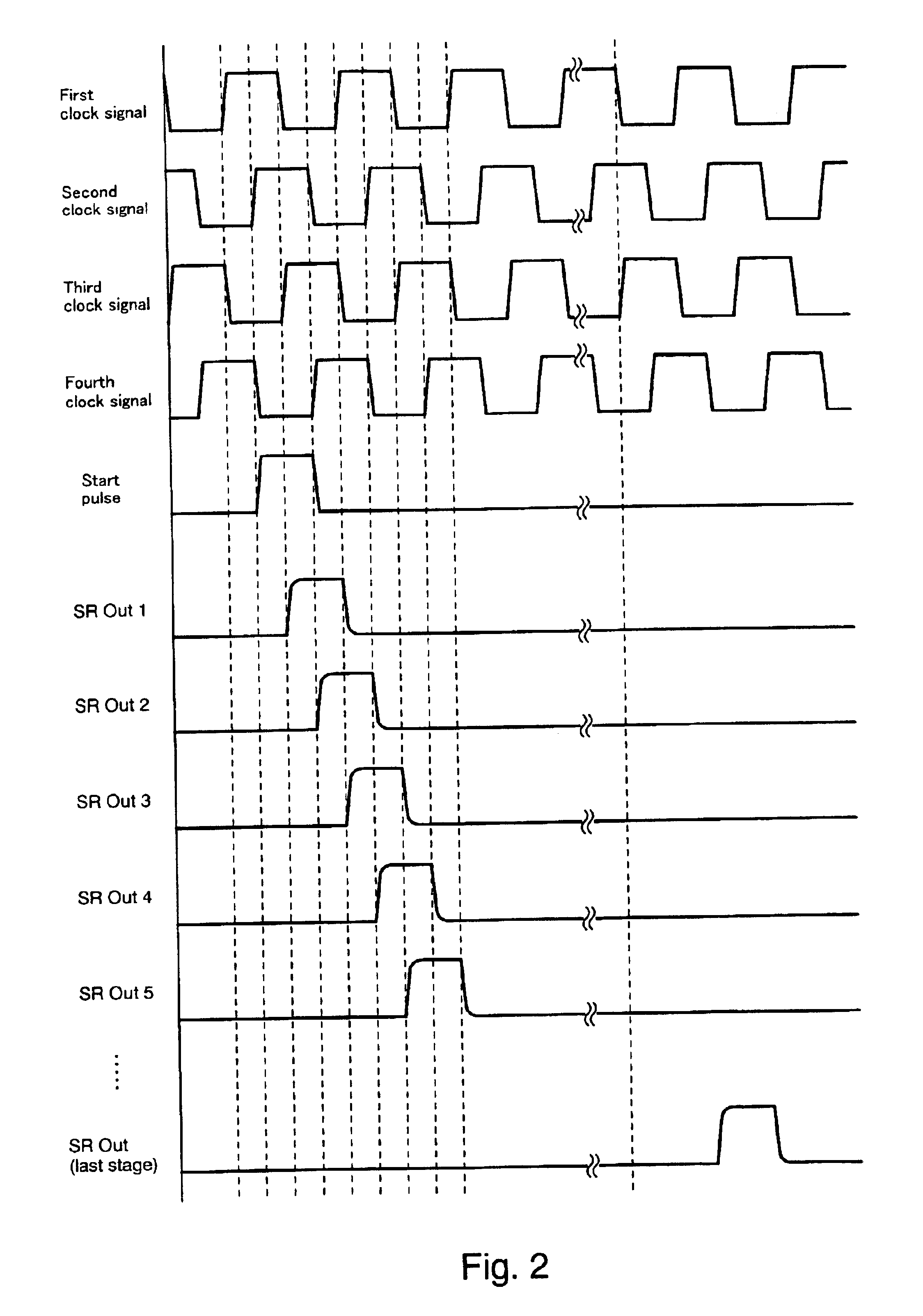

A shift register includes stages to generate gate signals in sequence. Each of the stages includes a first pull up drive control section, a pull up drive section and a pull down drive section. The first pull up drive control section outputs a control signal based on the gate signal of an adjacent stage. The pull up drive section receives a first clock signal and outputs the first clock signal as the gate signal to a corresponding gate line in response to the control signal. The pull down drive section inactivates the corresponding gate line in response to a second clock signal.

Owner:SAMSUNG DISPLAY CO LTD

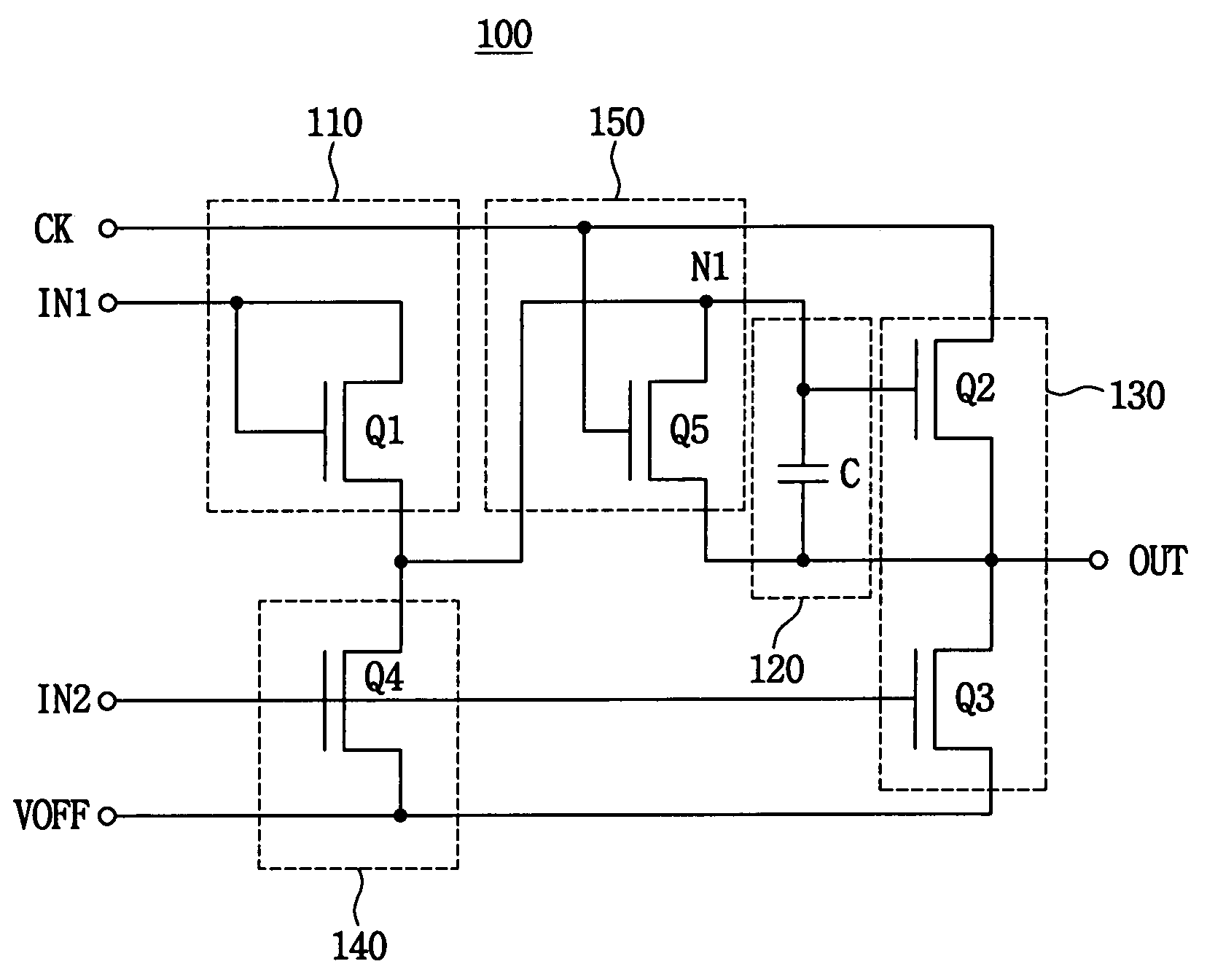

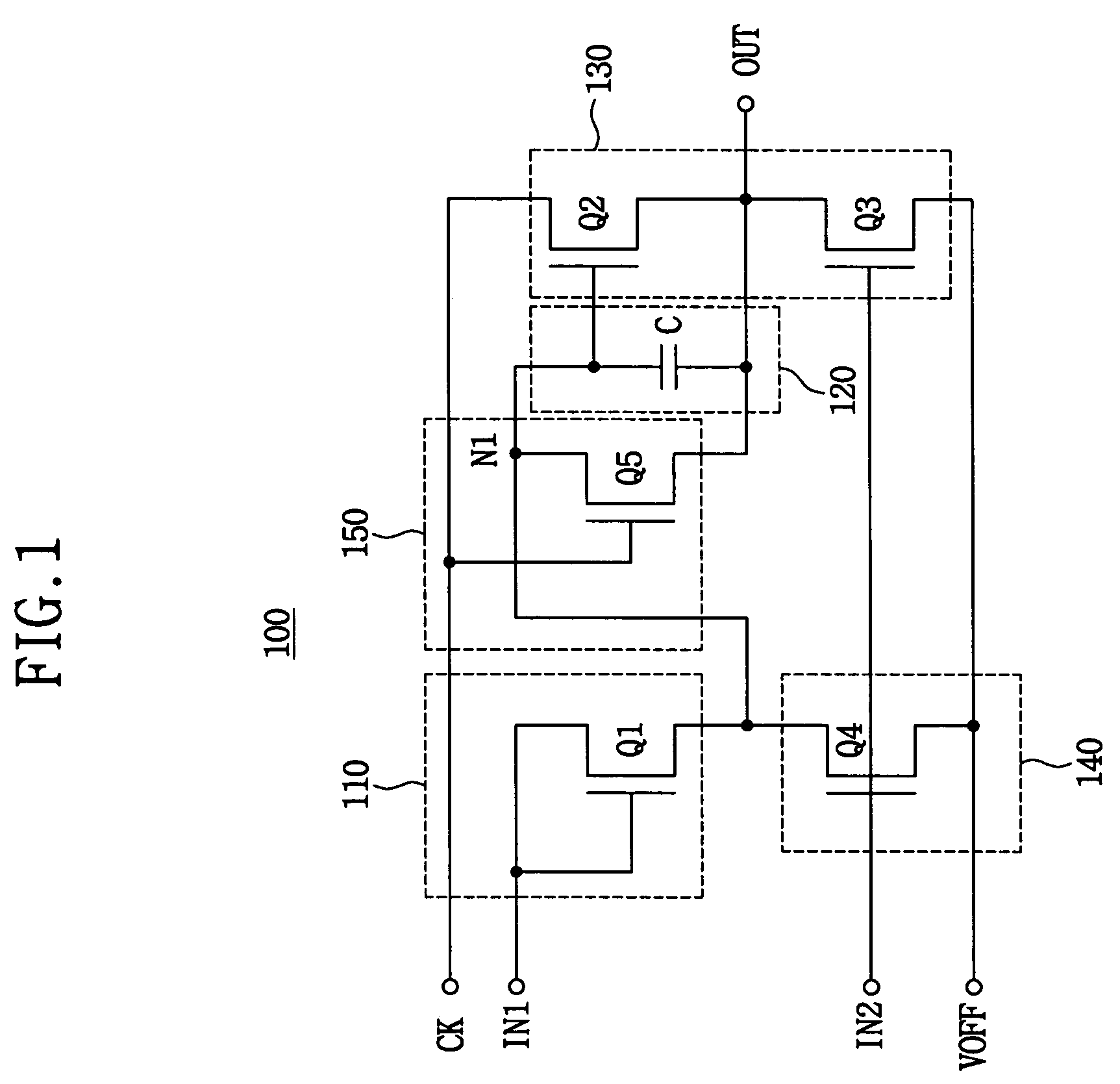

Shift register and image display apparatus containing the same

ActiveUS20080101529A1Increased circuit areaImprove driving reliabilityStatic indicating devicesDigital storagePower inverterShift register

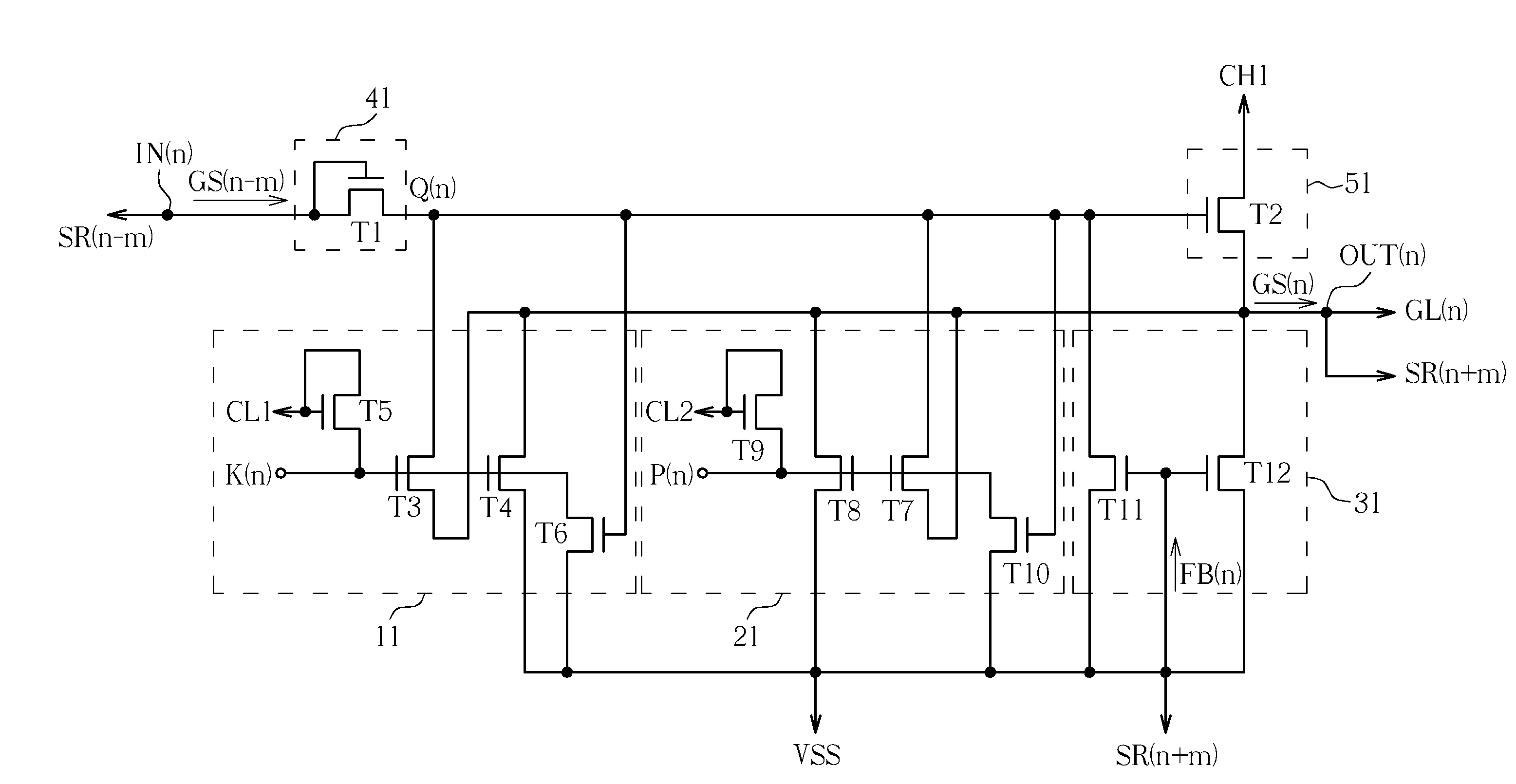

A shift register includes a first transistor supplying an output terminal with a clock signal input to a first clock terminal and a second transistor discharging the output terminal. Defining the gate node of the first transistor as a first node, and the gate node of the second transistor as a second node, the shift register includes an inverter circuit in which the first node serves as its input node and a capacitive element serves as a load, and a buffer circuit receiving the output from the inverter circuit and outputting a signal to the second node.

Owner:TRIVALE TECH

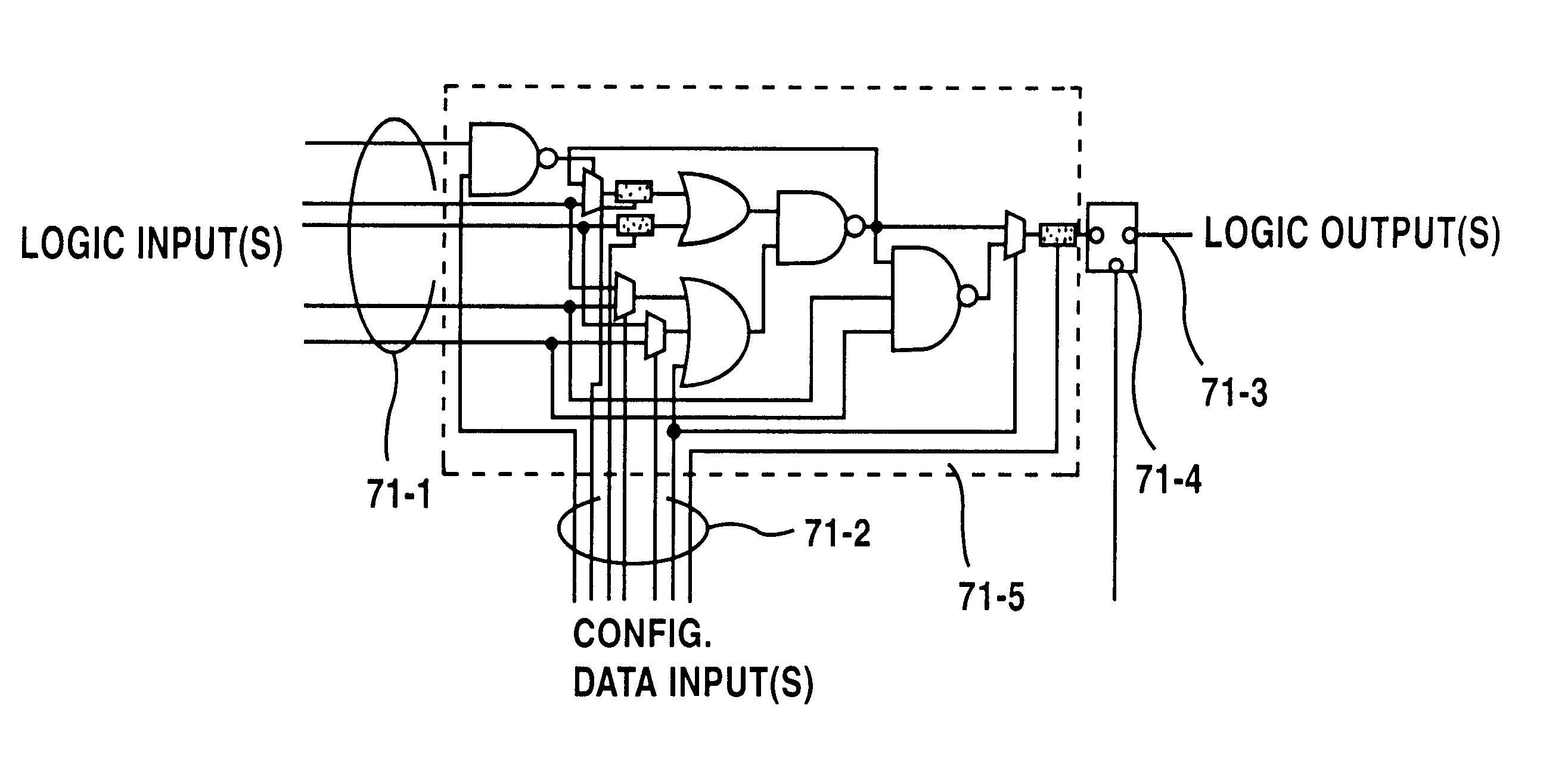

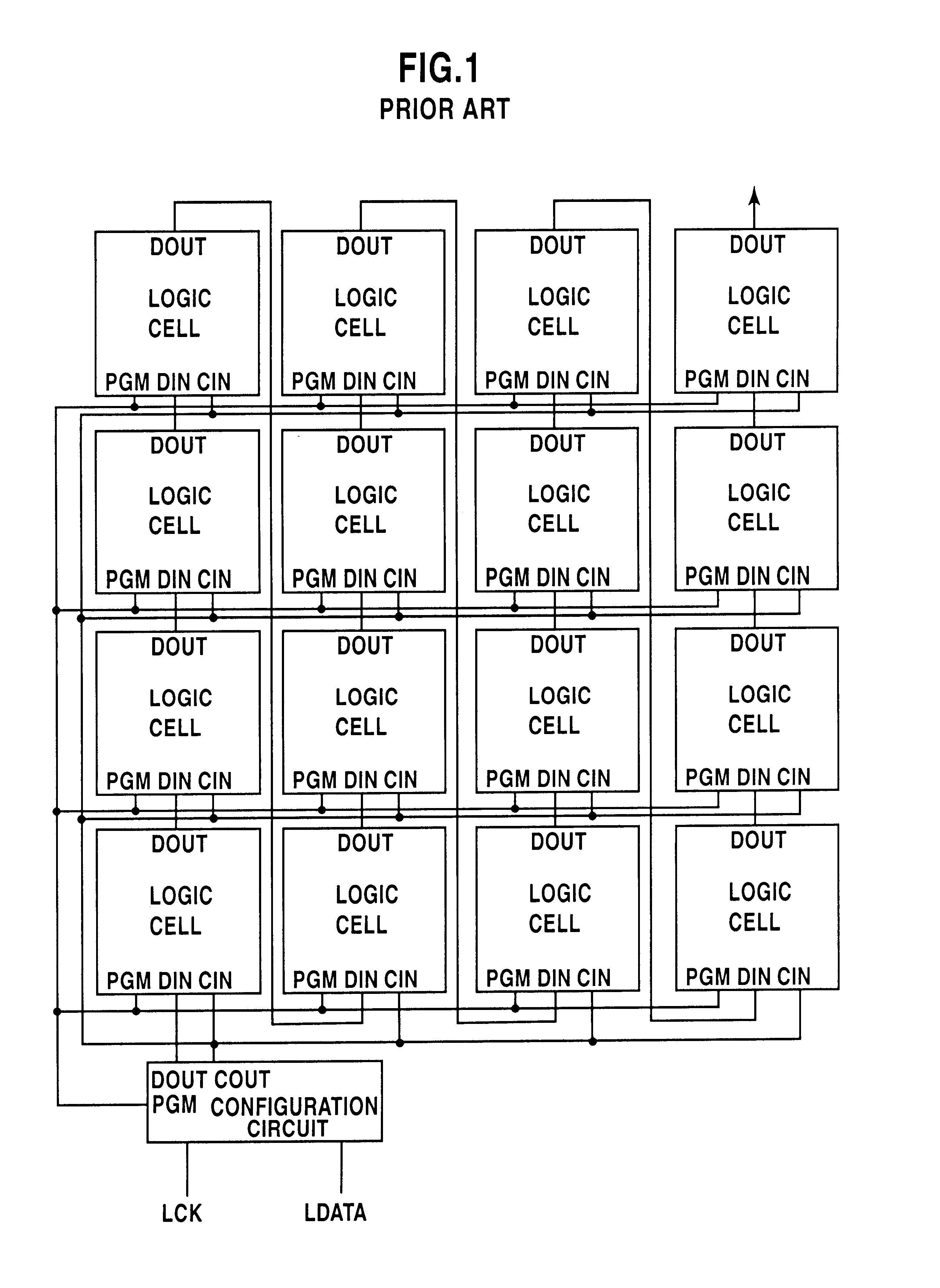

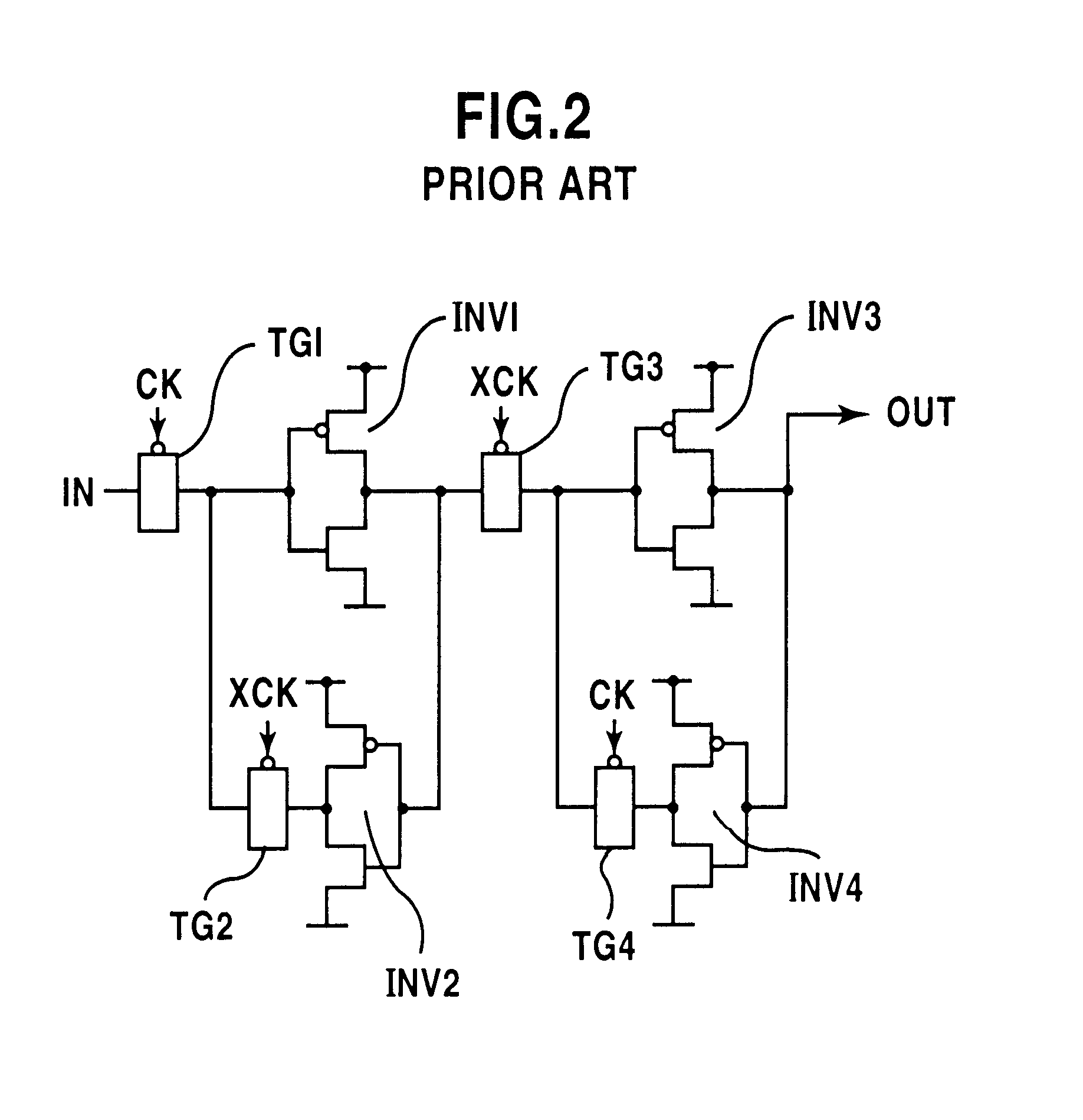

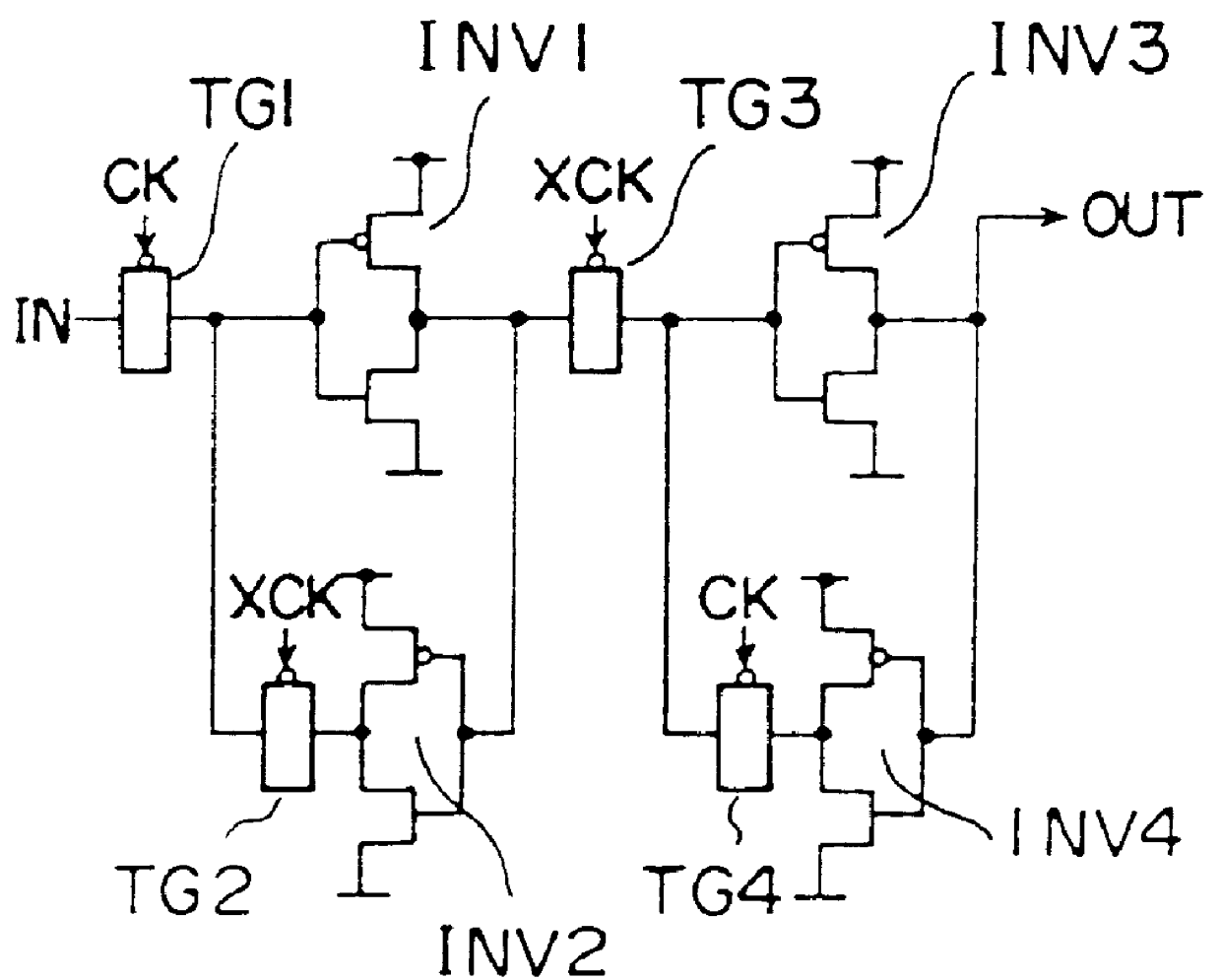

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

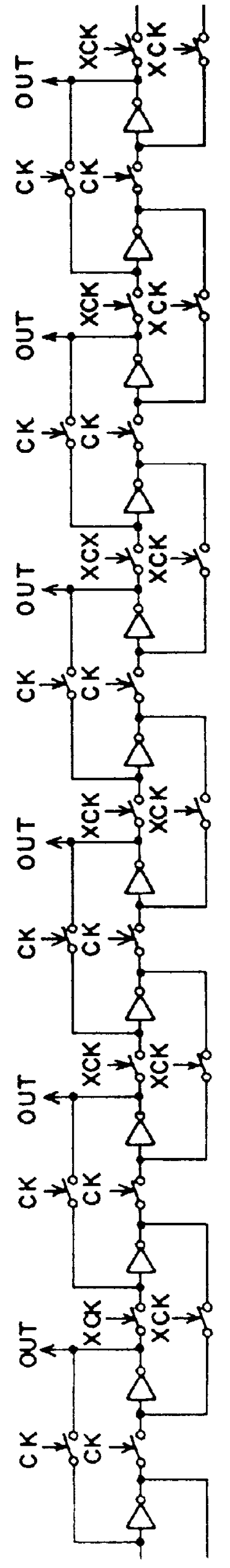

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

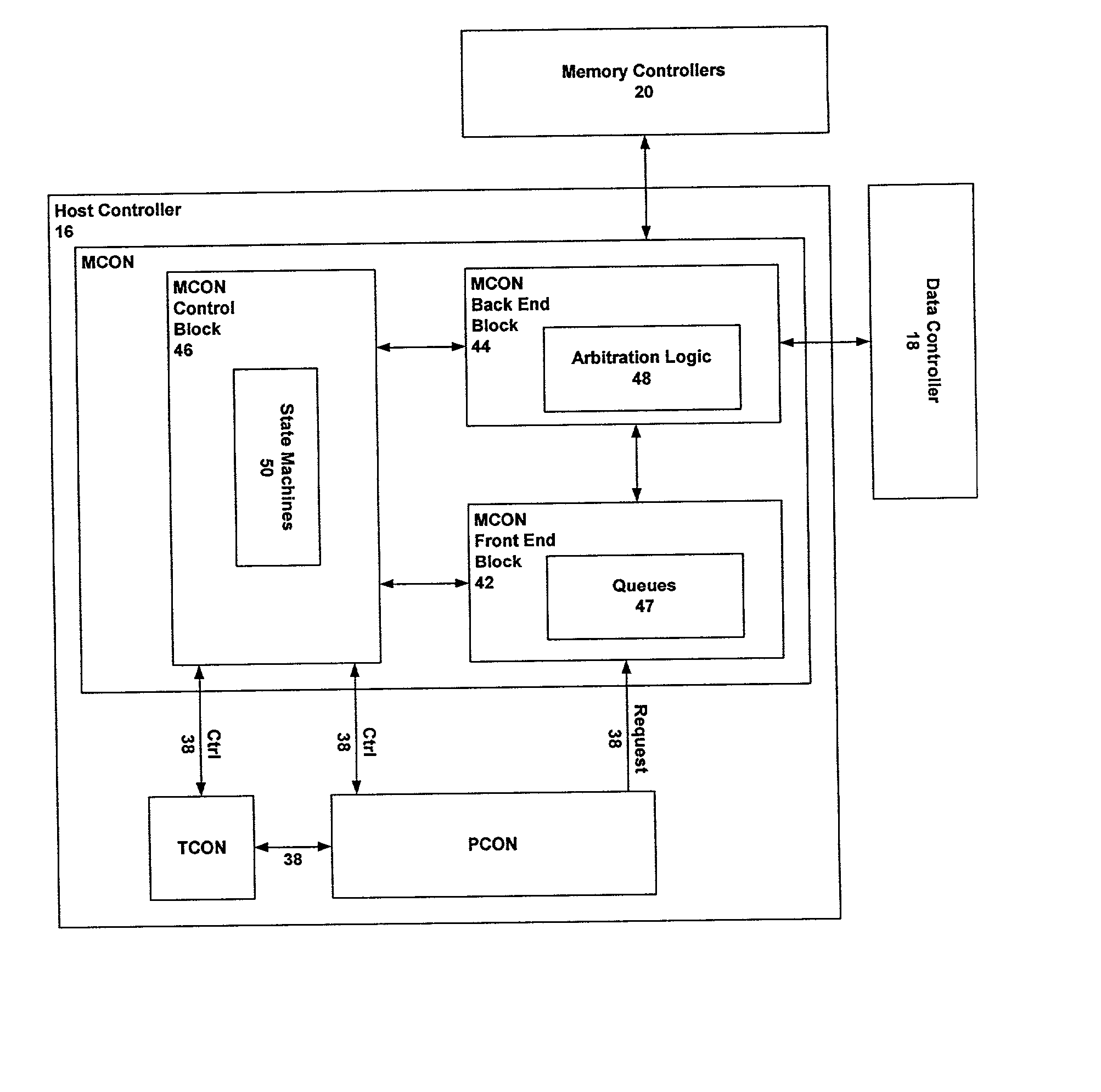

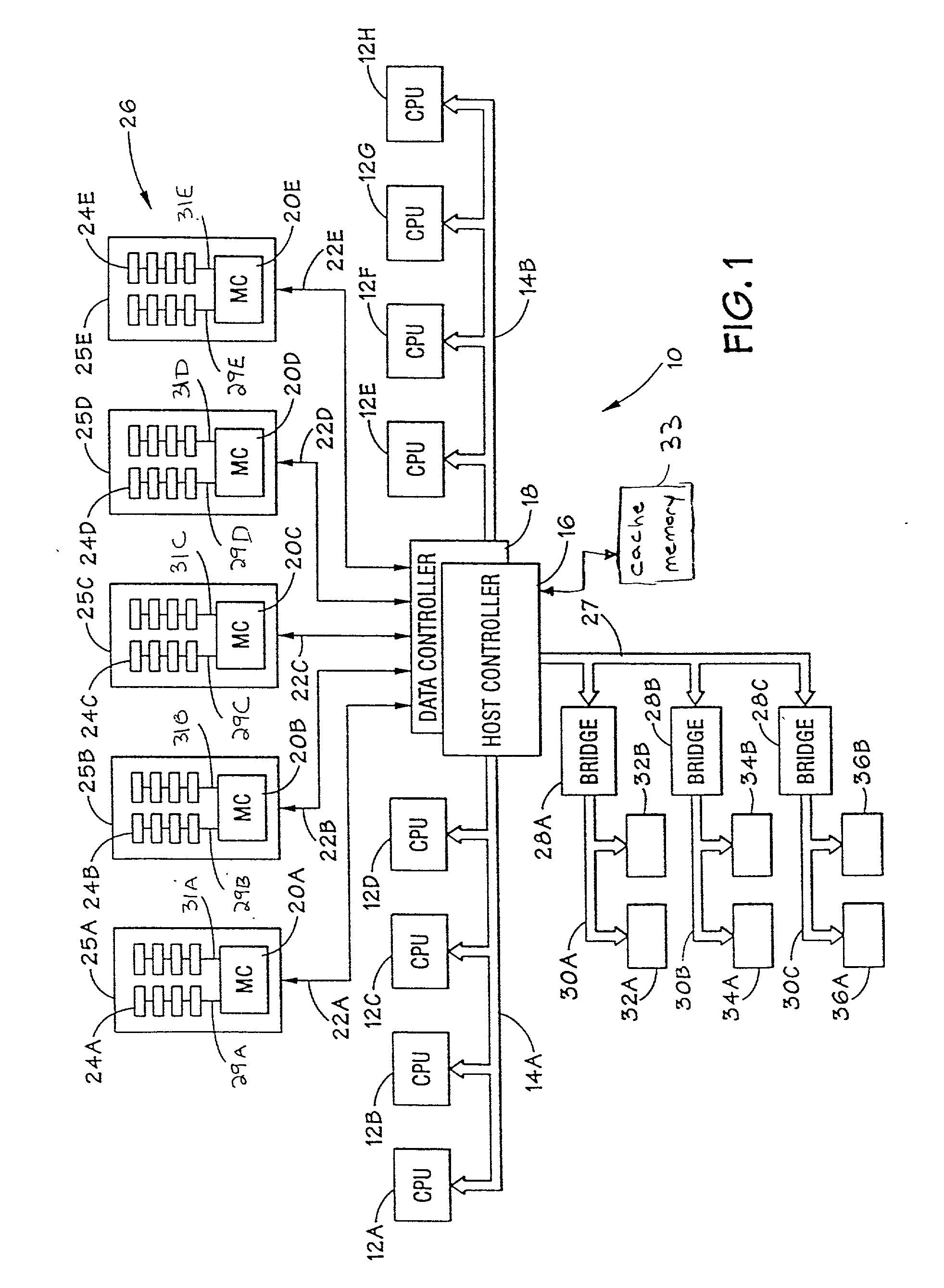

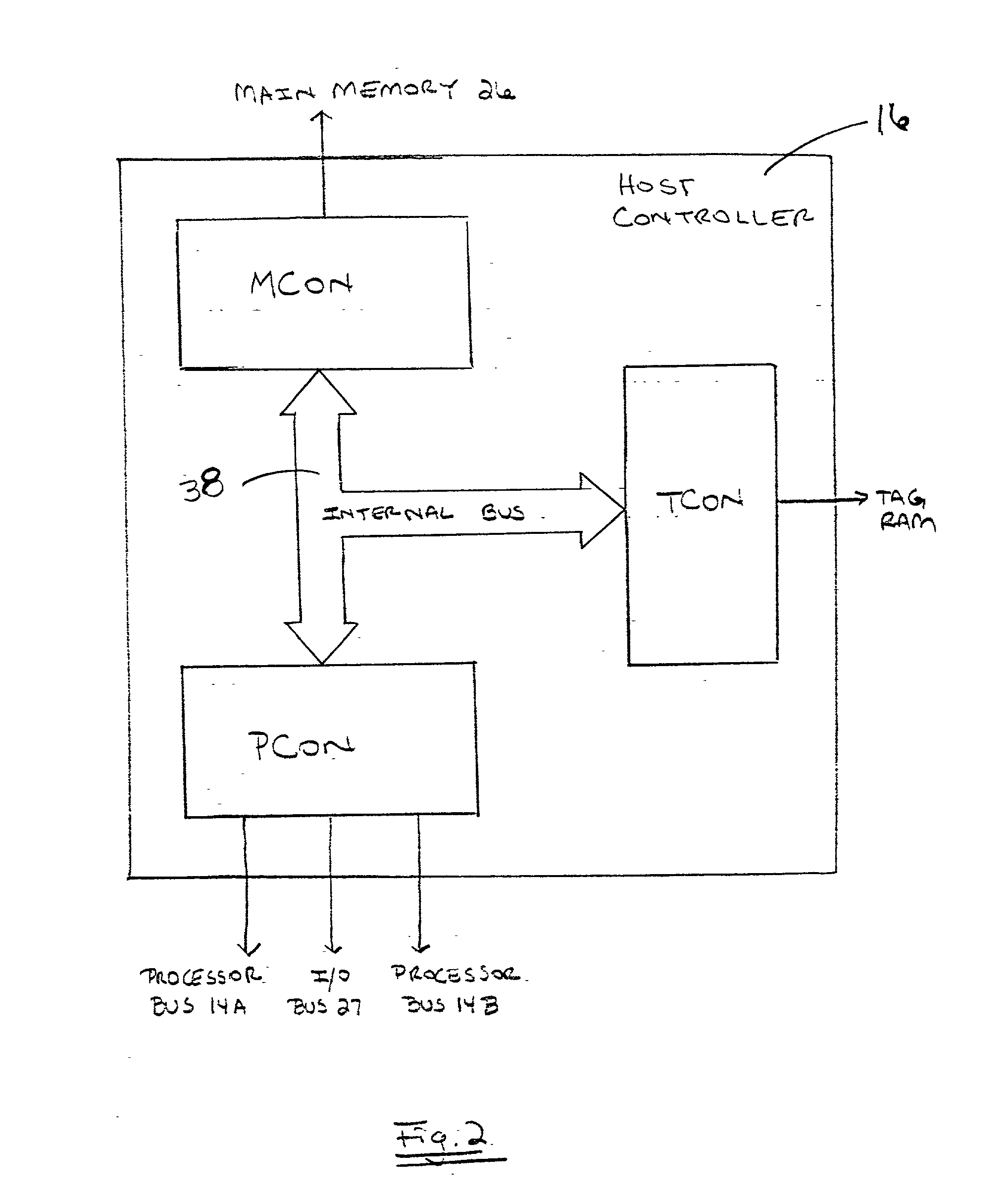

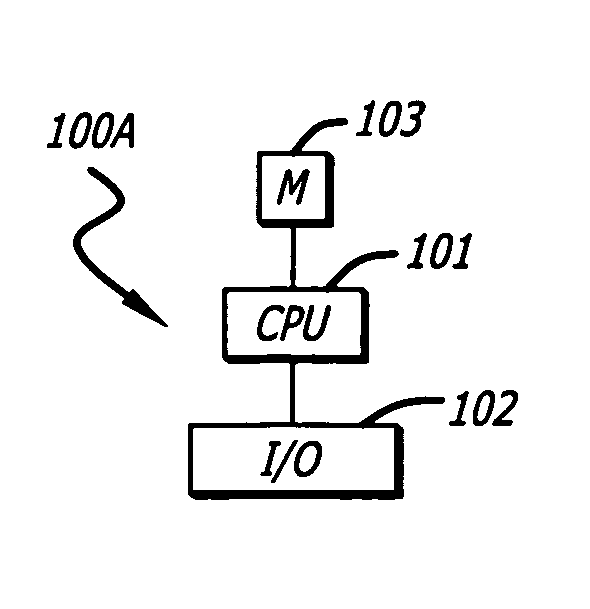

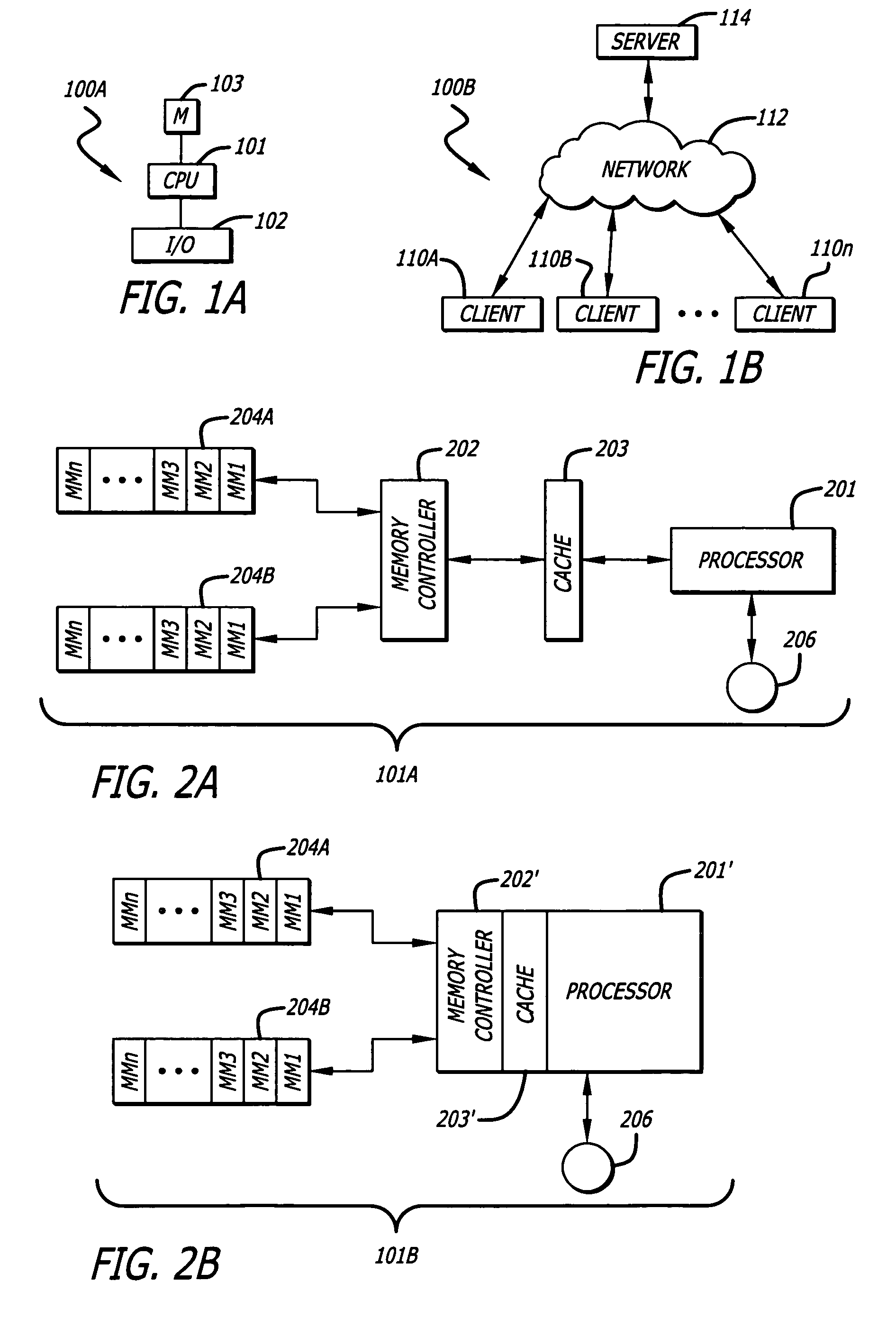

Techniques for processing out-of -order requests in a processor-based system

InactiveUS20030093630A1Memory systemsInput/output processes for data processingShift registerProcessor register

A mechanism for executing requests in a system. More specifically, a technique for processing requests to a memory system is provided. A shift register may be used to store an index associated with requests, such as read and write requests, to a memory system. Each request is stored in a respective queue depending on the source of the request and the request type (e.g. read or write). Each request includes flags which may be set to determine the processing order of the requests, such that out-of-order processing is feasible. An index corresponding to each of the requests is stored in an index shifter to facilitate the out-of-order processing of the requests. Alternatively, a shift register may be used to store each of the requests. Rather than shifting the indices to facilitate the out-of-order processing of requests, depending on the state of the corresponding request flags, the entire entry may be shifted.

Owner:VALTRUS INNOVATIONS LTD +1

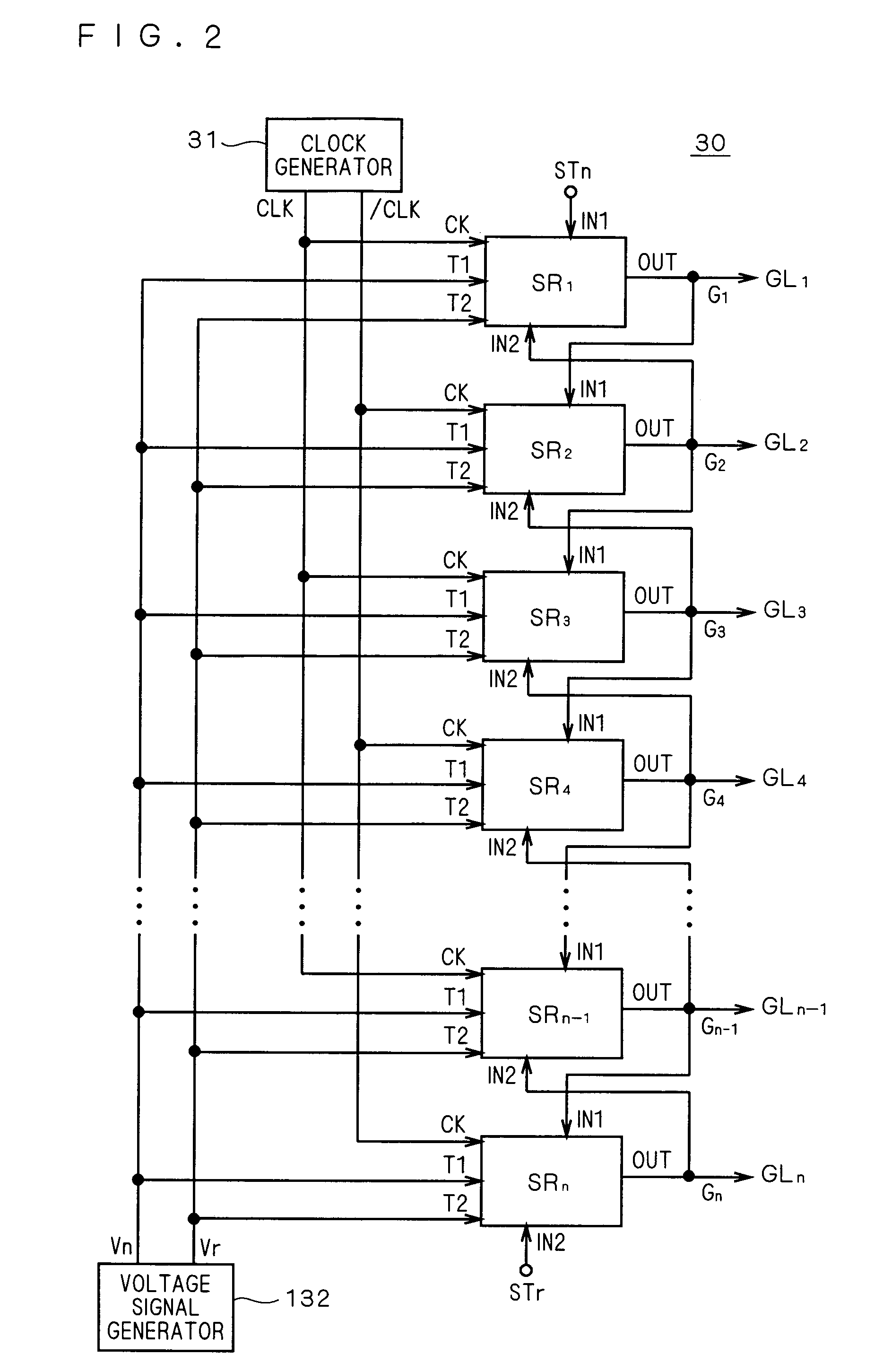

Shift register, liquid crystal display device having the shift register and method of driving scan lines using the same

In a bi-directional shift register and a liquid crystal display device having the bi-directional shift register, the shift register further includes a dummy stage for resetting a last stage. The dummy stage is reset by a control signal of the last stage or by the output signal of the dummy stage. Therefore, power consumption and layout area may be reduced. The shift register includes a plurality of stages and two dummy stages, and two selection signals for selecting shift direction is applied to each of the stages.

Owner:HEWLETT PACKARD DEV CO LP +1

Shift register circuit and image display apparatus equipped with the same

InactiveUS20070274433A1Suppress failureIncrease computing speedStatic indicating devicesDigital storageShift registerElectricity

Malfunction caused by leakage current of the transistor and shift in threshold voltage is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a first transistor Q1 for providing a first clock signal CLK to an output terminal OUT, a second transistor Q2 for discharging the output terminal OUT based on a second clock signal, third and fourth transistors Q3, Q4 for providing first and second voltage signals Vn, Vr complementary to each other to a first node, which is a gate node of the first transistor Q1, and a fifth transistor Q5 connected between the first node and the output terminal OUT. The fifth transistor Q5 is in an electrically conducted state based on the first clock signal CLK when the gate of the transistor Q1 is at L (Low) level.

Owner:MITSUBISHI ELECTRIC CORP

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages cascade-connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage Vona larger than the power voltage Von applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

Owner:SAMSUNG DISPLAY CO LTD

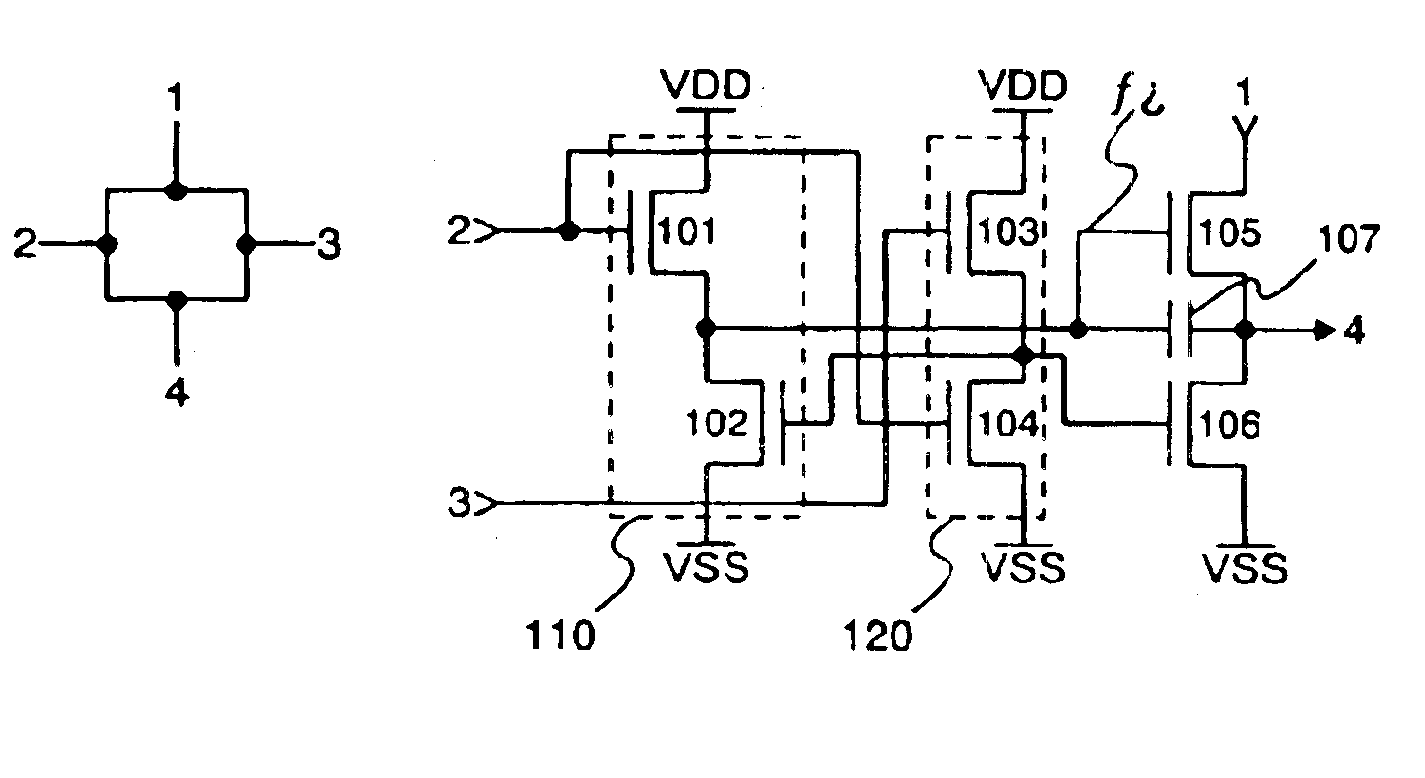

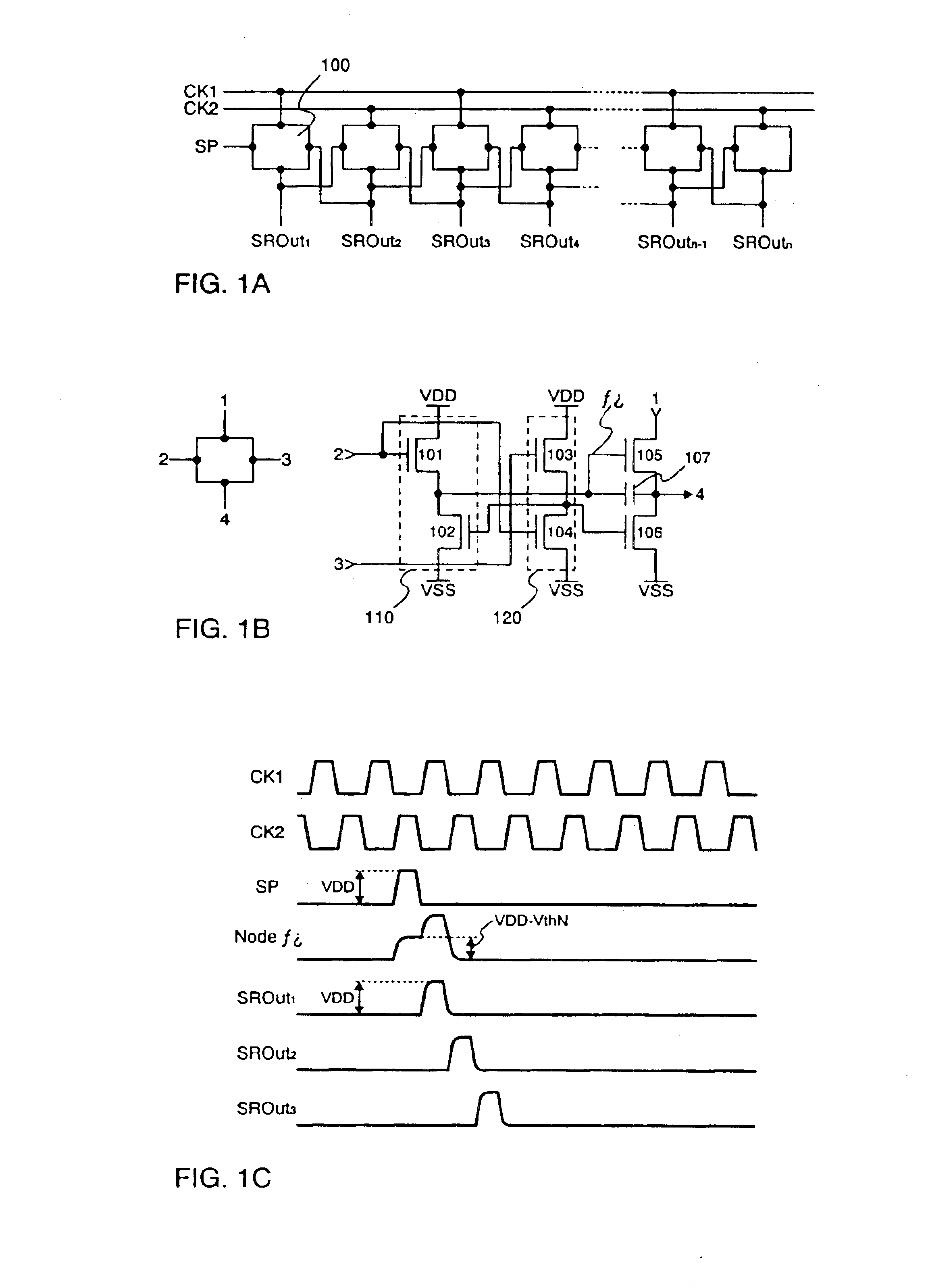

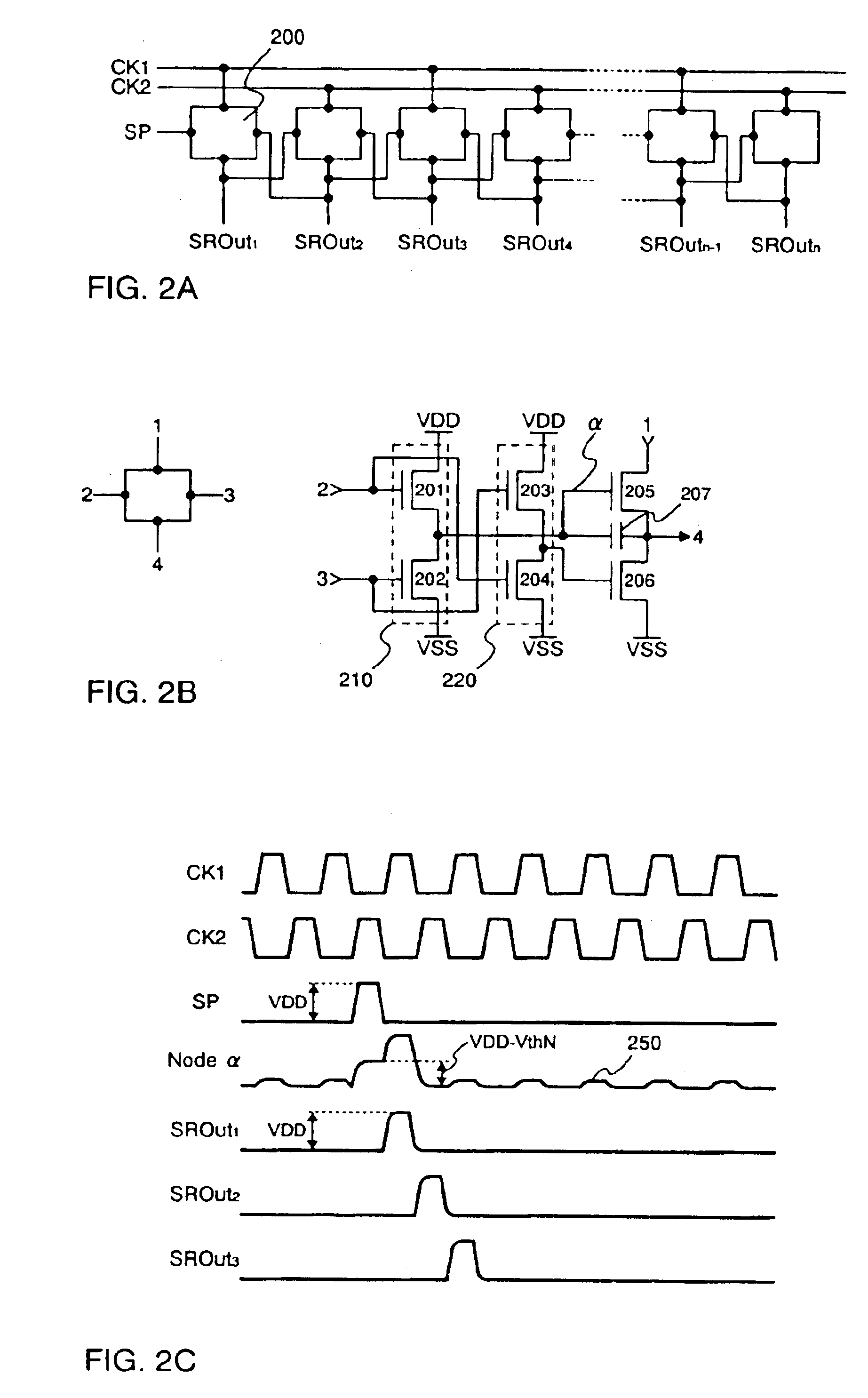

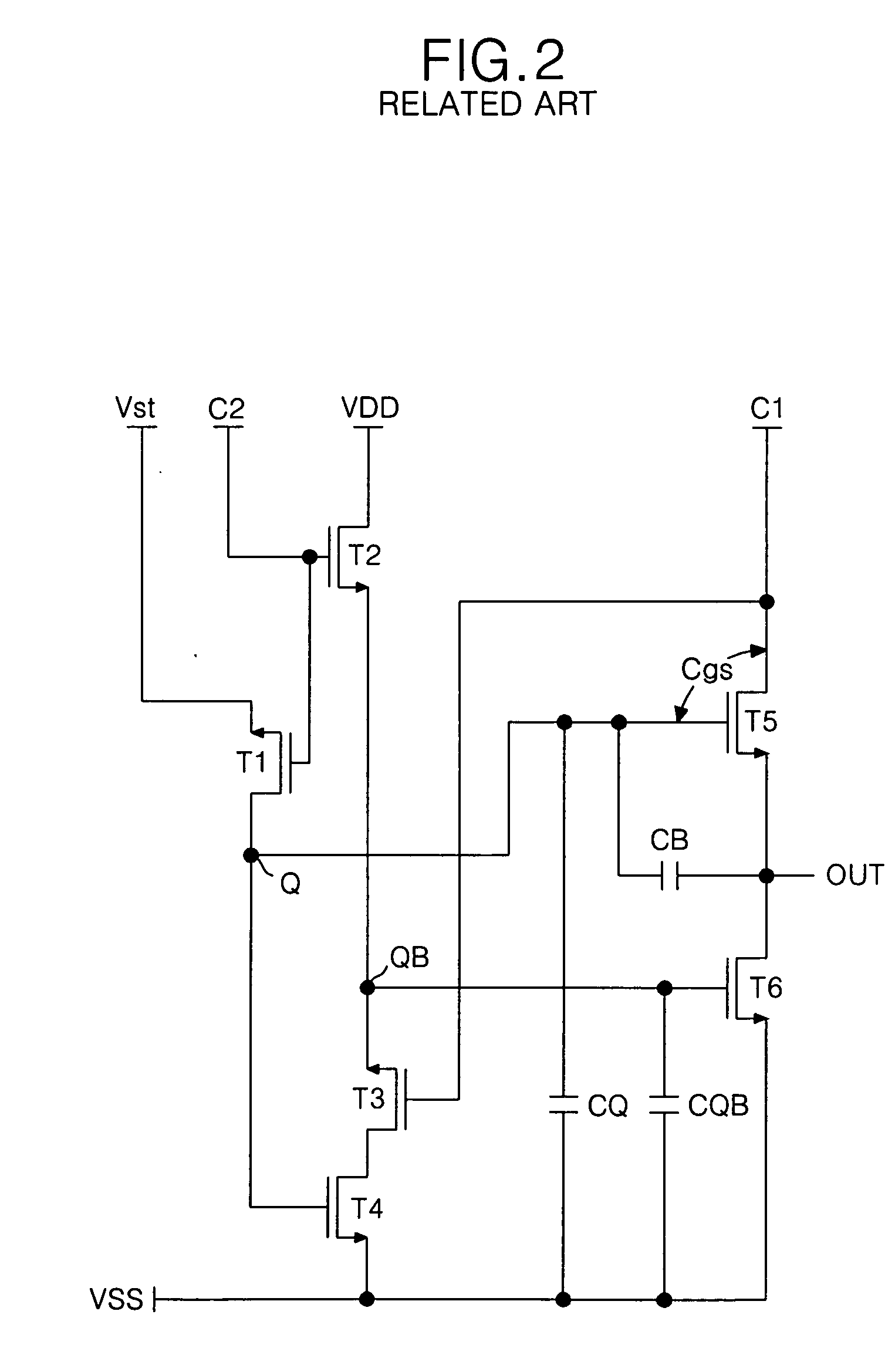

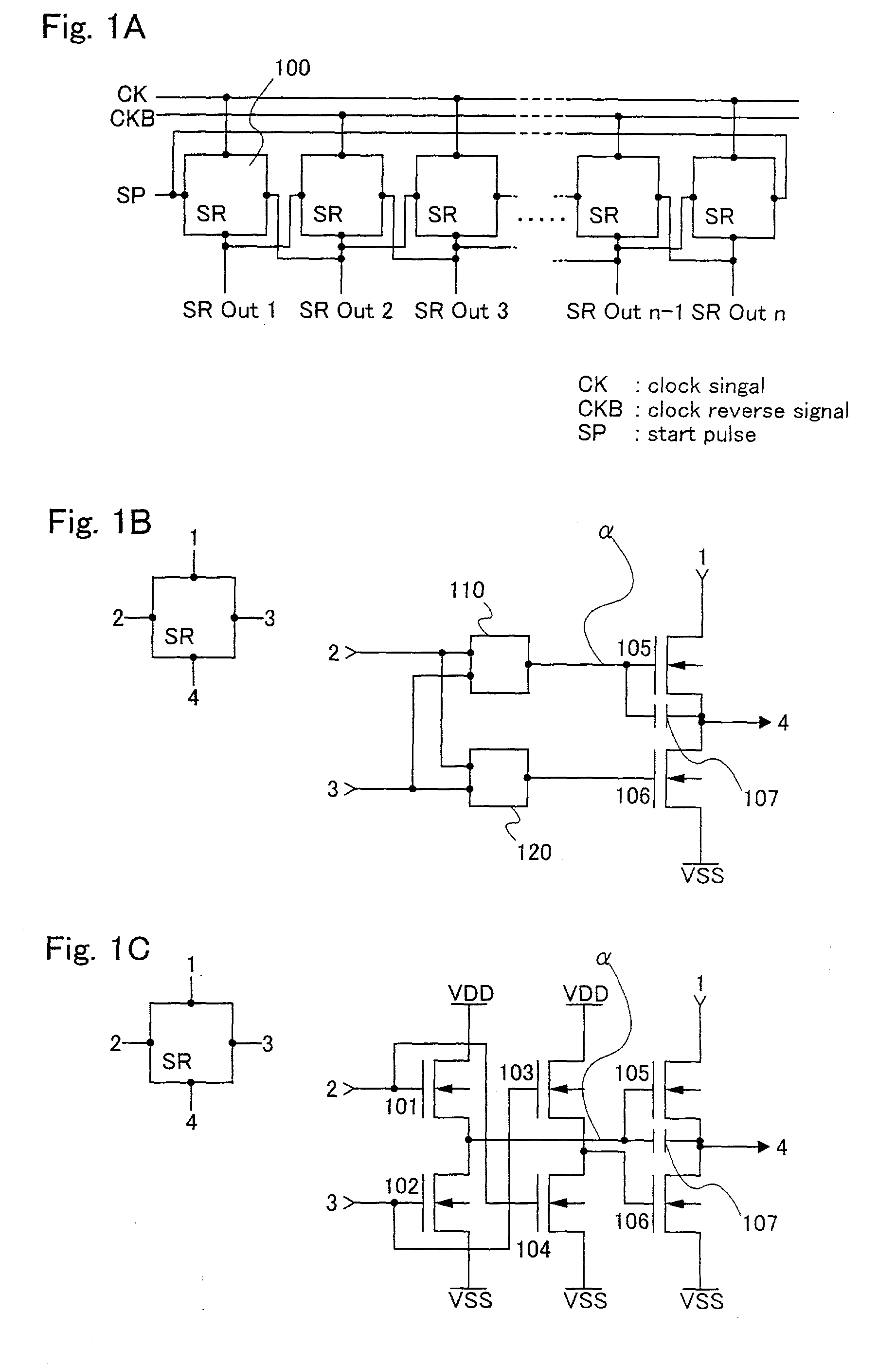

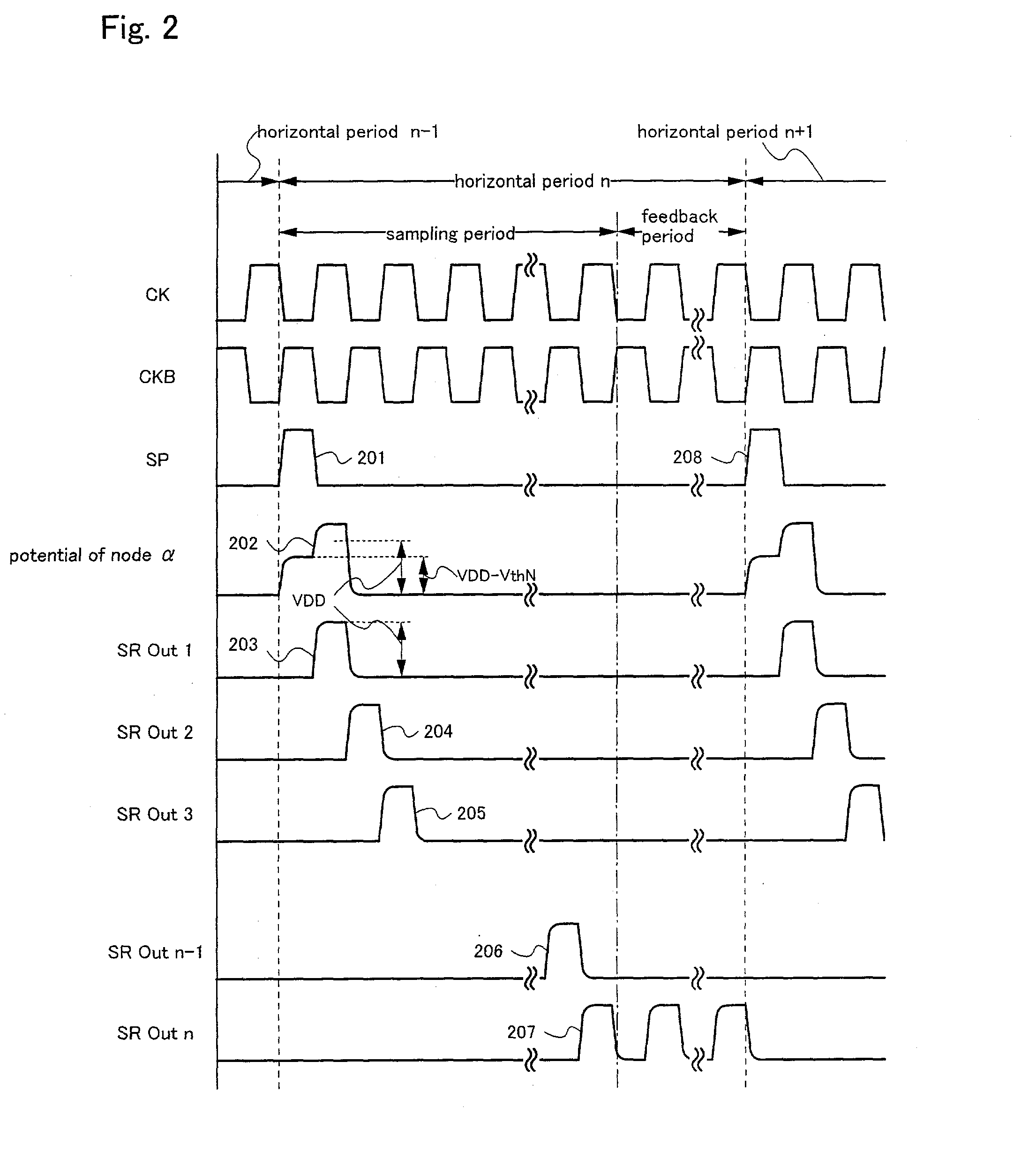

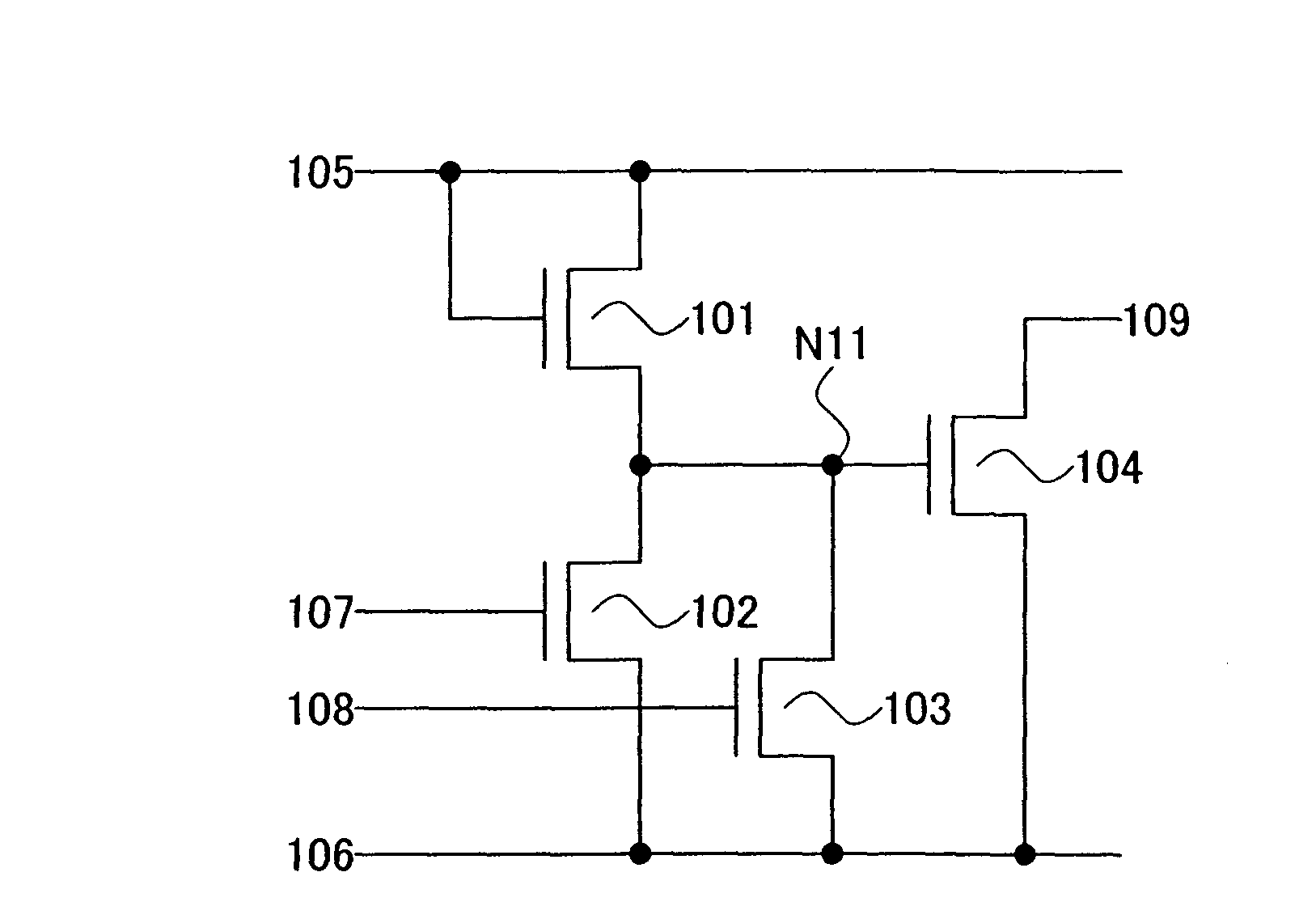

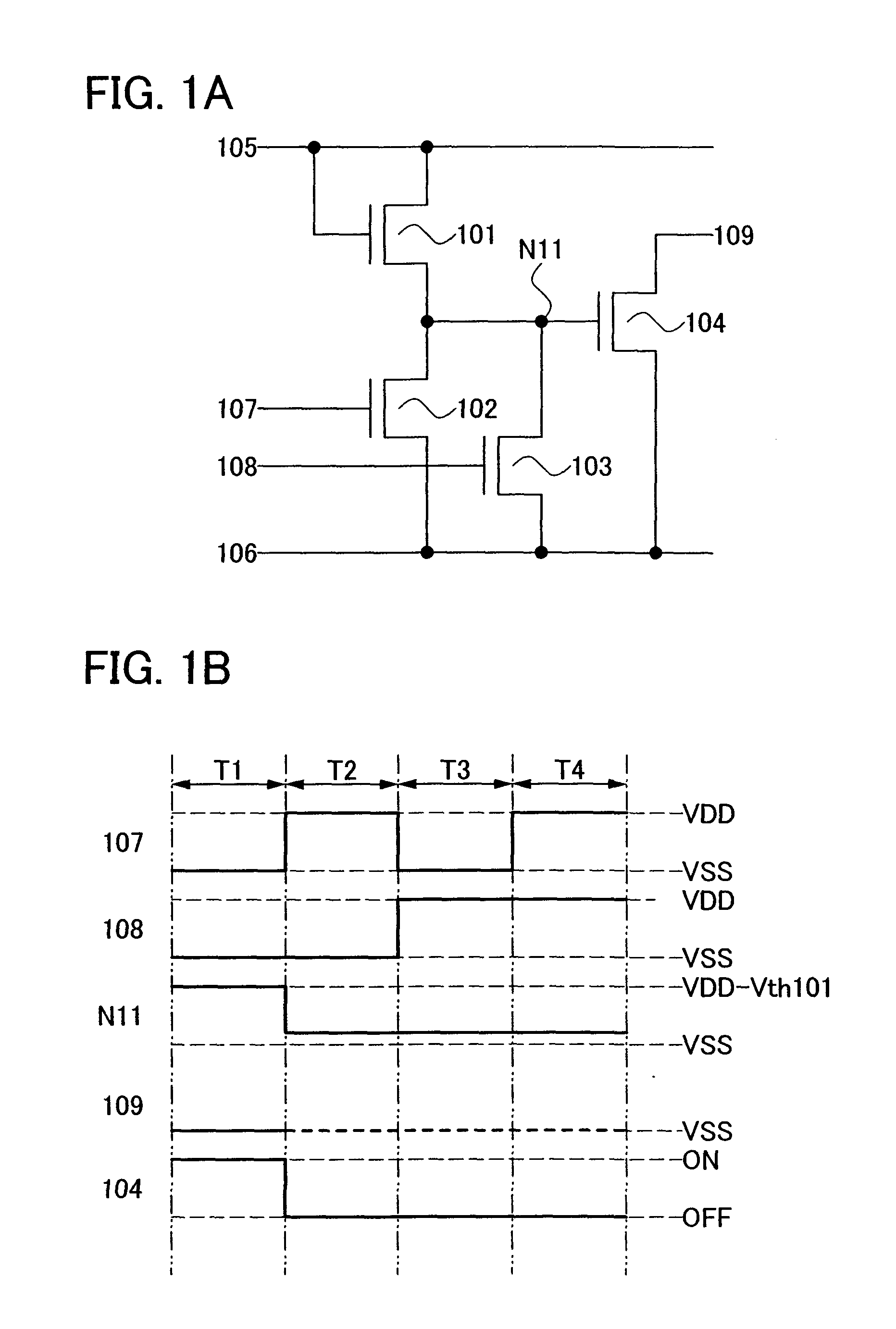

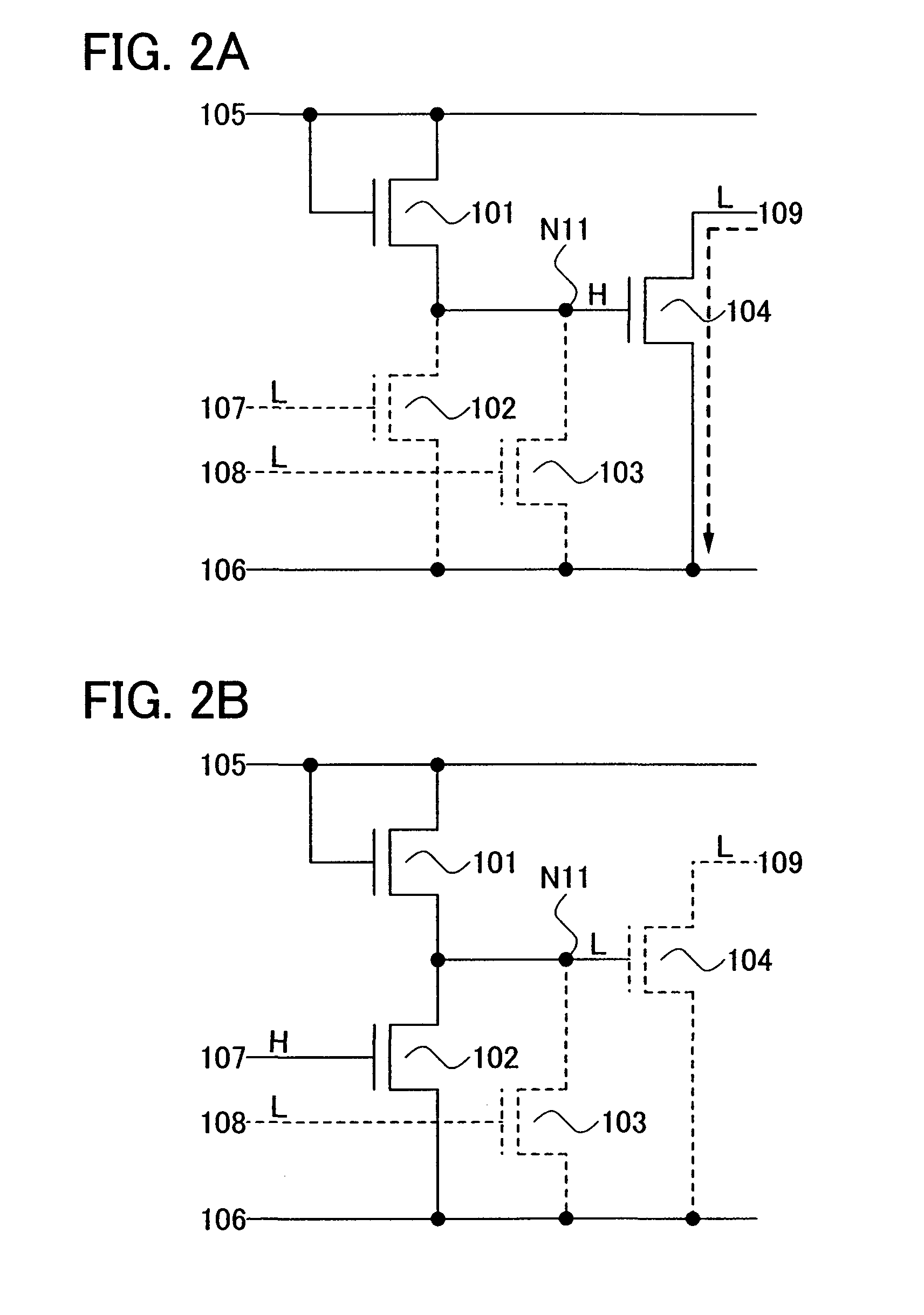

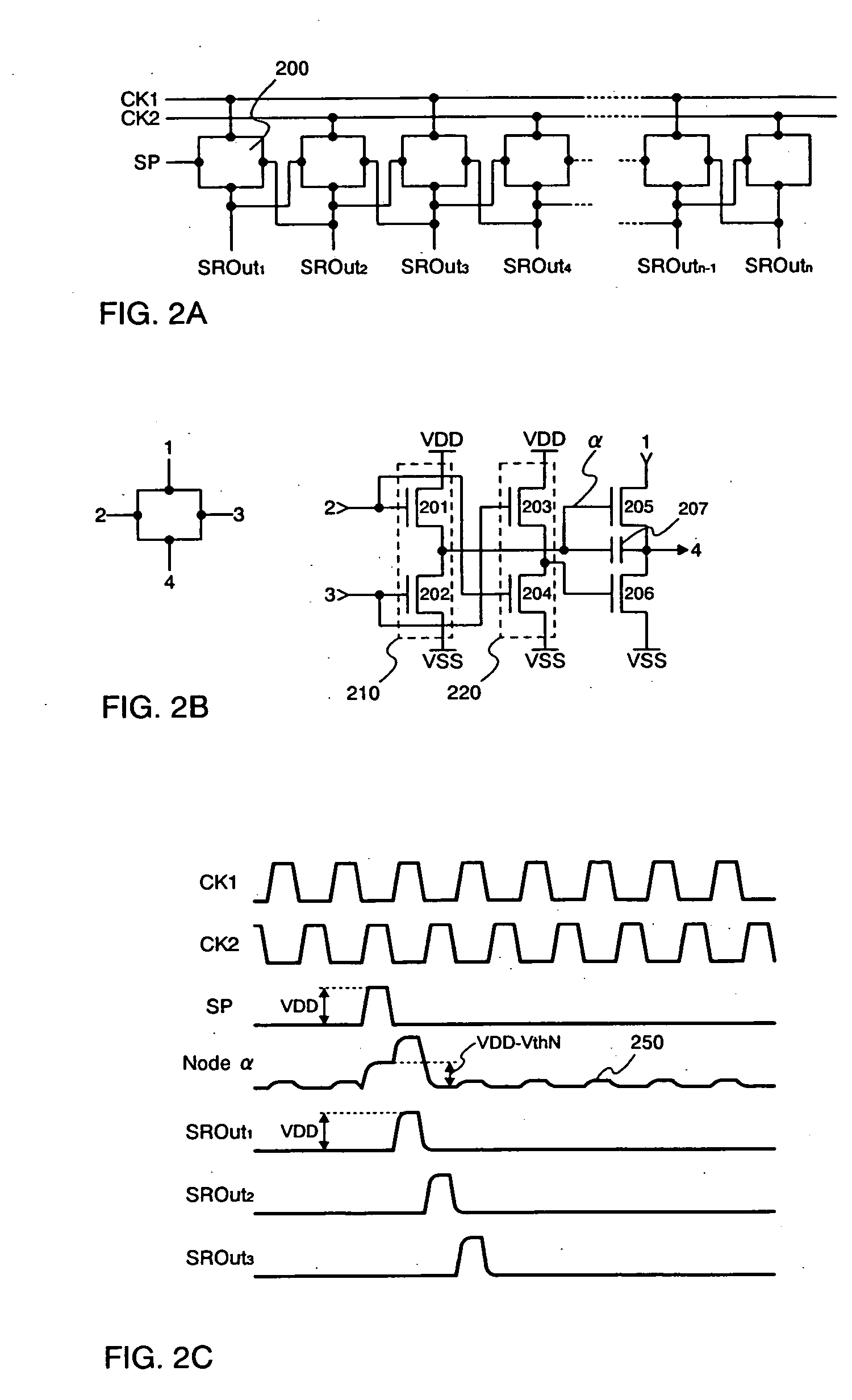

Pulse output circuit, shift register and electronic equipment

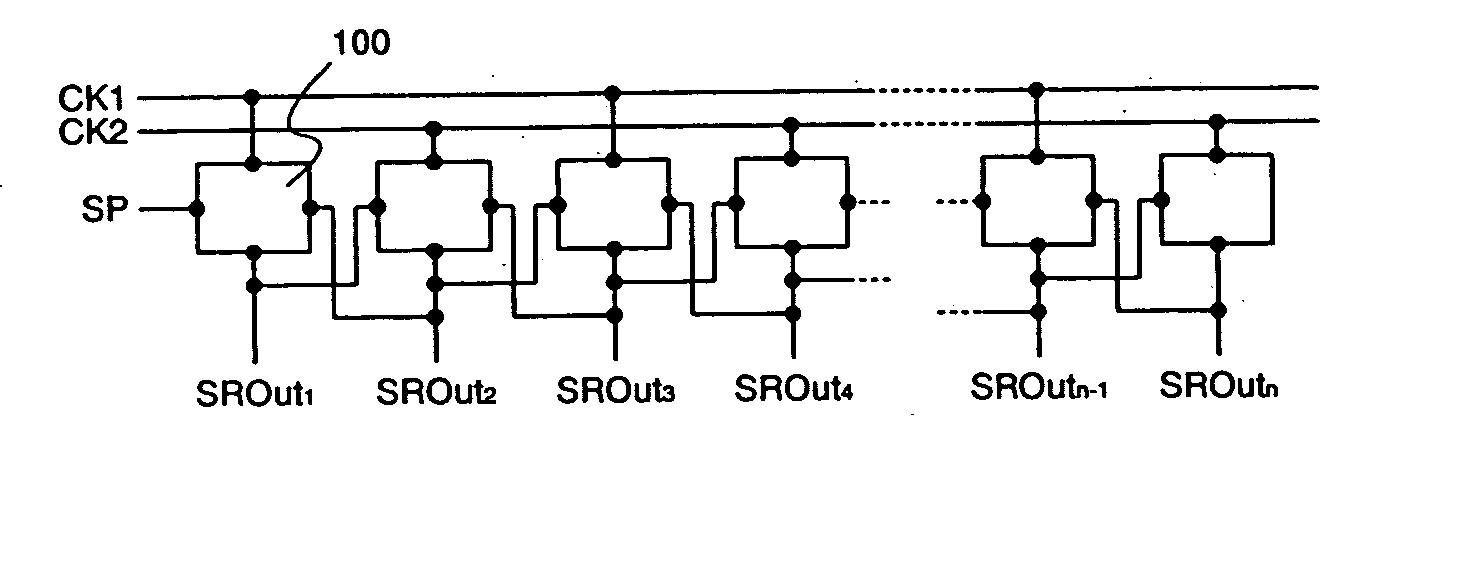

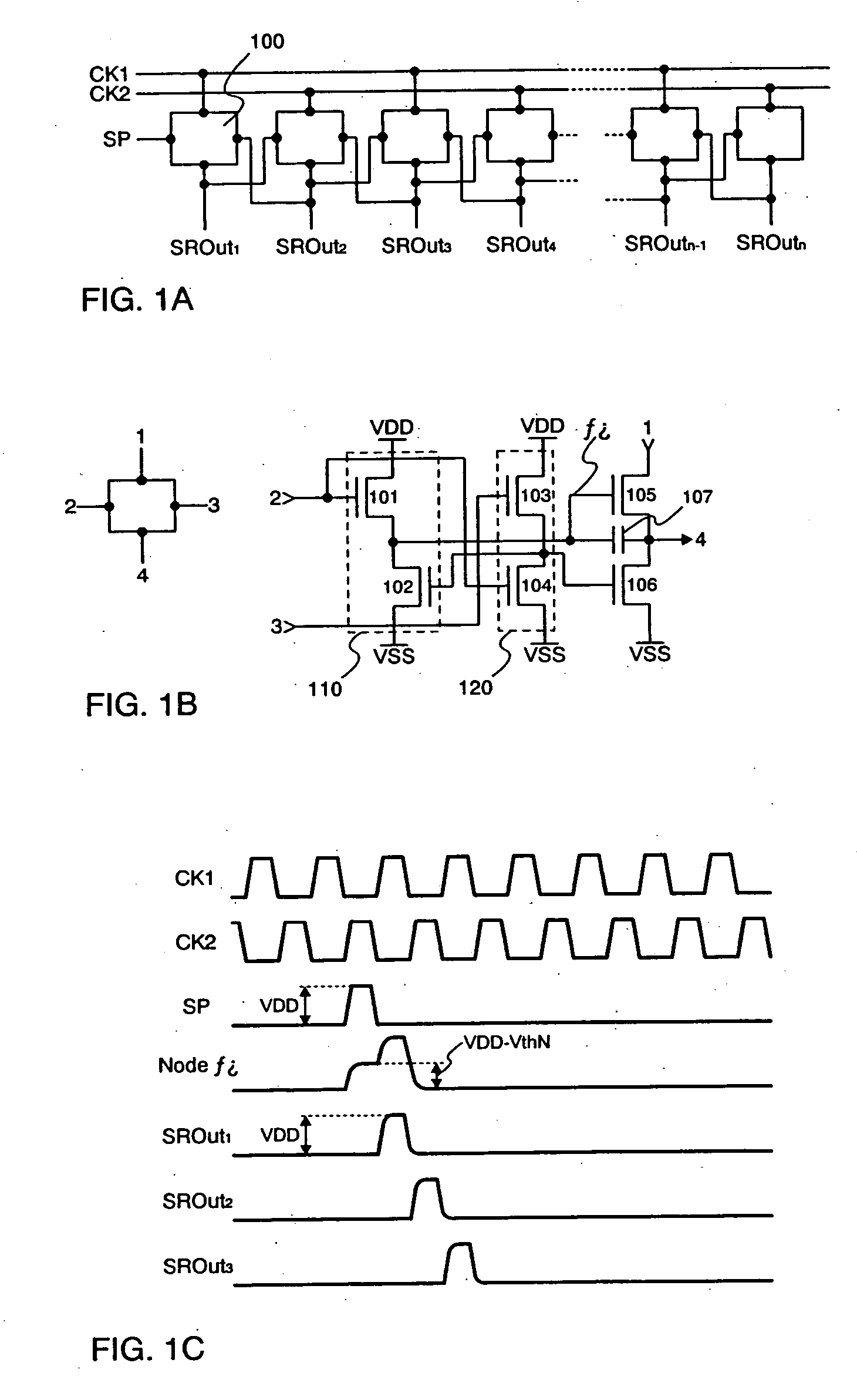

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

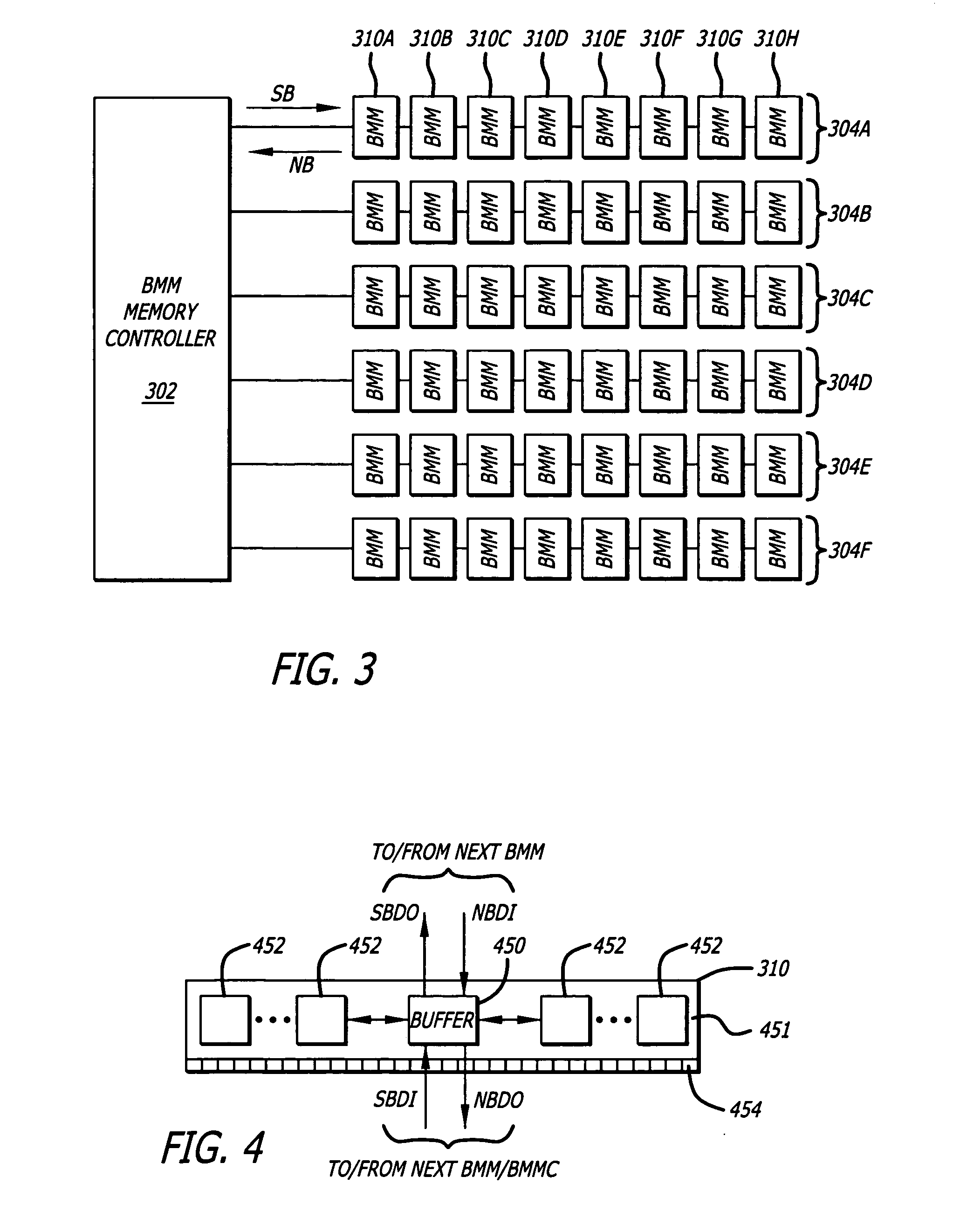

Memory buffers for merging local data from memory modules

InactiveUS20060195631A1Input/output for user-computer interactionDigital data processing detailsShift registerMultiplexing

An integrated circuit to serialize local data and selectively merge it with serialized feed-through data into a serial data stream output that includes a parallel-in-serial-out (PISO) shift register, a multiplexer, and a transmitter. The PISO shift register serializes parallel data on a local data bus into serialized local data. The multiplexer selectively merges serialized local data and feed-through data into a serial data stream. The transmitter drives the serial data stream onto a serial data link. In another embodiment of the invention, a method for a memory module includes receiving an input serial data stream; merging local frames of data and feed-through frames of data together into an output serial data stream in response to a merge enable signal; and transmitting the output serial data stream on a northbound data output to a next memory module or a memory controller. Other embodiments of the invention are disclosed and claimed.

Owner:INTEL CORP

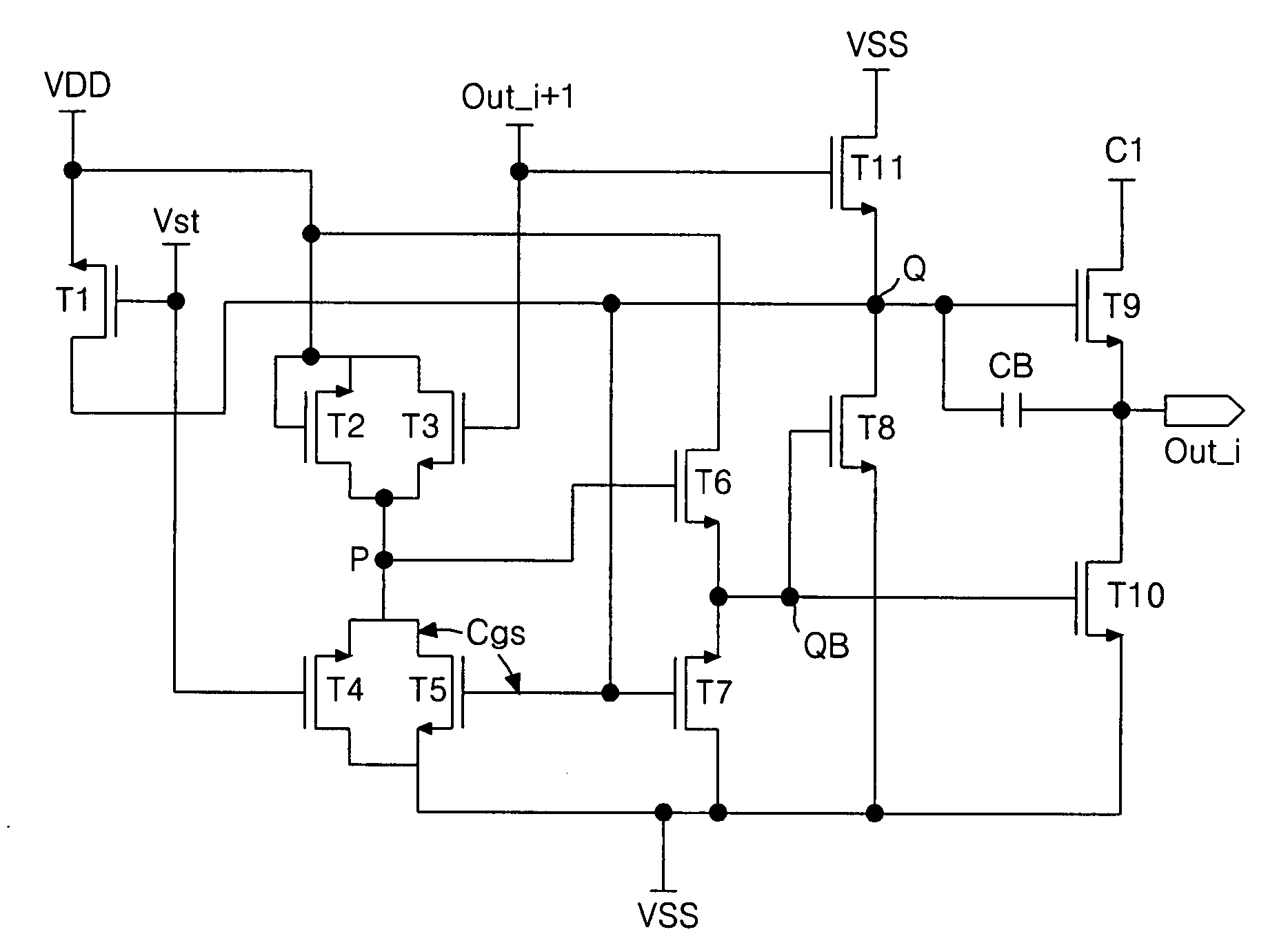

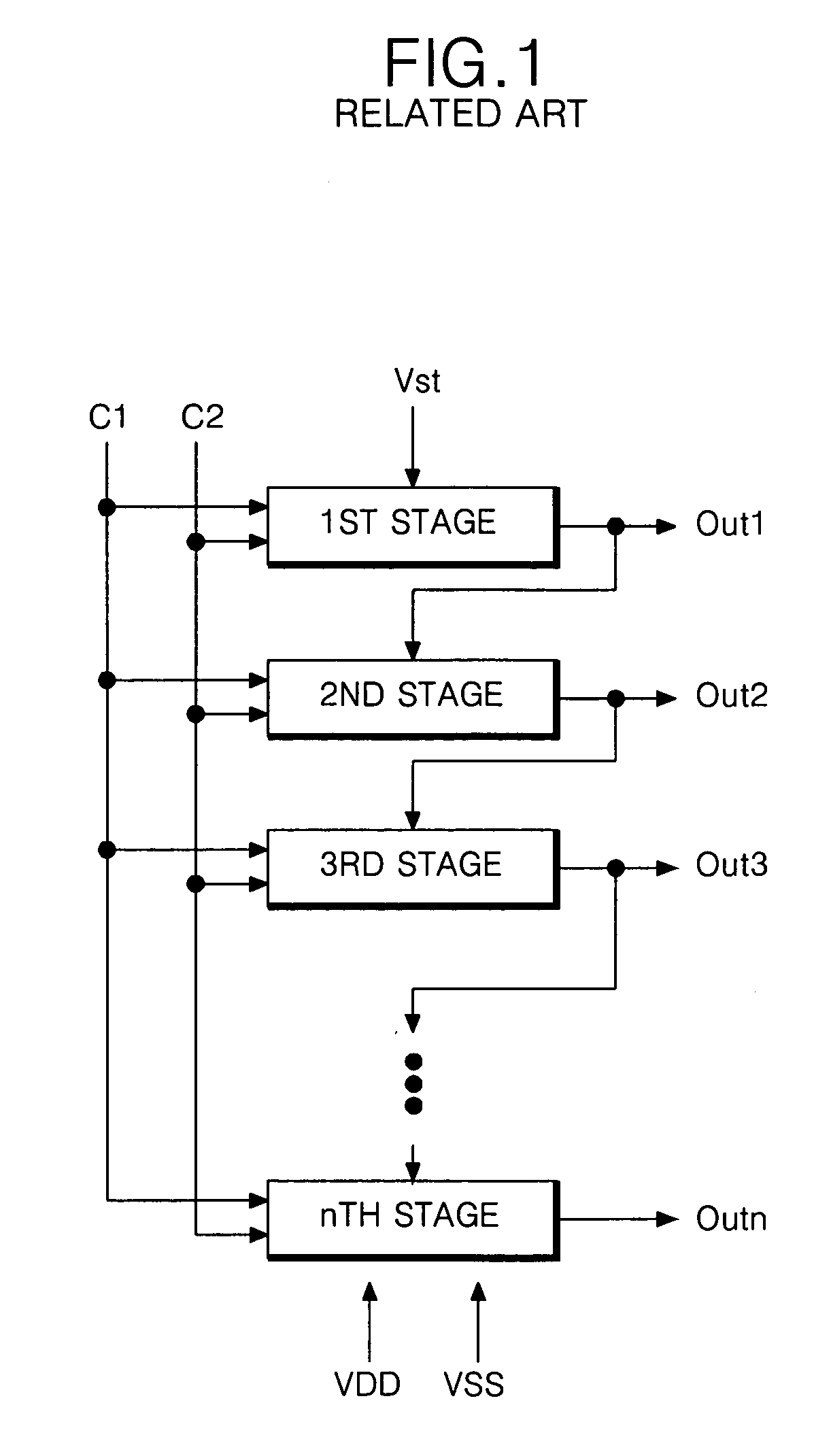

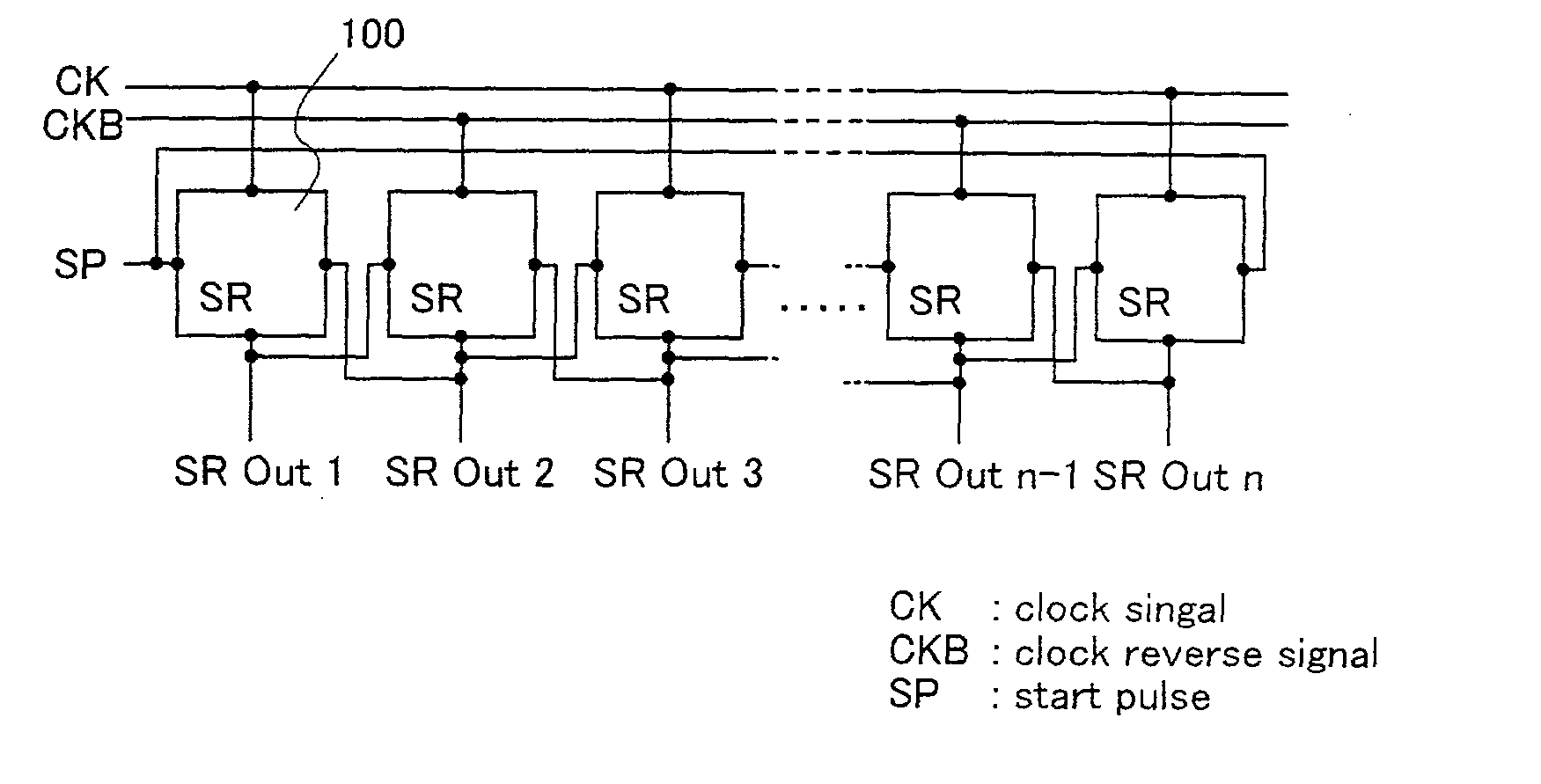

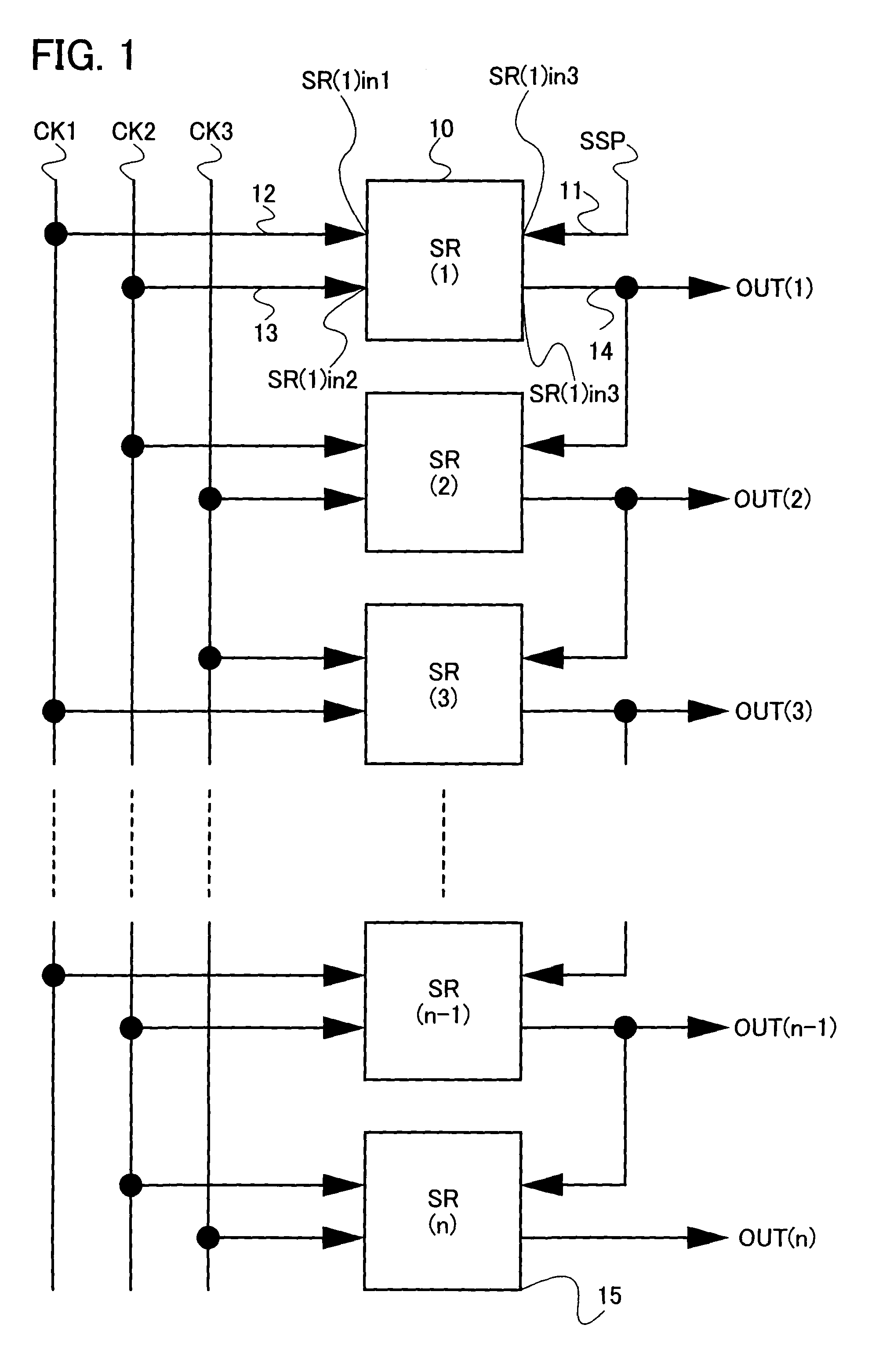

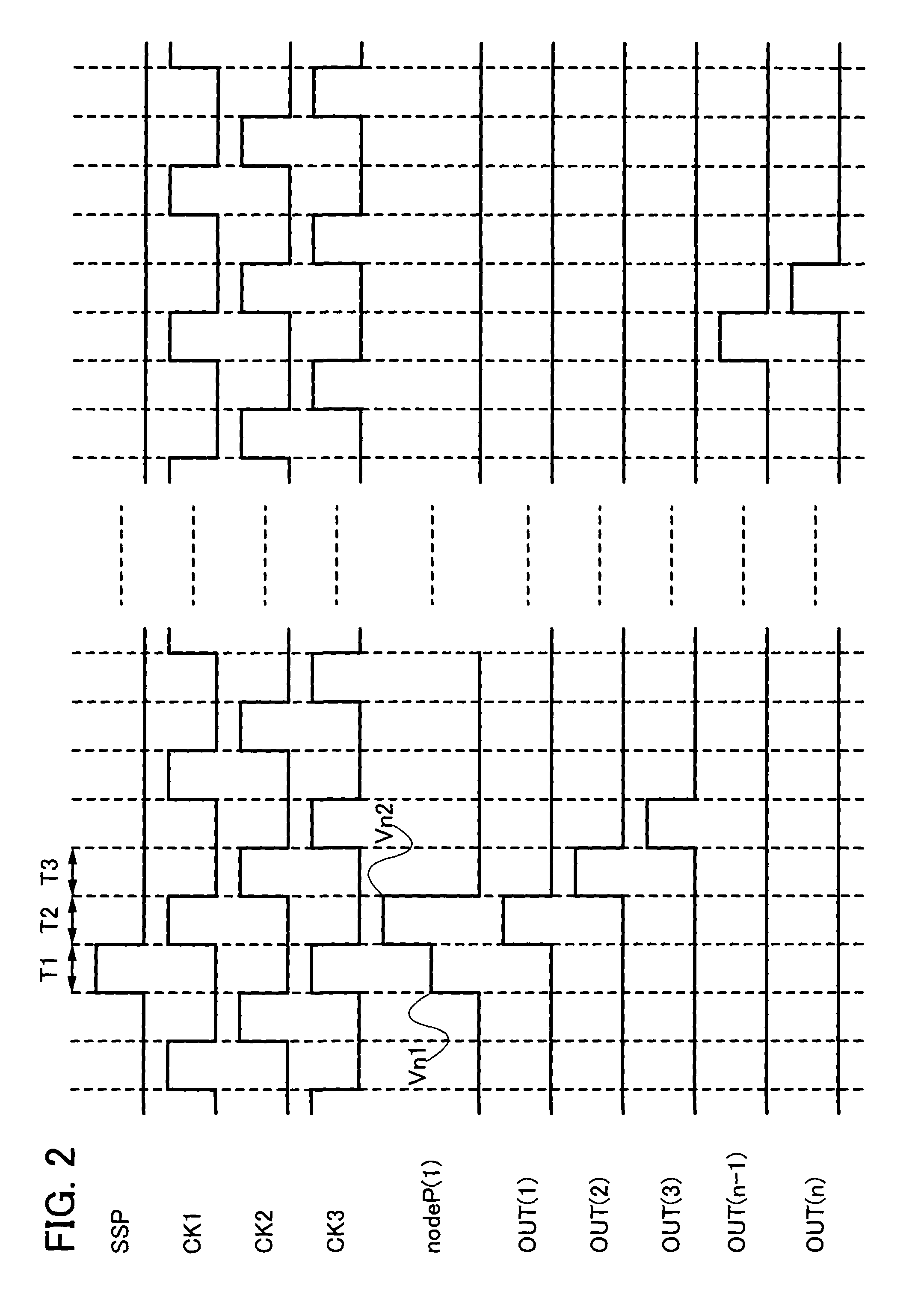

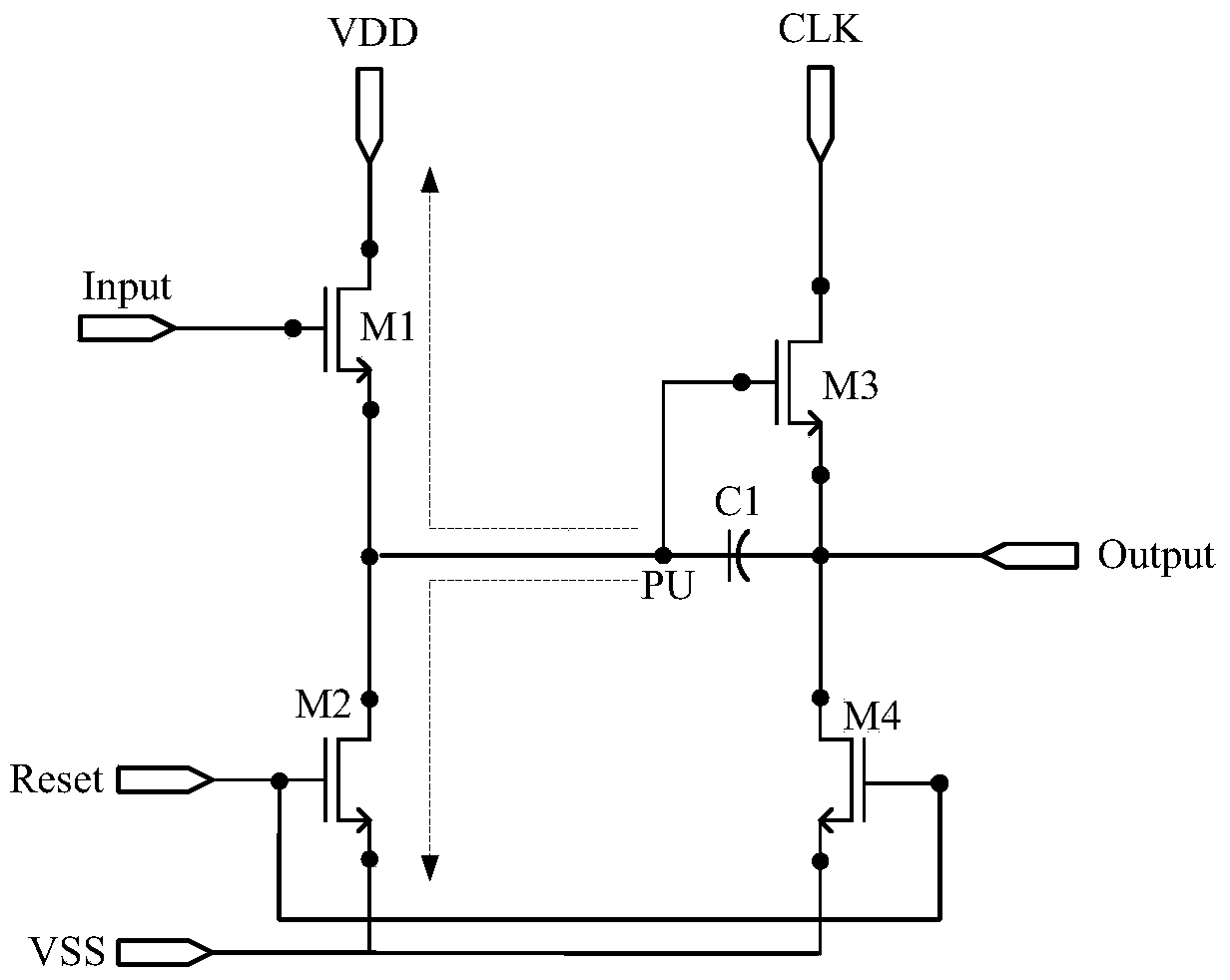

Shift register

An output buffer in each stage of a shift register applies a first clock signal to an output line under control of a first node and a second driving voltage to the output line under control of second and third nodes. A first node controller controls the first node using a start pulse and an output signal of the next stage. A second node controller selectively applies a voltage at a fourth node and the second driving voltage to the second node under control of the first and second clock signals. A third node controller applies the voltage at the fourth node and the second driving voltage to the third node opposite to the second node. A fourth node controller controls the fourth node such that the fourth node has a voltage opposite to the first node using a voltage at the first node and the first driving voltage.

Owner:LG DISPLAY CO LTD

Pulse output circuit, shift register and display device

A drive circuit of a display device, which comprise only single conductive TFTs and in which amplitude of an output signal is normal, is provided. A pulse is inputted to TFTs 101 and 104 so that the TFTs would turn ON and then potential of a node á rises. When the potential of the node á reaches (VDD-VthN), the node á became in a floating state. Accordingly, a TFT 105 then turns ON, and potential of an output node rises as a clock signal reaches the level H. On the other hand, potential of a gate electrode of the TFT 105 further rises due to an operation of capacitance 107 as the potential of the output node rises, so that the potential of the output node would be higher than (VDD+VthN). Thus, the potential of the output node rises to VDD without voltage drop caused by a threshold of the TFT 105. An output at the subsequent stage is then inputted to TFTs 102 and 103 to turn the TFTs 102 and 103 ON, while the potential of the node á drops down to turn the TFT 105 OFF. A TFT 106 turns ON at the same time so that the potential of the output node would reach the level L.

Owner:SEMICON ENERGY LAB CO LTD

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

InactiveUS6018559ADigital storageLogic circuits using elementary logic circuit componentsShift registerTransmission gate

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

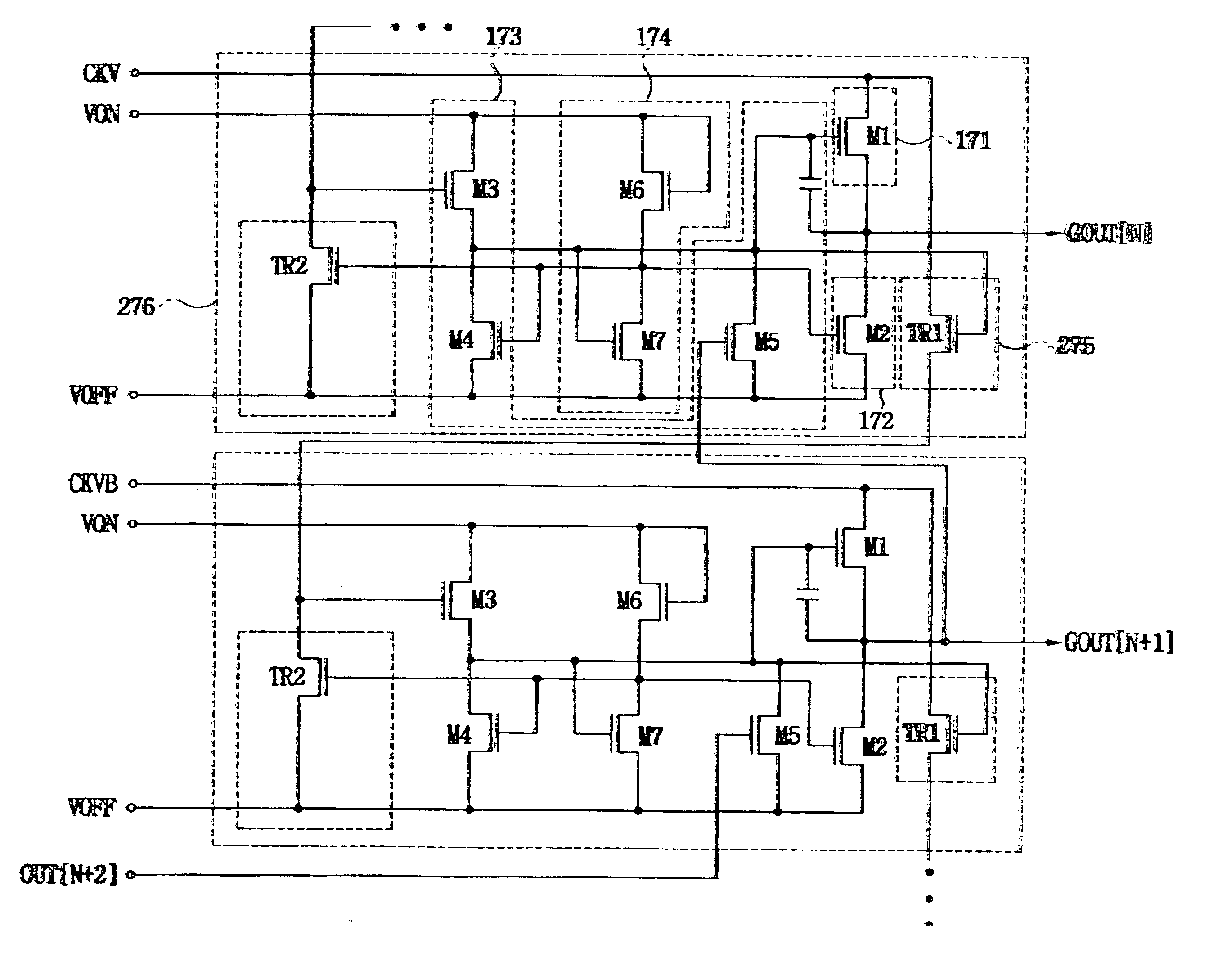

Shift register, scan driving circuit and display apparatus having the same

ActiveUS7486269B2Reduce parasitic capacitancePrevent floatingStatic indicating devicesDigital storageShift registerParasitic capacitance

A shift register includes a plurality of stages to generate a plurality of output signals, in sequence. Each of the stages includes a driving circuit, a charging circuit, a discharging circuit and a holding circuit. The driving circuit is configured to generate a first output signal in response to a first clock signal or a second clock signal having a phase different from the first clock signal. The charging circuit is configured to charge an electric charge in response to a scan start signal or a second output signal of an adjacent previous stage. The discharging circuit is configured to discharge the electric charge in response to a third output signal of an adjacent next stage. The holding circuit is configured to maintain the first output signal within a first voltage when the first output signal is in an inactive state. Therefore, a parasite capacitance is decreased to prevent a floating of a pull-up transistor.

Owner:SAMSUNG DISPLAY CO LTD

Shift register

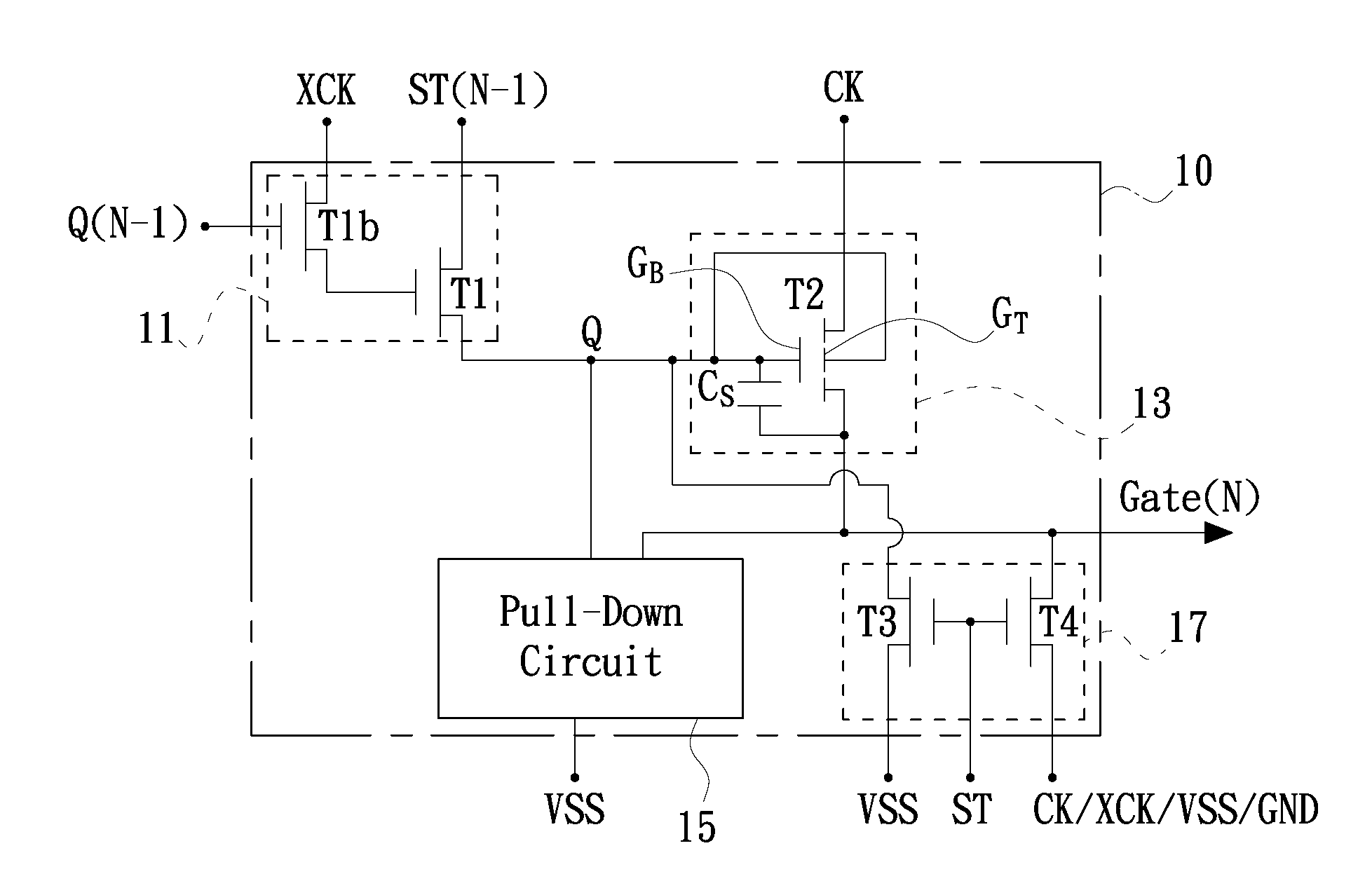

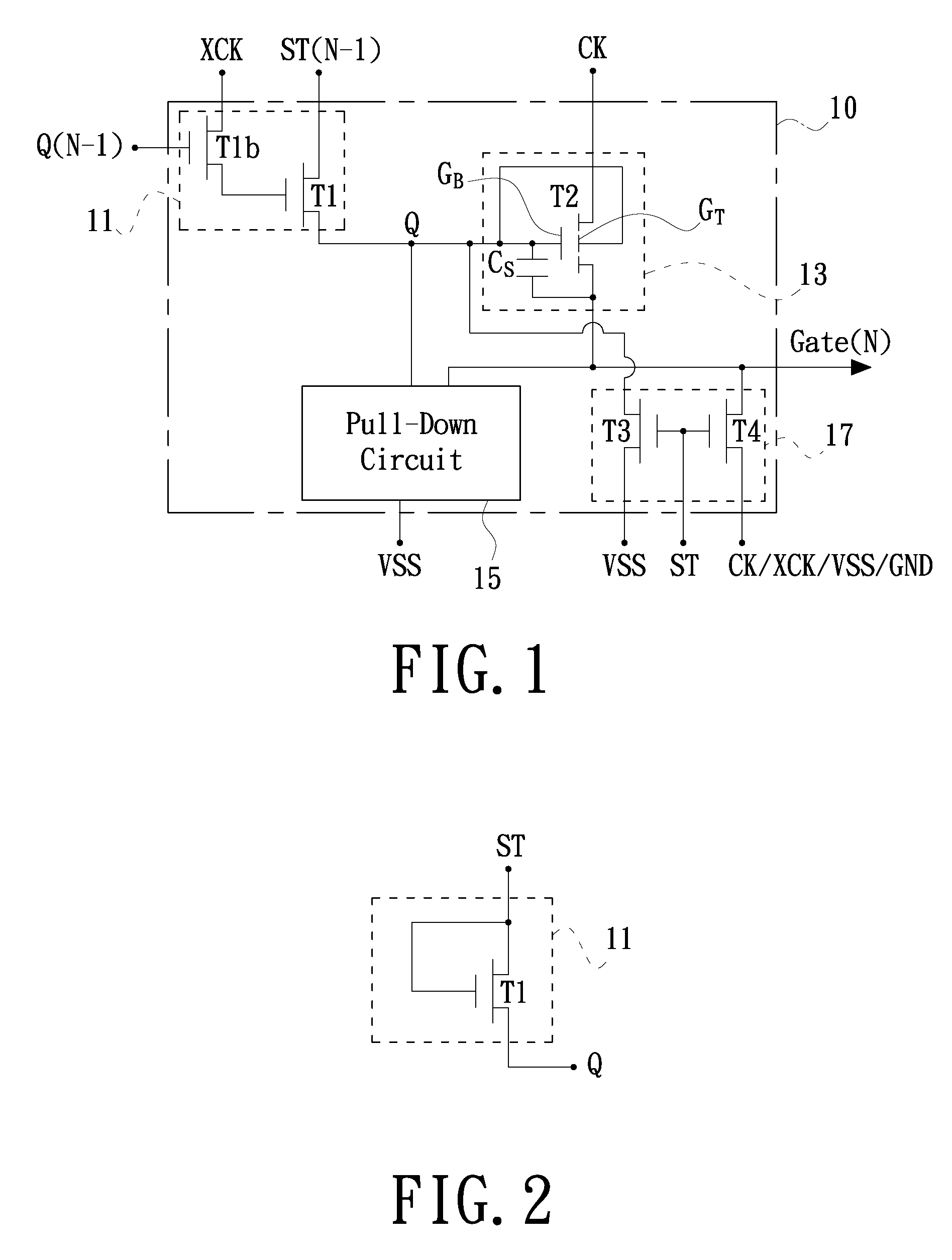

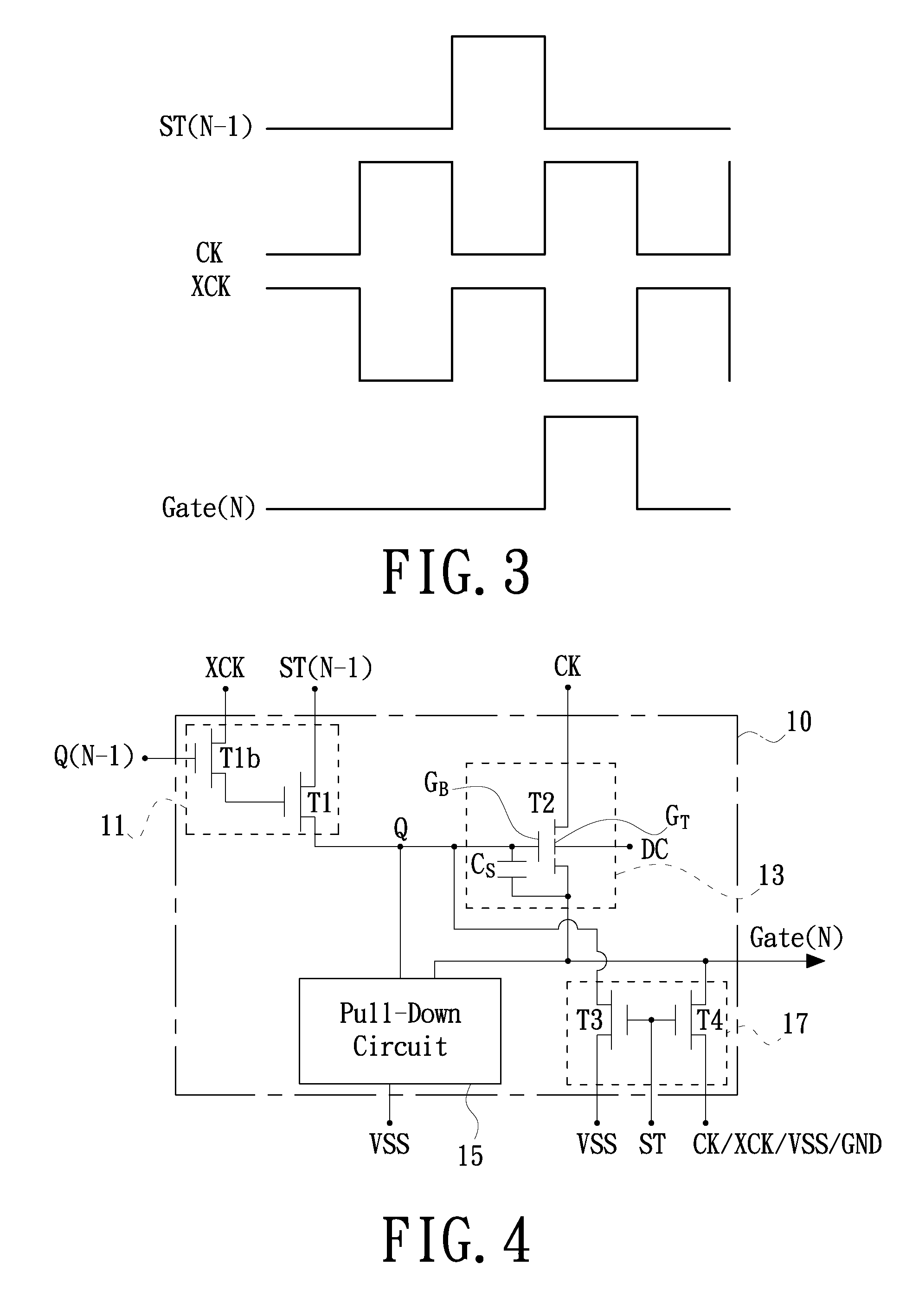

ActiveUS20110150169A1Large conduction currentReduce power consumptionStatic indicating devicesDigital storageShift registerControl signal

A shift register includes a control circuit, a pull-up circuit and a pull-down circuit. The control circuit generates a control signal according to a start pulse signal during being enabled. The pull-up circuit produces a gate pulse signal according to a clock signal during being enabled by the control signal. The pull-up circuit includes a dual-gate transistor. A first gate of the dual-gate transistor is electrically coupled to the control signal, a second gate of the dual-gate transistor is electrically coupled to a predetermined voltage, the source / drain of the dual-gate transistor serves as an output terminal for the gate pulse signal, and the drain / source of the dual-gate transistor is electrically coupled to the clock signal. The pull-down circuit pulls a potential at the first gate and another potential at the output terminal down to a power supply potential during the pull-up circuit is disabled

Owner:AU OPTRONICS CORP

Liquid crystal display device and electronic device

ActiveUS20080007296A1Optimize layoutMaintain good propertiesStatic indicating devicesSolid-state devicesShift registerLiquid-crystal display

Owner:SEMICON ENERGY LAB CO LTD

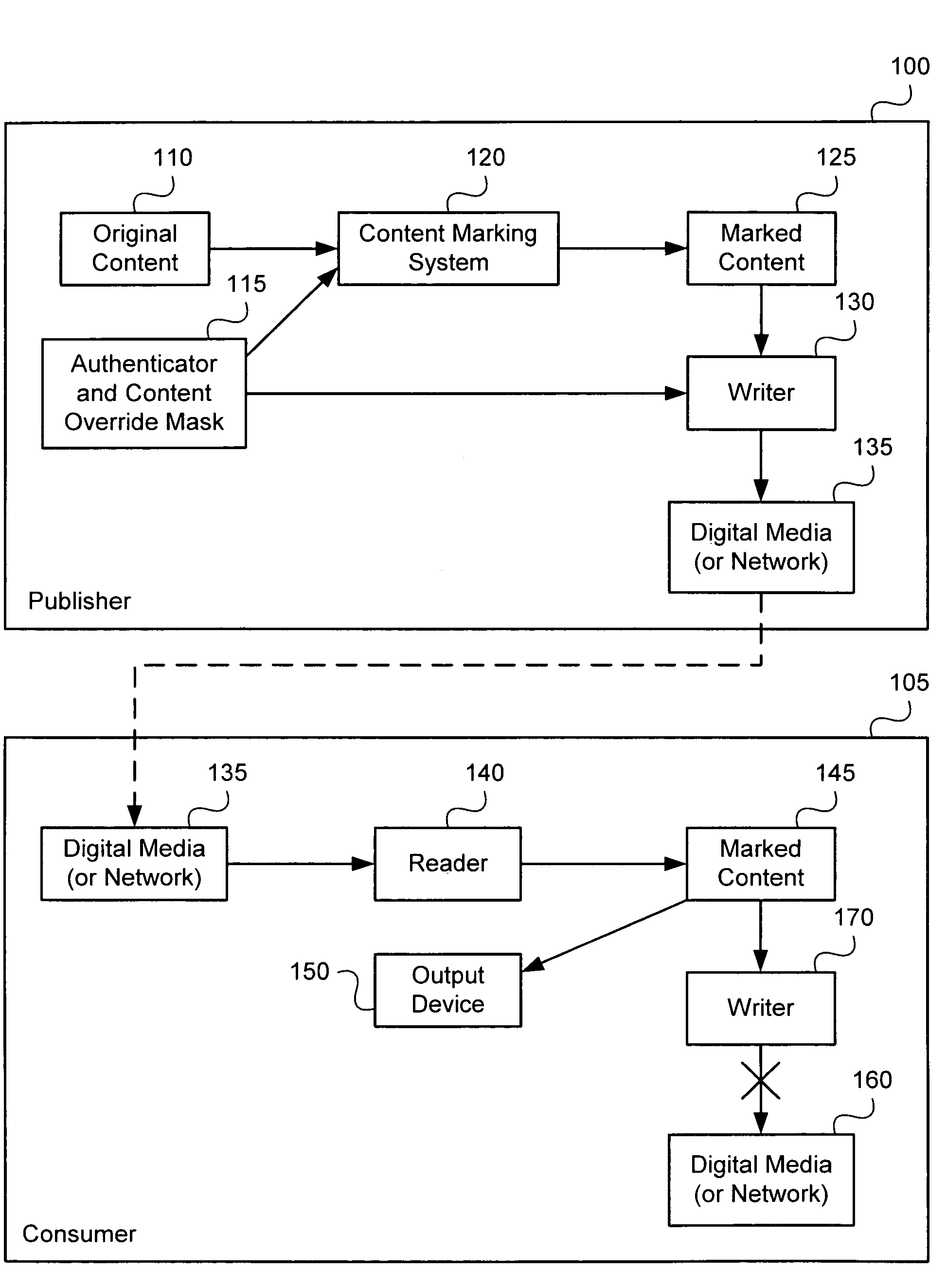

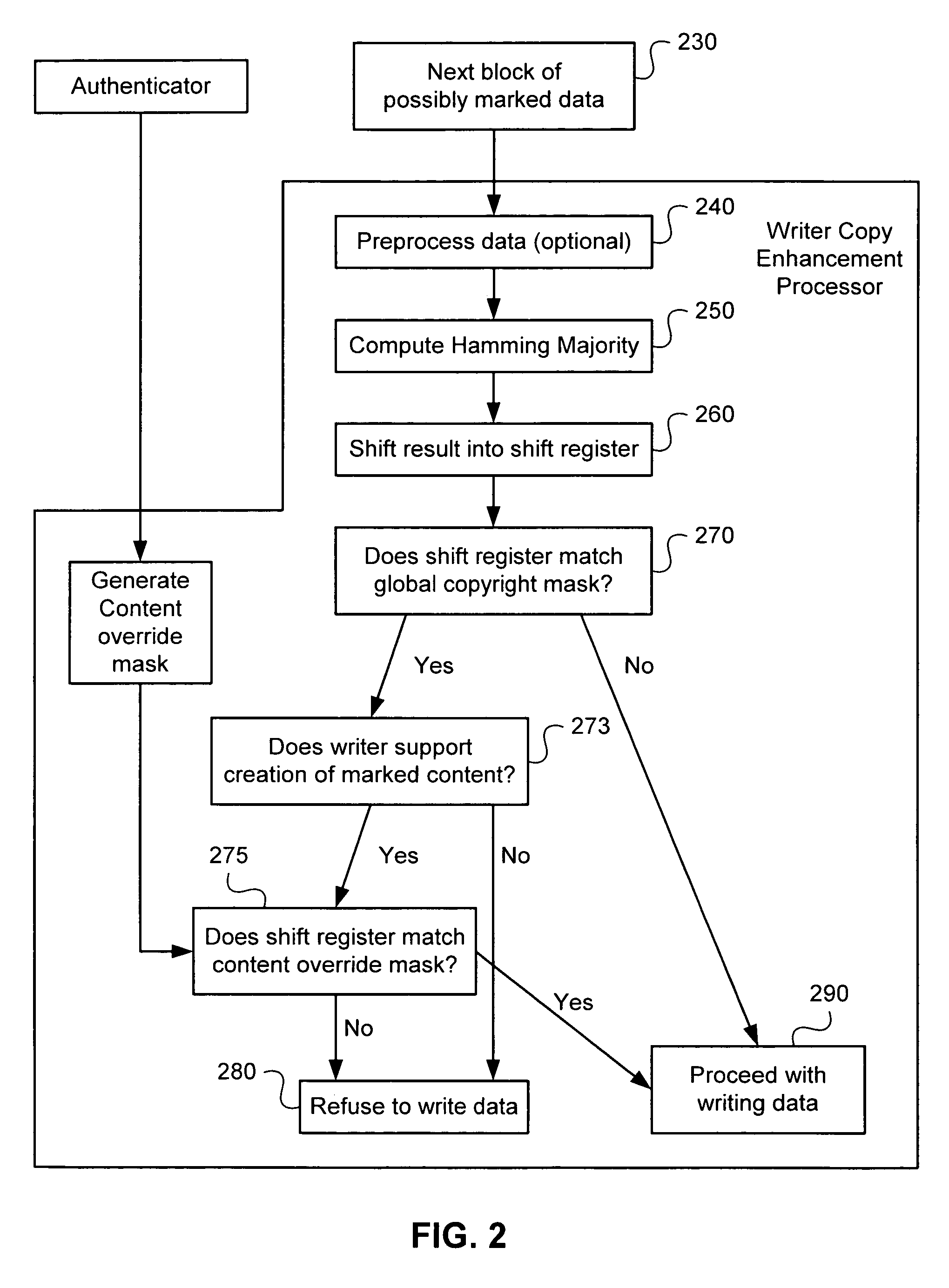

Method and system for copy-prevention of digital copyright works

InactiveUS6978370B1Obstruction is producedHighly effective copy-preventionUser identity/authority verificationTelevision systemsShift registerCoverage function

Methods and apparati for marking digital material and for detecting marks therein. For mark detection, the material is divided into a plurality of blocks, to which a non-collision resistant compression function is applied. Compression outputs are placed in a shift register, whose value is tested for predetermined values or patterns. Mark embedding may be performed by modifying the data (for example by altering low-order bits and other non-critical regions) such that the outputs of the compression operation, when used as an input to the shift register, yield a predetermined value or pattern. A Hamming Majority operation, computed as the most common bit in a block, may be used as the compression operation, enabling marking and mark detection with material of virtually all types and formats. Mark detection technology may be implemented in media writers and other devices to determine whether the digital material is copyrighted or otherwise protected. An override capability is provided to allow authorized parties to bypass the protection.

Owner:IRDETO USA

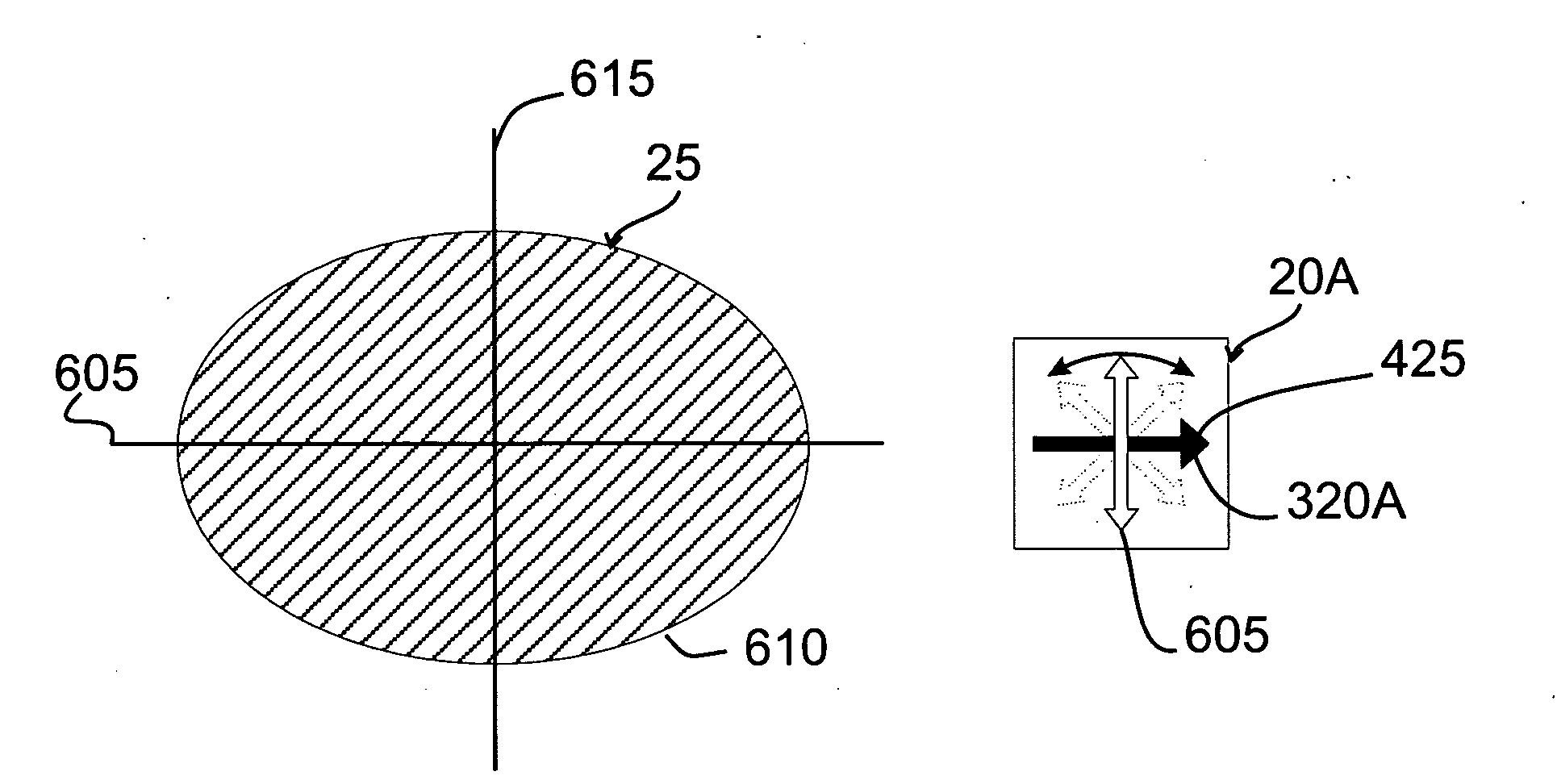

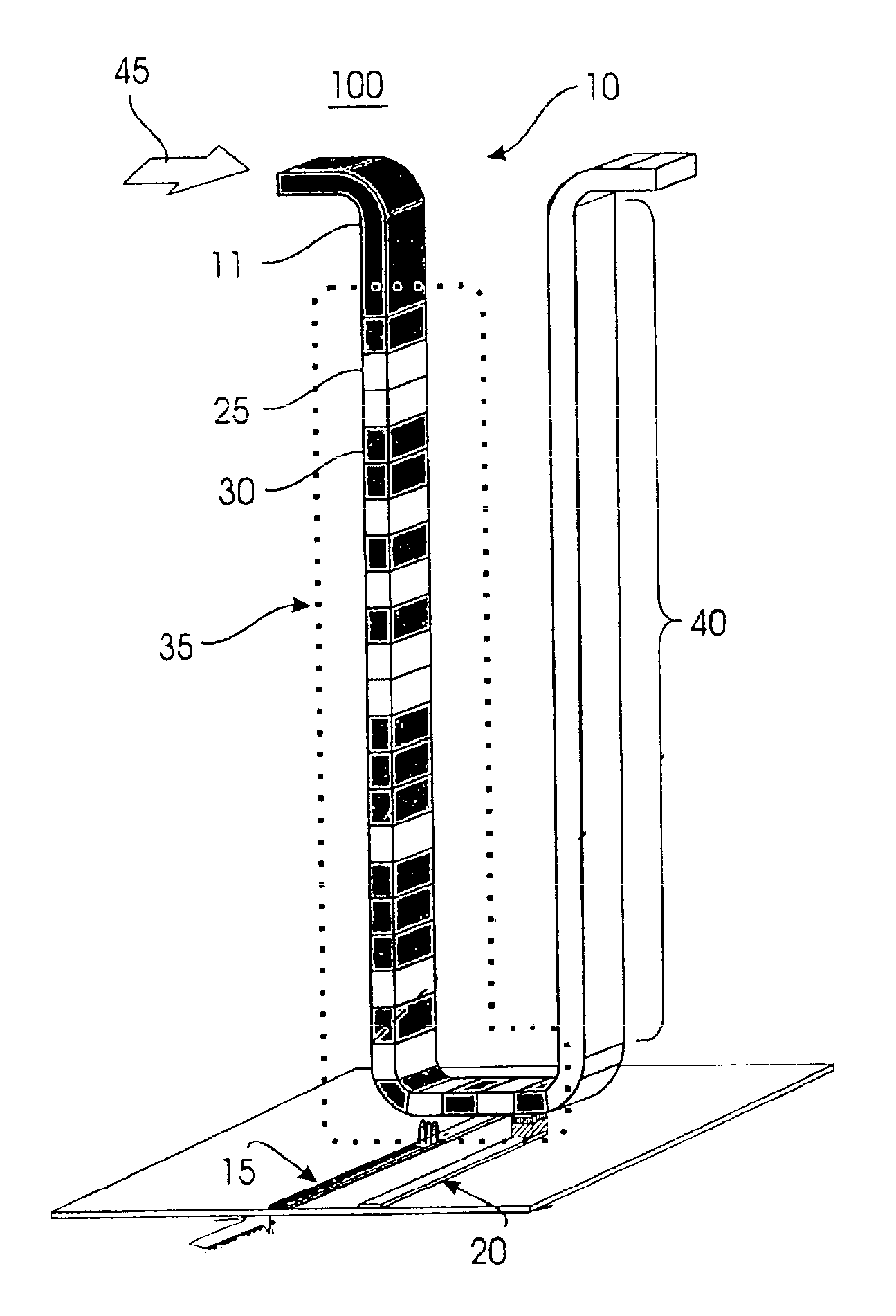

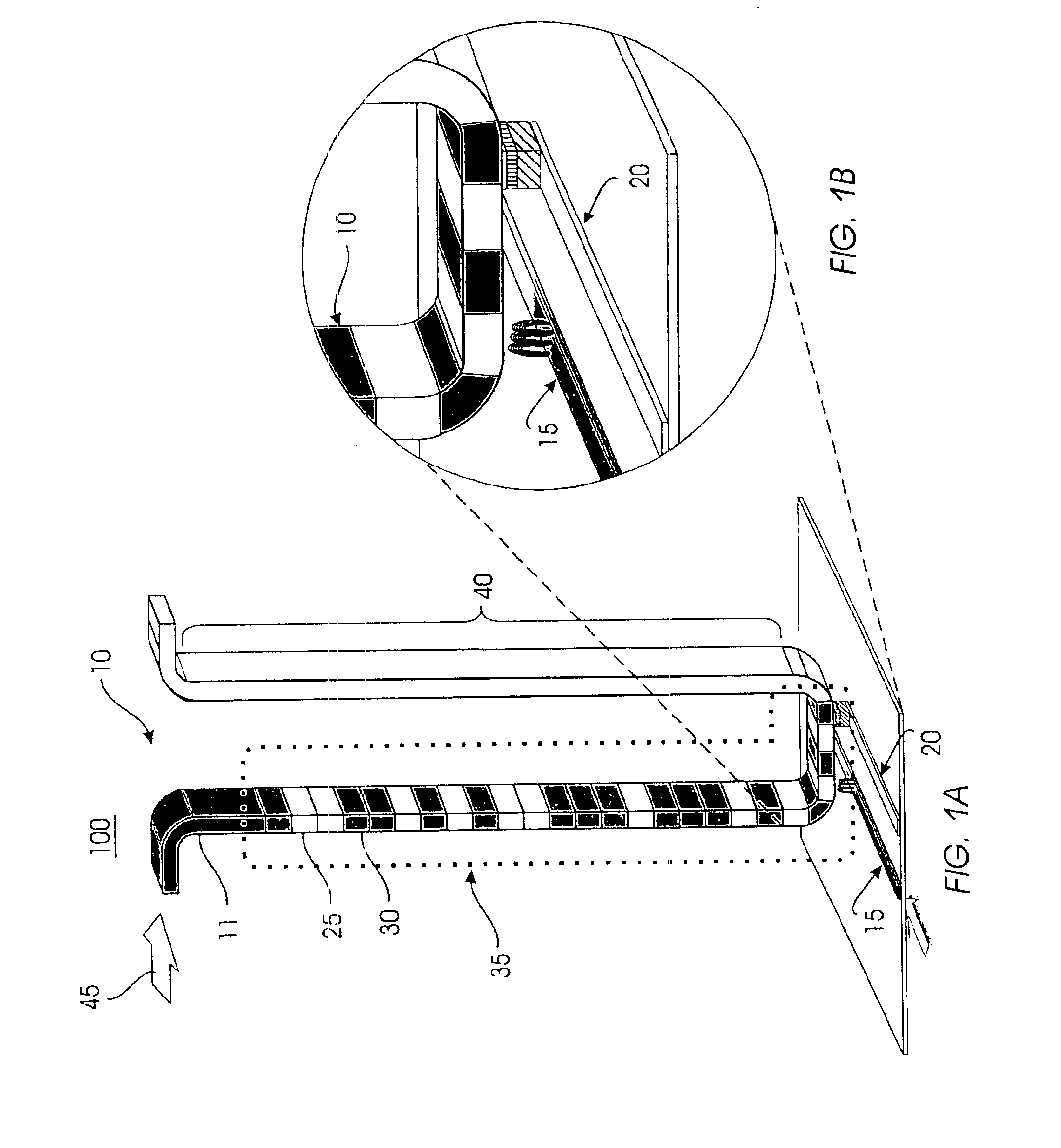

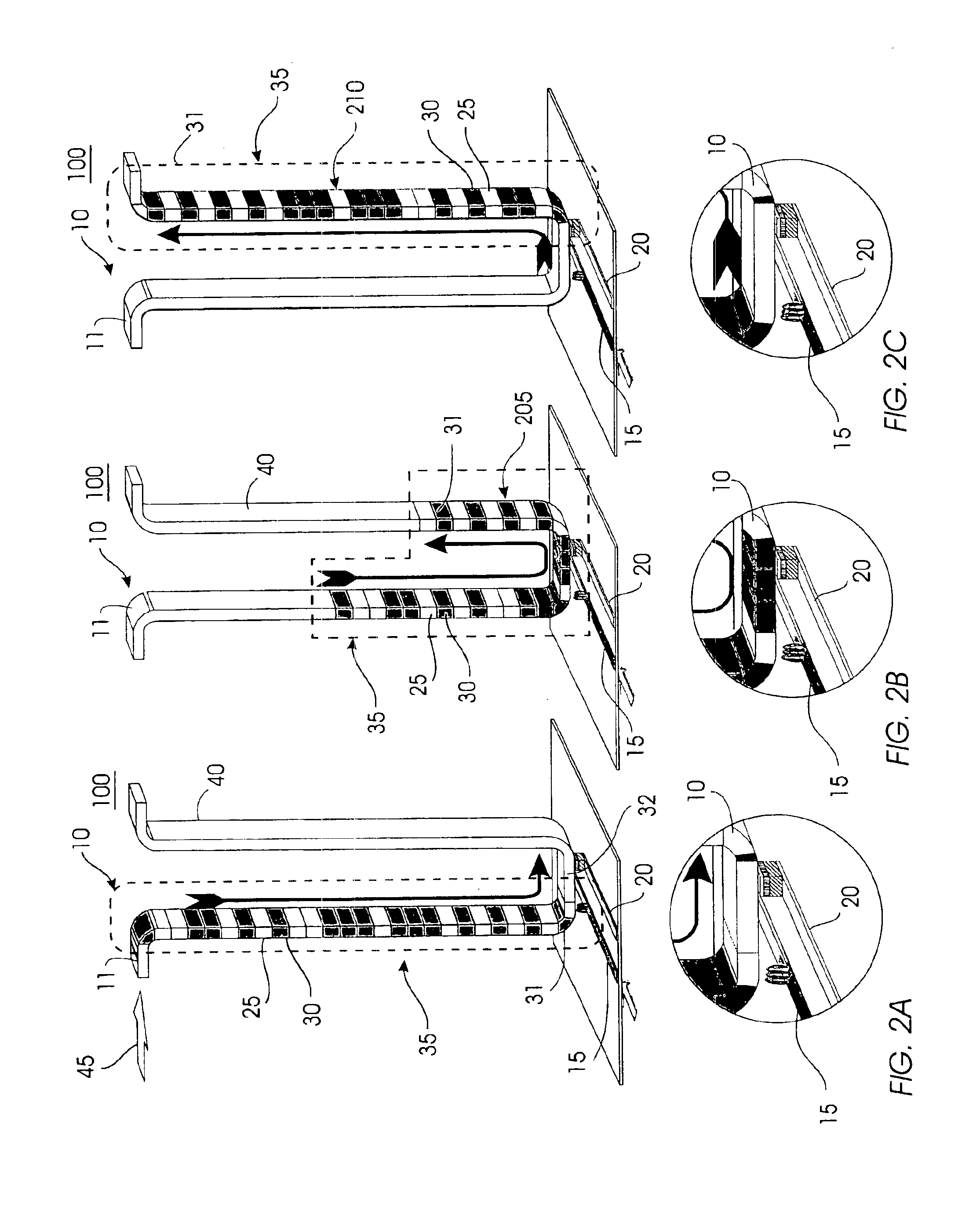

System and method for transferring data to and from a magnetic shift register with a shiftable data column

InactiveUS20060120132A1Magnitude fringing fieldEasy to operateDigital storageShift registerData storing

A magnetic shift register utilizes a data column comprising a thin wire of magnetic material. A writing element selectively changes the direction of the magnetic moment in the magnetic domains to write the data to the data column. Associated with each domain wall are large magnetic fringing fields concentrated in a very small space. These magnetic fringing fields write to and read from the magnetic shift register. When the domain wall is moved close to another magnetic material, the fringing fields change the direction of the magnetic moment in the magnetic material, effectively “writing” to the magnetic material. A reading element similar to a tunneling junction comprises a free layer and a pinned layer of magnetic material. Fringing fields change the direction of the magnetic moment in the free layer with respect to the pinned layer, changing electrical resistance of the reading element and “reading” data stored in the magnetic shift register.

Owner:GLOBALFOUNDRIES US INC

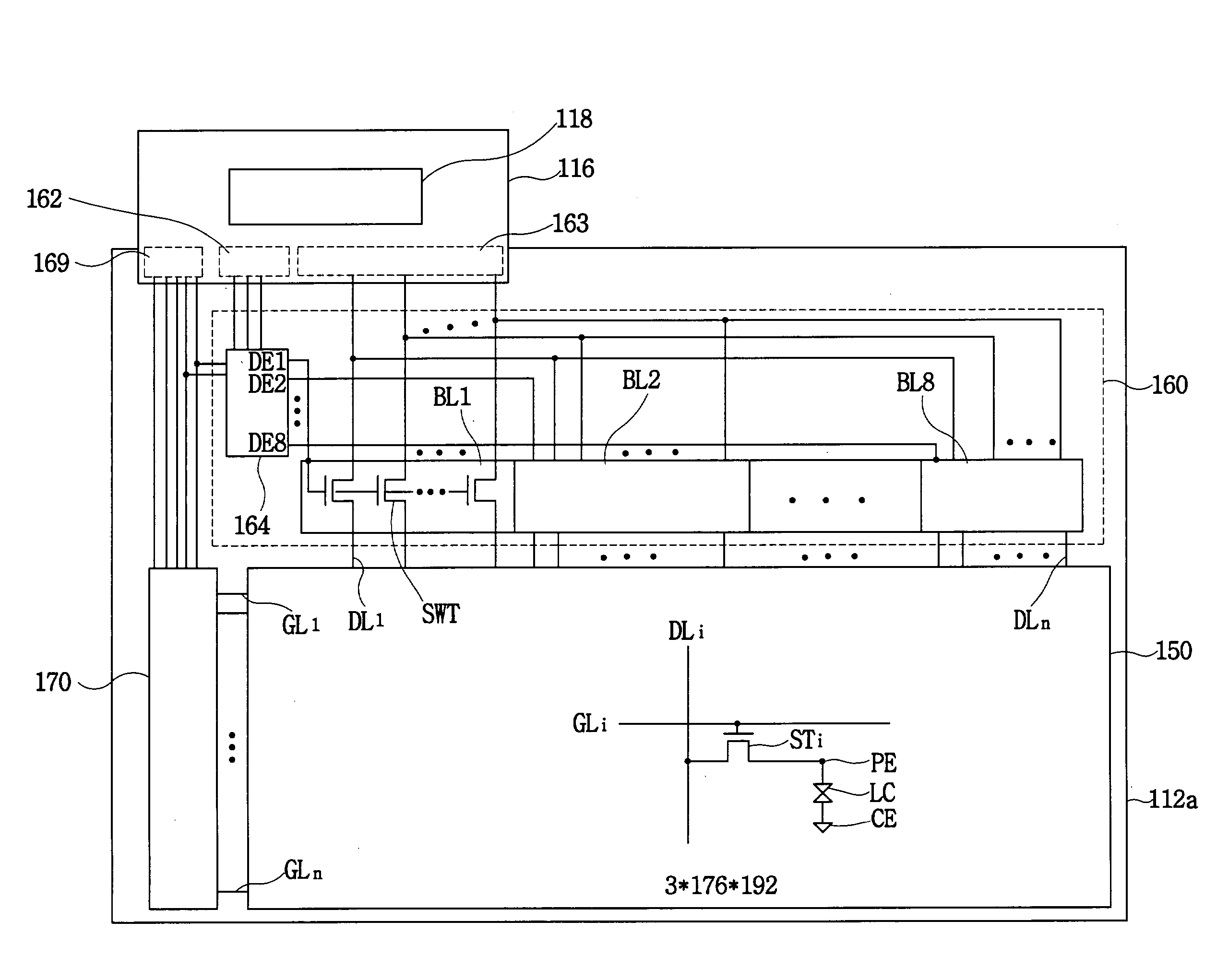

Shift register circuit and image display apparatus containing the same

InactiveUS7436923B2Avoid failureReduced driving abilityStatic indicating devicesDigital storageShift registerProcessor register

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:TRIVALE TECH LLC

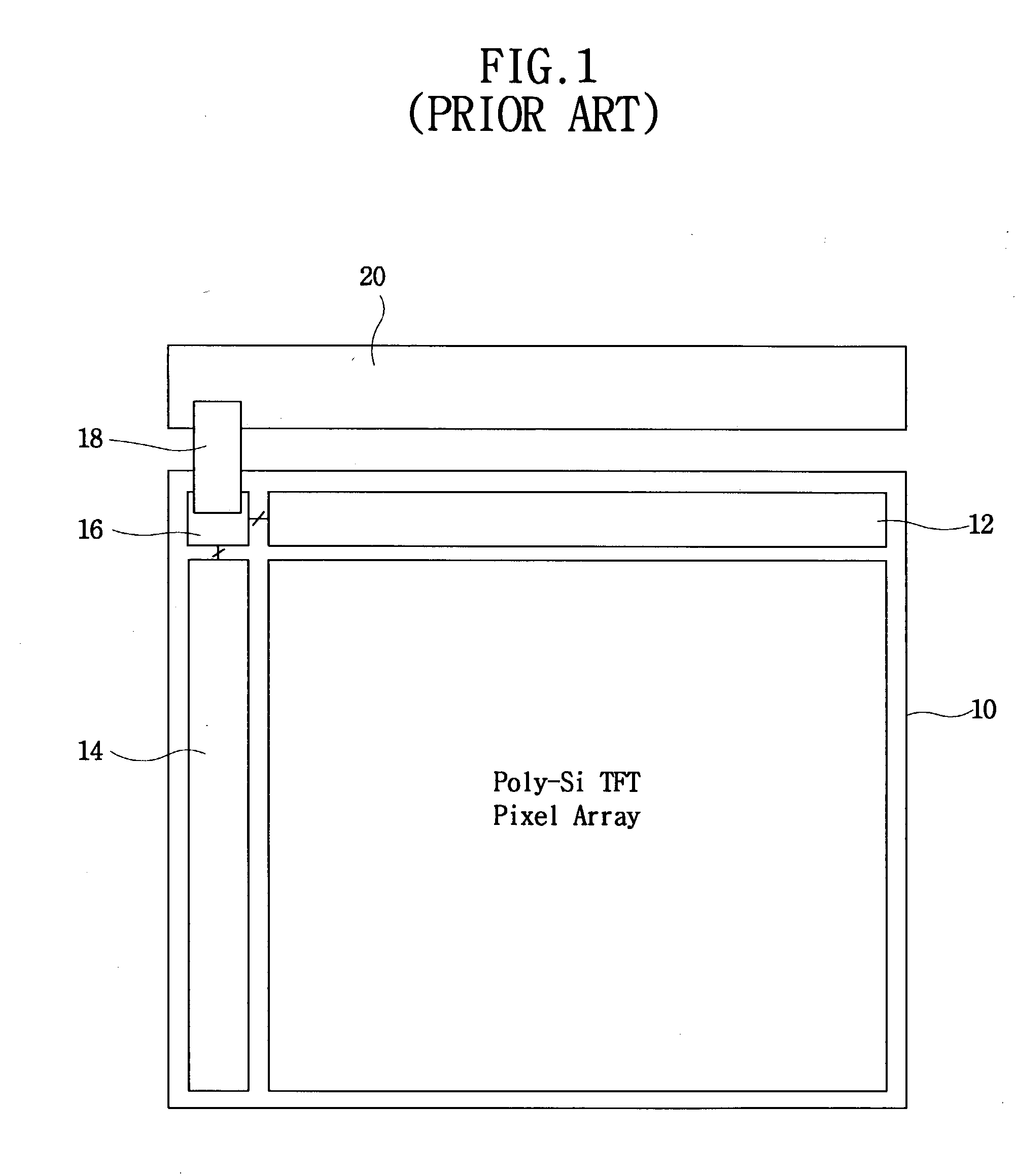

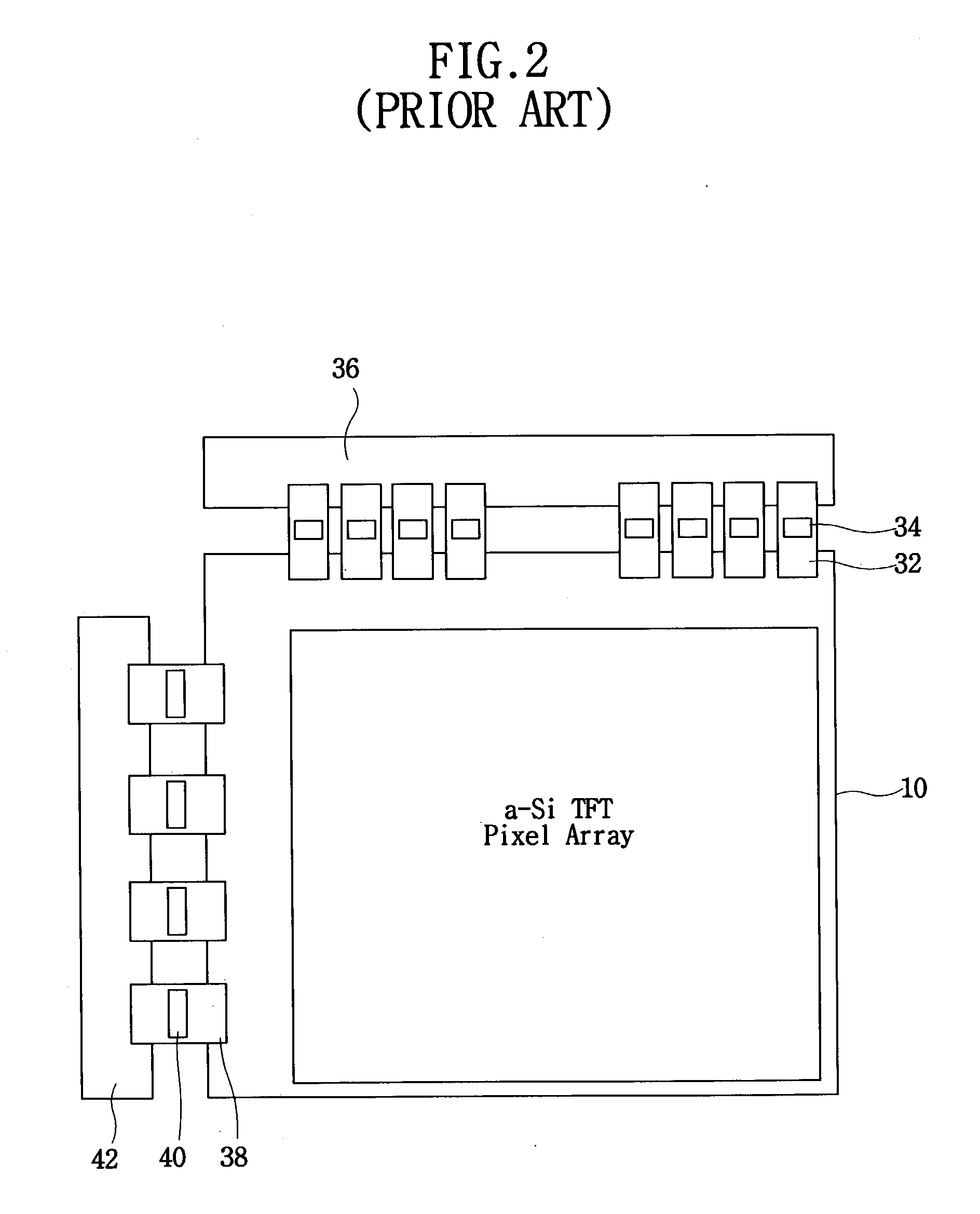

Shift register of LCD devices

A shift register includes a plurality of shift register units coupled in series. Each shift register unit, receiving an input voltage at an input end and an output voltage at an output end, includes a node, a pull-up driving circuit, a pull-up circuit and first through third pull-down circuits. The pull-up driving circuit can transmit the input voltage to the node, and the pull-up circuit can provide the output voltage based on a high-frequency clock signal and the input signal. The first pull-down circuit can provide a bias voltage at the node or at the output end based on a first low-frequency clock signal. The second pull-down circuit can provide a bias voltage at the node or at the output end based on a second low-frequency clock signal. The third pull-down circuit can provide a bias voltage at the node or at the output end based on a feedback voltage.

Owner:AU OPTRONICS CORP

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 ON, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

Shift register

Disclosed is a shift register capable of mitigating gate bias stress. The shift register, including a plurality of stages, includes an output buffer having a pull-up transistor and two pull-down transistors, each with gates connected to different nodes. One of the two pull-down transistors operates during an even frame portion of an LCD operation; and the other of the two pull-down transistors operates during an odd frame portion of the LCD display operation. Alternating operation of the pull-down transistors substantially mitigates gate stress, and substantially enables the shift register to be fabricated with amorphous silicon.

Owner:LG DISPLAY CO LTD

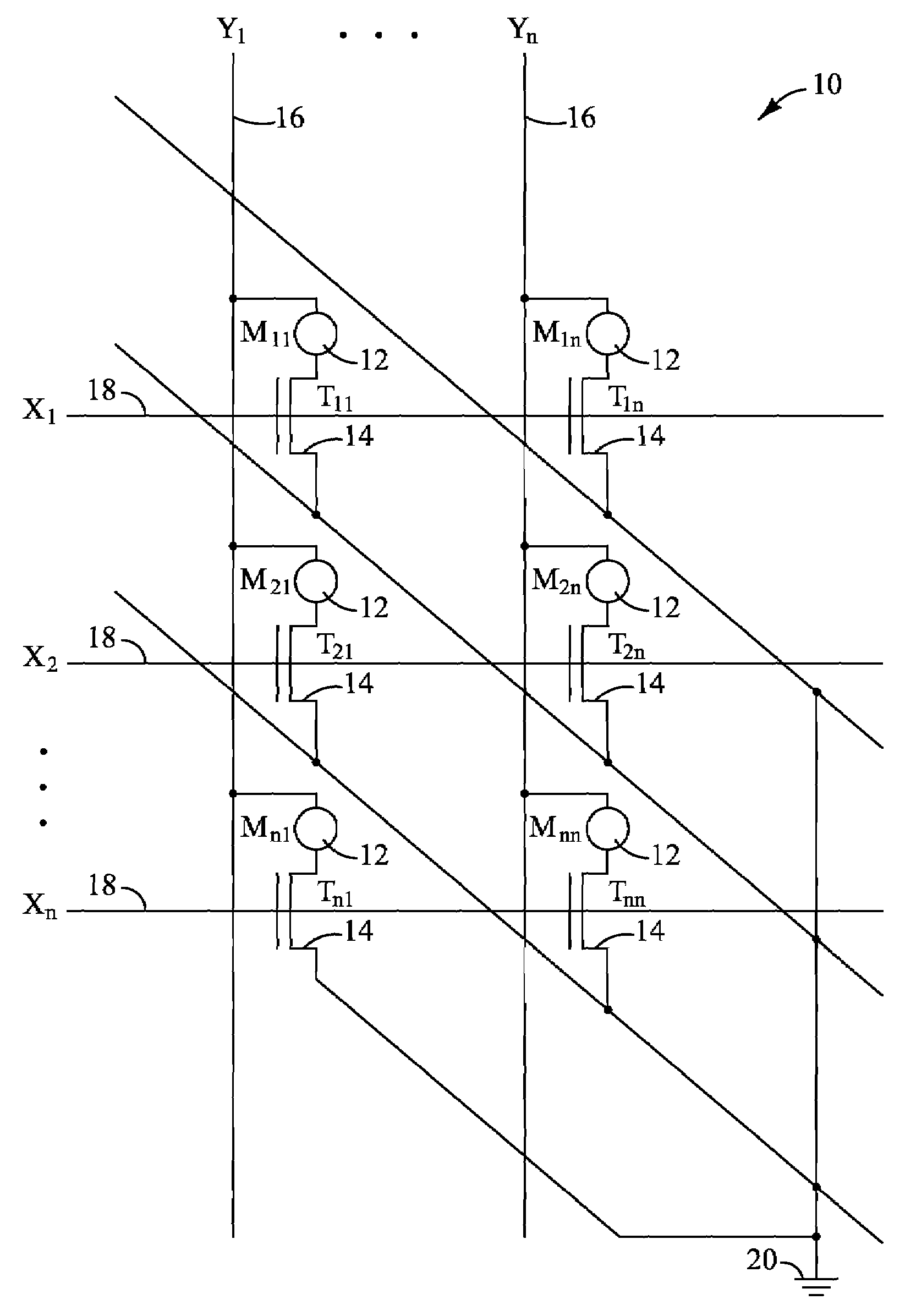

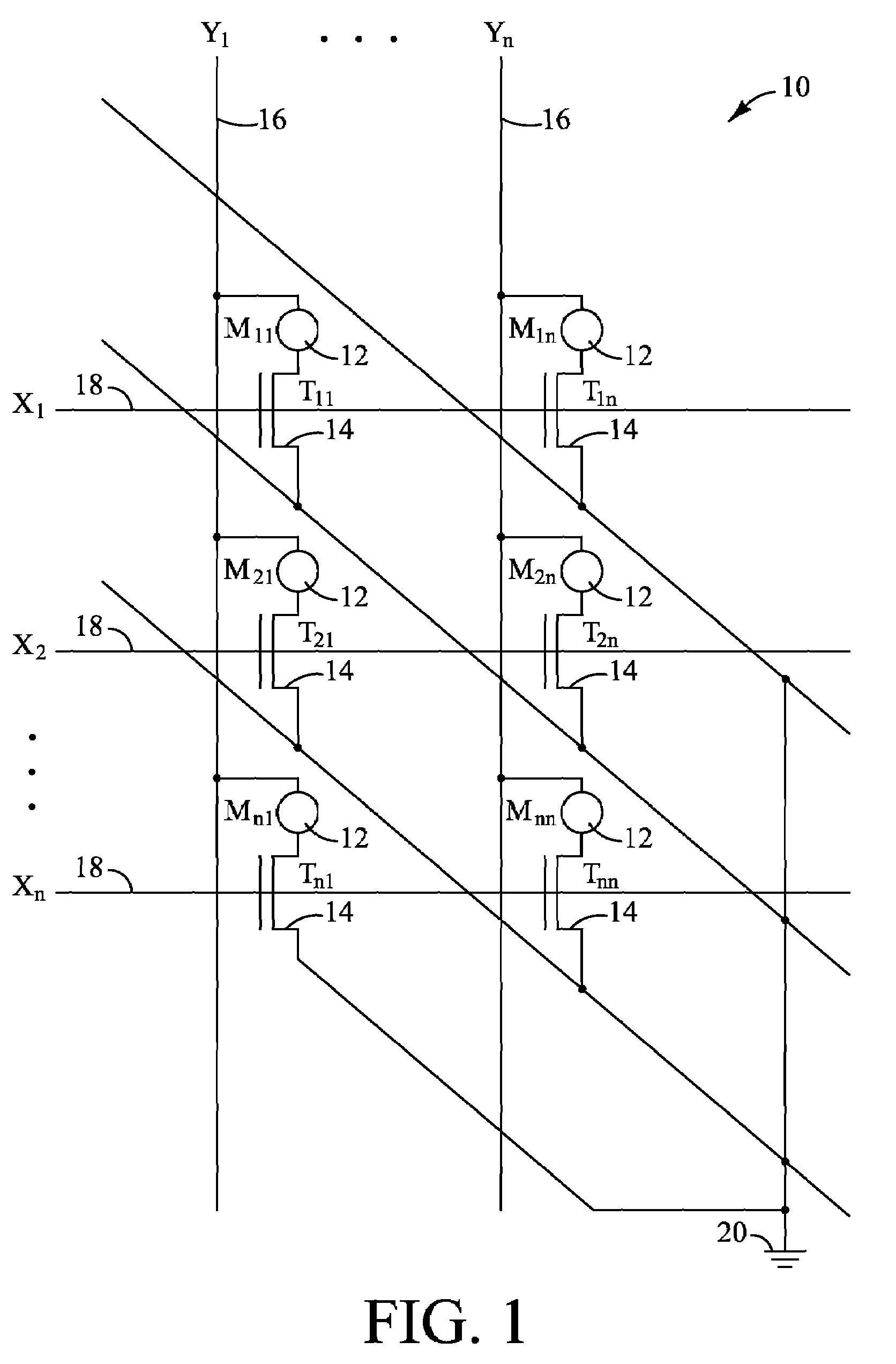

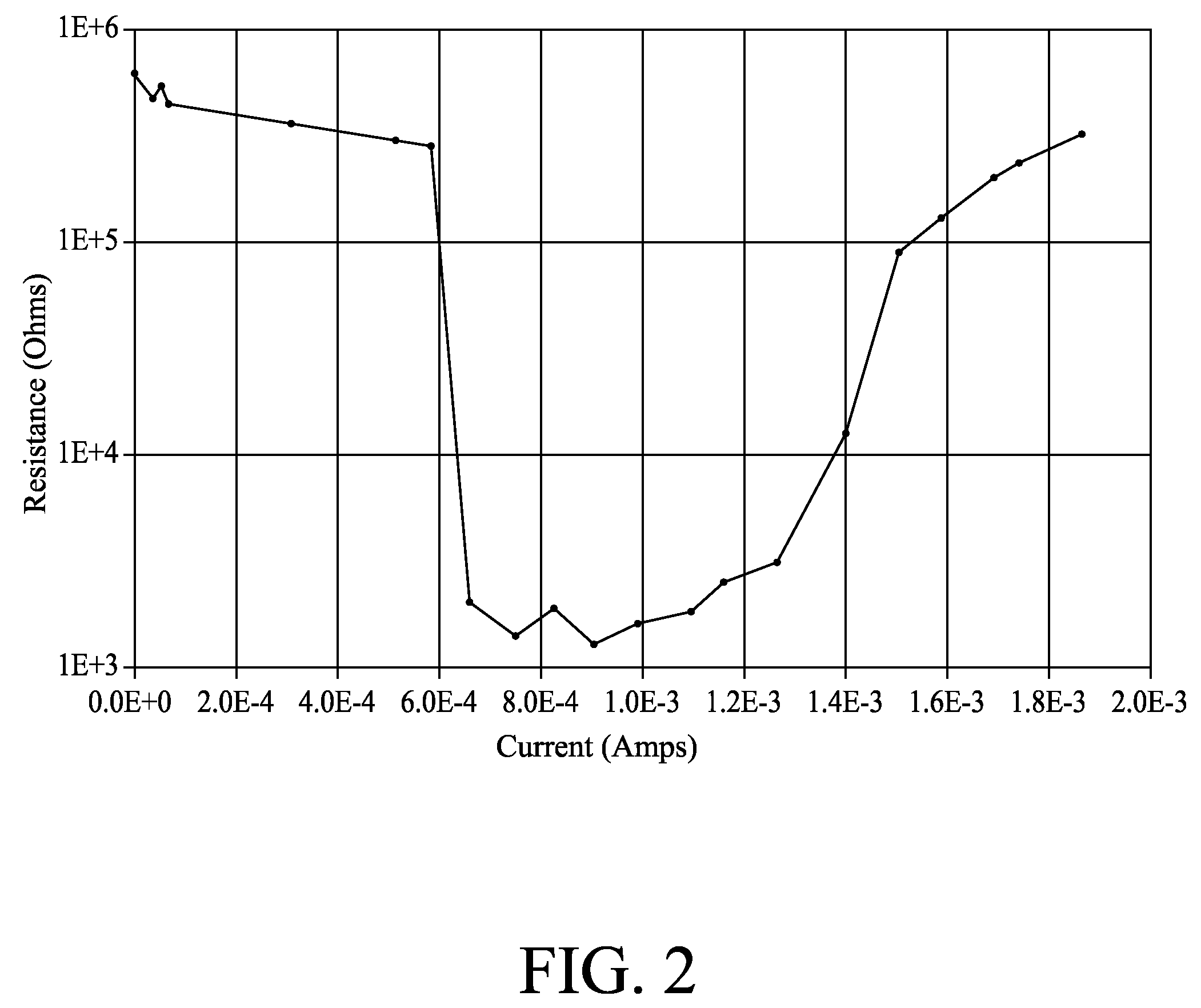

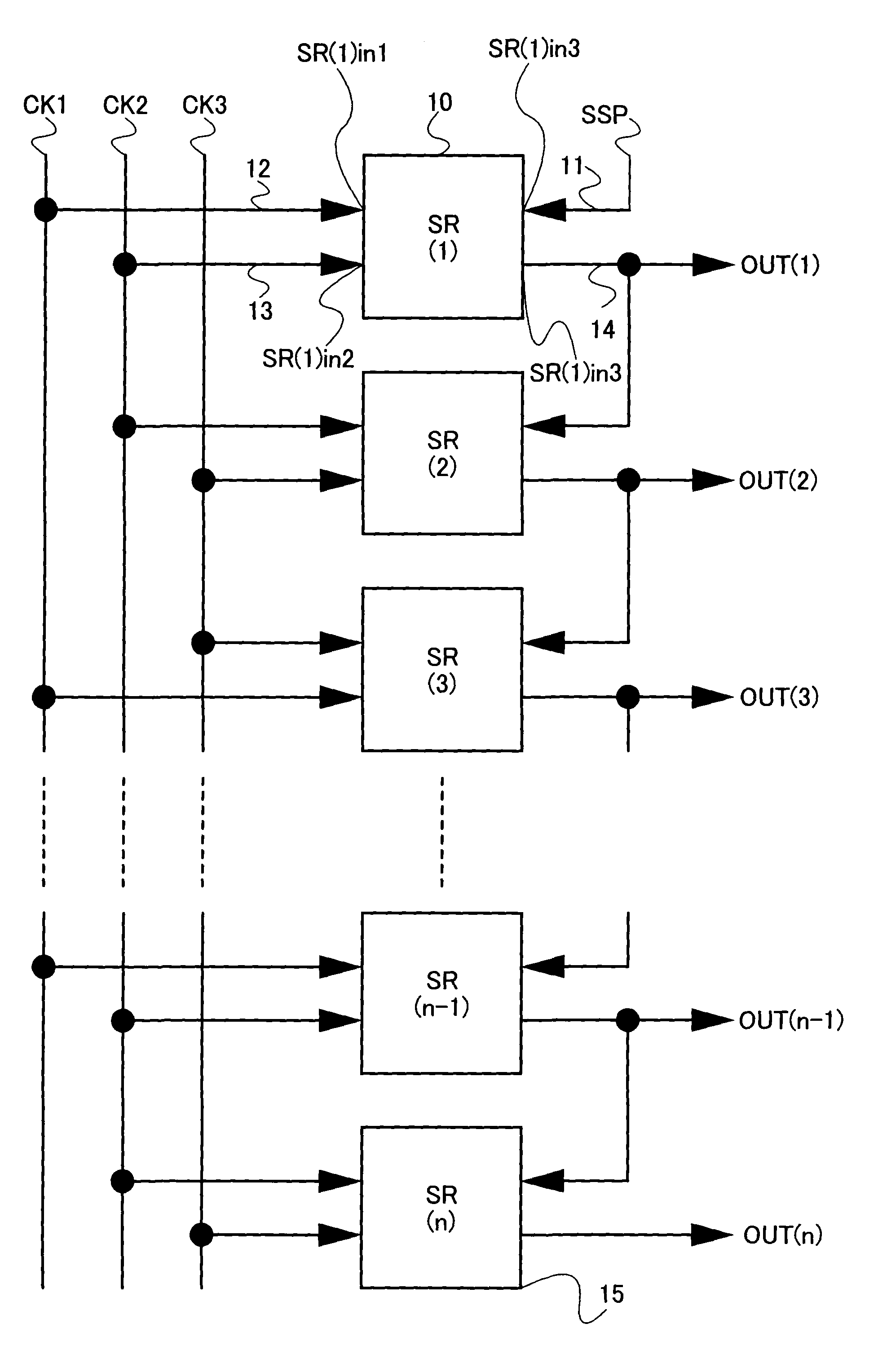

Sequential and video access for non-volatile memory arrays

An array of non-volatile memory cells arranged in logical columns and logical rows, and associated circuitry to enable reading or writing one or more memory cells on a row in parallel. In some embodiments, the array of memory cells may include a phase change material. In some embodiments, the circuitry may include a write driver, a read driver, a sense amplifier, and circuitry to isolate the memory cells from the sense amplifier with extended refresh. In some embodiments, the circuitry may further include shift registers and one or more arithmetic logic units to provide a video memory.

Owner:OVONYX MEMORY TECH LLC

Shift register, semiconductor device, display device, and electronic device

ActiveUS20100026619A1Reduce noiseDeterioration of characteristicElectrical apparatusStatic indicating devicesShift registerDisplay device

The invention provides a semiconductor device and a shift register, in which low noise is caused in a non-selection period and a transistor is not always on. First to fourth transistors are provided. One of a source and a drain of the first transistor is connected to a first wire, the other of the source and the drain thereof is connected to a gate electrode of the second transistor, and a gate electrode thereof is connected to a fifth wire. One of a source and a drain of the second transistor is connected to a third wire and the other of the source and the drain thereof is connected to a sixth wire. One of a source and a drain of the third transistor is connected to a second wire, the other of the source and the drain thereof is connected to the gate electrode of the second transistor, and a gate electrode thereof is connected to a fourth wire. One of a source and a drain of the fourth transistor is connected to the second wire, the other of the source and the drain thereof is connected to the sixth wire, and a gate electrode thereof is connected to the fourth wire.

Owner:SEMICON ENERGY LAB CO LTD

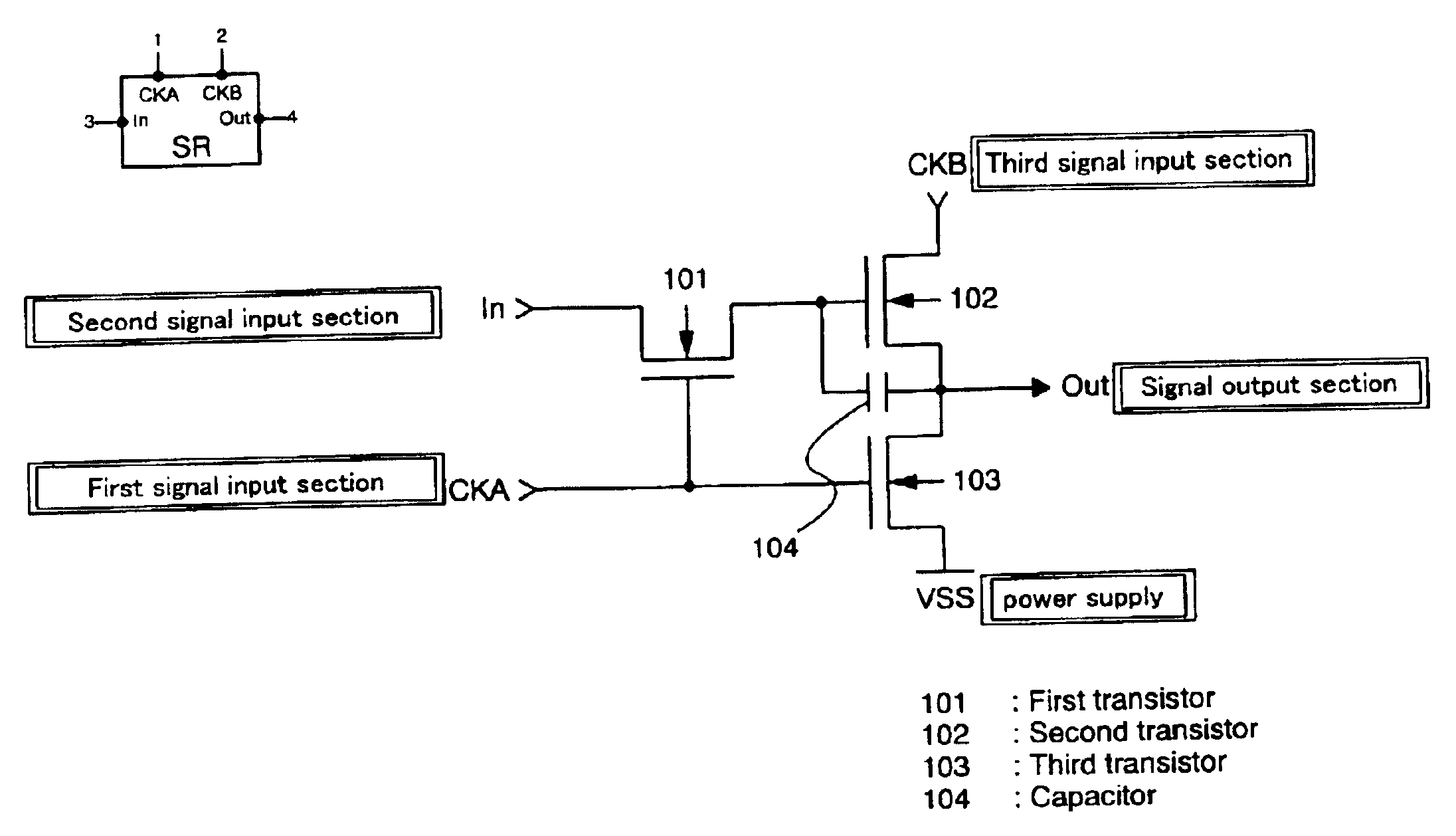

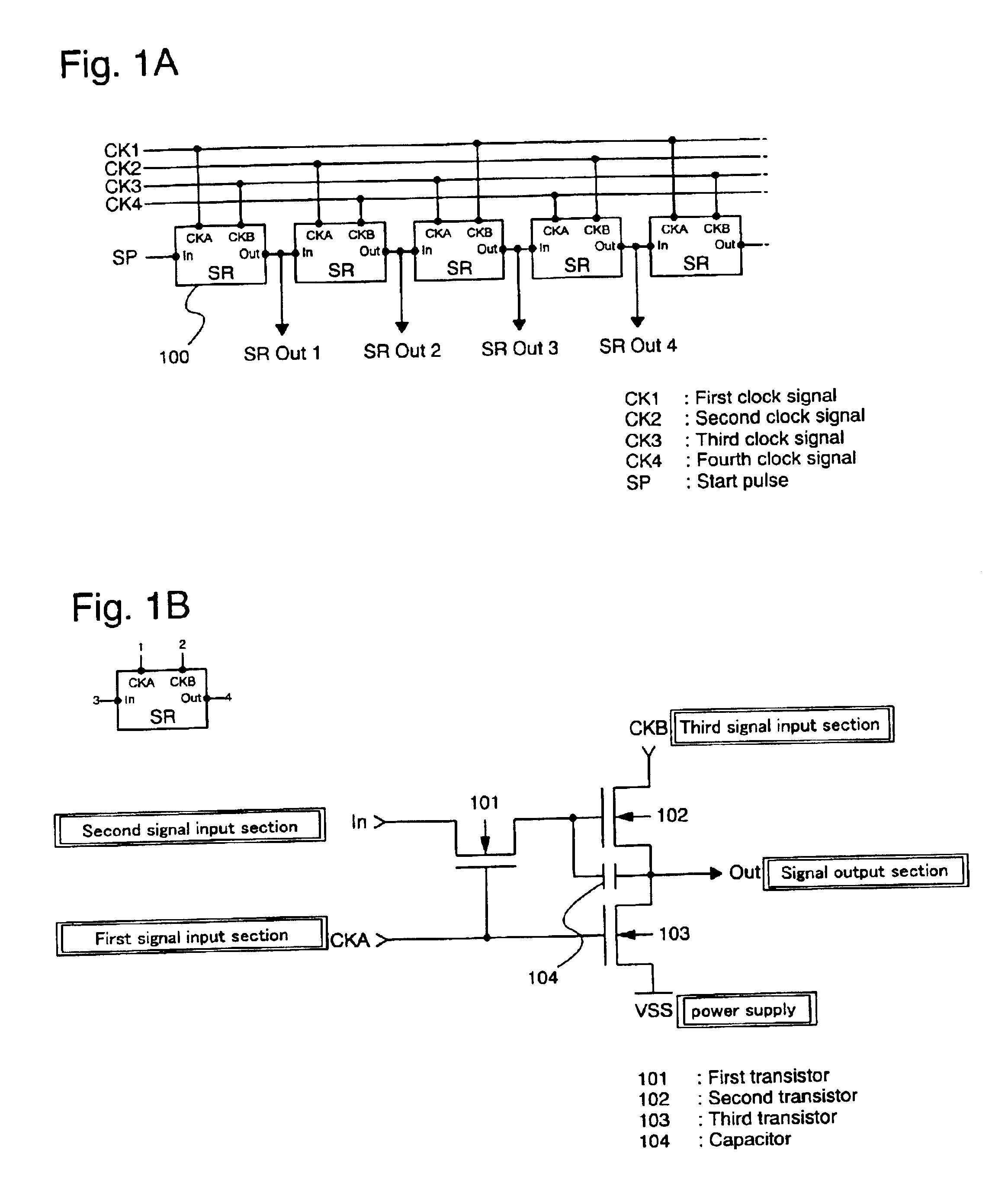

Pulse output circuit, shift register, and display device

InactiveUS6928136B2Low costReduce manufacturing stepsTransistorLogic circuits characterised by logic functionElectricityShift register

A circuit is provided which is constituted by TFTs of one conductivity type, and which is capable of outputting signals of a normal amplitude. When an input clock signal CK1 becomes a high level, each of TFTs (101, 103) is turned on to settle at a low level the potential at a signal output section (Out). A pulse is then input to a signal input section (In) and becomes high level. The gate potential of TFT (102) is increased to (VDD−V thN) and the gate is floated. TFT (102) is thus turned on. Then CK1 becomes low level and each of TFTs (101, 103) is turned off. Simultaneously, CK3 becomes high level and the potential at the signal output section is increased. Simultaneously, the potential at the gate of TFT (102) is increased to a level equal to or higher than (VDD+V thN) by the function of capacitor (104), so that the high level appearing at the signal output section (Out) becomes equal to VDD. When SP becomes low level; CK3 becomes low level; and CK1 becomes high level, the potential at the signal output section (Out) becomes low level again.

Owner:SEMICON ENERGY LAB CO LTD

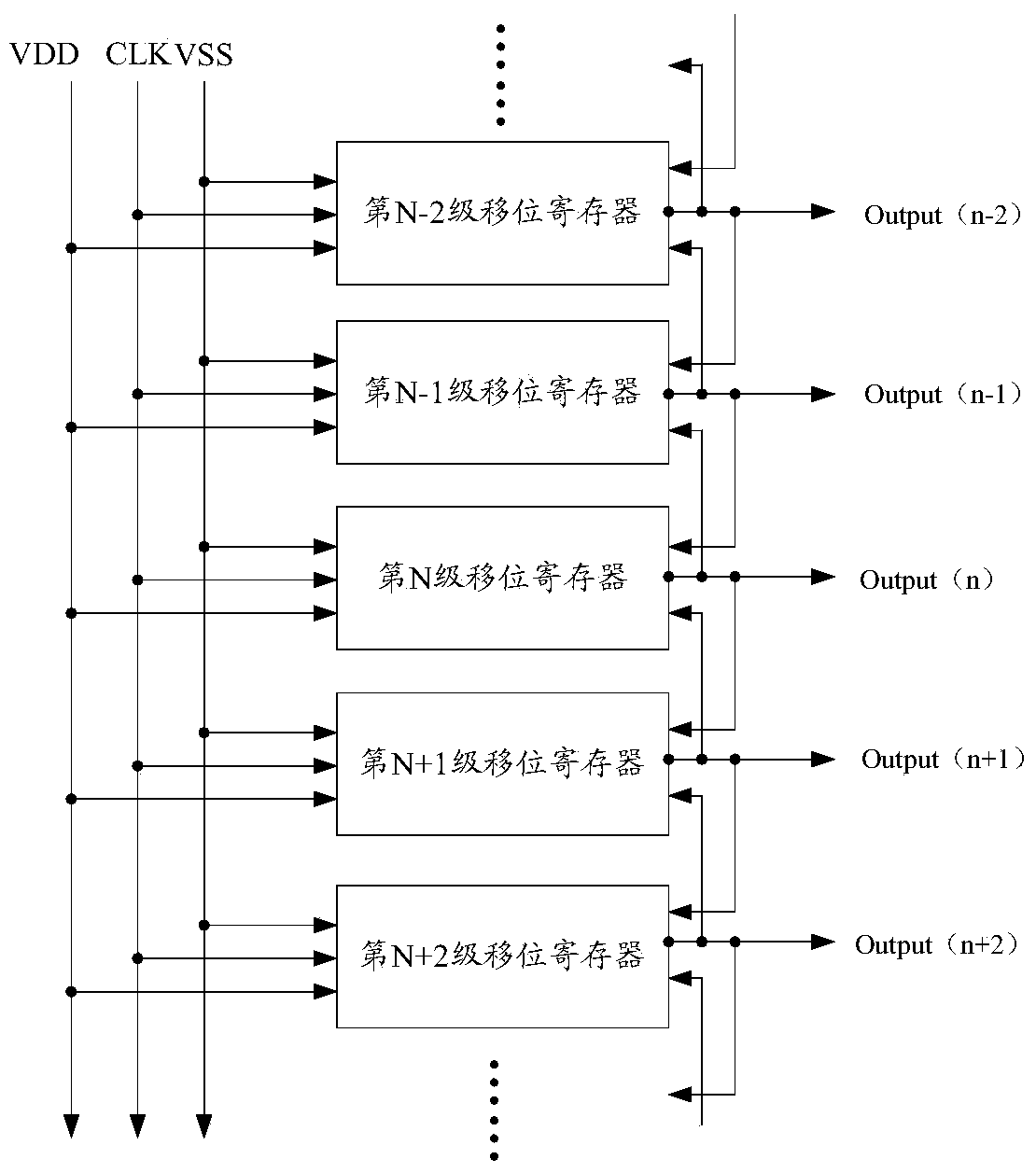

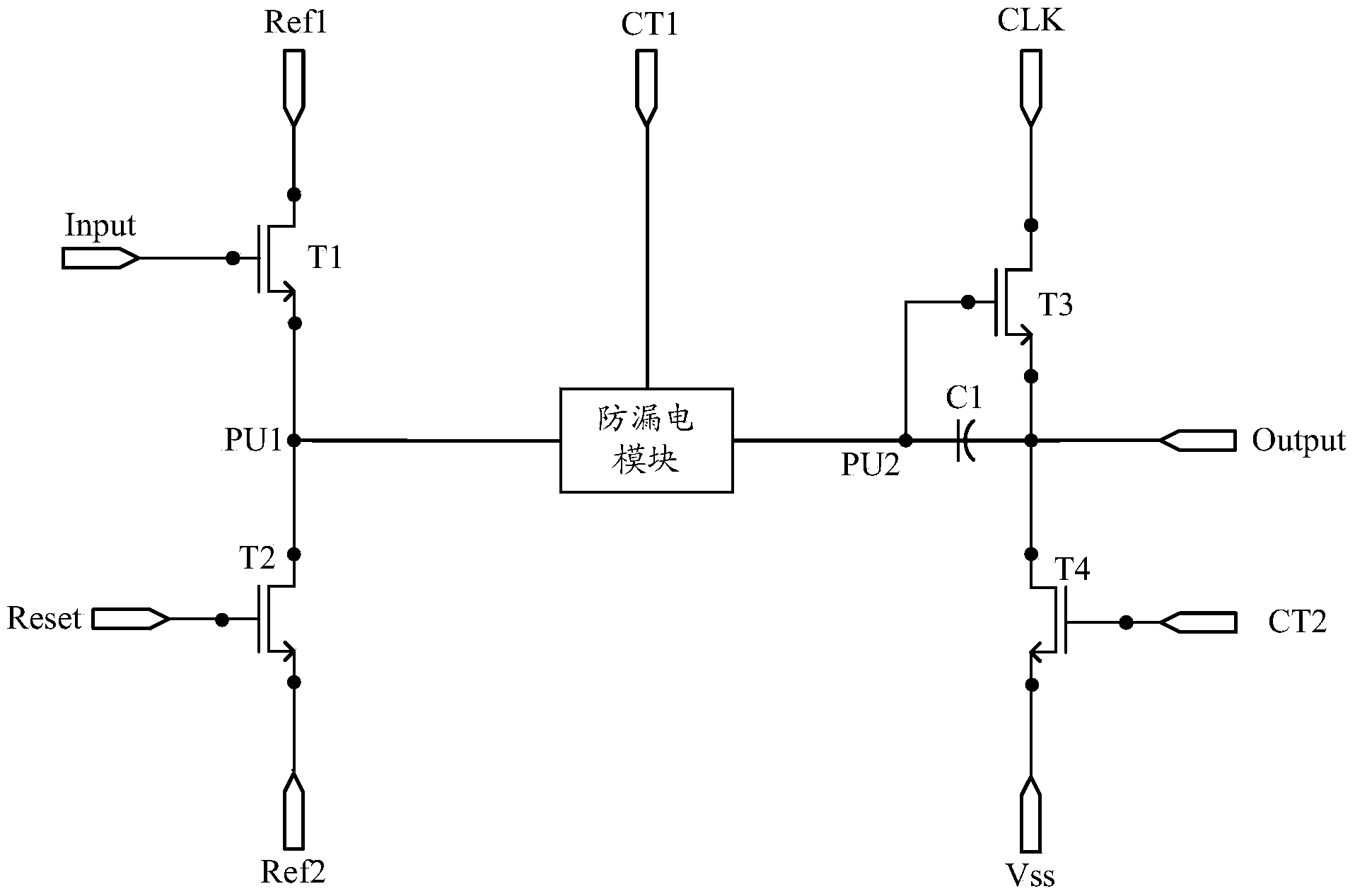

Shifting register, grid integration drive circuit and display screen

ActiveCN104021769AShorten the timeReduce leakage speedStatic indicating devicesDigital storageCapacitanceShift register

The invention discloses a shifting register, a grid integration drive circuit and a display screen. The joint of a source of a first thin film transistor and a drain of a second thin film transistor is set as a first upward-pull node, the joint of a capacitor and a grid of a third thin film transistor is set as a second upward-pull node, and a electric leakage prevention module is added between the first upward-pull node and the second upward-pull node; the first upward-pull node and the second upward-pull node are connected in display time duration of a frame through the electric leakage prevention module under the control of a display control signal end so that a grid startup signal can be normally outputted by the shifting register; the first upward-pull node and the second upward-pull node are disconnected in the touch control time duration of the frame, that is, a resistor with large resistance is connected to a discharge path of the capacitor in series, and therefore time of the capacitor for discharge can be greatly shortened, the electric leakage speed of the capacitor is effectively decreased, and the problem that normal display may not be achieved when the capacitor is applied to a touch screen with high report rate is solved.

Owner:BOE TECH GRP CO LTD +1

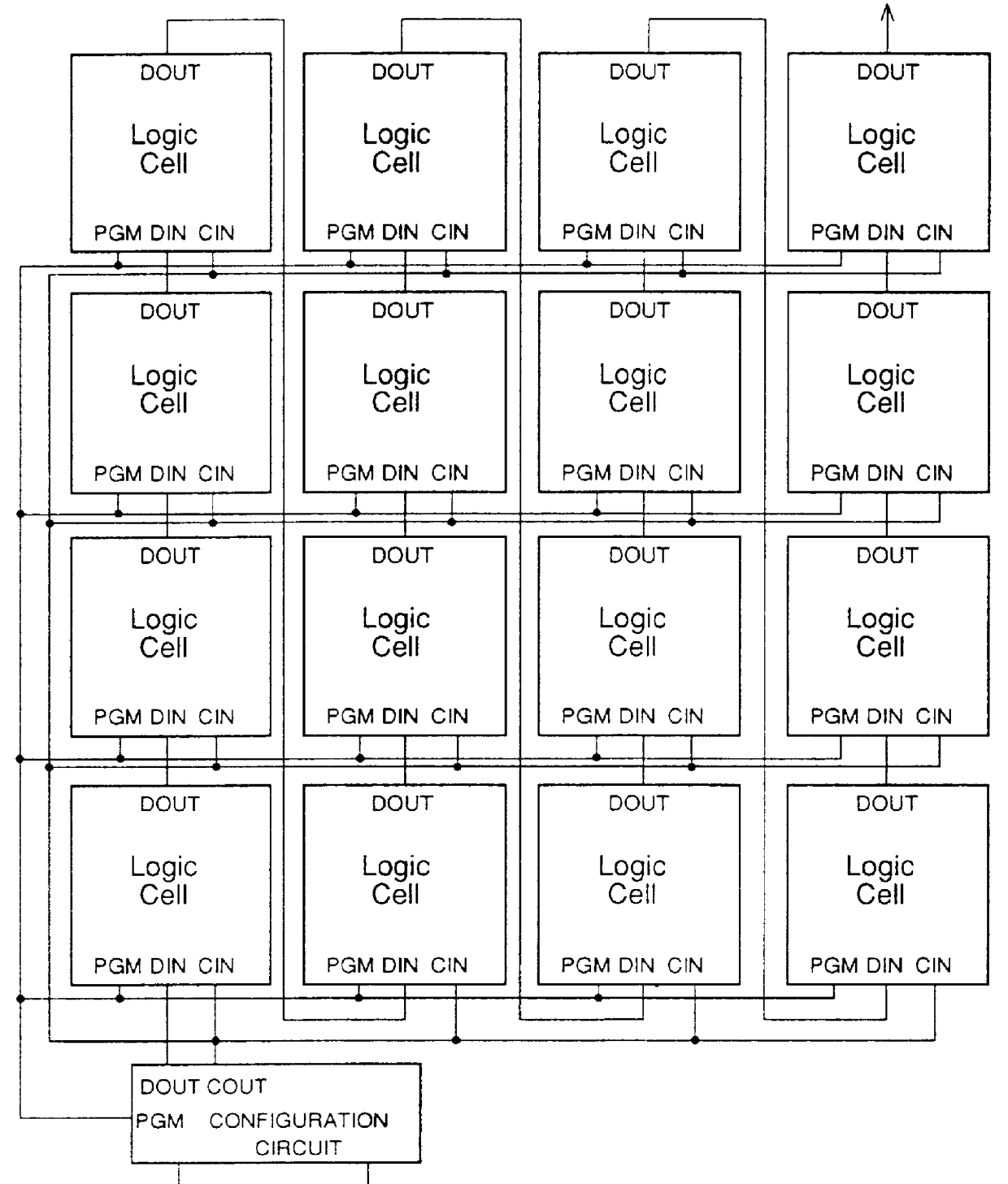

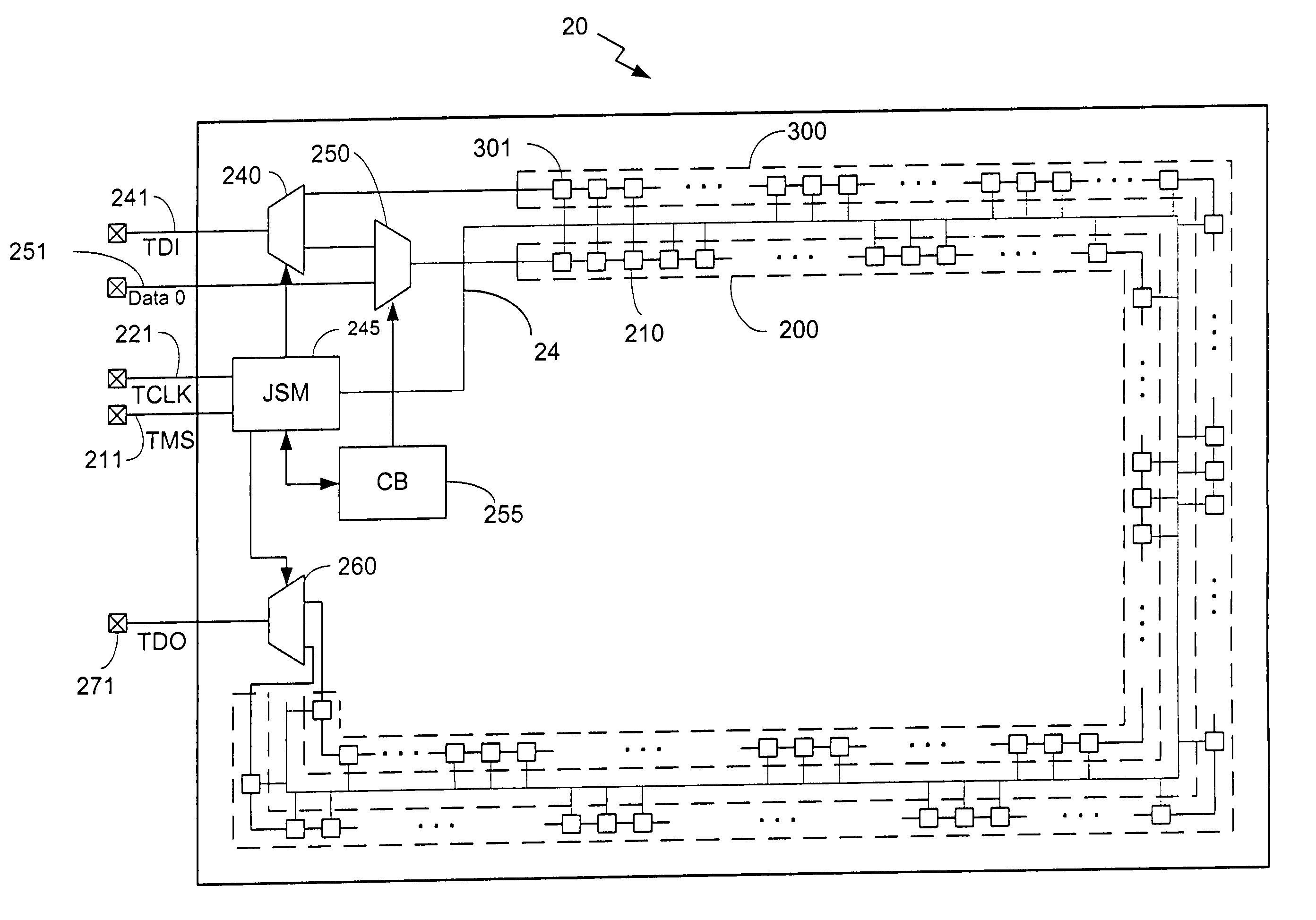

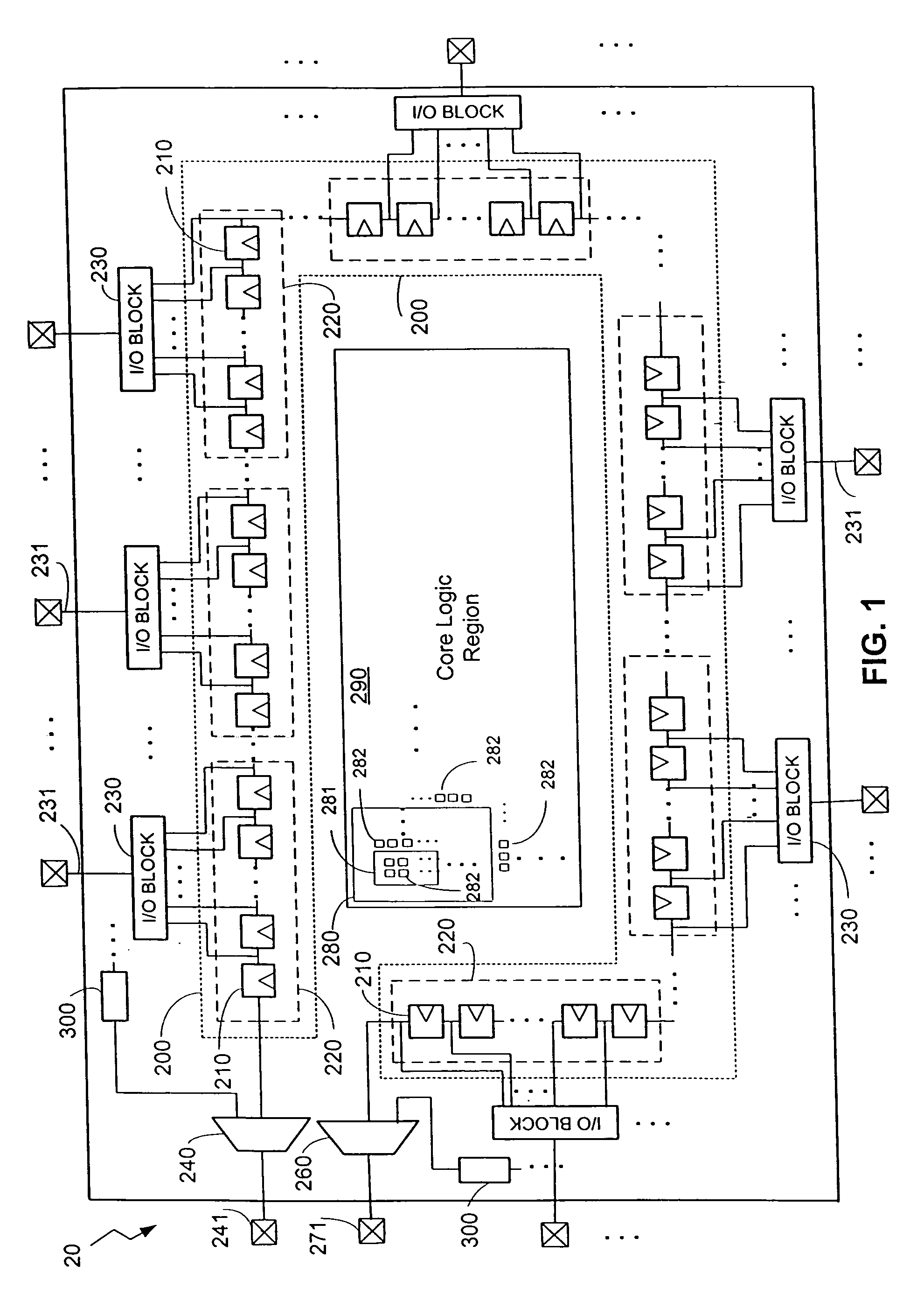

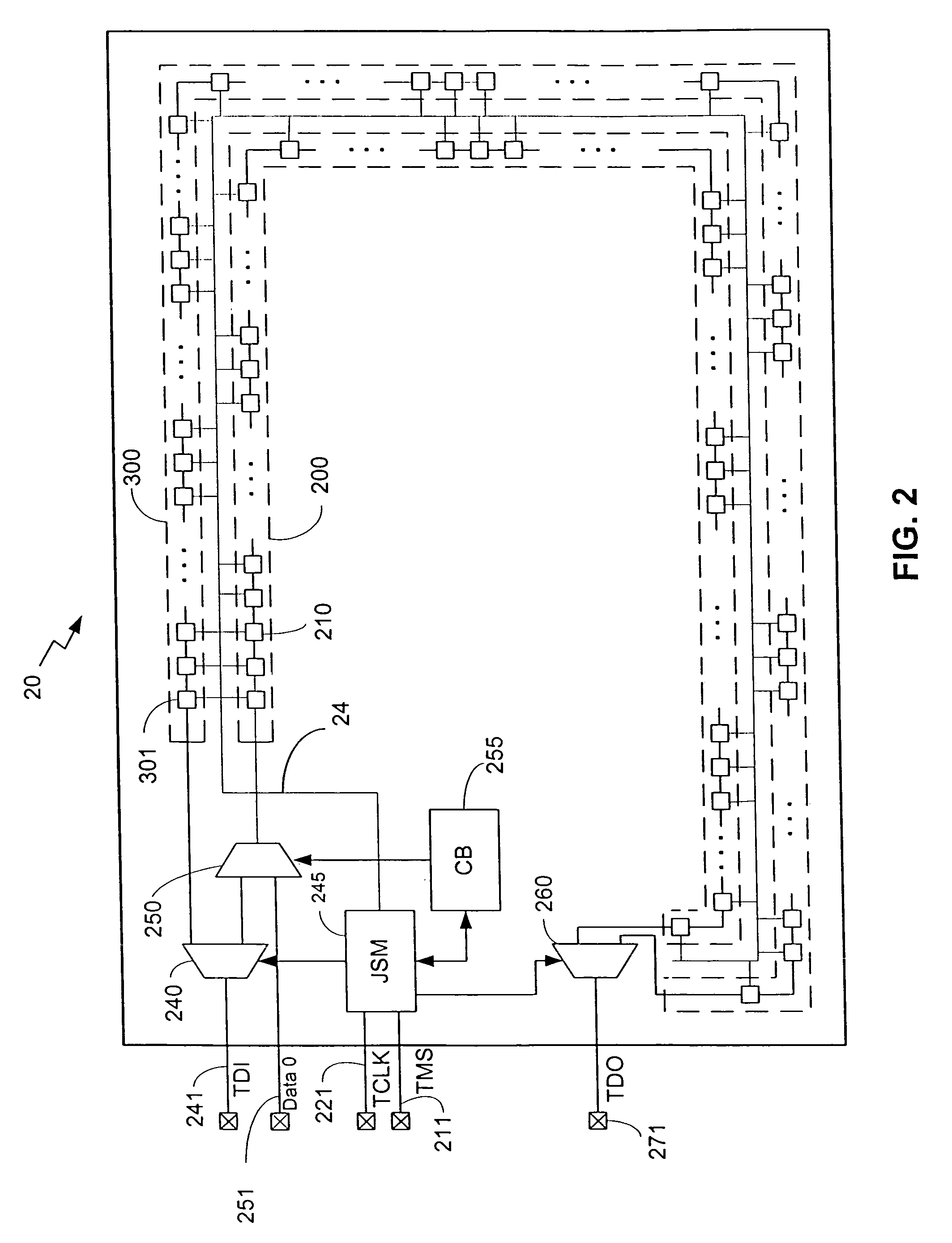

Configuration shift register

InactiveUS7112992B1Quickly reconfiguredSolid-state devicesLogic circuits using elementary logic circuit componentsShift registerElectronic equipment

An electronic device comprises a first plurality of configuration elements connected as a shift register for programming a subset of the programmable functions of the electronic device. The subset of programmable functions may be reprogrammed by loading configuration data into the first plurality of configuration elements such that the subset of programmable functions may be reprogrammed without necessarily reprogramming other programmable functions of the electronic device.

Owner:ALTERA CORP

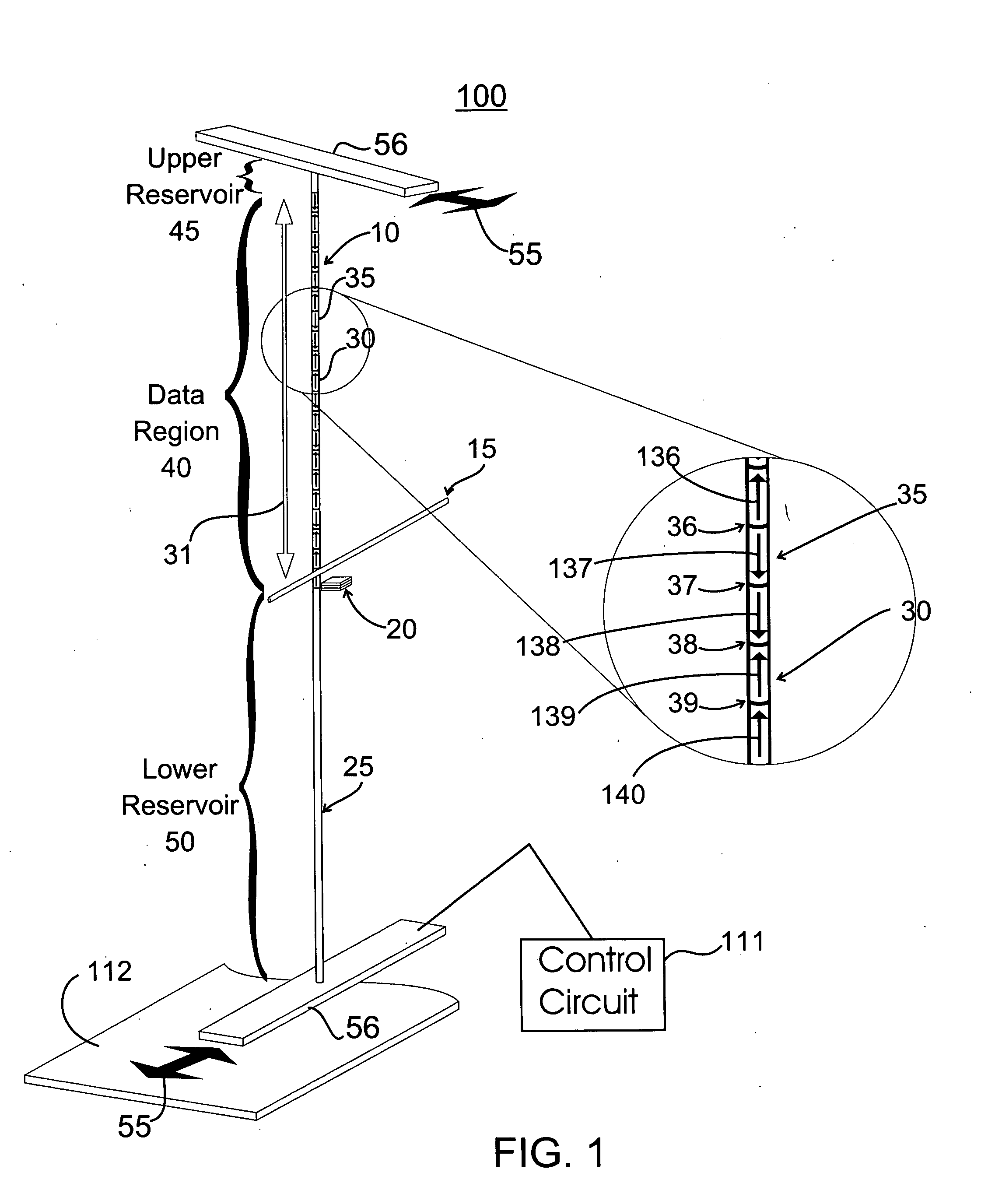

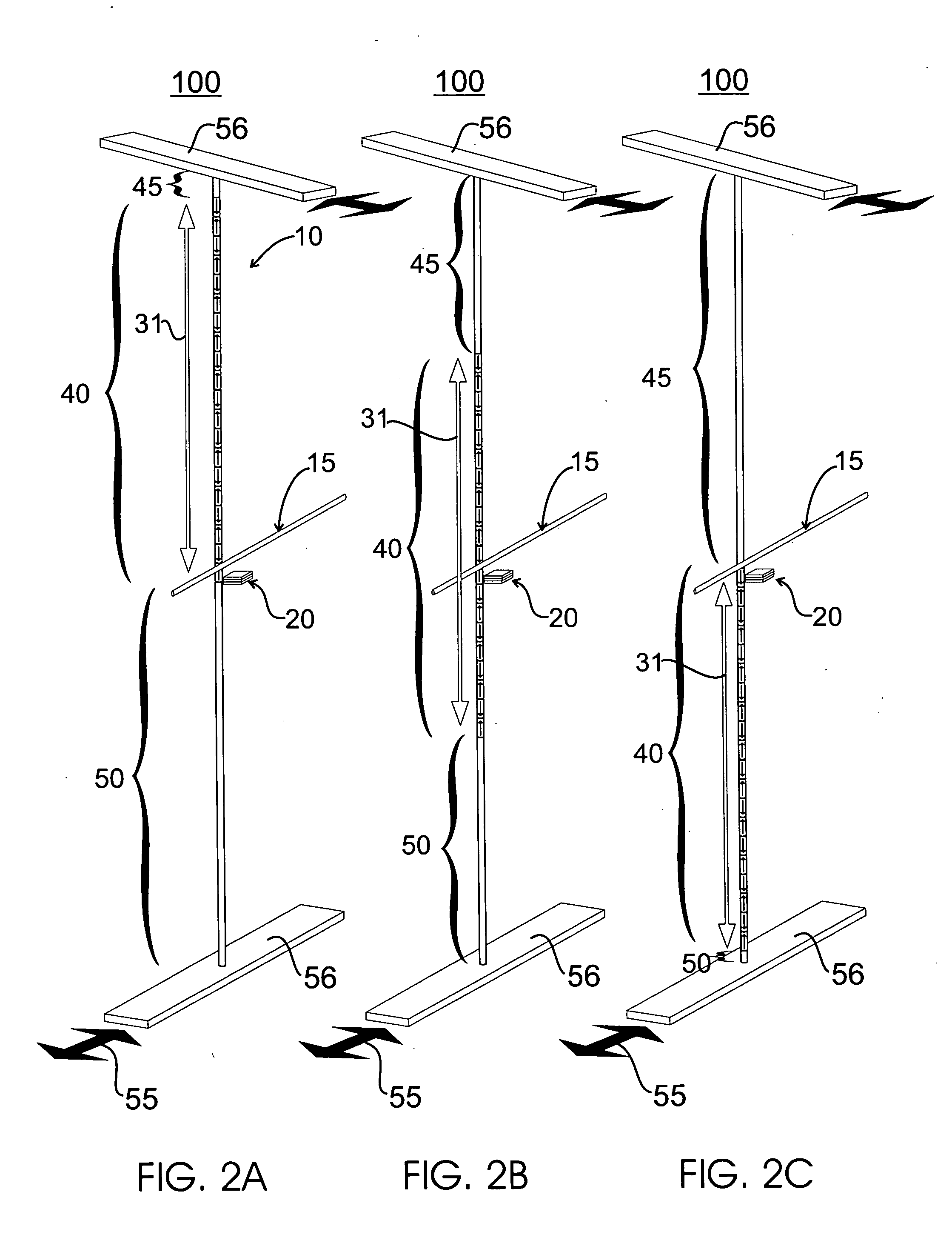

System and method for writing to a magnetic shift register

InactiveUS6898132B2Variable capacityHigh cost of readingLiquid applicationDigital storageShift registerMolecular physics

A writing device can change the direction of the magnetic moment in a magnetic shift register, thus writing information to the domains or bits in the magnetic shift register. Associated with each domain wall are large magnetic fringing fields. The domain wall concentrates the change in magnetism from one direction to another in a very small space. Depending on the nature of the domain wall, very large dipolar fringing fields can emanate from the domain wall. This characteristic of magnetic domains is used to write to the magnetic shift register. When the domain wall is moved close to another magnetic material, the large fields of the domain wall change the direction of the magnetic moment in the magnetic material, effectively “writing” to the magnetic material.

Owner:GLOBALFOUNDRIES US INC