Patents

Literature

66 results about "Bias stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

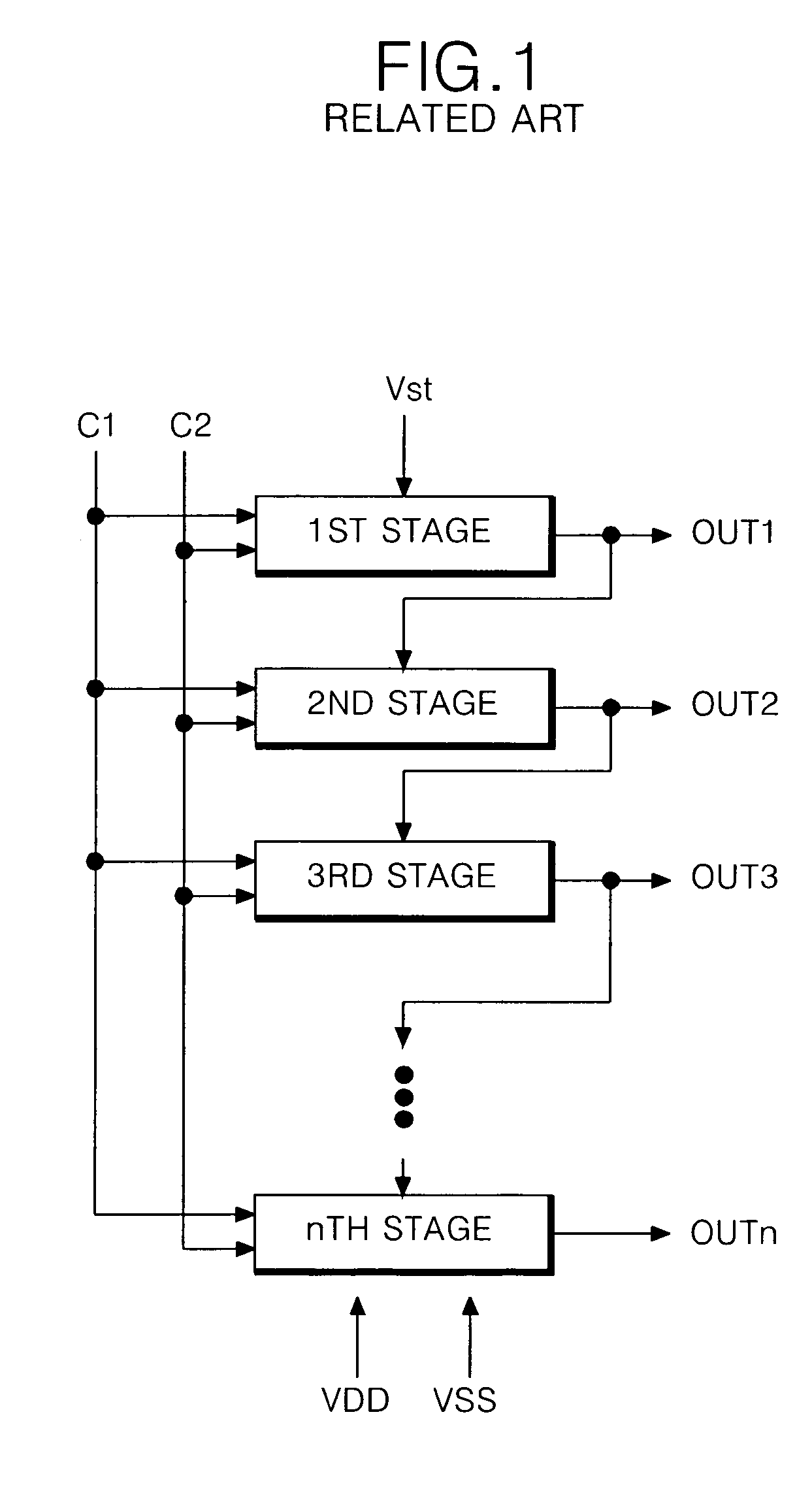

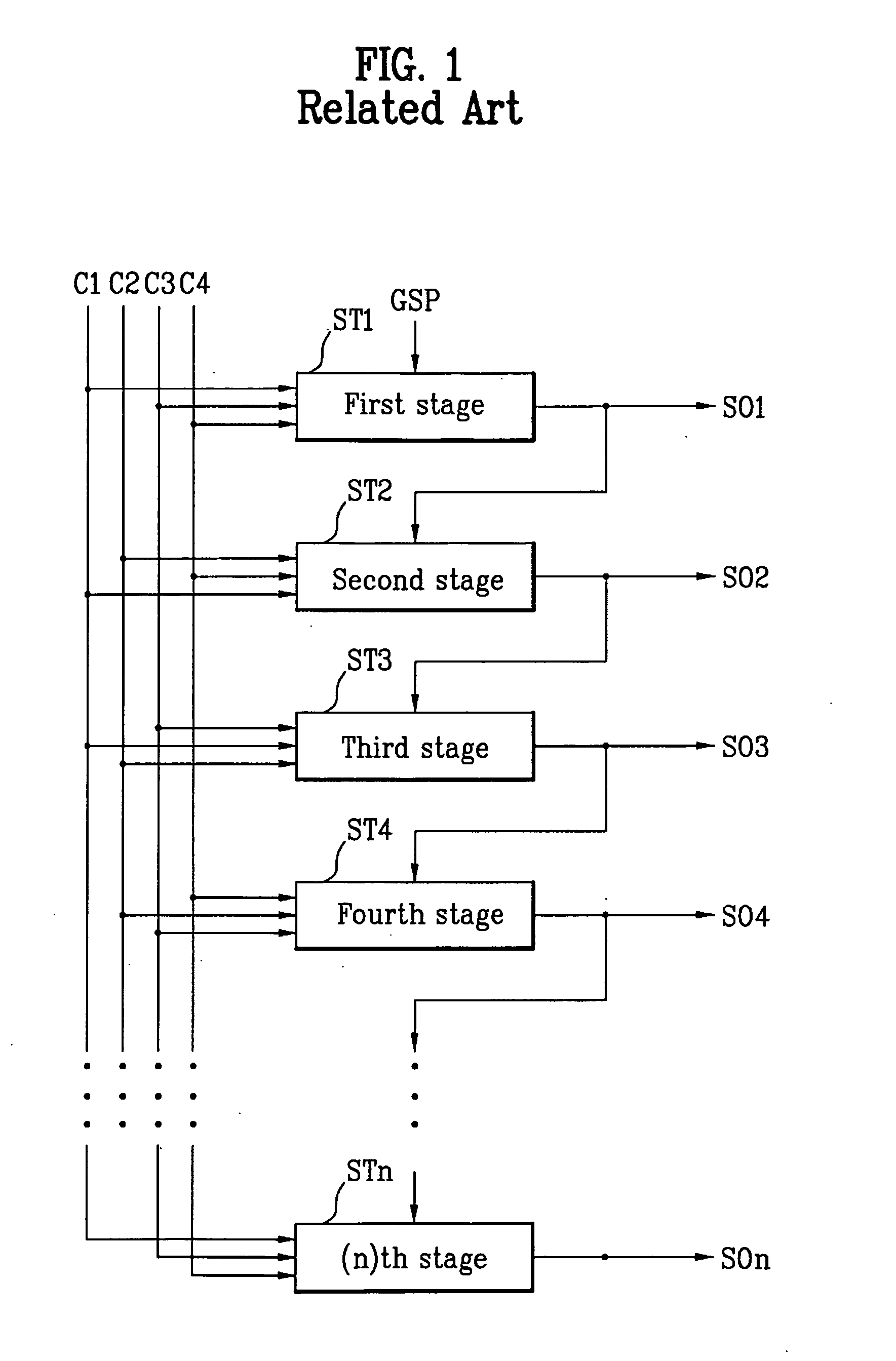

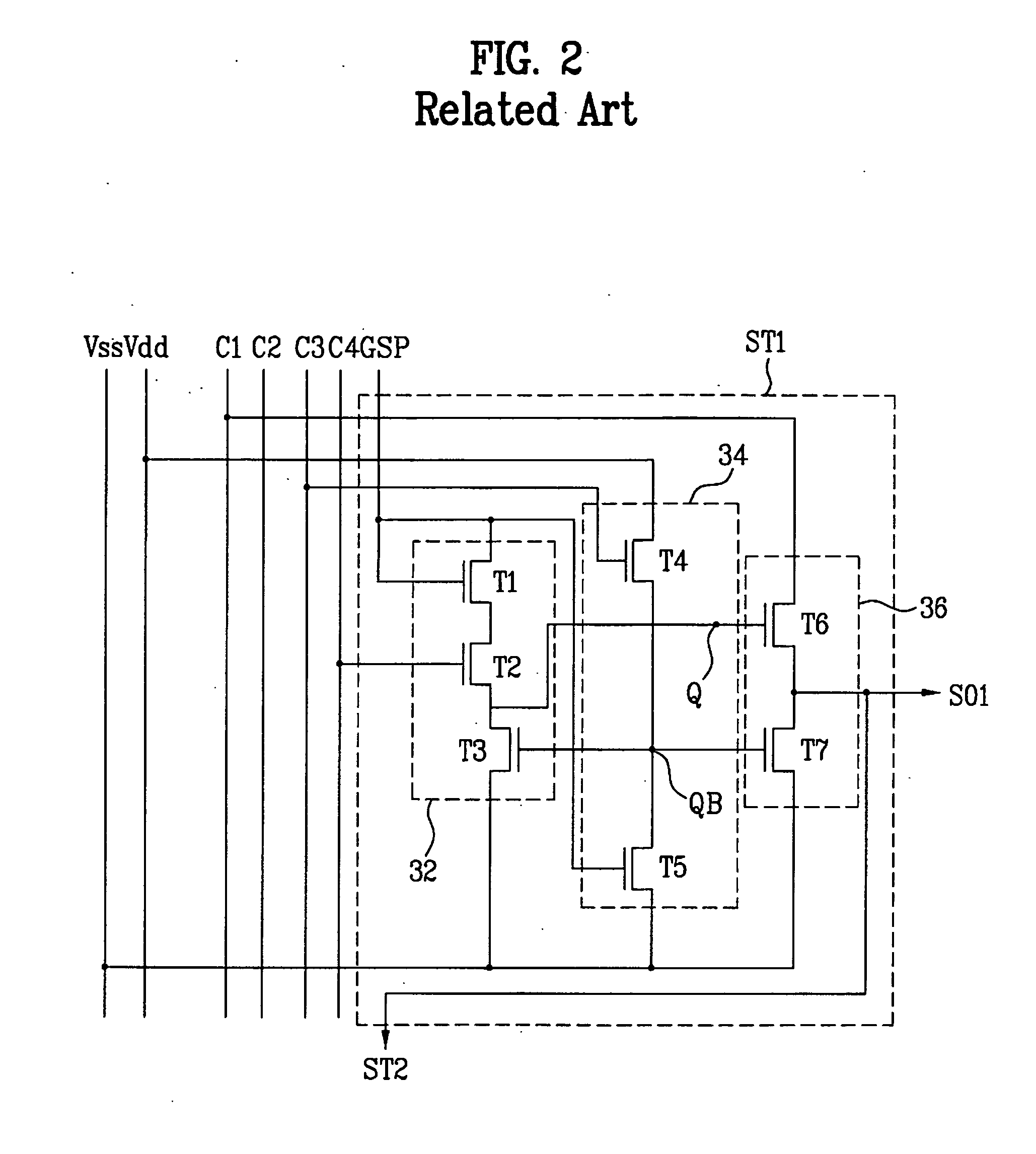

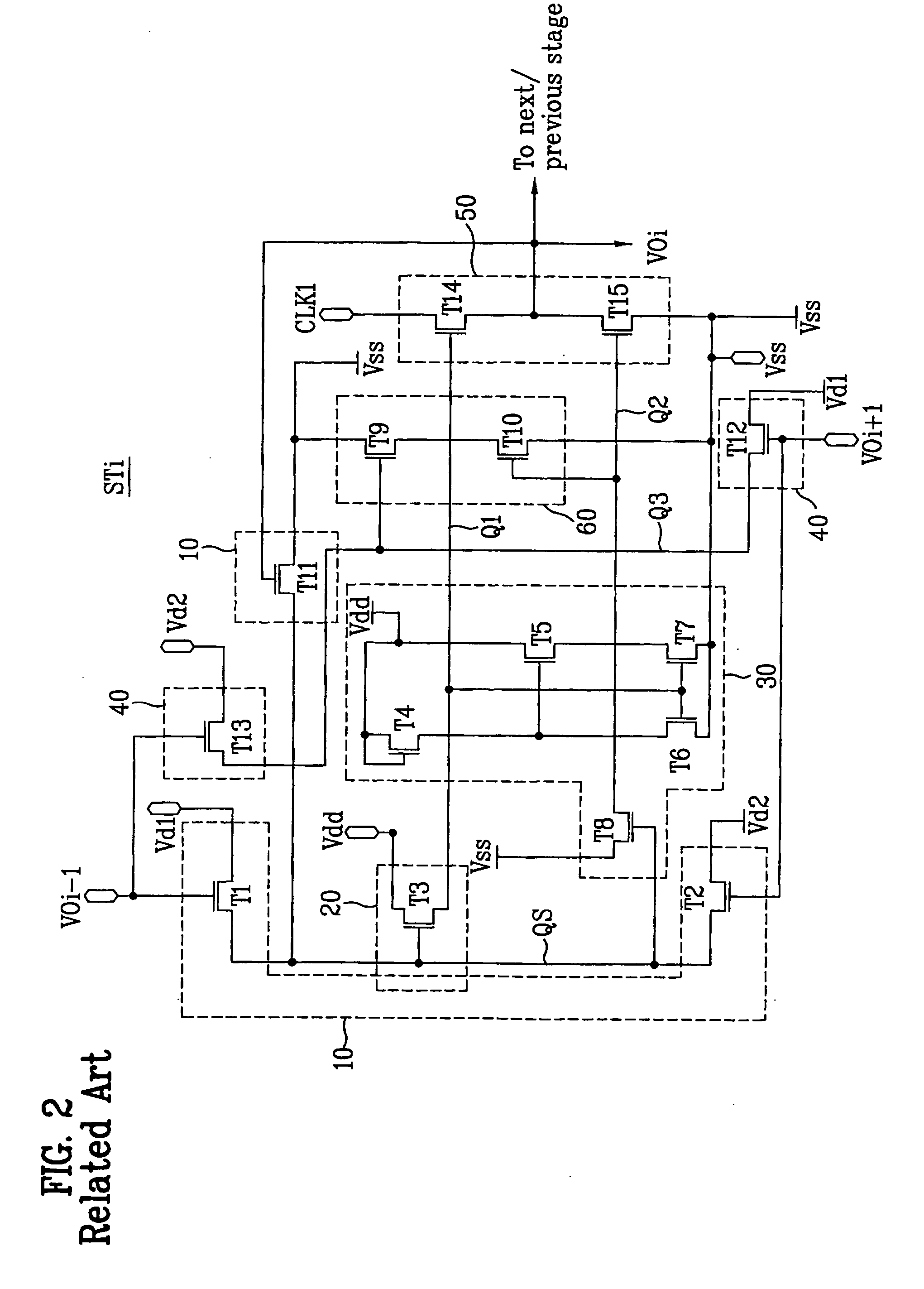

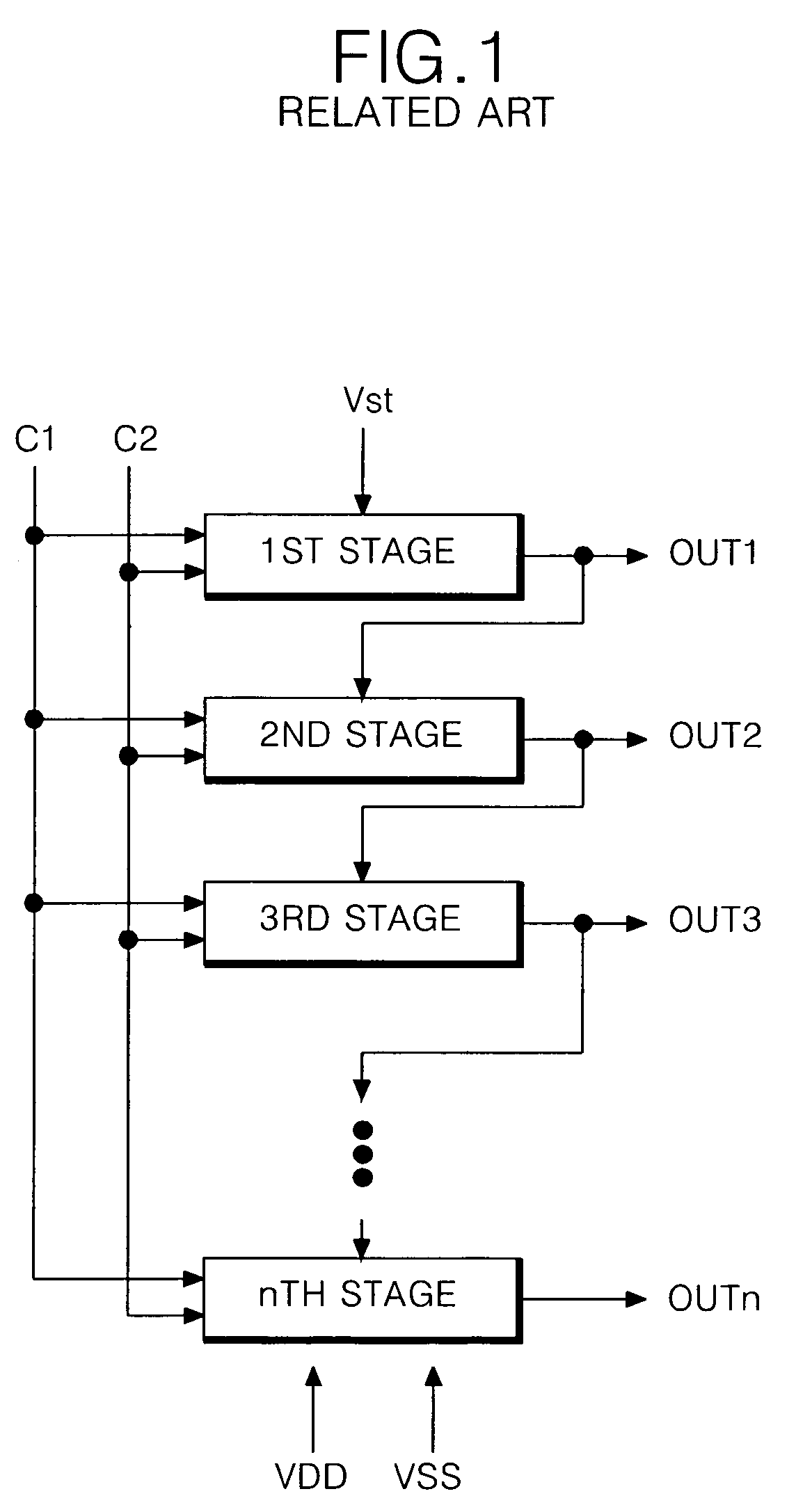

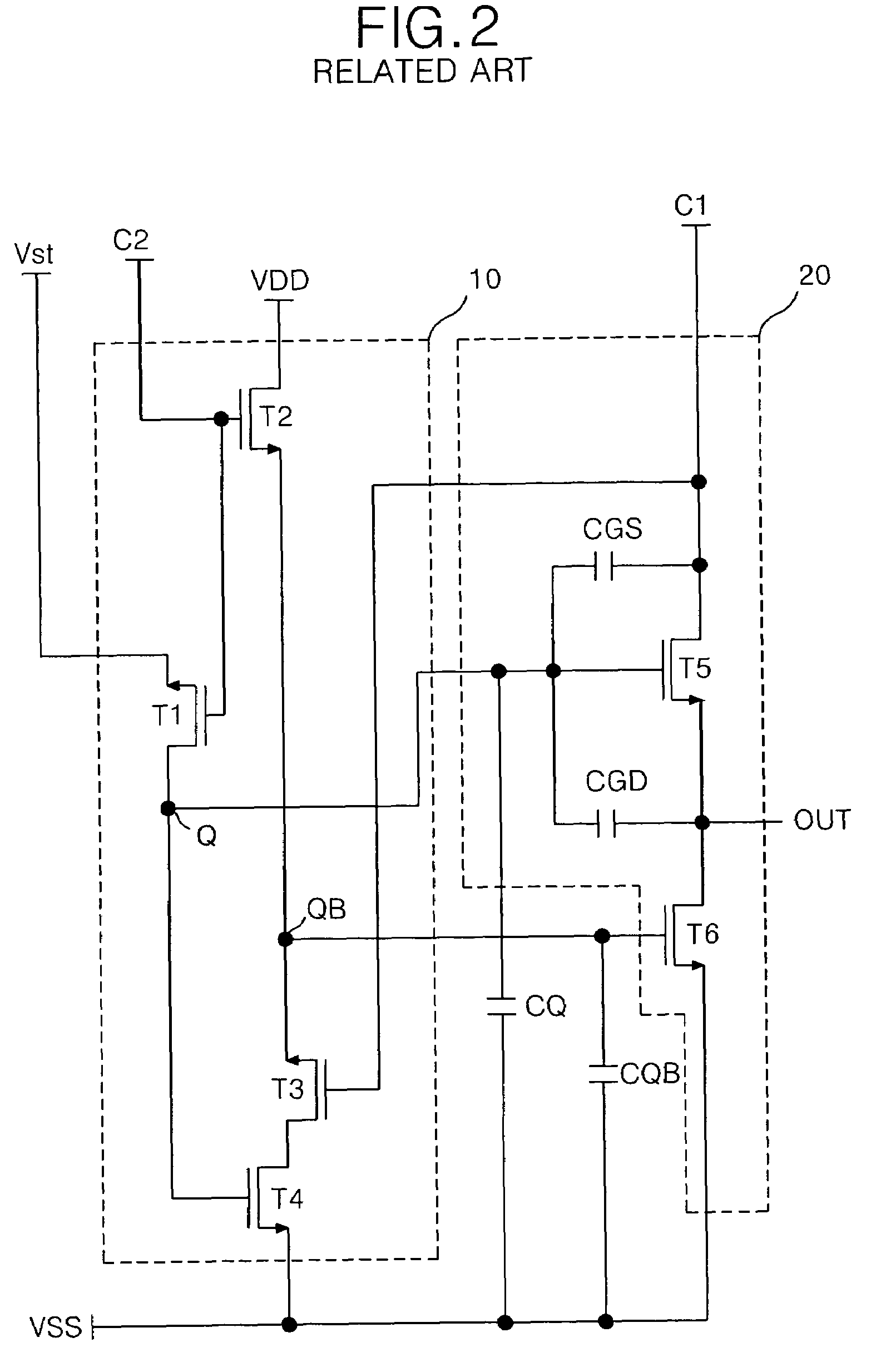

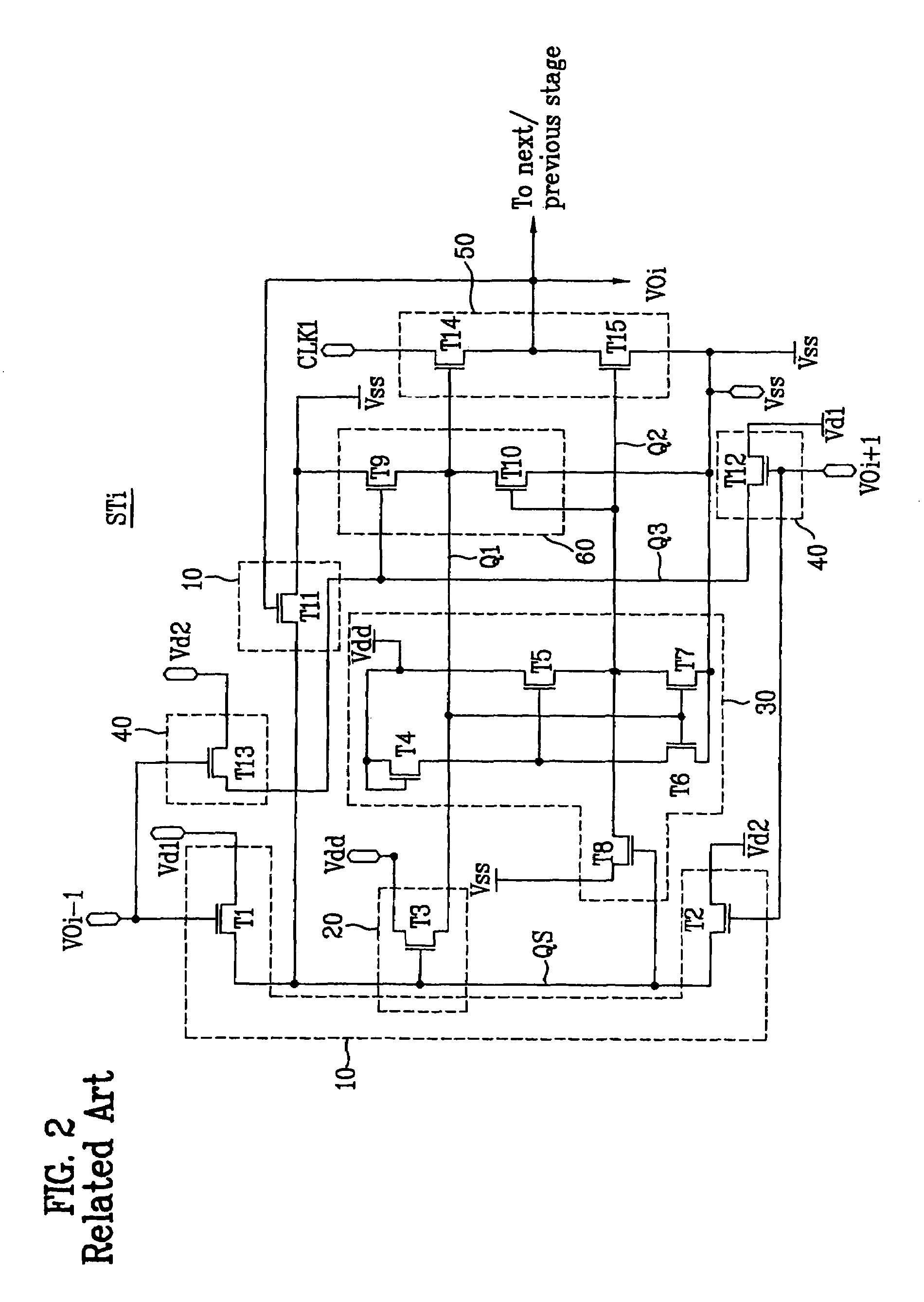

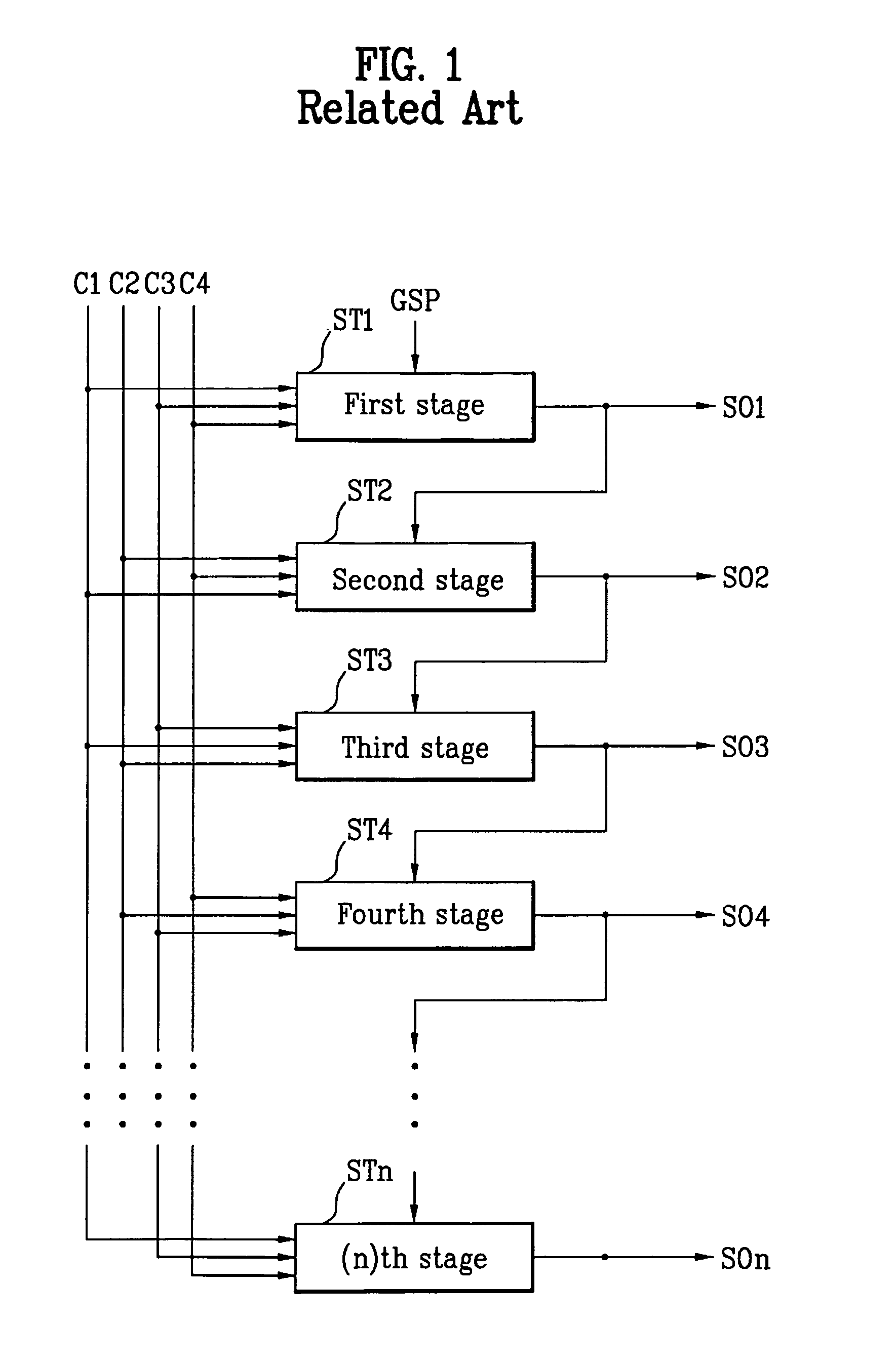

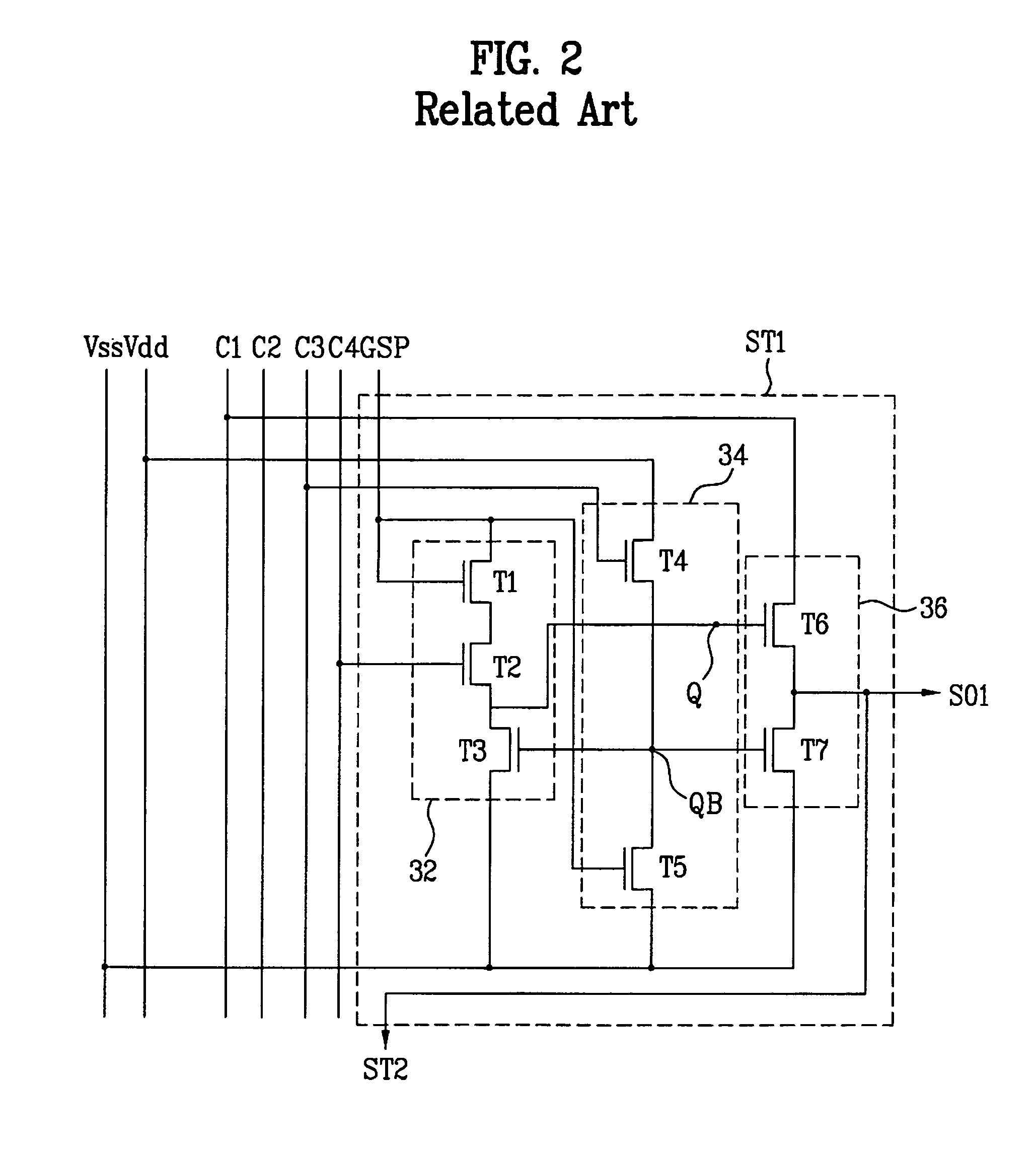

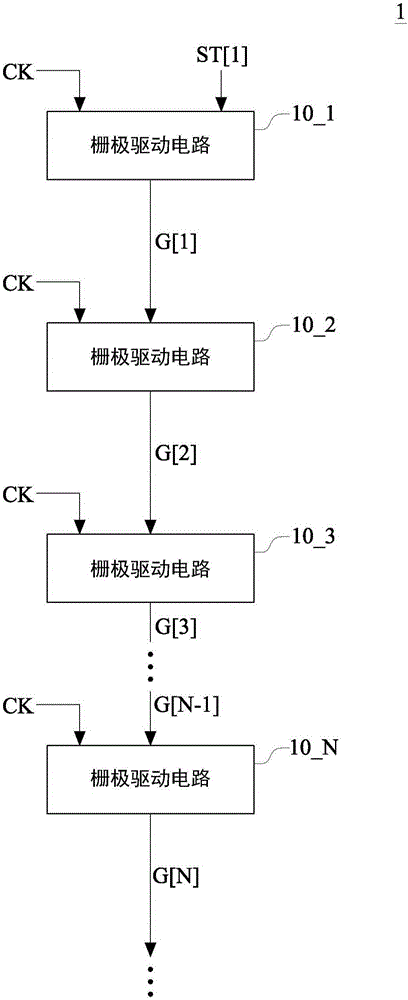

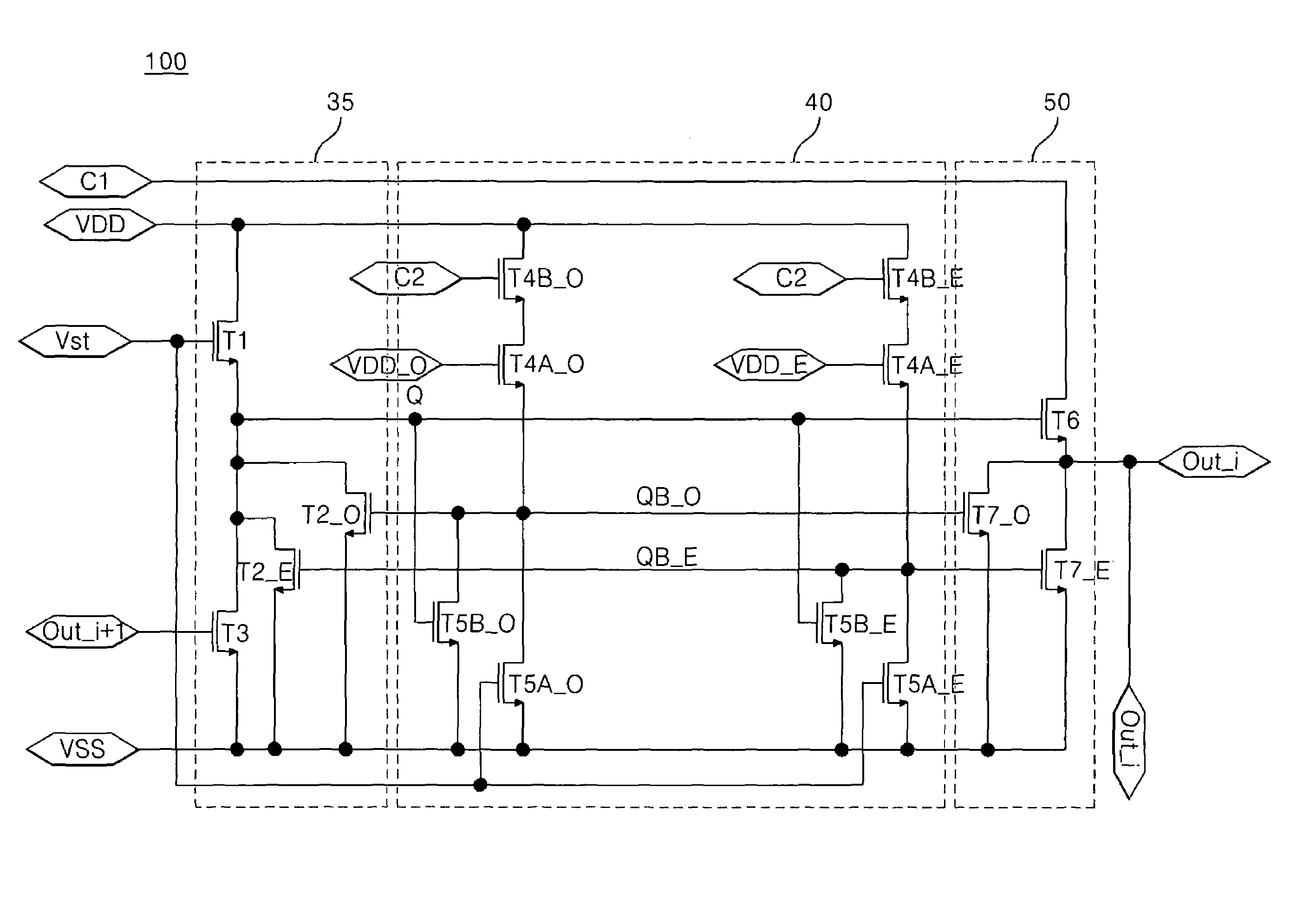

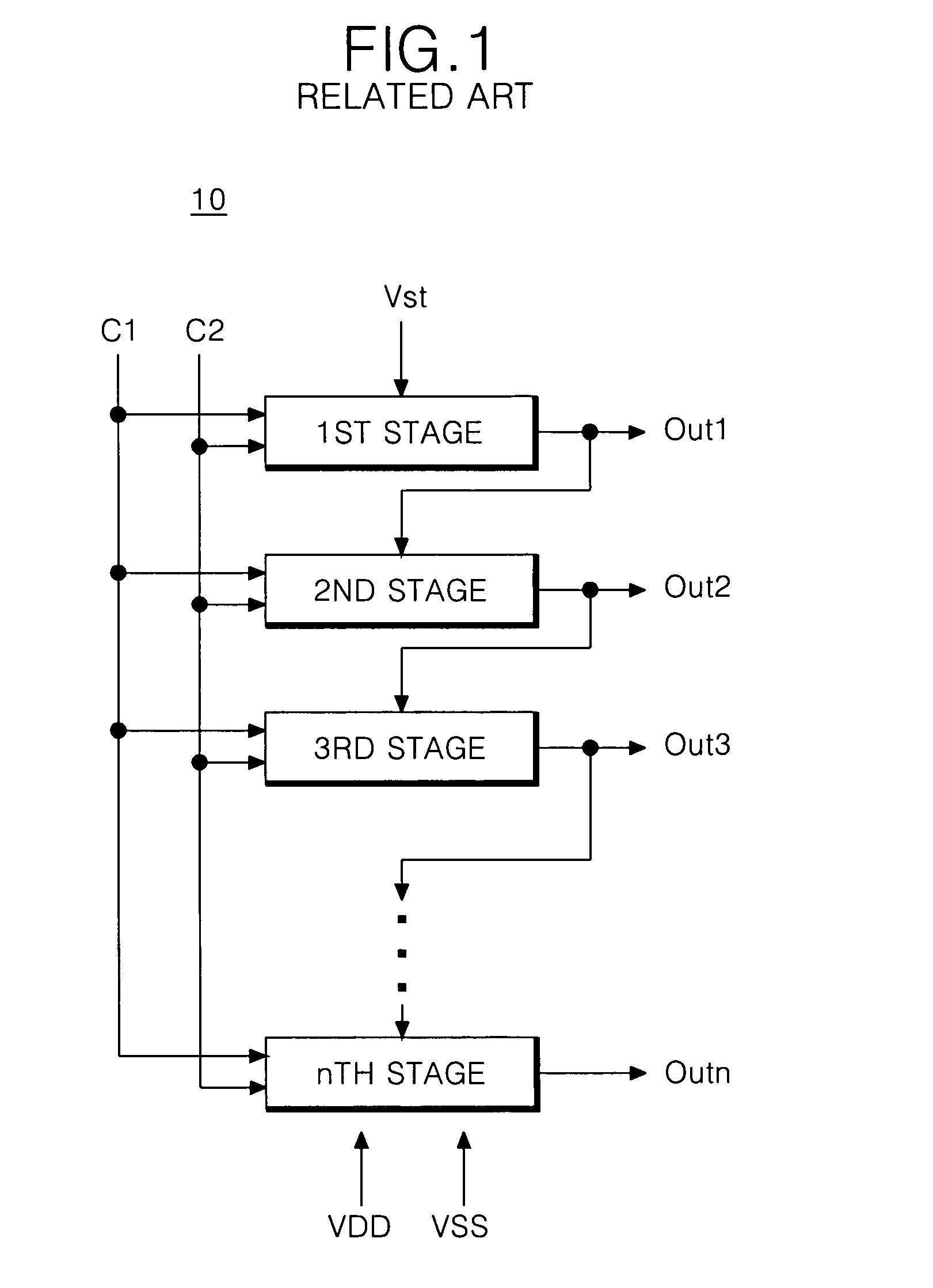

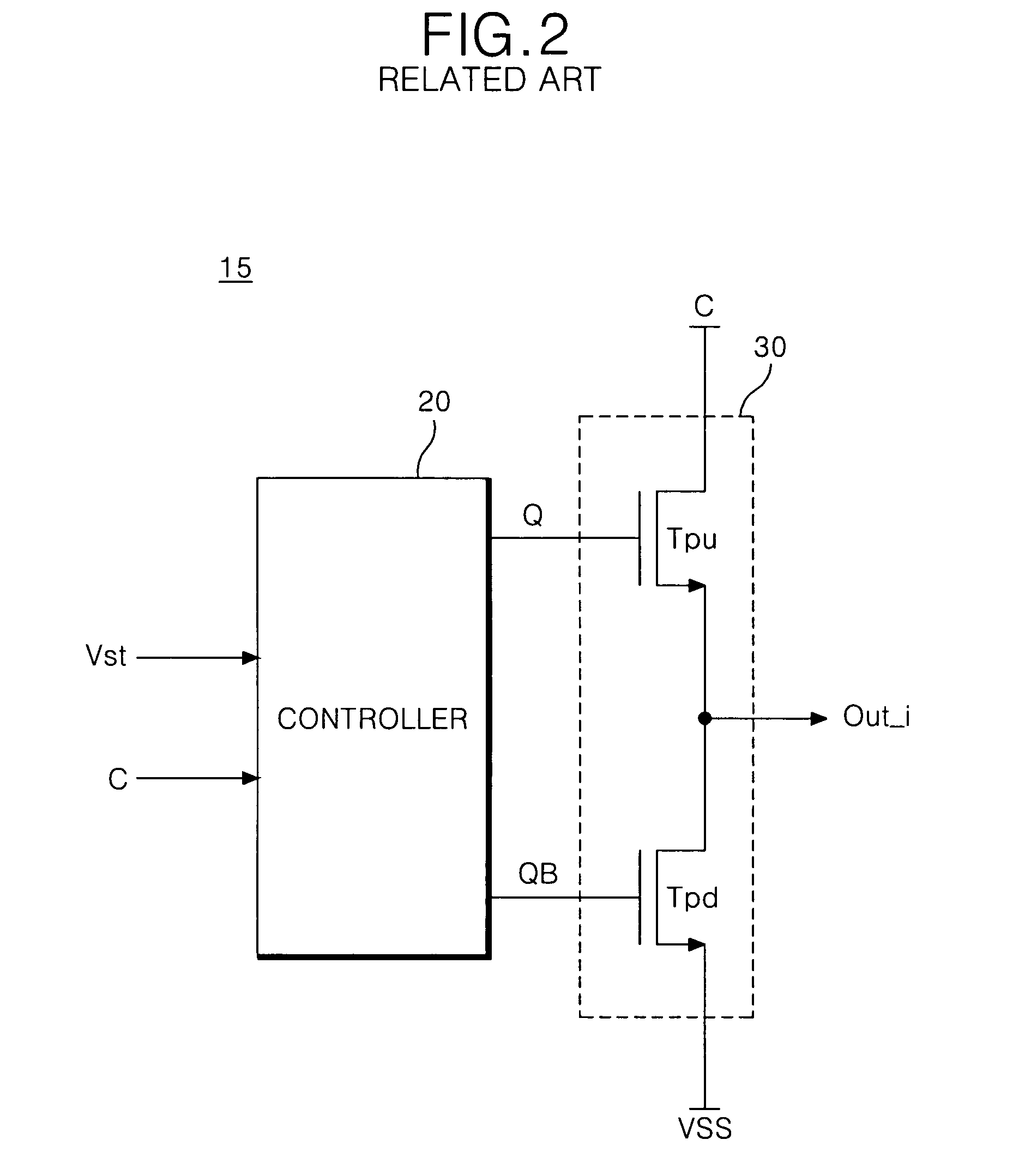

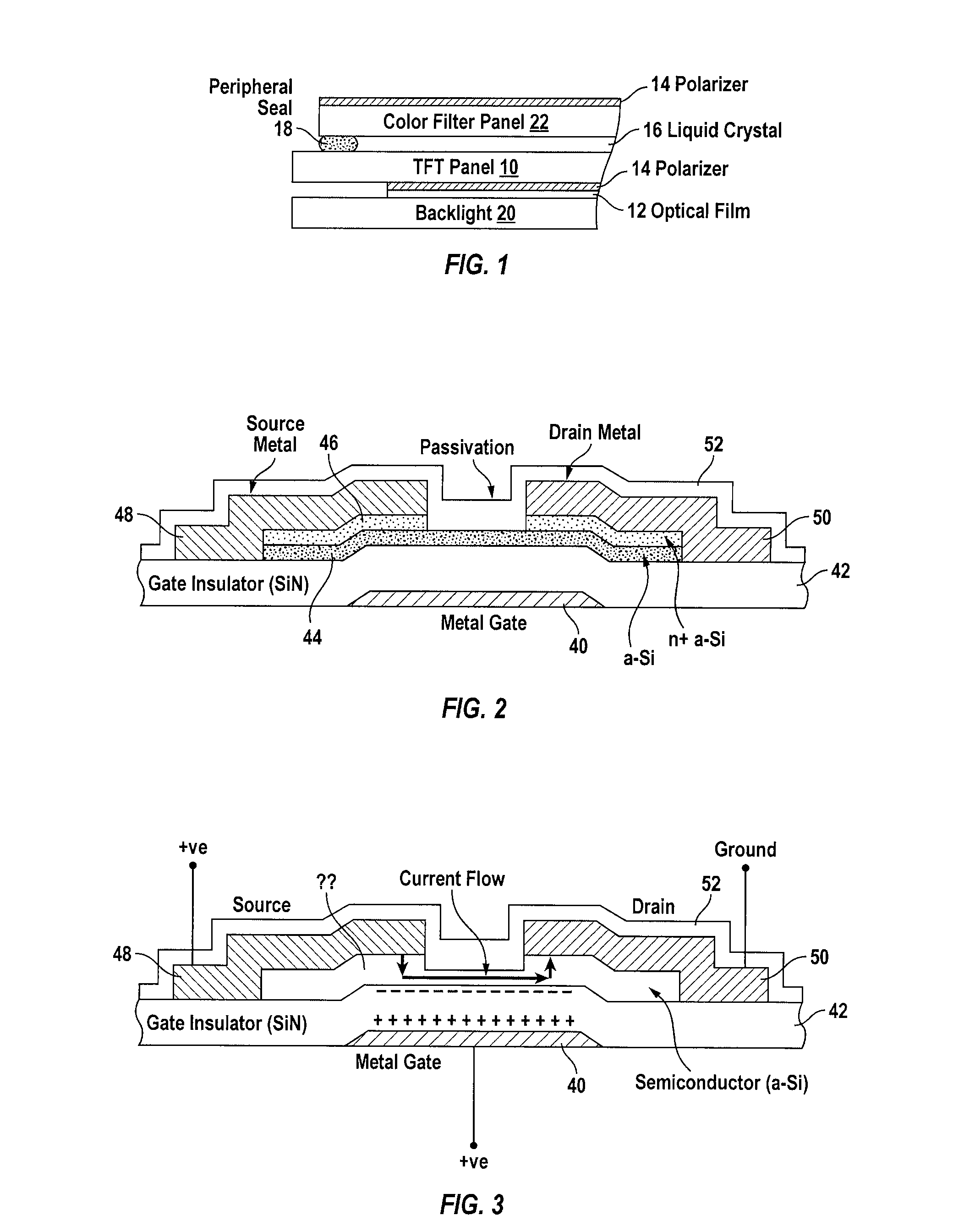

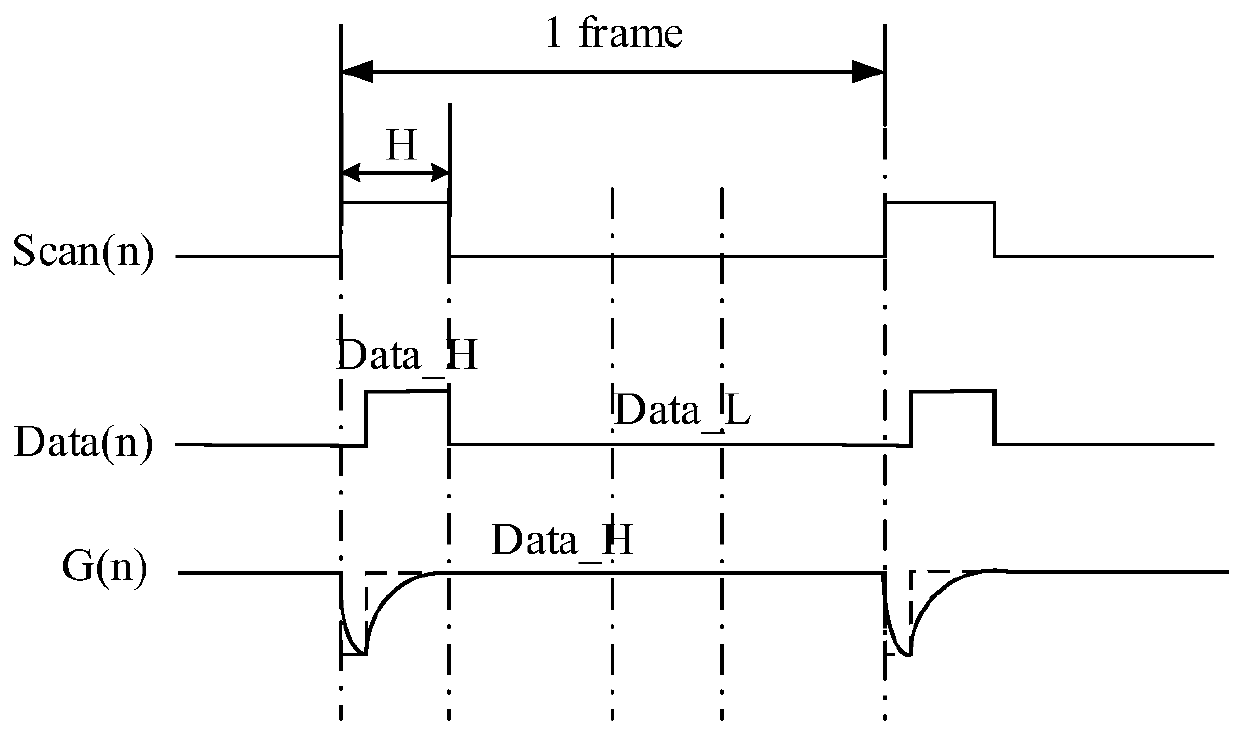

Shift register

Disclosed is a shift register capable of mitigating gate bias stress. The shift register, including a plurality of stages, includes an output buffer having a pull-up transistor and two pull-down transistors, each with gates connected to different nodes. One of the two pull-down transistors operates during an even frame portion of an LCD operation; and the other of the two pull-down transistors operates during an odd frame portion of the LCD display operation. Alternating operation of the pull-down transistors substantially mitigates gate stress, and substantially enables the shift register to be fabricated with amorphous silicon.

Owner:LG DISPLAY CO LTD

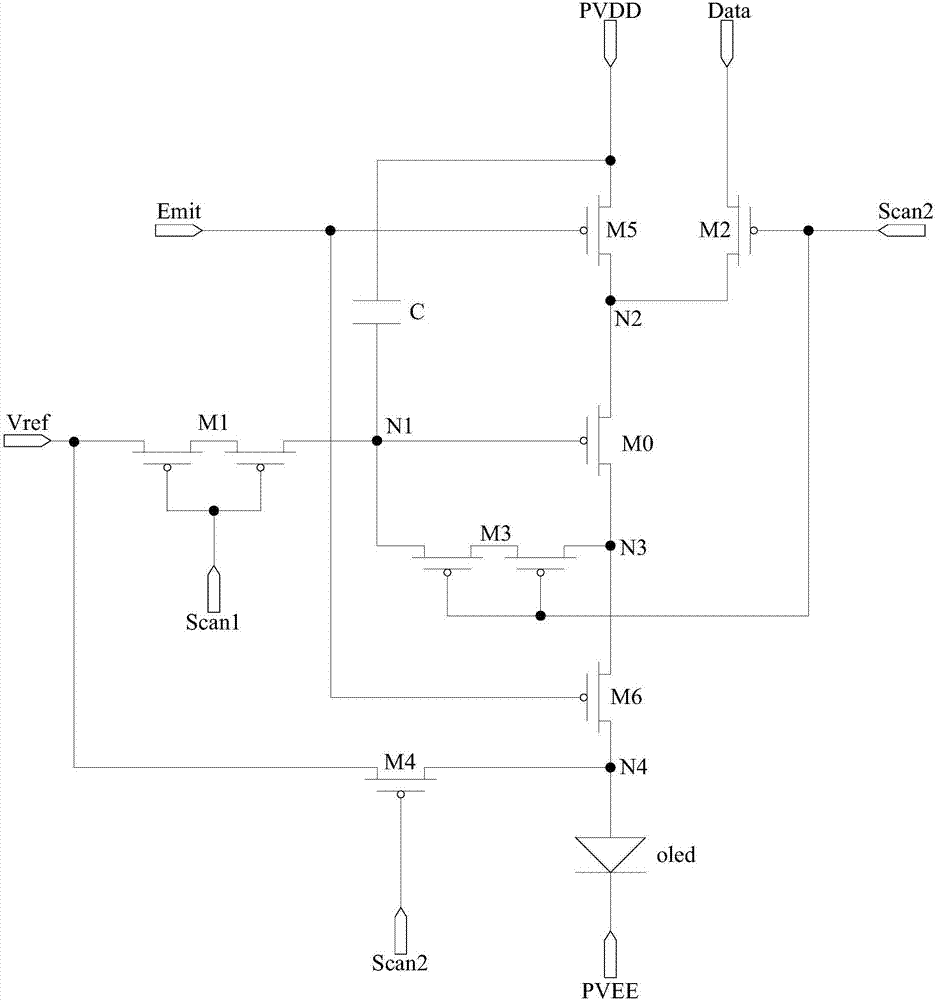

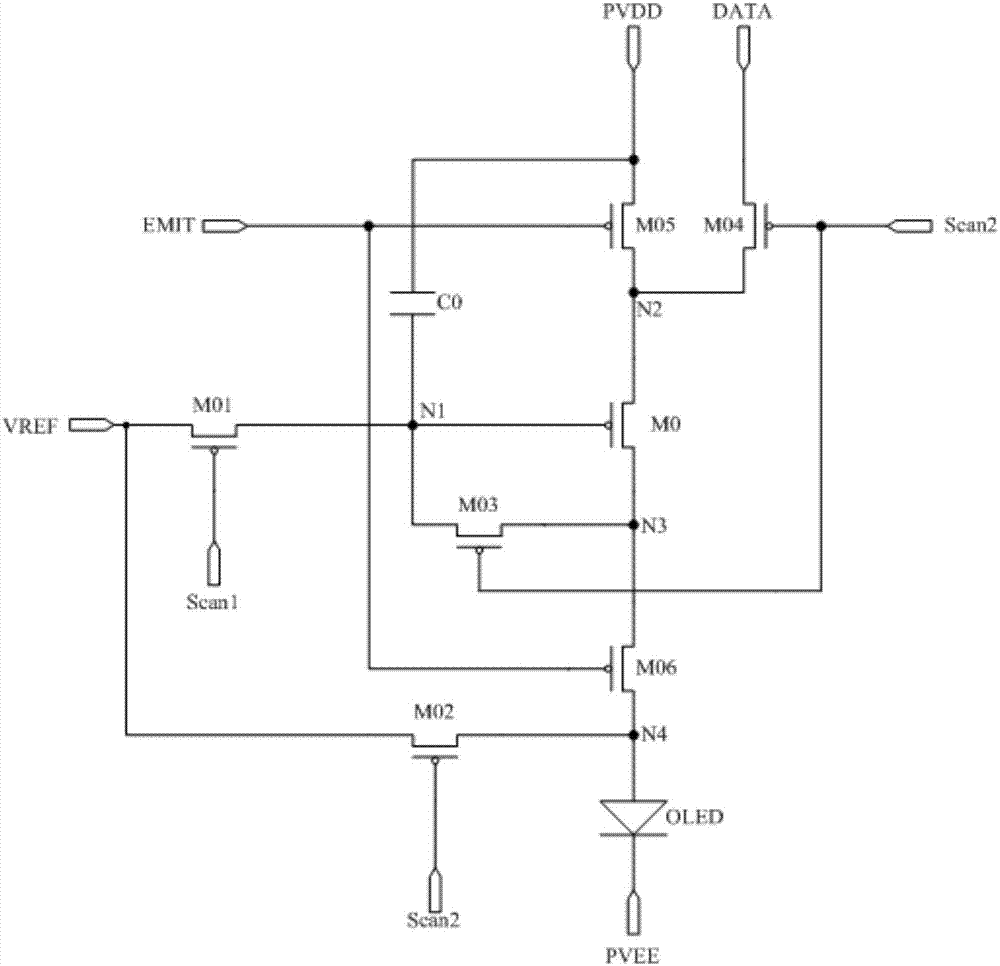

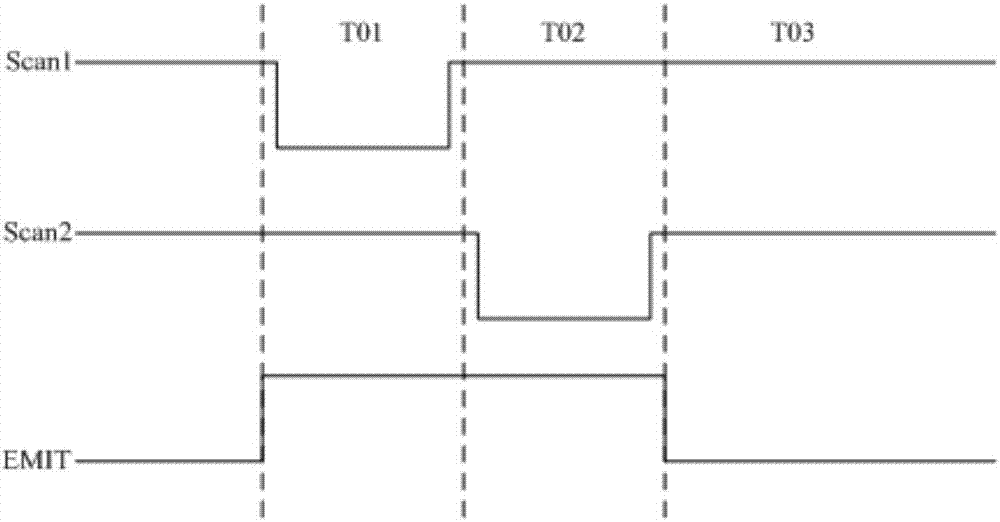

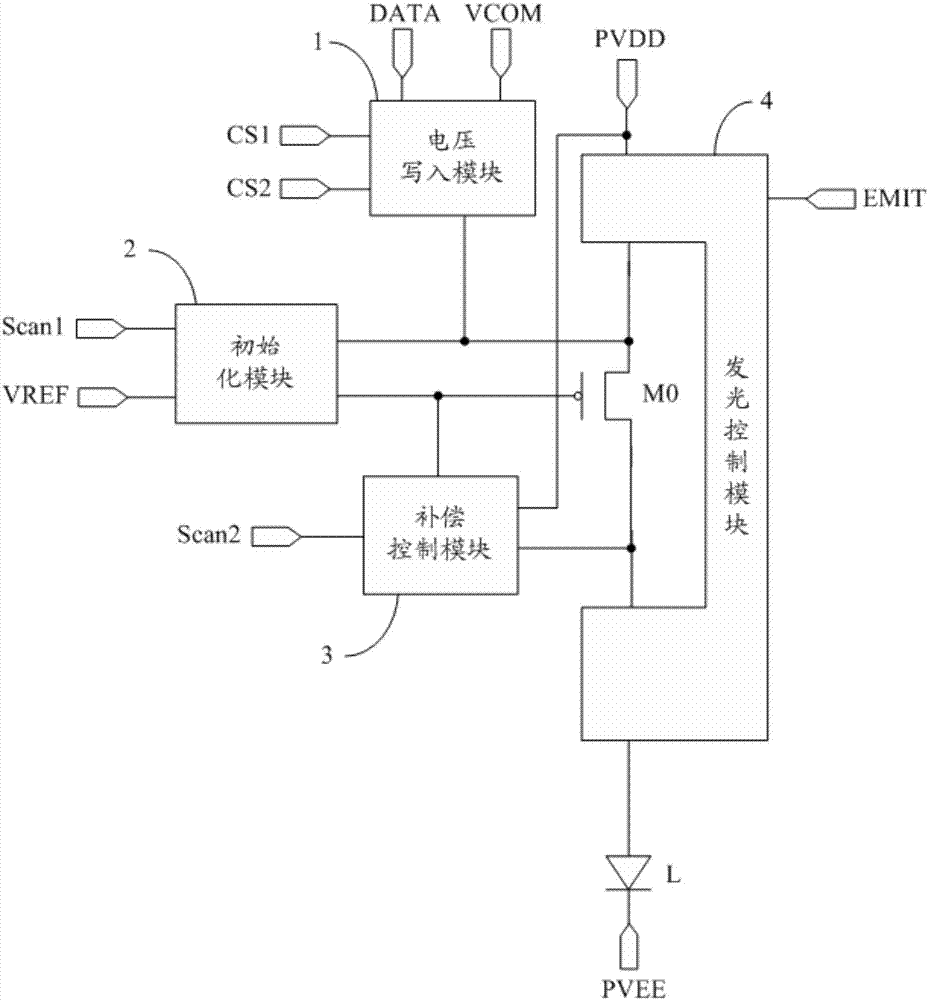

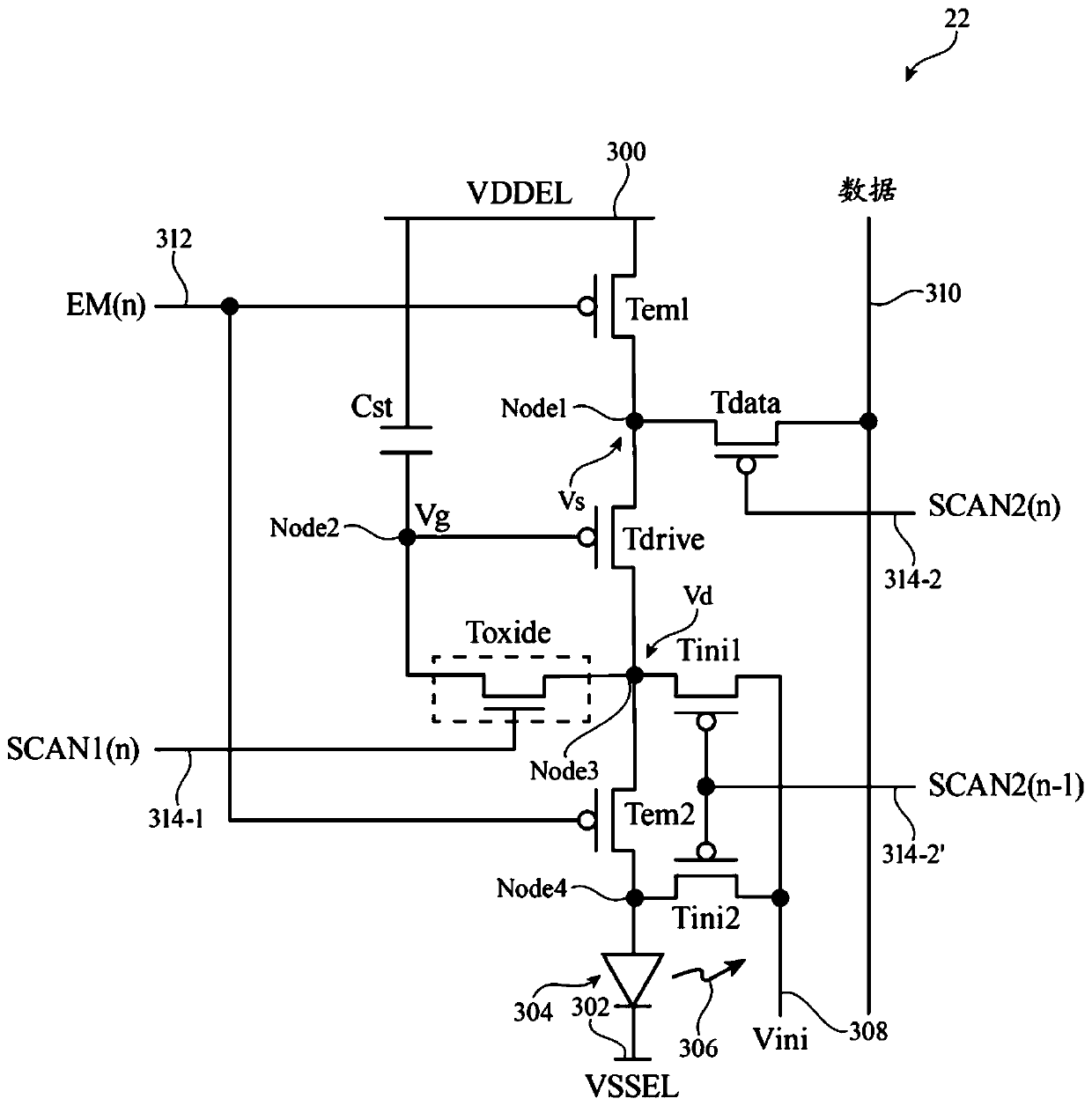

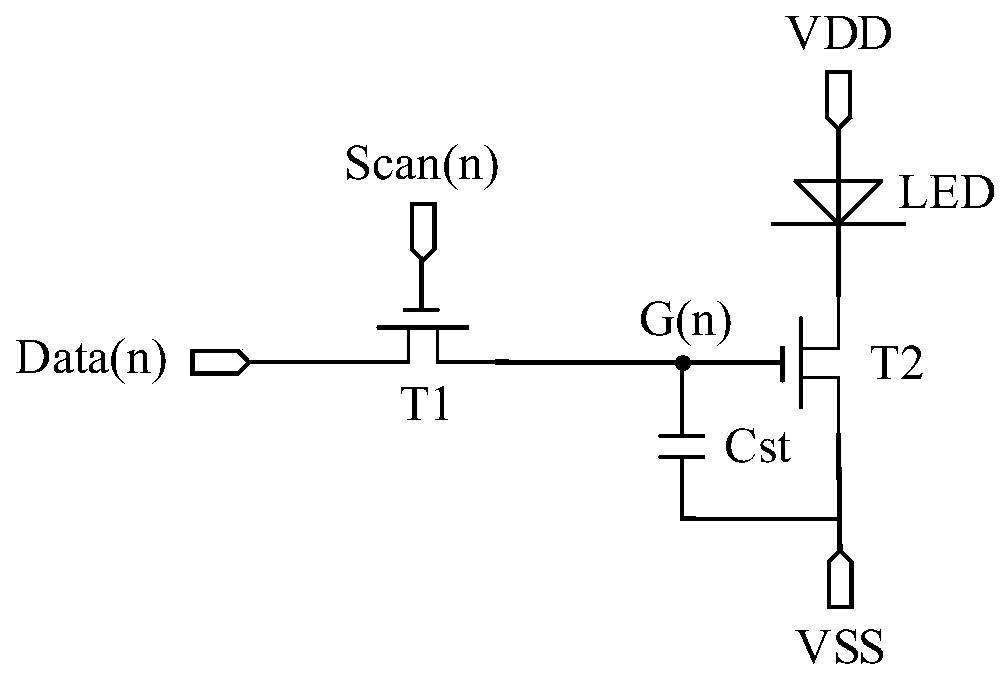

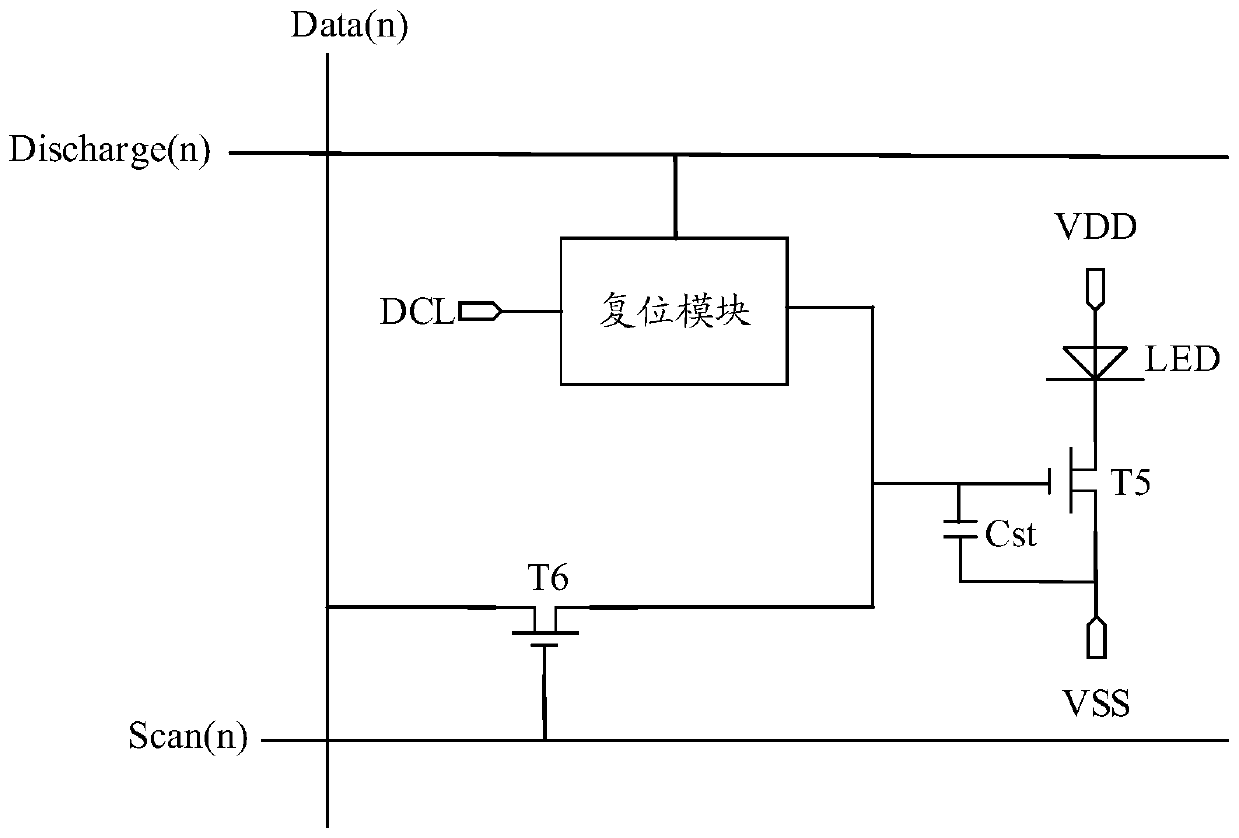

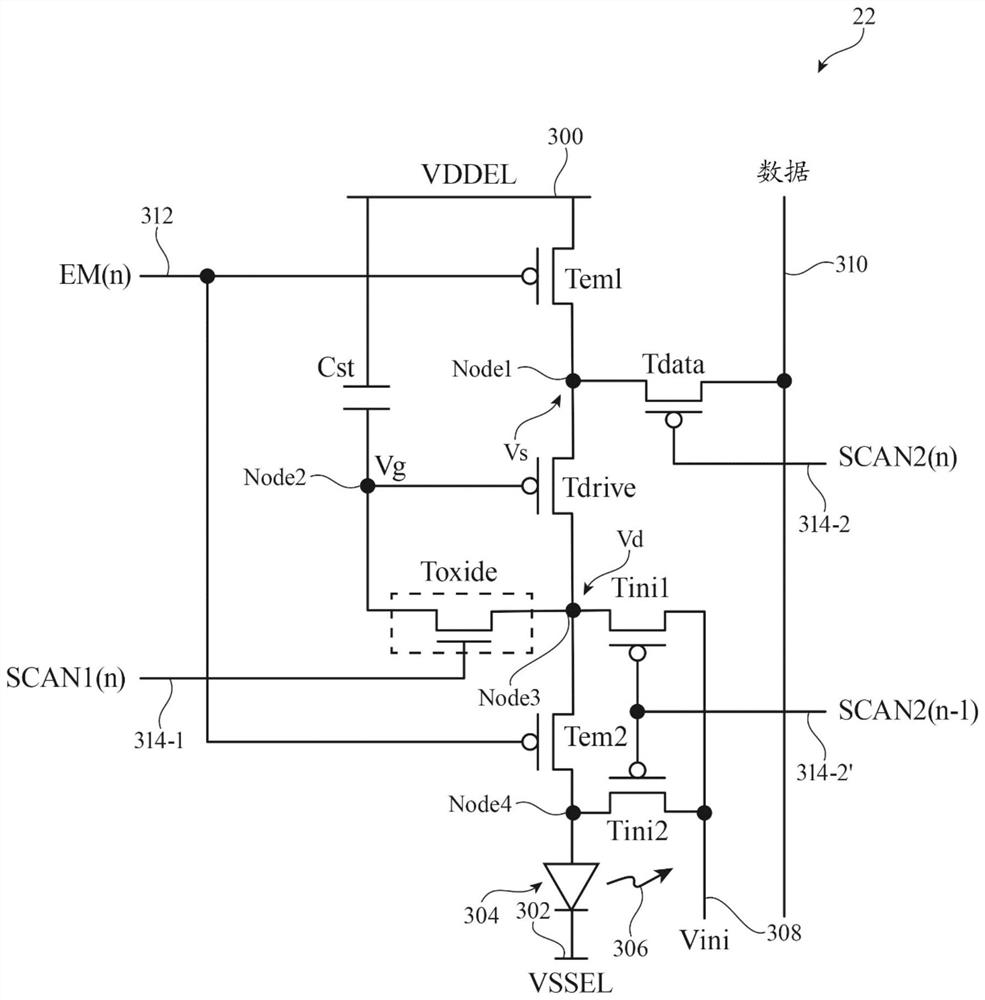

Pixel circuit, driving method thereof, display panel and display device

ActiveCN107256695AAvoid differencesConsistent brightnessStatic indicating devicesPersistence of visionGray level

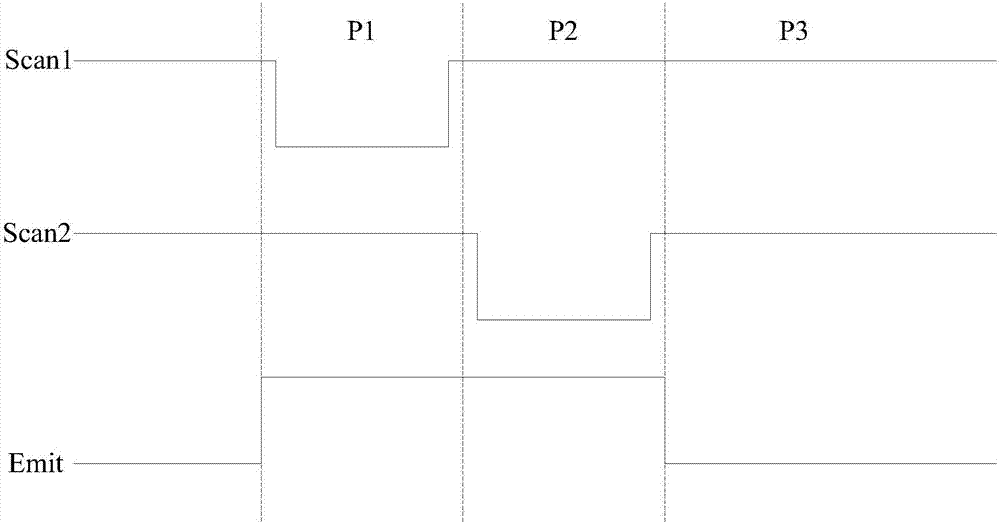

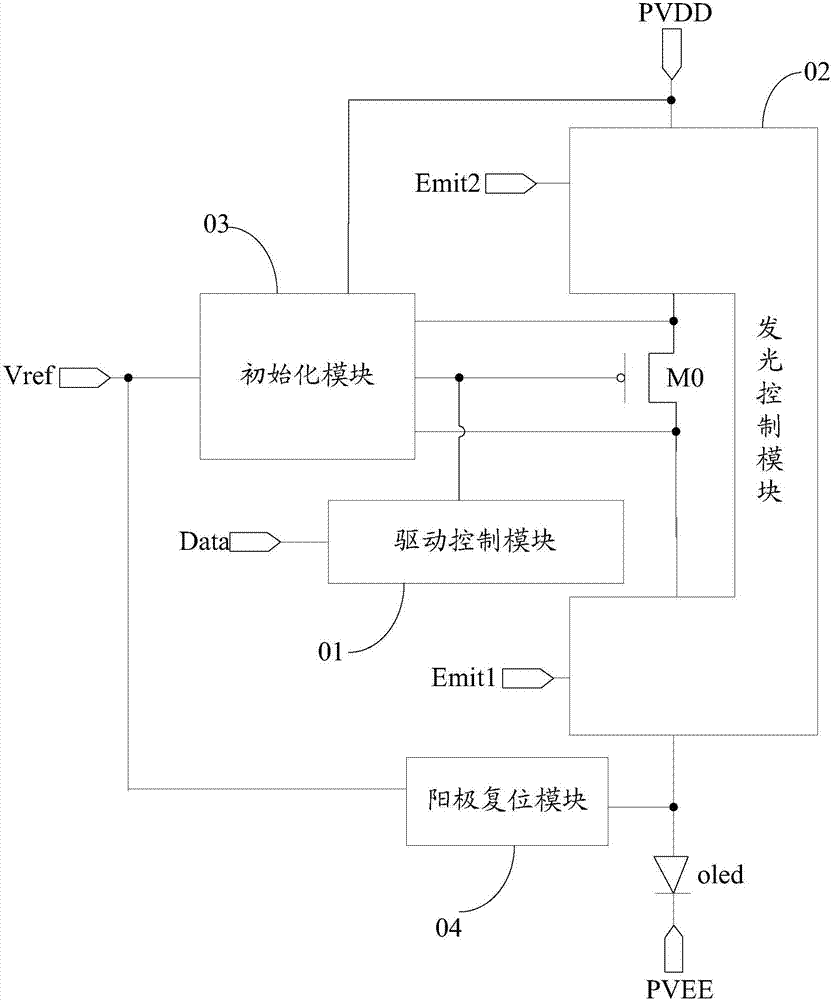

The present invention discloses a pixel circuit, a driving method thereof, a display panel and a display device. According to the present invention, before a light-emitting device emits light, an initialization module provides the signals at a reference signal end to the grid and the second pole of a driving transistor separately, provides a signal at a first voltage end to the first pole of the driving transistor, and is utilized to reset the grid and the first pole of the driving transistor separately, so that the difference caused by the parasitic capacitances of the grid and the first pole is avoided, and further the problem that due to the voltage jump, the threshold values are captured inconsistently, is avoided, and accordingly, the consistent brightness of a first frame after the high and low gray-scale switching can be guaranteed. Moreover, the second pole of the driving transistor is reset at the initialization stage of each frame, so that a large current flows through the driving transistor, and the threshold-voltage excursion of the driving transistor caused by the bias stress is forced to recover, and accordingly, a persistence of vision phenomenon is avoided.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

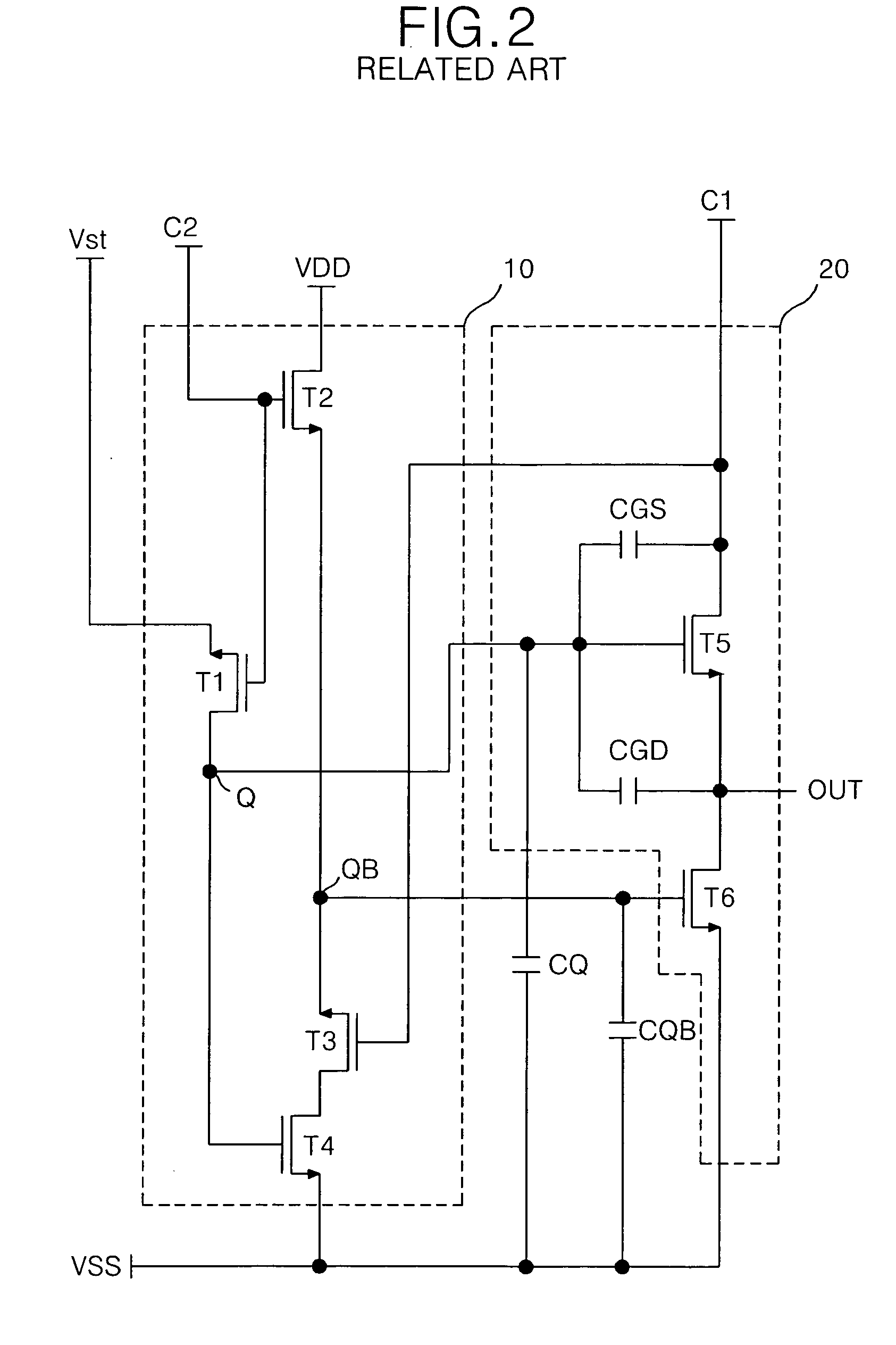

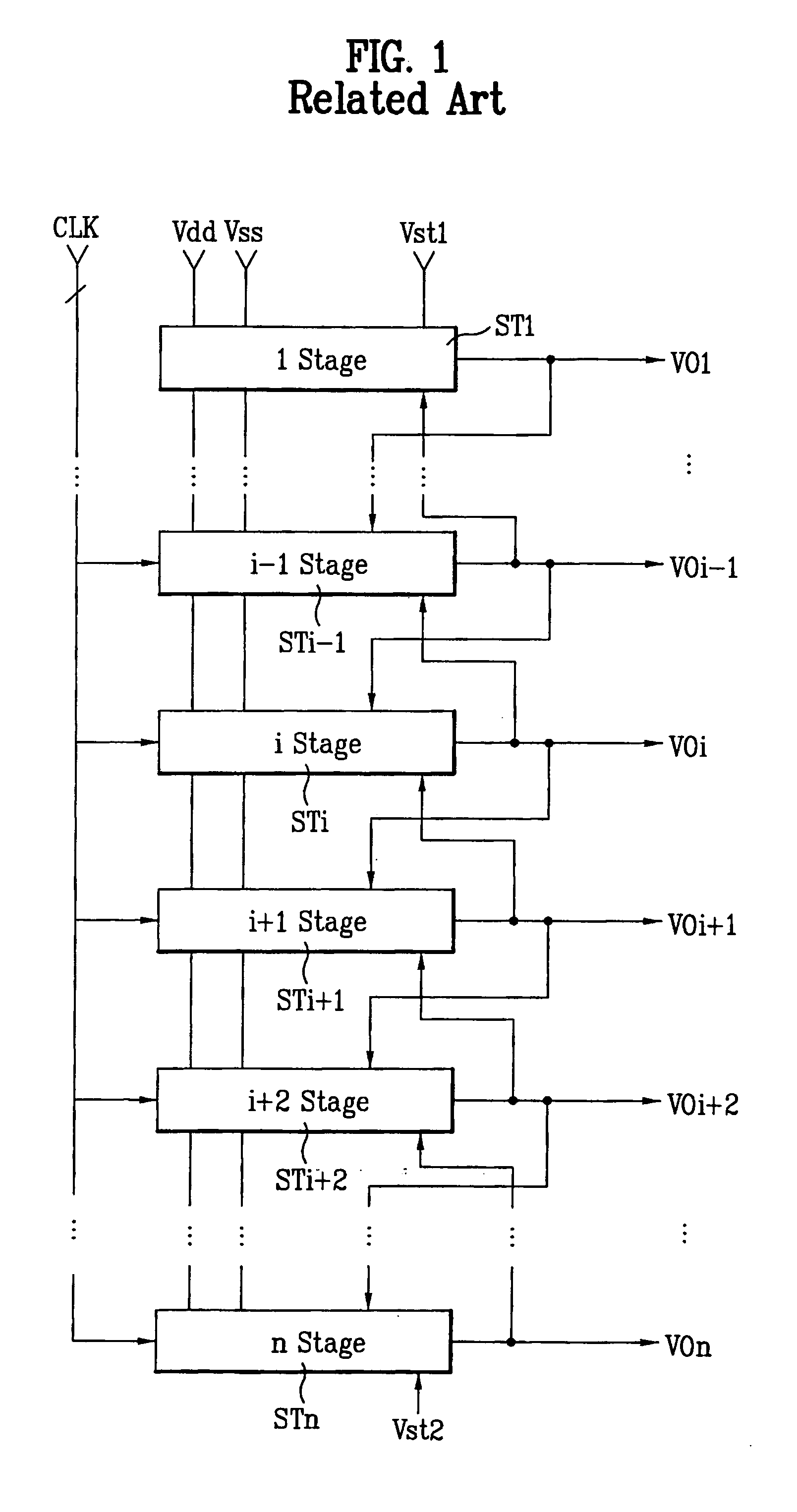

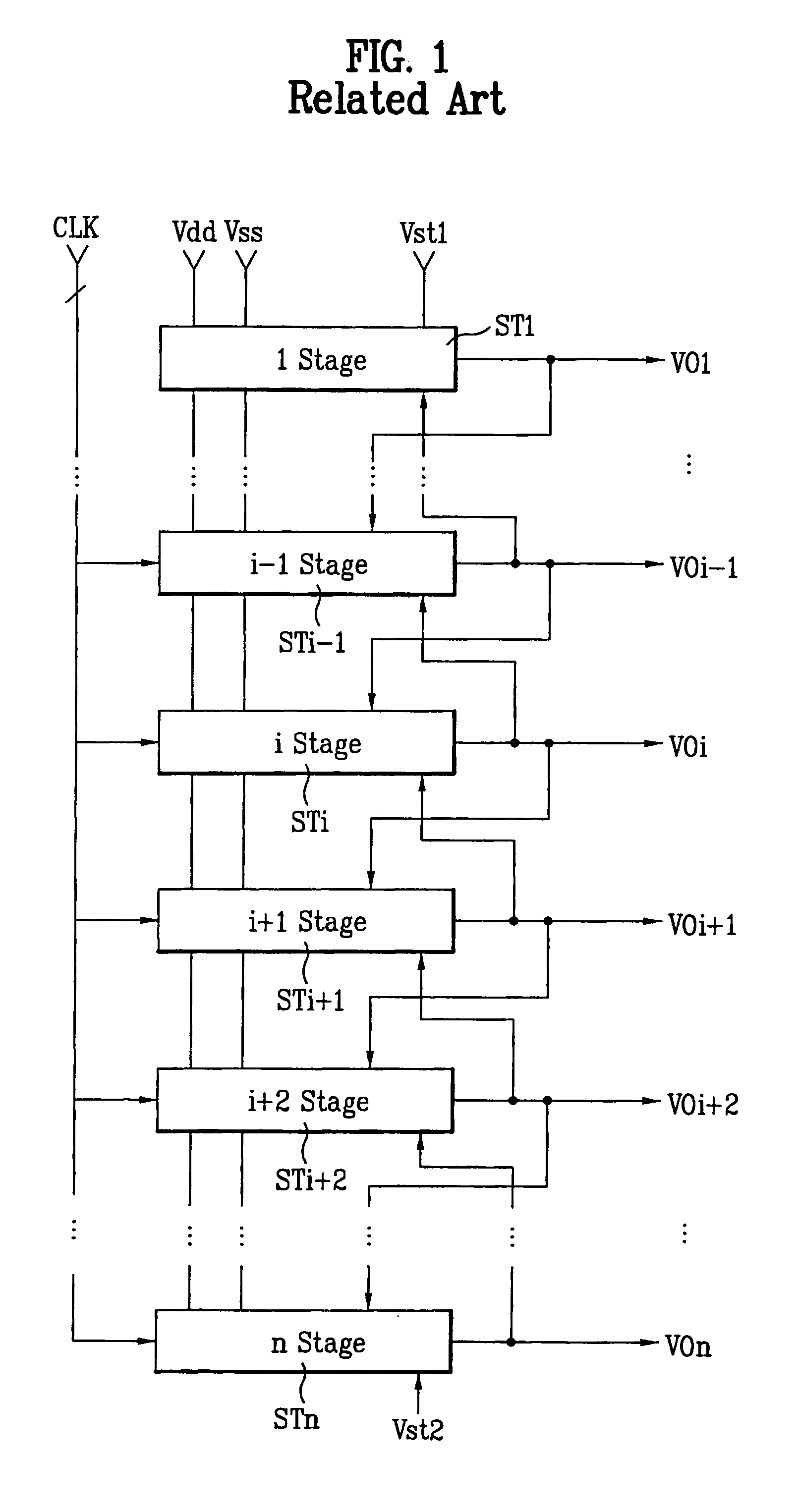

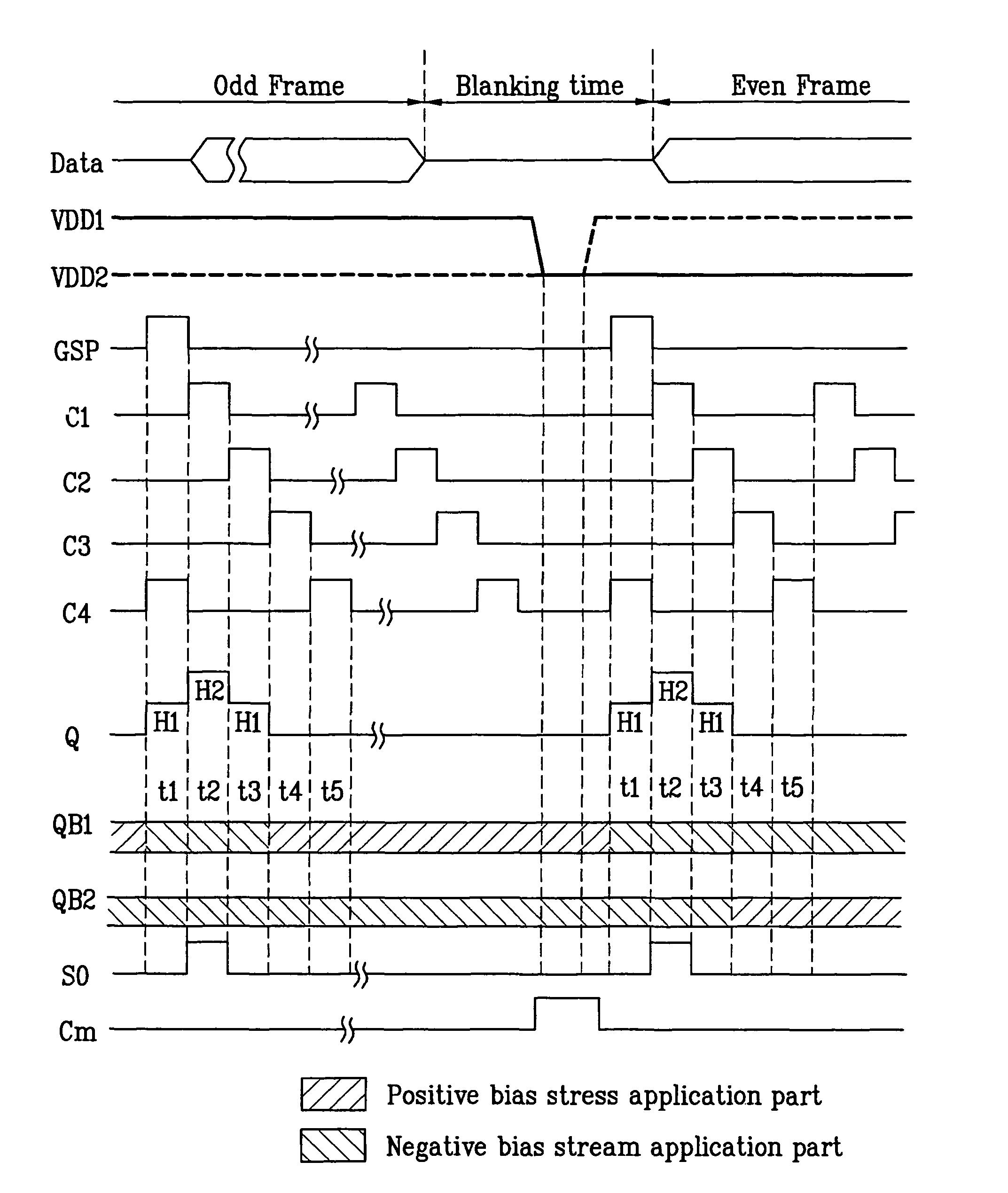

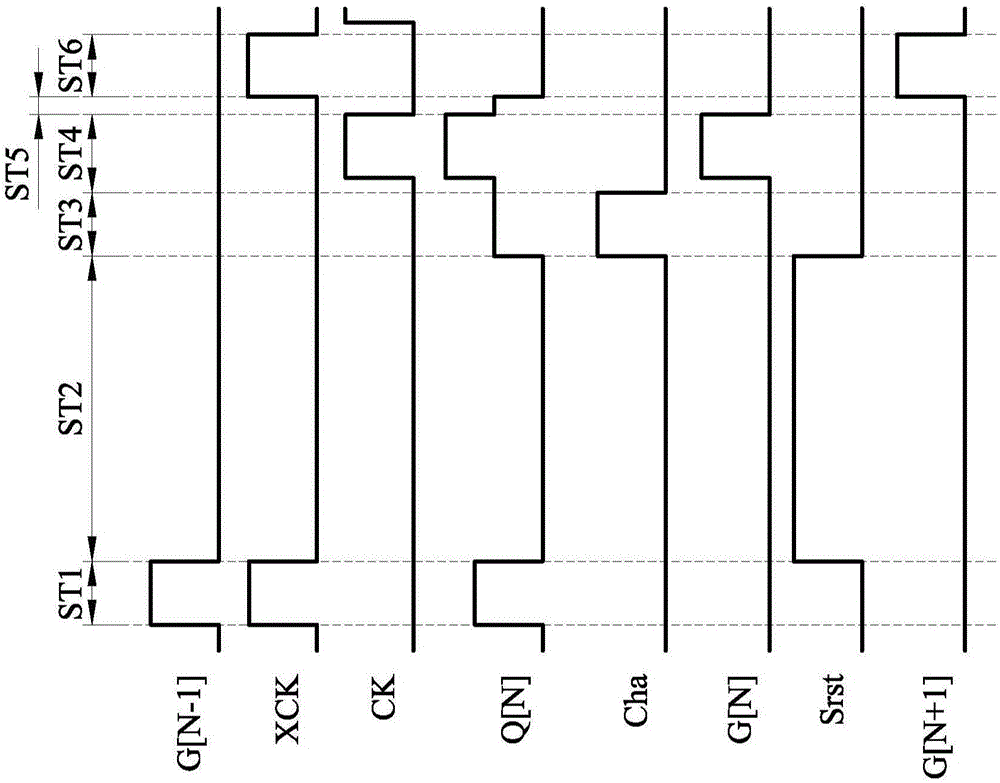

Shift register and liquid crystal display device using the same

A shift register and an LCD device to prevent the deterioration of a transistor by controlling a bias stress are disclosed. The shift register includes a plurality of stages for sequential shift signals, wherein each of the plurality of stages is connected with first and second supplying voltage input lines having opposite phases inversed by at least every frame, a start pulse input line, and at least one clock signal input line in which a phase of a first logic state is shifted in sequence, and a clock signal inputted to the clock signal input line is maintained in a second logic state different from the first logic state during a blanking time between frames.

Owner:LG DISPLAY CO LTD

Pixel circuit, driving method of pixel circuit, organic light-emitting display panel and display device

ActiveCN107452339AShorten write timeRecovery Threshold Voltage ShiftStatic indicating devicesSolid-state devicesDisplay deviceParasitic capacitance

The invention discloses a pixel circuit, a driving method of the pixel circuit, an organic light-emitting display panel and a display device. A unified public voltage signal is inputted to a first electrode of a drive transistor before a data signal is written into a control electrode of the drive transistor; the public voltage signal and a threshold voltage of the drive transistor are written into a control electrode of the drive transistor, so that relatively high current can pass through the drive transistor, threshold voltage deviation, which is caused by bias stress, of the drive transistor can be recovered, a retarding effect of the drive transistor can be improved and the occurrence of a ghosting phenomenon can be prevented; in addition, when the data signal is written into the control electrode of the drive transistor, a time of writing the data signal can be shortened, and the control electrode and the first electrode of the drive transistor can achieve jump through a unified potential, so that a difference, which is caused by stray capacitance between the control electrode and the first electrode of the drive transistor, can be prevented, the problem that threshold voltage grabbing is inconsistent due to voltage jump can be avoided and consistent brightness of the first frame after high-low grayscale switching can be guaranteed.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

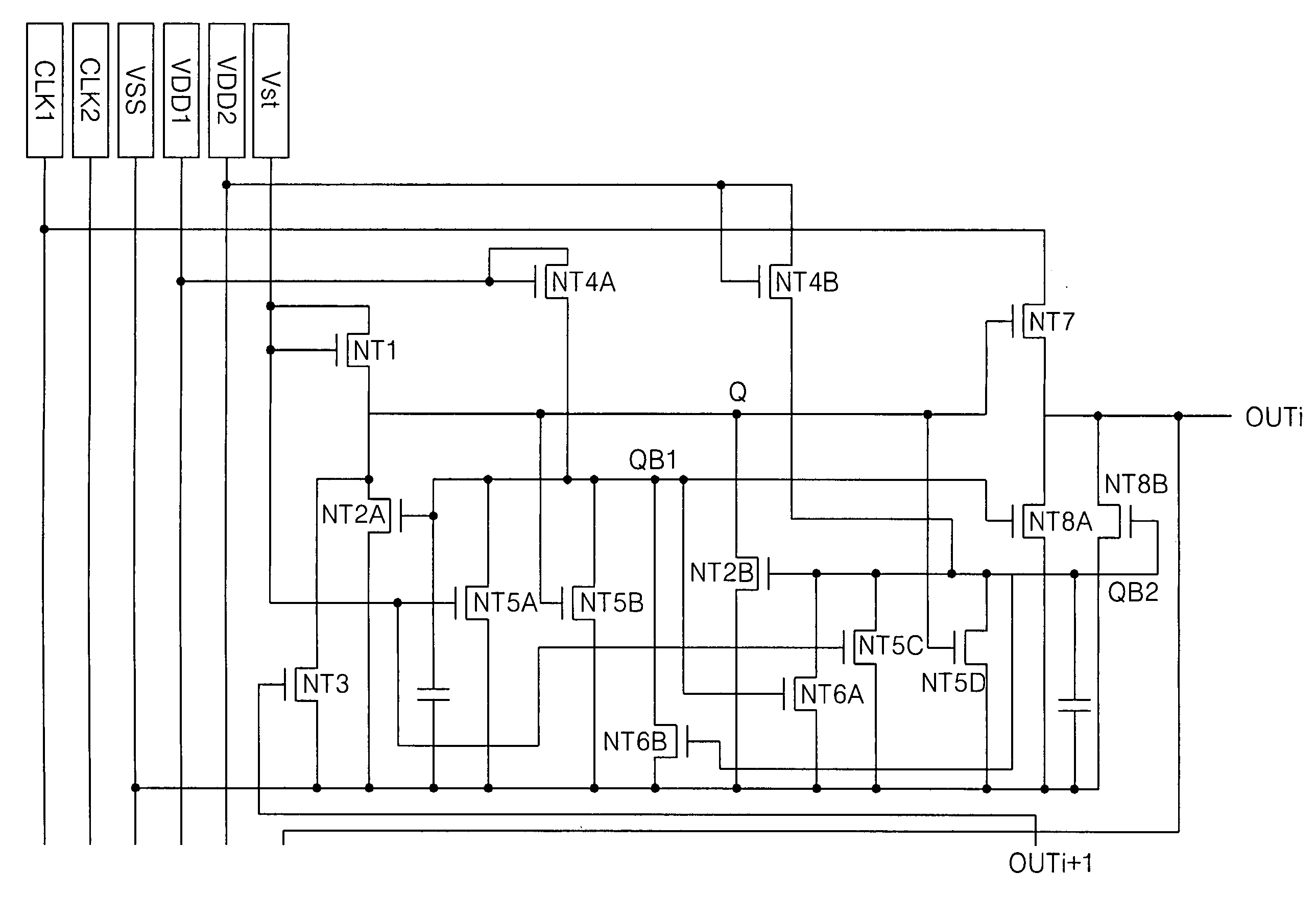

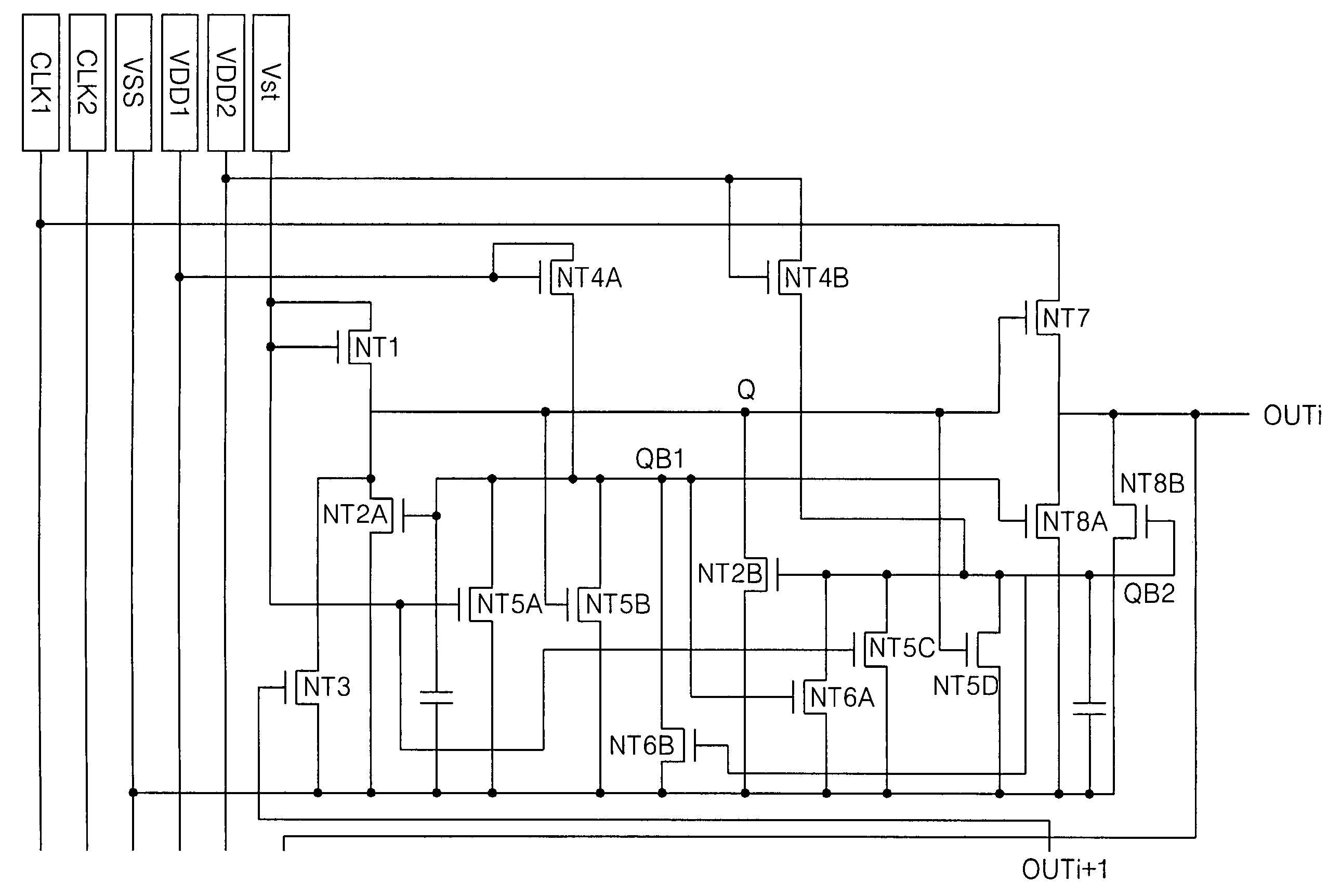

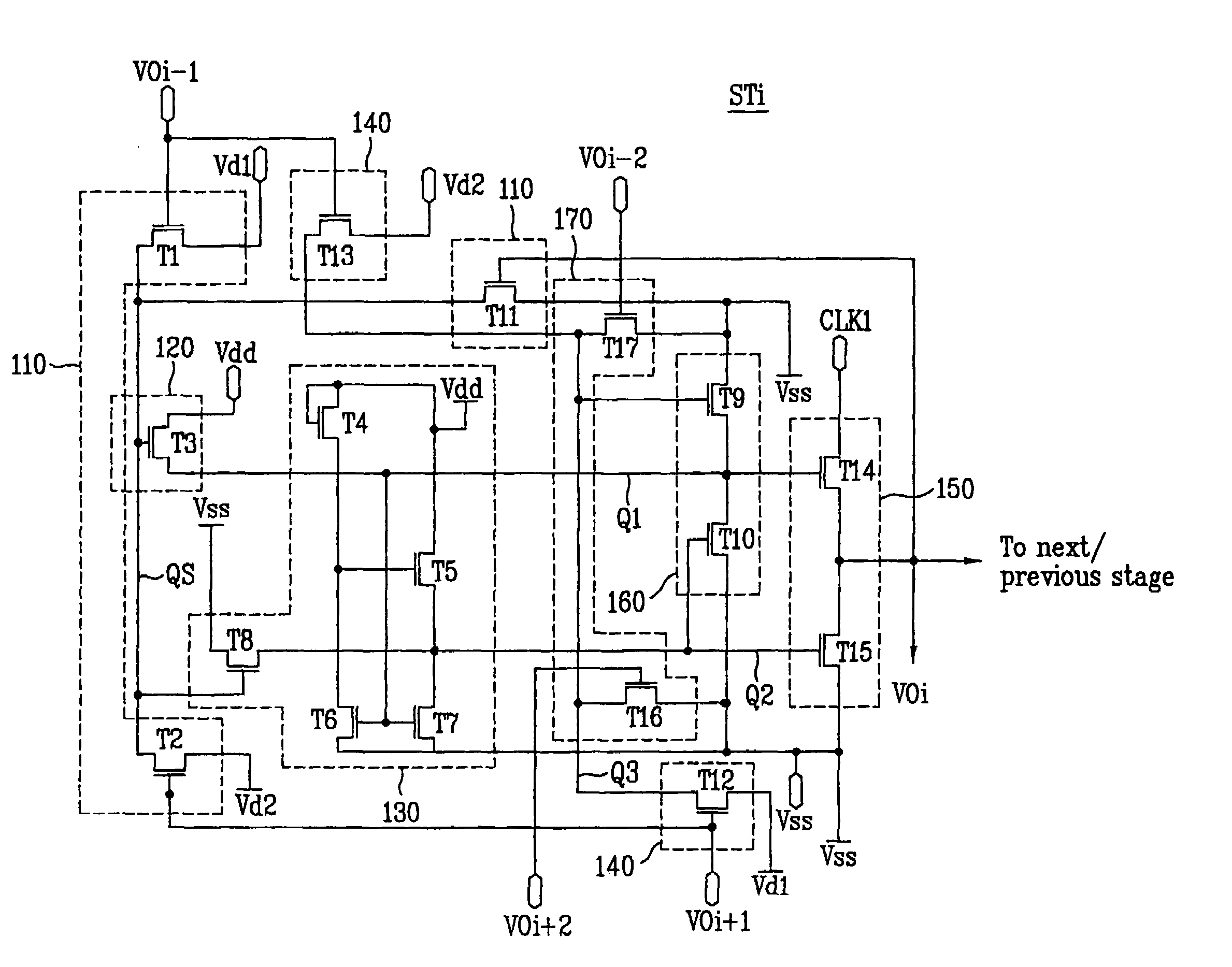

Shift register

ActiveUS20070127620A1Stress minimizationStatic indicating devicesCounting chain synchronous pulse countersShift registerBias stress

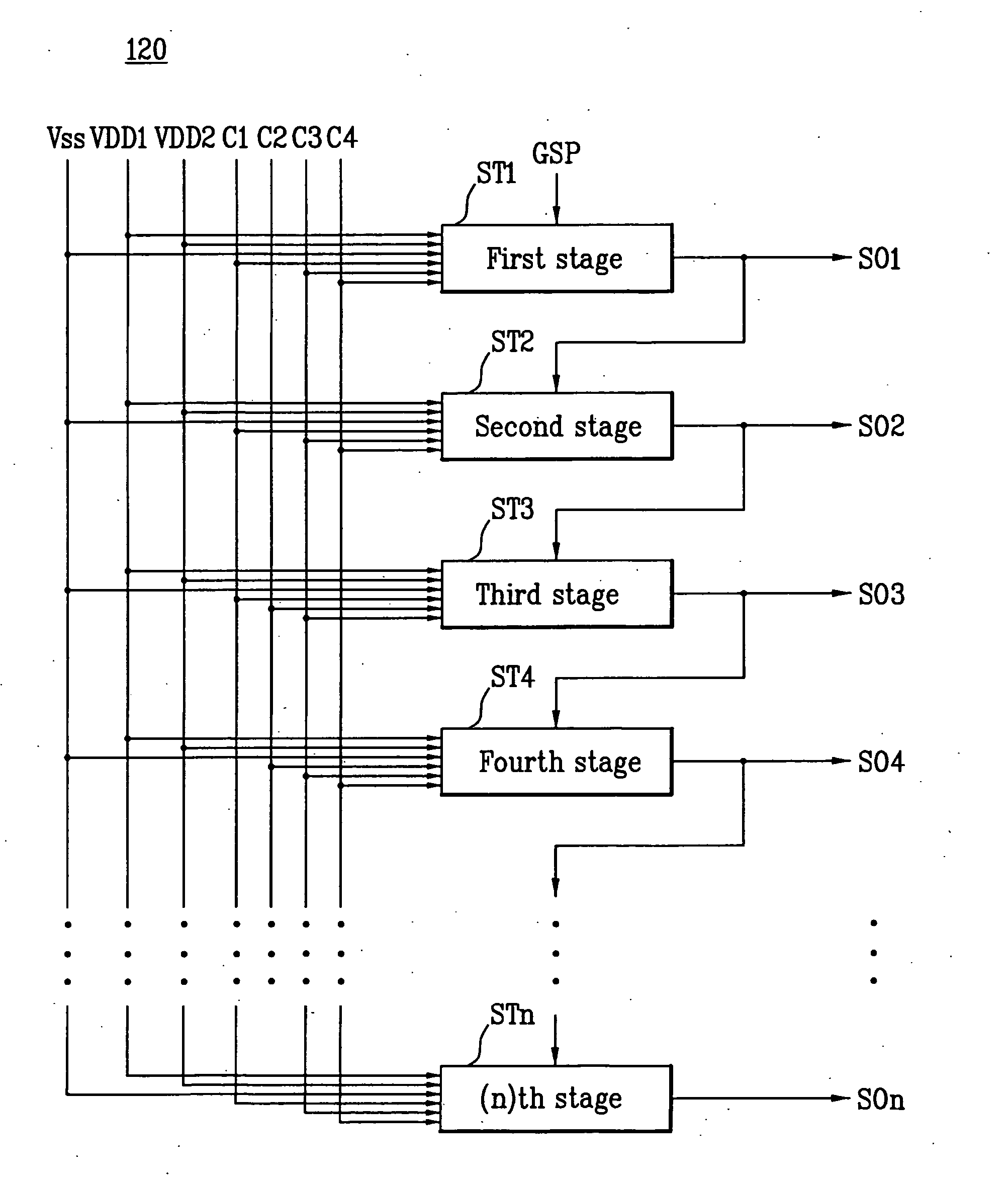

A shift register minimizing bias stress applied to transistors is disclosed. A shift register including n stages outputting scan pluses that are sequentially delayed in a forward or reverse direction thereof, where n is positive integer and wherein each stage includes: a scan direction controller that provides a first or second voltage to a scan direction control node according to a first or second enable signal and controlling the forward or reverse direction output; a first node controller that controls a first node according to a voltage on the scan direction control node; a second node controller that controls a second node according to the voltage on the scan direction control node and a voltage on the first node; an output unit that outputs a clock signal as scan pulse according to voltages on the first and second nodes; a third node controller that provides one of the first and second voltages to a third node according to the first and second enable signals; a first discharge circuit unit that discharges the voltage on the first node according to voltages of the second and third nodes; and a second discharge circuit unit that discharges the voltage on the third node according to one of a third enable signal and a fourth enable signal.

Owner:LG DISPLAY CO LTD

Shift register

Disclosed is a shift register capable of mitigating gate bias stress. The shift register, including a plurality of stages, includes an output buffer having a pull-up transistor and two pull-down transistors, each with gates connected to different nodes. One of the two pull-down transistors operates during an even frame portion of an LCD operation; and the other of the two pull-down transistors operates during an odd frame portion of the LCD display operation. Alternating operation of the pull-down transistors substantially mitigates gate stress, and substantially enables the shift register to be fabricated with amorphous silicon.

Owner:LG DISPLAY CO LTD

Shift register

ActiveUS7397885B2Stress minimizationStatic indicating devicesCounting chain synchronous pulse countersShift registerBias stress

A shift register minimizing bias stress applied to transistors is disclosed. A shift register including n stages outputting scan pluses that are sequentially delayed in a forward or reverse direction thereof, where n is positive integer and wherein each stage includes: a scan direction controller that provides a first or second voltage to a scan direction control node according to a first or second enable signal and controlling the forward or reverse direction output; a first node controller that controls a first node according to a voltage on the scan direction control node; a second node controller that controls a second node according to the voltage on the scan direction control node and a voltage on the first node; an output unit that outputs a clock signal as scan pulse according to voltages on the first and second nodes; a third node controller that provides one of the first and second voltages to a third node according to the first and second enable signals; a first discharge circuit unit that discharges the voltage on the first node according to voltages of the second and third nodes; and a second discharge circuit unit that discharges the voltage on the third node according to one of a third enable signal and a fourth enable signal.

Owner:LG DISPLAY CO LTD

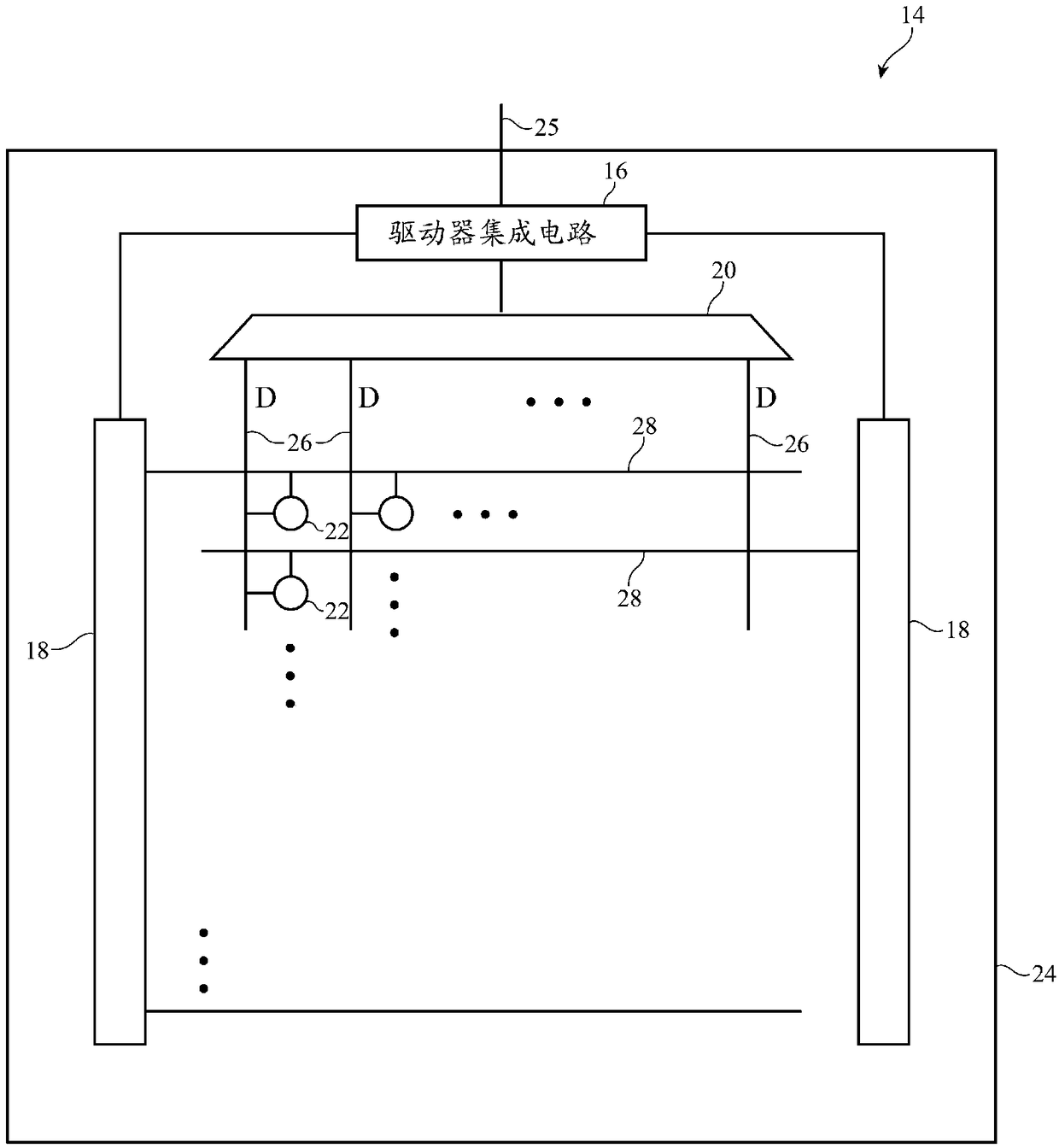

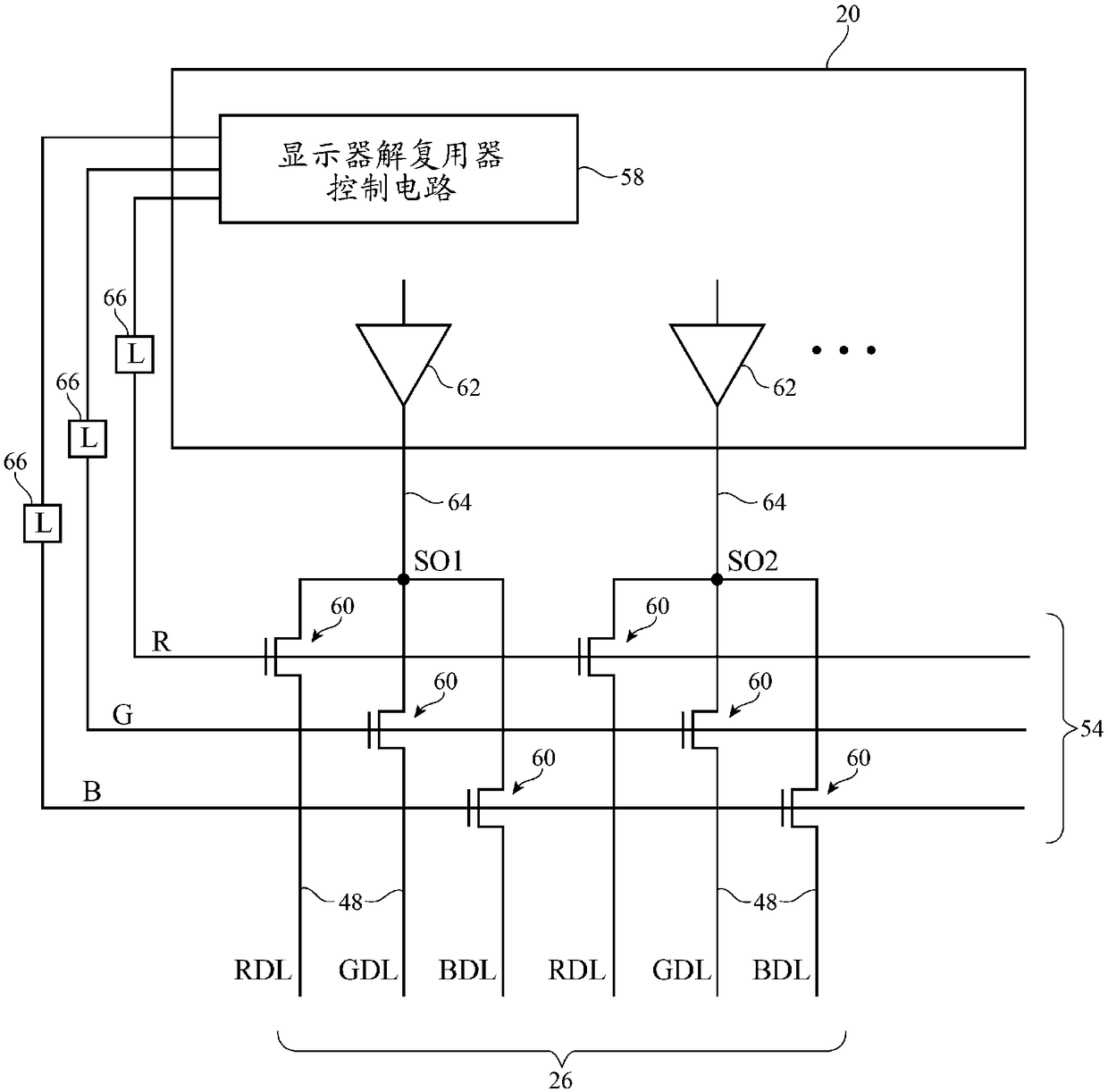

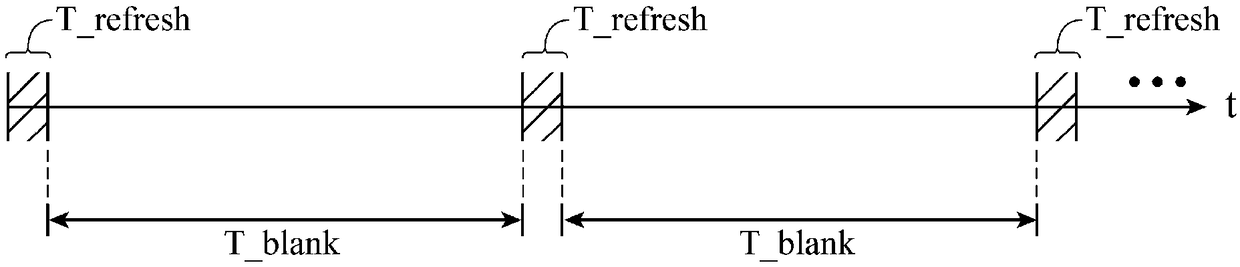

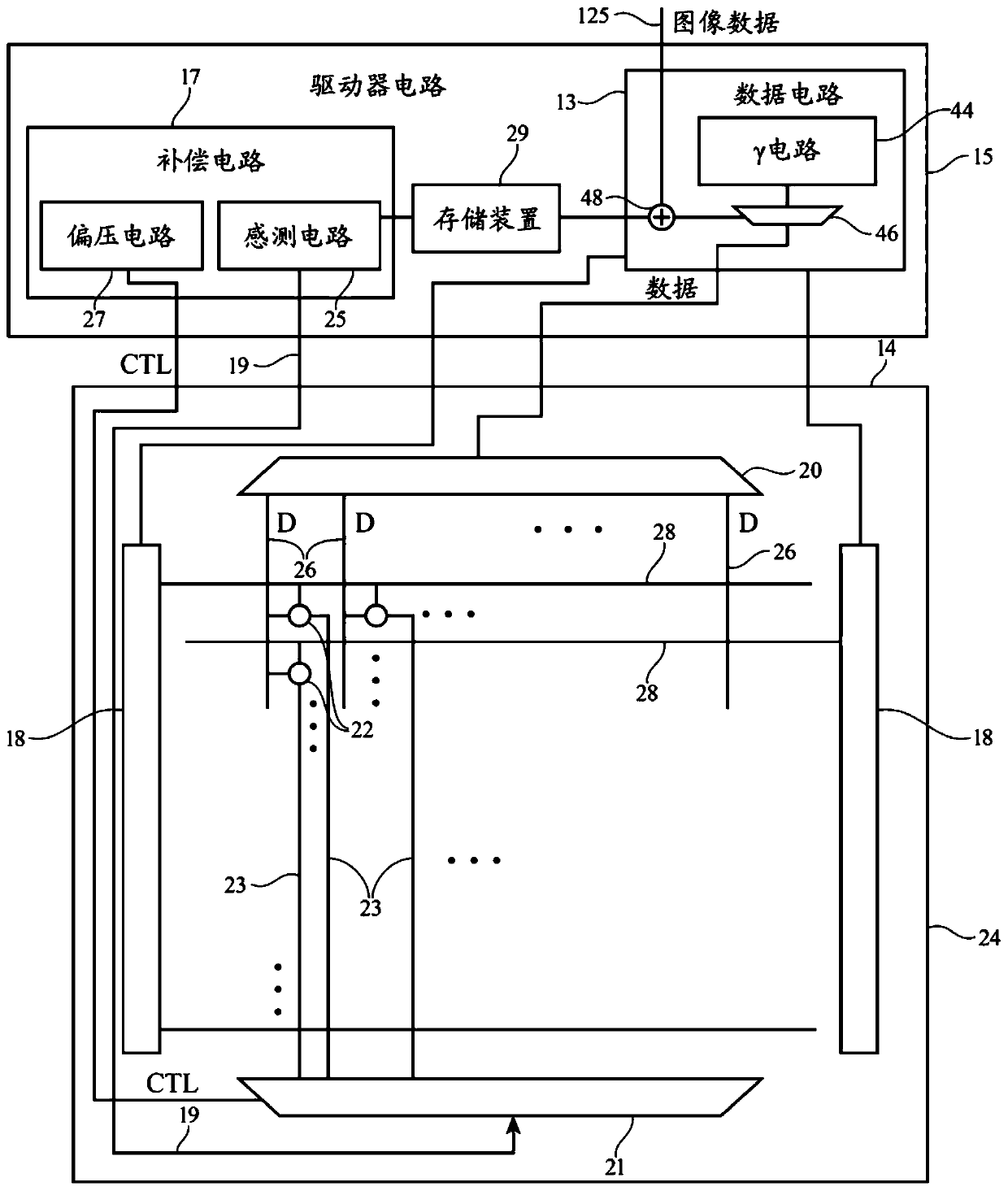

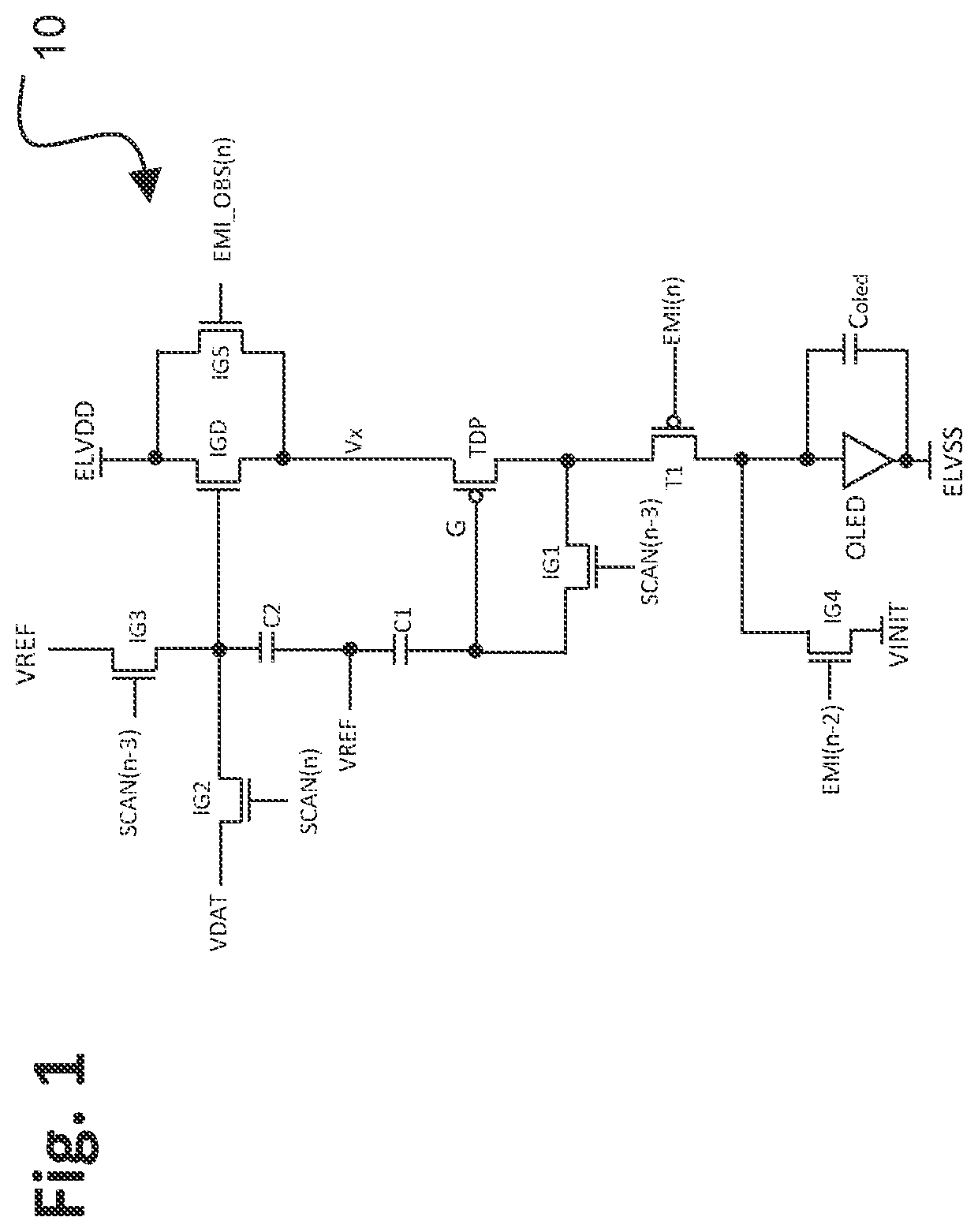

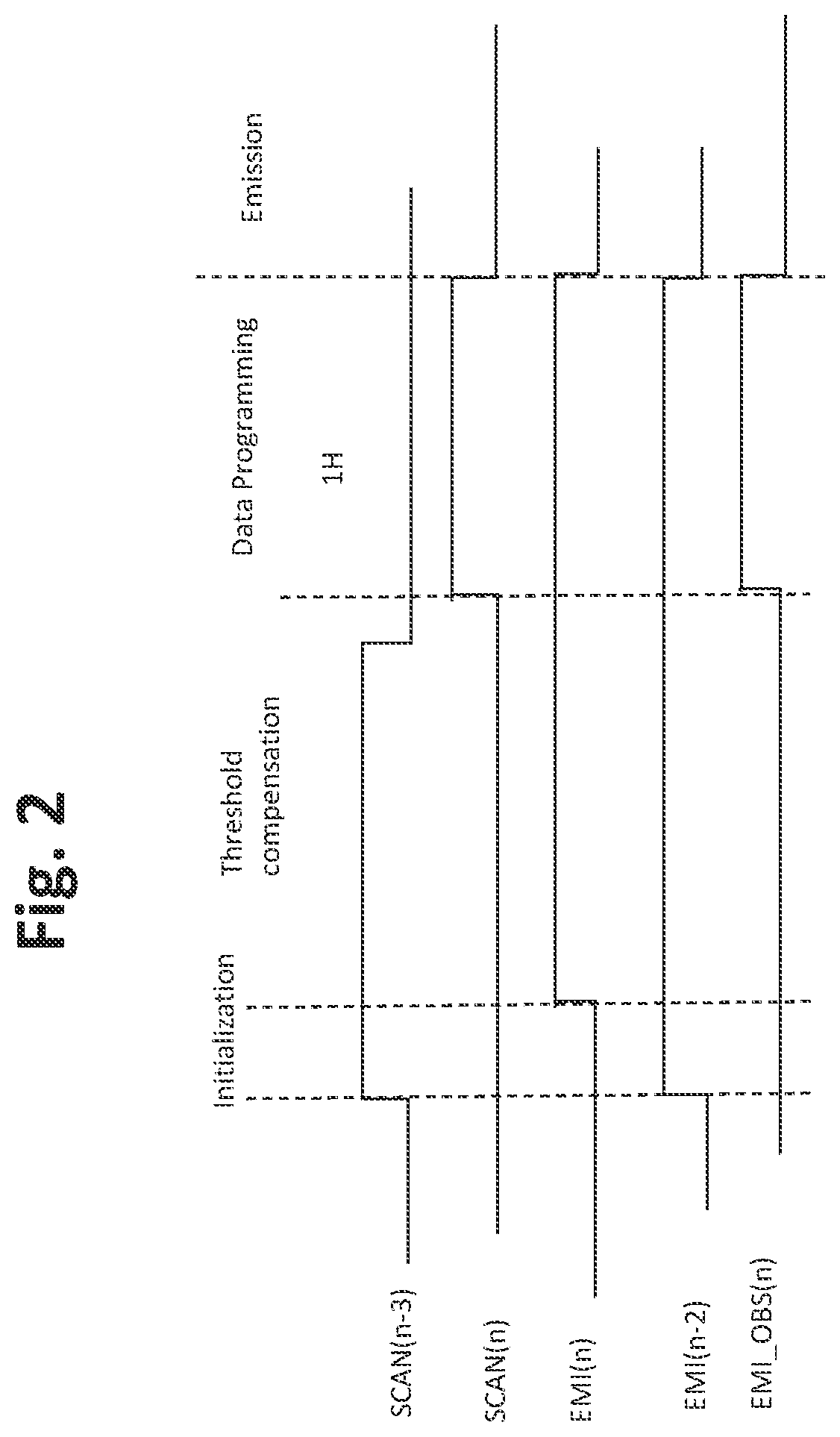

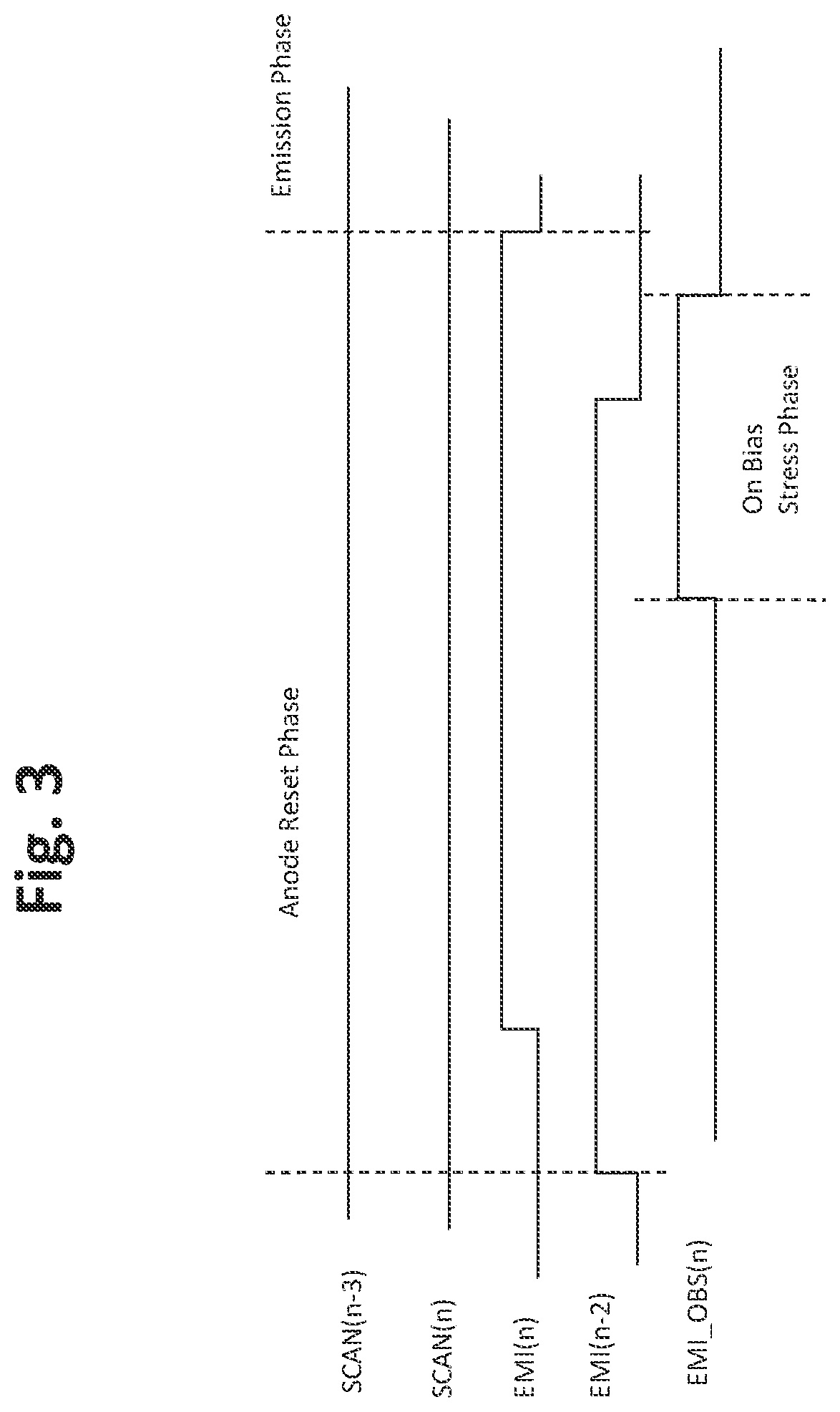

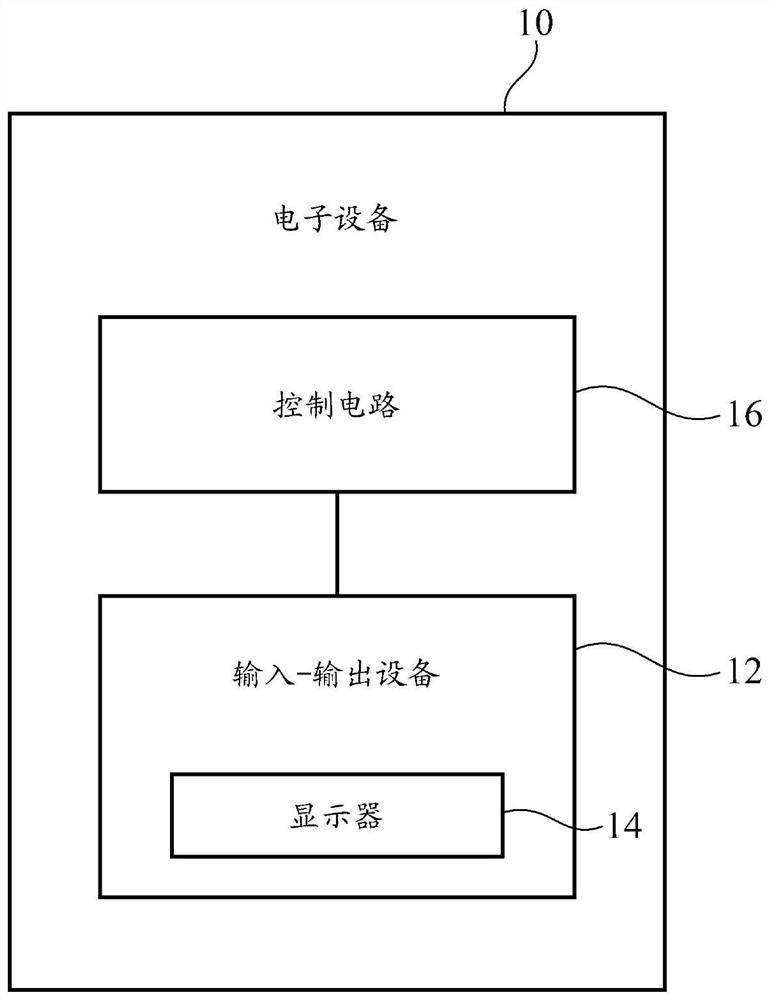

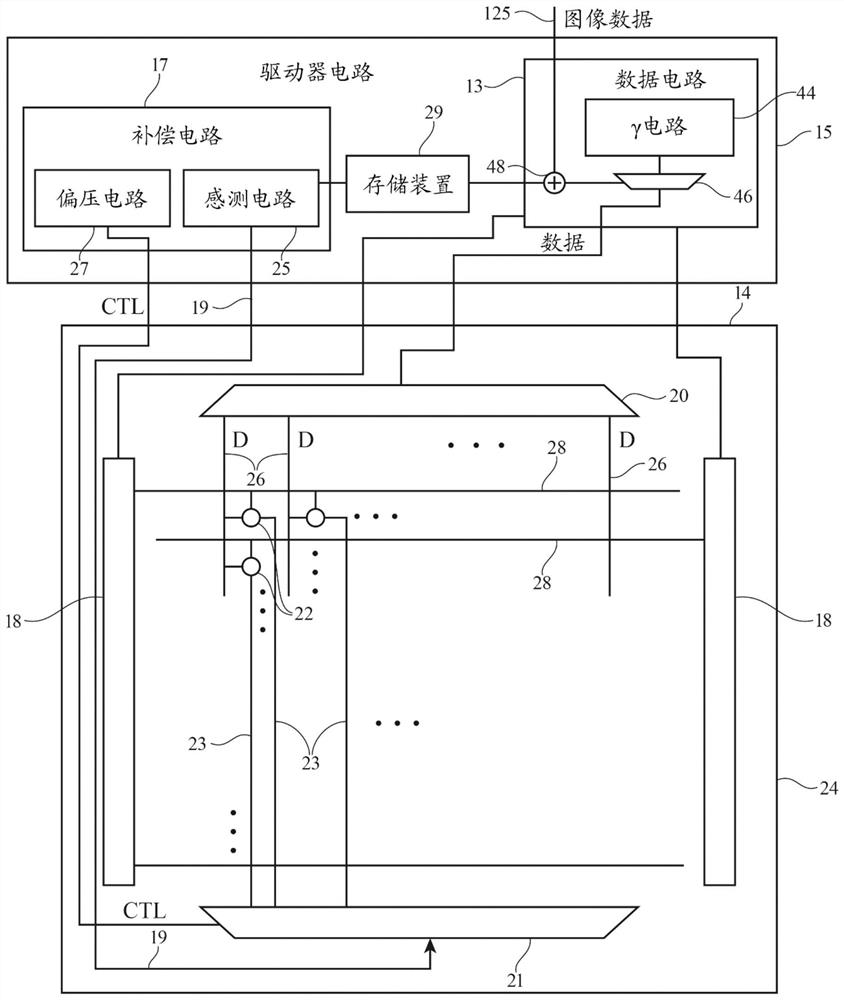

Electronic Devices With Low Refresh Rate Display Pixels

The invention discloses electronic devices with low refresh rate display pixels. The display may have an array of organic light-emitting diode display pixels operating at a low refresh rate. Each display pixel may have six thin-film transistors and one capacitor. One of the six transistors may serve as the drive transistor and may be compensated using the remaining five transistors and the capacitor. One or more on-bias stress operations may be applied before threshold voltage sampling to mitigate first frame dimming. Multiple anode reset and on-bias stress operations may be inserted during vertical blanking periods to reduce flicker and maintain balance and may also be inserted between successive data refreshes to improve first frame performance. Two different emission signals controllingeach pixel may be toggled together using a pulse width modulation scheme to help provide darker black levels.

Owner:APPLE INC

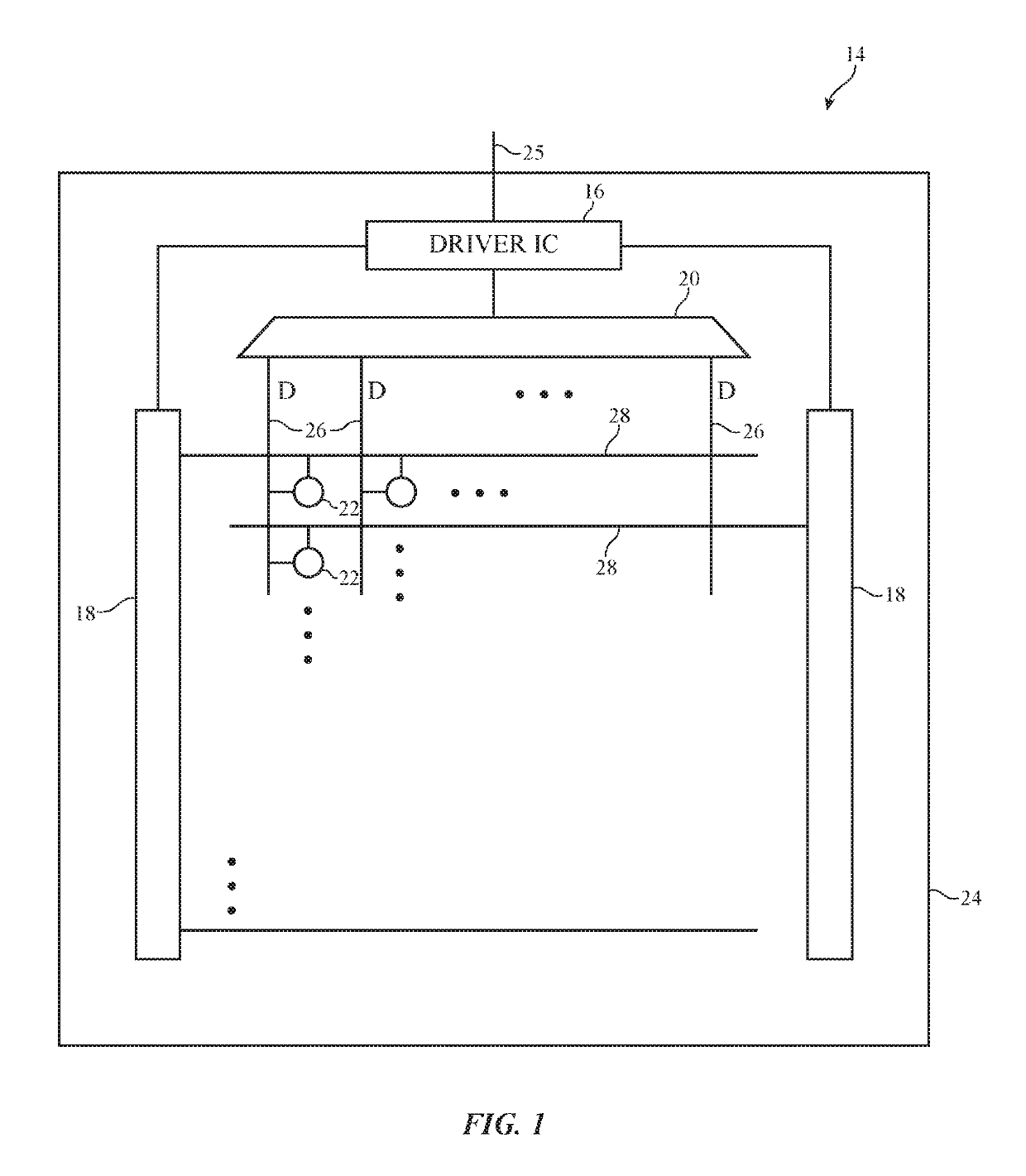

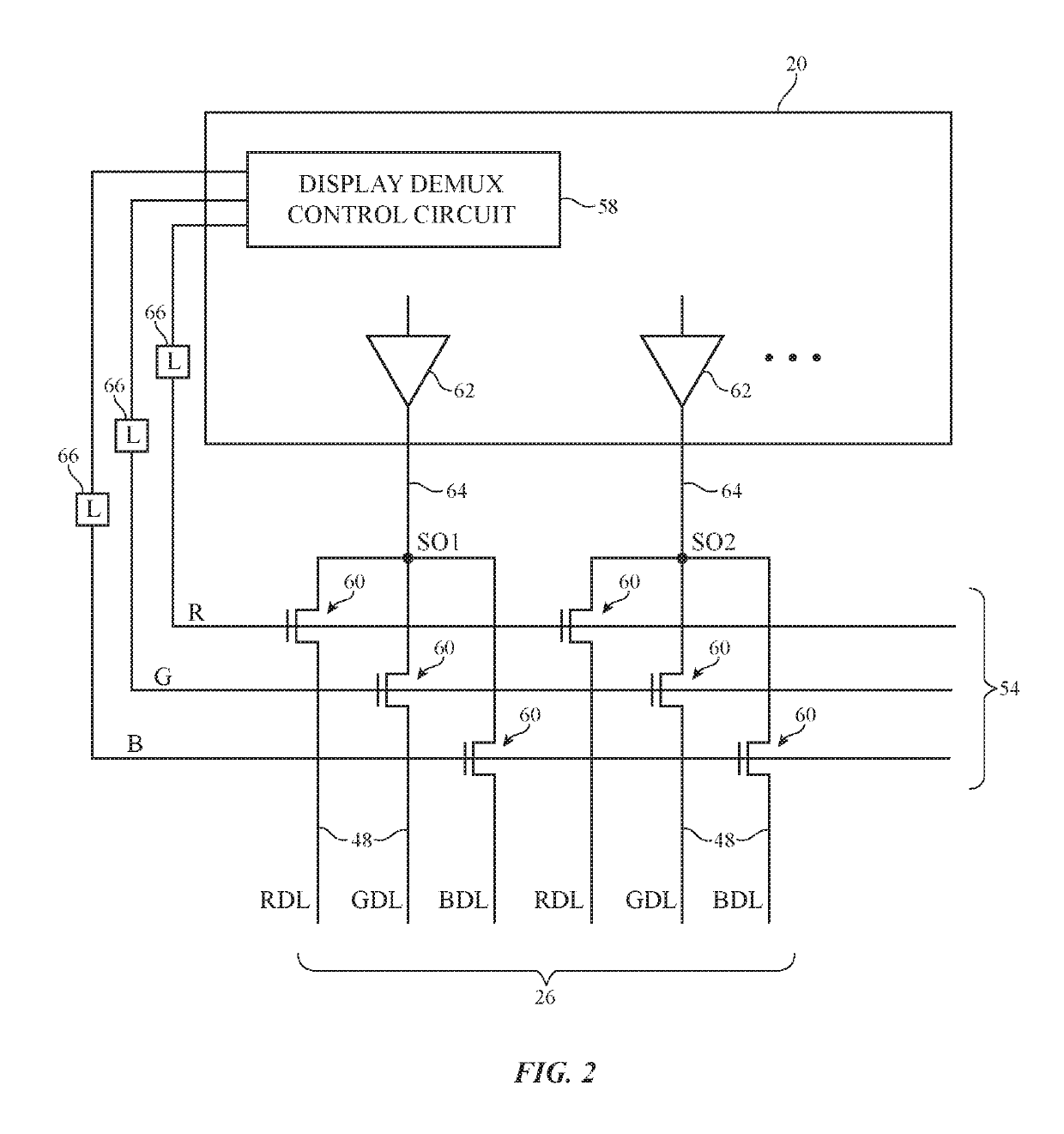

Electronic display with hybrid in-pixel and external compensation

PendingCN111435587AReduce flickerImprove low refresh rate performanceStatic indicating devicesSemiconductor devicesDisplay deviceBias stress

The invention relates to an electronic display with hybrid in-pixel and external compensation. A display pixel is provided that is operable to support hybrid compensation scheme having both in-pixel threshold voltage canceling and external threshold voltage compensation. The display may include multiple p-type silicon transistors with at least one n-type semiconducting-oxide transistor and one storage capacitor. An on-bias stress phase may be performed prior to a threshold voltage sampling and data programming phase to mitigate hysteresis and improve first frame response. In low refresh rate displays, a first additional on-bias stress operation can be performed separate from the threshold voltage sampling and data programming phase during a refresh frame and a second additional on-bias stress operation can be performed during a vertical blanking frame. The display pixel may be configured to receive an initialization voltage and an anode reset voltage, either of which can be dynamicallytuned to match the stress of the first and second additional on-bias stress operations to minimize flicker.

Owner:APPLE INC

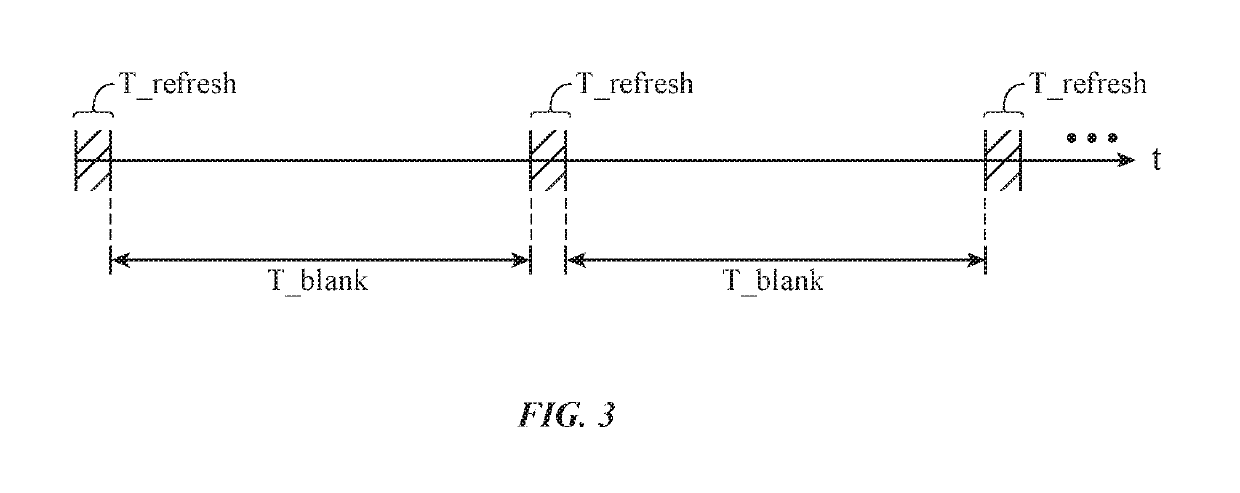

Shift register and liquid crystal display device using the same

A shift register and an LCD device to prevent the deterioration of a transistor by controlling a bias stress are disclosed. The shift register includes a plurality of stages for sequential shift signals, wherein each of the plurality of stages is connected with first and second supplying voltage input lines having opposite phases inversed by at least every frame, a start pulse input line, and at least one clock signal input line in which a phase of a first logic state is shifted in sequence, and a clock signal inputted to the clock signal input line is maintained in a second logic state different from the first logic state during a blanking time between frames.

Owner:LG DISPLAY CO LTD

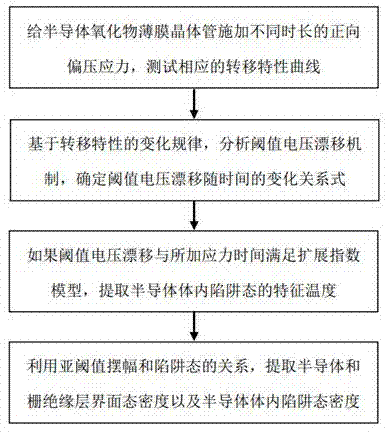

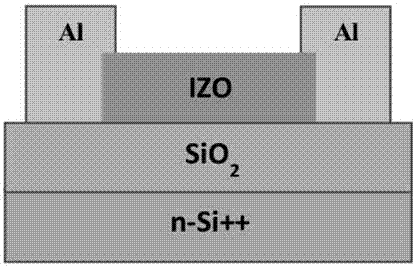

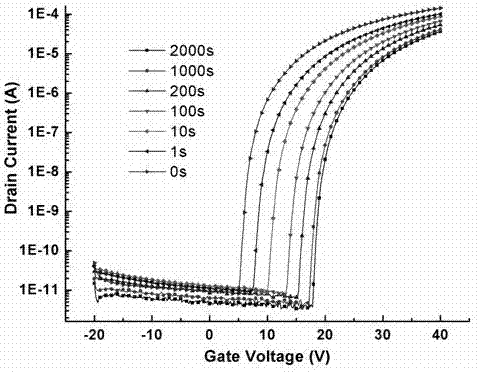

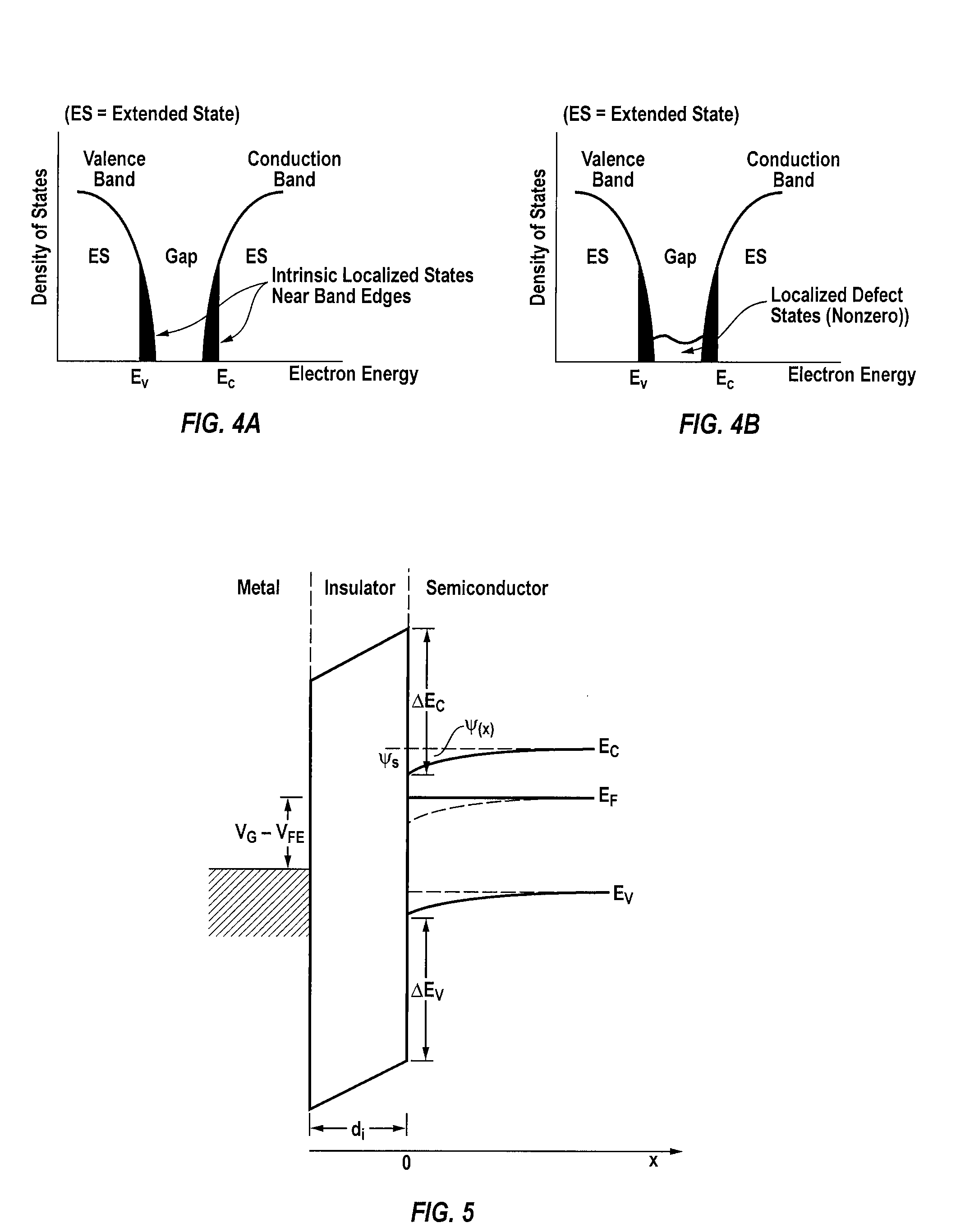

Oxide semiconductor film transistor trap state density extraction method

The invention relates to an oxide semiconductor film transistor trap state density extraction method, belongs to the technical field of a semiconductor device and includes semiconductor and gate insulation layer interface trap state extraction and internal trap state extraction of a semiconductor. The method comprises steps that (1), forward bias stresses with different durations are applied to an oxide semiconductor film transistor, and a corresponding transfer characteristic curve is tested; 2), based on transfer characteristic change rules, a threshold voltage drift mechanism is analyzed, and the change relation of the threshold voltage drift along with the time is determined; 3), if the threshold voltage drift and the applied stress time satisfy an expansion index model, characteristic temperature of an internal trap state of the semiconductor is extracted; and 4), the relationship between sub threshold amplitude and the trap state is utilized, semiconductor and gate insulation layer interface state density and internal trap state density of the semiconductor are extracted. The method is advantaged in that the film transistor interface trap state and the internal trap state can be simultaneously extracted, the calculation process is simpler compared with methods in the prior art, restriction conditions are a few, and the application scope is wide.

Owner:SUN YAT SEN UNIV

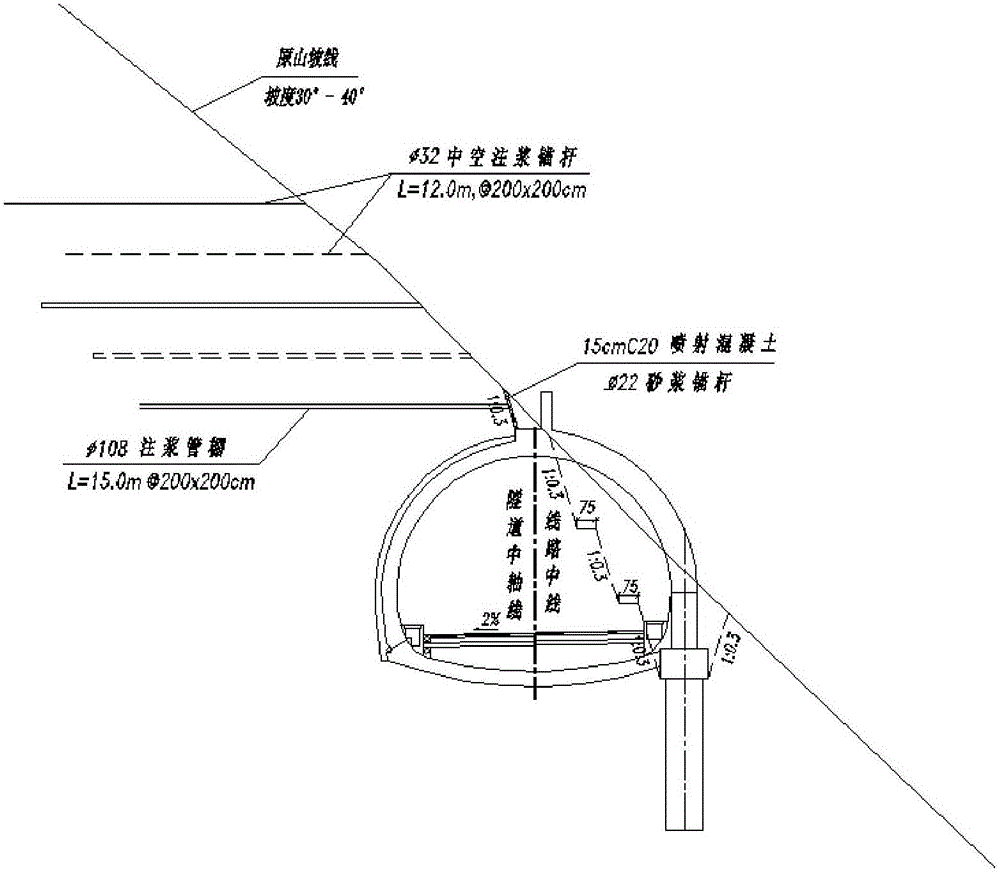

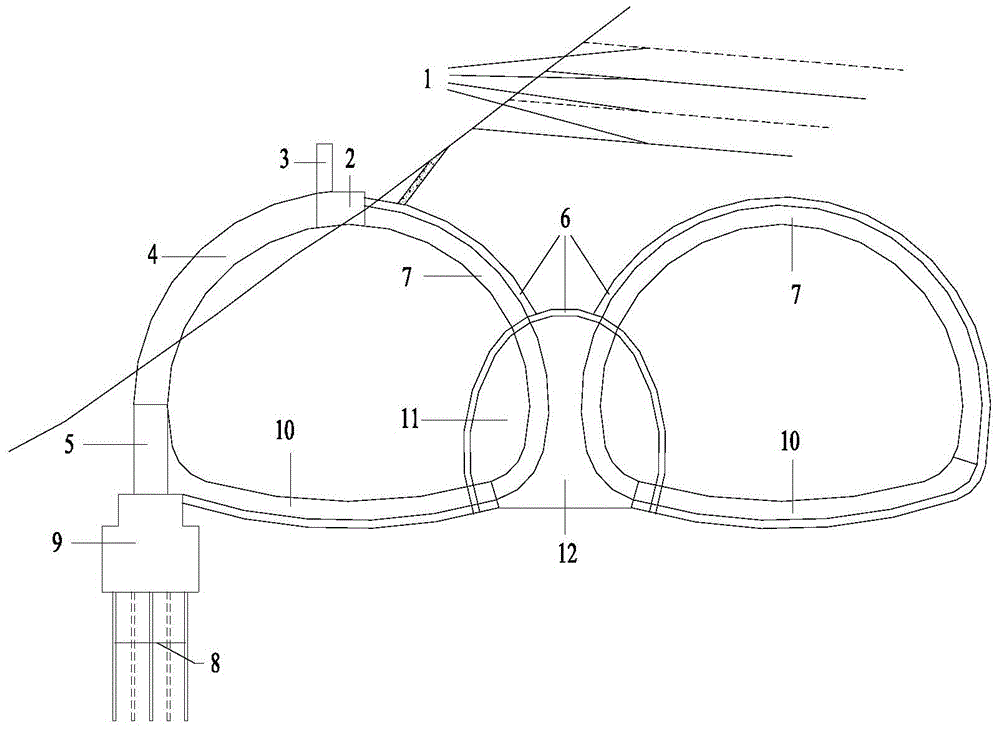

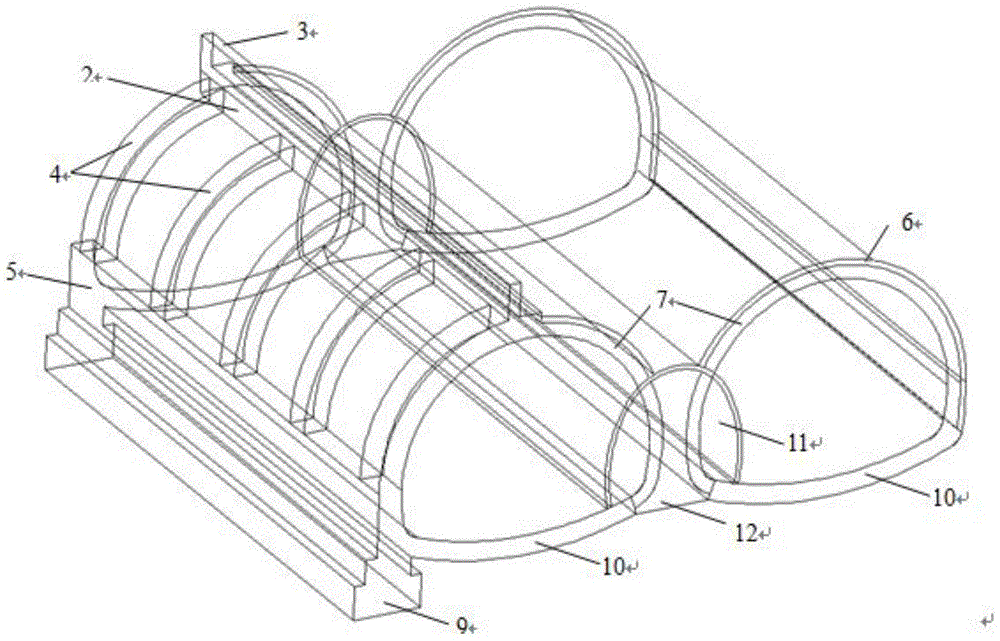

Permeable-rib type double-arch tunnel

The invention discloses a permeable-rib type double-arch tunnel which is of an embedded type asymmetrical double-arch structure. The permeable-rib type double-arch tunnel comprises an arch crown longitudinal beam, stone-falling preventing blocks, rib type arched beams, an anti-collision wall, primary lining layers, secondary lining layers, an expanded foundation, inverted arches, a middle guide cave and a middle partition wall. The secondary lining layer of an outer cave of the permeable-rib type double-arch tunnel, the arch crown longitudinal beam, the rib type arched beams and the anti-collision wall are uniformly poured into an overall structure and are connected with the inverted arches, the arch foot expanded foundation and the middle partition wall to form an annular load bearing system, so that bias stress of tunnel surrounding rock is balanced. The transverse pipe roof reinforcing range and the tunnel system anchor rod reinforcing range are connected, and a left cave and a right cave are dug step by step after left and right cave arch crown surrounding rock is strongly supported; the left cave and the right cave are connected by digging the middle guide cave and building the integral middle partition wall, meanwhile bias loads caused by mountain digging are borne, and the near-mountain double-arch tunnel structure with good ventilation and lighting effects, better stability and higher traffic capacity is formed.

Owner:ANHUI TRANSPORTATION HLDG GRP CO LTD +2

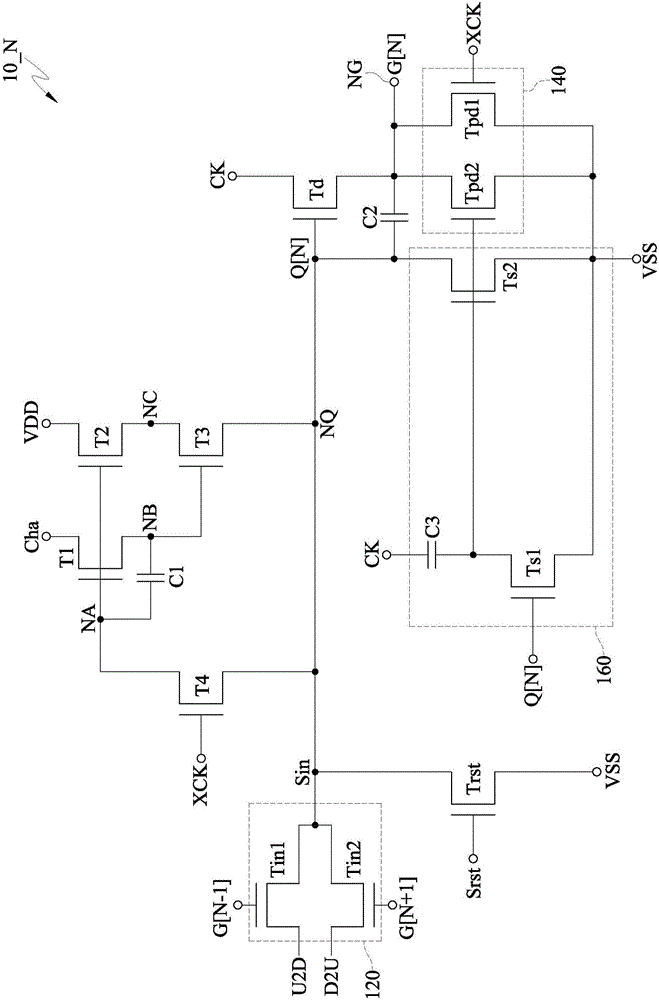

Grid electrode drive circuit

InactiveCN105869565AAvoid bias stressPrevent agingStatic indicating devicesCapacitanceComputer module

The invention provides a grid electrode drive circuit comprising a drive switch, an input module, a pull down module, a first switch, a second switch, a third switch, a capacitor and a reset switch; the drive switch is controlled by a first node voltage level; the input module is coupled to the first node; the pull down module is coupled to one end of the drive switch; two ends of the first node are respectively coupled to a charging signal end and a second node, and a control end is coupled to a storage node; two ends of the second switch are respectively coupled to a second reference voltage end and a third node, and a control end is coupled to the storage node; two ends of the third switch are respectively coupled to a third node and the first node, and a control end is coupled to the second node; two ends of the capacitor are respectively coupled to the storage node and the second node; two ends of the reset switch are respectively coupled to the first node and the first reference voltage end, and a control end is coupled to the reset signal end; a desired grid electrode drive signal is re-generated after a touch control sensing period, thus preventing elements in the grid electrode drive circuit from fast aging by the long time biased stress influence.

Owner:AU OPTRONICS CORP

Shift register

ActiveUS7595783B2Static indicating devicesCounting chain synchronous pulse countersShift registerLiquid-crystal display

A shift register for use with a liquid crystal display device includes a plurality of stages. A stage of the shift register includes a first controller, a second controller and an output buffer. The first controller charges and discharges a first node. The second controller charges and discharges a second node and a third node. The output buffer outputs a first output signal in response to the state of the first node and a second output signal in response to the state of the second and third nodes. The shift register may be adaptive to avoid a malfunction caused by a gate bias stress.

Owner:LG DISPLAY CO LTD

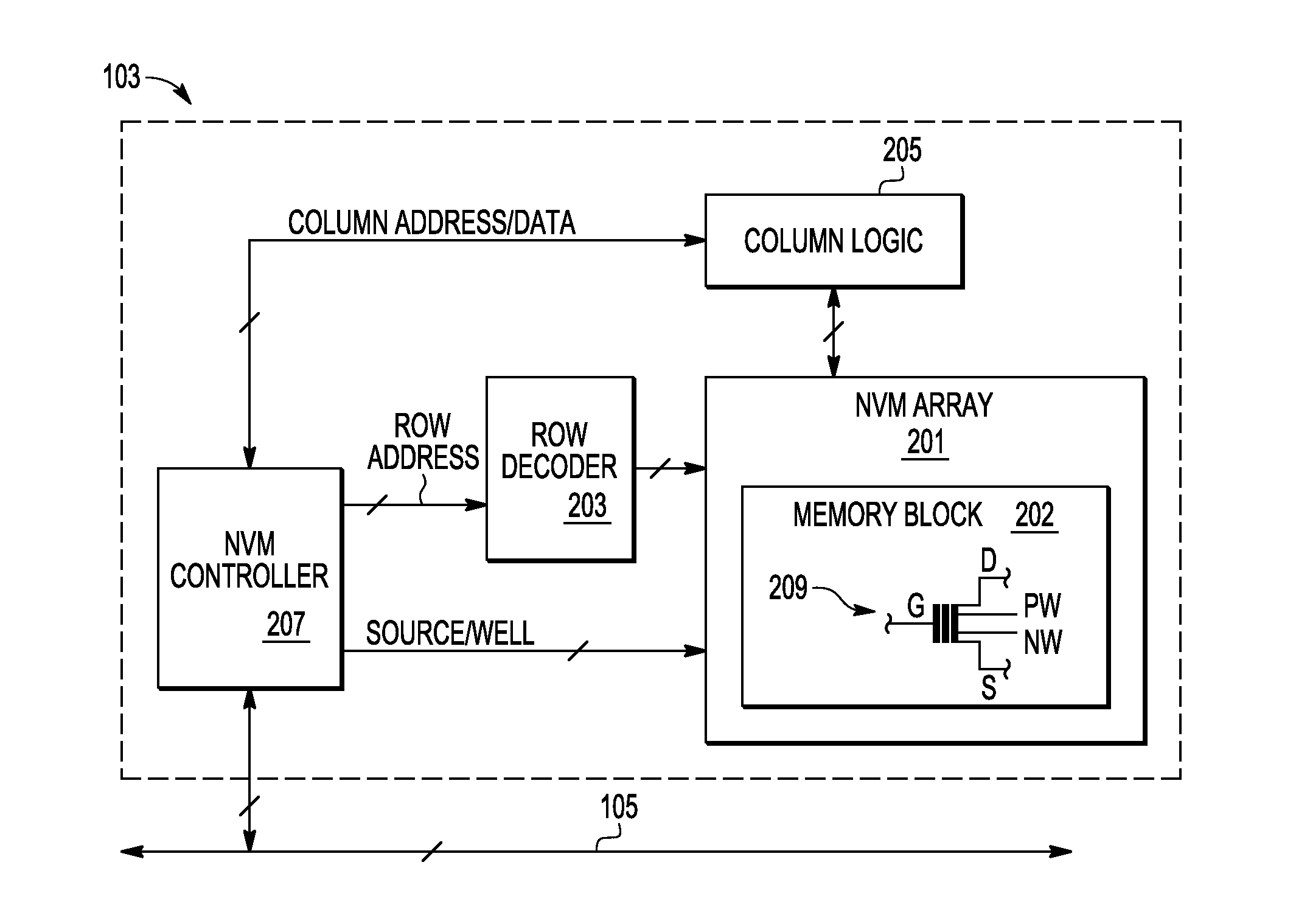

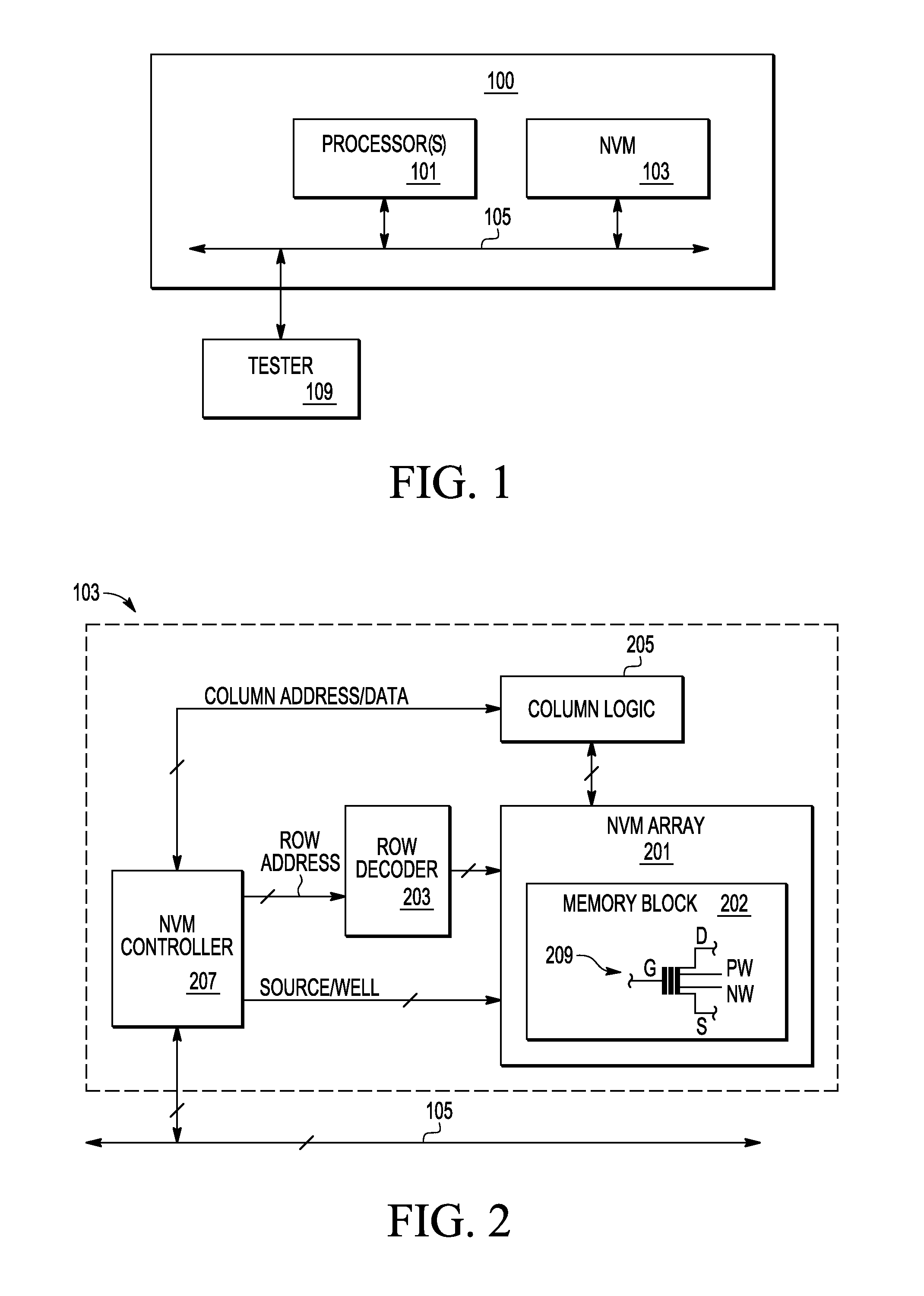

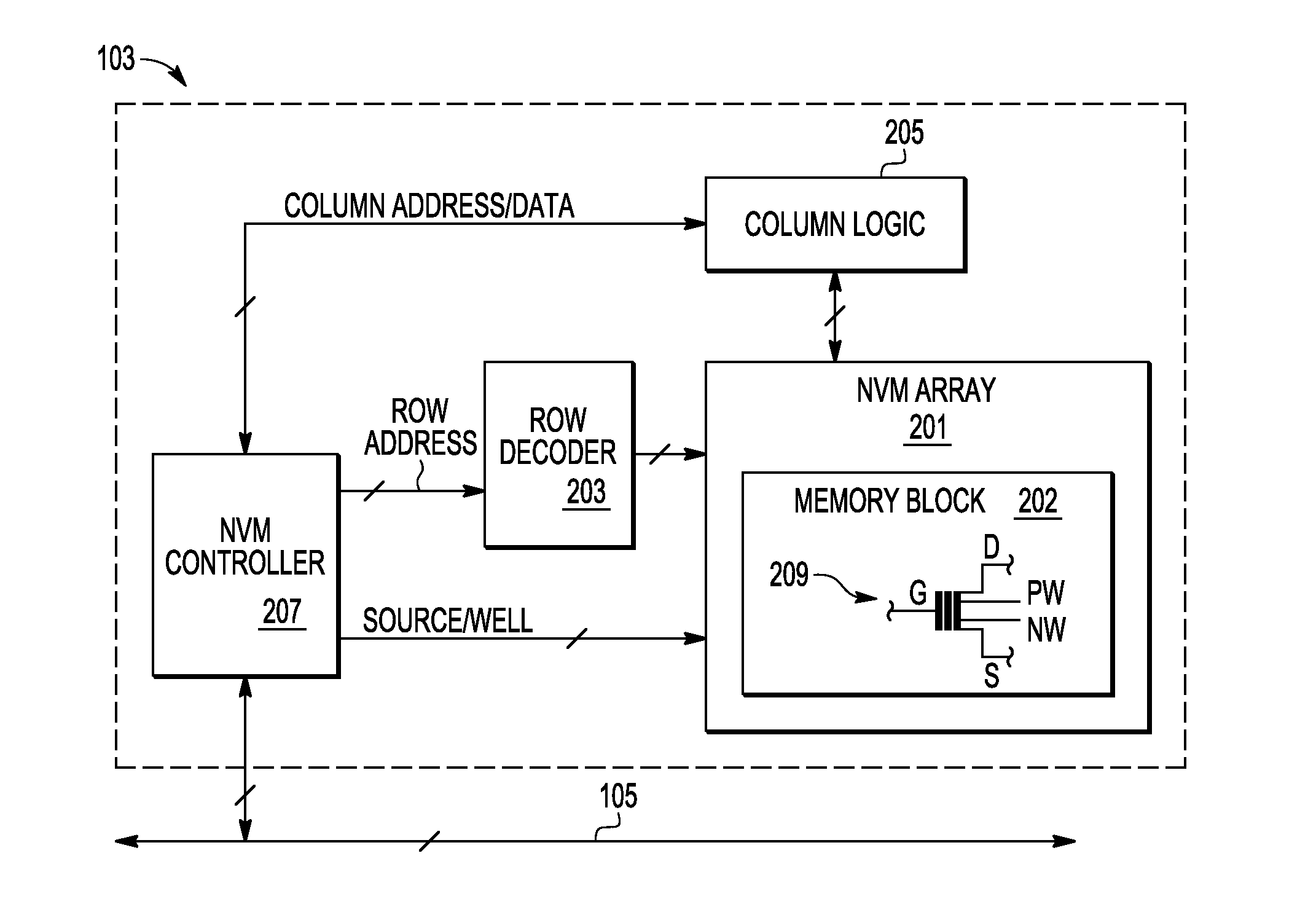

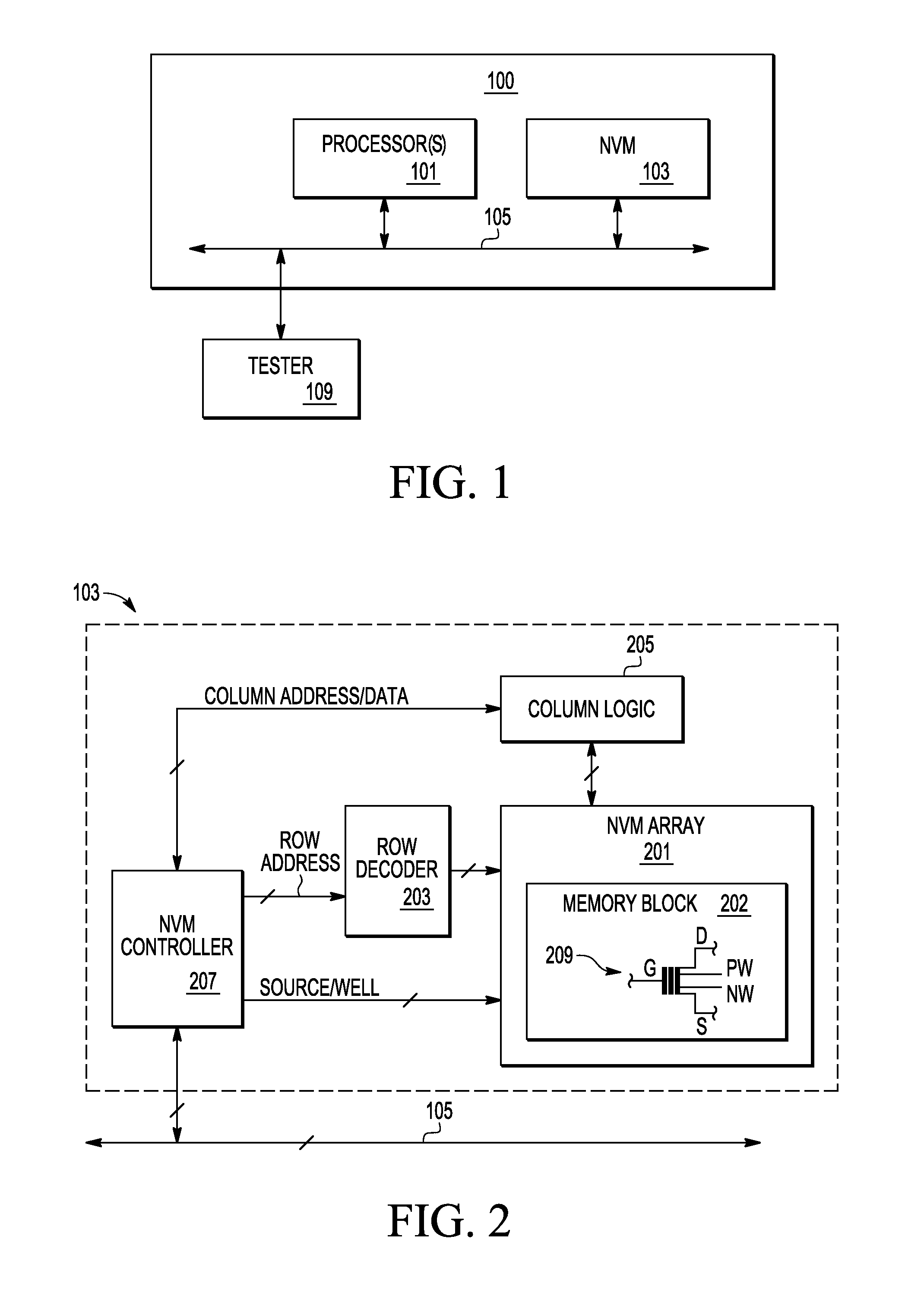

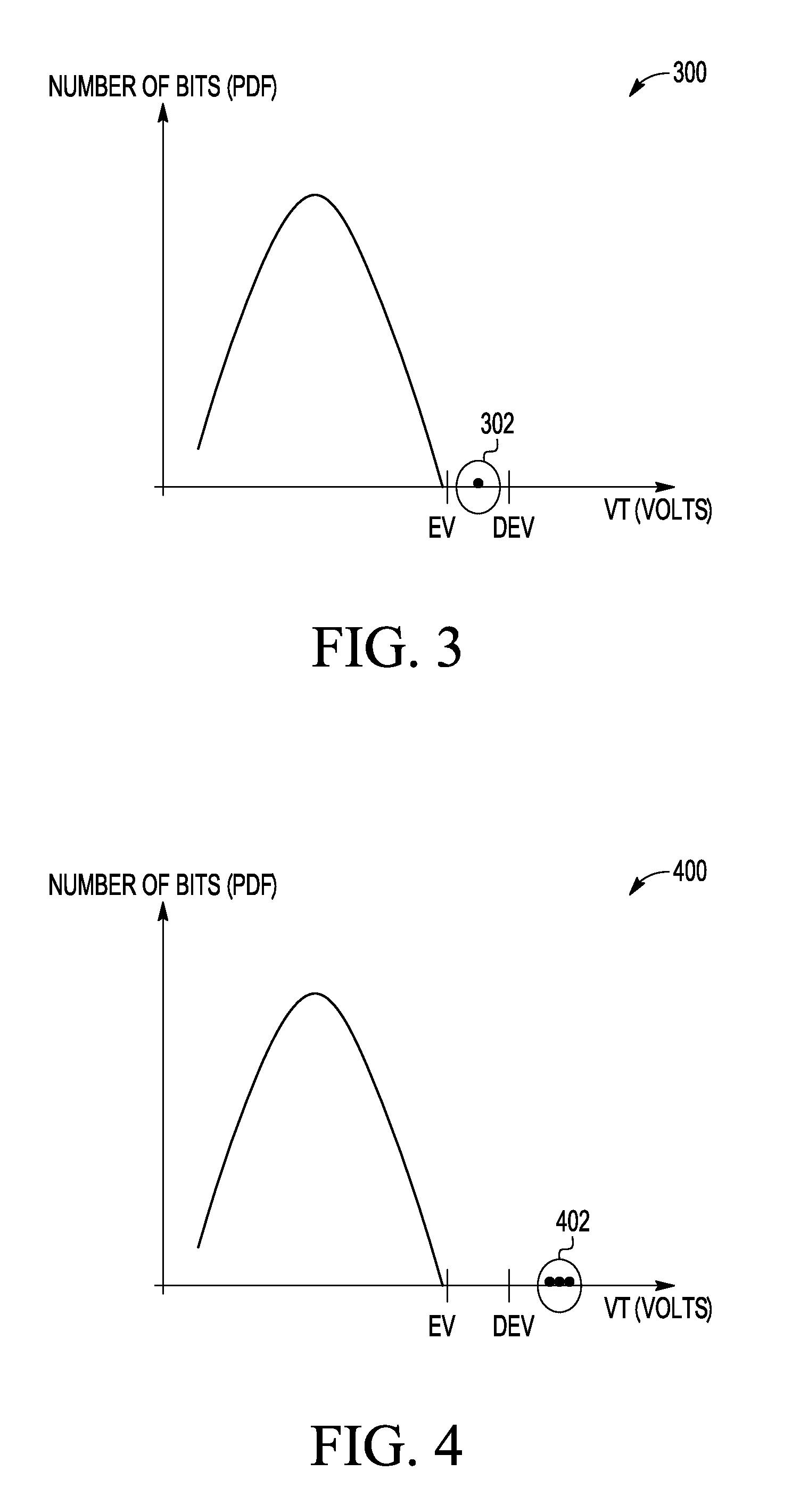

Test flow to detect a latent leaky bit of a non-volatile memory

A technique for detecting a leaky bit of a non-volatile memory includes erasing cells of a non-volatile memory. A bias stress is applied to the cells subsequent to the erasing. An erase verify operation is performed on the cells subsequent to the applying a bias stress to the cells. Finally, it is determined whether the cells pass or fail the erase verify operation based on whether respective threshold voltages of the cells are below an erase verify level.

Owner:NXP USA INC

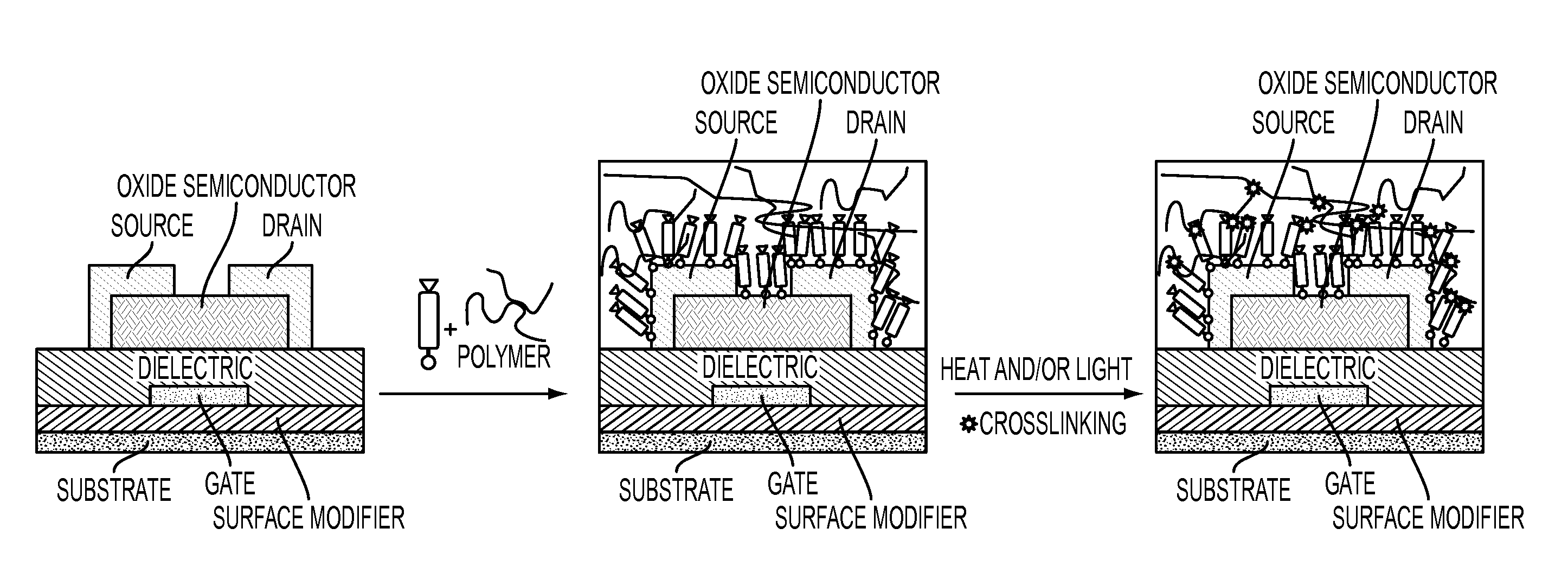

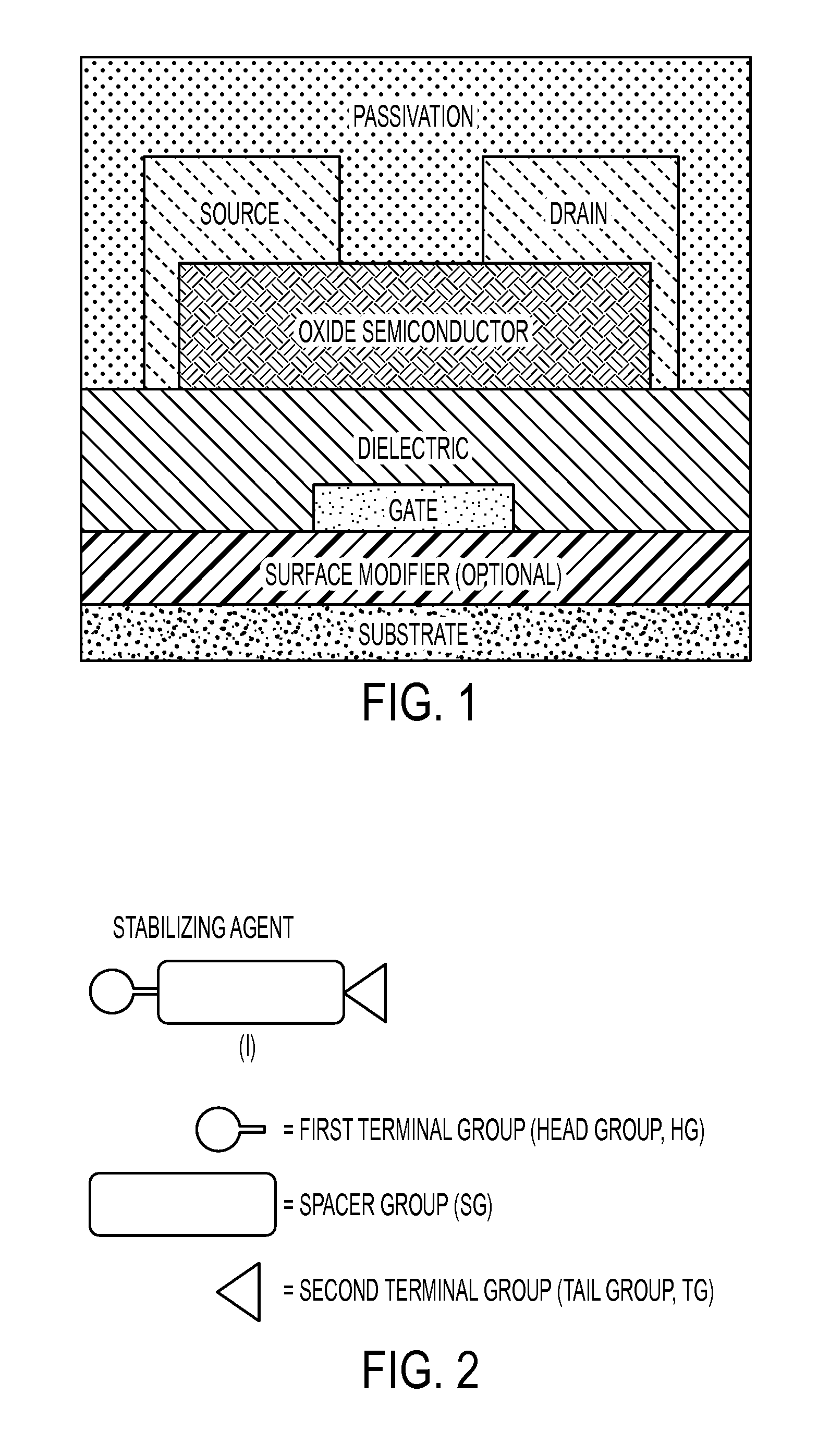

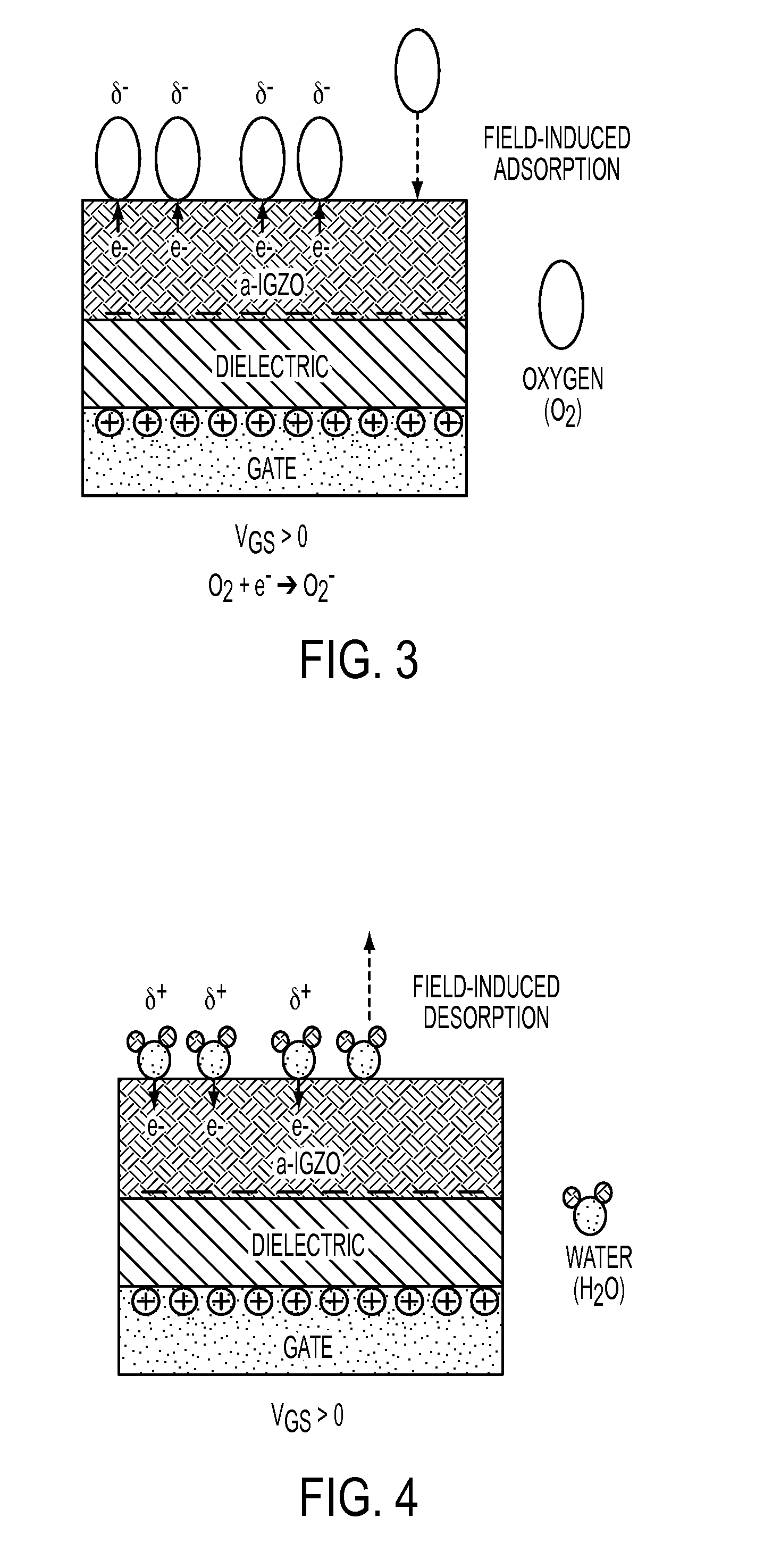

Coating Materials for Oxide Thin Film Transistors

InactiveUS20140021465A1Improve device stabilityImproved surface dehydrationTransistorSolid-state devicesOxide thin-film transistorBias stress

The present teachings provide a coating composition (a passivation formulation) for preparing a coating material in a metal oxide thin film transistor, where the coating material comprises a polymer blend including a polymer and a stabilizing agent. Incorporation of a stabilizing agent according to the present teachings in the coating material can lead to improved device performance of the metal oxide thin film transistor, in particular, reduced shift in the threshold voltage and long-term bias-stress stability.

Owner:FLEXTERRA INC

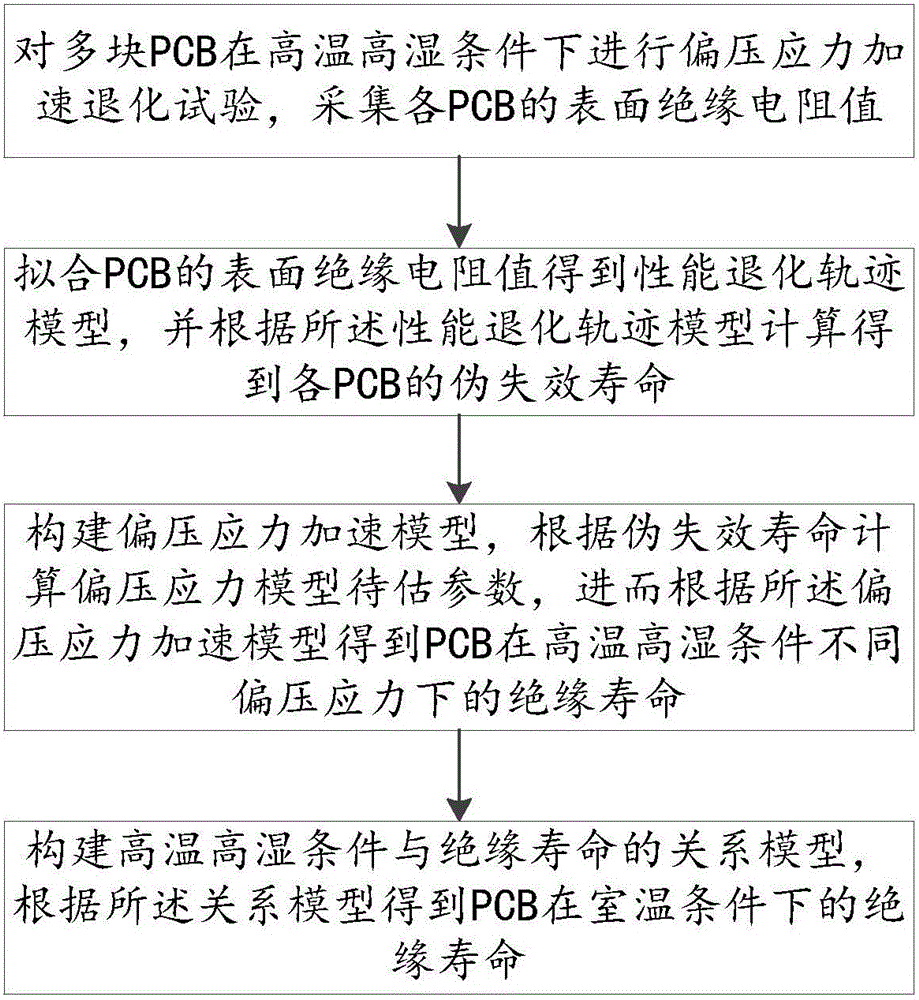

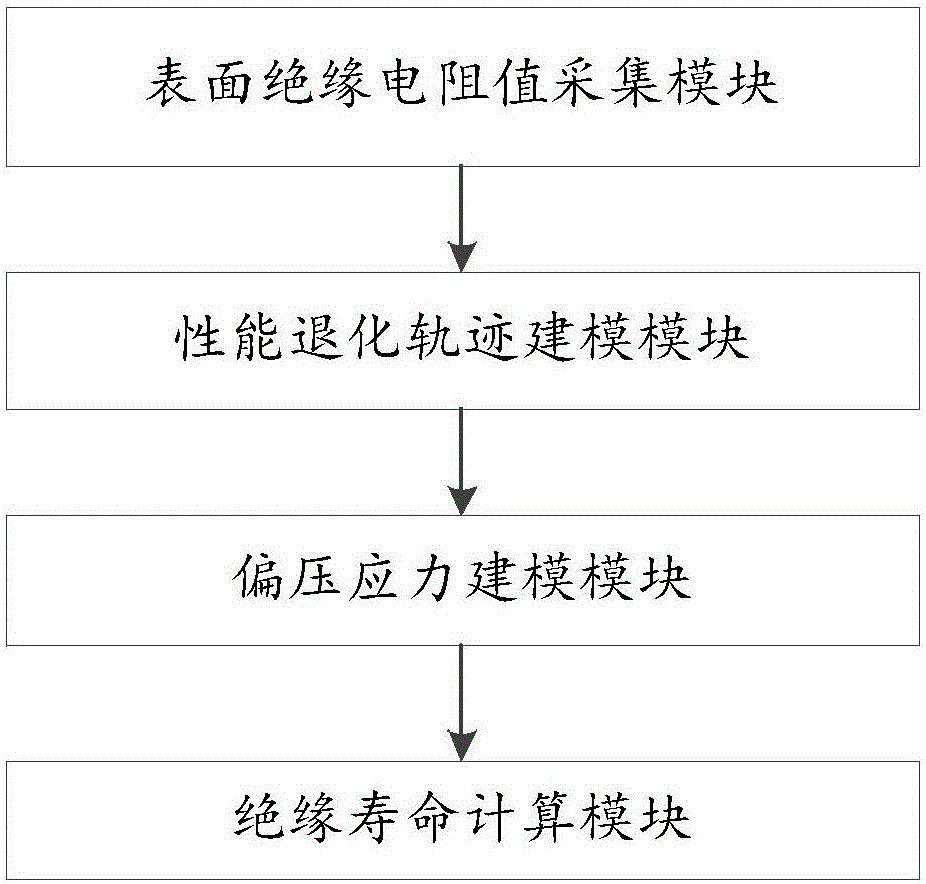

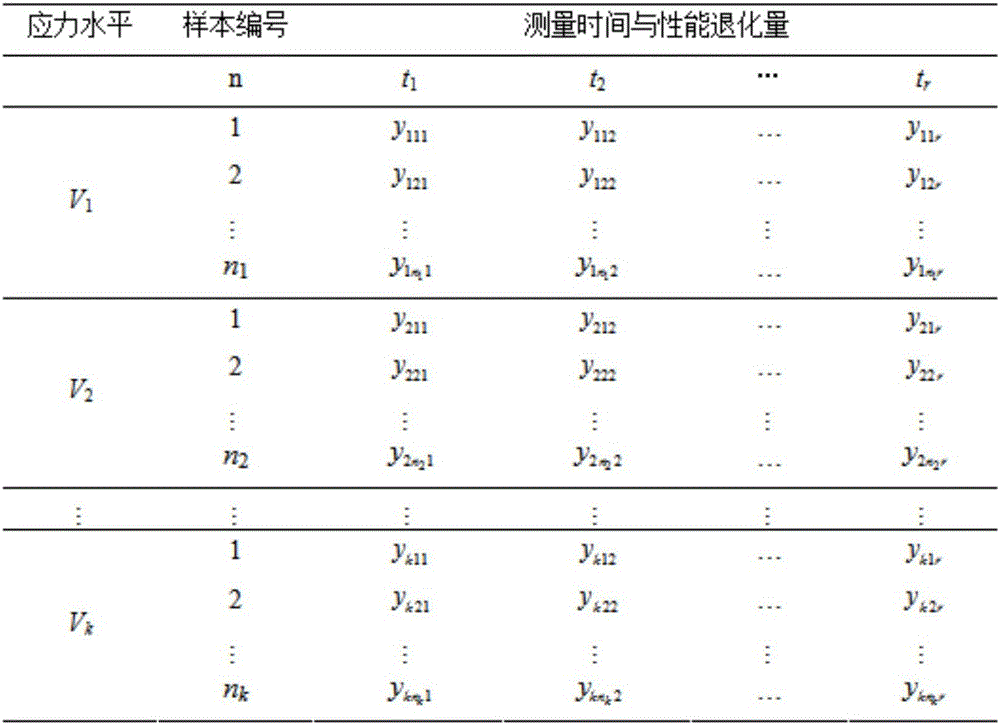

Accelerated degradation test based method and system for rapid prediction of PCB insulation life

InactiveCN105954667ASolve the technical problem of rapid prediction of PCB insulation lifeQuickly get the characteristics of the degraded trajectoryPrinted circuit testingRelational modelPredictive methods

The present invention relates to a method and system for rapid prediction of PCB insulation life based on accelerated degradation tests. The prediction method includes the following steps: step S1, conducting bias stress accelerated degradation tests on multiple PCBs under high temperature and high humidity conditions, collecting various The surface insulation resistance value of the PCB; step S2, fitting the surface insulation resistance value of the PCB to obtain a performance degradation trajectory model, and calculating the pseudo-failure life of each PCB according to the performance degradation trajectory model; step S3, constructing a bias stress acceleration model , calculate the estimated parameters of the bias stress acceleration model according to the pseudo-failure life, and then obtain the insulation life of the PCB under different bias stresses under high temperature and high humidity conditions according to the bias stress acceleration model; step S4, construct the high temperature and high humidity conditions and insulation life A relational model of life, according to the relational model, the insulation life of the PCB at room temperature is obtained. The invention solves the problem of quickly predicting the life of PCB insulation within a limited time by building an acceleration model, and is especially suitable for the technical field of PCB reliability.

Owner:YANTAI UNIV

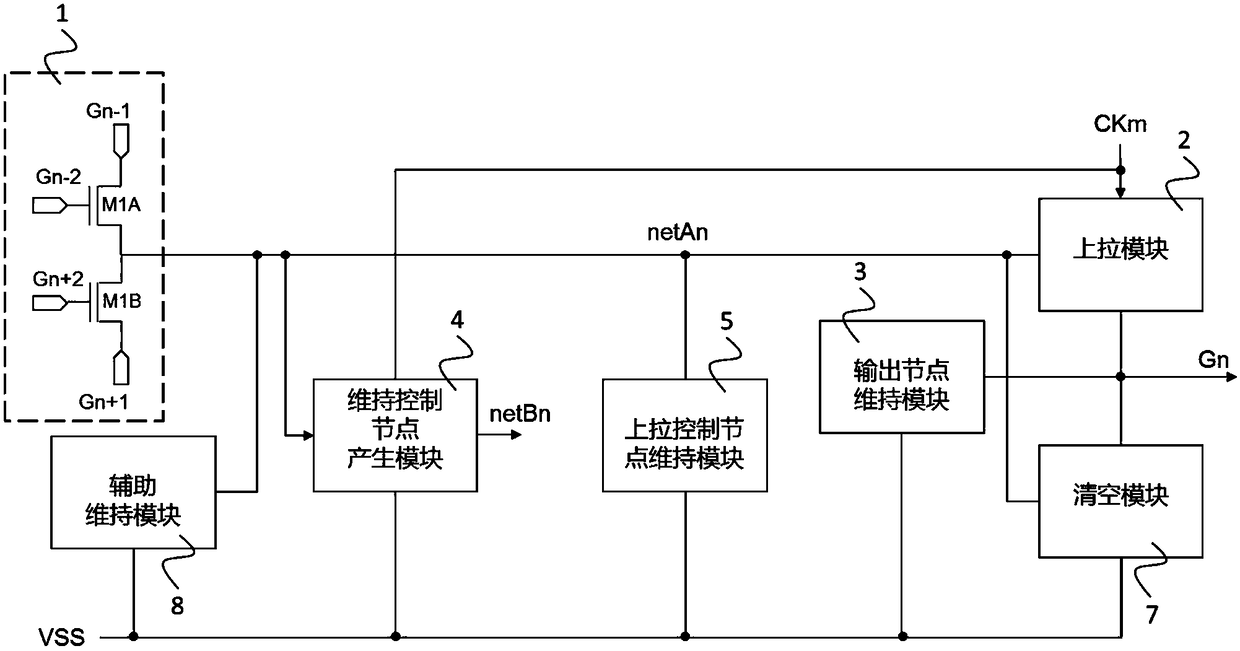

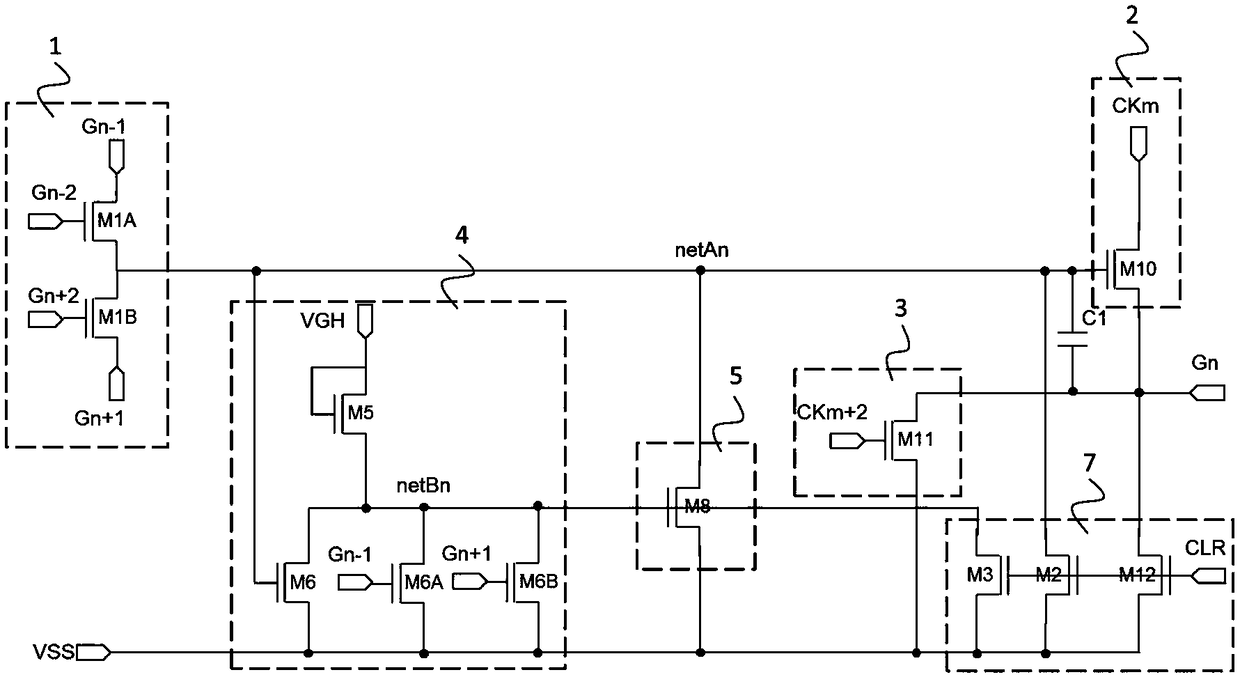

Gate scanning driving circuit

ActiveCN108154856AAvoid functional failureReduce in quantityStatic indicating devicesComputer moduleEngineering

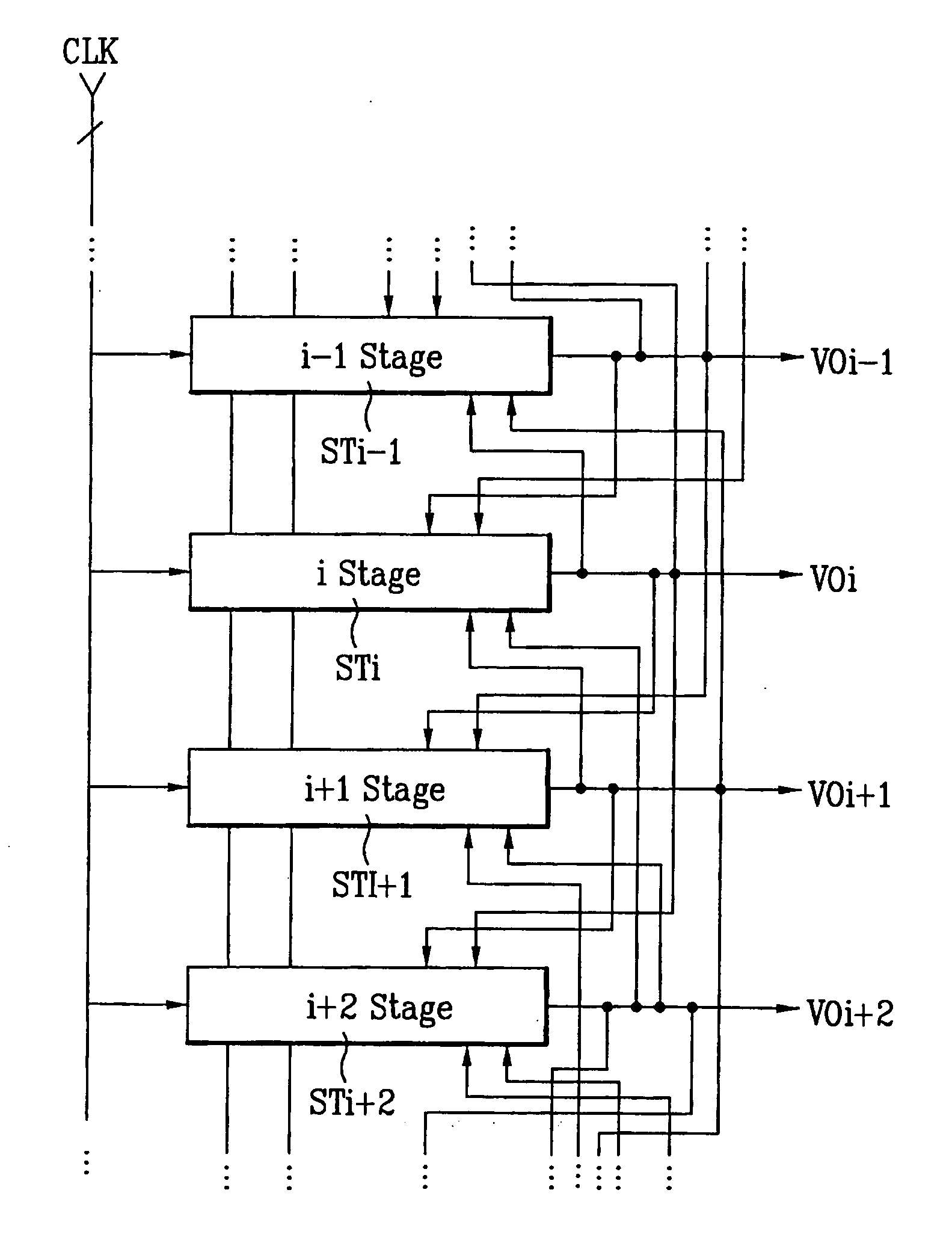

The invention discloses a gate scanning driving circuit. The gate scanning driving circuit comprises N (N is larger than 4 and is a positive integer) driving circuit units; a nth (n is larger than orequal to 1 and smaller than or equal to N, and is a positive integer) driving circuit unit comprises a pull-up control module, a pull-up module, an output-node maintaining module, a maintaining-control-node generating module and a pull-up control node maintaining module; the pull-up control module of the nth driving circuit unit comprises two thin film transistors, one thin film transistor is subjected to precharging of forward-and-reverse scanning controlling with scanning signals of a (n-1)th driving circuit unit and a (n-2)th driving circuit, and the other thin film transistor is subjectedto precharging of forward-and-reverse scanning controlling with scanning signals of a (n+1)th driving circuit unit and a (n+2)th driving circuit. Bias stress and threshold voltage shift of the thin film transistors are reduced, and the stability of the circuit is enhanced.

Owner:NANJING CEC PANDA LCD TECH

Electronic devices with low refresh rate display pixels

ActiveUS10304378B2Mitigate threshold voltage hysteresisPrevents noticeable luminance dimmingStatic indicating devicesDisplay deviceEngineering

A display may have an array of organic light-emitting diode display pixels operating at a low refresh rate. Each display pixel may have six thin-film transistors and one capacitor. One of the six transistors may serve as the drive transistor and may be compensated using the remaining five transistors and the capacitor. One or more on-bias stress operations may be applied before threshold voltage sampling to mitigate first frame dimming. Multiple anode reset and on-bias stress operations may be inserted during vertical blanking periods to reduce flicker and maintain balance and may also be inserted between successive data refreshes to improve first frame performance. Two different emission signals controlling each pixel may be toggled together using a pulse width modulation scheme to help provide darker black levels.

Owner:APPLE INC

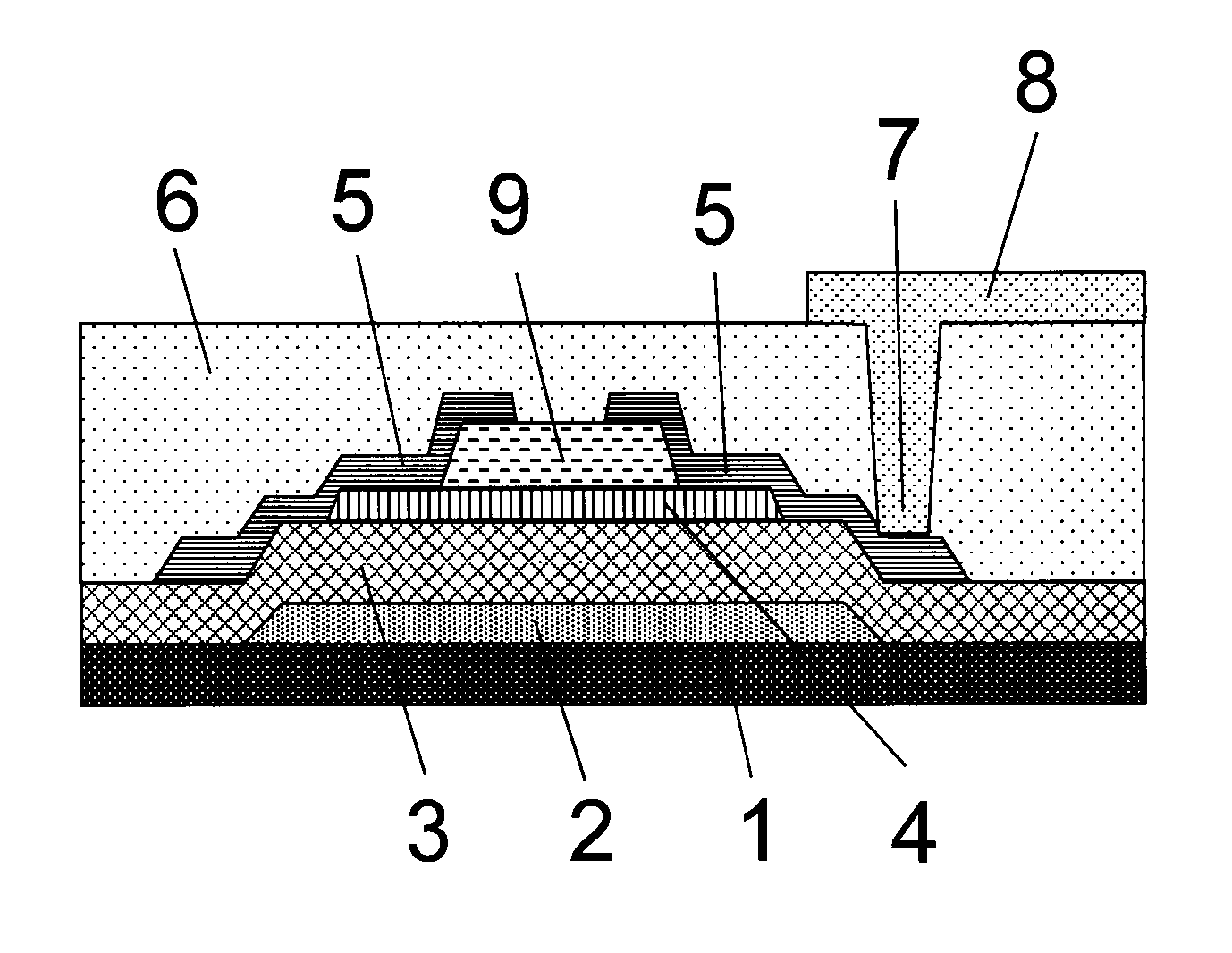

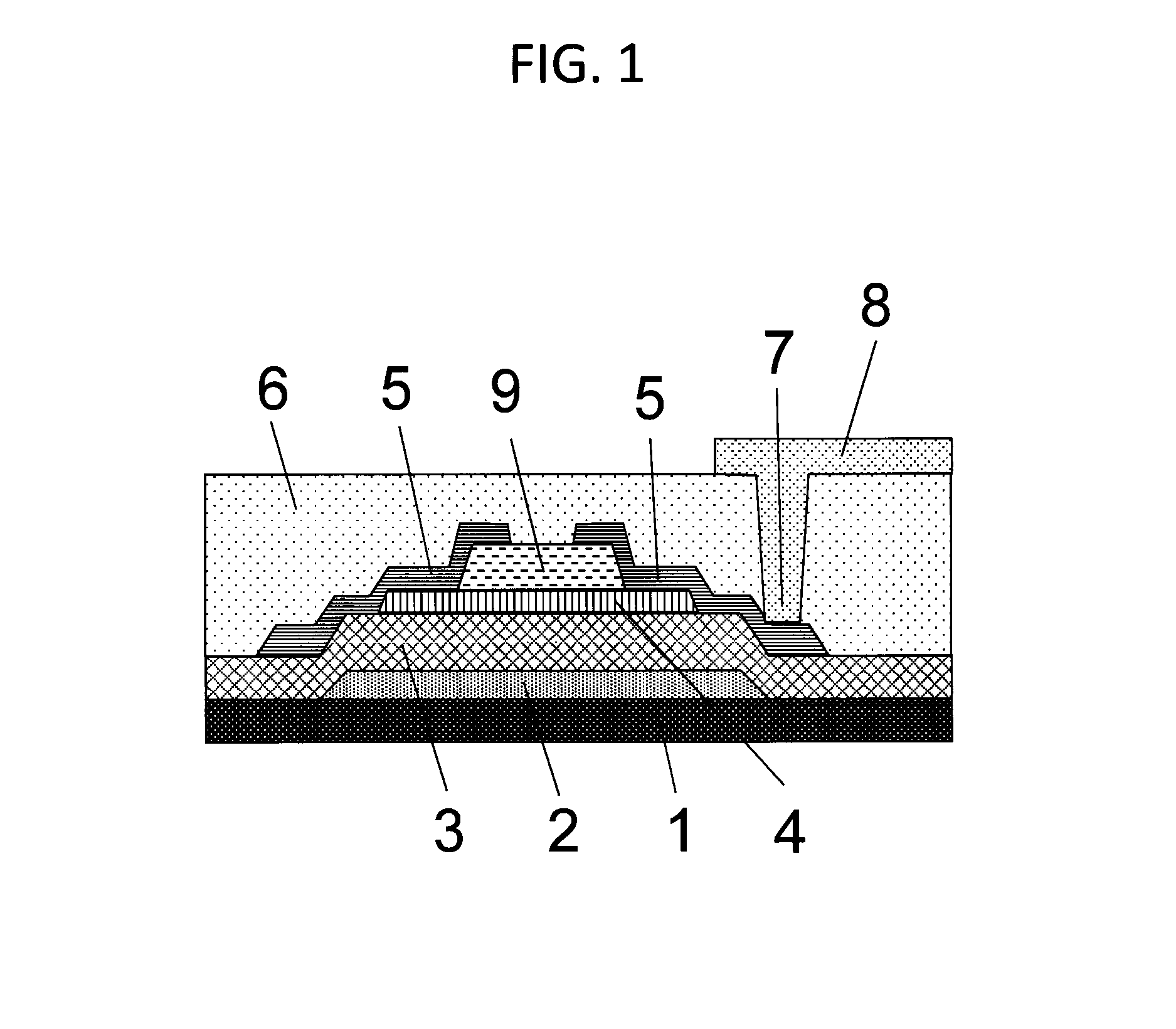

Thin film transistor and display device

ActiveUS20150206978A1Excellent switching characteristic and stress stabilityImprove reliabilityTransistorSolid-state devicesHydrogen concentrationOxide thin-film transistor

Provided is a thin film transistor comprising an oxide semiconductor thin film layer and has a threshold voltage that does not change much due to light, a bias stress or the like, thereby exhibiting excellent stress stability. A thin film transistor of the present invention is provided with: a gate electrode; two or more oxide semiconductor layers that are used as a channel layer; an etch stopper layer for protecting the surfaces of the oxide semiconductor layers; a source-drain electrode; and a gate insulator film interposed between the gate electrode and the channel layer. The metal elements constituting an oxide semiconductor layer that is in direct contact with the gate insulator film are In, Zn and Sn. The hydrogen concentration in the gate insulator film, which is in direct contact with the oxide semiconductor layer, is controlled to 4 atomic % or less.

Owner:KOBE STEEL LTD

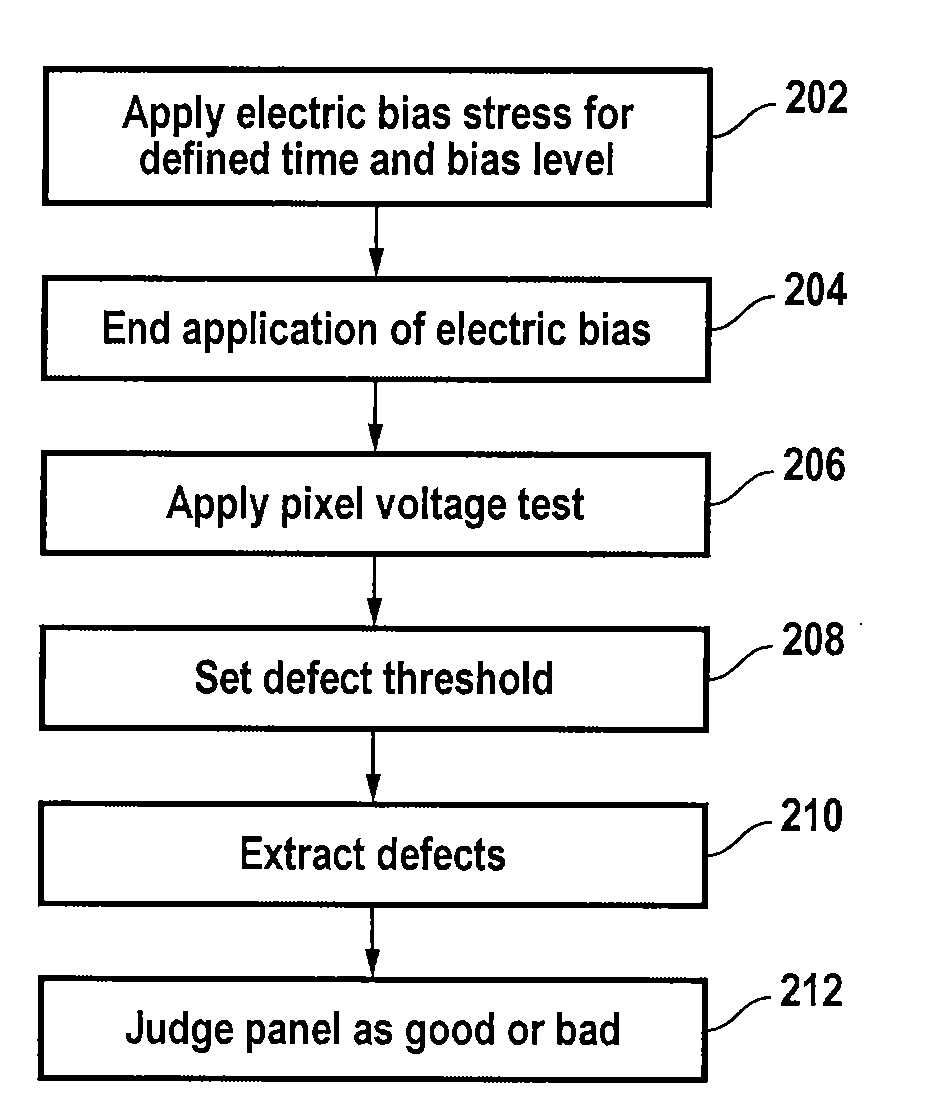

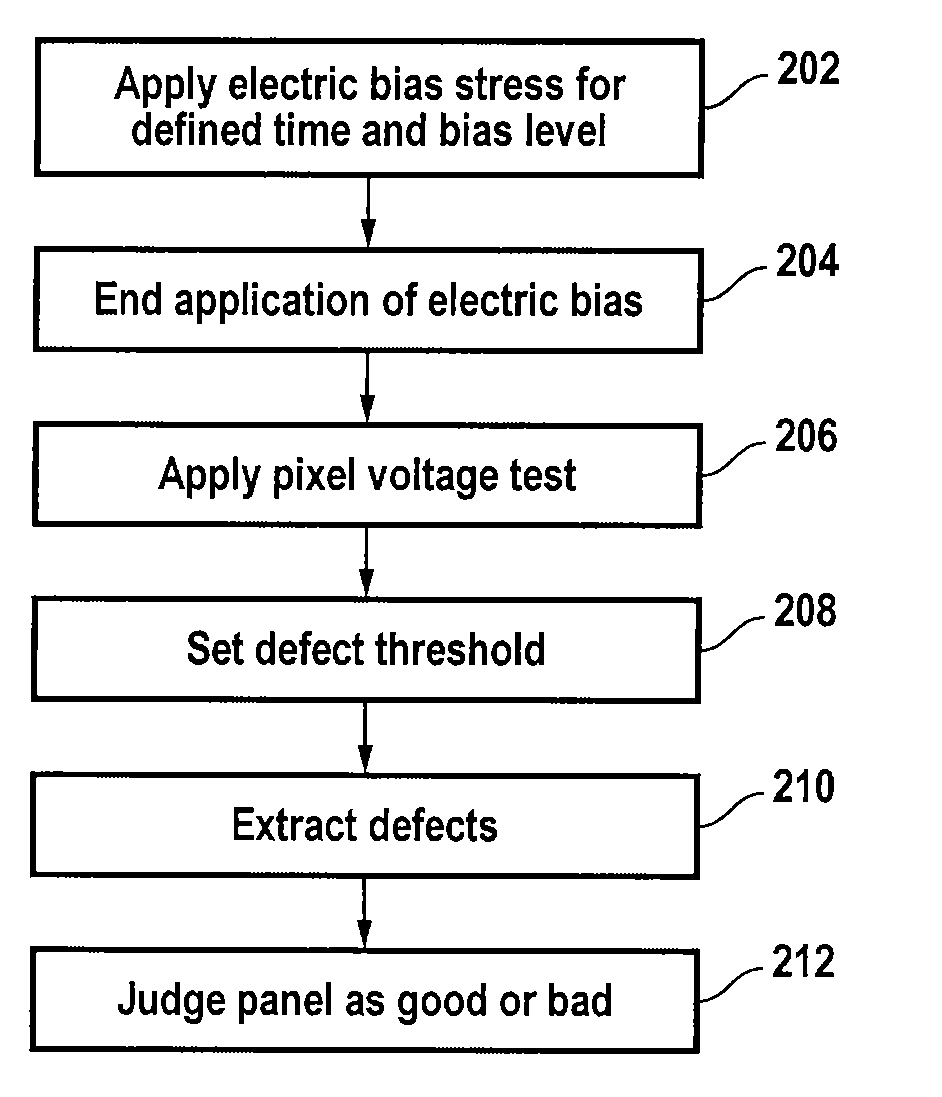

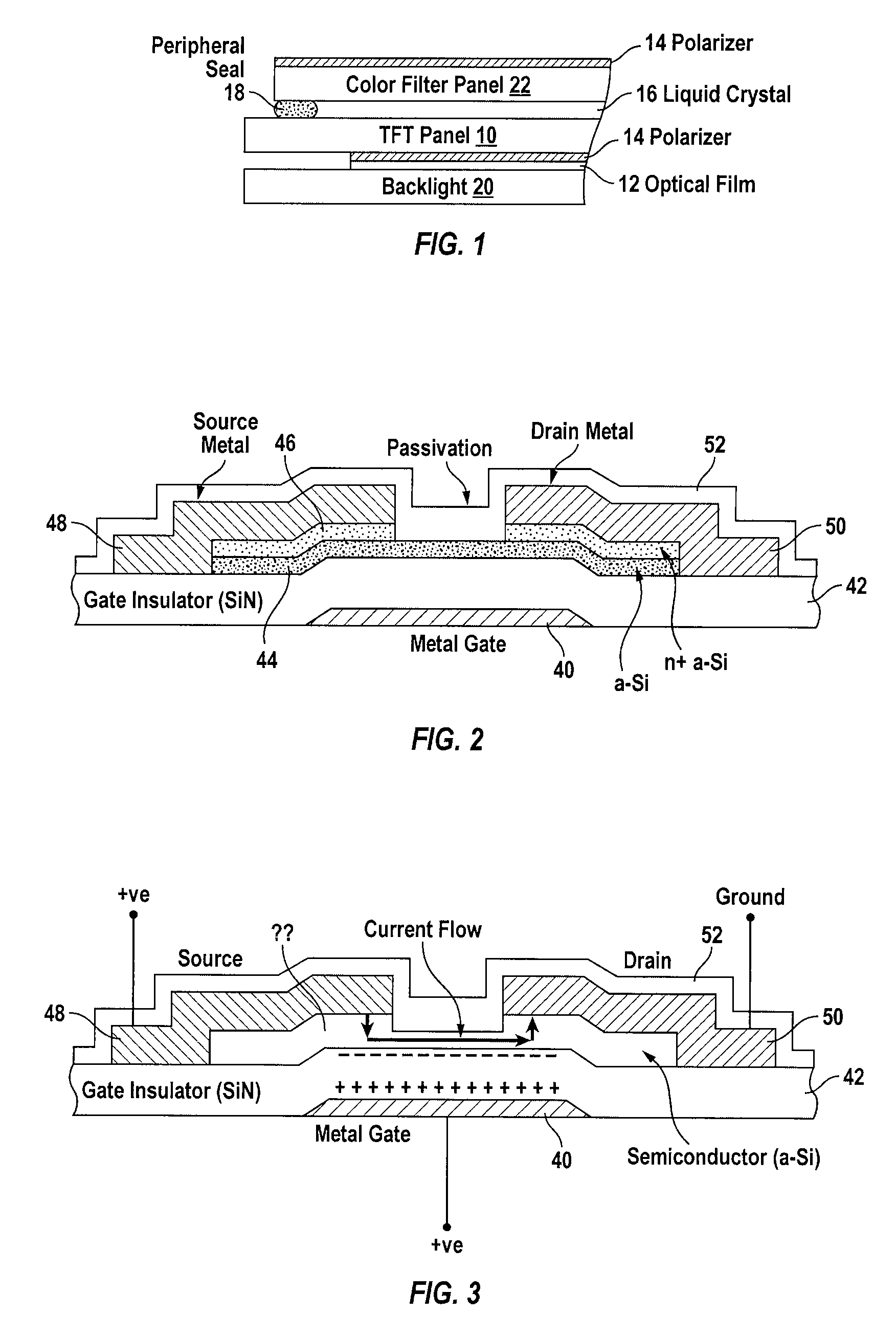

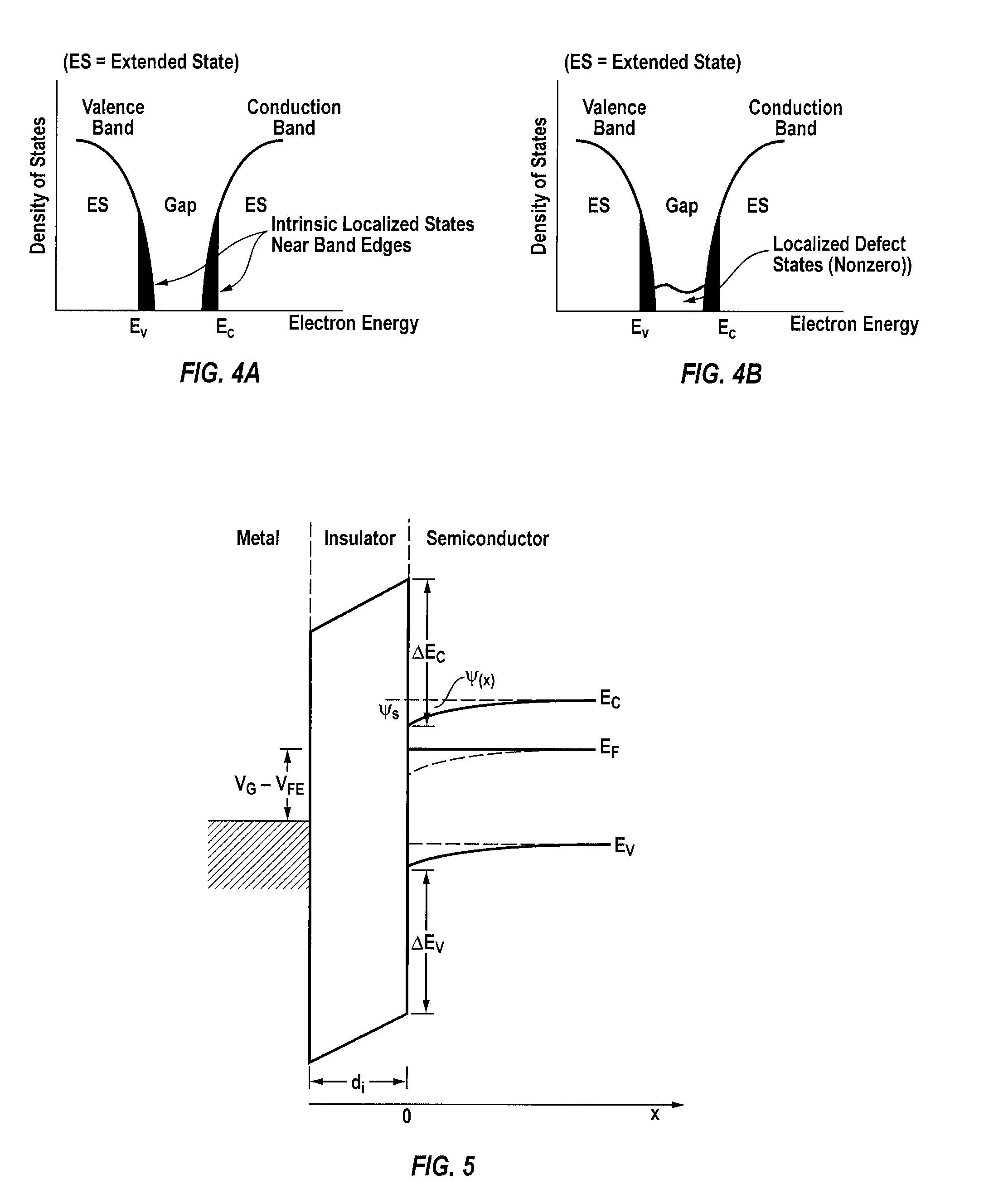

Array testing method using electric bias stress for TFT array

ActiveUS20080024157A1Low costElectric discharge tubesStatic indicating devicesElectricityLiquid-crystal display

Owner:ORBOTECH LTD

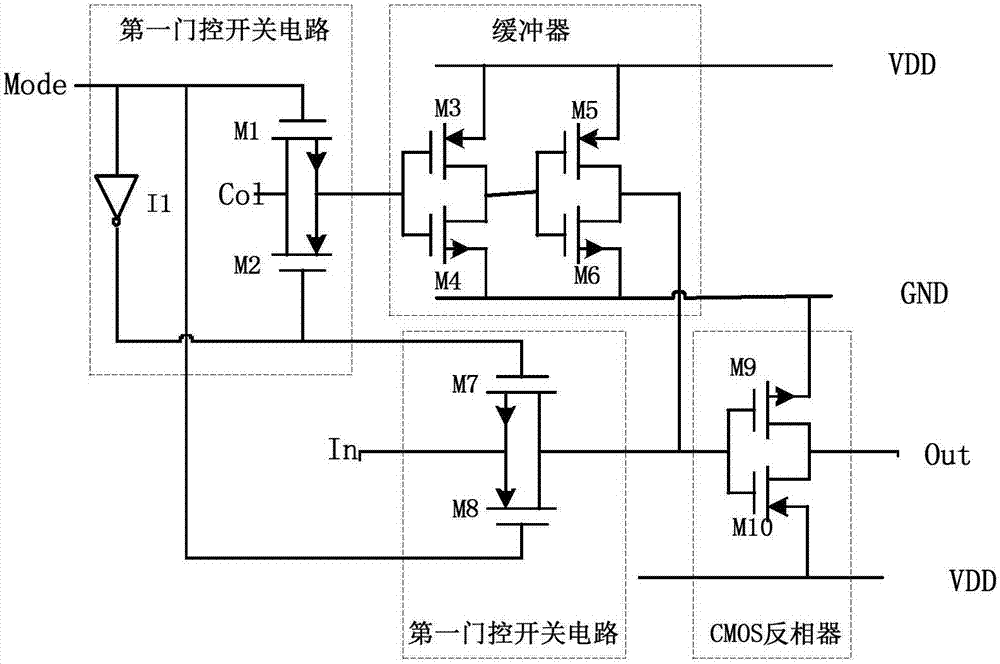

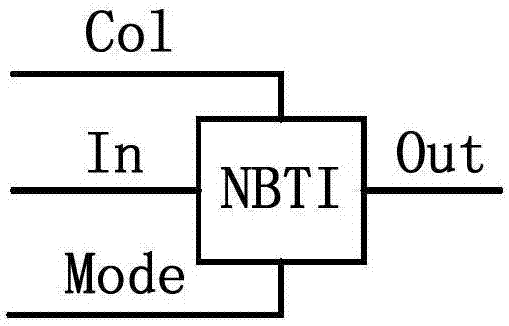

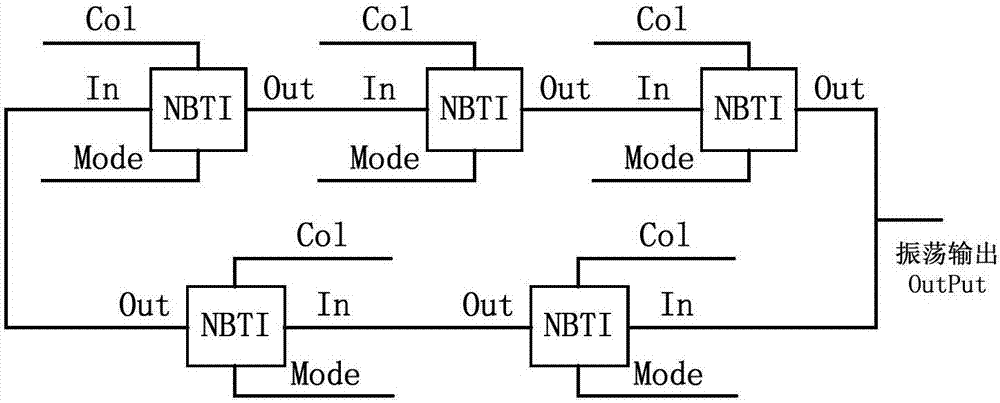

MOS tube parameter degradation circuit and MOS tube parameter degradation early warning circuit

ActiveCN107039299AImprove accuracyAccurately analyze the degree of degradationSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCMOSControl signal

The invention relates to a MOS tube parameter degradation circuit, which comprises a CMOS inverter, a stress applying circuit and a parameter measuring circuit. The CMOS inverter comprises a first PMOS tube and a first NMOS tube. The stress applying circuit becomes on under the control of a first mode-select signal. After the stress applying circuit receives a control signal, it exerts negative gate voltage bias stress or positive gate voltage bias stress on the first PMOS tube of the CMOS inverter. The parameter measuring circuit becomes on under the control of a second mode-select signal. The parameter measuring circuit receives an input signal and transmits the input signal to the input end of the CMOS inverter. The first mode-select signal and the second mode-select signal are compensation signals. With the invention, it is possible to make the MOS tube parameter degradation testing result more accurate. In addition, the invention also relates to a MOS tube parameter degradation early warning circuit, which can accurately analyze the influence of NBTI effect on PMOS tube component parameters.

Owner:CHINA ELECTRONICS PROD RELIABILITY & ENVIRONMENTAL TESTING RES INST

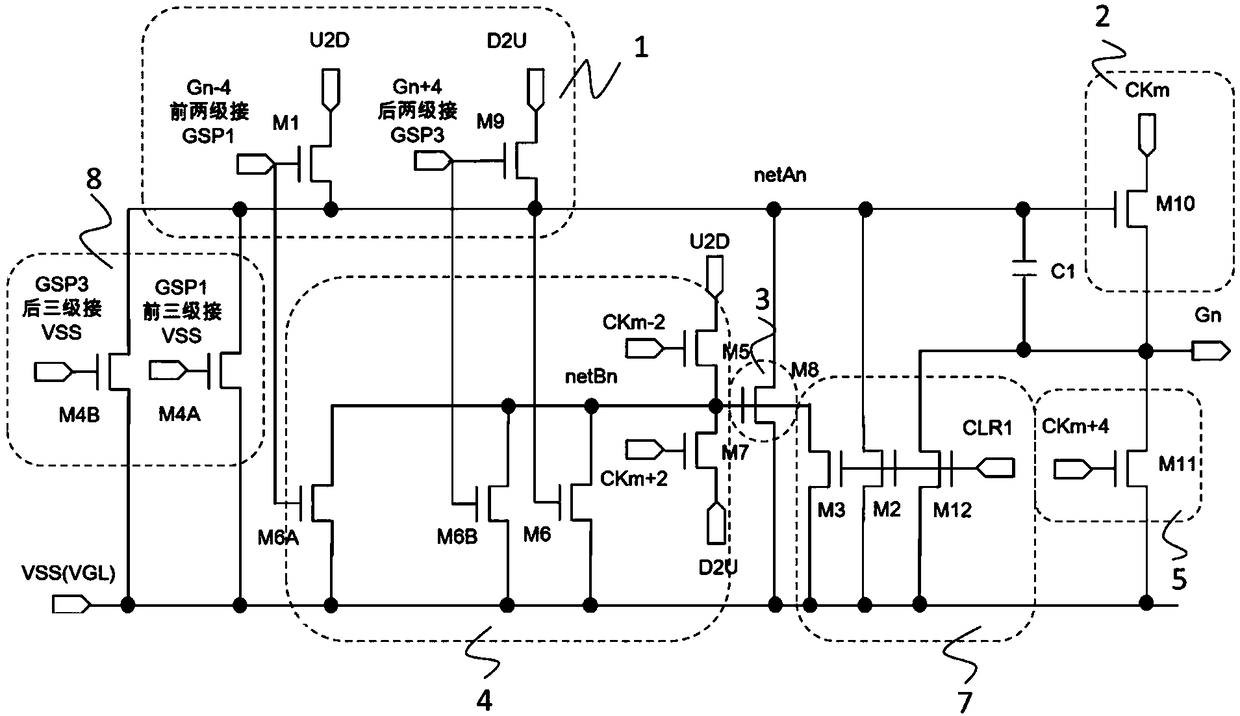

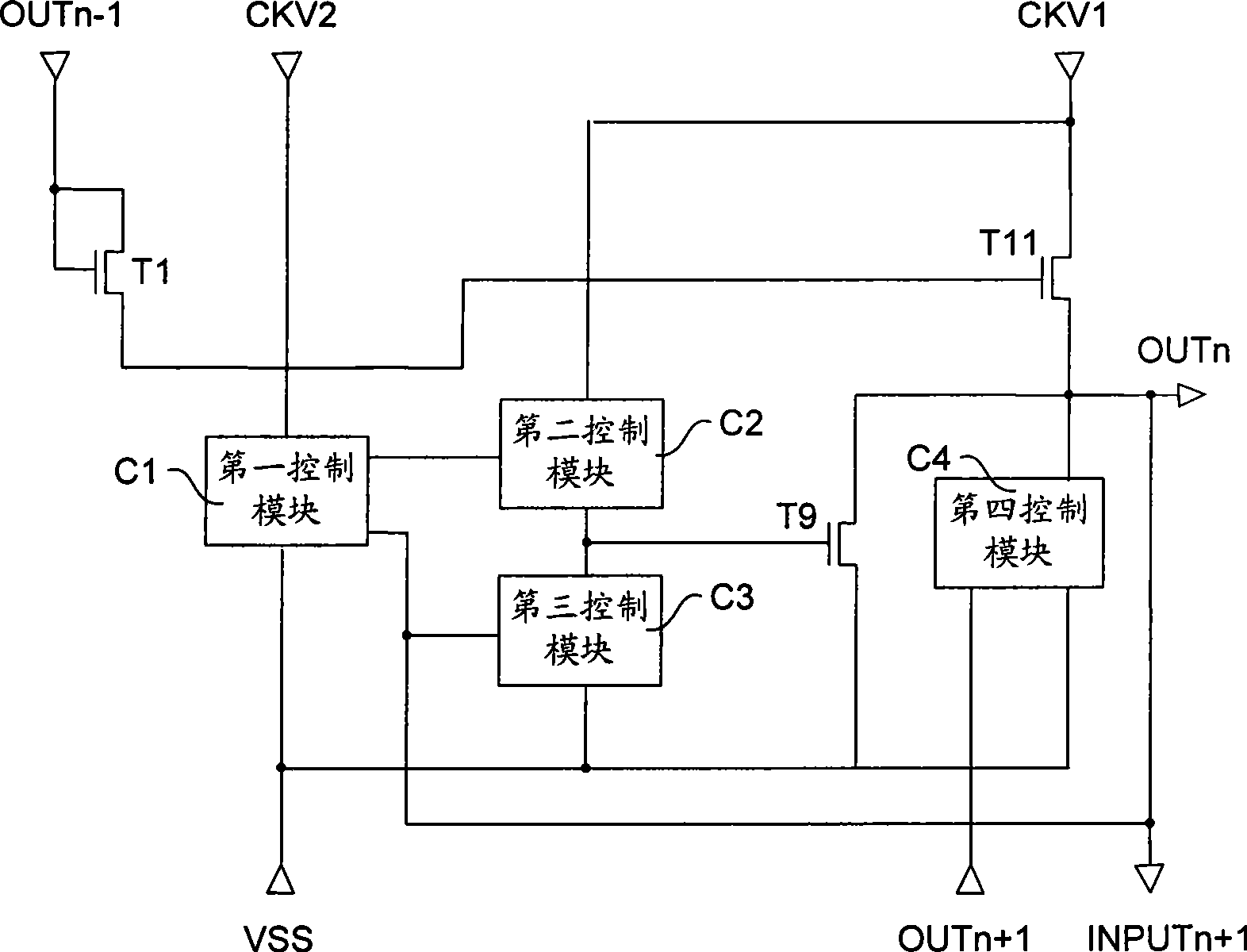

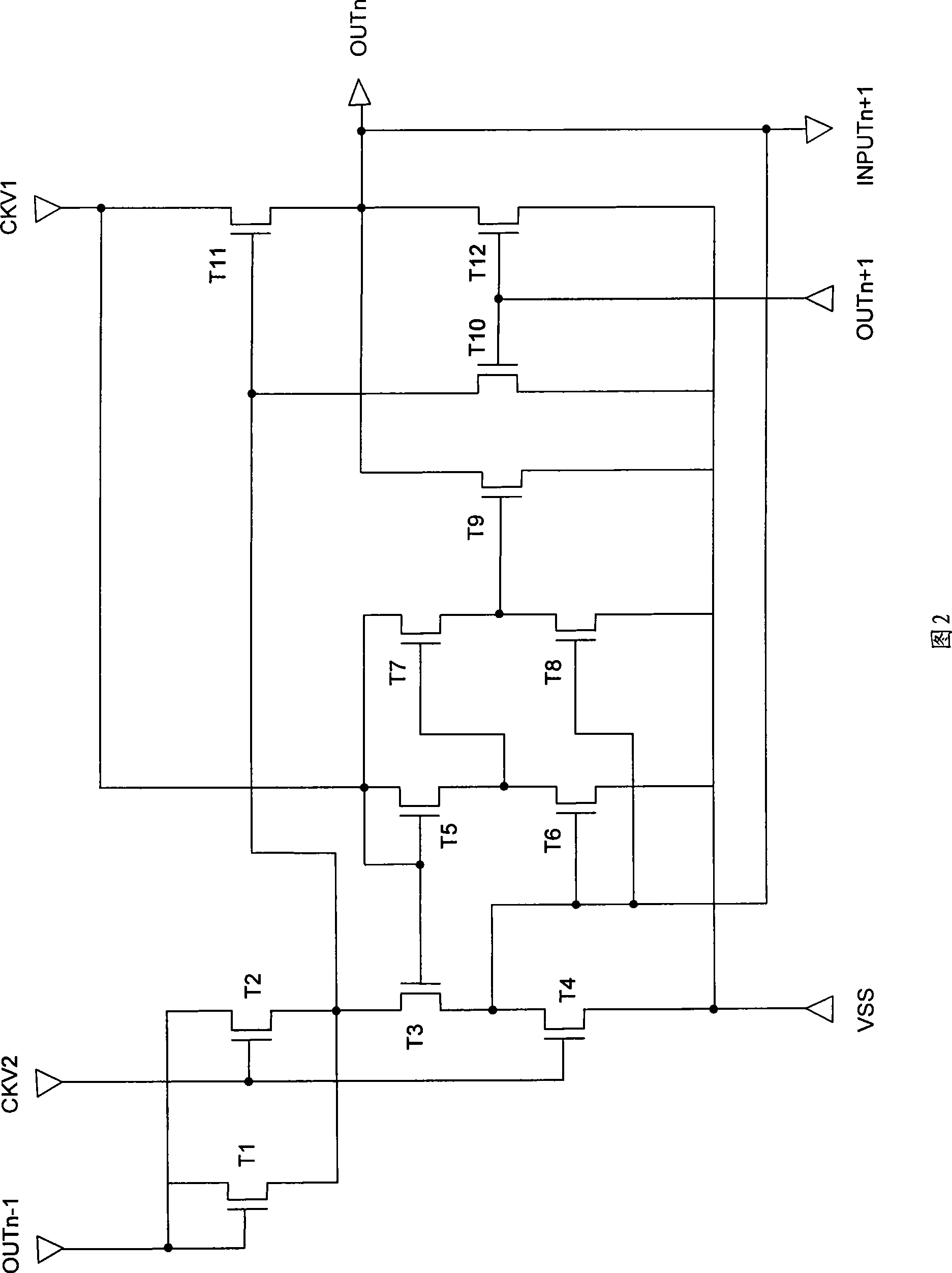

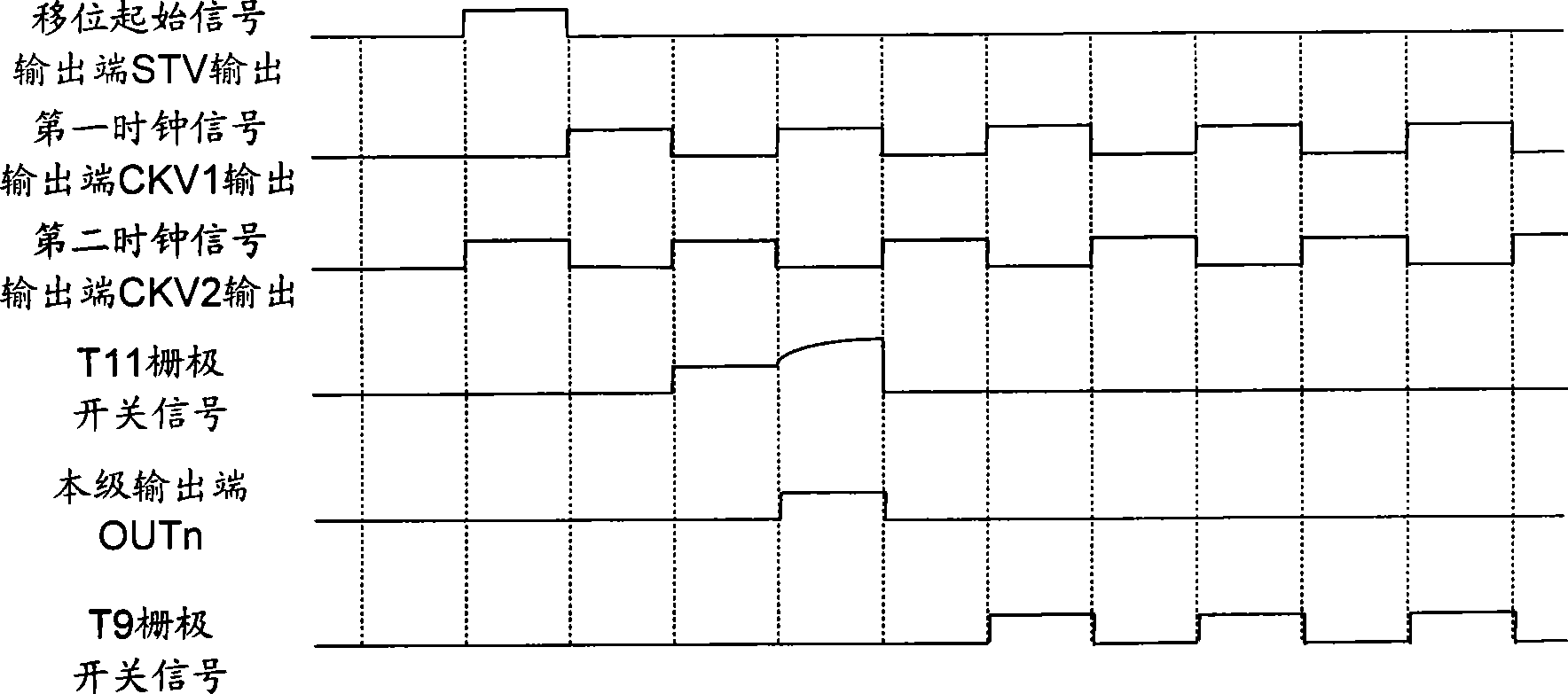

Displacement register and grid drive deivce thereof

The invention relates to a shift register and a gate driving device thereof. The shift register comprises a first film transistor which is directly deposited on an array substrate, a ninth film transistor, an eleventh film transistor and a plurality of control modules. The gate driving device comprises a displacement initial signal output end, a gate off-state voltage output end, a first clock signal output end, a second clock signal output end, a first shift register and a second shift register. The shift register and the gate driving device lower the gate bias stress of the film transistor, avoid the rise of the gate threshold voltage to the maximum, prolong the service life of the film transistor and avoid the misoperation that the film transistor is closed during the invalid state. Compared with the prior art, no additional power supplying circuit is required, the circuit is simple, the stable working can be ensured, and the cost is low.

Owner:K TRONICS (SUZHOU) TECH CO LTD +1

Array testing method using electric bias stress for TFT array

ActiveUS7327158B1Low costElectric discharge tubesStatic indicating devicesElectricityLiquid-crystal display

A method of detecting thin film transistor (TFT) defects in a TFT-liquid crystal display (LCD) panel, includes, in part, applying a stress bias to the TFTs disposed on the panel; and detecting a change in electrical characteristics of the TFTs. The change in the electrical characteristics of the TFTs may be detected using a voltage imaging optical system or an electron beam. The panel temperature may be varied while the bias stress is being applied. The change in the electrical characteristics is optionally detected across an array of the TFTs.

Owner:ORBOTECH LTD

Pixel circuit and driving method

ActiveCN111028767AGuaranteed stabilityDrift suppressionStatic indicating devicesControl signalHemt circuits

The invention discloses a pixel circuit and a driving method. The pixel circuit comprises a switching transistor, a driving transistor, a storage capacitor, a light emitting device and a reset module;the switching transistor is used for writing a data signal into a grid electrode of the driving transistor in data signal writing and light emitting stages, and the driving transistor drives the light emitting device to emit light according to the data signal; the reset module is used for outputting a reset signal to the grid electrode of the driving transistor according to the reset control signal in the reset signal writing and reset stage so as to neutralize the bias stress borne by the driving transistor in the data signal writing and light emitting stage, restrain further drifting of thethreshold voltage and guarantee the stability of the light-emitting brightness of the light emitting device.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

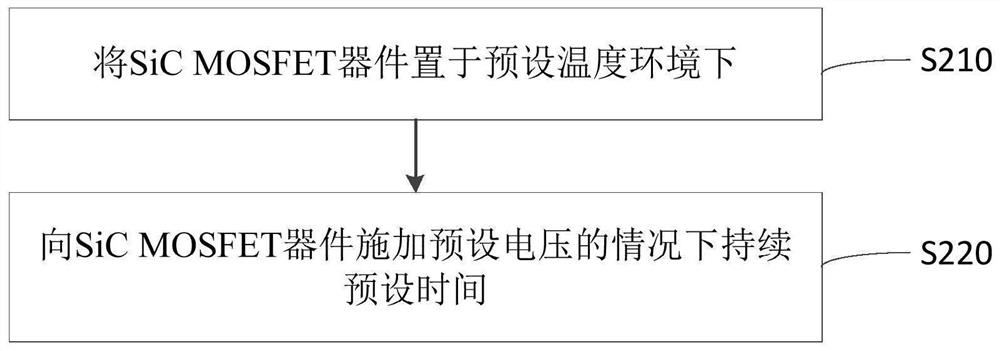

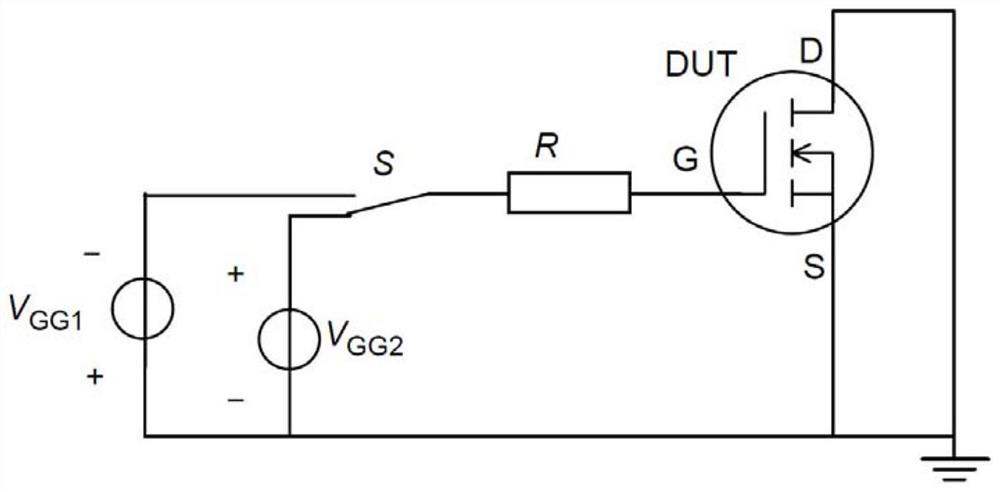

High-temperature grid bias test method of SiC MOSFET device, computer equipment and storage medium

ActiveCN113358991AAvoid inaccurate testingAccurate assessmentIndividual semiconductor device testingMOSFETComputational physics

The invention relates to the technical field of high-temperature grid bias tests, and discloses a high-temperature grid bias test method of a SiC MOSFET device, a computer device and a storage medium. When electrical parameter tests are carried out on the SiC MOSFET device in different test nodes for carrying out the high-temperature grid bias test on the SiC MOSFET device, if the measurement of the SiC MOSFET device is not completed in time, stress interruption time of the SiC MOSFET device can be evaluated, extra stress application time of the SiC MOSFET device can be obtained according to a pre-obtained function relation between a threshold voltage drift change rate of the SiC MOSFET device and the stress interruption time and the extra stress application time after interruption, the bias stress of the extra stress application time is applied to the SiC MOSFET device, so that after a threshold voltage on the SiC MOSFET device is recovered to a preset threshold value, and the SiC MOSFET device is measured in time, thereby guaranteeing that the measured threshold voltage can represent the real drift condition of the SiC MOSFET device at the moment.

Owner:CHINA ELECTRONICS PROD RELIABILITY & ENVIRONMENTAL TESTING RES INST

TFT pixel threshold voltage compensation circuit with a source follower

ActiveUS11170719B1Eliminate the effects ofImprove display uniformityStatic indicating devicesSolid-state devicesDisplay deviceHemt circuits

An enhanced pixel circuit for a display device provides separate compensation and data programming phases to permit minimization of the programming time. Variations in voltage supplies are accounted for by isolating the drive transistor from such power supply by using a second drive transistor configured as source follower relative to the first drive transistor. An on bias stress transistor is incorporated that can electrically connect the first drive transistor to the power supply during an on bias stress operation. During such operation, a voltage stress is applied to eliminate hysteresis effects associated with the drive transistor. The on bias stress operation may be performed as part of a refresh operation during which a data voltage is programmed to the pixel circuit, or as part of a low frequency operation during which a previously programming data voltage is maintained which reduces power consumption.

Owner:SHARP KK

Test flow to detect a latent leaky bit of a non-volatile memory

A technique for detecting a leaky bit of a non-volatile memory includes erasing cells of a non-volatile memory. A bias stress is applied to the cells subsequent to the erasing. An erase verify operation is performed on the cells subsequent to the applying a bias stress to the cells. Finally, it is determined whether the cells pass or fail the erase verify operation based on whether respective threshold voltages of the cells are below an erase verify level.

Owner:NXP USA INC

Electronic display with hybrid in-pixel and external compensation

ActiveCN112201208AReduce flickerImprove low refresh rate performanceStatic indicating devicesSemiconductor devicesDisplay deviceEngineering

The invention relates to an electronic display with a hybrid in-pixel and external compensation. A display pixel is provided that is operable to support hybrid compensation scheme having both in-pixelthreshold voltage canceling and external threshold voltage compensation. The display may include multiple p-type silicon transistors with at least one n-type semiconducting-oxide transistor and one storage capacitor. An on-bias stress phase may be performed prior to a threshold voltage sampling and data programming phase to mitigate hysteresis and improve first frame response. In low refresh ratedisplays, a first additional on-bias stress operation can be performed separate from the threshold voltage sampling and data programming phase during a refresh frame and a second additional on-bias stress operation can be performed during a vertical blanking frame. The display pixel may be configured to receive an initialization voltage and an anode reset voltage, either of which can be dynamically tuned to match the stress of the first and second additional on-bias stress operations to minimize flicker.

Owner:APPLE INC

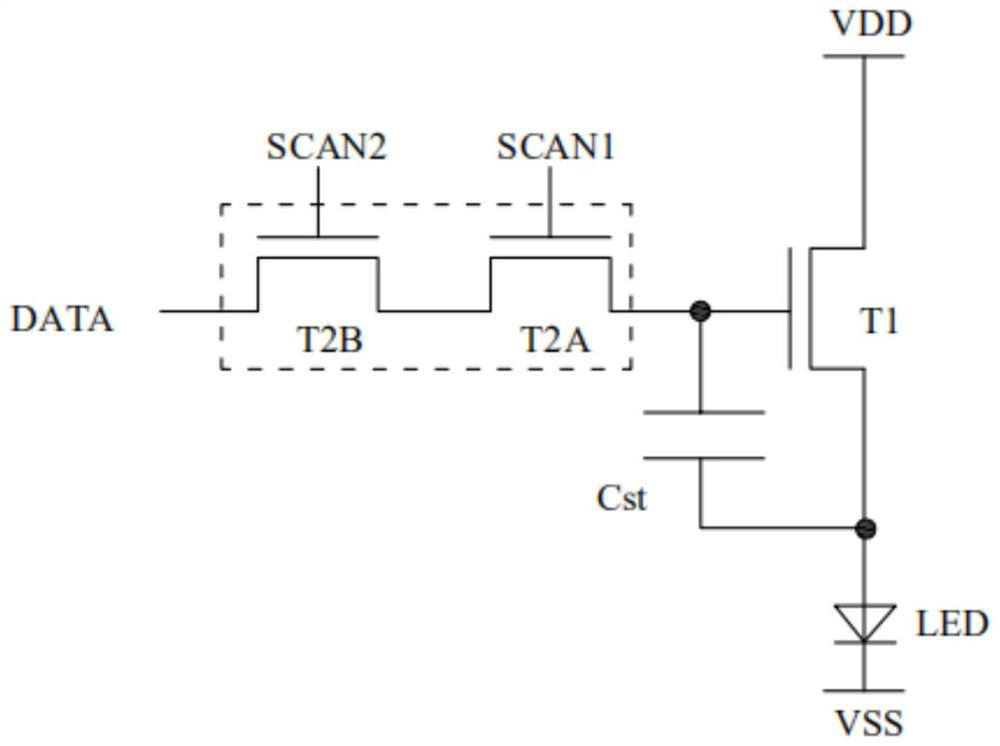

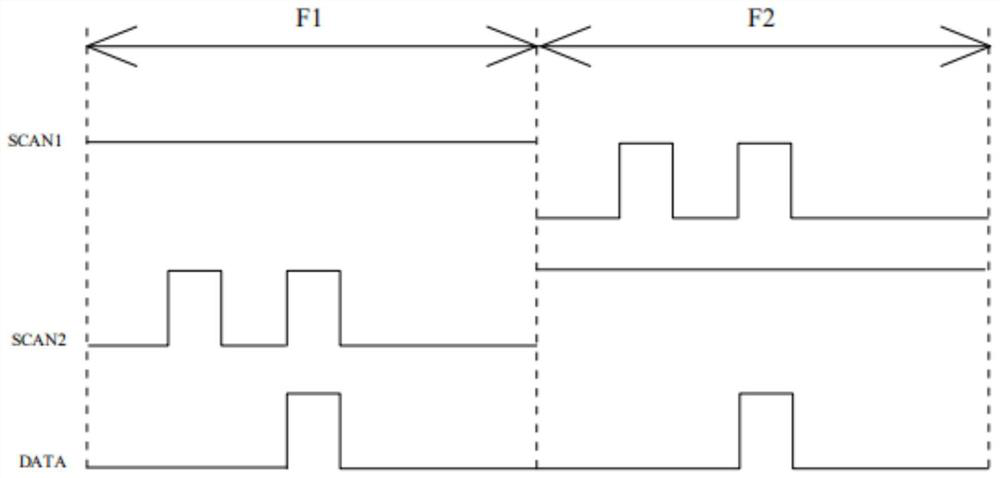

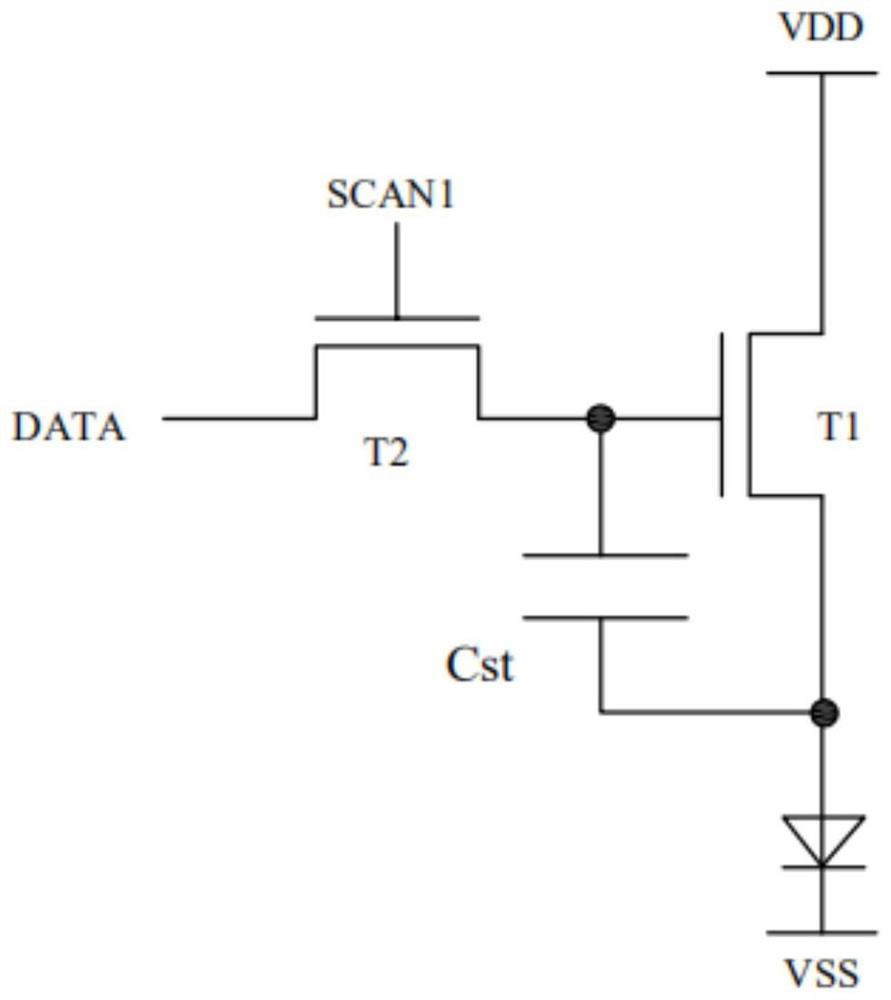

Driving circuit, driving method thereof and display device

ActiveCN111986622AAvoid crosstalkImprove stabilityStatic indicating devicesDisplay deviceHemt circuits

The application provides a driving circuit, a driving method thereof and a display device. A first switch connected with a grid electrode of a driving transistor is enabled to be in a first state in aprevious frame and in a second state in a current frame; a second switch connected in series with the first switch is in a second state in the previous frame and is in a first state in the current frame, wherein the first state is one of a conduction and cut-off switching state and a continuous conduction state and the second state is the other one of the conduction and cut-off switching state and the continuous conduction state; therefore, the bias stress accumulated by the first switch and the second switch in the previous frame is opposite to the bias stress accumulated by the first switchand the second switch in the current frame, threshold voltage drifting of the first switch and the second switch is avoided, the stability of the first switch and the second switch is improved, and aproblem of low-frequency display failure caused by gate leakage of the driving transistor due to poor stability is solved. And the first switch and the second switch are alternately in a conduction and cut-off switching state to avoid crosstalk of signals written into the gate of the driving transistor.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD