Oxide semiconductor film transistor trap state density extraction method

A technology of oxide semiconductors and thin film transistors, which is applied in the field of trap state density extraction of oxide semiconductor thin film transistors, and can solve problems such as changes in trap state distribution, difficult extraction of oxide semiconductor thin film transistors, and changes in material properties.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

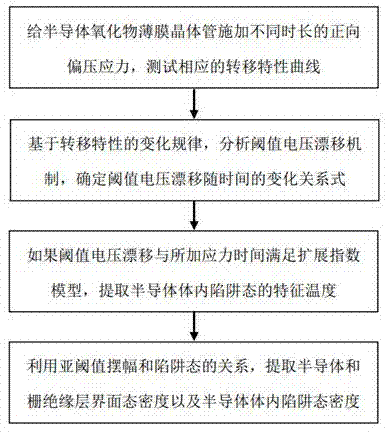

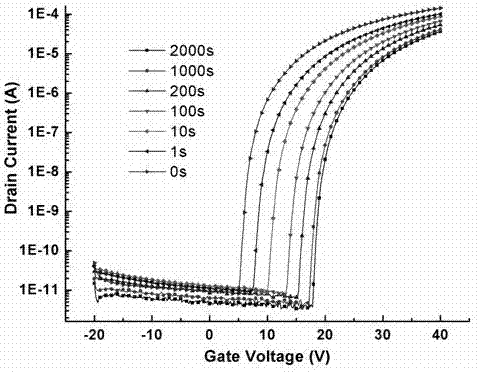

[0037] The object of the present invention is to provide a method for extracting the trap state density of oxide semiconductor thin film transistors, by measuring the transfer characteristic curves of oxide semiconductor thin film transistors under different time-length positive bias stresses at room temperature, if the threshold voltage drift and the applied stress time meet By extending the exponential model, the bulk state and interface state densities of thin film transistors can be calculated. The flowchart of the method is shown in figure 1 . The characteristic temperature of the trap state in the semiconductor body is extracted through the relationship between the threshold voltage drift and the time of the applied stress. obtained by calculation.

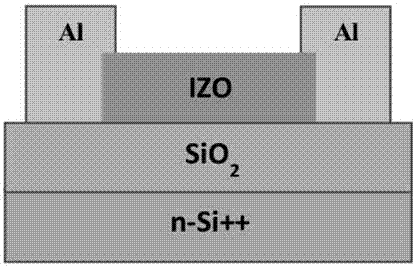

[0038]The specific embodiment of the present invention one is to adopt the trap state density extraction method of the oxide semiconductor thin film transistor provided by the present invention to extract the IZO / SiO of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More